# Portland State University PDXScholar

Dissertations and Theses

Dissertations and Theses

6-6-2018

# New Approaches for Memristive Logic Computations

Muayad Jaafar Aljafar Portland State University

# Let us know how access to this document benefits you.

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Aljafar, Muayad Jaafar, "New Approaches for Memristive Logic Computations" (2018). Dissertations and Theses. Paper 4372.

10.15760/etd.6256

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

New Approaches for Memristive Logic Computations

by

Muayad Jaafar Aljafar

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

> Dissertation Committee: Marek A. Perkowski, Chair John M. Acken Xiaoyu Song Steven Bleiler

Portland State University 2018

© 2018 Muayad Jaafar Aljafar

#### Abstract

Over the past five decades, exponential advances in device integration in microelectronics for memory and computation applications have been observed. These advances are closely related to miniaturization in integrated circuit technologies. However, this miniaturization is reaching the physical limit (i.e., the end of Moore's Law). This miniaturization is also causing a dramatic problem of heat dissipation in integrated circuits. Additionally, approaching the physical limit of semiconductor devices in fabrication process increases the delay of moving data between computing and memory units hence decreasing the performance. The market requirements for faster computers with lower power consumption can be addressed by new emerging technologies such as memristors.

Memristors are non-volatile and nanoscale devices and can be used for building memory arrays with very high density (extending Moore's law). Memristors can also be used to perform stateful logic operations where the same devices are used for logic and memory, enabling in-memory logic. In other words, memristor-based stateful logic enables a new computing paradigm of combining calculation and memory units (versus von Neumann architecture of separating calculation and memory units). This reduces the delays between processor and memory by eliminating redundant reloading of reusable values. In addition, memristors consume low power hence can decrease the large amounts of power dissipation in silicon chips hitting their size limit.

The primary focus of this research is to develop the circuit implementations for logic computations based on memristors. These implementations significantly improve the performance and decrease the power of digital circuits. This dissertation demonstrates inmemory computing using novel memristive logic gates, which we call *volistors* (voltageresistor gates). Volistors capitalize on rectifying memristors, i.e., a type of memristors with diode-like behavior, and use voltage at input and resistance at output. In addition, *programmable diode gates*, i.e., another type of logic gates implemented with rectifying memristors are proposed. In programmable diode gates, memristors are used only as switches (unlike volistor gates which utilize both memory and switching characteristics of the memristors). The programmable diode gates can be used with CMOS gates to increase the logic density. As an example, a circuit implementation for calculating logic functions in generalized ESOP (Exclusive-OR-Sum-of-Products) form and multilevel XOR network are described. As opposed to the stateful logic gates, a combination of both proposed logic styles decreases the power and improves the performance of digital circuits realizing twolevel logic functions Sum-of-Products or Product-of-Sums.

This dissertation also proposes a general 3-dimentional circuit architecture for inmemory computing. This circuit consists of a number of stacked crossbar arrays which all can simultaneously be used for logic computing. These arrays communicate through CMOS peripheral circuits. Dedication Seek knowledge from the cradle to the grave, Prophet Muhammad. To Noor, with love To Mustafa and Murtaza To my parents

#### Acknowledgements

I would like to thank my advisor, Dr. Marek Perkowski. He has been supportive since the days I began to learn about the basics of this research. My dissertation committee guided me through all these years. Thank you to John Acken, Xiaoyu Song and Steven Bleiler. Specially, I thank Dr. John Acken for patient guidance, encouragement and advice.

I thank my family. Their support has been unconditional all these years; they have given up many things for my success; they have cherished with me every great moment and supported me whenever I needed it.

Last and certainly not least, I thank the higher committee for education development in Iraq (HCED-Iraq) for their generous support.

### Table of Contents

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                              | i                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Dedication                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iii                                                      |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iv                                                       |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                        | viii                                                     |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ix                                                       |

| List of Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                 | xvi                                                      |

| Chapter 1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                        |

| <ul> <li>1.1 Introduction</li> <li>1.2 Memristor: The Missing Circuit Element</li> <li>1.3 The Missing Memristor is Found <ul> <li>1.3.1 Linear ion drift model</li> <li>1.3.2 Non-linear ion drift model</li> </ul> </li> <li>1.4 Applications <ul> <li>1.5 Research Goals and Methods</li> <li>1.6 Research Structure</li> </ul> </li> </ul>                                                                                                                        | 1<br>2<br>4<br>4<br>6<br>9<br>10<br>10                   |

| Chapter 2 Memristive Stateful Logic Gates                                                                                                                                                                                                                                                                                                                                                                                                                             | 12                                                       |

| <ul> <li>2.1 Introduction</li> <li>2.2 Crossbar Architecture</li> <li>2.3 Rectifying Memristors</li> <li>2.4 Stateful Logic Gates Realized with Typical Memristors</li> <li>2.5 Stateful Logic Gates with Rectifying Memristors</li> <li>2.6 Two-Input Multi-Output INH Gate</li> <li>2.7 EISD: Extended IMP Sequential Diagram</li> <li>2.8 Multi-Dimensional Crossbar Array</li> <li>2.9 Logic Computations in a Crossbar Array</li> <li>2.10 Conclusion</li> </ul> | 12<br>14<br>16<br>19<br>23<br>27<br>31<br>35<br>42<br>45 |

| Chapter 3 Memristive Volistor Logic Gates                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                       |

| <ul> <li>3.1 Introduction</li> <li>3.2 Volistor Logic</li> <li>3.2.1 Crossbar Structure</li> <li>3.2.2 Volistor NOT gate in a one-dimensional array</li> <li>3.2.3 Volistor NOR gate in a one-dimensional array</li> <li>3.2.4 Volistor AND gate in one-dimensional array</li> <li>3.2.5 Volistor OR and NAND gates one-dimensional array</li> <li>3.2.6 Mixed-input logic gates in one-dimensional array</li> </ul>                                                  | 46<br>48<br>48<br>51<br>53<br>55<br>55<br>56             |

| <ul><li>3.3 Hybrid Approach to Synthesize Boolean Functions in Crossbar Arrays</li><li>3.3.1 Hybrid computation in a one-dimensional array</li></ul>                                                                                                                                                                                                                                                                                                                  | 57<br>58                                                 |

| 3.3.3Hybrid computation in a crossbar network63.4Volistor Logic Power Consumption73.4.1Power analysis and switching delay in a $1 \times 8$ crossbar array for $S_1 > 0$ 73.4.2Power analysis in a $1 \times 8$ crossbar array for $S_1 = 0$ 73.4.3Power analysis and switching delay in a $1 \times 64$ Crossbar Arrays for $S_1 > 0$ 8                                        | 61<br>64<br>71<br>74<br>76<br>80<br>84             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Chapter 4 Memristive Programmable Diode Logic Gates 8                                                                                                                                                                                                                                                                                                                           | 86                                                 |

| 4.1 Implementation Approach 8                                                                                                                                                                                                                                                                                                                                                   | 86                                                 |

| Chapter 5 A Time-Efficient CMOS-Memristive Programmable Circuit Realizing Logi<br>Functions in Generalized AND-XOR Structures 9                                                                                                                                                                                                                                                 | gic<br>91                                          |

| 5.2 A Generalized ESOP Structure 9                                                                                                                                                                                                                                                                                                                                              | 03<br>04<br>11<br>14                               |

| Chapter 6 Multi-Input Volistor XNOR Gates 12                                                                                                                                                                                                                                                                                                                                    | 20                                                 |

| 6.1 Introduction126.2 Review of Rectifying Memristors, Volistors, and Programmable Diode Gates126.2.1 Rectifying memristors126.2.2 Volistor logic126.2.3 Memristive diode logic126.3 Two-Input Volistor XNOR Gate126.3.1 Setting operation126.3.2 Write operation126.3.3 Read operation126.3.4 Circuit simulation126.4 N-input Volistor XNOR Gate136.5 Summary and Conclusion13 | 22<br>23<br>23<br>24<br>25<br>25<br>26<br>26<br>30 |

| Chapter 7 Volistor Logic Gates in Crossbar Arrays of Rectifying Memristors 13                                                                                                                                                                                                                                                                                                   | 34                                                 |

| 7.1 Introduction137.2 Circuit Structure for Volistor Logic Gates137.3 Review of Volistor Gates in One-Dimensional Arrays137.3.1 Volistor NOR gate147.3.2 Input-volistor NOR gate147.4 Volistor Gates in Two-Dimensional Arrays14                                                                                                                                                | 37<br>39<br>40<br>41                               |

| 7.4.1 Improved volistor NOR gate                                | 143 |

|-----------------------------------------------------------------|-----|

| 7.4.2 Deselect of volistor NOR gate                             | 145 |

| 7.4.3 Volistor AND gate                                         | 147 |

| 7.4.4 Volistor COPY gate                                        | 149 |

| 7.5 Input-Volistor Gates in Two-Dimensional Arrays              | 150 |

| 7.5.1 Input-volistor INH gate                                   | 150 |

| 7.5.2 Input-volistor AND gate                                   | 151 |

| 7.6 Design Constraints of Volistor gates in Crossbar Arrays     | 151 |

| 7.6.1 Design constraints of improved volistor NOR gate          | 151 |

| 7.6.2 Design constraints of input-volistor NOR gate             | 154 |

| 7.6.3 Design constraints of input-volistor AND gate             | 156 |

| 7.7 Implementation Example and Comparisons                      | 157 |

| 7.7.1 Memristive programmable diode gates                       | 158 |

| 7.7.2 Realization of a multi-output AND-OR function in the mPLA | 159 |

| 7.7.3 Comparisons of the mPLA implementations                   | 160 |

| 7.8 Conclusion                                                  | 165 |

| Chapter 8 Memristive Circuit Architectures                      | 166 |

| 8.1 Memristive Circuit Architecture for Logic Computations      | 166 |

| Chapter 9 Summary, Conclusion, Achievements, and Future Work    | 172 |

| 9.1 Summary and conclusion                                      | 172 |

| 9.2 Achievements and publications                               | 175 |

| 1                                                               |     |

| Terminal References                                             | 177 |

| Appendix Power Properties                                       | 184 |

|                                                                 |     |

# List of Tables

| Table 2.1. Memristor's SPICE model parameters [47]                                                                                                        | 17  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 2.2.</b> Truth table of the IMPLY operation, $q + = p \rightarrow q = \neg p + q$                                                                | 22  |

| <b>Table 2.3.</b> Truth table of the INHIBIT operation $q^+$ : $p \rightarrow q = (\neg p) q$                                                             | 22  |

| <b>Table 2.4.</b> Logic gates realized by all possible voltage polarities and keeper/no                                                                   | 22  |

| keeper circuit combinations                                                                                                                               |     |

| Table 2.5. Logic gates realized by all possible polarity combinations in a crossbar                                                                       | 24  |

| array of rectifying memristors                                                                                                                            |     |

| <b>Table 2.6.</b> Tradeoffs for logic implementations in a crossbar array of typical and                                                                  | 26  |

| rectifying memristors                                                                                                                                     | 20  |

| Table 3.1. Implementation of multi-output volistor NOT gate                                                                                               | 53  |

| Table 3.2. Implementation of multi-input single-output volistor NOR gate                                                                                  | 54  |

| Table 3.2. Implementation of math input single output volision (volt gate         Table 3.3. Multiple logic structures and their De-Morgan's equivalences | 64  |

| Table 3.3. Multiple logic structures and then De-Morgan's equivalences         Table 3.4. Power consumption in each crossbar element                      | 73  |

| <b>Table 3.5.</b> Power consumption in each crossoal clement<br><b>Table 3.5.</b> Power consumption, switching delay, and power ration in a $1 \times 8$  | 73  |

| crossbar array                                                                                                                                            | 15  |

|                                                                                                                                                           | 77  |

| <b>Table 3.6.</b> Calculating $\frac{P_{SL}}{P_{VL}}$ in a 1 × 8 crossbar array for $S_1 = 0$ and $S_0$ varied from 1                                     | 11  |

| to 7                                                                                                                                                      |     |

| <b>Table 3.7.</b> Calculating $\frac{P_{SL}}{P_{VL}}$ in a 1 × 8 crossbar array for $S_1 = 0$ and varied $S_0$ and T                                      | 78  |

| <b>Table 3.8.</b> Calculating $\frac{P_{SL}}{P_{VI}}$ in a 1 × 8 crossbar array when $S_1 = 0$                                                            | 79  |

|                                                                                                                                                           |     |

| <b>Table 3.9.</b> Delay and power comparisons in a $1 \times 64$ crossbar array for varied $S_1$                                                          | 83  |

| and $S_0 \ge 33$                                                                                                                                          |     |

| <b>Table 3.10.</b> Delay and power comparisons in a $1 \times 64$ crossbar array for constant                                                             | 83  |

| $S_1$ and varied T                                                                                                                                        |     |

| <b>Table 3.11.</b> Delay and power comparisons in a $1 \times 64$ crossbar array for varied $S_1$                                                         | 84  |

| and $S_0 > 33$                                                                                                                                            |     |

| <b>Table 3.12.</b> Delay and power comparisons in a $1 \times 64$ crossbar array for varied T                                                             | 84  |

| Table 5.1. Number of products and literals of benchmark functions [65]                                                                                    | 96  |

| Table 5.2. Comparison of circuit implementation using diode gates with that of                                                                            | 117 |

| other logics styles                                                                                                                                       |     |

| Table 6.1. XNOR configuration                                                                                                                             | 127 |

| Table 6.2. Memristor Parameters                                                                                                                           | 127 |

| <b>Table 6.3.</b> Average power consumption of a two-input XNOR gate during setting,                                                                      | 129 |

| write, and read operations (values are in micro joules)                                                                                                   | -   |

| Table 6.4. Multiple realizations of 2-input primitive memristive XOR/XNOR                                                                                 | 129 |

| gates                                                                                                                                                     | 12) |

| Table 6.5. Multi-input XNOR circuit configuration                                                                                                         | 131 |

| Table 6.6. Different logic circuits of n-input XOR/XNOR memristive gates                                                                                  | 131 |

| Table 0.0. Different logic circuits of in-input XOR/MOOK memilistive gates         Table 7.1 Voltage levels required during the operations                | 131 |

| Table 7.1 Voltage levels required during the operations         Table 7.2 Volistor operations and their input locations                                   | 138 |

| Table 7.2 volision operations and then input locations         Table 7.3 Delay of multiple mPLA circuits                                                  | 164 |

| <b>Lusic</b> <i>in</i> Delay of multiple in LA circuits                                                                                                   | 107 |

|                                                                                                                                                           |     |

# List of Figures

| Figure 1.1. Four fundamental passive circuit elements [Redrawn from 2].                                               | 2  |

|-----------------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1.2.</b> <i>i-v</i> characteristic of the memristor for a rectangular pulse input. (Left)                   | 4  |

| Input voltage applied across the memristor. (Right) hysteresis behavior of the memristor.                             |    |

| Figure 1.3. (a) Structure of the HP example of memristor. (b) Circuit equivalent.                                     | 5  |

| [Redrawn from 2]                                                                                                      |    |

| Figure 1.4. The schematic of memristive device realized using tunnel barrier                                          | 8  |

| where $w$ and $Rs$ represent the state variable and the electroformed                                                 |    |

| channel resistor [Redrawn from 12].                                                                                   |    |

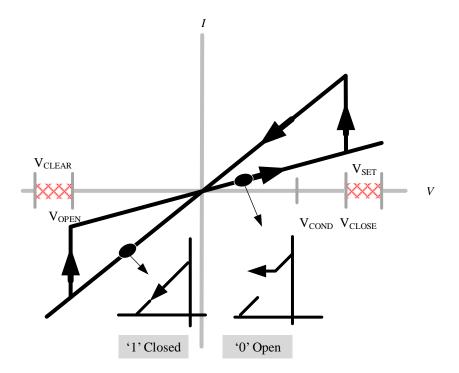

| Figure 2.1. Idealized hysteretic behavior of the memristor in the $i$ - $v$ plane. $V_{CLOSE}$                        | 13 |

| and $V_{OPEN}$ are threshold voltages, and $V_{SET}$ and $V_{CLEAR}$ are                                              |    |

| programming voltages.                                                                                                 |    |

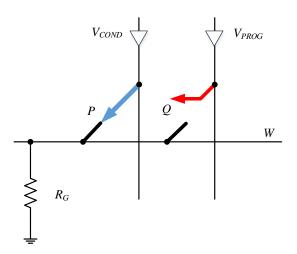

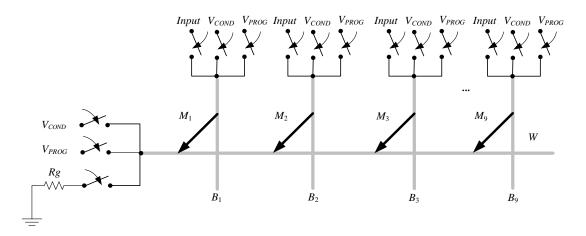

| <b>Figure 2.2.</b> Schematic diagram of a $1 \times 2$ crossbar array. The instant application                        | 16 |

| of voltage pulses $V_{COND}$ and $V_{PROG}$ to switches P and Q,                                                      |    |

| respectively, may toggle the logic state of $Q$ depending on the initial                                              |    |

| state of $P$ and $Q$ .                                                                                                | 10 |

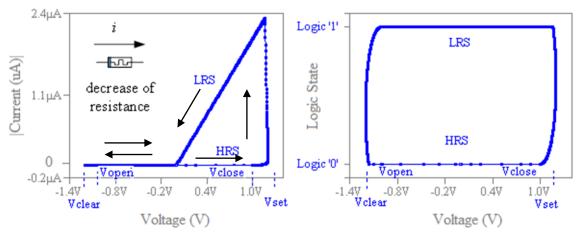

| <b>Figure 2.3.</b> Characteristics of a rectifying memristor. (Left) The <i>i-v</i> characteristic                    | 18 |

| of the memristor. (Right) The <i>s</i> - <i>v</i> characteristic of a memristor. The                                  |    |

| diagrams are depicted using the LTspice simulator and the                                                             |    |

| memristor model in [47].                                                                                              | 25 |

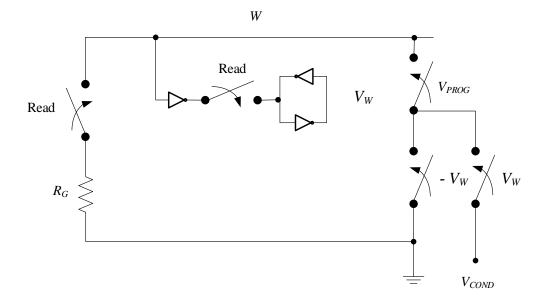

| <b>Figure 2.4.</b> Schematic of a keeper circuit [Redrawn from 48]. $V_W$ denotes the                                 | 25 |

| voltage on <i>W</i> .                                                                                                 | 20 |

| <b>Figure 2.5.</b> Schematic of a $1 \times 9$ crossbar array of rectifying memristors for                            | 28 |

| computing function $F$ .                                                                                              | 20 |

| Figure 2.6. Schematic of memristive computing circuit including control and                                           | 30 |

| datapath units.                                                                                                       |    |

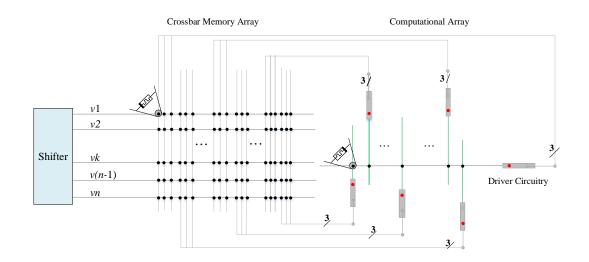

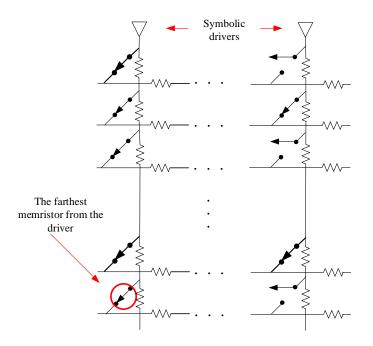

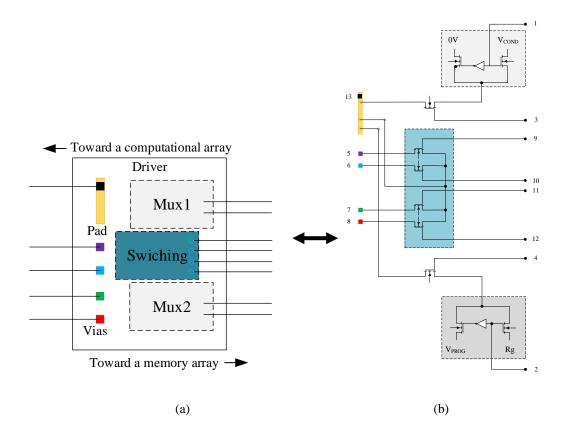

| Figure 2.7. (Left) Schematic of a computational array connected to driver                                             | 31 |

| circuitries. (Right) Schematic of each driver circuitry.                                                              |    |

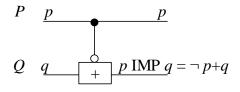

| Figure 2.8. Symbolic diagram of a 2-input IMP gate in ISD notation.                                                   | 31 |

| Figure 2.9. ISD of function NAND $(p, q)$ where the output is stored as a new state                                   | 32 |

| of memristor R.                                                                                                       |    |

| Figure 2.10. Symbolic diagram of a two-input INH gate in EISD notation.                                               | 32 |

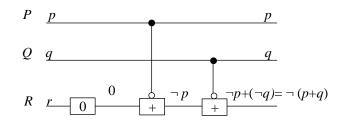

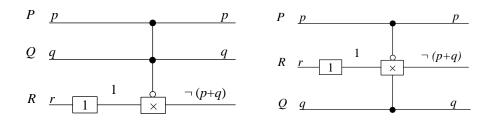

| <b>Figure 2.11.</b> EISD of NOR gate. Different EISD notations for $r = NOR(p, q)$                                    | 33 |

| depending on source and target memristors locations.                                                                  |    |

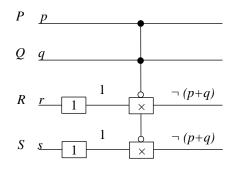

| <b>Figure 2.12.</b> EISD of multi-output function $\{OR \{p, q\} \neq r, OR \{p, q\} \neq s\}$ .                      | 33 |

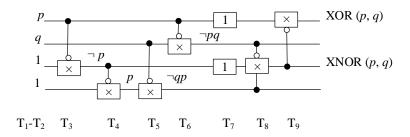

| <b>Figure 2.13.</b> EISD of XOR $(p, q) = [[(p \nrightarrow q) + (q \nrightarrow p)] \nrightarrow 1] \nrightarrow 1.$ | 33 |

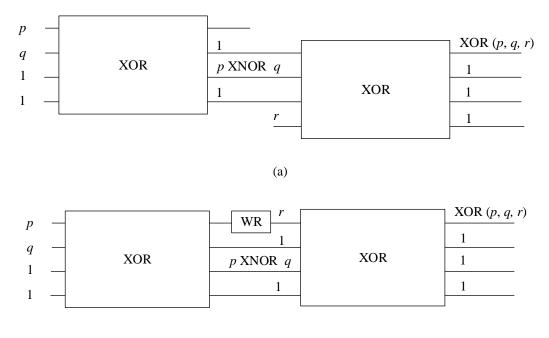

| Figure 2.14. EISD notation of XOR $(p, q, r)$ . (a) The XOR gate is implemented                                       | 34 |

| with 15 operations and five memristors. (b) The XOR gate is                                                           |    |

| implemented with 16 operations and four memristors. The EISD                                                          |    |

| shows the trade-off between the number of memristors and the                                                          |    |

| operations.                                                                                                           |    |

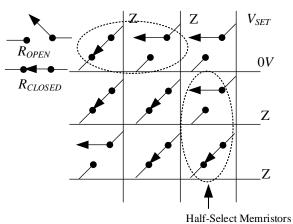

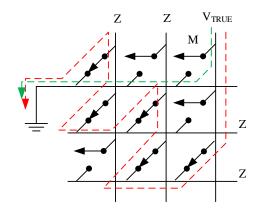

| <b>Figure 2.15.</b> A $3 \times 3$ crossbar array of non-rectifying memristors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

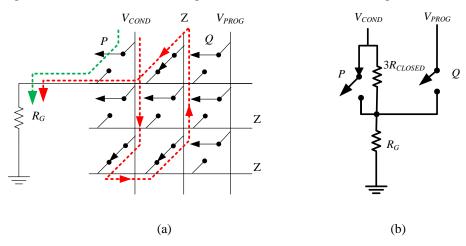

| Figure 2.16. Half-select problem may cause sneak current paths. The green dash-<br>line represents the desired current path whereas the red dash-lined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37 |

| represents an undesired sneak current path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Figure 2.17. (a) The sneak path disturbs the READ and WRITE operations. (b) The circuit equivalent of the crossbar array with sneak path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

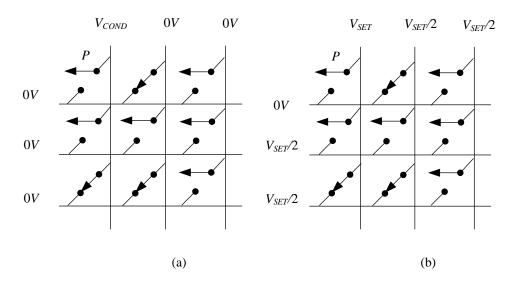

| phenomenon.<br><b>Figure 2.18.</b> Biasing schemes for READ and WRITE operation. These schemes limit the sneak path currents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39 |

| Figure 2.19. The effect of nonzero resistance of wires on the READ and WRITE operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

| Figure 2.20. Schematic of the complete memristor crossbar array. The driver circuitries are illustrated in Fig. 2.7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

| Figure 2.21. Symbolic matrix. The entities show the values of the crossbar memristors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43 |

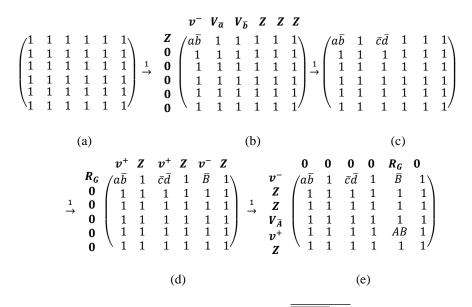

| <b>Figure 2.22.</b> Symbolic matrices illustrate the steps of computing XOR $(p, q, r)$ with INH gates. The number of operations (clock cycles) to implement the XOR gate is 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43 |

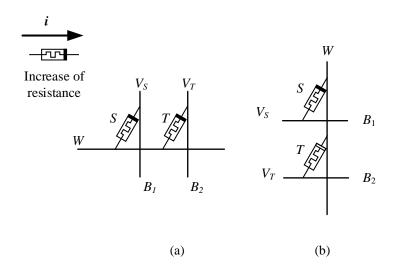

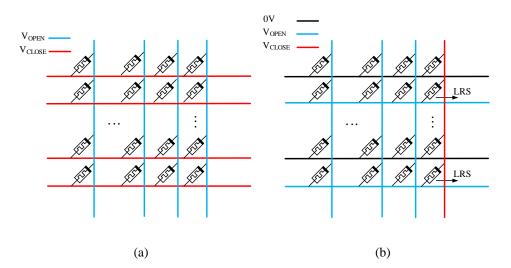

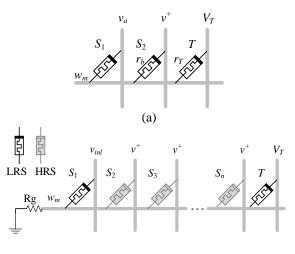

| <b>Figure 3.1.</b> Crossbar arrays. (a) $1 \times 2$ crossbar array. (b) $2 \times 1$ crossbar array. The inset shows the symbolic diagram of a memristor. The flow of current into the device, as shown above, increases the resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

| <b>Figure 3.2.</b> Symbolic illustration of a driver circuit connected to each wire.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50 |

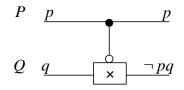

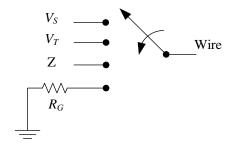

| <ul> <li>Figure 3.3. Symbolic notations for volistor logic gates. (a) Volistor NOT. (b) two-input volistor NOR gate. (c) two-input volistor AND gate. (d) mixed-input NOR gate. Inside the gates, symbols V and R denote whether a signal is a voltage-based or resistance-based, respectively.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51 |

| Figure 3.4. Volistor NOT behavior. (a) $1 \times 8$ crossbar array implementing a four-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52 |

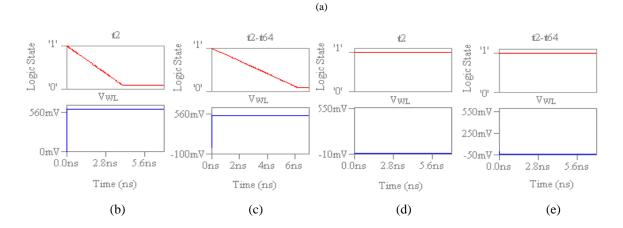

| output NOT and showing arbitrary nature of the locations of source<br>memristors S and target memristors T. The contribution of each<br>memristor is determined by the voltage driver, to which it is<br>connected. Wire W is connected to Z. (b) The operation of a one-<br>output NOT in a $1 \times 2$ array. $V_W$ stabilizes at $\approx 600$ mV indicating<br>$v_s$ = '1' manifesting on W. In addition, $\mathbf{t}_1$ toggles to '0'. (c) The<br>operation of a 63-output NOT in a $1 \times 64$ array. $V_W$ stabilizes and $\mathbf{t}$<br>toggles as in b. (d) The operation of a one-output NOT in a $1 \times 2$<br>array. $V_W$ stabilizes at $\approx 0$ V indicating $v_s$ = '0' manifesting on W. As<br>a result, $\mathbf{t}$ remains '1'. (e) $V_W$ stabilizes as in d. |    |

| <b>Figure 3.5.</b> A $3 \times 1$ crossbar array used to implement a two-input volistor NOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _  |

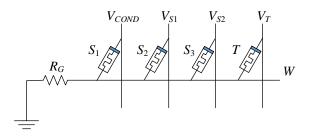

- Figure 3.6. Mixed input NOR. The implementation of a three-input one-output  $S_1$  NOR gate. The resistive input is stored in  $S_1$  and the voltage inputs are applied to  $S_2$  and  $S_3$ . The output is stored in memristor T.

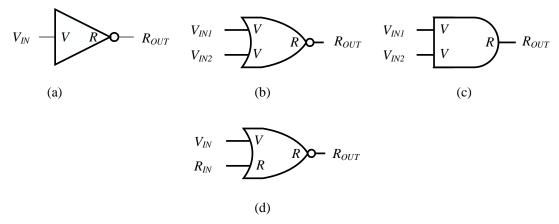

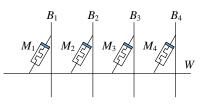

- **Figure 3.7.** Example of logic computation based on hybrid approach in a crossbar array. (a)  $1 \times 4$  crossbar array used to implement SOP function *f*.

(b) Circuit configuration to implement each step. The total number of consecutive operations (pulses) to realize f is 5.

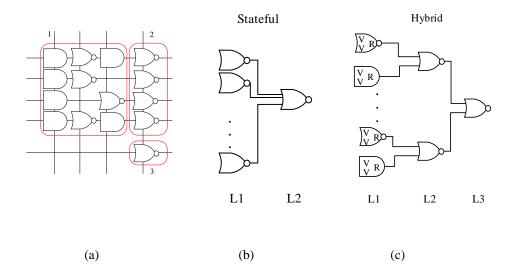

Figure 3.8. Crossbar array. (a) Crossbar array is divided into three sections; gates in section 1 are implemented with volistors but in section 2 and 3 are realized with stateful NOR. (b) The stateful approach realizes two logic levels. (c) However, the hybrid approach realizes three logic levels with the same implementation cost of the stateful approach. Li is the number of logic level.

**Figure 3.9.** Symbolic matrices illustrate the steps of computing  $f = \overline{a\overline{b} + c\overline{d}} + \overline{A}$  64 based on the hybrid approach. (a) Initialization step. (b) Computing  $a\overline{b}$  with volistor AND. (c) Computing  $\overline{cd}$  with volistor AND. (d)

Computing ab + cd with stateful NOR. (e) Computing f with mixed-input NOR.

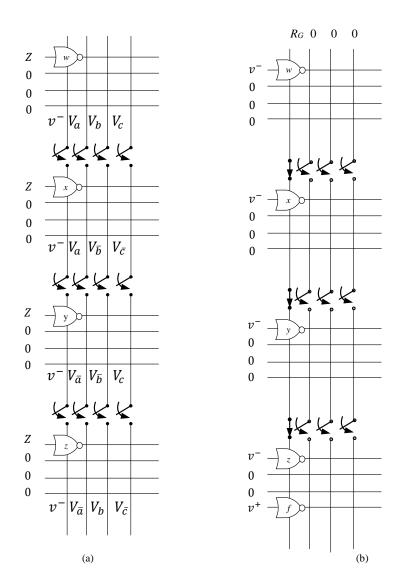

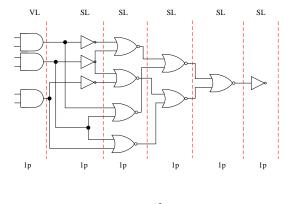

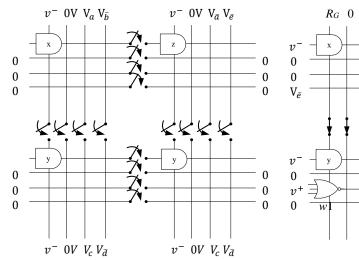

- **Figure 3.10.** Implementation of POS function f in a crossbar network. The function 66 is realized in a two-step process. (a) Realizing the first logic level of function f in separate crossbars. This step produces four NOR gates. (b) Realizing the second logic level of function f in a 16 × 1 crossbar array. This step produces the output of the POS function. The interconnections and voltages applied to the wires show the network configuration in each step.

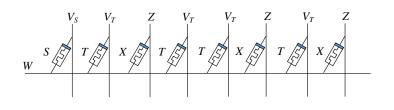

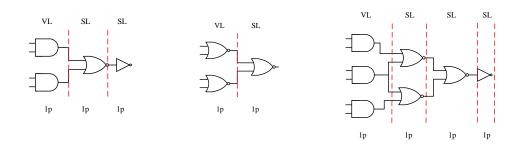

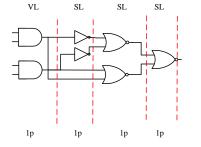

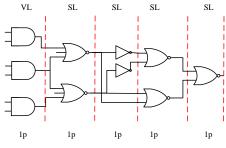

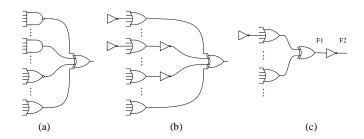

- Figure 3.11. Implementation of Boolean functions in different logic structures based on the hybrid approach. (a) Example of a SOP function. (b) Example of a POS function. (c) Example of a three level sum of products of sums. (d) Example of an XOR of two products. (e) Example of a NAND-AND-XOR logic function. (f) Example of an AND-XOR-OR logic function. 'P' stands for pulse (operation), e.g., 1p indicates one pulse for implementing a logic level. VL and SL stand for volistor and stateful logic operations. In all circuits, only the first logic level is implemented with volistor gates.

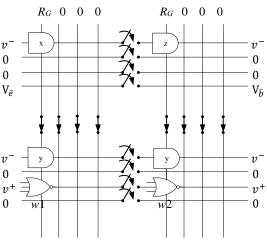

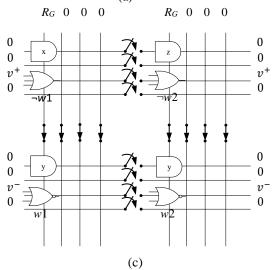

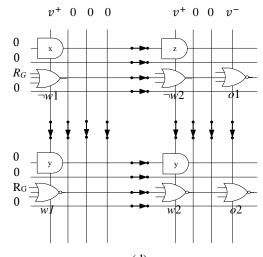

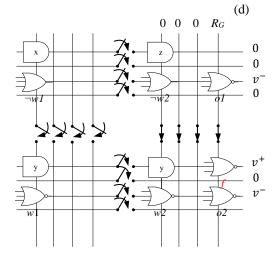

- **Figure 3.12.** Realization of NAND-AND-XOR function *f*. The function is realized 71 in a six-step process in four crossbar arrays. (a) The first logic level is realized with volistors; (b) the second logic level is realized with mixed-input gates; (c)-(e) the other logic levels are realized with stateful logic. Wires are set to 0V,  $v^+$ , or  $v^-$  or connected to GND through load resistor  $R_G$  or to Z. In each step, the operation is depicted by symbolic gates, and the results are shown as outputs of the gates.

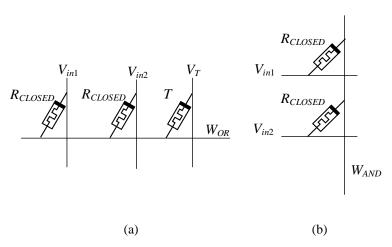

- Figure 4.1. Memristive programmable diode OR gate. (a) A schematic of a two-input diode OR gate implemented with rectifying memristors. (b) The behavior of a two-input diode NOR gate. (c) The relation between the size of a diode NOR gate and its RC delay during the precharge interval. (d) A schematic of a 100-input diode NOR gate. (e) The behavior of 100-input diode NOR gate. (f) A schematic of

a two-input diode NOR with pull-down transistor. (g) The behavior of two-input diode NOR with pull-down transistor.

- Figure 4.2. Memristive programmable diode AND gate. (a) A schematic of a two-input diode AND gate implemented with rectifying memristors. (b) The behavior of a two-input diode NAND gate. (c) Relation between the size and RC delay of a diode NAND gate during the charge interval. (d) A schematic of a 100-input diode NAND gate. (e) The behavior of 100-input diode NAND gate. (f) A schematic diagram of a two-input diode NAND gate with pull-up resistor. (g) The behavior of two-input diode NAND with pull-up resistor.

- Figure 5.1. (a) Schematic of {NAND, AND, NOR, OR}-XOR logic structure. (b)

97 Logical equivalence of {NAND, AND, NOR, OR}-XOR structure as realized in mPLD-XOR. (c) mPLD-XOR realizes functions in NOT-OR-XOR-NOT logic structure.

97

99

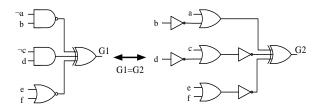

- **Figure 5.2.** Function G1 is implemented as its logical equivalence, G2.

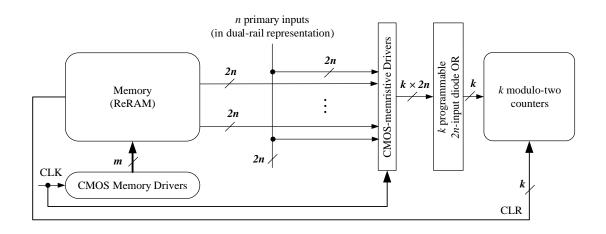

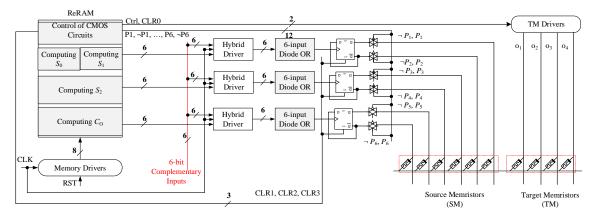

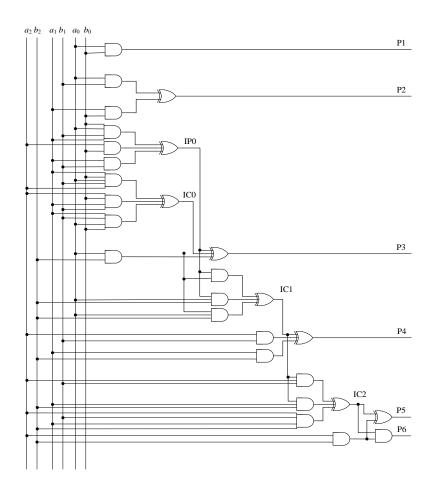

- Figure 5.3. Schematic of the mPLD-XOR.

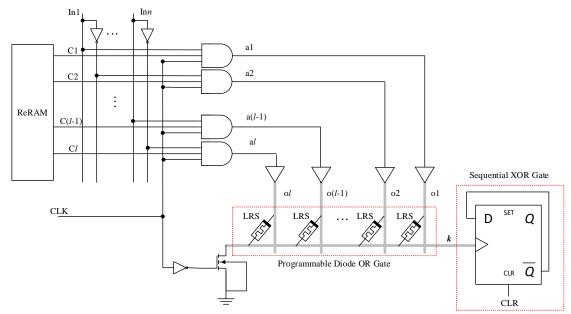

- Figure 5.4. Schematic of an mPLD-XOR for realizing an *n*-input single-output function with *l* lines diode OR where *l*=2*n* to allow for inputs complemented. Ini are the primary inputs where i ∈ {1, ..., n}, and Cj are the control signals stored in ReRAM where j ∈ {1,..., l}. The output of the circuit is Q or Q depending on the function being implemented.

- **Figure 5.5.** Schematic of ReRAM of the mPLD-XOR shown in Figure 5.3 with 100 the reference resistor Rg.

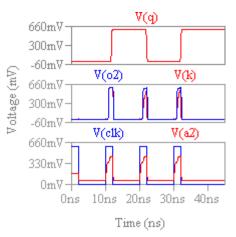

- **Figure 5.6.** Simulation results of the single-output mPLD-XOR shown in Figure 101 5.4 with the ReRAM configuration shown in Figure 5.5.

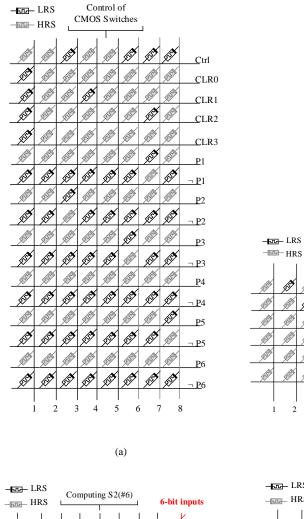

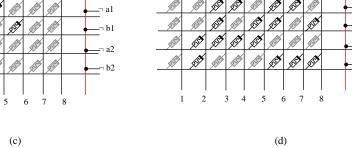

- **Figure 5.7.** Programming the ReRAM. (a) Initializing the ReRAM to HRS (or 103 logic '0'). (b) Programming the right-most column of the ReRAM.

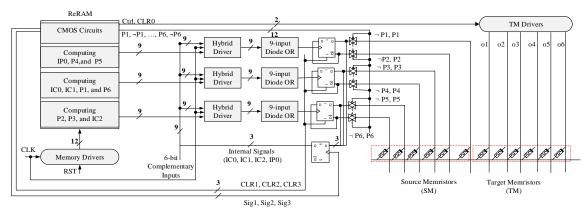

- **Figure 5.8.** Generic fabric of the mPLD-XOR programmed for realizing a 3-bit 104 adder. The grey rectangles correspond to memristive arrays, the white rectangles correspond to hybrid CMOS-memristive circuits, and the rest of the blocks correspond to CMOS circuits.

- **Figure 5.9.** Schematic diagram of sub-ReRAMs. Sub-ReRAM (a) stores the 109 control data for driving CMOS sub-circuits of the mPLD-XOR. Sub-ReRAMs (b)-(d) store control data for realizing  $S_0$  and  $S_1$ ,  $S_2$ , and  $C_o$ , respectively. The number of clock cycles for calculating an output is shown in parenthesis, e.g., (#8). The size of sub-ReRAMs is  $35 \times 8$ .

- **Figure 5.10.** (a)-(j) The computational steps for realizing a 3-bit adder with stateful 111 gates. The total number of IMP and FALSE operations is 29. In each step, the numbers of operations are shown.

- Figure 5.11. Schematic of mPLD-XOR for realizing a 3-bit multiplier. In this 112 implementation, the number of computational steps is 12, and instructions occupy  $47 \times 12$  of the ReRAM size.

- **Figure 5.12.** Schematic diagram of a 3-bit multiplier in a six-level-XOR-network 113 structure with any combination of sums, products, XORs, and literals at the input of any XOR gate. This circuit is implemented with the mPLD-XOR with feedback circuit. The internal signals are stored in the memory cells to decrease the size of the ReRAM.

- Figure 5.13.  $6 \times 16$  crossbar array used to implement a 3-bit multiplier with 113 stateful logic gates. The matrix elements denote initial states of crossbar memristors.

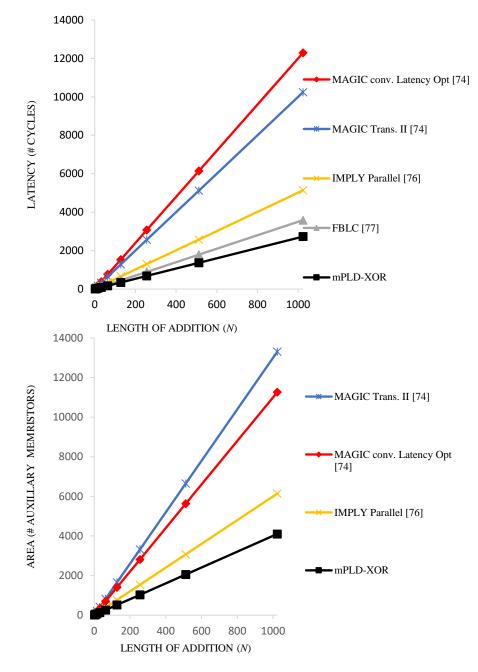

- **Figure 5.14.** Area and delay comparisons of an *N*-bit Adder realized with multiple 116 approaches.

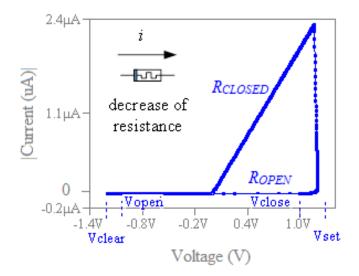

- **Figure 6.1.** The i-v characteristic of a rectifying memristor and its symbolic 122 diagram. The flow of current into the device, as shown above, decreases the resistance.

- **Figure 6.2.** Implementation of memristive gates. (a) Implementation of two-input 124 volistor NOR gate. (b) Implementation of a 2-input programmable diode AND gate.

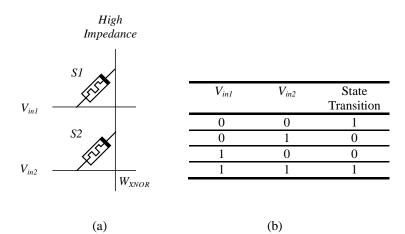

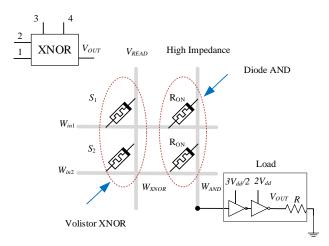

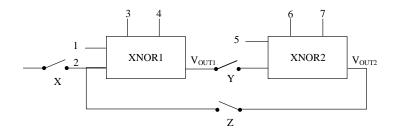

- Figure 6.3. Volistor XNOR gate. (a) Schematic of 2-input volistor XNOR gate. 125 (b) Behavior of volistor XNOR gate.

- **Figure 6.4.** Read operation. Non-destructive voltage  $V_{READ}$  is applied to the 126 volistor XNOR gate to read the output. The inset shows the symbolic diagram of the XNOR gate.

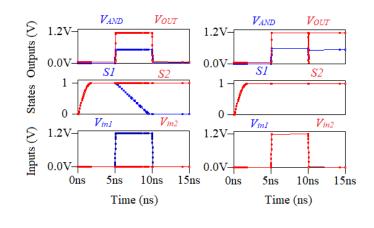

- **Figure 6.5.** XNOR Circuit Simulation. The initial states are (s1, s2) = (0, 0). (a) 128 The circuit behavior when inputs are  $(V_{in1}, V_{in2}) = (1, 0)$ . (b) The circuit behavior when inputs are  $(V_{in1}, V_{in2}) = (1, 0)$ . The outputs,  $V_{AND}$  and  $V_{OUT}$ , are relevant only during the read operation.

- Figure 6.6. Schematic diagram of a multi-input volistor XNOR gate.

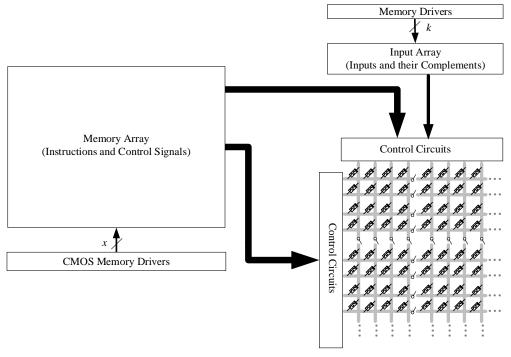

- Figure 7.1. General circuit structure for logic computations based on volistor and 137 stateful gates.

130

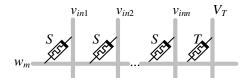

- **Figure 7.2.** Schematic of an n-input volistor NOR gate realized in a  $1 \times (n+1)$  141 memristive array.

- **Figure 7.3.** Implementation of a three-input volistor NOR gate with a fan-out of 141 three. The source memristors are in LRS. Horizontal wires are connected to high impedance Z.

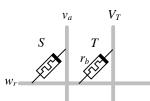

- **Figure 7.4.** (a) Schematic of two-input-volistor NOR gate. Inputs are  $v_a$  and  $r_b$ , 142 and the output is  $r_T$ . (b) Schematic of an *n*-input-volistor NOR gate where all of the inputs are logic '0'.

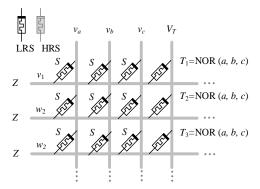

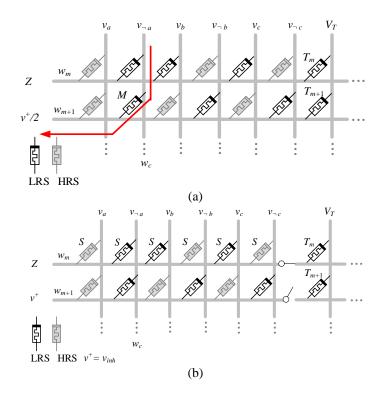

- **Figure 7.5.** Implementation example of multiple volistor NOR gates in a crossbar 144 array. The circuit implements  $T_m = \text{NOR}(a, b, c)$  on  $w_m$  and  $T_{m+1} = \text{NOR}(\neg a, \neg b, \neg c)$  on  $w_{m+1}$ . Source memristors on  $w_{m+2}$  are in HRS to disconnect the input voltages.

- **Figure 7.6.** Deselecting a volistor gate in a crossbar array. (a) Traditional approach 145 for deselecting a volistor gate by  $v^+/2$  scheme might disturb the circuit operation. (b) Our approach for deselecting a volistor gate is to use pass transistors and  $v^+$  scheme to ensure the correct operation of the circuit.

- **Figure 7.7.** Example of four sub-crossbar arrays (A, B, C, and D) connected by a 146 column and row of pass transistors.

- **Figure 7.8.** Implementation of volistor AND gate with input resistances stored in 147 a computational array. (a) Realization of  $T_m$ =AND (a, b, c) where inputs are located on row  $w_{m-1}$  (b) Realization of  $T_n$  = AND (a, b, c) where inputs are located on column  $w_{n-1}$ .

- **Figure 7.9.** Volistor COPY Operation. (a) COPY value *a* on  $v_{m-1}$  to memristor  $T_m$  149 on  $v_m$  (b) COPY value *a* on  $w_{n-1}$  to memristor  $T_n$  on  $w_n$ .

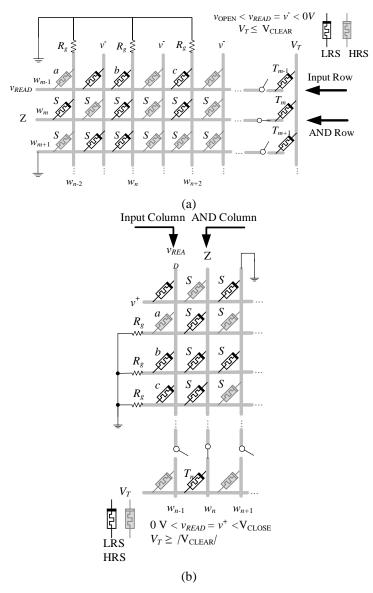

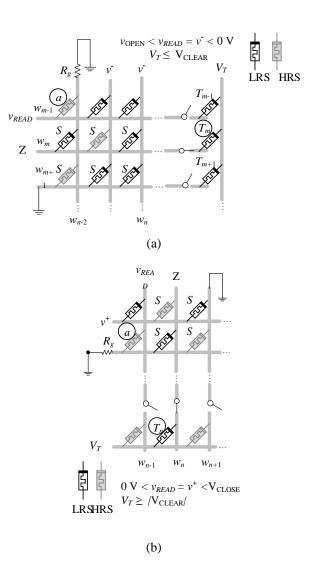

- **Figure 7.10.** Schematic of input-volistor INH gate. Inputs are  $v_a$  and  $r_b$ , and the 150 output is  $(\neg a) b$ , which updates resistance state  $r_b$  of memristor *T*.

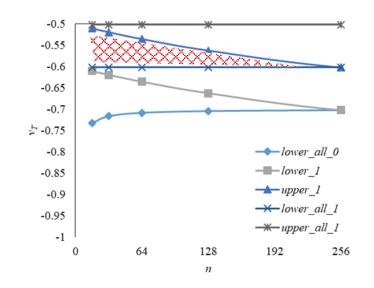

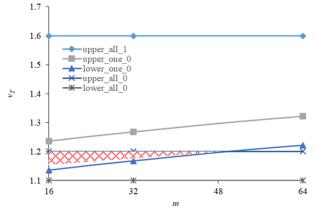

- **Figure 7.11.**  $V_T$ -*n* relations of multiple volistor NOR gates realized in two  $m \times n$  153 crossbar arrays. The shaded area shows the range of  $V_T$  for implementing *i*-input volistor NOR gates where  $i \le n 1$ .

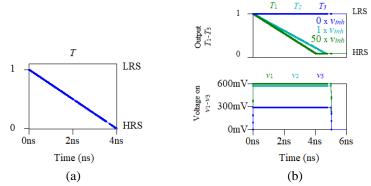

- **Figure 7.12.** (a) State transition delay in LRS memristor connected to  $V_{CLEAR}$ . (b) 154 Simulation results of three 50-input volistor NOR gates executed in a 3×101 crossbar array where  $0 \times v_{inh}$ ,  $1 \times v_{inh}$ , and  $50 \times v_{inh}$  show the number of high inputs applied to each volistor NOR gate. Also,  $v_1$ ,  $v_2$ , and  $v_3$  denote the voltages on horizontal wires  $w_1$ ,  $w_2$  and  $w_3$ of volistor NOR gates. And  $T_1$ ,  $T_2$ , and  $T_3$  are the memristances (resistance states) of target memristors denoting the outputs.

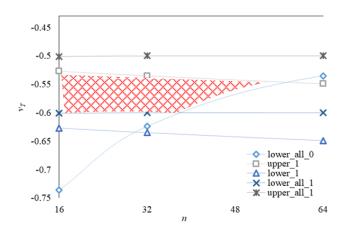

- **Figure 7.13.**  $V_T$ -*n* relations of multiple input-volistor NOR gates realized in two 156  $m \times n$  crossbar arrays. The shaded area shows the range of  $V_T$  for implementing *i*-input-volistor NOR gates where  $i \leq 2n$ -2.

- **Figure 7.14.**  $V_T$ -*m* relations of multiple volistor AND gates realized in two  $m \times n$  157 crossbar arrays. The shaded area shows the range of  $V_T$  for realizing *i*-input volistor AND gates where  $i \leq 2m 1$ .

- Figure 7.15. Schematic of the mPLA for realizing a multi-output POS function. 159

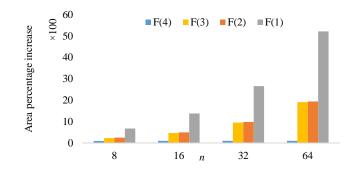

- Figure 7.16. Area estimation of memory array. The graphs show the maximum 164 size of memory arrays in each mPLA circuit.

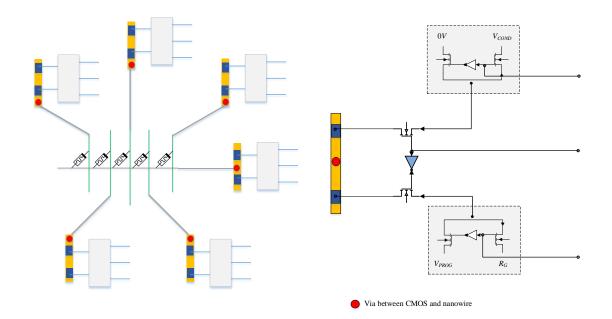

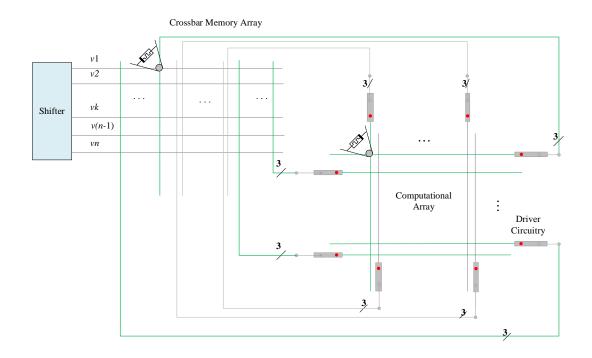

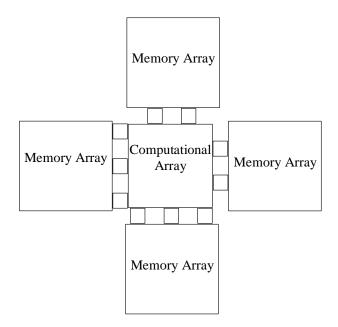

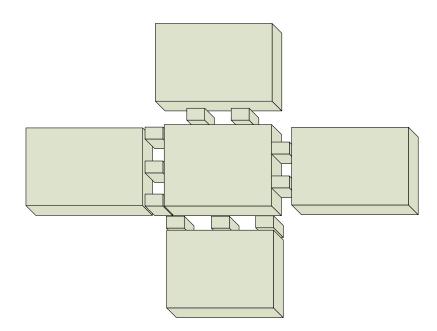

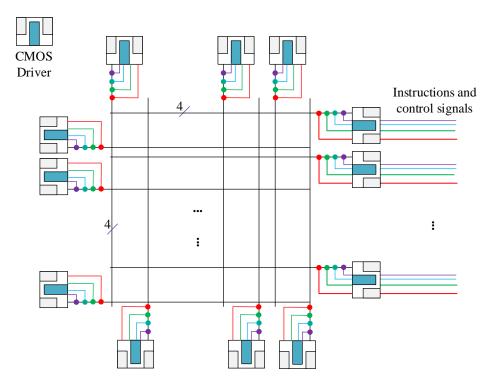

- **Figure 8.1.** Bock diagram of a memristive circuit for logic computations (upper 167 view). Logical operations are implemented in the computational array. The memory arrays store the instructions. Memory arrays and computational array communicate through CMOS drivers shown as small rectangles.

- Figure 8.2. Block diagram of a 3D memristive array (top side view). 168

- **Figure 8.3.** (Left) Schematic of a single CMOS driver in Fig. 8.2. (Right) Driver's 168 circuitry.

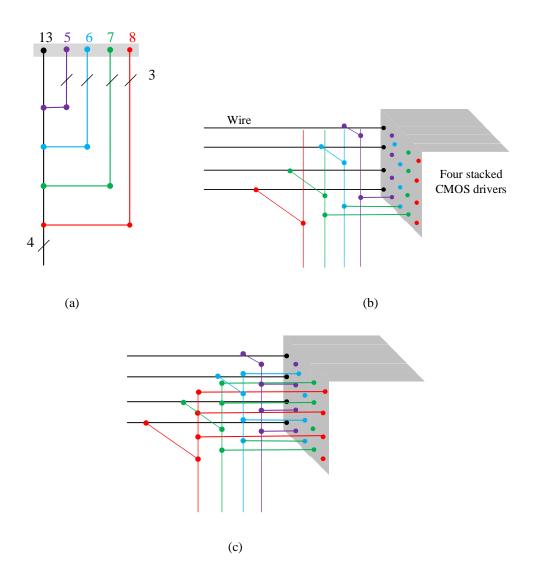

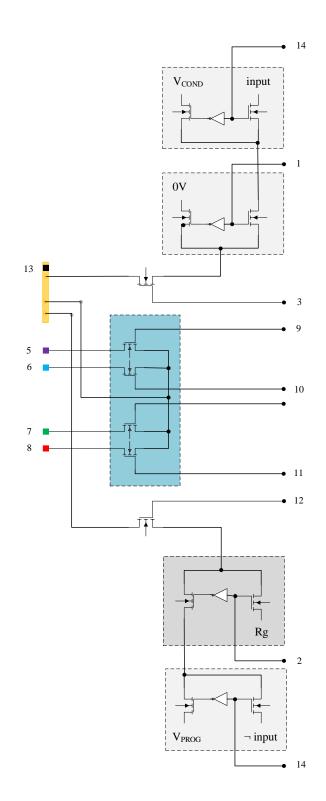

- **Figure 8.4.** Schematic of four stacked computational arrays and their CMOS 169 drivers (bird view). Outputs of the stacked computational arrays are beneath the memory arras. The memory arrays are not shown in this figure.

- **Figure 8.5.** (a) Schematic of driver's interconnections with computational arrays 170 shown in Fig. 8.2 (bird view) (b) Four stacked CMOS drivers (Bird view). (c) Schematic of four stacked CMOS drivers which shows how four wires of four stacked computational arrays communicate through the drivers (side view).

- **Figure 8.6.** CMOS driver for logic computing with hybrid volistor and stateful 171 logic operations.

### List of Abbreviations

| Symbol                                    | Definition                                                                                              |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------|

| ASIC                                      | Application-Specific Integrated Circuit                                                                 |

| 3D Array                                  | 3-Dimenstional crossbar Array                                                                           |

| CMOL                                      | CMOS-Molecular scale device                                                                             |

| ESOP                                      | Exclusive-or-Sum-of-Products                                                                            |

| GND                                       | Ground node                                                                                             |

| LRS                                       | Low resistance state of a memristor                                                                     |

| HRS                                       | High resistance state of a memristor                                                                    |

| Memristor                                 | Memory-resistor                                                                                         |

| POS                                       | Product-of-Sums                                                                                         |

| PPRM                                      | Positive Polarity Reed-Miller                                                                           |

| V <sub>COND</sub> or<br>V <sub>READ</sub> | Applied to source memristors during the READ operation in stateful logic                                |

| V <sub>CLOSE</sub>                        | Positive threshold voltage for programming a memristor to LRS                                           |

| VOPEN                                     | Negative threshold voltage for programming a memristor to HRS                                           |

| VSET                                      | Positive programming voltage for abrupt resistance switching (form HRS to LRS)                          |

| VCLEAR                                    | Negative programming voltage for abrupt resistance switching (form LRS to HRS)                          |

| VPROG                                     | Applied to target memristors while executing stateful gates                                             |

| $V_W$                                     | Voltage on wire W                                                                                       |

| $V_S$                                     | Input voltage applied to a source memristor while executing volistors                                   |

| V <sub>T</sub>                            | Applied to a target memristor while executing volistors                                                 |

| VL                                        | Volistor logic                                                                                          |

| SL                                        | Stateful logic                                                                                          |

| P <sub>S0</sub>                           | Average power consumption in a source memristor connected to logic<br>'0' (in VL) or set to HRS (in SL) |

| $P_{SI}$                                  | Average power consumption in a source memristor connected to logic<br>'1' (in VL) or set to LRS (in SL) |

| $P_S$                                     | Average power consumption in a source memristors during SL or VL                                        |

| $P_T$                                     | Average power consumption in a target memristor                                                         |

| $R_G$                                     | Load resistor                                                                                           |

| $P_{RG}$                                  | Average power consumption in load resistor R <sub>G</sub>                                               |

| $P_{S0}^{WL}$                             | $P_{S0}$ (average power consumption in source memristors set to '0') during VL                          |

| $P_{S1}^{WL}$                             | P <sub>S1</sub> (average power consumption in source memristors set to '1') during VL                   |

| $P_S^{WL}$                                | Ps (average power consumption in source memristors) during VL                                           |

| $P_{S0}^{SL}$                             | P <sub>s0</sub> (average power consumption in source memristors in HRS) during SL                       |

| $P_{S1}^{SL}$ | P <sub>S1</sub> (average power consumption in source memristors in LRS) during |

|---------------|--------------------------------------------------------------------------------|

|               | SL                                                                             |

| $P_S^{SL}$    | P <sub>S</sub> (average power consumption in source memristors) during SL      |

| SOP           | Sum-of-Products                                                                |

| $S_0$         | Number of source memristors in logic '0'                                       |

| $S_1$         | Number of source memristors in logic '1'                                       |

| TANT          | Three-level AND NOT Network with True inputs                                   |

| $T_d$         | Switching delay in a memristor                                                 |

| Volistor      | Voltage-resistor                                                               |

| Ζ             | High impedance                                                                 |

Chapter 1

#### Background

#### **1.1 INTRODUCTION**

The exponential advances in microelectronics over the past five decades are unlikely to continue for the next decade due to physical limitations. The density of transistors in each square centimeter has already exceeded 100 Million. The heat dissipation and memory access delay are the main problems in these ultra-dense microcomputers. The computing research community have been challenged to find variables other than charge or voltage, devices, and architectures that enable the integration to go far beyond the limits of conventional microelectronics technology [1]. In 2008, researchers in Hewlett Packard Labs [2] connected the theory of memristor [3] to the thin film devices (TiO<sub>2</sub>). Memristors and memristive devices [4] are two terminal nanoscale devices whose characteristics are explained by the relation between magnetic-flux ( $\varphi$ ) and charge (q). Memristors and memristive devices are non-volatile devices that can be used for *in-memory computing*. Therefore, memristors can perform advanced computing paradigms of combining calculation and memory units. Unlike traditional computing paradigms, which separate calculation from memory, in new computing paradigms there is no problem of memory access delay and power crisis as one that exists in digital integrated circuits. However, using this new paradigm of logic computation requires executing long sequences of logic operations, which in turn increases the power consumption and complicates the control of the circuit. In this dissertation, this problem is addressed. Multiple solutions are proposed to decrease the number of in-memory logical operations. The proposed techniques also

decrease the power dissipation when compared to other memristive in-memory computing approaches.

In addition to digital computing, memristors enable analog computing, e.g., in neuromorphic applications. However, this dissertation only focuses on digital memristive computing, i.e., memristors are used as binary switches with memory ability.

In this chapter, the theory of memristors, the practical memristors, models and applications of memristors are briefly described. The goals of this research are also defined.

**1.2 MEMRISTOR: THE MISSING CIRCUIT ELEMENT**

The circuit elements *R*, *C*, *L*, and *M* can be functions of *v*, *i*, *q*, and  $\varphi$  in their defining equations. For example, a charge-controlled memristor is defined as a single-valued function *M*(*q*)[2]. In 1971, Leon Chua reasoned that there should be another fundamental

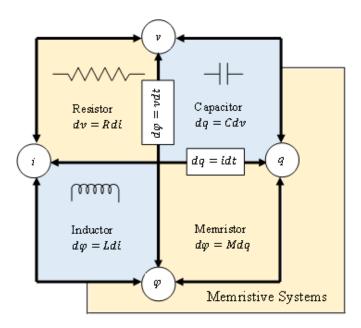

Fig. 1.1. Four fundamental passive circuit elements [Redrawn from 2].

passive circuit element in addition to the resistor, capacitor, and inductor. He called this new element "memristor", short for memory-resistor [3]. His reasoning was based on symmetry arguments where he noted that the number of equations connecting pairs of circuit variables (electrical current *i*, voltage *v*, charge *q*, and magnetic-flux  $\varphi$ ) are six. Two equations (out of six) are dq = i and  $d\varphi = v$  (Faraday's law of induction). Other (four) equations connect pairs of circuit variables via circuit elements. However, before Chua's invention, there were only three known circuit element *R*, *L*, and *C*. Chua reasoned the existence of another circuit element (memristor), which links flux and charge as  $d\varphi = Mdq$ where *M* is the memristance of memristor (Fig. 1.1). Note that *M* is a function of charge, yielding a nonlinear element. If *M* were a constant, it would be identical to *R*. The basic definition of a current-controlled memristor is shown in (1.1) and (1.2) where *w* is the state variable, which is the charge, and *R* is a state-dependent resistance.

$$v = R(w)i \tag{1.1}$$

$$\frac{dw}{dt} = i \tag{1.2}$$

The memristor concept was generalized in 1976 by Chua and Kang to include a much broader class of non-linear dynamic systems called memristive system [4]. A memristive device is a two-terminal passive device whose resistance is a function of state variable wand the voltage v (or current i) and not on the charge or the flux, directly. The currentcontrolled time-invariant memristive devices are described by (1.3) and (1.4).

$$v = R(w, i)i \tag{1.3}$$

$$\frac{dw}{dt} = f(w, i) \tag{1.4}$$

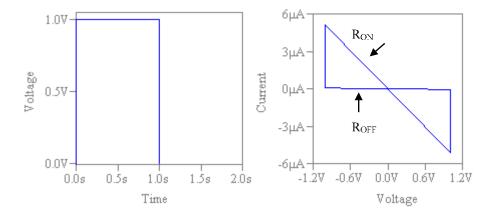

Note that Equation (1.4) is a general case of (1.2) where f(w, i) = i. The *i*-v characteristic of a memristor or a memristive device looks like a pinched hysteresis loop (bow tie) crossing the origin. Fig. 1.2 shows the hysteresis behavior of a memristor for a rectangular pulse input.

#### **1.3 THE MISSING MEMRISTOR IS FOUND**

After three decades of Chua's invention, in 2008, HP (Hewlett Packard) researchers demonstrated a simple analytical example of a memristor. In this example, the memristor's resistance (also called memristance) arises under external voltage bias where solid-state electronic and ionic transport are coupled. This model is known as linear ion drift model.

#### 1.3.1 Linear ion drift model

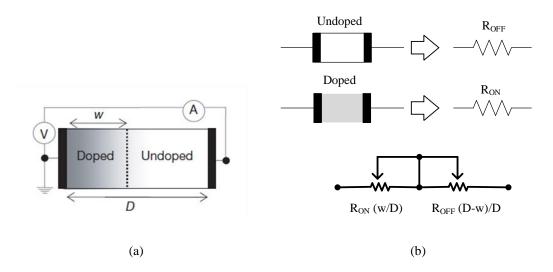

The HP example of memristor is shown in Fig. 1.3a. The device consists of a thin semiconductor film of thickness D sandwiched between two metal contacts, particularly Pt-TiO<sub>2</sub>-Pt. The semiconductor has two regions: one with high concentration of dopants (i.e., oxygen vacancies of TiO<sub>2</sub>, denoted TiO<sub>2-x</sub>) and another with zero dopant (which is

Fig. 1.2. *i-v* characteristic of the memristor for a rectangular pulse input. (Left) Input voltage applied across the memristor. (Right) hysteresis behavior of the memristor.

only oxide region TiO<sub>2</sub>). An external voltage bias across the device can drift the chargeddopants yielding a variable resistance. In other words, the device is analogous to two variable resistors connected in series as shown in Fig. 1.3b where w(t) represents the state variable and  $0 \le w(t) \le D$ . The resistance is  $R_{ON}$  when w(t) = D, and the resistance is  $R_{OFF}$ when w(t) = 0. Equation (1.5) and (1.6) explain the HP model of memristor where  $\mu_V$  is the average ion (vacancies) mobility. Note that Equation (1.5) and (1.6) are derived for the simplest cases of ohmic electronic conduction and linear ion drift in a uniform field with average ion mobility  $\mu_V$ .

$$v(t) = \left(R_{ON}\frac{w(t)}{D} + R_{OFF}\left(1 - \frac{w(t)}{D}\right)\right)i(t)$$

(1.5)

$$\frac{dw}{dt} = \mu_V \frac{R_{ON}}{D} i(t) \tag{1.6}$$

To keep w(t) within the interval [0, D], it is required to multiply  $\frac{dw}{dt}$  by window function as used in [5-7].

Fig. 1.3. (a) Structure of the HP example of memristor. (b) Circuit equivalent. [Redrawn from 2]

#### 1.3.2 Non-linear ion drift model

Although the linear ion drift model shows the basic device behaviors, there is a significant mismatch between the *i*-*v* characteristics of this model and that shown in experiments [8-9]. The linear ion drift model does not represent the non-linear dependence between  $\frac{dw}{dt}$  and i(t). A number of non-linear ion drift models, which is desired for logic computations, have been proposed. Three examples of non-linear ion drift models are discussed below.

#### 1) Lehtonen et al. model

Lehtonen *et al.* [10-11] proposed a model based on experimental results shown in [8] where the i-v relation is explained by (1.7).

$$i(t) = w(t)^{n}\beta \sinh(\alpha v(t)) + \chi[\exp(\gamma v(t) - 1]$$

(1.7)

The  $\alpha$ ,  $\beta$ , and  $\gamma$  are experimental fitting parameters, and n determines the influence of w(t) on i(t). The state variable, w, is normalized within interval [0, 1]. When the device is in the on-state ( $w \approx 1$ ),  $i(t) \approx w(t)^n \beta \sinh(\alpha v(t))$ . When the device is in the off-state ( $w \approx 0$ ),  $i(t) \approx \chi [\exp(\gamma v(t) - 1]$ . The model assumes: 1) asymmetric switching behavior, and 2) the non-linear dependence between  $\frac{dw}{dt}$  and v(t) as explained by (1.8) where a is a constant, m is an odd constant, and f(w) is a windows function.

$$\frac{dw}{dt} = a.f(w).v(t)^m \tag{1.8}$$

#### 2) Simmons tunnel barrier model

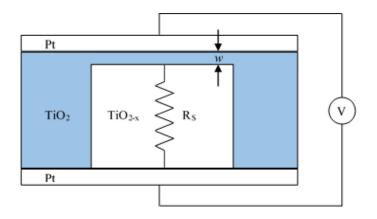

Pickett *at el.* [12] showed a mathematic definition of non-linear memristive devices, known as Simmons tunnel barrier model. This model was derived from experimental results of dynamic testing protocols applied to Pt-TiO<sub>2</sub>-Pt devices. The model shows that the energy required to switch a metal-oxide-metal device decreases exponentially with increasing current through the device. Fig. 1.4 shows the scheme of memristive device used to derive the tunnel barrier model. The Simmons tunnel barrier width [13] (which is the width of the undoped oxide region) represents the state variable *w*, and  $R_S$  represents the electroformed channel resistor of a few hundred ohms resistance. In this model, the velocity of the oxygen vacancy drift (dw/dt) is explained by (1.9) where  $f_{off}$ ,  $f_{on}$ ,  $i_{off}$ ,  $i_{on}$ ,  $a_{off}$ ,  $a_{on}$ , *b*, and  $w_c$  are fitting parameters. Parameters  $f_{off}$  and  $f_{on}$  influence the magnitude of dw/dtwhere  $f_{on}$  is an order of magnitude larger than  $f_{off}$ . Parameters  $i_{off}$  and  $i_{on}$  are effectively limiting the threshold currents. When  $i < i_{off}$  or  $i < i_{on}$ , dw/dt is negligible. Parameters  $a_{off}$ and  $a_{on}$  set upper and lower bounds for *w* and the model does not require a window function.

$$\frac{dw}{dt} = f_{off} \sinh\left(\frac{i}{i_{off}}\right) \exp\left[-\exp\left(\frac{w-a_{off}}{w_c} - \frac{|i|}{b}\right) - \frac{w}{w_c}\right] \quad (off\text{-switch}) \quad i > 0$$

$$\frac{dw}{dt} = f_{on} \sinh\left(\frac{i}{i_{on}}\right) \exp\left[-\exp\left(-\frac{w-a_{on}}{w_c} - \frac{|i|}{b}\right) - \frac{w}{w_c}\right] \quad (on\text{-switch}) \quad i < 0 \tag{1.9}$$

The experimental results show the on and off switching behaviors are asymmetric, i.e., the on-switching is significantly faster than the off-switching. In addition, the switching energy decreases exponentially with the current through the device.

Fig. 1.4. The schematic of memristive device realized using tunnel barrier where *w* and *Rs* represent the state variable and the electroformed channel resistor, respectively [Redrawn from 12].

#### 3) TEAM mod

TEAM [14], short for ThrEshold Adaptive Memristive Model, assumes no change in state variable w when the current is between the thresholds,  $i_{on} < i < i_{off}$ . In addition, a polynomial dependence rather than exponential dependence is assumed. In this model memristors have adaptive nonlinearity and threshold currents. Therefore, Equation (1.9) is rewritten as shown in (1.10) where  $k_{off}$  and  $k_{on}$  are fitting parameters,  $a_{off}$  and  $a_{on}$  are adaptive nonlinear parameters,  $i_{off}$  and  $i_{on}$  are threshold currents, and w is the state variable, which represents the effective electric tunnel width. Note that  $k_{off}$  is a positive constant while  $k_{on}$  is a negative constant. The state variable w is within the interval  $[w_{on}, w_{off}]$ .

$$\frac{dw(t)}{dt} = \begin{cases} k_{off} \left(\frac{i(t)}{i_{off}} - 1\right)^{a_{off}} \exp\left[-\exp\left(\frac{w - a_{off}}{w_c}\right)\right], & 0 < i_{off} < i \\ 0, & i_{on} < i < i_{off} \\ k_{on} \left(\frac{i(t)}{i_{on}} - 1\right)^{a_{on}} \exp\left[-\exp\left(-\frac{w - a_{on}}{w_c}\right)\right], & i < i_{on} < 0 \end{cases}$$

(1.10)

#### **1.4 APPLICATIONS**

The primary use of memristors is for memory application where memristors are considered as emerging non-volatile technologies. The characteristics of memristors such as their small size, non-volatility (memristors remember their resistances when powered off), high endurance (the number of write cycles exceed 10<sup>9</sup> and it can reach up to 10<sup>15</sup> while the device remains reliable), low switching delay (sub-nanosecond-few tens of nanoseconds), low switching energy (0.1-1pJ), as well as being passive devices make them ideal candidates for memory use. The generic structure for memristive memory is a crossbar array [15]. The crossbar arrays can be stacked creating a three-dimensional memory architecture [16-17]. In addition to memory use of memristors, there are many proposals to use the memristors for computations [18-30], neuromorphic circuits and machine learning applications [31-34].

Memristors may have different roles during logic computation. For example, memristors can serve only as logic gates [22], [24], [27]. In this approach, logic values are voltage signals. In another approach, memristors serve only as configurable switches in FPGA-like circuits to realize routing networks [35-36]. Similar to the previous approach, here, the logic values are voltage signals, as well. Memristors can also be used to perform stateful logic. In this approach, memristors simultaneously serve as gates and latches [18-20], [23], [25], [28]. Computations based on stateful logic are usually performed in crossbar memory arrays. This unconventional approach to logic computations is performed in non von-Neumann computer architectures.

#### **1.5 RESEARCH GOALS AND METHODES**

In this dissertation, the capabilities and limitations of logic computations based on memristors are studied. Multiple approaches are proposed to decrease the computational delays in non von-Neumann computer architectures. For example, a small hybrid CMOSmemristive circuits is designed for fast implementation of generalized exclusive OR-Sumof-Products functions. The complexity of memristive circuits performing in-memory computations is also studied. A general circuit architecture is proposed. The proposed circuit architecture simplifies the datapath and reduces the size and computational delay. In addition, a novel 3-dimentioal circuit architecture for in-memory computing is proposed.

#### **1.6 RESEARCH STRUCTURE**

This dissertation is organized as follows. Chapter 1 is a review of memristor theory, practical memristors, memristor models, applications, and the contributions in this dissertation. Chapter 2 reviews multiple design choices for logic computations based on memristors. In addition, the generic circuit structures for logic computations with memristors and their capabilities and potential problems are explained. Chapter 3 describes volistors (voltage-resistor logic gates), i.e., new logic gates based on rectifying memristors. Chapter 4 describes programmable diode logic gates, i.e., new logic gates based on rectifying memristors. Chapter 5 shows a generic CMOS-memristive circuit structure for in-memory computing called mPLD-XOR, i.e., memristive Programmable Logic Device connected to XOR circuits. Multiple implementation examples using mPLD-XOR are explained. Chapter 6 shows implementation example of multi-input XOR logic function using a combination of volistor XNOR gates, programmable diode AND gates, and CMOS