## Short-Term Plasticity: A Neuromorphic Perspective

# PhD thesis submitted for the degree of DOCTOR OF ENGINEERING (Dr.-Ing.)

<sup>by</sup> Harshawardhan Ramachandran

Supervisor: Prof. Dr. Elisabetta Chicca

Reviewers:

Prof. Dr. Martin Paul Nawrot Dr. Chiara Bartolozzi

> Bielefeld University Faculty of Technology Universitätsstr. 25 33615 Bielefeld Germany

> > April, 2018

Harshawardhan Ramachandran: *Short-term plasticity: a neuromorphic perspective*, the design of neuromorphic short-term plasticity circuits and the demonstration of the short-term plasticity in a cricket calling song recognition network using the neuromorphic hardware, © April 2018

supervisor: Prof. Dr. Elisabetta Chicca I declare that this thesis entitled "Short-term plasticity: a neuromorphic perspective" is the outcome of my research at the Bielefeld University. This work contains no material previously published or written by another person nor material which to a substantial extent has been accepted for the award of any other degree or diploma of the university or other institute, except where due acknowledgement has been made in the text.

Bielefeld, April 2018

Harshawardhan Ramachandran, April 12, 2018

#### PUBLICATIONS

- Thomas Rost, Harshawardhan Ramachandran, Martin Paul Nawrot, and Elisabetta Chicca, "A neuromorphic approach to auditory pattern recognition in cricket phonotaxis", in Circuit Theory and Design (ECCTD), 2013 European Conference on, pp. 1-4. IEEE, 2013.

- Harshawardhan Ramachandran, Stefan Weber, Syed Ahmed Aamir, and Elisabetta Chicca, "Neuromorphic circuits for Short-Term Plasticity with recovery control", in 2014 IEEE International Symposium on Circuits and Systems (IS-CAS), pp. 858-861. IEEE, 2014.

- Moritz B. Milde, Olivier J.N. Bertrand, Harshawardhan Ramachandran, Martin Egelhaaf and Elisabetta Chicca, "Spiking elementary motion detector in neuromorphic systems", Neural Computation, submitted.

- Harshawardhan Ramachandran, Martin Paul Nawrot, and Elisabetta Chicca, "Short-term plasticity and adaptation as computational primitives for temporal filtering in small neural circuits", in preparation.

#### ACKNOWLEDGEMENTS

I would like to acknowledge the following people who played special parts in the journey of my PhD.

I would like to thank Dr. Elisabetta Chicca, for providing me an opportunity to work in this project, for guiding me in the right directions during my research and for her valuable advices that shaped my approach to tackle the problems.

I would like to thank Dr. Martin Paul Nawrot, for sharing his valuable knowledge and supporting me with confidence in the areas of my non-expertise.

I would like to thank Dr. Giacomo Indiveri, for providing critic and valuable suggestions to my research.

I would to like to thank Dr. Emre O. Neftci, Dr. Sadique Sheik and Dr. Fabio Stefanini, for helping me to understand the working of the neuromorphic hardware.

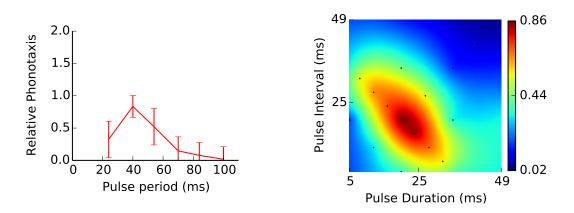

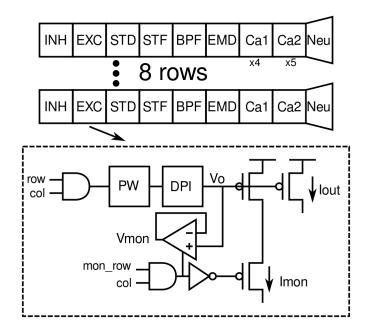

I would to like to thank Dr. Thomas Rost and Dr. Gundula Meckenhäuser, for providing me the simulation and behavior data of cricket phonotaxis.

I would like to thank Dr. K. P. Soman, for inspiring me to do a PhD.

I would like to thank Lauryna Jurkutė, Christian Poth, Dr. Fernando Perez-Peña, and Dr. Stephen Nease, for encouraging me throughout my PhD.

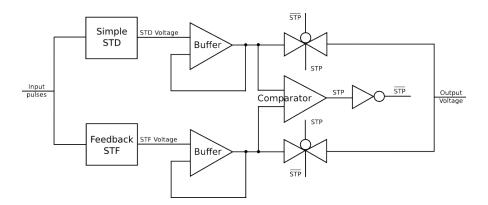

I would like to thank Stefan Weber and Dr. Stephen Nease for the ideas about the design of neuromorphic feed-back Short-Term Plasticity (STP) circuits and STP based band-pass filter circuits.

I would like to thank Uta Scheidt, for collecting data from the fabricated STP circuits.

I would like to thank Lauryna Jurkutė, Tim Walther, Philipp Klein and Dr. Stephen Nease for proof-reading my thesis. I would like to thank Dr. Sebastian Zehe, Frank Lucio Maldonado Huayaney, Neurobiology group and Active Sensing group for their vaulable feedback to prepare for my PhD defense.

I would like to thank Cordula Heidbrede and Daniel Wolf, for helping me in all my requests.

I would like to thank Ineta Jurkutė, Egidiya Jurkienė and Sigitas Jurkus, for giving me a great moral support.

I would like to thank Dr. Qiang Li, Stefan Weber, Ole Richter, Tim Walther, Marius Schirmer and Philipp Klein for guiding me in Germany.

I would like to thank all the nice people of the Welcome Centre, especially Monika Bokermann and Bodo Gülich, for supporting me with their valuable advice in all the times.

I would like to thank all the present and the past members of the Neuromorphic Behaving Systems group, for nice discussions during the breaks.

I would like to thank all the kind-hearted people in mensa, for providing me a good nourishment.

I would like to thank my parents, for motivating me throughout my career.

#### ABSTRACT

Short-Term Plasticity (STP) is the ability of the synapse to modify its strength for a short time. Despite several silicon implementations, STP remains one of the least explored topics in the neuromorphic computing research. One form of STP implementation called Short-Term Depression (STD) is available to use in our mixed-signal subthreshold neuromorphic chip. However, the design lacks an independent control over recovery rate of STD. This limitation prevents the circuit to execute a particular synaptic dynamics, such as a strong depression followed by a fast recovery. Another variant of STP called Short-Term Facilitation (STF) is possible to implement in our neuromorphic chip by operating the synapse circuit available, in a specific regime. This operation prevents the time-constant of the synapse to be tuned independently from that of STF implementation. We designed novel STD and STF circuits to solve these problems. The STP circuits are compact in design, but the responses of one of the STP circuits (STF) reached the steady-state values only for certain input frequencies. Therefore, we designed another set of STP circuits by adding a negative feedback loop to our previous design. All these STP circuits are designed and fabricated in a standard Complementary Metal Oxide Semiconductor (CMOS) 180 nm technology and characterized. Alongside the Very Large Scale Integration (VLSI) design, we also demonstrated the role of the STP in a network to recognize the calling songs of crickets. We chose this network due to its small size and the auditory neurons involved in recognition are electrophysiologically studied in the literature. Although several research groups proposed the connectivity of these neurons, the functional structure of the network remains unclear. Therefore, we modeled a spiking neural network using STF in our neuromorphic hardware based on the neurophysiological evidence. Our network model selects the attractive frequencies comparable to the observations in female crickets and gives an idea about the connectivity scheme. Overall, through this research on Short-Term Plasticity (STP), we contributed to two active research fields: neuromorphic computing and computational neuroscience.

### CONTENTS

| 1 | INT | RODUCTION 2                                            |

|---|-----|--------------------------------------------------------|

|   | 1.1 | Motivation of this study 2                             |

|   | 1.2 | Objectives of this research 3                          |

|   | 1.3 | Main contribution of this work 4                       |

|   | 1.4 | Structure of the thesis 4                              |

| 2 | SHO | ORT-TERM SYNAPTIC PLASTICITY 6                         |

|   | 2.1 | Introduction 6                                         |

|   | 2.2 | Models of Short-Term Plasticity 7                      |

|   | 2.3 | Computational role of STP 10                           |

|   |     | 2.3.1 Temporal filtering 10                            |

|   |     | 2.3.2 Burst detection 12                               |

|   |     | 2.3.3 Gain control 13                                  |

|   |     | 2.3.4 Direction selectivity 15                         |

|   |     | 2.3.5 Encoding sound intensity 17                      |

|   | 2.4 | Conclusion 19                                          |

| 3 | SUB | -THRESHOLD NEUROMORPHIC HARDWARE 20                    |

|   | 3.1 | Introduction 20                                        |

|   | 3.2 | MOSFET 23                                              |

|   | 3.3 | Sub-threshold characteristics of a transistor 25       |

|   |     | 3.3.1 Sub-threshold ohmic operation 28                 |

|   |     | 3.3.2 Sub-threshold saturation operation 30            |

|   | 3.4 | Basic building blocks of analog VLSI circuits 31       |

|   |     | 3.4.1 Diode-connected transistor 31                    |

|   |     | 3.4.2 Current mirror 32                                |

|   |     | 3.4.3 Source follower 33                               |

|   |     | 3.4.4 Differential pair 34                             |

|   | 3.5 | Silicon synapse 35                                     |

|   | 3.6 | Silicon neuron 41                                      |

|   | 3.7 | Neuron array 45                                        |

|   | 3.8 | Neuromorphic architecture 48                           |

|   | 3.9 | Conclusion 52                                          |

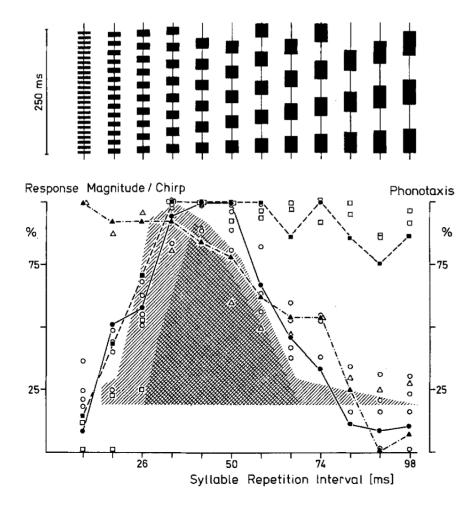

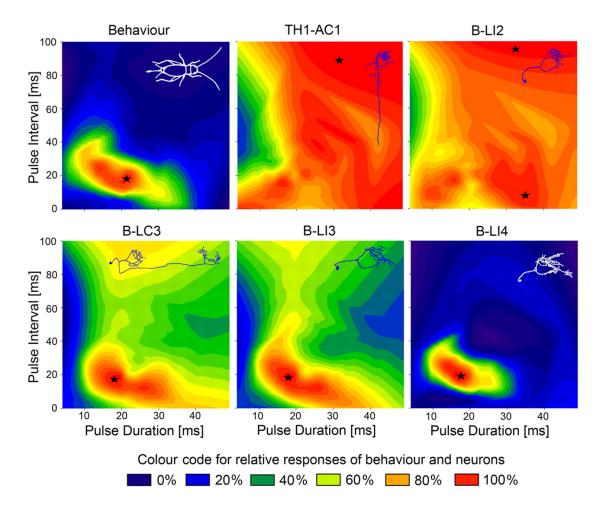

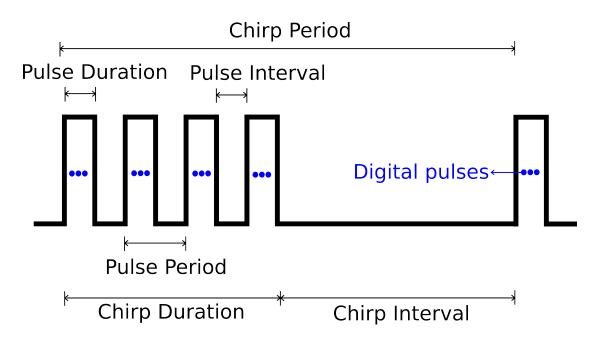

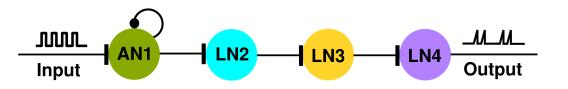

| 4 | NEU | UROMORPHIC DESIGN OF SHORT-TERM PLASTICITY CIRCUITS 54 |

Introduction 4.1 54 Analog sub-threshold neuromorphic STD circuits 4.2 57 STP circuits with recovery control 64 4.3 STD circuit 4.3.1 64 STF circuit 68 4.3.2 STP circuits with feedback recovery control 72 4.4 STF circuit 4.4.1 72 4.4.2 STD circuit 76 Simulations of STP circuits 78 4.5Fabrication and testing of STP circuits 4.6 80 Conclusion 88 4.7 NEUROMORPHIC MODEL FOR CRICKET CALLING SONG RECOGNITION 5 NETWORK 90 Introduction 5.1 90 Neurobiology of cricket phonotaxis 5.2 91 Experimental methods 5.3 97 Stimulus 5.3.1 97 Network model 5.3.2 99 Computational primitives 5.3.3 103 Results 109 5.4 5.4.1 Behavioral data of cricket phonotaxis 123 Discussion 125 5.5Conclusion 5.6 126 6 CONCLUSION 128 Advantages of neuromorphic approach 6.1 129 Future works 6.2 130 Outlook of neuromorphic engineering research 6.3 131 APPENDIX 134 7 Fabricated cricket calling song recognition network 7.1 134 STP based band-pass filter 7.2138

7.3 Supplementary material 142

#### ACRONYMS

- **VLSI** Very Large Scale Integration

- DPI Differential-Pair Integrator

- IF Integrate-and-Fire

- AER Address Event Representation

- PCB Printed Circuit Board

- AMS Austria Micro Systems

- CMOS Complementary Metal Oxide Semiconductor

- IF2DWTA Integrate-and-Fire 2-Dimensional Winner-Take-All

- IFSLWTA Integrate-and-Fire Soft-Learning Winner-Take-All

- BJT Bipolar Junction Transistor

- FET Field Effect Transistor

- JFET Junction gate Field Effect Transistor

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- FPGA Field-Programmable Gate Array

- CMI Current-Mirror Integrator

- **OTA** Operational Transconductance Amplifier

- DVS Dynamic Vision Sensor

- **EPSP** Excitatory Post-Synaptic Potential

- **IPSP** Inhibitory Post-Synaptic Potential

- EPSC Excitatory Post-Synaptic Current

- **IPSC** Inhibitory Post-Synaptic Current

- SFA Spike Frequency Adaptation

- **STP** Short-Term Plasticity

- **STD** Short-Term Depression

- STF Short-Term Facilitation

- **STSP** Short-Term Synaptic Potentiation

- PTP Post-Tetanic Potentiation

- **PPF** Paired-Pulse Facilitation

- LTD Long-Term Depression

- LTP Long-Term Potentiation

- **STDP** Spike-Timing Dependent Plasticity

- NMDA N-methyl-D-aspartate

- LIF Leaky Integrate-and-Fire

- AN1 Ascending Neuron 1

- AN2 Ascending Neuron 2

- LN1 Local Neuron 1

- LN2 Local Neuron 2

- LN3 Local Neuron 3

- LN4 Local Neuron 4

- **BN** Brain Neuron

- BNC Central Brain Neuron

- BNC1 Central Brain Neurons 1

- BNC<sub>2</sub> Central Brain Neurons 2

- PD Pulse Duration

- PI Pulse Interval

- PP Pulse Period

- **CD** Chirp Duration

- CI Chirp Interval

- CP Chirp Period

- **ISI** Inter-Spike interval

- **SD** Standard Deviation

- PIR Post-Inhibitory Rebound

- **EMD** Elementary Motion Detection

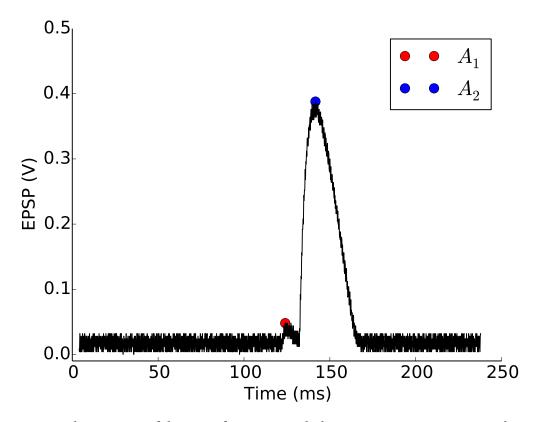

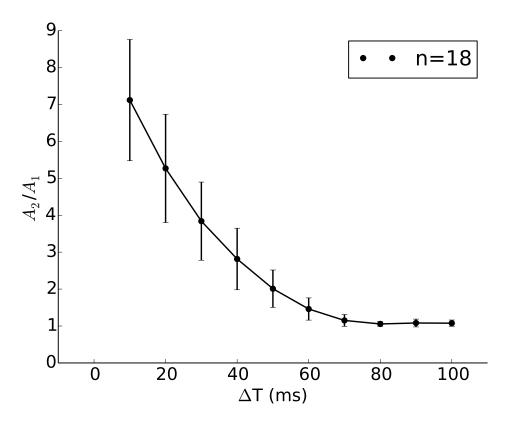

- **PPR** Paired Pulse Ratio

#### INTRODUCTION

#### 1.1 MOTIVATION OF THIS STUDY

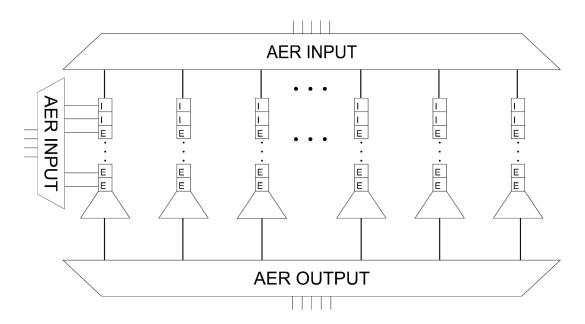

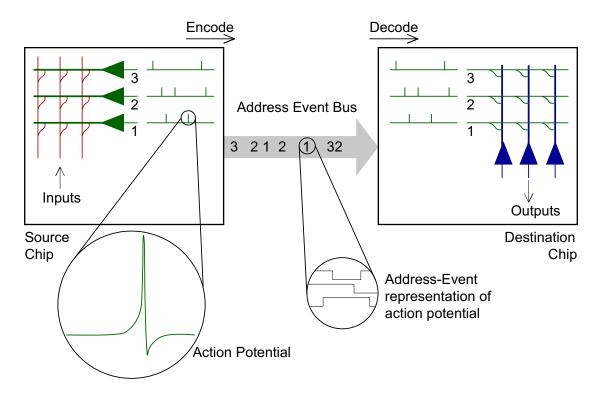

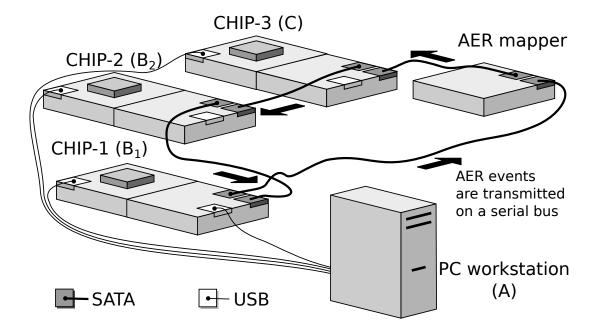

Deep neural networks, the state-of-art in artificial intelligence have been proven to show high accuracy in solving classification problems. However, the number of computational resources utilized by these deep networks are significantly high. Recently, the bio-derived class of neural networks called spiking neural networks are gaining a lot of attention from the computing research community due to its energy efficiency trait. The main ingredient of spiking neural networks are spikes, whose sparse nature minimizes the computational power required to process them. Time is inherently represented in spiking networks, meaning that no additional resource is needed to compute the time. This aspect paved the way for the development of an energy-efficient spikecommunication protocol called the Address Event Representation (AER), in which the neurons communicate to each other concerning 'spike-times' and 'neuron-addresses'. The spiking networks can efficiently model the time-varying dynamics of the bioinspired systems. In recent years, more and more dedicated hardware for running spiking neural networks are being developed. This class of dedicated hardware is called the neuromorphic hardware, and their design/architecture are optimized to implement spike-based algorithms. In this research, we model one such spiking network that recognizes the artificial calling songs of crickets, in the neuromorphic hardware.

We aim to model a system in the hardware that genuinely implements the biophysical models in silicon. Several kinds of neuromorphic hardware exist. Amongst all, the mixed-signal sub-threshold neuromorphic hardware adequately captures the dynamics of the bio-inspired neuron models and operates in biologically realistic timeconstants. The hardware runs asynchronously and executes the computation in entirely parallel fashion. This system uses low-power and can be integrated with eventbased sensors to be used in real-time closed-loop robotic applications. This type of neuromorphic hardware can also be used to explore the properties of computational neuroscience models. Therefore, the mixed-signal sub-threshold neuromorphic hardware is the best suitable choice to implement our network of auditory pattern recognition in crickets. The neuromorphic chips are designed to be served as general purpose hardware to emulate the spiking neuron models. However, the silicon models are unchangeable after fabrication. Therefore, the designed system must implement the necessary aspects of the neuron models as much as possible. It is feasible to capture the fine details of the biophysical models by modeling a small-scale system. Therefore, the small-scale design minimizes the risk involved to miss out any aspect in a large-scale system design. It is also important to mention here that the fabrication costs are high to design a custom chip. The chip design has to be updated accordingly because bio-physical models are regularly improving. In this case, small-scale systems are ideal to be designed in dedicated hardware concerning design costs and the chip can be redesigned faster compared to the large-scale hardware. The small-scale system also serves as a prototype for the large-scale design. Considering the advantages mentioned above, we model a small-scale system inspired by the auditory system of crickets in this research.

#### 1.2 OBJECTIVES OF THIS RESEARCH

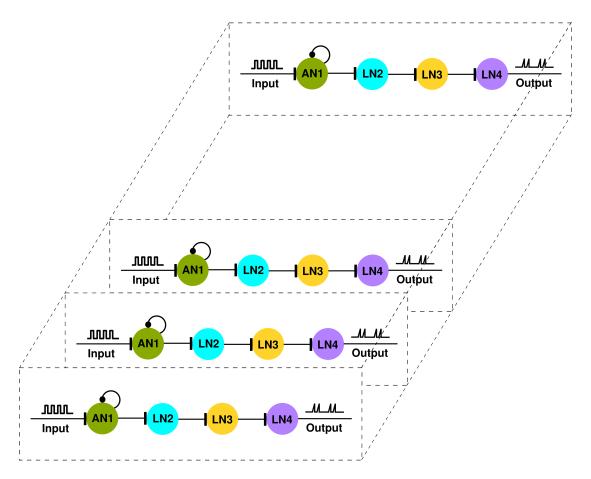

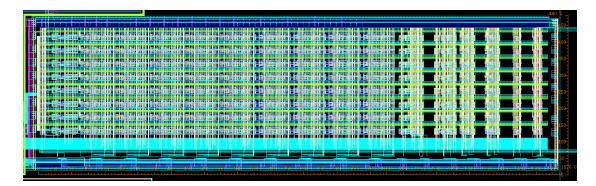

We aim to understand insects with neural structures that are several orders of magnitude smaller than the mammalian brain yet display a variety of complex behavior. For example, crickets are exciting for neuroscientists due to their acoustic-oriented behavior. Male crickets produce calling songs, and female crickets respond to these calling songs by approaching the males. This phenomenon is called a cricket phonotaxis. The studies on phonotaxis suggest that females are attracted to certain types of male calling songs with specific temporal features. The electrophysiological recordings of the auditory neurons of a cricket brain validate this proof of principle. However, the underlying neural network responsible for the recognition of the calling songs is not evident in the literature. Understanding these small systems can give an insight into the computations occurring in tiny brains. An elementary network of cricket phonotaxis is modeled in [96] based on the neurophysiological evidence. This network model laid the foundation for this research. The model consists of four neurons with Short-Term Plasticity (STP) synapses in between. STP is one of the short and quick learning mechanisms of the synapses of the brain which is used in speech recognition, motor control, etc. Considering the small size, we implemented this network in the existing mixed-signal sub-threshold neuromorphic hardware designed by Prof. E. Chicca and Prof. G. Indiveri, at the Institute of Neuroinformatics, University of Zürich and ETH Zürich. Neuromorphic systems aim at emulating the biophysical mechanisms of the neural elements in the silicon substrate. Calling song recognition network of crickets is compact to study through the neuromorphic chips. During the implementation, we discovered that we cannot implement specific temporal dynamics of STP with the cir-

#### INTRODUCTION

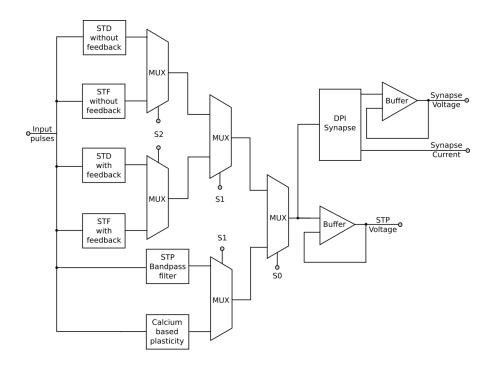

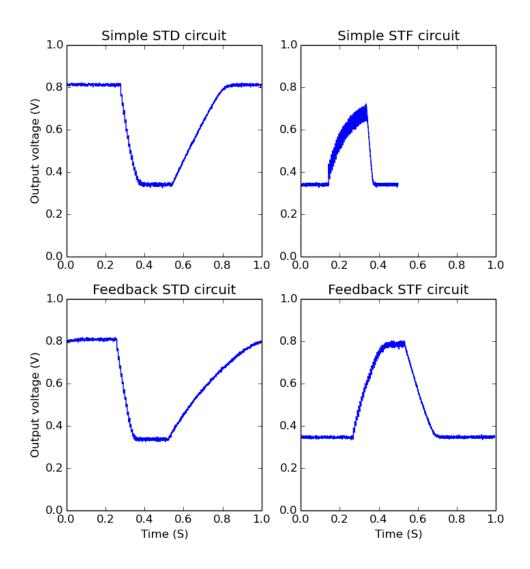

cuit present in the neuromorphic chip. Therefore we designed a series of STP circuits to perform particular computations of the STP such as the detection of bursts of spikes. To summarise, we redesign the STP circuit that can be tuned to emulate specific temporal dynamics to detect bursts. We also demonstrate the STP by modeling the calling song recognition network of crickets in the neuromorphic hardware.

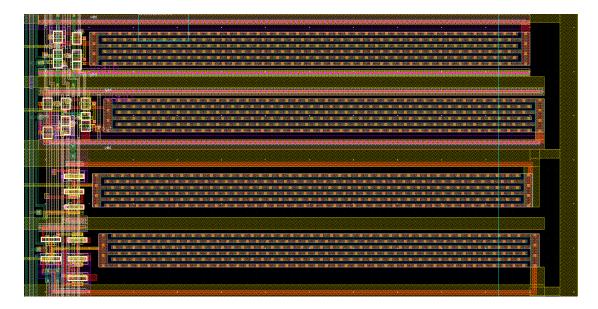

#### 1.3 MAIN CONTRIBUTION OF THIS WORK

With this interdisciplinary research, we aimed to contribute to both the computational neuroscience and the neuromorphic engineering. We designed and fabricated four neuromorphic STP circuits that are capable of detecting bursts of spikes. The proposed STP circuits can be integrated with the existing mixed-signal subthreshold neuromorphic system. Due to its compact design, the STP blocks can be used in large synaptic arrays. A novel calling song recognition network of crickets is modeled using STP. The model selectively chooses the attractive stimuli comparable to the neurophysiological evidence. It also suggests the connection scheme of auditory neurons in cricket brain. This model can be exported to perform acoustic-based tasks in neuro-robots.

#### 1.4 STRUCTURE OF THE THESIS

The structure of this thesis is defined as follows:

Chapter 1 gives the general introduction which includes the motivation, aims, and the contribution of this research.

Chapter 2 is a literature review on short-term plasticity from the computational neuroscience perspective. The biophysical mechanisms of the STP and the commonly used STP models along with examples of the computational roles of the STP in neural circuits are discussed.

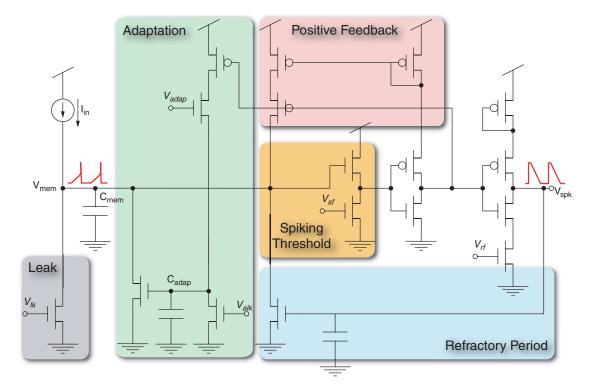

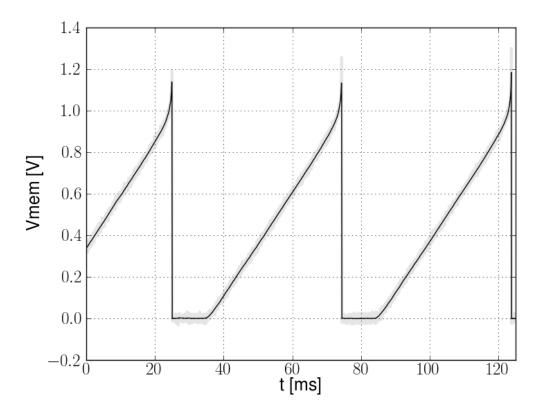

Chapter 3 provides an overview of neuromorphic hardware circuits used in this research. A wide variety of topics, ranging from the basic operations of transistors to the complex neuromorphic synapse and neuron circuits are reviewed, and different types of neuromorphic hardware, in particular, the hardware used for this research are covered.

Chapter 4 is dedicated to the neuromorphic circuits of the STP. The existing STP circuits are examined, and the novel STP circuits are proposed. The design of these STP circuits

are explained, and their operations are analyzed using simulations and hardware implementations.

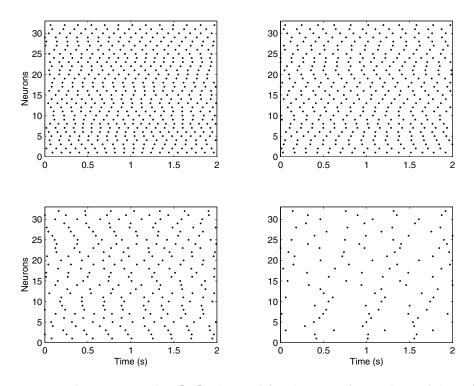

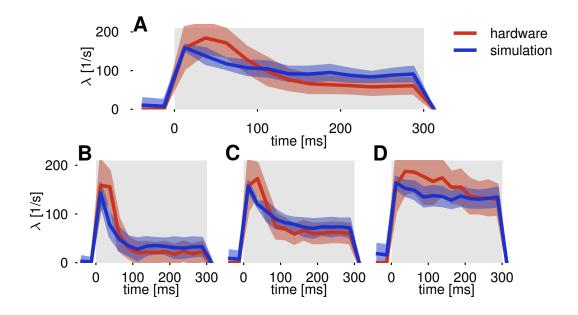

Chapter 5 demonstrates the STP in a calling song recognition network of crickets. The network is modeled using the neuromorphic hardware, and the responses of the individual neurons are tuned based on the neurophysiological evidence. The network responses are presented along with the deviations resulting from device mismatch effects, across a group of same networks.

Chapter 6 is the conclusion of this research. Future directions of this study and outlook of the neuromorphic engineering are discussed.

#### SHORT-TERM SYNAPTIC PLASTICITY

#### 2.1 INTRODUCTION

Plasticity in synapses postulates learning in biology. Synaptic plasticity helps to remember the history of activity between the neurons. Neural systems of animals in various developmental stages exhibit different forms of synaptic plasticity. For example, the calyx of Held synapse, located in the mammalian auditory brainstem shows a rapid type of synaptic learning mechanism called Short-Term Plasticity (STP). STP is a type of synaptic plasticity that lasts for a short period ranging from milliseconds to seconds and even minutes. STP relies only on the pre-synaptic activity that modifies the release of the neurotransmitters from the synaptic bouton. Structural changes of the synapse are instead involved in long-term plasticity. Pre- and post-synaptic activities influence long-term plasticity, which supports the formation of lifelong memory [13] as well as working memory [77]. In vivo [110] and in vitro [3] stimulations suggest long-term modifications of synaptic strength lasting for hours or longer. Both shortand long-term plasticities affect the strength of the synapse in two distinct ways: potentiation (or facilitation) strengthens the synapse, depression weakens the synapse. STP is the key element of this research. We built circuits that emulate the temporal dynamics of the STP (in chapter 4). We also demonstrated the STP in a small neural network, which recognizes the calling songs of crickets (in chapter 5). In this chapter, we discuss the two types of STP, its computational properties and the theoretical models of STP. We aim to provide an understanding of the STP, from the perspective of a neuroscientist.

One form of STP called the Short-Term Facilitation (STF) is an enhancement of synaptic efficacy for a short period in the order of tens to hundreds of milliseconds. STF has been reported in neuro-muscular junctions [6], hippo-campus [94], synapses between pyramidal cells, and bi-tufted inter-neurons [95]. Facilitation occurs due to the additive influx of calcium ions following the pre-synaptic spikes, thereby increasing the probability of release of neurotransmitters into the synapse cleft. Many types of synaptic enhancement exist, and they occur on several short timescales. For instance, a type of facilitation called augmentation increases the synaptic strength for a few seconds. Others include Post-Tetanic Potentiation (PTP) that strengthens the synapse for several seconds to minutes and Short-Term Synaptic Potentiation (STSP) that enhances the synapse for several minutes. According to [93], it is often unclear to distinguish augmentation from the PTP.

Another form of STP called the Short-Term Depression (STD) exists in the synapses between the pyramidal cells and the multi-polar inter-neurons [95], synapses in layer 2/3 of rat primary visual cortex [108], and neuro-muscular junctions [18]. STD is the short-time reduction in strength of a synapse due to the depletion of neurotransmitters caused by the pre-synaptic activity. In the pre-synaptic terminal, several sites (or pools) contain the neurotransmitters. They are reserved pool, readily releasable pool, and immediately releasable pool. Depletion of neurotransmitters in the readily releasable pool determines the STD.

Short-term depression and facilitation may coexist at the same synapse. The balance between the two depends on the number of the available vesicles of neurotransmitters, that is, the quantal content. High probability of release of neurotransmitter per action potential favors depression [114] (because the most readily releasable quanta are released first). The remaining quanta are less quickly released (due to the slow replenishment of quantal store). The low probability of neurotransmitter release per action potential favors facilitation [114]. Facilitation does not depend on the release of the neurotransmitter during the pre-synaptic spike. Only the entry of calcium after the first pre-synaptic spike causes facilitation. The residual calcium exists always after every pre-synaptic spike. Over repeated spike activity increases the amount of remaining calcium thereby favors facilitation. Both STD and STF turn the static synapse into a dynamic synapse. The adaptive strength of the STP ensures the synapses to display various temporal dynamics. Few of them will be discussed in the next sections of this chapter.

#### 2.2 MODELS OF SHORT-TERM PLASTICITY

Several models based on the bio-physical mechanisms of Short-Term Plasticity (STP) have been proposed in the literature [108, 71, 107]. STP models from [108] and [71] will be briefly discussed in this section as they are commonly used in neuroscience research.

Abbott and his colleagues proposed a STP model in [108]. They fit the recordings from the excitatory synapses (in layer 2/3) of rat primary visual cortex with the STP model.

The parameters from the fits are then used to predict the responses of the STP model to arbitrary stimuli. This STP model provides a tool to understand the role of synaptic processes in the sensory responses of cortical neurons. In biology, STP is characterized by the change in the amplitude of the Excitatory Post-Synaptic Potential (EPSP) due to the modification in the synaptic strength. In the model, the change in the response amplitude A results from the product of an initial amplitude and dynamic variables representing facilitation and depression. The EPSP amplitude A is defined as:

$$A = A_0 \cdot F \cdot D \tag{1}$$

where  $A_0$  is the initial value of EPSP amplitude. F is the facilitation variable which is  $\geq$  1, and D is the depression variable which is  $\leq$  1. The dynamic variables are updated for each incoming pulse by the following equations:

$$\mathsf{D} \leftarrow \mathsf{D} \cdot \mathsf{d} \tag{2}$$

$$F \leftarrow F + f$$

(3)

where d and f are constant factors. They represent the amount of depression and facilitation per pre-synaptic action potential. The depression is updated multiplicatively, whereas the facilitation is updated additively, to limit the substantial effects of facilitation, especially during the high-input frequencies.

During Inter-Spike intervals (ISIs), depression and facilitation variables recover toward their initial values exponentially, as given by the following first-order differential equations:

$$\tau_{\rm D} \cdot \frac{dD}{dt} = 1 - D \tag{4}$$

$$\tau_{\rm F} \cdot \frac{{\rm d}F}{{\rm d}t} = 1 - F \tag{5}$$

where  $\tau_D$  and  $\tau_F$  are the time-constants of depression and facilitation.

For simplicity reasons, we considered only the two-compartment model with one depression variable D, as proposed in the original model in [108]. On the contrary, the four-compartment model has several depression variables  $D_1$ ,  $D_2$ , and  $D_3$  and different time-constants. This simple model can capture the main features of the short-term temporal dynamics that affect the strength of the synapse during and between input pulses. The model also predicts the complex stimulation patterns such as Excitatory Post-Synaptic Current (EPSC) responses to random stimulus trains, similar to those occurring in vivo. However, the model lacks the precision to predict the response to specific stimuli within the spike train (due to the increase in the error of the fits that follows the trial-to-trial variability in the data).

We look into another phenomenological model of STP proposed by Markram and his colleagues in [71]. The model was used to analyze the transmission of essential synaptic features to the post-synaptic neuron during STP. The following equations characterize the model:

$$\frac{\mathrm{dR}}{\mathrm{dt}} = \frac{1-\mathrm{R}}{\mathrm{D}} \tag{6}$$

$$\frac{\mathrm{d}u}{\mathrm{d}t} = \frac{\mathrm{U}-\mathrm{u}}{\mathrm{F}} \tag{7}$$

where STD and STF are represented as two independent variables R and u respectively. U corresponds to the utilization of synaptic efficacy which is determined by the probability of release of neurotransmitters. D represents the time-constant of depression, and F represents the time-constant of facilitation. This is also a simple model with only three parameters, U, D and F the values of which are  $\leq 1$ . The model is updated for every incoming pre-synaptic action potential by the following equations in the preserved order:

$$\mathsf{R} \leftarrow \mathsf{R} \cdot (\mathsf{1} - \mathsf{u}) \tag{8}$$

$$\mathbf{u} \leftarrow \mathbf{u} + \mathbf{U} \cdot (1 - \mathbf{u}) \tag{9}$$

The parameter U determines the peak value of the first action potential. A small U favors facilitation and a significant U results in depression. Features that get transferred from the pre-synaptic neuron to the post-synaptic neuron during the STP are investigated using this model in [71]. This model suggests the change in the input frequencies is the most significant feature that gets transferred across the neurons. The above mentioned STP models are commonly used by the neuroscientists to demonstrate the computational role of STP in individual neurons as well as in large networks (which will be discussed in the following section). These models laid the foundation of designing STP circuits in silicon [15].

#### 2.3 COMPUTATIONAL ROLE OF STP

Several scientific works explain the computational significance of STP at the level of single neurons as well as in large networks. This section will be useful in understanding the fundamental properties of the STP based on which our circuits and the network are designed. Few of the primary computational roles of STP synapses will be discussed in the following.

#### 2.3.1 Temporal filtering

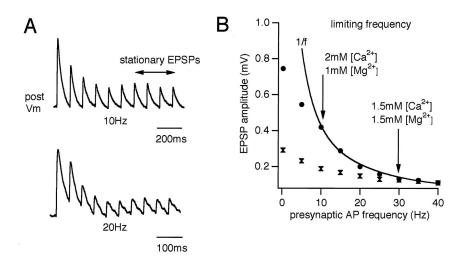

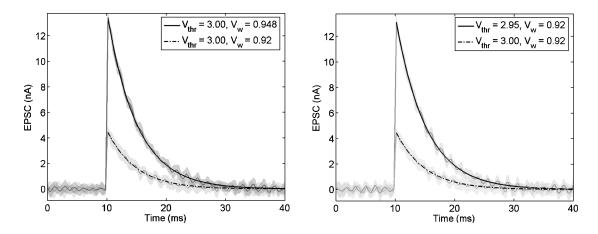

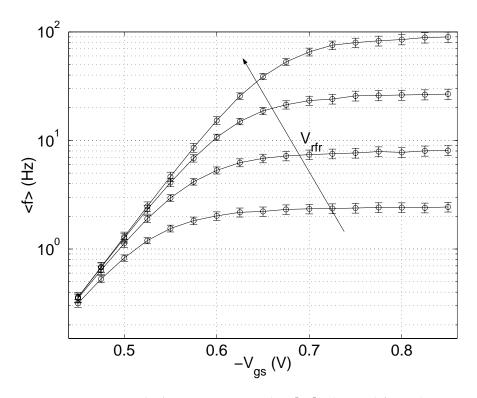

Synapses of a brain act as temporal filters to the incoming neuronal signals. STP implements one such filtering mechanism that affects the strength of the synapse. The strength of the synapse with STD is gradually decreased in response to a continuous stream of pre-synaptic spikes. This effect makes the post-synaptic neuron less responsive to a sustained stimuli. At the same time, the synaptic strength is recovered during the ISIs. An example, describing the filtering properties of STD presented in [107] is shown in Fig. 1.

In case of a low-frequency stimulus, sufficient time is available for STD to recover the synaptic strength back to its initial value. On the other hand, the synaptic strength is reduced quickly, to a high-frequency stimulus. Hence, STD tunes the synapse as a low-pass filter given that the high-frequency components of the stimulus are suppressed, and the low-frequency components are transmitted with the highest strength.

Opposite behavior is observed in the case of STF, during which the strength of the synapse increases in response to incoming spikes. Initially, the post-synaptic neuron does not respond to the incoming spikes, due to the weak synapse. Over repeated

Figure 1: Temporal filtering properties of STD measured at the neocortical pyramidal neurons, presented in [107]. The EPSPs responses of the same neuron, averaged over 20 trials, to a 10 Hz (top) and 20 Hz (bottom) spike train stimuli are shown in (A). In both the frequencies, the amplitude of the EPSP is decreased and eventually reached a steady-state value (stationary EPSP) over repeated stimulation, due to the presence of STD. The EPSPs amplitude recovers towards its resting value during the ISIs. The magnitude of the stationary EPSP in response to the 20 Hz stimulus is smaller than that of 10 Hz stimulus. The EPSP amplitudes (stationary) plotted against the pre-synaptic stimulus frequencies are shown in (B). The solid line shows the inverse relationship of the EPSP amplitude to (stationary) the pre-synaptic input frequency. Filled 'O' marks denote the responses to the high concentration of calcium, and filled 'X' marks denote the responses to low calcium concentration (see filled 'O' and filled 'X'), which slows the rate of synaptic depression. The low-pass filter characteristics of the neuron towards its pre-synaptic input frequencies are visible from this plot.

stimulations, the number of input spikes is increased, and as a result, the synapse becomes strong, due to the presence of STF.

The strength of the synapse recovers back to its weak initial value for a low-frequency stimulus due to large ISIs. However, the synaptic strength is increased in response to the high-frequency stimuli. Therefore, STF tunes the synapse as a high-pass filter given that the low-frequency components of the input are suppressed, and the highfrequency components are transmitted with full strength. It is to be noted that the synaptic strengths are always limited by the highest and the lowest possible values.

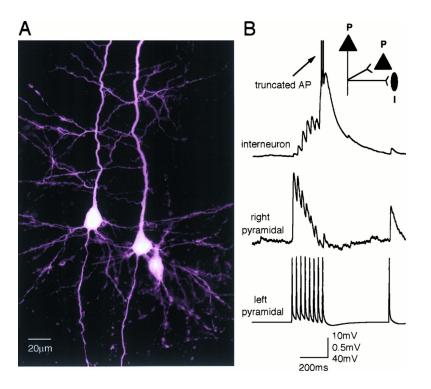

Figure 2: Selective communication between the neurons through STP using neuronal bursts, as shown in [71]. (A) displays the image of three biocytin-filled neurons pictured through the light microscope. Top right of the figure shows the connectivity diagram. The pyramidal neuron (left) is connected to the pyramidal neuron (right) and the bipolar inter-neuron (right). (B) shows the single-trial responses of all three neurons to the same input spike train with 30 Hz frequency. The left pyramidal neuron projects to the right bipolar inter-neuron through the STF synapse. The EPSPs of the inter-neuron builds-up and spikes at the end of the input burst, as a result of the increase in synaptic strength by STF. The left pyramidal neuron projects to the right pyramidal neuron through the STD synapse. The right neuron marks the onset of the burst with a spike, because of the high initial synaptic strength. Eventually, the amplitude of the EPSP is decreased, and no spike is elicited during the burst due to STD. After a long ISI which followed after the burst, the right pyramidal neuron responds again with a spike to a single spike input, as the strength of the synapse is recovered back to its high initial strength.

#### 2.3.2 Burst detection

Short-Term Plasticity (STP) in the synapse enables the post-synaptic neuron to detect bursts from the pre-synaptic neuron. 'Bursts' are strictly timed spikes with short ISIs. Following example explains the role of STP in identifying the neuronal bursts. Consider a burst of spikes stimulates a neuron through the STD synapse. Assume the strength of the STD synapse is high when the first spike of the burst arrives at the synapse. The incoming spikes reduce the synaptic strength (due to STD), because of insufficient time available to recover back to its original strength during a burst. In this way, the post-synaptic neuron can detect the onset of bursts due to the high initial synaptic strength.

On the contrary, imagine the post-synaptic neuron with the STF synapse is tuned for a specific frequency and duration of the burst, such that the neuron slowly builds up its Excitatory Post-Synaptic Potential (EPSP) during the burst without eliciting any spike. When the EPSP crosses the threshold, the neuron eventually spikes marking the end of the burst. Therefore, the STD and the STF makes the post-synaptic neuron to detect the onset and offset of the bursts. These burst detection properties enable the neurons to communicate to other neurons of the network [71] selectively.

An example to demonstrate the selective communication through STP is adapted from [71] and shown in Fig. 2. The light microscopic image of the three biocytin-filled neocortical neurons is shown in the left half of figure (A). The connectivity pattern of the three neurons is shown in the top right corner of figure (B), which shows that the left pyramidal neuron innervated the right pyramidal neuron as well as the bipolar inter-neuron (right). The synapse between the left pyramidal neuron and the right pyramidal neuron has STD. The synapse between the left pyramidal neuron and the bipolar inter-neuron has STF. The responses of all three neurons to the same spike train stimulus of 30 Hz frequency are shown in the bottom right part of the figure. When the left pyramidal neuron emits a mixture of spike bursts followed by a single spike with a large ISIs, the bipolar inter-neuron responds only to the bursts (due to the high-pass filter property of the STF). The right pyramidal neuron with the STD synapse responds to both the single spike input and the bursts (due to the high initial synaptic strength). In this way, a single neuron can communicate in different ways to other neurons through the STP synapses and the neuronal bursts.

#### 2.3.3 Gain control

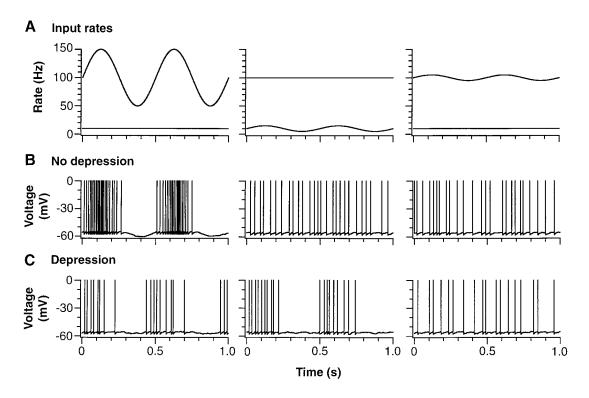

STD implements a gain control mechanism in the synapses. An example of this principle is demonstrated in [2] using an integrate-and-fire model. The setup consists of two neuron groups connected to one post-synaptic neuron. This neuron receives a low-frequency stimulus (10 Hz) through 100 synapses from one neuron group and a high-frequency stimulus (100 Hz) through another 100 synapses from the other group. A random spike train stimulus is presented to the network. Three experiments are performed by modulating the input frequency as shown in each column of the Fig. 3.

- Figure 3: The gain control established by STP, as demonstrated in [2]. (A) shows three input frequency modulations. (B) shows the post-synaptic neuron output without STD synapses. (C) shows the post-synaptic neuron output with STD synapses. Refer to the text for details about the network. Large high-frequency modulations are shown in the left, large low-frequency modulations in the middle and small high-frequency modulations in the right. Neuron without STD in (B) is unable to differentiate between the large low-frequency modulations (middle) and the small high-frequency modulations (right). Neuron with STD in (C) captures the large percentage modulations for the low-frequency stimulus (middle).

- Scenario-1: The high-frequency stimulus is modulated by 50% (i.e., 100  $\pm$  50 Hz) without changing its mean-frequency over time.

- Scenario-2: The low-frequency stimulus is modulated by 50% (i.e., 10  $\pm$  5 Hz).

- Scenario-3: The high-frequency stimulus is modulated by 5% (i.e.,  $100 \pm 5$  Hz).

Two different cases are considered for each scenario of this experiment. In the first case (Fig. 3 middle), the neuron has STD synapses and in the second case (Fig. 3 bottom), the neuron does not have STD in its synapses.

Let us start by discussing the case-1. Since there is no depression in the synapses, the strength of the synapses remains unchanged.

- Scenario-1: The post-synaptic neuron can capture the significant modulations of the high-frequency inputs in its output.

- Scenario-2: Large modulations of the low-frequency inputs do not affect the output.

- Scenario-3: The responses to small modulations of the high-frequency inputs look similar to the ones from scenario-2.

Let us proceed to the case-2. In this case, the synaptic weights adapt due to STD.

- Scenario-1: The post-synaptic neuron shows significant high-frequency modulations in its response. Meanwhile, the spike count drops due to STD. However, the synapses are tuned in such a way, that the synaptic weights are restored back before the input modulation completes its cycle.

- Scenario-2: STD amplifies the output of large low-frequency modulations with a high gain and suppresses the domination of high-frequency modulations with a low gain.

- Scenario-3: Unlike the case-1, responses to small high-frequency modulations are distinguishable from the responses to large low-frequency input modulations.

It is important to note in both the cases, the output of the post-synaptic neuron is a result of a combination of the low-frequency and the high-frequency inputs. However, with the presence of STD (case-2), the post-synaptic neuron can capture the modulations both in low- and high-frequencies. This way, STD controls the gain in large networks.

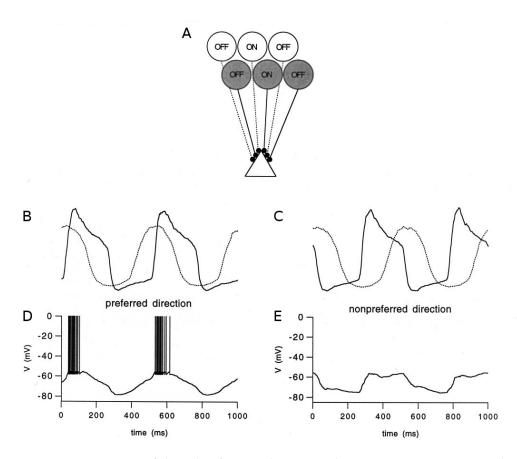

#### 2.3.4 Direction selectivity

The role of STD in direction selection is demonstrated in [19] and their implementation is discussed here. A small network of the visual cortex is modeled using the STD synapses. The network is shown in Fig. 4(A). Each circle represents a subset of afferent neurons in the ON-OFF receptive field. The ON afferent neurons stimulate the post-synaptic neuron called the V1 cell when the central region of the receptive field alone is exposed to luminance without the outer surrounding region. The OFF affer-

15

Figure 4: Demonstration of the role of STP in direction selectivity in vision, presented in [19]. (A) The network model of simple cells in the primary visual cortex. The top row represents afferent neurons without the STD, and the bottom row represents afferent neurons with STD synapses. The ON (or the OFF cells) in each row stimulate the V1 cell when the central region (or the surrounding region) of the receptive field is exposed to luminance. The EPSPs of the V1 cell is shown by presenting a sinusoidal signal on each row of the network separately (B and C) and on both the rows of the network simultaneously (D and E). EPSP of the V1 cell, when stimulated in a preferred direction, is shown in (B) and non-preferred direction in (C). Solid curves in (B and C) represents the EPSP of the V1 cell when stimulated through the STD synapses, and the dotted lines (B and C) denote the EPSPs when stimulated through the non-STD synapses. (B) The EPSPs are in phase when stimulated in a preferred direction. (D) The spiking behavior of the V1 cell when stimulated in a preferred direction. (C) The membrane potentials are out of phase when stimulated in a non-preferred direction. (E) The non-spiking behavior of the V1 cell when stimulated in a non-preferred direction.

ent neurons stimulate the same V<sub>1</sub> cell only when the surrounding region around the central region of the receptive field is exposed to luminance without the center. The ON and OFF afferent neurons are arranged in two rows, all converging into the V<sub>1</sub> cell. In the top row, the synapses between the afferent neurons and the V<sub>1</sub> cell have no STD, while in the bottom row, the synapses have STD.

A sinusoidal luminance signal is presented separately to stimulate the two rows of the network. The network is arranged in a spatially distinct manner, such that the stimulus reaches the non-STD afferent neurons row first when it comes from one direction, and the stimulus hits the STD afferent neurons when it comes from the other direction (see Fig. 4(A) for clarity). This arrangement provides a spatially distinguishable response, and STD offers a temporal variability in the output response.

By stimulating the non-STD afferents separately, the V1 cell shows oscillations in its EPSP (see Fig. 4(B) and (C) dotted lines).

When stimulated the STD afferents alone, the V1 cell shows saw-tooth-like waveforms (with a phase-advance) in its EPSP (see Fig. 4(B) and (C) solid lines).

Let us discuss the outcome of presenting the stimulus to both the rows simultaneously. Two directions are possible in this scenario: Either the signal hits the non-STD afferents first (non-preferred direction) or the other (preferred direction).

By presenting the stimulus in a non-preferred direction, even when both the rows responds, the V<sub>1</sub> cell fails to evoke a spike, because the afferent outputs are out of phase (see Fig.  $_4(D)$ ). However, when both the rows are stimulated in the other direction, the two afferent outputs are in phase, thanks to the phase-advancement by STD (see Fig.  $_4(E)$ ). Therefore, the V<sub>1</sub> cell responds with a maximum number of spikes for the preferred direction.

The output of the V1 cell depends on where the signal reaches first. Hence, STD can be used to implement direction selection in networks.

#### 2.3.5 Encoding sound intensity

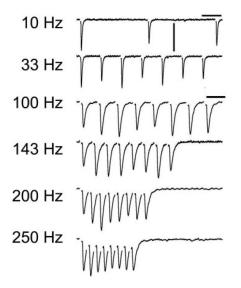

[69] presents the evidence of the STP in synapses of the auditory nerve in the auditory brainstem of the chick. Fig. 5 shows the averaged EPSP responses in response to eight input pulses that are provided for six different pulse frequencies [69]. The

Figure 5: Evidence of STP in the synapses of an auditory nerve in the auditory brainstem of the chick, as presented in [69]. The traces show the average responses of EPSPs to input trains of 8 pulses provided at six different pulse frequencies. The EPSP responses to 10 Hz and 33 Hz stimuli indicate the presence of the STD, as the maximum amplitude of the second EPSP is smaller compared to the first EPSP. In the responses shown from the 100 Hz stimulus to the 250 Hz stimulus, the magnitude of the second EPSP is higher compared to the first EPSP, which shows the presence of the STF with a faster time-constant than the STD. The amplitudes of the EPSP responses to the high-frequency stimuli start decreasing after receiving a certain number of input spikes. This fall in amplitude indicates the presence of the STD with a slow time-constant. The rise and the fall of the EPSP amplitudes in response to the high-frequency stimulus are postulated due to the interplay between the STD and the STF in the same synapse.

EPSPs in response to a low-frequency stimulus shows the presence of the STD, which is evident from the maximum amplitude of the second spikes of the 10 Hz and the 33 Hz stimuli. During intermediate frequencies starting from the second spike of the 100 Hz stimulus up to the 250 Hz stimulus, the effect of the STF is visible in the increase in their maximum amplitudes. At the same time, the maximum amplitudes of the EPSPs start decreasing after the enhancement of a few spikes in response to the high-frequency stimuli due to the STD. The competition between the STF and the STD at the same synapse results in the band-pass filter response of the neuron. Therefore, the presence of STP is evident in the audition, which plays a role in selecting particular frequencies that encode the preferred sound intensities. This kind of temporal bandpass filter is modeled using STP in an auditory network of female crickets to recognize the male calling songs. More details of this model and implementation can be found in see Chapter 5.

2.4 CONCLUSION

#### 2.4 CONCLUSION

So far, we discussed various computational roles of the STP such as temporal filtering, detecting bursts and controlling gain in this chapter. These temporal filtering properties are useful in shaping the network activity. We learned that the synapses with STP are relevant in sensory processing and higher-order cortical processing. The examples we discussed in this chapter justify the importance of modeling STP synapses in a single neuron as well as in large networks. The temporal filtering property of STP is the crucial element of this research. We used STP as a temporal filter in a small neural network, that selects the attractive stimuli (see Chapter 5 for more details). We also characterized the temporal filtering properties of the neuromorphic STP circuits that we designed (refer Chapter 4 for further information).

#### SUB-THRESHOLD NEUROMORPHIC HARDWARE

#### 3.1 INTRODUCTION

Neuromorphic engineering is a term coined by Carver Mead in the late 80's, which describes the use of the Very Large Scale Integration (VLSI) technology to implement the neural computations [72]. VLSI is a process of manufacturing integrated circuits or chips using many transistors. A transistor is a semiconductor device which acts as a voltage controlled current source, depending on the operation region (for example, it acts as a resistor in the ohmic region, see Sec. 3.3 for further explanation). The idea of neuromorphic engineering originated from building silicon neuron circuits by exploiting an equivalence between neuroscience and electronics. The ionic conductance of a biological neuron depends exponentially on the membrane potential of the neuron. Similarly, when the transistor is operating in the sub-threshold regime, the amount of flow of charge carriers in the channel of the transistor is exponentially dependent on the applied gate voltage of the transistor. The definition of the term 'neuromorphic' has been changed over the last two decades. Now any dedicated analog, digital, or mixed-signal hardware that emulates or simulates the computations of neurobiology is referred to as neuromorphic hardware. In the recent years, neuromorphic hardware has gained a lot of attention from the electronics community considering the power efficiency, processing speed, and scalability factor. Mixed-signal (analog/digital) neuromorphic platforms such as the sub-threshold neuromorphic system and 'BrainScales' perform parallel asynchronous computations. Therefore the speed of the operation does not scale with the network size. The power consumption of the sub-threshold hardware is low because the transistors are operated in a sub-threshold regime, during which the magnitude of the currents is in the order of nano- or pico-Ampere. The digital neuromorphic hardware also has its design optimised for power efficiency. For example, IBM's 'TrueNorth' neuromorphic chip is capable of classifying images at 6000 frames per second [32] per watt in comparison to NVIDIA's Tesla P4 which classifies images at 160 frames per second per watt. Therefore, the term 'neuromorphic' refers to the silicon implementation of the powerful and parallel computing elements of the brain. Neuromorphic systems offer a platform to emulate the neural networks directly on the hardware. The size of the network does not influence the speed of this neuromorphic hardware. In contrast to the Von-Neumann architecture of the conventional digital systems, memories are co-localized in the neuromorphic design of the analog systems. This feature makes the neuromorphic systems best-suited for computationally intensive tasks which involve extensive (write and) read operations (to and) from memory. For example, updating the synaptic weights in a network. There are different types of brain-like neural computing systems proposed in the literature, and we will discuss a few of them.

The Stanford University desinged a real-time neuromorphic system known as 'Neurogrid' [12]. Their chip is made of analog sub-threshold circuits that consume a small amount of power. A quadratic integrate-and-fire model is used to implement silicon neurons. The chip has an inbuilt router that communicates to other chips through spike packets. Neurogrid is aimed to be used in neuro-prosthesis and robotic applications.

The Institute of Neuroinformatics, University of Zürich and ETH Zürich designed two variants of full-custom mixed-signal neuromorphic chips called 'Dynap-se' for constructing spiking neural networks with dense connections and 'Dynap-le' optimized for online learning [51]. Currently, both the chips are prototypes, and they comprise low-power analog sub-threshold circuits that operate in real-time. These neuromorphic systems aim to reproduce the computations of the brain from the biophysics of the real neurons to the silicon neurons. The applications of this hardware cover a broad scope of possibilities, ranging from brain-machine interfaces to robotic applications. Recently, a neuromorphic processor called 'ROLLS' is designed in ETH Zürich using 180 nm CMOS process [88]. The chip consists of 256 neurons and 128k synapses. The chip is re-configurable and supports online learning. The chip also supports the implementation of attractor neural networks. The analog neuromorphic hardware offers low-power consumption in contrast to their digital counterparts. The hardware offers real-time (or accelerated) parallel computations. However, the models are fixed in the analog hardware and it is prone to issues such as variability in the responses and reproducability of the parameters.

The Heidelberg University developed a multi-scale wafer system called 'BrainScaleS' [99]. BrainScaleS is made of real analog circuits that operate transistors in the abovethreshold regime. The wafer-scale system delivers a speed of 10,000 times faster than the real-time. The basic communication is implemented within the wafer, and the wafer-to-wafer communication is implemented through the Field-Programmable Gate Array (FPGA). FPGA is an integrated circuit which consists of programmable logic gates

21

and I/O circuitry. BrainScaleS is designed with the aim to understand time-consuming factors of biological systems such as long-term training tasks. The models of learning synapses are continually evolving due to the recent advancements in neuroscience. Therefore, an on-chip plasticity processor is designed in the latest revision of the Brain-Scales called the 'HICANN-DLS', in which the learning rules are programmable [37]. The chip consists of 2k synapses and 64 neuron blocks and operates at a speed-up factor of 1000 compared to the biological real-time. Currently this chip is a prototype, and in the long run, it is aimed to be scaled-up to implement large-scale networks.

The University of Manchester developed a massively parallel digital computing machine known as 'SpiNNaker' [38]. SpiNNaker is a multi-core system made of ARM core processors that provide a real-time simulation environment for running synapse and neuron software models. The routing between the cores is based on the packetswitched Address Event Representation (AER) protocol, where the spikes are sent as packets. This system is developed with the goal of modeling large-scale spiking neural networks. The digital neuromorphic hardware offers several advantages such as the flexibility of the neural models and the portability of the parameters. However, the hardware has limitations for successful real-time operations.

Despite the university research groups, the silicon industries are also developing dedicated hardware to implement spiking neural networks, considering the promising outcomes of the neuromorphic computing research. IBM launched a fully digital neuromorphic chip called 'TrueNorth' [76]. Their chip consists of 5.4 million transistors fabricated in 28 nm technology made up of 4096 cores. Each core consists of 256 neurons and 256 synapses. TrueNorth is power-efficient and is used in real-time cognitive applications such as processing high-dimensional visual data.

The selection of the neuromorphic hardware varies with the target application. In this research, we aimed to model the synaptic computations at the level of single neuron in silicon. Given the small size of our network and the need for the biologically realistic time-constants (50-200 ms [89]), our best choice for this research is the sub-threshold mixed-signal hardware developed by Prof. E. Chicca and Prof. G. Indiveri at the Institute of Neuroinformatics, University of Zürich and ETH Zürich. We will start with a basic understanding of the transistors and the building blocks of sub-threshold neuromorphic circuits. Knowledge of these circuits is helpful in uncovering operation of STP circuits proposed in the next chapter. The working principles of silicon synapses and silicon neurons present in our neuromorphic hardware are explained. These synapses and neurons are used in constructing the calling song recognition network (see Chap-

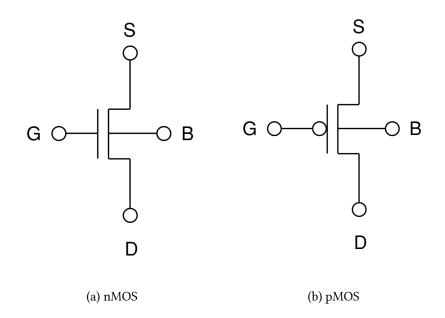

Figure 6: Transistor symbols presented in [64], showing the four terminals: source (S), drain (D), gate (G) and bulk (B). The bubble is used to denote the hole as a majority charge carrier in the pMOS.

ter 5 for more details). The setup of our neuromorphic hardware is covered towards the end of the chapter.

3.2 MOSFET

Transistors form the basic building block of modern electronics. Invented in 1947 at Bell Laboratories, transistors revolutionized the field of electronics. In modern technology, transistors are present in almost all electronic devices ranging from calculators to mobile phones we use every day. Transistors are commonly used in digital circuits to construct logic circuits and switches. The process of the fabrication has been improved a lot over the years, allowing to produce smaller devices. The semiconductor fabrication process defines the technology node based on the size of the smallest transistors that are commercially available. The size of the next technology node is expected to be 10 nm by 2017 in contrast to the 10  $\mu$ m sized node in the 70's.

Based on the structure, transistors are classified into Bipolar Junction Transistors (BJTs) and Field Effect Transistors (FETs). BJTs use both electron and hole charge carriers in their channels, whereas FETs are uni-polar transistors that are operated by a single-carrier-type in their channels. Junction gate Field Effect Transistors (JFETs) are purely voltage-controlled devices without any need for bias currents to turn them ON. Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) need a minimal current to

#### SUB-THRESHOLD NEUROMORPHIC HARDWARE

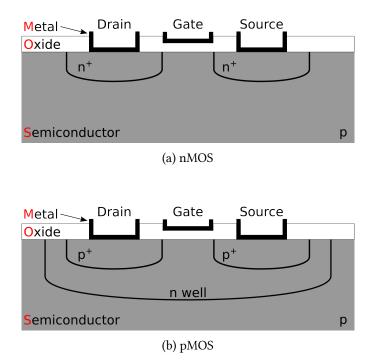

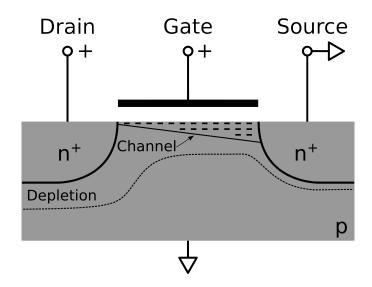

turn ON, and they can source high currents to the load. MOSFETs is one of the transistor types that are most commonly used in the VLSI design. The word metal (M) in the MOSFET is given because the gate of the transistor is used to be made from the aluminum in the earlier days, whereas now the gates of the transistors are made of poly-silicon. Traditionally, silicon-oxide (O) is deposited on the surface of the semiconductor (S) substrate to isolate the gate from the channel. The term (FET) corresponds to the field-effect transistor. An electric field is applied to alter the conductivity of the channel in the substrate of the MOSFETs. MOSFETs are divided into n-type and p-type based on their majority charge carriers. Fig. 6 shows the symbols of nMOS (a) and pMOS (b). MOSFETs consist of four terminals: source, drain, gate, and bulk. In this chapter, we describe the transistor design based on the single-tub process, because the transistors of the neuromorphic chips we use are manufactured using the same process. In this fabrication process, a separate n-tub or n-well is placed within the p-substrate to implant a pMOS. The cross-section view of the nMOS and the pMOS transistors are shown in the Fig. 7. In case of both the nMOS and the pMOS transistors, polycrystalline silicon doped with a p-type semiconductor material forms the substrate of the transistors. The gate of the nMOS and the pMOS transistors do not conduct any charge because of the insulator oxide deposited between the gate and the substrate. The bulk is a reference terminal for the transistors.

In the case of an nMOS transistor, the source is an n-type doped material on the psubstrate that serves as a source of electrons which is at a lower potential compared to the gate voltage of the transistor. The drain of the nMOS transistor is at a higher potential than the source and serves as the drain for the electrons. In nMOS, the bulk is the substrate, connected to the Ground. The movement of electrons results in a current flow across the nMOS transistor from its source to the drain through the channel.

The flow of holes (electron-holes) results in a current of pMOS transistors. The source of a pMOS is at a higher potential than the gate and serves as a source of holes. The drain of a pMOS is at a lower potential than the source and serves as the drain to holes. In pMOS, the bulk is a separate 'n'-well (see Fig. 7: top), connected to the power supply (VDD), to the source, or to any arbitrary voltage. According to the standard layout design rules provided by the manufacturer, a proper n-well placed for the pMOS occupies an ample space in the silicon and makes the pMOS design costly [64]. Nevertheless, pMOS is used as widely as nMOS transistors in the analog circuit designs.

# 3.3 SUB-THRESHOLD CHARACTERISTICS OF A TRANSISTOR

Both the nMOS and pMOS transistors can be operated in two regimes: the subthreshold and the above-threshold, based on the applied gate voltage. Transistors are used in the above-threshold regime in standard digital electronics as well as in conventional analog electronics such as Operational Transconductance Amplifiers (OTAs). In the digital domain, the transistors operating in the sub-threshold regime are considered to be OFF. Transistors are operated in the above-threshold regime, during which the currents are in the range of micro to milli-Ampere based on the fabrication process.

The operation of a transistor is shown in Fig. 8. When a positive voltage is applied to the gate of an nMOS, the holes in the channel are repelled towards the substrate

#### SUB-THRESHOLD NEUROMORPHIC HARDWARE

Figure 8: Cross-section of an nMOS transistor (source: Neuromorphic Engineering I lecture by Dr. Elisabetta Chicca). The n-type source and drain diffusion are visible in the p-substrate. The poly-silicon represented a black bar on top of the substrate is used as the gate. The oxide between the gate and the substrate is shown as white space. A depletion region is formed on the p-substrate below the gate between the source and the drain when a positive voltage is applied to the gate of an nMOS. Due to this positive voltage, the holes in the channel are repelled, and a depletion layer of negatively charged ions is formed. A thin inversion layer of free electrons called a channel is formed between the gate and the depletion layer when the gate voltage exceeds a certain threshold.

and a depletion layer of negatively charged ions is formed between the source and the drain below the gate. When the gate voltage exceeds a certain threshold, a thin inversion layer (or channel) of free electrons is also formed between the gate and the depletion layer. Hence, the above-threshold regime is also called a strong inversion mode. When the electric field is applied to the transistor, the drift-currents are created due to the movement of the free electrons. The drift current is the major component of the current source in the above-threshold regime.

In case of the sub-threshold regime, the inversion layer (or channel) is not formed when the gate voltage stays below the threshold. Hence, the sub-threshold regime is also called a weak-inversion mode. The diffusion of charges from source to drain results in diffusion currents. In the sub-threshold regime, the diffusion current is the major component of the current flow. The sub-threshold currents are tiny compared to the above-threshold currents and are in the order of pico- or nano-Ampere. The sub-threshold currents are in similar orders of magnitude (pico-Ampere), as measured in electro-physiology [52]. Small currents result in less power consumption of circuits which makes the sub-threshold transistors ideal choice for developing neuro-

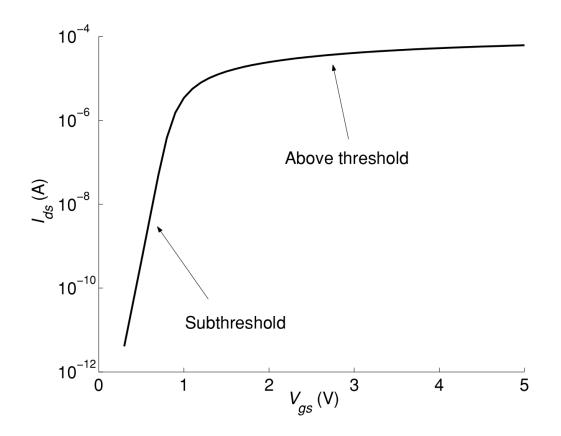

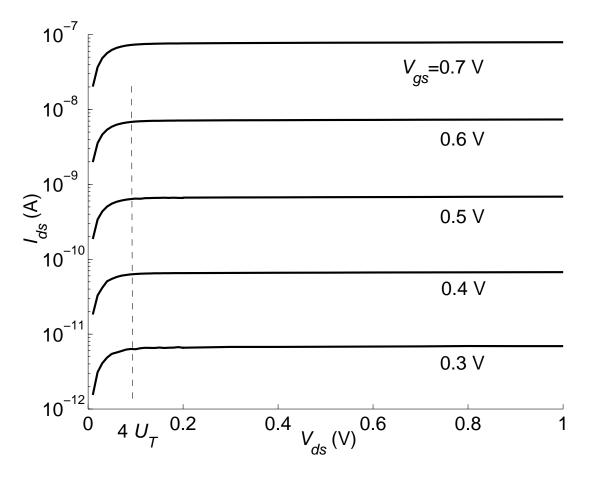

Figure 9: Sub-threshold Current-Voltage (IV) characteristics of the transistor presented in [64]. For a given gate-source voltage  $V_{gs}$ , transistor current raises linearly, when  $V_{ds}$  is  $\leq U_T$ , and gets saturated, when  $V_{ds}$  is  $\geq 4U_T$ , by changing  $V_{ds}$ .

morphic chips. These low-power chips are potentially useful in power-hungry computations: for example, real-time object recognition in mobile robots. We also used the sub-threshold transistors in our design of the STP neuromorphic circuits (see Chapter 4).

Current-Voltage (IV) characteristics of a transistor, for the gate-source voltage (gate voltage with respect to the source voltage)  $V_{gs}$  sweep is shown in Fig. 9. Both subthreshold and the above-threshold regimes are visible in the plot. In both the regimes, the transistor is operating in the saturation region, which will be discussed in the following section. Current-Voltage (IV) characteristics of a sub-threshold transistor is shown in Fig. 10. There are two regions of sub-threshold operation called linear (or ohmic) and saturation, depending on the applied drain-source voltage (drain voltage with respect to the source voltage)  $V_{ds}$ . Let us look into the behaviour of the transistor current in all these regions in the following.

Figure 10: IV characteristics of the sub-threshold nMOS transistor for various gate voltages, presented in [64]. The current increases exponentially for every 100 mV increase in gate-source voltage. Hence, the log y scale is used that spans the entire sub-threshold transistor currents, ranging from pico-Ampere to hundreds of micro-Ampere. Therefore linear increase denotes the exponential rise, and the saturation region denotes the linear rise in currents. It can be seen from the plots, that the transitions from the linear region to the saturation regions are independent of the applied gate-source voltages.

#### 3.3.1 Sub-threshold ohmic operation

For small  $V_{ds}$ , the current  $I_{ds}$  is approximately linear with  $V_{ds}$  as shown in Fig. 10. Therefore, it is called the ohmic or linear region of the sub-threshold transistor. The following equations describe the current-voltage (IV) characteristics of the nMOS and the pMOS operating in the sub-threshold linear region.

nMOS

$$I_{ds} = I_{n0} e^{\kappa_n V_g / U_T} \left( e^{-V_s / U_T} - e^{-V_d / U_T} \right)$$

(10)

$$I_{ds} = I_{n0} e^{(\kappa_n V_g - V_s)/U_T} \left( 1 - e^{-V_{ds}/U_T} \right)$$

(11)

For  $V_{ds} \leqslant 4U_T$ ,

$$I_{ds} \simeq I_{n0} e^{(\kappa_n V_g - V_s)/U_T} \left( V_{ds}/U_T \right)$$

(12)

*pMOS*

$$I_{sd} = I_{p0} e^{\kappa_p (V_{dd} - V_g)/U_T} \left( e^{-(V_{dd} - V_s)/U_T} - e^{-(V_{dd} - V_d)/U_T} \right)$$

(13)

$$I_{sd} = I_{p0} e^{(-\kappa_p V_g + V_s)/U_T} \left( 1 - e^{V_{ds}/U_T} \right)$$

(14)

For  $V_{sd} \leqslant 4U_T$ ,

$$I_{sd} \simeq -I_{p0} e^{(-\kappa_p V_g + V_s)/U_T} (V_{ds}/U_T)$$

(15)

where

- $I_{n0}$  and  $I_{p0}$  denote the transistor dark-currents. The dark-current comes from the random generation of electrons and holes in the depletion region. The dark-current contributes to leakage and serves as the source of noise in the transistor.

- $\kappa_n$  and  $\kappa_p$  denote the capacitive coupling ratio that determines the transistor sub-threshold slope factor.  $\kappa$  can be calculated from the slope of the log of IV characteristics of the sub-threshold transistor operating in the saturation region. There is a basic analog circuit called the source follower (explained in next section), the output of which depends on this slope factor.

- $U_T$  the thermal voltage.

- +  $V_g$  the gate voltage,  $V_s$  the source voltage, and  $V_d$  the drain voltage.

- $V_{dd}$  is the power supply voltage provided to the bulk.

#### 3.3.2 Sub-threshold saturation operation

For  $V_{ds} \ge 4U_T$ , the concentration of electrons at the drain end of the channel becomes negligible concerning the concentration at the source end. The diffusion current becomes independent of the drain voltage and depends only on the source voltage. It is called the saturation operation of the sub-threshold transistor as shown in Fig. 10. An ideal sub-threshold transistor operates in a saturation region. The equations of the saturated sub-threshold transistors are as follows.

nMOS

$$I_{ds} = I_{n0} e^{(\kappa_n V_g - V_s)/U_T} \left( 1 - e^{-V_{ds}/U_T} \right)$$

(16)

For  $V_{ds} > 4U_T$ ,

$$I_{ds} = I_{n0} e^{(\kappa_n V_g - V_s)/U_T}$$

<sup>(17)</sup>

*pMOS*

$$I_{sd} = I_{p0} e^{(-\kappa_p V_g + V_s)/U_T} \left( 1 - e^{V_{ds}/U_T} \right)$$

(18)

For  $V_{sd} > 4U_T$ ,

$$I_{sd} = I_{p0} e^{(-\kappa_p V_g + V_s)/U_T}$$

<sup>(19)</sup>

where

- $I_{n0}$  and  $I_{p0}$  denote the transistor dark currents.

- $\kappa_n$  and  $\kappa_p$  denote the capacitive coupling ratio.

- $U_T$  the thermal voltage.

- $V_g$  the gate voltage,  $V_s$  the source voltage, and  $V_d$  the drain voltage.

Ideally, in this region, the currents are exponential to the applied gate voltage. Therefore, this exponential characteristic is useful to model the biologically realistic temporal dynamics, which are also exponential. Mostly we operate all the circuits in our neuromorphic chip (mixed-signal hardware) in this region of the transistor. Therefore, the parameter choices are significant for the ideal operation of these circuits. The following section provides a better understanding of the subthreshold operation of these circuits.

# 3.4 BASIC BUILDING BLOCKS OF ANALOG VLSI CIRCUITS

Complex neuromorphic circuits, such as silicon synapse and silicon neuron circuits, are constructed based on analog building blocks. Few of these basic building blocks will be discussed in this section. The STP circuits we designed in this research are built based on these elements. These circuits are also used in developing general analog circuits outside the neuromorphic domain.

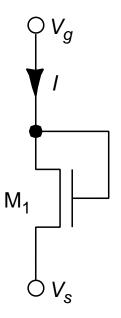

# 3.4.1 Diode-connected transistor

The schematic of the diode-connected transistor is shown in Fig. 11. The transistor itself is a voltage controlled current source. The current is an exponential function of the gate voltage when the transistor is operated in the sub-threshold saturation region. A sub-threshold transistor can be used as an exponential current-to-voltage converter by merely fixing the source voltage and providing the input current through the drain. However, the gate is isolated from the channel, and the input current does not have any effect on the gate. Therefore, the gate is shorted to the drain terminal, to see the change in the gate voltage for the given input current. In this configuration, the input node stays in a positive feedback loop with the gate terminal. As long as a sufficient amount of the current flows, the diode-connected transistor always operates in the saturation region (as the drain is reverse-biased with respect to the channel). The

Figure 11: Schematic of an n-type diode-connected transistor, presented in [64]. The positive feedback loop from the drain to the gate is needed to operate the diode-connected transistor in the saturation region.

transistor operates as a diode, allowing the current to flow from drain to source, at the same time, blocking the current flow in the opposite direction. The diode-connected transistor is used in building the current-mirror circuit (see next subsection).

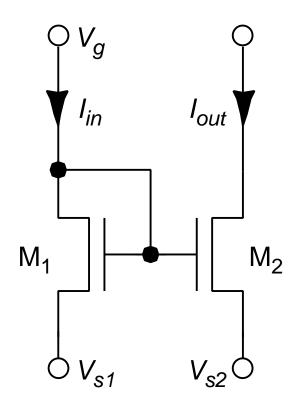

# 3.4.2 Current mirror

The schematic of a current-mirror circuit is shown in Fig. 12. The current-mirror is a two transistor circuit that mirrors the input current into a scaled output current. The circuit consists of two transistors of the same type, where one of them is a diodeconnected transistor, and the gates of the two transistors are shorted. The input is the current supplied through the drain of the diode-connected transistor. The output is the scaled version of the input current available at the drain of the other transistor. There are two configurations of the current mirror. In the first configuration, the source voltages are fixed. The transistor dimensions determine the linear scaling factor of the output currents. In the second configuration, the dimensions of both the transistors are identical. The source voltages are varied to determine the current-mirror gain which is exponential in this case. Based on the required type of gain, either the transistors width-and-length ratios or the source voltages are varied. In case of linear gain configuration, the transistor dimensions are fixed after fabrication. Therefore the gain is also non-modifiable. The current-mirror circuits are used in providing a positivefeedback loop, for example, in opamps or in silicon neuron circuits (to generate spikes

Figure 12: Schematic of an n-type current-mirror circuit, presented in [64]. The input current  $I_{in}$  is supplied through the drain of the diode-connected transistor. The gates of two transistors  $M_1$  and  $M_2$  are shorted. Therefore the input current is mirrored at the drain of the output transistor with a scaling factor. The scaling factor is decided either by the difference between the source voltages or the width-and-length ratios, depending on the current mirror configuration.

at a low-power). Current-mirrors can also be used to amplify small sub-threshold currents.

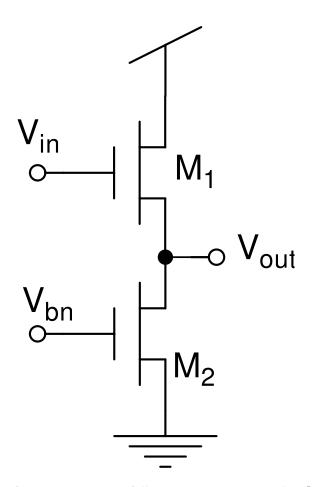

#### 3.4.3 Source follower

The schematic of a n-type source-follower circuit is shown in Fig. 13. The source follower is another type of the two-transistor circuit, the output voltage of which follows the input voltage with the gain. Two nMOS transistors are connected in series as shown in the figure. The bias voltage  $V_{bn}$  sets the total current flowing through the circuit. The input voltage  $V_{in}$  is provided to the input transistor. Output voltage  $V_{out}$ is measured at the connecting node of the transistors. The output voltage is the difference between the input and the bias voltages, multiplied by a scalar  $\kappa$ . The source follower can be used to provide an adjustable offset to a voltage, for example, a threshold in the silicon neuron circuit. It is also used in the neuromorphic dynamic vision

Figure 13: Schematic of an n-type source-follower circuit, presented in [64].  $V_{in}$  is the input voltage and  $V_{bn}$  is the bias voltage that sets the total current flowing in the branch of the source follower. The output voltage  $V_{out}$  follows the input voltage  $V_{in}$  (source) with a gain  $\kappa_n$ .

sensor together with the photo-diode. In this research, we used the source-follower to provide a negative-feedback loop in the STP circuits (refer Sec. 4.4 for more details).

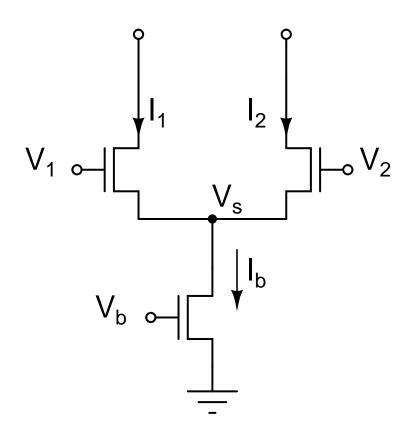

# 3.4.4 Differential pair

The schematic of a differential-pair circuit is shown in Fig. 14. The circuit consists of three transistors (in two branches), the output currents of which depend on the difference of two input voltages. The design of the circuit follows the same structure as the source follower, with an additional transistor connected to the source follower's common voltage node. The bias voltage  $V_b$  sets the whole current through the circuit. By Kirchoff's law, the sum of the output currents flowing through two input transistors is equal to the bias current. For a differential input voltage  $\delta V = V_1 - V_2$ , the resulting currents I<sub>1</sub> and I<sub>2</sub> are sigmoidal in shape. This non-linearity is useful in implementing several neural functions, for example, the activation function of a node in artificial neu-

Figure 14: Schematic of an n-type differential-pair circuit, presented in [64]. The differential pair shares the same basic structure as the source follower, except that the bias current  $I_b$  from  $M_b$  is shared by two input transistors  $M_1$  and  $M_2$ . When a differential voltage  $V_1 - V_2$  is applied to the input transistors, the resulting output currents  $I_1$  and  $I_2$  will be sigmoidal in shape.

ral networks. The differential-pair circuit is used to build amplifiers, silicon synapses, and neuron circuits.

All these essential analog building blocks we discussed until now, are used in the design of the vital neuromorphic circuits, which will be detailed in the following sections.

#### 3.5 SILICON SYNAPSE

A synapse is a junction through which a neuron communicates with other neurons. The synapse is a fundamental processing unit of neural computation. An average mammalian neuron spans around 1000 synaptic connections with the post-synaptic neuron, at the same time, a pre-synaptic neuron receives input spikes through approximately 10,000 synaptic links (for example, the Purkinje cell of the cerebellum [56]). Two types of synaptic connections exist. They are electrical and chemical synapses. The electrical synapses are also called gap junctions which are useful for short-range transmission of spikes between the neurons. The chemical synapses are used in long-range communi-

cations between the neurons and are capable of producing complex synaptic behavior such as amplifying the signals with a high gain. Silicon synapses presented here implement the conductance-based transmission model of the chemical synapses [27]. These synapses integrate the incoming spikes spatiotemporally from the pre-synaptic neurons. Simplified synaptic models describe the Excitatory Post-Synaptic Current (EPSC) as a step increase during the onset of the pre-synaptic spike. The EPSC decays exponentially after the pre-synaptic spike. This rise-and-fall dynamics of the EPSC has been implemented in many silicon synapses. Few of these synapse circuits designed using sub-threshold transistors will be discussed in this section.

Several analog synapses are proposed in the neuromorphic literature. One of the oldest sub-threshold transistor based 'pulsed current-source' synapse circuit is proposed by Carver Mead in [72]. The circuit consists of two transistors and outputs the synaptic current. The post-synaptic neuron connected to this synapse integrates the current and shows a rise in its membrane potential. The advantage of this circuit is compact design. However, the circuit cannot integrate the input pulses into continuous currents. Another drawback is, when the input spike trains with same mean rate arrive at different times to this synapse, it is not possible for the post-synaptic neuron to distinguish between the two input spike trains. Nevertheless, this synapse is widely used in [79], [39], and [22] due to its compactness.

Another compact synapse circuit called 'reset-and-discharge' was proposed by [61] in the early 1990s. For a given input voltage pulse, the synaptic current is produced. The duration of the output current can be modified by a tunable recovery. However, the circuit response depends on the last input spike only. Therefore, the linear summation of the post-synaptic currents is not possible at the neuron, which is an essential property in the theoretical analysis of neural networks.

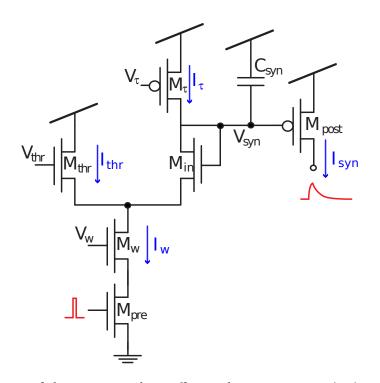

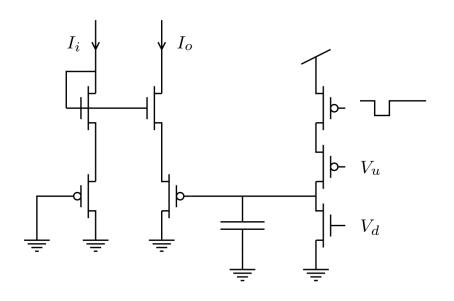

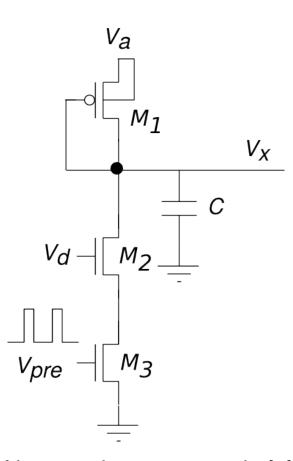

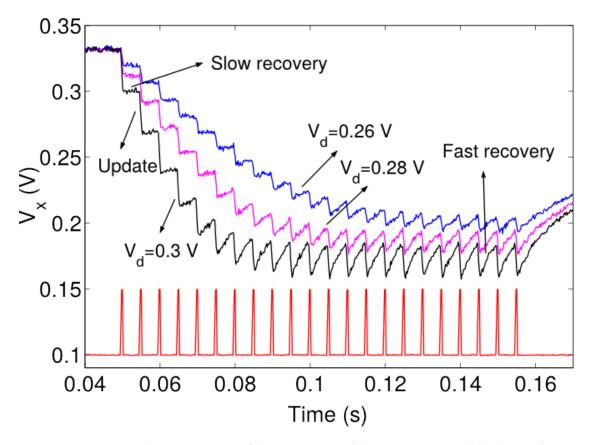

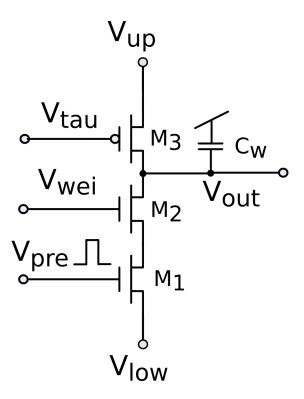

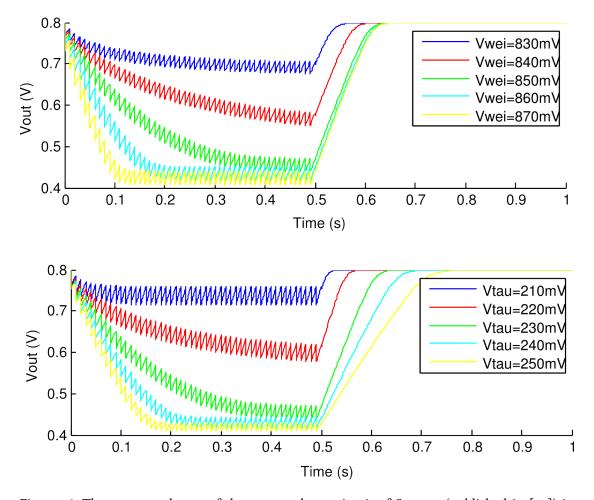

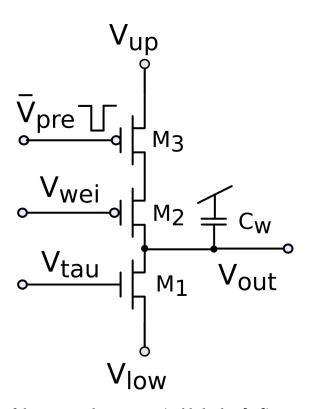

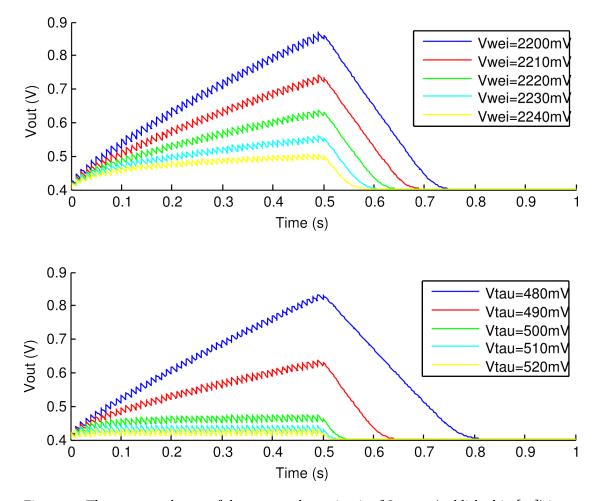

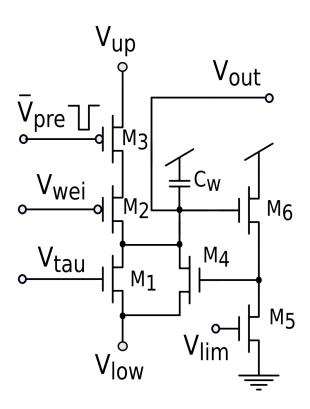

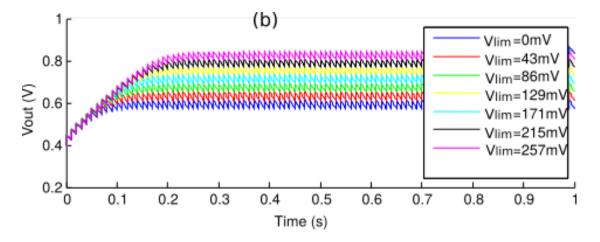

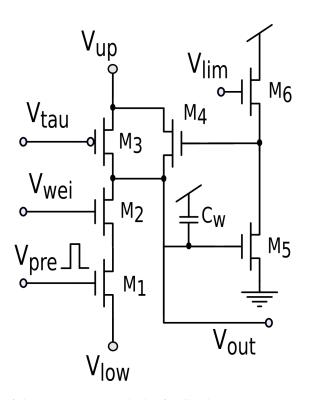

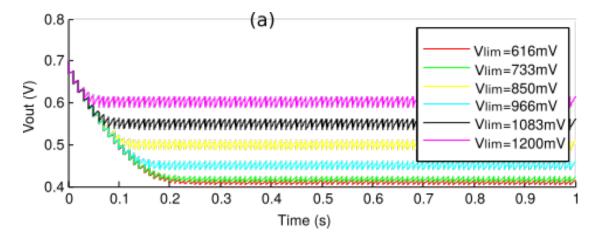

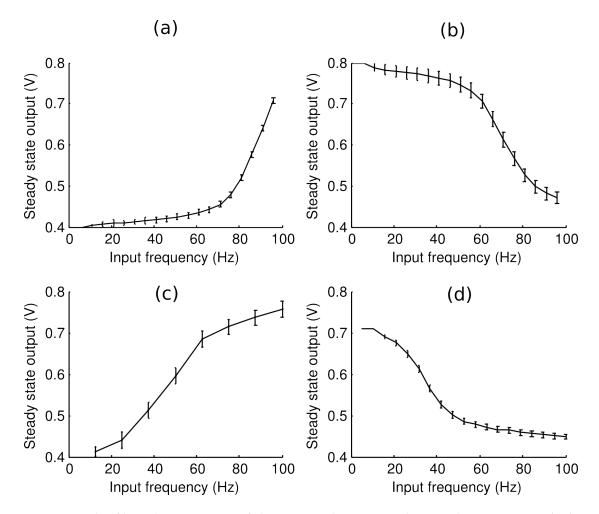

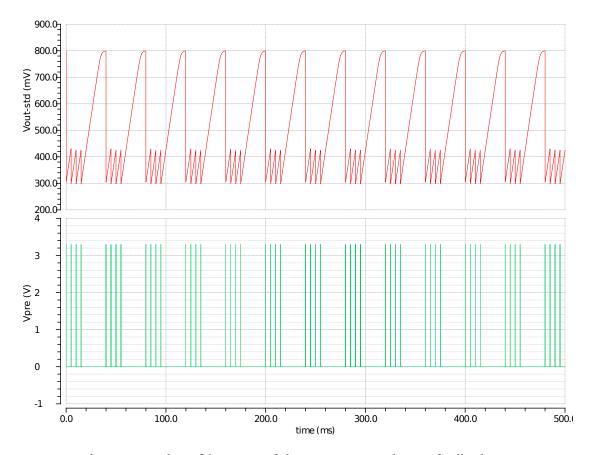

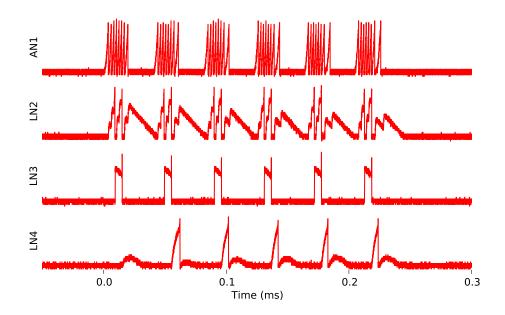

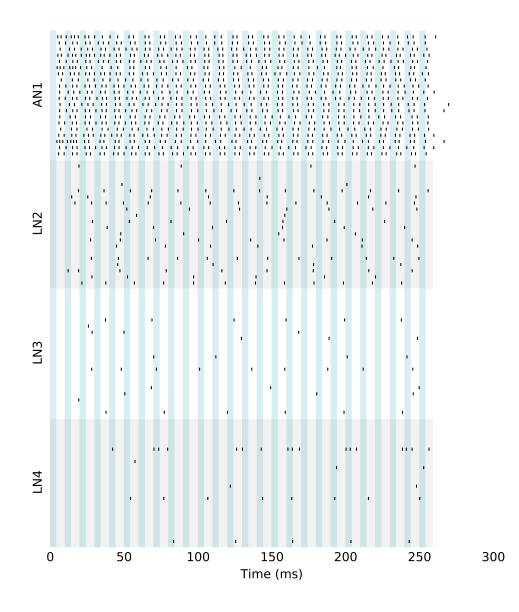

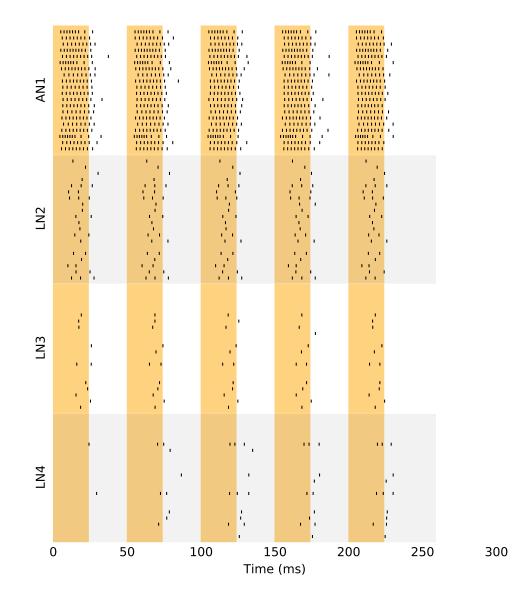

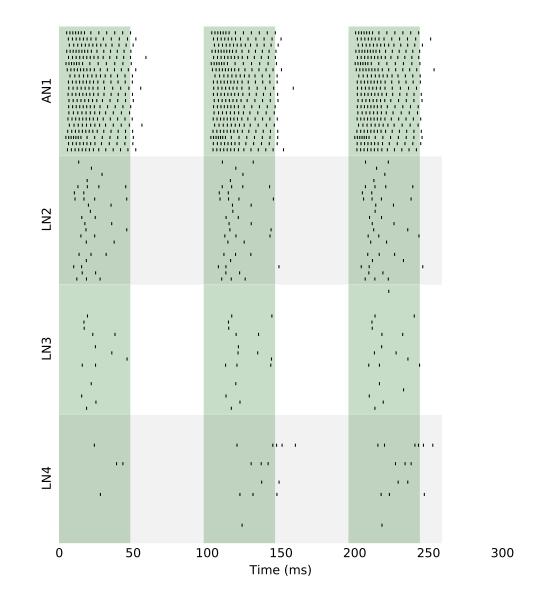

A modified version of the 'reset-and-discharge' synapse called the 'linear charge-anddischarge' synapse circuit is proposed in [5]. It is one of the commonly used synapse circuits in neuromorphic chips. However, the EPSC of the circuit saturates exponentially during which the input frequencies cannot be encoded by the synapse.