# Efficient Transactional-Memory-based Implementation of Morph Algorithms on GPU

Shayan Manoochehri

A Thesis in The Department of Computer Science and Software Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Computer Science at Concordia University Montreal, Quebec, Canada

# August 2017

© Shayan Manoochehri, 2017

# CONCORDIA UNIVERSITY

# School of Graduate Studies

This is to certify that the thesis prepared

By: Shayan Manoochehri

Entitled: Efficient Transactional-Memory-based Implementation of Morph Algorithms on GPU

and submitted in partial fulfillment of the requirements for the degree of

### M. Comp. Sc.

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|             | Dr. TH. Chen                                                     | Chair      |

|-------------|------------------------------------------------------------------|------------|

|             | Dr. H. Harutyunyan                                               | Examiner   |

|             | Dr. R. Jayakumar                                                 | Examiner   |

|             | Dr. D. Goswami                                                   | Supervisor |

| Approved by | Chair of Department or Graduate Program Director                 |            |

|             | Dr. Amir Asif, Dean<br>Faculty of Engineering and Computer Scien | nce        |

Date

# Abstract

# Efficient Transactional-Memory-based Implementation of Morph Algorithms on GPU

# Shayan Manoochehri

General Purpose GPUs (GPGPUs) are ideal platforms for parallel execution of applications with regular shared memory access patterns. However, majority of real world multithreaded applications require access to shared memory with irregular patterns. The morph algorithms, which arise in many real world applications, change their graph data structures in unpredictable ways, thus, leading to irregular access patterns to shared data. Such irregularity makes morph algorithms more challenging to be implemented on GPUs which favor regularity. The Borouvka's algorithm for calculating Minimum Spanning Forest (MSF), and multilevel graph partitioning are two examples of morph algorithms with varied levels of expressed parallelism. In this work we show that a transactional-memory-based design and implementation of the morph algorithms on GPUs can handle some of the challenges arising due to irregularities such as complexity of code and overhead of synchronization. First, we identify the major phases of the algorithm which requires synchronization of the shared data. If the algorithm exhibits certain algebraic properties (e.g., monotonicity, idempotency, associativity), we can use lock-free synchronizations for performance; otherwise we utilize a Software Transactional Memory (STM) based synchronization method. Experimental results show that our GPU-based implementation of Borouvka's algorithm outperforms both the fastest sequential implementation and the existing STM-based implementation on multicore CPUs when tested on large-scale graphs with diverse densities. Moreover, to show the applicability of our approach to other morph algorithms, we do a pen-and-paper implementation and complexity analysis of multilevel graph partitioning.

# Dedication

I dedicate this thesis to my mother and brothers who always supported me with love, and to the memory of my father who taught me to be strong and kind to others.

# Table of Contents

| Li | st of Tal    | bles, Figures and Algorithms                                      | vi           |

|----|--------------|-------------------------------------------------------------------|--------------|

| 1  | Introduction |                                                                   | 1            |

| 2  | Backg        | round                                                             | 6            |

|    | 2.1 (        | GPU Architecture                                                  | 6            |

|    | 2.1.1        | GPU System Model                                                  | 6            |

|    | 2.1.2        | GPU's Synchronization Mechanisms                                  | 8            |

|    | 2.1.3        | The Locks Challenges                                              | 9            |

|    | 2.2 Т        | ransactional Memory Model                                         | 10           |

|    | 2.2.1        | Transactional Memory                                              | 10           |

|    | 2.2.2        | Progress Guarantees                                               | 12           |

|    | 2.2.3        | Transactional Execution                                           | 14           |

|    | 2.3 (        | Overview of GPU STMs                                              | 16           |

|    | 2.3.1        | Block Level STM                                                   | 16           |

|    | 2.3.2        | Hierarchical Validation STM                                       | 19           |

|    | 2.3.3        | Lightweight STM                                                   | 20           |

| 3  | Transa       | actional-Memory-based Implementation of Minimum Spanning Forest A | Algorithm on |

| G  | PU           |                                                                   | 23           |

|    | 3.1 Т        | ransactional-Memory-based Minimum Spanning Forest                 | 25           |

|    | 3.1.1        | Edge Discovery Phase                                              | 27           |

|    | 3.1.2        | Merge Phase                                                       | 30           |

|    | 3.1.3        | Optimization                                                      | 35           |

|    | 3.2 E        | Experimental Evaluations                                          | 36           |

|    | 3.3 S        | ummary                                                            | 41           |

| 4  | Transa       | actional-Memory-based Implementation of Graph Partitioning on GPU | 42           |

|    | 4.1 N        | Iultilevel Graph Partitioning                                     | 43           |

|    | 4.1.1        | Coarsening                                                        | 45           |

|    | 4.1.2        | Initial Partitioning                                              | 47           |

|    | 4.1.3        | Un-coarsening                                                     | 48           |

| 4.2 Multi-threaded Graph Partitioning             |    |  |

|---------------------------------------------------|----|--|

| 4.2.1 Coarsening                                  |    |  |

| 4.2.2 Initial Partitioning                        |    |  |

| 4.2.3 Un-coarsening                               |    |  |

| 4.3 Segmented Sort and Pack                       |    |  |

| 4.3.1 Segmented Scan                              |    |  |

| 4.3.2 Primitives Built On the top of Scan         | 60 |  |

| 4.4 Transactional-Memory-based graph partitioning |    |  |

| 4.4.1 Graph Data Structure                        | 64 |  |

| 4.4.2 Coarsening                                  | 64 |  |

| 4.4.3 Un-coarsening                               | 71 |  |

| 4.5 Summary                                       | 75 |  |

| 5 Conclusion & Future Works                       | 77 |  |

| References                                        |    |  |

# List of Tables, Figures and Algorithms

| Table 3.1 USA Road Networks, Random, and R-MAT graphs                              | 37    |

|------------------------------------------------------------------------------------|-------|

| Table 3.2 K40 GPU versus serial and STM-based parallel on CPU                      |       |

| Figure 2.1 GPU's Execution Model                                                   | 6     |

| Figure 3.1 A graph with 4 vertices and 5 edges in the CSR format                   | 27    |

| Figure 3.2 Result of edge discovery phase in example graph                         | 29    |

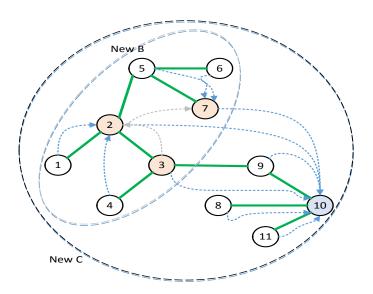

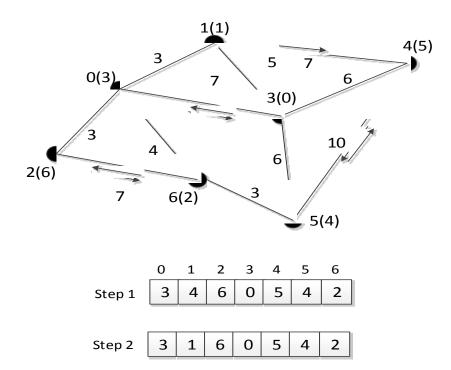

| Figure 3.3 Merge in example graph following the edge discovery phase               | 32    |

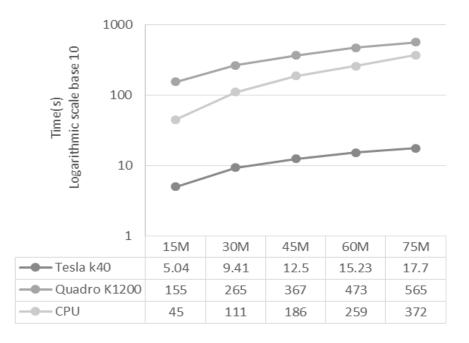

| Figure 3.4 Comparison of execution time of CPU versus different GPUs               |       |

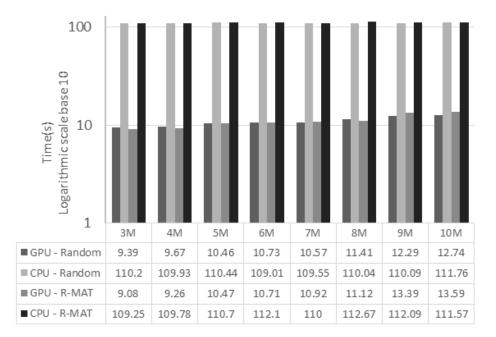

| Figure 3.5 Execution times on Tesla GPU versus serial on CPU for random/R-MAT grap | ohs39 |

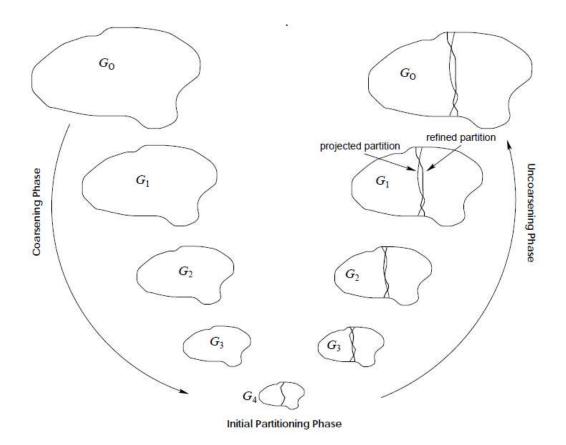

| Figure 4.1 Multilevel graph bisection adopted from [32]                            | 45    |

| Figure 4.2 Matching stage of coarsening phase                                      | 51    |

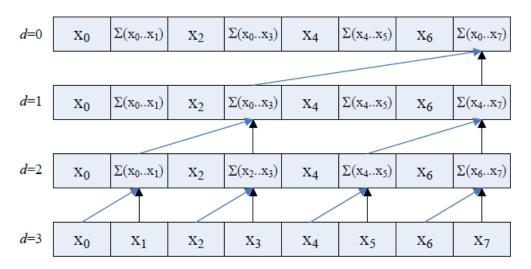

| Figure 4.3 Up-sweep phase of work-efficient sum scan algorithm adopted from [36]   | 57    |

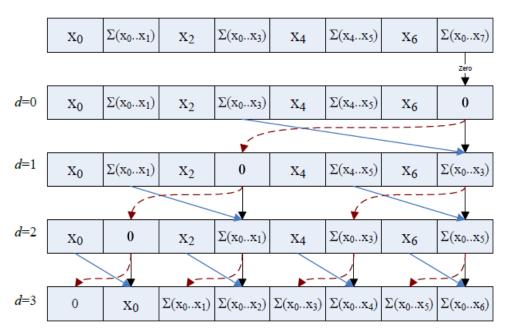

| Figure 4.4 Down-sweep phase of work-efficient sum scan algorithm adopted from [36] | 58    |

| Algorithm 2.1 Illustration of deadlock case in GPU                                 | 10    |

| Algorithm 2.2 Illustration of simple fix to deadlock issue in GPU                  | 10    |

| Algorithm 3.1 Borouvka's MST algorithm                                             | 24    |

| Algorithm 3.2 MST edge discovery operation                                         |       |

| Algorithm 3.3 Mark function used in priority based STM                             |       |

| Algorithm 3.4 Merge operation using STM transactions                               | 35    |

| Algorithm 4.1 Up-sweep (reduce) phase of a work-efficient sum scan algorithm       | 56    |

| Algorithm 4.2 Down-sweep phase of a work-efficient parallel sum scan algorithm     | 57    |

| Algorithm 4.3 Reduce (up-sweep) phase of a segmented scan algorithm                | 59    |

| Algorithm 4.4 Down-sweep phase of a segmented scan algorithm                       | 60    |

# **1** INTRODUCTION

An application with data-level parallelism (DLP) contains computations that can be performed on many data items simultaneously. In contrast, the task-level parallelism is expressed in computations wherein multiple tasks can be executed in parallel. An application with data-level parallelism scales with the increase in amount of data, whereas an application with task-level parallelism scales as the number of functionalities increase [1]. GPUs are throughput-driven, highly multithreaded processors benefiting the applications with large data-level parallelism to achieve high performance. DLP computations can either be performed in regular or irregular fashion, as we discuss in the following.

An application's behavior, with respect to the control flow and memory access patterns, is largely determined by its degree of dependency to the values of data items. When the dependency is predictable or follows a pattern, the data-parallelism is regular; otherwise, the behavior of the application is irregular. In regular parallelism, roughly identical computation is performed on each data item; therefore the load balance on processing cores is easy to achieve leading to efficient utilization of the system resources. Furthermore, the predictable memory access patterns can be exploited to improve the efficiency of memory transfers, i.e., memory accesses exhibit spatial and temporal locality as the result of predictable behavior expressed in the regular computation which can be exploited for DLP computation optimizations.

On the contrary, in irregular parallelism, the amount of computation performed in each data item can be quite variable. The challenges to efficiently perform these computations are mainly due to: (1) the control flow of each data item's processing is data-dependent, which leads to load imbalance. (2) The branch divergence arising due to if-then-else constructs, which can lead to underutilization of the SIMD hardware in GPUs. (3) The irregular memory access patterns, which make it difficult to group memory transfers that exhibit temporal and/or spatial locality into one memory request (memory coalescing), leading to underutilization of the high memory bandwidth available in GPU.

Widespread deployment of GPUs in the recent years has resulted in substantial speedup of applications with regular memory access patterns. However, many real world applications exhibit computations with irregular DLP. Some of the irregular computations are originated from the complexity of data structures they use, e.g. graphs. Morph algorithms [2] are a type of irregular algorithms that change the underlying graph data structure in unpredictable ways, making them difficult to exploit memory coalescing and mitigate control flow divergence on GPUs. Moreover, the implementation of the morph algorithms in massively multi-threaded environments give rise to synchronization problems caused by dynamic data sharing. This leaves us with a question with no clear answer: how should we reduce the cost and complexity of synchronization overheads in these applications to be able to fully utilize the processing power of the thousands of GPU cores?

Examples of some of the morph algorithms are: Borouvka's Minimum Spanning Tree (MST) algorithm [3] to find a minimally weighted subset of the graph edges that connects all the vertices without any cycle; multilevel graph partitioning to divide the underlying graph to partitions of roughly equal size via three phases: coarsening, initial partitioning, and uncoarsening; and Delaunay Mesh Refinement (DMR) to transform triangles of the given triangulated input mesh that do not conform to certain quality constraints by recreating the neighborhood around them. Parallelizing morph algorithms on GPUs exemplifies the challenges of executing irregular real world applications, and is the focus of our research.

Over the past few years, there have been some implementations of morph algorithms on GPU, which are relatively complex and non-scalable. Vineet et al [4] implemented a recursive formulation of Borouvka's algorithm on GPU using CUDA primitives such as scan, segmented scan, and split. However, their approach is not only complicated but also doesn't scale well to larger graphs due to the restrictions on the input graph. Nasre et al. [5] implemented the Borouvka's algorithm on GPU, avoiding any synchronization all together. On the downside, they proposed a rather complex algorithmic technique deviating from the phases of the original algorithm, e.g., it included a phase to break the formation of cycles among components to prevent race conditions. Moreover, their approach did not prove to be quite efficient, which could be due to the extra work required to avoid synchronization, as we show in our experimental results.

On the other hand, there are other works which are not quite reliable, e.g., Nasre et al. [6] have proposed a techniques to improve the performance of DMR algorithm by performing a three-phase race-and-resolve synchronization method using global barriers. Unfortunately, global barriers can result in poor performance on GPU due to load imbalances caused by dissimilar workloads. Moreover, it has the potential of causing livelocks which makes it an unreliable technique.

Software Transactional Memory (STM) [7] is a software method supporting transactional programming of synchronization operations. It simplifies development of parallel code by allowing the programmer to mark sections of the code that should be executed concurrently and atomically in an optimistic manner. High abstraction level of STM makes the transition from the algorithmic design to implementation a natural process as opposed to tedious programming efforts required in a lock-based implementation.

Cederman et al. [8] implemented two versions of blocking and non-blocking STMs on GPUs that work with the granularity of one thread-block, which limit the proper utilization of system resources. They employed linear and exponential backoff functions to recover from transactional conflicts as well as avoiding livelocks. Later, Xu et al. introduced GPU-STM [9] with a hierarchical validation approach which is a combination of timestamp-based and value-based validations. They used locks-sorting to avoid livelocks. None of the above STMs showed good scalability, mainly due to expensive conflict detection mechanism they employed.

Following Xu et al. [9], Holey et al. [10] presented a scalable Lightweight Software Transactions for GPUs with a back-off strategy to avoid livelocks. Their work is more efficient as compared to GPU-STM as it lowered the overhead of STM by introducing two variations of STM supports: ISTM (invisible reads) and PSTM (pessimistic). ISTM introduced invisible reads to reduce conflicts during a transaction where reads with no modifications to memory locations comprised the good portion of memory accesses. PSTM is a simpler, yet more effective, method in majority of applications where transactions regularly read and write to the same memory location. It treats the writes and reads in the same manner, leading to simpler design and reduced overhead, therefore, resulting in higher scalability especially when the contention level is high.

Shen et al. [11] introduced a priority rule based STM (PR-STM) which incorporates a lock stealing technique to avoid the possibilities of both livelocks and deadlocks by prioritizing transactions based on the threads' identifiers. We built our STM on top of PR-STM and incorporated the optimization technique used in PSTM to lower some of its overheads. Both Shen's and Holey's work show a good level of scalability in the benchmark applications they used. However, we chose to build on the work of Shen mainly because of the backoff strategy which is not a natural match for GPU due to its SIMD hardware.

In this thesis, we demonstrate efficient transactional-memory-based design and implementation of some of the morph algorithms on GPUs. We believe that transactionalmemory-based design facilitates the scalable implementation of the algorithm and reduces the amount of programming effort. In each major phase of the algorithm, we first attempt to extract certain algebraic properties of the computation (e.g., monotonicity, idempotency, and associativity) [6] to exploit lock-free transactions for performance. Otherwise, we utilize an STM based synchronization method. We also apply different optimization techniques like "*warp segmentation*" [12] in our implementation to maximize the load balance which can lead to proper GPU utilization and good performance.

To show the effectiveness of our transactional-memory-based approach, we implemented the Borouvka's algorithm on GPU: in the first major phase of the Borouvka's algorithm (edge discovery), we extract certain algebraic properties of the computation (monotonicity) [6] to exploit lock free synchronization. The edge discovery phase is monotonic due to ever decreasing values produced in finding the MSF edges. However, due to lack of such properties in the merge phase, we apply STM based synchronization, using our priority-based STM implementation. Moreover, to show the applicability of our approach to other irregular algorithms, we perform a pen-and-paper design and analysis of a transaction-memory-based multilevel graph partitioning algorithm, wherein STM transactions are used during coarsening (matching stage) and un-coarsening (refinement stage) phases.

The main contributions of this research are as follows:

• Design and implementation of an STM-based Borouvka's MSF algorithm. The STMbased approach improves the programmability and cost of synchronization as compared to some other existing approaches that use fine-grained locks or algorithmic methods to avoid locks altogether. The STM-based approach is also simple to implement, which reduces the gap between the original algorithm and its actual implementation.

- Implementation of a priority-based STM to be used in the synchronization steps of a morph algorithm.

- Comparison of our experimental evaluations with the sequential and STM-based multicore implementations of MSF for large graphs (both real-world and artificial) demonstrates substantial performance improvement.

- We demonstrate the applicability of our approach to other morph algorithms by discussing a pen-and-paper design and complexity analysis of the multilevel graph partitioning algorithm.

The rest of this thesis is organized as follows: chapter 2 elaborates the background information including GPU architecture, Transactional Memory, and an overview of STM implementations on GPU. Chapter 3 elaborates the design and implementation of the transactional-memory-based Borouvka's algorithm on GPU and our priority-based STM; this is followed by a discussion on the experimental evaluations and analysis. In chapter 4 we discuss the design and analysis of a transactional-memory-based multilevel graph partitioning algorithm. Finally, Chapter 5 concludes the thesis with a discussion on future works.

# 2 BACKGROUND

# 2.1 GPU Architecture

In this section, we first start by outlining the system model of GPU and then explain GPU's synchronization mechanisms, namely atomic operations and barriers. Finally, the challenges of using locks in GPU are discussed.

# 2.1.1 GPU System Model

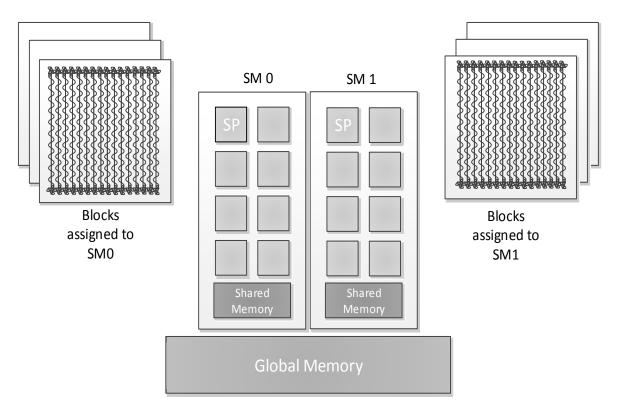

Figure 2.1. GPU's Execution Model.

A GPU application starts on the CPU and uses a compute acceleration API such as CUDA [13] to launch a highly multithreaded kernel onto the GPU. Introduced by NVIDIA, CUDA is a general purpose parallel computing architecture to execute compute-intensive programs on NVIDIA's graphics processors. Moreover, CUDA provides a compiler for a language based on C/C++ with the extensions in order to run kernel codes (functions) on the NVIDIA's GPU. In the following we use all the terminologies related to CUDA.

GPUs support thousands of threads executing in parallel. Such computing power is provided by an array of streaming multiprocessors (SM). Each kernel launch consists of a hierarchy of threads, called a grid, executing the same compute kernel. The thread hierarchy organizes threads as thread blocks wherein each thread block is scheduled to one of the SMs as a single unit of work, staying there until all of its threads complete execution. At execution time, threads within the same thread block are further partitioned into warps [13] to exploit their regularities and spatial localities.

As it is shown in Figure 2.1, each SM consists of an array of simple cores that are referred to as streaming processors (SP). In a given cycle, the SPs belonging to a single SM execute the same instruction but on different memory locations, an execution model known as single instruction multiple data (SIMD) or single instruction multiple threads (SIMT) [13] due to hardware threading. Threads within the same warp are simultaneously scheduled to the SIMT cores or SPs, and thus are executed in lockstep fashion, while threads across different warps are executed asynchronously in a multiple instruction multiple data (MIMD) like fashion. Moreover, using memory access coalescing mechanism, multiple consecutive accesses to the same DRAM row are coalesced to generate a single memory request, leading to an efficient memory operation.

Moreover, the arrangement of threads into warps by the programmer provides optimizations with respect to control flow. Ideally, threads within the same warp execute through the same instruction path, so that the GPU's SIMT cores can execute them in lockstep fashion. However, a warp may encounter a branch divergence when its threads diverge as the result of data-dependent branches. Modern GPUs contain masking hardware to handle branch divergence until the threads re-converge.

Note that GPU kernel can be launched with any number of thread blocks that can go beyond the capacity of GPU on-chip resources. The thread blocks of a grid are enumerated and distributed to multiprocessors with their available execution capacity, i.e., the launch unit dispatches as many thread blocks as the GPU's capacity, and dispatches the remaining thread blocks when the resources are released by completed thread blocks; this process ends when all the thread blocks are dispatched and completed. Such hardware-accelerated thread scheduling mechanism distinguishes GPUs from other processors such multi-core. Therefore, given such mechanism, GPU applications can decompose their workloads into as many threads as possible without imposing any major overhead.

The GPU contains an on-chip memory in each SM, which is explicitly managed by a programmer, referred to as the shared memory. The shared memory is accessible among different threads of each SM-assigned thread block. On the other hand, global memory, which is an off-chip device memory, is accessible to all threads in a GPU kernel. The access latency of device memory is high which can potentially make the memory accesses costly.

To compensate for such high memory latency, (1) consecutive memory accesses to device memory from different threads in a warp are automatically coalesced, i.e., combined into a single larger access, exploiting GPU's large memory bandwidth, and (2) fast context switching in each processing core help to perform some useful computation while waiting for the memory operation to complete, where only a limited number of threads are allowed on each processing core. As opposed to global memory, local memory is private to individual threads, although, it also resides in the off-chip device memory.

# 2.1.2 GPU's Synchronization Mechanisms

#### **Atomic Operations**

GPUs provides hardware-based atomic operations for the GPU kernels to synchronize critical sections with supports for both shared and global memory spaces. Such atomic mechanisms are capable of updating a memory location atomically with a new value computed based on the old value. An atomic operation involves 3 steps: reading the old value from the memory location, modifying it into a new value, and writing the new value back to memory where all three steps are performed atomically with respect to the thread executing the atomic operation.

Moreover, the atomic operations are the basic primitives for constructing synchronization mechanisms such as locks, barriers, non-blocking data structures and software transactional memory. Among different types of atomic primitives, atomic compare-and-swap (CAS) is the basis to build other atomic primitives in GPUs such as atomic min, max, add and etc. An atomic CAS receives 3 input parameters: the memory location to be updated, the expected old value at the location, and a new value; this primitive will write the new value into the memory location

only if the location's current value is equal to the expected old value. If the operation is successful the old value is returned to the thread, otherwise, the new value is returned to indicate the failure, i.e., the atomic primitive of current thread aborts as other thread has changed the value of the location before the current thread has a chance to complete. The CAS may be repeated using a loop construct until it succeeds.

#### **Barriers**

A barrier provides synchronization among a set of threads such that none get past the barrier until every thread in the set has reached to the barrier. Barriers can be used in a programming method known as *bulk-synchronous programming* [14] wherein the computation is divided into multiple phases, with each phase consisting of a set of independent tasks executed concurrently, therefore, avoiding any race conditions. I.e., the barrier between subsequent phases ensures that all tasks are finished and their updates have reached to the global memory before proceeding to the next phase.

However, if the tasks are dissimilar, this process leads to load imbalance and underutilization of system resources. This is because the threads which have finished their assigned tasks quicker may have long idle time at the barrier, waiting for other threads to catch up. Therefore, bulksynchronous programming is more effective for applications with regular parallelism, in which threads are assigned with roughly the same amount of workloads.

Multi-core processors usually implement barriers via the use of atomic operations. In the simplest implementation, each thread atomically increments a single counter, and then spins until the counter equals to the total number of threads participating in the barrier. Modern GPUs provide hardware barrier instructions that synchronize threads at the level of thread block (using *\_\_\_\_\_syncthreads* in CUDA), which can be utilized to implement software-based global barriers which involves all the kernel's threads.

# 2.1.3 The Locks Challenges

In addition to traditional challenges of lock-based synchronization, concurrency issue can be even more troublesome due to GPU's SIMT execution paradigm. For example, as shown Algorithm 2.1, assume that there are two threads within a warp competing for a spinlock. In this situation, one of them acquires the lock, and waits at the start of critical section for reconvergence, while the other spins forever, leading to deadlock.

```

1. repeat locked = CAS(&lock,0,1)

2. until locked = 0;

3. //critical section ...

4. Lock = 0;

```

Algorithm 2.1. Illustration of deadlock case in GPU.

```

1. done = false;

2. while done == false do

3. if CAS(&lock,0,1) == 0 then

4. //critical section ...

5. lock = 0;

6. Done = true;

```

Algorithm 2.2. Illustration of simple fix to deadlock issue in GPU.

The updated version of Algorithm 2.1 (Algorithm 2.2) a local "boolean" variable is added to fix the issue. This algorithms works well when each thread acquires a single lock, however, when two threads from the same warp attempting to acquire two locks in reverse orders, it leads to livelock. I.e., when a thread incurs locking failure, it releases the lock acquired and retries but since warps execute the same instruction in lockstep fashion, those two threads loop forever. Therefore, due to livelocking issue, fine-grained locking on GPUs is extremely challenging.

## 2.2 Transactional Memory Model

In this section we discuss the basic idea and benefits of using Transactional Memory as opposed to conventional synchronization method by means of locks. Subsequently we discuss the progress guarantee provided by different types of systems underlying the Transactional Memory, and finally we discuss the common steps of transactional execution of a typical STM system.

## 2.2.1 Transactional Memory

Herlihy et al. [15] introduced transactional memory (TM), a new multiprocessor architecture implemented by straightforward extensions to any multiprocessor cache-coherence protocol, which provides an efficient and easy-to-use synchronization technique without using locks. In contrast, conventional mutual exclusion using locks ensures that only one thread at a time can operate within the critical sections, while serializing access to the shared memory locations. TM, on the other hand, can circumvent common problems associated with locks, including priority inversion, which occurs when a lower-priority thread is preempted while holding a lock needed by higher-priority threads; convoying, which occurs when a thread holding a lock is descheduled causing other threads capable of running wait; and difficulty of avoiding deadlock.

TM allows programmers to define transaction as a block of code with read-modify-write operations which atomically updates multiple memory locations. Building on the hardware based TM [15], Shavit et al. [7] proposed a software transactional memory (STM), a software method for supporting flexible programming of transactions; their design, however, has a major practical limitation in its transaction definition which its data set and operations should be known in advance, i.e., it uses static transactions. This limitation was later addressed in the following TM designs, making the transactions dynamic.

The underlying TM system should ensure the transactions, are (1) executed atomically, meaning that either all or none of a transaction's operations are executed, and (2) in isolation, meaning that transactions do not observe un-committed updates of other transactions in (shared) memory. Therefore, the TM system can provide an abstraction which frees the programmer from the complexity and caveats of dealing with low level synchronization primitives. I.e., the TM paradigm greatly simplifies concurrent programming compared to the traditional lock-based techniques, that is, using TM system, the programmer does not need to write code via locks to ensure mutual exclusion.

The TM system automatically executes transactions in parallel for performance, while resolving data-races among concurrently executed transactions. The programmer only need to mark the code block which has to be executed atomically and the TM ensures its correct execution and good performance. With a well-implemented TM system, transactions can approach a performance comparable to that of fine-grained locking. Despite having a diverse

programming syntax, TM code has been shown to be less error-prone than locks [16], while being easier to understand [17]. Moreover, the programmer can compose transactions using TM [15], which further boosts programmer productivity as compared to traditional programming using locks.

Even though a TM system execute transactions concurrently, to execute correctly it should satisfy the *serializability* as its basic correctness criterion. Serializability defines how a set of committed transactions may update the memory system [15], and it is satisfied when transactions appear to execute serially, that is, the steps of one transaction never appear to be interleaved with the steps of other transactions. Hence, The TM system should ensure that the current execution is serializable, that is, equivalent to executing the same set of transactions in a serial order. In a serializable order, every transaction behaves as if it is executed serially one after another. By showing that all transactions committed by a TM system satisfy serializability, atomicity and isolation are also satisfied. Note that serializability only requires the concurrent execution of transactions to have at least one equivalent serial order, that is, it does not restrict which serial order should be matched by the concurrent execution.

## 2.2.2 Progress Guarantees

Conventional lock-based concurrency control methods guarantee data consistency by enforcing mutually exclusive access to critical sections guarded by locks that are exclusively acquired by concurrent threads. Once a lock has been acquired by a thread, other concurrent threads demanding to acquire the same lock are forced into a wait state until the lock is released by the thread owning it. Therefore, the waiting threads may spin, yield, or ask the scheduler to block them, that is, they can't make forward progress until the lock is released. This wait state is the major cause of the various problems including deadlock, priority inversion and convoying.

Similar to the initial STM implementation [7], the proposed non-blocking STMs provide synchronization mechanism to circumvent the problems caused by mutual-exclusion using locks, so the failure of any number of threads could not prevent the remainder of the system from making progress. As a result, non-blocking STMs are not relying on the poor scheduling decisions and performed well in spite of arbitrary thread termination. To support non-blocking property, the non-blocking STMs exclude the use of locks because the locks could be held by

threads and never be released. However, due to the efficiency limitations of the non-blocking STMs, most of the recent STMs are blocking, and hence, lock-based, an approach which has shown better performance in practice, partly due to its design simplicity.

In the non-blocking STMs, threads do not need to wait, e.g. spin, to gain access to a shared memory location in face of contention. That is, the transactions in a non-blocking STM are free from wait state, when run by concurrent threads. Instead of waiting, a thread may either abort and optionally retry later; or abort the conflicting thread. In other words, non-blocking STM permit concurrent reads/writes to the shared memory locations, while guaranteeing consistent updates using atomic primitives such as CAS. As we discuss in the following, the non-blocking STMs can be classified according to the kind of progress guarantee they provide to wait-freedom, lock-freedom and obstruction-freedom.

The strongest progress guarantee is wait-freedom which, while having the poor performance, guarantees a transaction always succeeds in a finite number of its own steps, therefore, eliminates the occurrence of deadlocks as well as starvation. This guarantee is usually only relevant to real-time systems, where predictability is compromised with performance.

A weaker and more practical guarantee is lock-freedom, which guarantees that, given a set of concurrent transactions, at least one transaction makes progress in a finite number of execution time steps of any other transaction. In spite of the name, lock-freedom does not necessarily preclude locks, as long as these can be revoked. Lock-freedom eliminates the occurrence of deadlocks but not starvation. E.g., the original proposal for STM suggested by Shavit et al. [7] was a lock-free STM with no use of locks.

An even weaker guarantee is obstruction-freedom. It guarantees that a transaction will always succeed if it is executed without conflicts with other transactions. This leads to greater simplification and flexibility in the design of non-blocking STMs. This property strong enough to prevent deadlock and priority inversion, but requires separate mechanisms such as exponential back-off to avoid livelock. A contention manager is often required to achieve high throughput and to prevent livelocks. Thus, in practice, obstruction-free STMs seem to be faster than wait-free and lock-free alternatives.

In contrast to the above mentioned progress guarantees the non-blocking STMs provide, the blocking STMs provide no guarantees at all since they use locks. Regardless of the lack of progress guarantees, they allow for a simpler design and, according to Ennals [18], a potentially more efficient implementation. Moreover, (1) the majority of programs incorporating STM use it to improve the performance, (2) in the programming models, it is acceptable for one atomic operation to block other atomic operations of the same or lower priority, and (3) the number of threads in an application can be adaptively be matched to the number of physical processing cores, thus, making it unlikely for a thread's transaction to be blocked by another transaction which its thread has been swapped out. The disadvantage of using a blocking implementation is that it makes the STM much more dependent on the scheduler.

### 2.2.3 Transactional Execution

In this section, we outline the common steps of transactional execution for a typical STM system. We start by giving a formal definition of transaction: A transaction is a sequence of instructions, including reads and writes to memory that either commits, that is, executes to the end atomically, or aborts with no effect. All the speculative writes to memory location performed by a committed transaction become permanent, and hence, visible to the rest of the system, while the speculative writes of an aborted transaction is discarded. The STM system usually needs a version management mechanism to record the speculative writes to ensure a consistent memory view from different threads, along with conflict detection mechanism to detect the dependence violations between different transactions.

Version management can be performed eagerly at the time of memory access, or lazily when the transaction commits. In the eager mechanism, the changes are optimistically applied directly to the memory locations as a transaction makes progress, while logging the old values stored in the memory locations to an undo log which is used to revert the changes in case of abort. Generally, eager version management performs well when conflict detection rate is low, while lazy version management is more effective in high contention workloads [19]. However, in the lazy, rather pessimistic, mechanism, the speculative writes will be logged in transaction-private redo logs until the commit time which is the time that the transaction's speculative writes are stored to memory, whereas the redo log is discarded when the transaction aborts. Similar to version management, conflict detection can be performed either eagerly or lazily. Eager conflict detection detects violation early, thus, is able to lessen redundant work by the threads and make computation and memory resources available for other threads. Besides, with the eager conflict detection, the aborted transaction are allowed to retry early. On the other hand, in the lazy mechanism, the conflict detection is optimistically executed at the commit time, allowing for higher degree of concurrency due to the reduced abort rate. Note that the selection of conflict detection mechanism depends on the chosen version management mechanism. In eager version management, conflicts on writes need to be detected eagerly before any write to the memory locations, whereas the conflicts on reads can be detected either eagerly or lazily.

The data conflicts can be detected by tracking the transactional reads and writes to memory locations recorded by transactions within the (shared) memory, hence, making them visible to other transactions. To do so, most of the STM implementations dedicate a separate (shared) memory space for either one memory location or a group of memory locations (memory stripe) to record the tracking entries which include information such as version number, which is used for invisible reads, ownership (lock) status, current executing thread, operation type (read or write) and old/new value for each memory location accessed. Each transaction also keeps a local copy of such entries for each speculative read or write operation performed.

A STM system can abort transactions either explicitly based on the logic of code, or implicitly due to the conflicts with concurrent transactions. The implicit conflict detection along with resolution, which is the abort followed by retry, mechanisms avoid the deadlocks which naive fine-grained locking implementations suffer from. In practice, STM usually aborts transactions even before a deadlock takes place, typically as soon as the conflict is detected.

In a typical STM system, performing an *abort* operation, generally reverts all the changes made by the transaction, effectively voiding the entire transaction, and subsequently releases the ownership of the acquired memory locations. This is commonly referred to as transaction rollback. While when a transaction completed successfully via the *commit* operation, the changes to memory locations become visible to other threads by releasing the ownership of the acquired memory locations.

15

To maximize the degree of concurrency, STM implementations typically differentiate among reads and writes to memory locations, allowing several transactions to read the same memory location concurrently, as long as no update is performed by any transaction at the same time. This doesn't violate the data consistency as the transactions are only reading from the same location. On the other hand, the conflict occurs when at least one of the transactions writes to the memory location while any other transaction read from the same location.

### 2.3 Overview of GPU STMs

Providing efficient STM support on GPU is challenging due to sheer large number of lightweight threads in GPU as compared to few powerful threads in CPU. Such lightweight threads could experience substantial performance overheads with transaction management tasks such as tracking dependences (version management), detecting dependence violations (conflict detection), locally buffering data before a transaction commits, and re-executing aborted transactions across thousands of GPU threads at runtime.

In the following we briefly highlight some of the major works to design and implement STMs on GPUs and compare their effectiveness with respect to efficiency and scalability.

### 2.3.1 Block Level STM

Cederman et al. [8] have designed and implemented two versions of blocking and nonblocking STMs on GPUs that work with the granularity of one thread-block, thus, avoiding intra warp livelock. However, such granularity limits the proper utilization of system resources. Their non-blocking STM follows the obstruction-free design proposed by Harris et al. [20]. Both STMs perform lazy version management using the redo logs for best performance in applications with high contention, while detecting the conflicts at commit time, i.e., applying lazy conflict detection. They employed linear and exponential back-off functions to recover from transactional conflicts. Below, we first briefly review the design techniques used in the non-blocking STM, using the design outlined by Harris et al., followed by their blocking STM implementation, and then report the performance related comparison among these two STMs.

#### **Non-blocking STM**

Harris et al. [20] argue that helping proposed by Shavit et al. [7] is expensive due to the heavy contention it generates. Therefore, instead of helping mechanism, they proposed a mechanism based on locks stealing with merge (during stealing phase) and redo (during lock release phase) operations as we explain in the following.

At commit time, a transaction attempts to acquire all the locks it requires to get exclusive access to its memory locations. If a transaction has acquired all its locks, but not yet written the new values, other conflicting transaction can steal locks from it, using the new value that is to be written. However, if the transaction has not yet acquired all its locks, the stealer transaction may abort it before attempting to acquire its own locks.

In the stealing phase, the stealer transaction merges the transaction entries from the conflicting transaction, which we refer to it as victim, to its own. However, stale updates may occur during the lock release phase of a victim transaction, where the stealing transaction makes updates to the shared memory locations before the victim transaction does, and then the victim transaction makes its stale updates to those locations, overwriting the most recent updates made by the stealer transaction.

To avoid such stale updates, when the victim transaction discovers a potential risk of stale updates, on detecting a stolen lock, it redoes the updates to the memory locations corresponding to the stolen lock, using the new value for the location stored in stealer's transaction entries, only if the stealer is no longer active. Therefore, the most recent update is always performed to the shared memory locations.

#### **Blocking STM**

In the blocking STM, during the execution of a transaction, for each memory location accessed for read, a check is performed to see whether its lock has been taken by other transaction or not. If the lock is taken, the transaction waits until it the lock is released before transferring its value to its local memory. This check is done once again to make sure the lock is still free, and has not been taken yet, otherwise, the check is repeated until the lock is free again. For writes to the memory locations, however, since the STM uses lazy version management, all

the memory updates are applied locally using the redo log corresponding to the thread performing transaction.

At commit time, the blocking STM transaction needs to ensure that no other thread block has changed any of the memory locations accessed earlier, that is, read and/or written, before it can write back the updates to shared memory. Therefore, each of the accessed memory locations is checked, and if the original value read matches the current value in shared memory, its lock is acquired using a compare-and-swap (CAS) atomic operation. Recall that the CAS operation will only succeed as long as the lock status has not changed in the meantime. Any failure in acquiring the locks, or the lock has already been taken, causes the transaction to abort. Once all locks have been successfully acquired, the updates are written back to the shared memory, followed by releasing the locks. Note that, in case of abort, all the already acquired locks should also be released for functional correctness as well as data consistency.

To evaluate and compare the effectiveness of STMs, Cederman et al. [8] carried out their experiments with 2 different contention levels. In the first version, the threads in test applications perform some local work before executing the transactions, leading to a low contention scenario, while in the second version, the high contention scenario is achieved, by having most of the work performed through transactions.

Overall, based on their reported result, at a low level of contention, the blocking and the nonblocking STMs both scale similarly, that is, when the number of thread-blocks increases, the number of operations per millisecond grows equally. In addition, the average number of aborts per transaction is about the same in both STMs. With higher contention, however, the performance with respect to the number of operations per millisecond is better using the nonblocking STM, and hence, the corresponding test applications display higher level of scalability.

Given different back-off schemes, there were no significant change in performance and abort rate. This could be attributed to the hardware scheduler's behavior and the fact that there is only one transaction per thread-block. Consequently, regardless of limited concurrency level in the STMs proposed by Cederman et al., providing additional progress guarantees, such as obstruction-freeness, appears effective to improve performance, while a blocking STM is simpler to implement.

# 2.3.2 Hierarchical Validation STM

Xu et al. [9] proposed an STM system on GPU which consists of a *hierarchical validation* (HV) technique and an *encounter-time lock-sorting* mechanism with commit-time locking, which we refer to as H*STM*, attempting to address the major challenges of using fine-gained locking on GPU: (1) by ensuring good scalability with respect to the massive multithreading, and (2) by preventing livelocks caused by the SIMT execution paradigm of GPUs. Unlike block level STM we discussed earlier which suffers from limited concurrency, HSTM supports per-thread transactions for each thread within a thread block. Furthermore, the HSTM uses the early conflict detection for reads and late detection for writes, while implementing the lazy version management.

The hierarchical validation technique combines *timestamp-based validation* (TBV) with *value-based validation* (VBV), two commonly used conflict detection strategies. At the cost of a slight increase in memory requirements, and of the potential contention on a shared timestamp counter, performing the TBV significantly reduces the high overhead of using the VBV alone, whereas the VBV is helpful to eliminate false conflicts caused by timestamp-based validation.

The TBV is implemented by associating a timestamp with each group of shared memory locations (memory stripe) to indicate when these location was last modified. A transaction also acquires a timestamp indicating the time, referred to as linearization point, when its effects become visible to the rest of the system. Thus, the comparisons of the order of execution is made possible, providing the HSTM system an opportunity to skip validation when the memory location was last modified before the transaction's linearization point.

In GPU, the back-off mechanism is not ideal to avoid livelocks, because threads within the same warp cannot wait for different delays due to the lockstep execution. To adopt a back-off mechanism specific to GPU, when lock acquisition is required, first, the threads within a warp try to acquire locks in parallel, and then those which failed try to acquire locks again sequentially. Hence, livelocking within a warp is avoided by sequentially locking, which could cause a bottleneck during commit and thus degrade performance. Therefore, in the HSTM, the encounter-time lock-sorting together with commit-time locking is used so that the transactions

can acquire the locks in the same order. Hence, livelock-freedom is ensured, and no backoff mechanism is required. Unfortunately, the HSTM suffers from poor performance and low level of scalability which can be attributed to high overhead of its validation mechanism.

# 2.3.3 Lightweight STM

The inadequate scalability which previous STM implementations exhibit is due to high overheads in their transaction management, especially in conflict detection. To address this problem, Holey et al. [10] proposed a low overhead, lightweight STM *(LSTM)* so that the applications could scale satisfactorily to thousands of threads available in GPU-based systems. Given a program, the LSTM exploits the characteristics of the program to either trade–off conflict detection accuracy with detection overheads or avoid tracking entry updates on reads by making reads invisible to other transactions. Holey et al. showed, with their proposed techniques, programs with varying levels of contention can scale to thousands of threads on GPU.

In order to implement LSTM, Holey et al. [10] suggested two flavors of transactional support exploiting an overall transaction's property calculated for a program: *visibility*. This property can be calculated by dividing the total number of writes followed by reads to the memory locations over the total number of reads. Note than this property can be variable during the runtime of a program. The LSTM uses eager version management along with eager conflict detection on writes or eager/lazy conflict detection on reads, depending on the transaction's visibility, performed during a transaction.

In eager conflict detection, a transaction can abort other transaction while it gets aborted later, therefore, the livelock is not avoidable. For instance, two transactions can keep on aborting each other, leading to a livelock. To avoid livelocks a backoff mechanism is utilized in the LSTM by adding a variable delay before restarting aborted transactions to ensure forward progress. In the following, we briefly discuss both abovementioned transactional supports.

The pessimistic transactional support of LSTM specifically targets the applications that in good portion of their execution time, the same memory locations are read and then written within the same transaction, that is, they own high values for visibility property we discussed earlier. Such support reduces the conflict detection overhead which is possible by tracking the

speculative reads and writes equally, leading to a quite simple, yet low overhead conflict detection mechanism. I.e., in addition to regular read–write conflicts, a conflict can also be detected even if two threads read the same memory location, exploiting the fact that if a transaction in a program reads a location, it will most likely write to the same location. Therefore, the read conflicts are detected eagerly, leading to early release of the computation and memory resources.

Conversely, in programs which do not exhibit such memory access behavior, they will incur high overhead costs due to false conflicts. I.e., given pessimistic transactional support, the performance of LSTM could hurt when a program has higher number of reads than writes within its transactions. This is caused by fewer actual updates to the memory locations, therefore, majority of the conflicts detected are false, leading to low performance.

To implement pessimistic support, the tracking entry for each memory location records which thread has accessed it by using the id of thread wherein a conflict is detected by a single CAS atomic operation.

In second transactional support, which is known as invisible read, the conflicts on reads are optimistically detected/validated in lazy fashion at commit time. I.e.., speculative reads are invisible to other transactions, and because they do not modify the tracking entries, this leads to faster transactional reads. This support suits the programs which during their execution, only small portion of reads to memory locations are followed by writes to the same locations, yielding to higher performance. Recall that both transactional support designs detect conflicts on writes eagerly.

Each tracking entry used for detecting dependence violations in invisible read support is consist of version number and lock status, we refer to the combination as version locks. The version lock can be implemented using an unsigned integer to represent lock status with the lease significant bit and the rest of the bits for version number. Thus, using versioned locks speculative reads remain invisible to other transactions, while writes are still visible. Note that the version number is locally stored in transaction private memory and compared with the shared memory at commit time. Holey et al. evaluated their proposed techniques against the fine-grained locking and two state-of-the-art STMs previously discussed, from the standpoint of overheads and scalability. They also used the benchmarks with varying degree of contention, number of memory operations, and transaction sizes for their experimentations. Their results show that the proposed STM support considerably outperforms the earlier STM works, while achieving performance comparable to fine grained locking. Specially, their techniques perform better than other STM designs which specifically target high–contention workloads, on programs with higher conflict rates.

Overall, when critical sections contribute to small portion of the total execution time, that is, the programs spend significant time executing the native code, both transactional supports show low overhead cost. I.e., if the time spent in transactions is relatively short, the STM overheads can be amortized by non-transactional execution in the program. Moreover, among pessimistic and invisible read transactional supports, pessimistic version performs better under high contention and when same data are read first and then written in the transaction.

Recall that in the STM design of Cederman et al. [8], a transaction executes at a thread block level rather than at a thread level, that is, the threads within a thread block do not fall into race conditions; this assumption, of course, is not practical in order to fully utilize the system multiprocessors as SIMT engines. To have a fair comparison, however, Holey et al. modified this design so that each thread within a thread block can take independent transaction(s). Subsequently, they showed LSTM design scales better as the number of GPU threads increases compared to both STM implementations of Cederman et al. and HSTM.

Lower scalability of both Cederman et al.'s STM and HSTM can be attributed to consistency checks performed on reads, which hinders their performance. In Cederman et al.'s STM the read operation waits until a concurrent write from other transaction to the same location is complete, while HSTM performs incremental validation after each read that involves timestamp checking followed by value–based validation for all reads performed earlier within a transaction. Note that even though these STMs employ lazy version management, but even under high contention the eager mechanisms of LSTM outperforms, which is due to lightweight conflict detection mechanisms.

# 3 TRANSACTIONAL-MEMORY-BASED IMPLEMENTATION OF MINIMUM SPANNING FOREST ALGORITHM ON GPU

Minimum Spanning Tree (MST) is used in many real world applications, e.g., distributed networks [21], VLSI design, and medical imaging [22]. Parallelizing of MST calculation on GPUs exemplifies the challenges of executing irregular applications on these platforms. An MST algorithm on an undirected connected graph finds a minimally weighted subset of the graph edges that connects all the vertices without any cycle. If the graph has several connected components, then it involves calculating the Minimum Spanning Forest (MSF) which constitutes one MST for each connected component.

Among the different proposed algorithms for MSF, the Borouvka's algorithm [3] has the most expressed parallelism. It calculates a subset of the graph edges for each connected subgraph of the forest that spans all the vertices with minimum cost. As illustrated in Algorithm 3.1, for each such subgraph G, all the vertices are initialized as individual components. The algorithm iterates through the components and connects each component to another component with a minimum cost path from the component. The iterative process continues until only one component is left.

```

1. Input: an undirected graph G

2. // each component c<sub>i</sub> initially contains one vertex v<sub>i</sub>

3. T = {c<sub>1</sub>, c<sub>2</sub>, c<sub>3</sub>...c<sub>k</sub>}

4. while (number of components in T) >1 {

5. for each component c<sub>i</sub> in T{ // edge discovery phase

6. S = {};

7. for each Vertex v<sub>j</sub> in c<sub>i</sub> {

8. e = minOutComponentEdge (v<sub>j</sub>);

9. S.add(e);

```

10. }

11. T.add (minEdge(S));

12. } // end of edge discovery phase

13. mergeComponents(T); // merge phase

14. } // end of while loop

15. Output: T is minimum spanning tree of Graph G

Algorithm 3.1. Borouvka's MST algorithm

Over the past few years, there have been several implementations of morph algorithms on GPUs, which are relatively complex and non-scalable. Vineet et al [4] implemented the Borouvka's MST algorithm on GPU, using CUDA primitives such as scan, segmented scan, and split on a recursive formulation of Borouvka's algorithm. However, their approach is not only complicated but also doesn't scale well to larger graphs due to the data restrictions, e.g., by imposing some restrictions on the edge weights and the number of vertices. Though it shows substantial performance gain for some types of graphs, their approach is not applicable to other larger graphs, e.g., for the majority of the randomly generated large graphs in section 3.2 of this chapter.

On the other hand, Nasre et al. [5] implemented the Borouvka's algorithm on GPU, avoiding the synchronization all together. However, they proposed rather complex algorithmic techniques, such as subgraph addition together with multiple phases deviating from the phases of the original algorithm, e.g., it included a phase to break the formation of cycles among components to prevent race conditions. Their approach, however, did not prove to be quite efficient as we show in our experimental result which could be due to the extra work required to avoid synchronization. In section 3.2, we do a further comparison with their work.

Kang et al [23] designed and implemented an STM based Borouvka's algorithm on a multicore CPU system with 64 cores. They concluded that satisfactory performance, compared to the fastest known sequential implementation, can be achieved only if further solutions are available to lower the overhead of transactional memory, e.g., by having a transactional memory at the hardware level. As we will see in the experimental results (section 3.2), their work has some additional limitations for randomly generated large graphs due to restrictions in the number of disconnected components.

In this chapter, we demonstrate an efficient transactional-memory-based design and implementation of the Borouvka's algorithm on GPUs. In the first phase of the Borouvka's algorithm (edge discovery), we extract certain algebraic properties of the computation (e.g. monotonicity) [6] to exploit lock-free synchronizations (i.e., synchronizations using atomic instructions). The edge discovery phase is monotonic due to ever decreasing values produced in finding the MSF edges. However, the second phase of the algorithm (merge phase) lacks such algebraic properties and hence we utilize STM as a synchronization mechanism in this phase.

In addition to STM, we apply different optimization techniques like "warp segmentation" [12] in our implementation to maximize GPU utilization and load balancing, which are found to significantly enhance efficiency and performance.

The rest of this chapter is organized as follows: Section 3.1 elaborates our transactionalmemory-based design and implementation of Borouvka's algorithm on GPUs. The experimental evaluations are discussed in section 3.2. Finally, section 3.3 concludes the chapter with a summary of our work.

# 3.1 Transactional-Memory-based Minimum Spanning Forest

In this section we discuss the design and implementation of a transactional-memory-based MSF algorithm. We partition the Borouvka's algorithm (Algorithm 3.1) into two main phases: edge discovery and merge. In the edge discovery phase, there exists an algebraic property of monotonicity which helps implement lock-free synchronizations using atomic operations. This is further elaborated in the following. In the merge phase, however, there are no such algebraic properties and hence we resort to an STM-based synchronization mechanism to overcome race conditions.

In the edge discovery phase, each vertex in a component initially finds its minimum-weight edge (edge suggestion) to other components. Based on the original Borouvka's algorithm (Algorithm 3.1), the edge suggestions of different vertices in a component are stored in a set from which the least expensive edge is selected. In contrast, in our implementation, all the vertices of a component can write their edge suggestions to a shared location in a lock-free approach. We exploit the disjoint-set data structure to represent the components, wherein each

component C contains a disjoint-subset of vertices; a tree data structure represents such a disjoint-subset with its root vertex as the representative of C. Additionally, the "union" operation merges two subsets into one by attaching the root of the tree associated with one subset into another, and the "find" operation locates the subset's representative of a constituent vertex by traversing its corresponding tree. The representative maintains the shared location. A vertex's edge suggestion is compared with its representative's shared location and if such suggestion is less expensive, then the representative's content is replaced.

Since we are only interested in retaining the least expensive of edge suggestions in each subsequent comparison, the edge weight in a component representative monotonically decreases. As such, the corresponding algebraic property of monotonicity is exploited to discover the least expensive edge suggestion for a component. If an atomic-free approach is used (i.e., without the use of atomic operations like "compare and swap") to handle the critical race in writing to a shared location in a component representative, we are required to repeat the edge discovery phase until there is no further change in the content of any component representative. However, through our experiments we noticed that such atomic-free approach could result in more work due to increased number of iterations in finding the MSF of moderate size graphs. Hence we use atomic "compare and swap" operations in the edge discovery phase because the focus of our work is on large graphs.

In the merge phase, we use the minimum-weight edges, which are discovered and collected in each component representative, to connect their endpoint components (disjoint subsets) via disjoint-set "union" operation. Since components may run into race to join with each other, synchronizing the merge operations is inevitable. We resort to an STM-based synchronization mechanism by implementing a priority-based STM for the merge phase. The STM facilitates a natural mapping of the merge phase to the implementation code, e.g., variable sized transactions are handled seamlessly as opposed to fine-grained synchronization using locks.

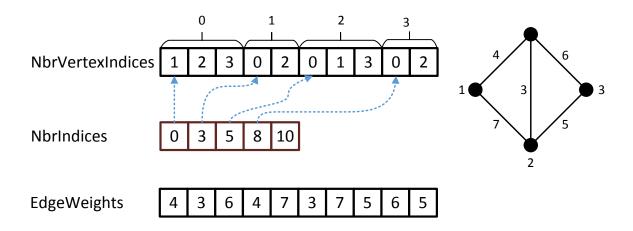

Figure 3.1. A graph with 4 vertices and 5 edges in the CSR format

Two optimization techniques are applied at the end of the merge phase: pruning and flattering. Pruning reduces the workload of the edge discovery phase in the subsequent iterations by eliminating the edges whose endpoints are located in the same component. In flattening, each vertex's parent is updated to point to the root vertex (i.e., the component representative), reducing the cost of disjoin-set "find" operations in future invocations.

To minimize the global memory overhead for the graph representation on the GPU, we use the Compressed Sparse Representation (CSR) format. Figure 3.1 shows the 3 arrays that constitute CSR:

- NbrVertexIndices: stores the adjacency list of graph's vertices.

- NbrIndices: contains the indices of the adjacency set of each vertex in NbrVertexIndices.

- EdgeWeights: holds the weights of the edges corresponding to the vertices in NbrVertexIndices.

In the following subsections, we discuss the edge discovery and merge phases in detail.

# 3.1.1 Edge Discovery Phase

The main task of the edge discovery phase is to determine the minimum-weight edge from each component of the graph connecting it to other components. In each component, it first finds the minimum-weight edge (edge suggestion) for each vertex connecting it to adjacent vertices in other components. This is followed by finding the minimum of these edge suggestions: discovered MST edge. To implement this phase on a GPU, the naive approach is to have each thread in charge of processing one vertex and all its incident edges. However, in CUDA-capable GPUs, a set of 32 contiguous threads of a warp execute in the SIMD fashion. So, due to different number of neighbors of each vertex in the graph, the threads in the warp can have dissimilar workloads, resulting in intra-warp load imbalances and hence performance degradation.

To address the above problem, in our approach we utilize the "warp segmentation" technique [12] in which the adjacency lists of the vertices are grouped in different sized segments. Each warp is assigned to 32 consecutive vertices (we call them warp-assigned vertices) and their adjacency lists, which are copied to the fast shared memory in a warp to maximize the processing speed. However, since these adjacency lists could not fit into the shared memory of a warp, they are streamed into a shared buffer in chunks of 32 neighbors.

Hence, all the threads in the warp collaborate iteratively in processing the neighbors of the warp-assigned vertices, resulting in increased load balance. During each iteration, threads of a warp perform parallel reduction to find the minimum-weight edges incident on the warp-assigned vertices. Upon finding such minimum-weight edge in each vertex (i.e. edge suggestion), it is compared with the current value of the component's representative which monotonically retains the least expensive of such edge suggestions.

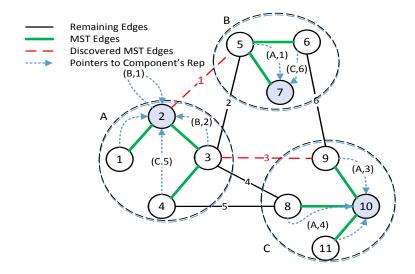

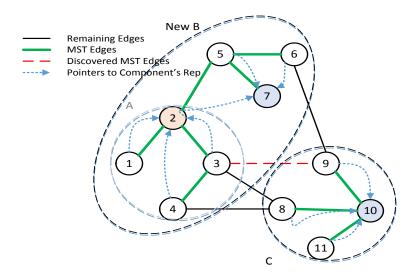

Figure 3.2 shows the result of edge discovery performed on a graph with three components: A, B and C. The figure also shows the MST edges discovered in each component by retaining the least expensive edge suggestions made from the component's vertices. For example, the least expensive edge is selected among all edge suggestions made to component A's representative (i.e. vertex 2), which is illustrated by pointers from vertices 1, 2, 3 and 4 to vertex 2. The final suggestion of component A is the MST edge incident on vertex 2 (in component A) connecting to vertex 5 (in component B).

Algorithm 3.2 illustrates the edge discovery phase. Initially, a shared memory buffer \_Shared\_Suggestions is allocated as a placeholder for all incident edges of each warp-assigned vertex (line 2). The second shared memory buffer is allocated to fetch indices of NbrIndices corresponding to the warp assigned vertices (lines 3-4). Each warp thread determines the region within NbrVertexIndices and EdgedValues arrays that belongs to the 32 assigned vertices (lines

5-6). Finally, the warp threads iterate in a for-loop over all the edges incident on the warpassigned vertices to determine the minimum-weight edges (lines 7-18).

Figure 3.2. Result of edge discovery phase in example graph

```

1. parallel-for warp

{

2. declare Shared Suggestions[blockDim] of Edge;

3. declare Shared NbrIndices[blockDim] of Integer;

4. Shared NbrIndices [warpThreadBlockOffset +laneID]

= NbrIndices [GlobalThreadID];

5. startEdgeIndex // boundary start

= Shared NbrIndices [warpThreadBlockOffset];

6. endEdgeIndex //boundary end

= NbrIndices [warpGlobalOffset + 32];

7. for (edgeIndex = startEdgeIndex + laneID;

edgeIndex < endEdgeIndex; edgeIndex += 32) {</pre>

8.

segment = getWarpSegParams(edgeIndex, endEdgeIndex);

9.

if segment.warp assigned vertex is not active continue;

10.

reduceWithinWarpSeg (edgeIndex, segment);

11.

if segment.inSegId == 0 // first thread in a segment

12.

if segment.warp assigned vertex has no edge suggestion

13.

deactivate(segment.warp assigned vertex);

14.

else {

rootVertex = find ( segment.belongingVertex );

15.

```

16. suggest(rootVertex, segment.belongingVertex);

17. }

18. } // for loop end

19. } // parallel-for warp end

#### Algorithm 3.2. MST edge discovery operation

All the consecutive edges belonging to a warp-assigned vertex form a segment within a warp, wherein the parallel reduction is performed to find the minimum-weight edge. Therefore, during the for-loop iterations, each warp thread first determines which of the 32 warp assigned vertices owns the current edge using a binary search within \_Shared\_NbrIndices; this is followed by detecting the segment size and its index (inSegId) inside the segment (line 8). Having the segment information, the minimum-weight edge is determined by parallel reduction (line 10).

Following the reduction step, the first thread of each segment compares the minimum-weight edge, stored in \_Shared\_Suggestion buffer, with the rootVertex (i.e. representative of the component) of its warp-assigned vertex (lines 15-16). However before such comparison, if the current warp-assigned vertex does not have any edge suggestion left, it will be deactivated (line 13). Eliminating such vertices from the components improves the algorithm efficiency by reducing useless computations in the following edge discovery phases (line 9). In performing the comparison (via suggest function), the suggested weight is compared to the current weight in the root vertex and the minimum of both is retained in global memory through an atomic operation (e.g. "compare and swap"). Subsequent comparisons with each component's vertices monotonically decreases the current suggested weight in each component until the minimum of such weights is found.

# 3.1.2 Merge Phase

In the merge phase, components of the graph are merged together to form larger components using the MST edges discovered in previous phase (edge discovery). For this purpose, each component's representative (root vertex) is queried to get its discovered MST edge, from which the neighbor vertex of the other component can be located. Subsequently, the root vertex of the other component is located using the neighbor vertex. Finally two components are merged into one by selecting one of the root vertices as the root vertex of newly constructed component.

During the merge phase, components may run into critical race to join with each other. To avoid such race conditions, we exploit synchronized transaction to perform merge within the critical section; we call it merge transaction. The merge transaction atomically reads all the vertices involved to locate the root vertex of the other component, followed by updating them to point to the root vertex of the new component. Here, we design and implement a lightweight priority-based STM as a synchronization mechanism for the merge transactions.

Figure 3.3 shows the merge phase following the edge discovery phase for the example graph in Figure 3.2. First, in the race among components A, B and C to merge with each other (A to merge with B, B to merge with A, and C to merge with A), component B successfully proceeds resulting in component new B which is constructed encompassing all the vertices from the previous components A and B. As the result of the merge, vertex 2, previously the root vertex in component A, now points to vertex 7 which is the component new B's root vertex (Figure 3.3(a)).

Later, component C proceeds to merge with the newly created component, new B, which now contains the vertex 3, previously a member of component A. The vertex 3 is the neighbor vertex located using the discovered MST edge for component C. The thread processing the root vertex 10 of component C starts a new transaction which first locates the root vertex (vertex 7) of vertex 3 and then updates vertex 7, previously the root vertex of component B, to point to component C's root vertex (vertex 10). Finally, within the same transaction, vertices 3 and 2 are updated to point to vertex 10, which is the component new C's root vertex.

To support STM based transactions, we include an unsigned integer as a tracking entry in each vertex of the graph. The most significant bit of the tracking entry indicates the lock status and the remaining bits are used for the priority of the thread performing a transaction. We define threadID value as the priority for a thread where the highest value indicates the lowest priority. Each thread allocates a local array of vertices to keep track of all the vertices participating in an STM transaction. The size of the local array is a constant L, i.e., the longest transaction size. A transaction of size greater than L aborts and restarts until its size is lowered as the side effect of merging of other components.

Figure 3.3(a). Merging component B with A to create new B

Figure 3.3(b). Merging component C with new B

Figure 3.3. Merge in example graph following the edge discovery phase