#### A Study of Novel Fabrication Techniques for Development of 3-D Silicon Nanostructure Array

Bahareh Yaghootkar

A Thesis

In the Department

of

Electrical and Computer Engineering

Presented in partial fulfillment of the degree requirements

For the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

August 2014

© Bahareh Yaghootkar, 2014

# CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

| Ву:           | Bahareh Yaghootkar                                                     |                              |                      |

|---------------|------------------------------------------------------------------------|------------------------------|----------------------|

| Entitled:     | A Study of Novel Fabrication Techniques for Development of 3-D Silicon |                              |                      |

|               | Nano-structure Array                                                   |                              |                      |

|               |                                                                        |                              |                      |

| and submitted | in partial fulfillment of the                                          | he requirements for the deg  | gree of              |

|               | DOCTOR OF PHILO                                                        | DSOPHY (Electrical and Com   | puter Engineering)   |

|               | the regulations of the Ur<br>inality and quality.                      | niversity and meets the acce | epted standards with |

| Signed by the | final examining committe                                               | e:                           |                      |

|               | Dr. R. Sedaghati                                                       |                              | Chair                |

|               | Dr. Z. Mi                                                              |                              | External Examiner    |

|               | Dr. Y. Zeng                                                            |                              | External to Program  |

|               | Dr. M. Z. Kabir                                                        |                              | Examiner             |

|               | Dr. I. Stateikina                                                      |                              | Examiner             |

|               | Dr. M. Kahrizi                                                         |                              | Thesis Supervisor    |

| Approved by   |                                                                        |                              |                      |

|               |                                                                        |                              | _                    |

|               | Chair of Department or 0                                               | Graduate Program Director    | •                    |

|               | - <u> </u>                                                             |                              |                      |

|               | De                                                                     | ean of Faculty               |                      |

#### **ABSTRACT**

#### A Study of Novel Fabrication Techniques for Development of 3-D Silicon Nanostructure Array

#### Bahareh Yaghootkar, PhD

#### Concordia University, 2014

The large surface area and high aspect ratio of nano-structures make them promising candidates as a fundamental building block for manufacturing various devices. The potential applications of silicon nano-structure array include, but are not limited to, electron emitters, sensors, solar cells, rechargeable batteries, and hydrogen storage devices. With advances in nanotechnology, various techniques have been reported for synthesis and fabrication of nano-structures. However, these techniques like chemical vapor deposition and vapor liquid solid suffer from the need of very sophisticated and high cost equipment. Furthermore, the need of high operating temperature, high vacuum, and catalyst material such as gold are major challenges of these techniques. On the other hand some fabrication techniques such as top-down approaches involve complicated fabrication steps that ultimately increase the cost of the device.

Therefore, a rising impetus has been devoted to development of less complicated and low-cost fabrication techniques of silicon nano-structure.

The goal of this thesis was to introduce novel and cost-effective fabrication methods which also maintain the benefits of CMOS compatibility. Two non-lithography top-down approaches were introduced for fabrication of silicon nano-structures array with capability of controlling the structure characteristics.

The first fabrication approach consists of three steps: 1) patterning of silicon surface in TMAH using anisotropic etching technique, 2) formation of porous layer on patterned silicon surface using electrochemical anodic etching, and 3) treatment of porous silicon layer using an alkaline etching to reveal the silicon nano-structure array.

The second fabrication approach consisted of two steps, namely: Anisotropic etching followed by electrochemical etching. The main idea behind this approach was that unlike

the first approach the electrochemical etching is performed in transition regime not porous silicon formation regime.

These techniques allowed for the controlling the characteristics and morphology of silicon nano-structures.

Completely different morphologies of nanostructures were achieved as a result of transforming the electrochemical process from porous silicon formation to transition regime.

A study on effect of type of dopant, p- and n-type, on over-mentioned fabrication methods was also investigated.

To my Family

#### Acknowledgments

I would like to express my deep gratitude to my supervisor Prof. Mojtaba Kahrizi for providing me with opportunity to join to his research lab. I would not be able to finish my studies without his constant support and guidance. I would also like to acknowledge that this work was funded by NSERC, and faculty of Engineering and Computer Science at Concordia University.

I would like to thank my thesis committee members for their time and critical assessment of this work.

I would like to express my great appreciation to my parents, Sorayya and Neamat, whom I owe my life. A simple thank is insufficient for my dear family, without whom my studies and educational journey would not have been possible.

#### **Table of Contents**

| List of Fig | ures                                                          | X             |

|-------------|---------------------------------------------------------------|---------------|

| List of Tal | bles                                                          | xiii          |

| List of Acı | ronyms                                                        | xiv           |

| List of Syr | mbols                                                         | xvi           |

| 1. Introd   | luction                                                       | 1             |

| 1.1         | A brief history of nanotechnology                             | 2             |

| 1.2         | Motivation                                                    | 4             |

| 1.3         | Objectives                                                    | 7             |

| 1.4         | Overview of this thesis                                       | 8             |

| 2. Overv    | view of silicon chemical/ electrochemical etching             | 10            |

| 2.1         | The Etching of silicon                                        | 11            |

| 2.2         | The anisotropic wet-chemical dissolution of silicon           | 12            |

| 2.3         | Electrochemical anodic dissolution                            | 15            |

| 2.4         | IV Characteristics                                            | 17            |

| 2.5         | Etching mechanism                                             | 17            |

| 2.6         | Porous silicon formation                                      | 20            |

| 2.6.1       | Area-selective etching of porous silicon                      | 22            |

| 2.6.2       | Application of porous silicon layer                           | 23            |

| 3. Fabric   | cation of vertical nano-structure array on silicon wafer: Ele | ectrochemical |

| etchi       | ng at porous formation regime                                 | 28            |

| 3.1         | Introduction                                                  | 29            |

| 3.2         | Experimental procedure and setup                              | 30            |

| 3.3         | The fabrication process flow                                  | 33            |

| 3 3 1       | Fabrication of the pyramids (1 <sup>st</sup> stage)           | 33            |

| 3.3.2    | Creation of porous silicon (2 <sup>nd</sup> stage)                                       | 33    |

|----------|------------------------------------------------------------------------------------------|-------|

| 3.3.3    | The creation of silicon nano-structure array (3 <sup>rd</sup> stage)                     | 34    |

| 3.4      | Results and discussion                                                                   | 34    |

| 3.4.1    | Characterization of the textured silicon surface                                         | 34    |

| 3.4.2    | Characterization of the porous silicon layer created at 2 <sup>nd</sup> stage            | 36    |

| 3.4      | .2.1 Pores initiation and growth mechanism                                               | 36    |

|          | .2.2 Porous formation under various anodic etching conditions with a stant charge passed | 38    |

| 3.4.3    | Characterization and analysis of the nano-structure array created at 3 <sup>rd</sup>     | _     |

| 3.4      | .3.1 Effect of anodic etching conditions with constant Q                                 | 40    |

| 3.4      | .3.2 Effect of anodic etching condition at various Q values                              | 41    |

| 3.4      | .3.3 Effect of pyramid surface coverage                                                  | 43    |

| 3.4.4    | The Morphology of the nano-structure                                                     | 48    |

| 3.5      | Conclusions                                                                              | 51    |

| 4. Fabri | cation of vertical nano-structure array on silicon wafer: Electrochen                    | nical |

| etchi    | ing at transition regime                                                                 | 53    |

| 4.1      | Introduction                                                                             | 54    |

| 4.2      | Experimental Procedure                                                                   | 55    |

| 4.2.1    | Fabrication of the pyramids (1 <sup>st</sup> stage)                                      | 55    |

| 4.2.2    | Development of silicon nano-structure (2 <sup>nd</sup> stage)                            | 55    |

| 4.3      | Results and Discussion                                                                   | 56    |

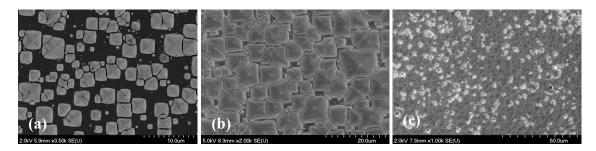

| 4.3.1    | Characterization of the textured silicon surface (1 <sup>st</sup> stage)                 | 56    |

| 4.3.2    | The creation of silicon nano-structure arrays (2 <sup>nd</sup> stage)                    | 58    |

| 4.3.3    | Effect of pyramid size uniformity on formation of the silicon nano-                      |       |

|          | structures                                                                               | 62    |

| 4.3.4     | Effect of HF concentration on the formation of nano-structure arrays 64 |    |

|-----------|-------------------------------------------------------------------------|----|

| 4.3.5     | The Morphology of the nano-structure                                    | 66 |

| 4.4       | Conclusions                                                             | 69 |

| 5. Fabric | cation of n-type silicon nano-structure: Light-induced electro-chemic   | al |

| etchi     | ng                                                                      | 71 |

| 5.1       | Introduction                                                            | 72 |

| 5.2       | Experimental procedure                                                  | 73 |

| 5.2.1     | Textured surface preparation                                            | 73 |

| 5.2.2     | Porous layer preparation                                                | 73 |

| 5.3       | Results and discussion                                                  | 74 |

| 5.3.1     | Characterization of textured silicon surface                            | 74 |

| 5.3.2     | Pores initiation comparison for p- and n-type samples                   | 75 |

| 5.3.3     | Development of macro-pore arrays                                        | 77 |

| 5.3.4     | Macro-pore array as building blocks for formation of nano-structure     | 82 |

| 5.4       | Conclusions                                                             | 84 |

| 6. Concl  | usions, contributions and suggestions for further research              | 86 |

| 6.1       | Contributions                                                           | 88 |

| 6.2       | Future work                                                             | 89 |

## **List of Figures**

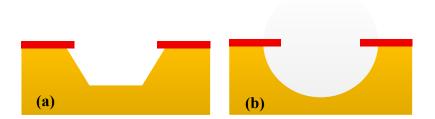

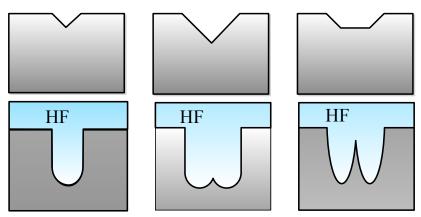

| Figure 2.1  | Schematic representation of a cross-section of a silicon etched a) anisotropic b) isotropic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

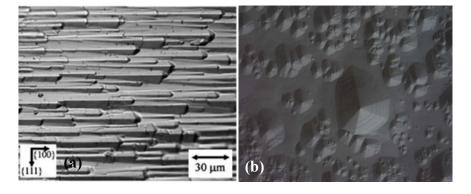

| Figure 2.2  | (a) Zigzag pattern on Si (110) [47]. (b) Formation of deep pits on (111) due                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | to dislocations. Experimental image from Sato Laboratory, Nagoya                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | University [48]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

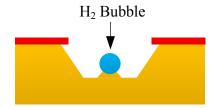

|             | Natural etching mask caused by hydrogen bubbles [53]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

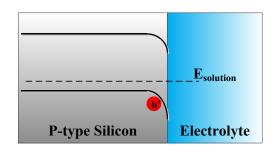

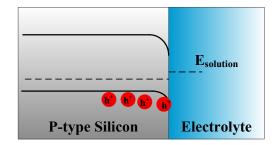

| Figure 2.4  | Charge transport processes at the semiconductor/electrolyte interface for a p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | type silicon. The increase in hole current across the interface under forward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | bias (silicon positive relative to the Pt counter - electrode in solution) is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 2.5  | depicted [63]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

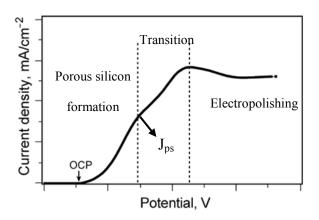

| riguit 2.3  | porous silicon formation, transition and electropolishing [67]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

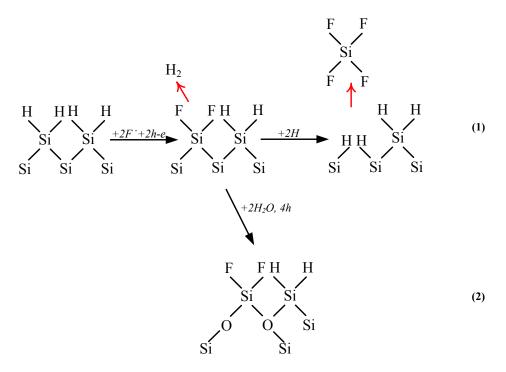

| Figure 2.6  | Possible reaction paths for the electrochemical reaction in HF solution 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

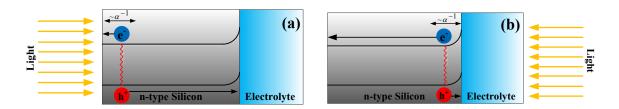

| _           | Diagram illustrates the depth where the hole-electron pairs are generated and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1184114 -47 | the distance hole carriers have to travel to reach the silicon/electrolyte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | interface. (a) back-side illumination, (b) front-side illumination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

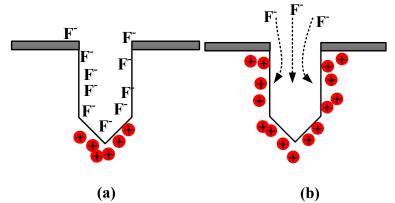

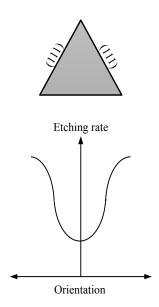

| Figure 2.8  | 3 Schematic illustrates the effect of shape and dimension of the tips on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | electrochemical etching of silicon [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

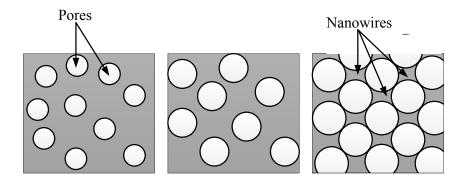

| Figure 2.9  | Idealized plan view of porous silicon layer with different porosities [22] 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

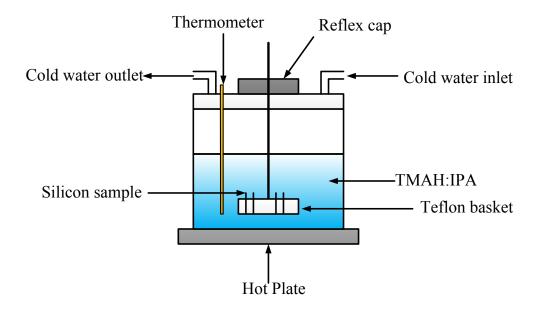

| _           | Schematic view of wet chemical anisotopic etching apparatus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

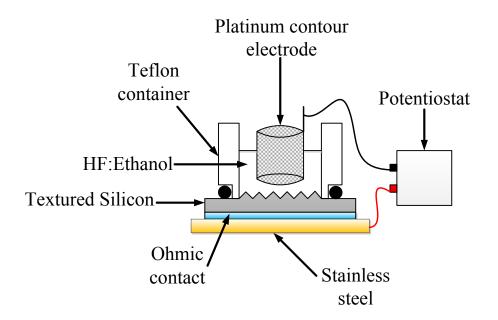

| Figure 3.2  | Schematic of a two - electrode electrochemical cell used to make porous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | silicon. Silicon is the working electrode. The counter - electrode is platinum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

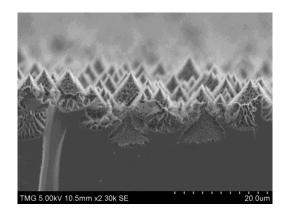

| E. 22       | 32 (A) To a definition of the second of the |

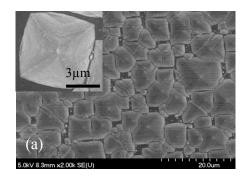

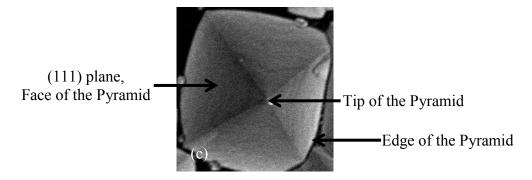

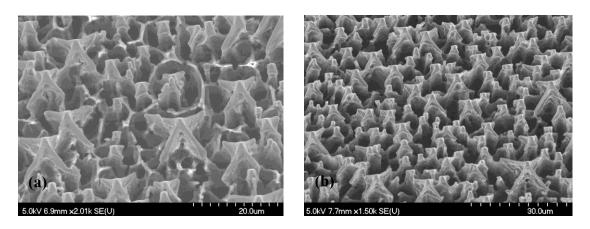

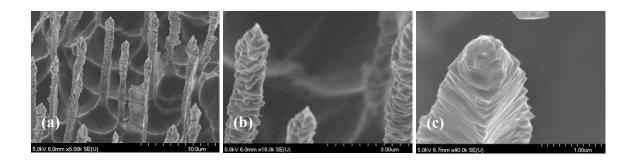

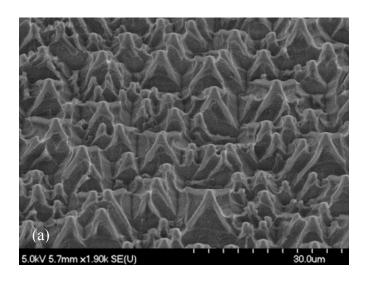

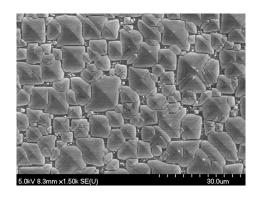

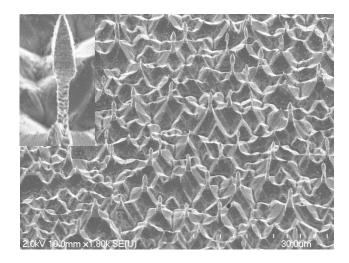

| Figure 3.3  | (a) Textured silicon surface, (b) image analysis of the textured silicon surface,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | (c) an enlarge view of the pyramid structure, the tip, edge and face pf the pyramid are indicated using arrows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

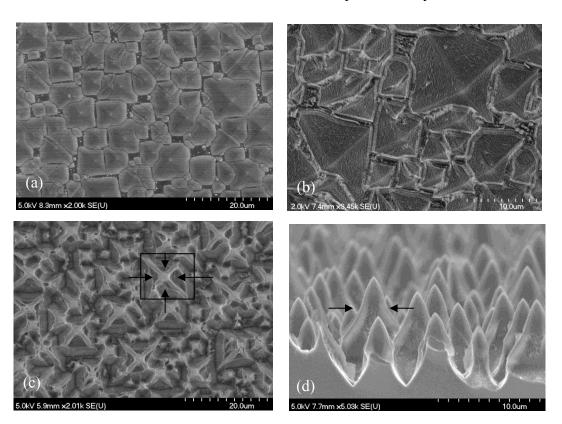

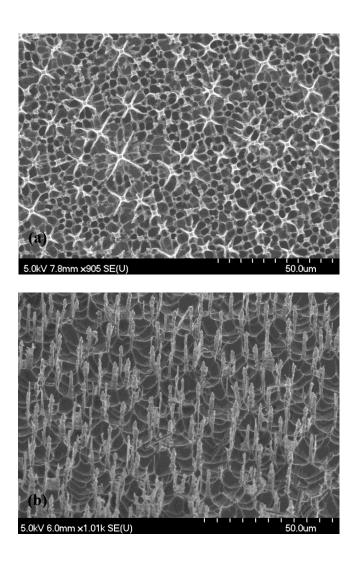

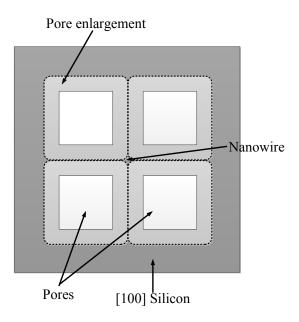

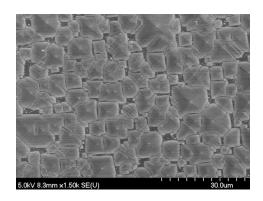

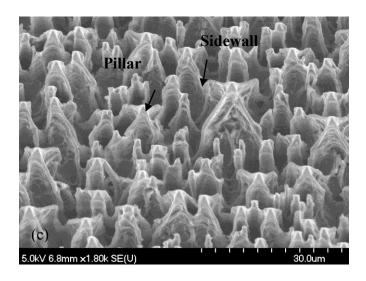

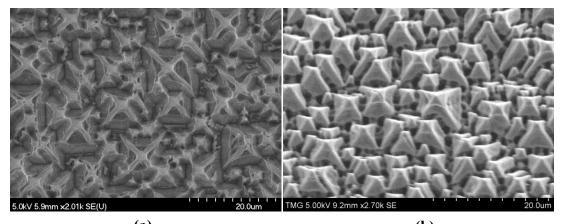

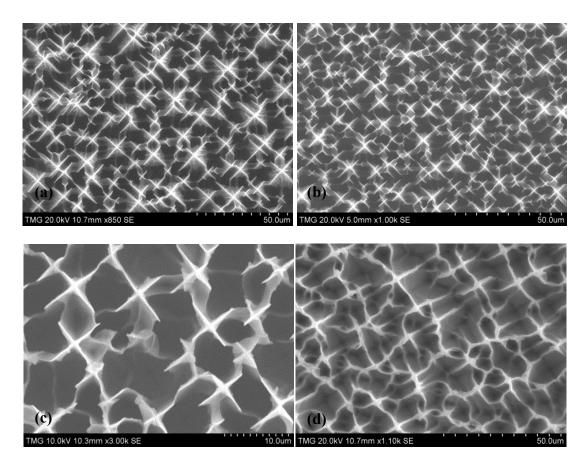

| Figure 3.4  | The top view of start and progression of the porous layer, (a) textured surface,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rigure 5.1  | (b) after 1 minute anodic etching time, (c) after 3 minute anodic etching time,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | (d) cross section view of the structures (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

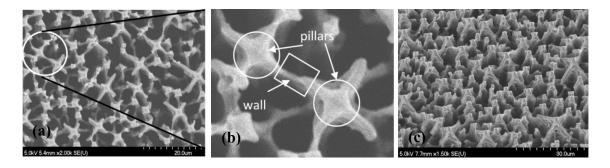

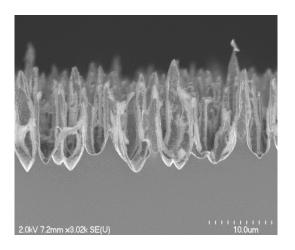

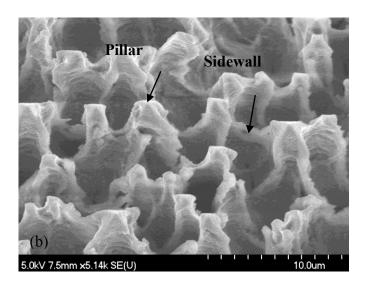

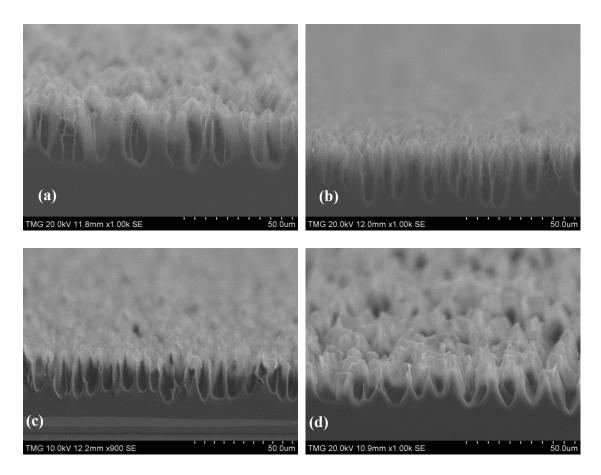

| Figure 3.5  | (a) The top view of silicon porous layer after 30 min, (b) enlarged image of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C .         | circled area, and (c) 45 degree tilted view of the image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

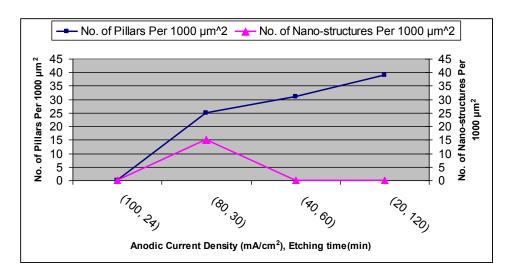

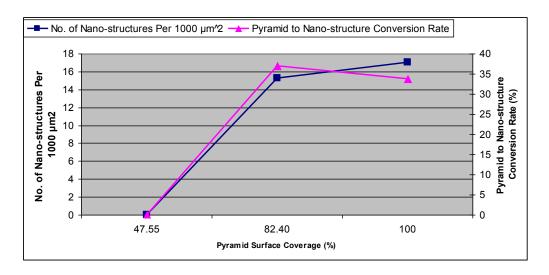

| Figure 3.6  | Number of pillars per 1000 $\mu$ m <sup>2</sup> and number of nano-structures per 1000 $\mu$ m <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | at various anodic etching conditions. 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

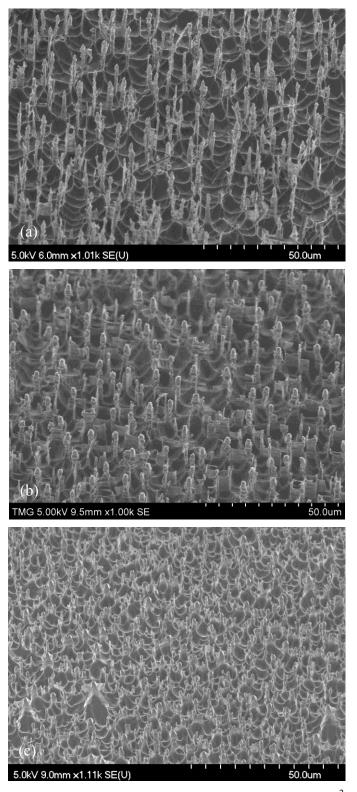

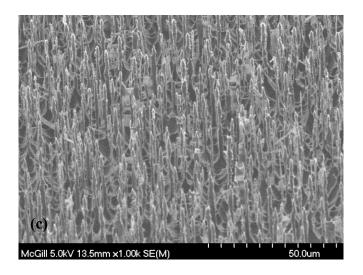

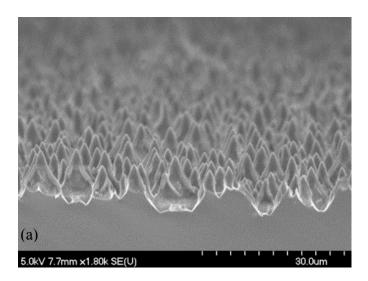

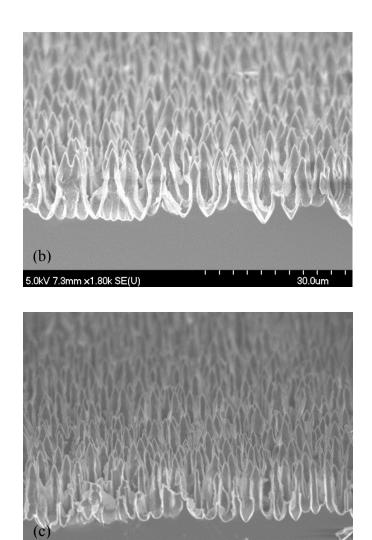

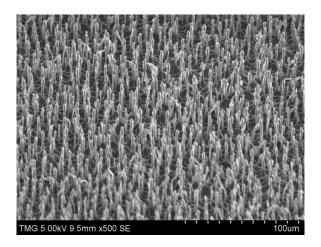

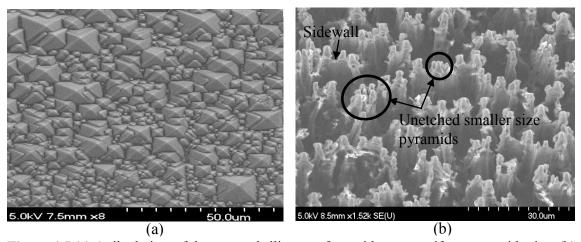

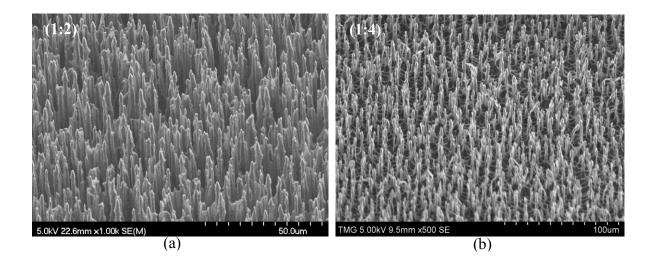

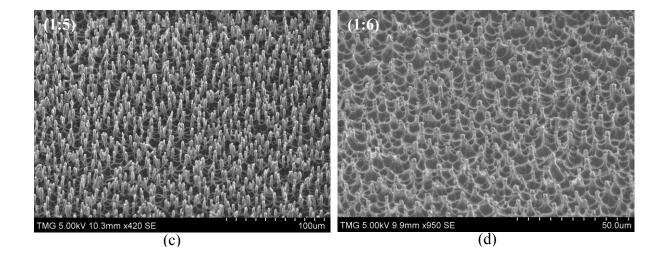

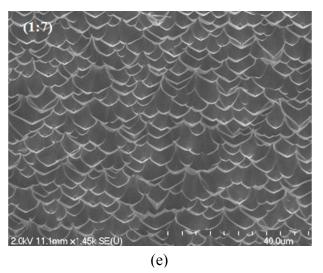

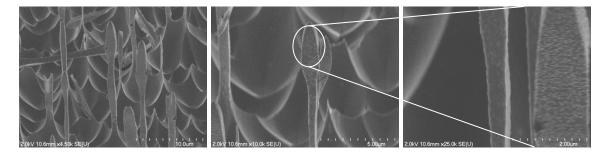

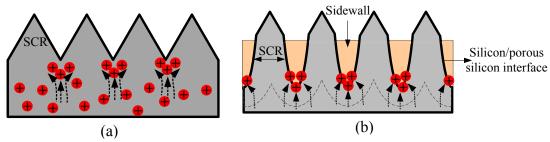

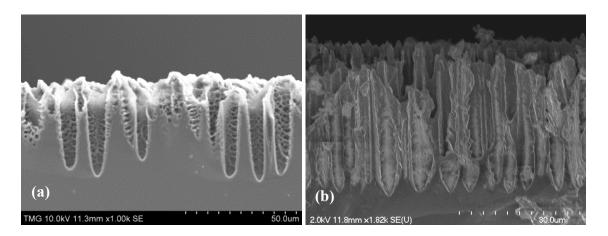

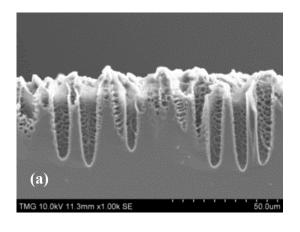

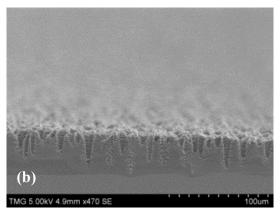

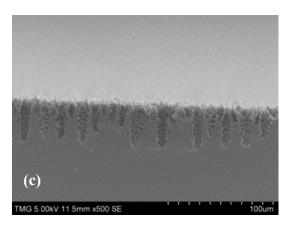

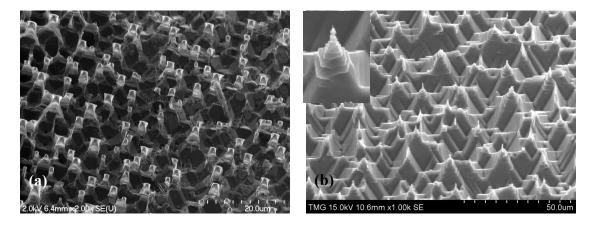

| Figure 3.7  | The nano-structure array fabricated under constant 80 mA/cm <sup>2</sup> and various                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |