# A LABVIEW BASED POWER CONVERTER DESIGN FOR TIME DOMAIN ELECTROMAGNETIC SYSTEM

#### HARJOT SINGH SAINI

A Thesis

in

The Department

Of

**Electrical & Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science

(Electrical & Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

February 2014

© HARJOT SINGH SAINI, 2014

# CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

| This is to           | certify that the thesis prepared                                           |                                |

|----------------------|----------------------------------------------------------------------------|--------------------------------|

| Ву:                  | Harjot Singh Saini                                                         |                                |

| Entitled:<br>system" | "A LabVIEW based power converter design for                                | time domain electromagnetion   |

| and subn             | nitted in partial fulfillment of the requirements fo                       | or the degree of               |

|                      | Master of Applied Science                                                  |                                |

|                      | with the regulations of this University and mee o originality and quality. | ts the accepted standards with |

| Signed by            | the final examining committee:                                             |                                |

|                      |                                                                            |                                |

|                      |                                                                            | _ Chair                        |

|                      | Dr. M. Z. Kabir                                                            |                                |

|                      |                                                                            | _ Examiner, External           |

|                      | Dr. L. Wang (BCEE)                                                         |                                |

|                      |                                                                            | _ Examiner                     |

|                      | Dr. S. Williamson                                                          |                                |

|                      |                                                                            | _ Supervisor                   |

|                      | Dr. L. A. Lopes                                                            |                                |

| Approved             | d by:                                                                      |                                |

|                      | Dr. W. E. Lynch, Chair                                                     |                                |

|                      | Department of Electrical and Computer En                                   | ngineering                     |

|                      | 20                                                                         |                                |

|                      |                                                                            | Christophor Truoman            |

Dr. Christopher Trueman

Interim Dean, Faculty of Engineering and

Computer Science

### **ABSTRACT**

# A LabVIEW based Power Converter design for Time Domain Electromagnetic System

### **Harjot Singh Saini**

In geophysical survey industry, helicopter time domain electromagnetic systems (HTEM) are used widely due to their better spatial resolution and ability to conduct surveys in difficult geographical areas. However, these systems are limited in terms of the exploration depths achieved due to the constraints on the overall weight of the system that a helicopter can safely tow. There is a scope to develop a compact yet high power system that is light in weight, fast in response and able to control high current pulses to achieve deeper exploration depths. In this thesis, a new LabVIEW based power converter is proposed and implemented to achieve *flexible and faster* control of the TEM system. The current control is implemented with hysteresis current control logic and a constant ON-Time current control logic. Proposed topology and current control helps to achieve the targeted fall-time (100 µs) at the end of current pulse. An optimized LabVIEW code and constant ON-Time current control scheme is implemented to achieve sampling times as low as 2 µs. The comparison of experimental results with MATLAB simulation results validates the effectiveness of the control scheme. To reduce the switching power loss in the converter, the same hard switching power converter, working with constant ON-Time current control is modified to simulate a zero current switching scheme by designing the required resonant elements.

# **ACKNOWLEDGEMENTS**

First and foremost I would like to express my sincere gratitude to Dr. Luiz A.C. Lopes for his invaluable guidance, ideas and motivation in my thesis work and his amazing lectures in Power Electronics which have inspired me to continue my graduate studies in this area of expertise. His humble attitude and helpful nature made my first steps in academic research a fulfilling and exciting experience.

I would also like to thank Dr. Jose Martinez, a great human being and a true friend, for his unconditional support and guidance in my research work. I deeply appreciate the way he made my work at GDS a fun filled learning experience.

I would like to express my warm feelings of gratitude to Dr. Pragasen Pillay and Dr. Sheldon Williamson for their time to time support and encouragement.

I am extremely grateful to my friends at Power Electronics and Energy Research (PEER) Group at the P. D. Ziogas Laboratory for their support .I really enjoyed time to time idea exchanges through technical discussions.

I am thankful to NSERC, Canada and Power Corporation of Canada in supporting my studies through monetary funding.

Last but not the least thanks to the almighty God for always bestowing me with the company of best people, in the form of family and friends who inspired my journey till date.

| Dedicated to my parents Sardar Mohinder Singh and Sardarn |

|-----------------------------------------------------------|

|                                                           |

| Surinder Kaur                                             |

# **TABLE OF CONTENTS**

| LIST OF | FIGURES                                                 | viii    |

|---------|---------------------------------------------------------|---------|

| LIST OF | TABLES                                                  | xi      |

| LIST OF | ACRONYMS                                                | xii     |

| LIST OF | PRINCIPAL SYMBOLS                                       | xiii    |

| CHAPTE  | R 1. INTRODUCTION                                       | 1       |

| 1.1     | AIRBORNE ELECTROMAGNETIC SYSTEMS                        | 1       |

| 1.2     | TEM SYSTEM AND PRINCIPLE                                | 3       |

| 1.3     | THESIS OBJECTIVE AND CHALLENGES                         | 6       |

| 1.4     | THESIS CONTRIBUTIONS                                    | 6       |

| 1.5     | THESIS OUTLINE                                          | 7       |

| CHAPTE  | R 2. REVIEW OF POWER CONVERTER TOPOLOGIES IN AEM SYSTEM | MS9     |

| 2.1     | INTRODUCTION                                            | 9       |

| 2.2     | SELECTION OF CURRENT WAVEFORM                           | 9       |

| 2.3     | PRESENT CURRENT CONTROL TOPOLOGIES                      | 10      |

| 2.4     | CONCLUSION                                              | 14      |

| CHAPTE  | R 3. THE PROPOSED POWER CONVERTER – DESIGN AND SIMULAT  | TIONS15 |

| 3.1     | INTRODUCTION                                            | 15      |

| 3.2     | IMPORTANT CONSIDERATIONS                                | 15      |

| 3.3     | PROPOSED CONVERTER TOPOLOGY                             | 17      |

| 3.3     | 3.1 MODES OF OPERATION (HARD SWITCHING)                 | 17      |

| 3.3     | 3.2 CURRENT GOVERNING EQUATIONS                         | 20      |

| 3.3     | 3.3 SELECTION OF DC LINK CAPACITOR                      | 22      |

| 3.3     | 3.4 SELECTION OF DC POWER SOURCE                        | 23      |

| 3.3     | 3.5 SELECTION OF IGBTS                                  | 24      |

| 3.3     | 3.6 SIMULATION RESULTS                                  | 25      |

| 3.4     | CONSTANT ON - TIME CURRENT CONTROL SCHEME               | 28      |

| 3.5     | DESIGN OF SNUBBER CIRCUIT                               | 34      |

| 3.5     | 5.1 ADVANTAGES OF RCD SNUBBER                           | 34      |

| 3.5     | 5.2 CALCULATION OF SNUBBER CAPACITANCE                  | 35      |

| 3.5     | 5.3 CALCULATION OF SNUBBER RESISTOR                     | 36      |

| 3.6     | CONCLUSION                                              | 37      |

| CHAPTE  | R 4. HARDWARE IMPLEMENTATION AND EXPERIMENTAL RESULTS   | S39     |

| 4.1     | INTRODUCTION                                            | 39      |

| 4.2     | INTRODUCTION TO LABVIEW                                 | 39      |

| 4.3     | INTRODUCTION TO FPGA                                    | 40      |

| 4          | .4         | COM      | PACTRIO SYSTEM ARCHITECTURE                        | 40   |

|------------|------------|----------|----------------------------------------------------|------|

|            | 4.4.1      | =        | REAL TIME CONTROLLER (NI CRIO 9014):               | 41   |

|            | 4.4.2      | <u> </u> | RECONFIGURABLE FPGA CHASSIS (NI CRIO 9111 -4 SLOT) | 42   |

|            | 4.4.3      | }        | ANALOG INPUT MODULE (NI 9222)                      | 43   |

|            | 4.4.4      | ļ.       | DIGITAL OUTPUT MODULE (NI 9474)                    | 43   |

|            | 4.4.5      | ;        | CONTROLLER POWER SUPPLY (NI PS –15 POWER SUPPLY)   | 44   |

|            | 4.4.6      | j        | COMPACTRIO SYSTEM BLOCK DIAGRAM                    | 45   |

| 4          | .5         | PRO      | GRAMMING LOGIC IN LABVIEW                          | 47   |

|            | 4.5.1      | -        | GUI.VI                                             | 48   |

|            | 4.5.2      | <u> </u> | FPGA.VI (FPGA TARGET)                              | 53   |

| 4          | .6         | COD      | E OPTIMIZATION                                     | 58   |

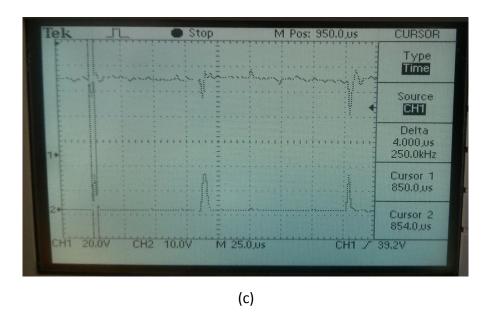

| 4          | .7         | SWIT     | CH TURN-OFF DELAY                                  | 63   |

| 4          | .8         | EXPE     | RIMENTAL RESULTS                                   | 71   |

| 4          | .9         | COM      | PARISON BETWEEN SIMAULTION AND TEST RESULTS        | 77   |

| 4          | .10        | CON      | CLUSION                                            | 79   |

| CHA        | APTER !    | 5. ZEF   | O CURRENT SWITCHING CONVERTER DESIGN               | 80   |

| 5          | .1         | INTR     | ODUCTION                                           | 80   |

| 5          | .2         | NEE      | FOR SOFT SWITCHING                                 | 80   |

| 5          | .3         | SELE     | CTION BETWEEN ZCS AND ZVS                          | 81   |

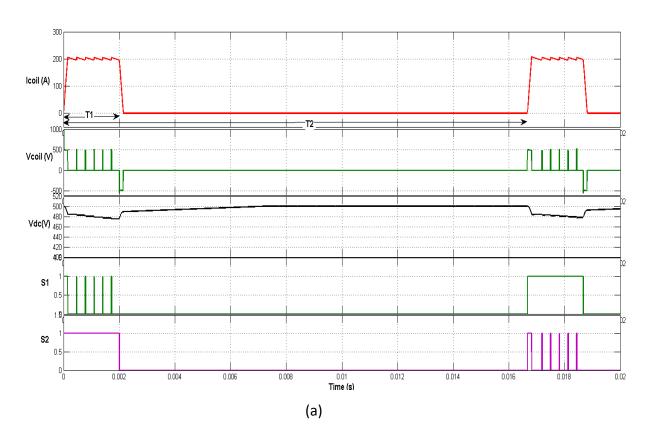

| 5          | .4         | ZCS S    | SOFT SWITCHING CONVERTER TOPOLOGY                  | 82   |

|            | 5.4.1      | -        | MODES OF OPERATION (SOFT SWITCHING)                | 82   |

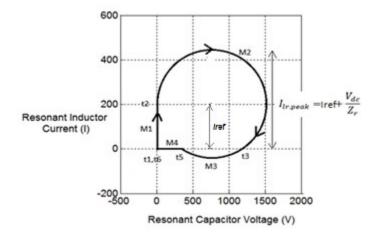

|            | 5.4.2      | <u> </u> | STATE PLANE TRAJECTORY AND DESIGN CRITERIA FOR ZCS | 86   |

|            | 5.4.3      | 3        | DESIGN CALCULATIONS                                | 89   |

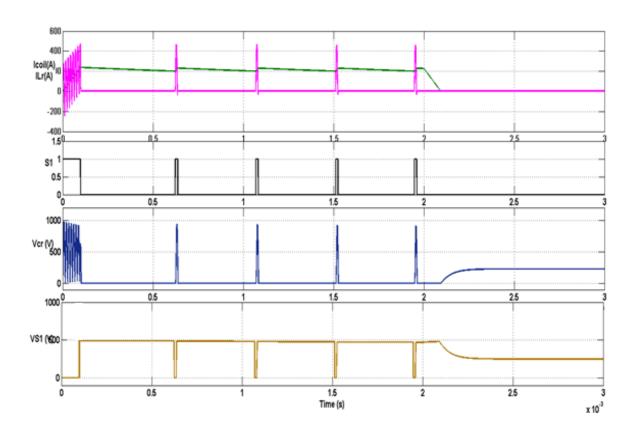

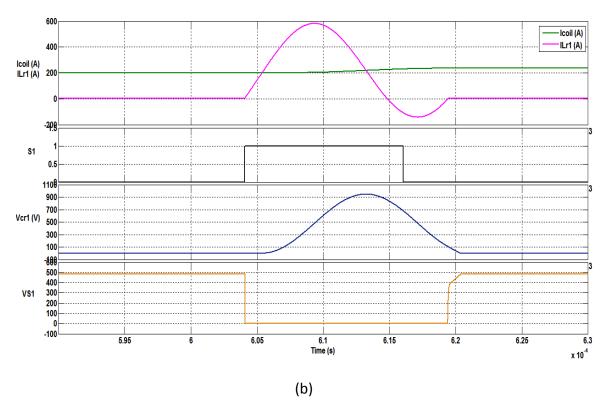

|            | 5.4.4      | ļ        | SIMULATION RESULTS                                 | 91   |

| 5          | .5         | CON      | CLUSION                                            | 93   |

| CHA        | APTER      | 6. CO    | NCLUSION AND FUTURE WORK                           | 94   |

| 6          | 5.1        | SUM      | MARY                                               | 94   |

| $\epsilon$ | 5.2        | SUG      | GESTED FUTURE WORK                                 | 95   |

| REF        | ERENC      | ES       |                                                    | 97   |

| APF        | ENDIX      |          |                                                    | .101 |

| A          | <b>\-1</b> | CALC     | CULATION OF TURN ON AND TURN OFF GATE RESISTORS    | .101 |

| ,          | 2          | DOM      | IER LOSS CALCULATION                               | 102  |

# **LIST OF FIGURES**

| Fig. 1.1 Fixed Wing TEM System <sup>1</sup>                                                         | 2      |

|-----------------------------------------------------------------------------------------------------|--------|

| Fig. 1.2 Helicopter Time Domain Electromagnetic (HTEM) system <sup>2</sup>                          | 2      |

| Fig. 1.3 TEM Principle [4]                                                                          | 4      |

| Fig. 1.4 TEM Waveforms                                                                              | 5      |

| Fig. 2.1 TEM Converter Topology using two energy storage elements [7]                               | 10     |

| Fig. 2.2 Load Current and capacitor voltage waveforms [7]                                           | 10     |

| Fig. 2.3 Converter Topologies for fast current reversal (a) unclamped topology (b) clamped Topology | [8] 12 |

| Fig. 2.4 Voltage and current waveforms- Unclamped Topology [8]                                      | 13     |

| Fig. 3.1 Proposed Topology & Modes of Operation (Hard Switching)                                    | 19     |

| Fig. 3.2 Simulation waveforms with hysteresis current control                                       | 28     |

| Fig. 3.3 Flow Chart for Constant ON Time Current Control                                            | 30     |

| Fig. 3.4 Simulation waveforms with Constant ON –Time                                                | 33     |

| Fig. 3.5 Converter circuit with RCD snubber                                                         | 35     |

| Fig. 4.1 NI cRIO-9014 RT controller                                                                 | 42     |

| Fig. 4.2 NI cRIO-9111 four –slot, reconfigurable embedded chassis                                   | 43     |

| Fig. 4.3 NI-9222 Analogue Input Module (4- Channel)                                                 | 43     |

| Fig. 4.4 NI-9474 Digital Output Module (8- Channel)                                                 | 44     |

| Fig. 4.5 NI PS-15 Power Supply                                                                      | 44     |

| Fig. 4.6 CompactRIO System                                                                          | 45     |

| Fig. 4.7 System Block Diagram                                                                       | 45     |

| Fig. 4.8 Circuit Diagram- Experimental Setup                                                        | 47     |

| Fig. 4.9 GUI.vi Front Panel (Hysteresis Current Control)                                            | 49     |

| Fig. 4.10 GUI.vi Front Panel (Constant ON-Time Control)                                             | 50     |

| Fig. 4.11 GUI.vi Block diagram (Indicators)                                                         | 50     |

| Fig. 4.12 GUI block Diagram (DMA- FIFO)                                                             | 52     |

| Fig. 4.13 Data Acquisition using User Controlled I/O sampling on the FPGA target side                              | 54 |

|--------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.14 Reading Input channels with FPGA I/O node                                                                | 54 |

| Fig. 4.15 User-Controlled I/O sampling                                                                             | 54 |

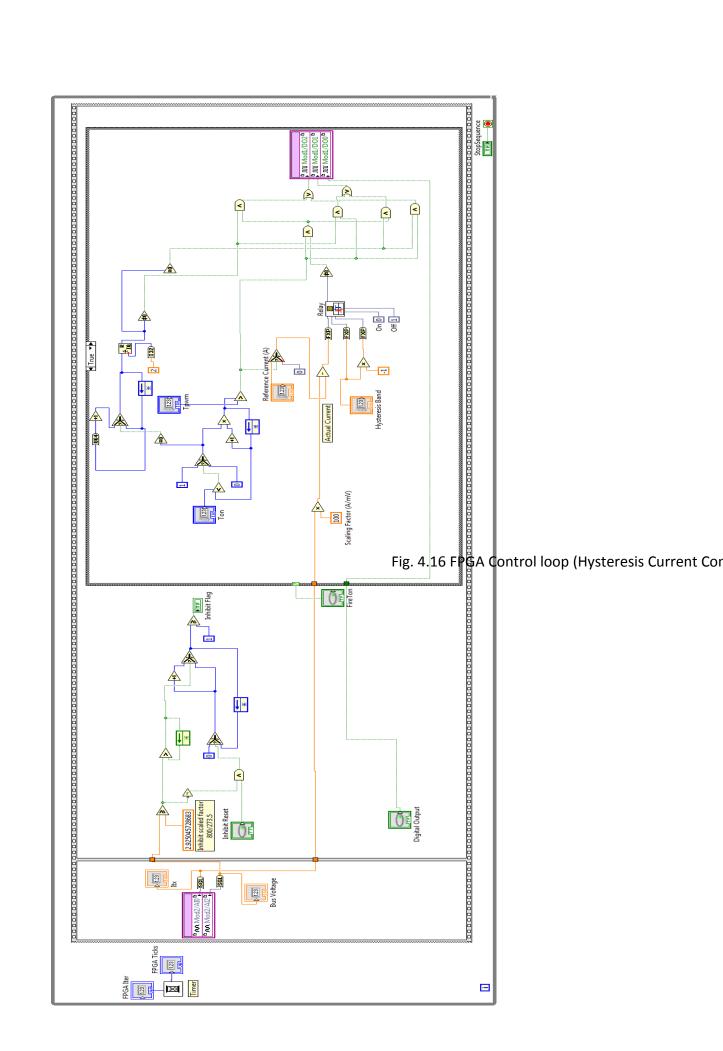

| Fig. 4.16 FPGA Control loop (Hysteresis Current Control)                                                           | 57 |

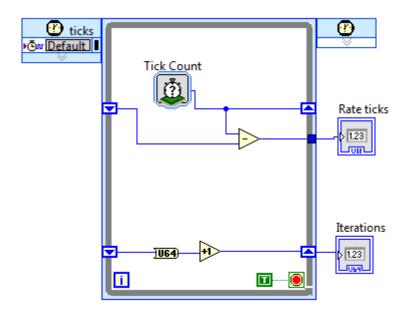

| Fig. 4.17 Block Diagram for Timer sub VI                                                                           | 58 |

| Fig. 4.18 Reading and writing data using individual FPGA I/ O nodes                                                | 59 |

| Fig. 4.19 Reading and Writing data using Single I/O node                                                           | 59 |

| Fig. 4.20 Implementation of hysteresis current control using (a) Relay VI (b) S-R flip flop                        | 60 |

| Fig. 4.21 Interchanging switch gate signals using cycle counter and logic gates                                    | 61 |

| Fig. 4.22 Interchanging gate signals using case structures                                                         | 62 |

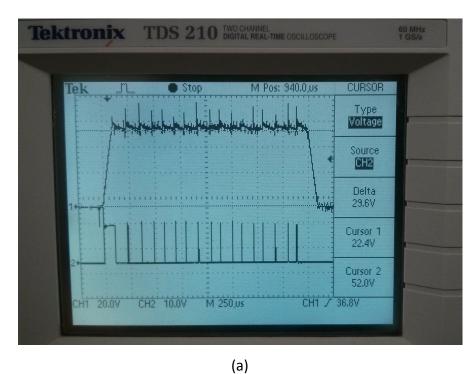

| Fig. 4.23 Experimental waveforms ( $V_{dc}$ = 125V, $I_{ref}$ =60A, ON-Time= 4 $\mu$ s)                            | 64 |

| Fig. 4.24 Experimental waveforms without pull down resistor                                                        | 64 |

| Fig. 4.25 Pull down Resistor and Ni 9474 digital output module                                                     | 65 |

| Fig. 4.26 Experimental waveforms (with pull down resistor of $1k\Omega$ )                                          | 67 |

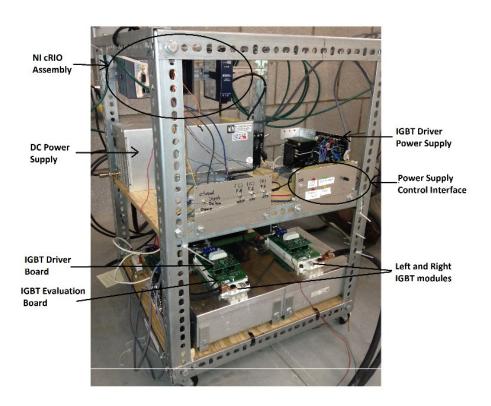

| Fig. 4.27 Experimental Setup                                                                                       | 69 |

| Fig. 4.28 CompactRIO Assembly                                                                                      | 69 |

| Fig. 4.29 IGBT Modules                                                                                             | 70 |

| Fig. 4.30 Power supply control interface                                                                           | 70 |

| Fig. 4.31 Experimental waveforms- (Vdc= 125V, Iref =60A, ON-Time= 4 μs)                                            | 72 |

| Fig. 4.32 Experimental waveforms- (V <sub>dc</sub> = 125V, I <sub>ref</sub> =60A, ON-Time= 16μs)                   | 73 |

| Fig. 4.33 Experimental waveforms (V <sub>dc</sub> = 500 V, $I_{ref}$ =200 A, ON-Time= 4 $\mu$ s)                   | 74 |

| Fig. 4.34 Experimental waveforms- (Vdc= 500V, Iref =200A, ON-Time= 12μs)                                           | 75 |

| Fig. 4.35 Experimental waveforms- ( $V_{dc}$ = 500 V, $I_{ref}$ =200 A, ON-Time= 12 $\mu$ s, Fund. Period = 30 Hz) | 76 |

| Fig. 4.36 Experimental waveforms- ( $V_{dc}$ = 500 V, $I_{ref}$ =200 A, ON-Time= 12 $\mu$ s, Fund. Period = 10Hz)  | 77 |

| Fig. 4.37 Comparison of simulation and test current waveforms                                                      | 79 |

| Fig. 5.1 Proposed Topology & Modes of Operation (Soft Switching)                                                   | 85 |

| Fig. 5.2 Soft Switching waveforms with zero current switching                                                      | 86 |

| Fig. 5.3 State Plane Trajectory                                               | 86  |

|-------------------------------------------------------------------------------|-----|

| Fig. 5.4 Simulation waveforms with ZCS (Vdc= 500V, Iref =200A, ON-Time= 12μs) | 93  |

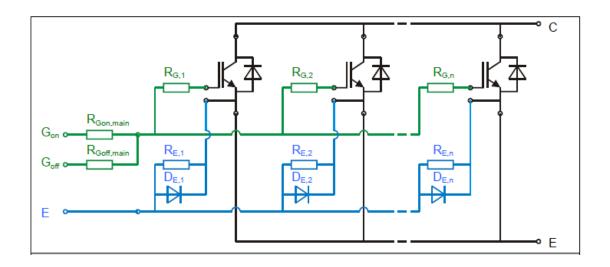

| Fig. A.1 Semix IGBT module gating circuit                                     | 101 |

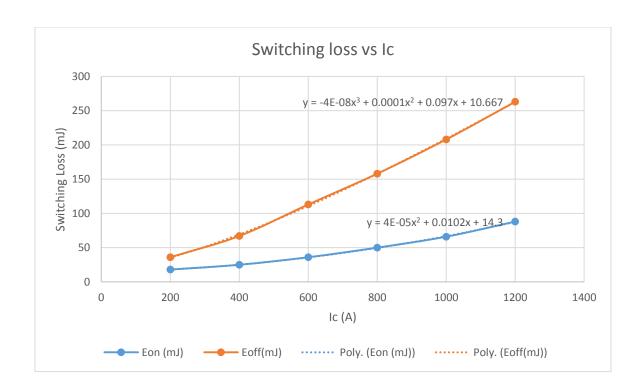

| Fig. A.2 Switching loss versus collector current                              | 103 |

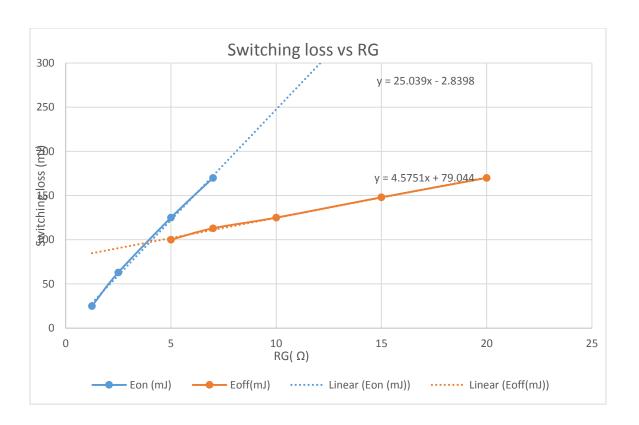

| Fig. A.3 Switching loss versus Gate resistor                                  | 104 |

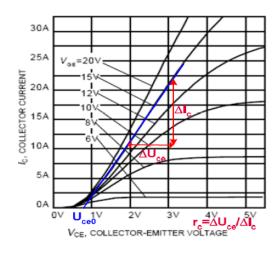

| Fig. A.4 Measurement of U <sub>ceo</sub> and r <sub>c</sub>                   | 107 |

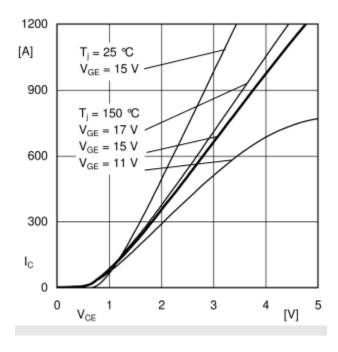

| Fig. A.5 Ic versus Vce for Semix IGBT                                         | 108 |

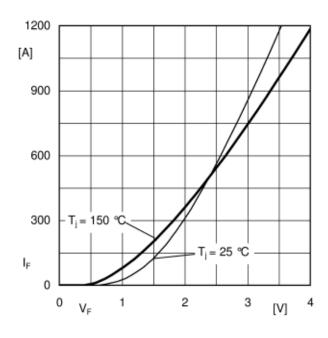

| Fig. A.6 I <sub>c</sub> versus V <sub>ce</sub> for Semix Diode                | 109 |

# **LIST OF TABLES**

| Table 3-1 Simulation Parameters                                     | 26  |

|---------------------------------------------------------------------|-----|

| Table 4-1 Hardware Description                                      | 68  |

| Table 5-1 ZCS Design Summary                                        | 91  |

| Table A-1 Test Parameters - Switching loss versus collector current | 103 |

| Table A-2 Test Parameters- Switching loss versus Gate resistor      | 104 |

| Table A-3 Summary - Hard Switching Power loss                       | 110 |

# **LIST OF ACRONYMS**

TEM Time Domain Electromagnetic

FEM Frequency domain electromagnetic

AEM Airborne Electromagnetic

HTEM Helicopter Time domain Electromagnetic

Tx- coil Transmitter coil

Rx- coil Receiver coil

GPS Global Positioning System

ZCS Zero current switching

ZVS Zero voltage switching

DC Direct current

AC Alternating current

IGBT Insulated Gate Bipolar Transistor

NI National Instruments

LabVIEW Laboratory Virtual Instrument Engineering Workbench

FPGA Field-Programmable Gate Array

VI Virtual Instrument

AISC Application-Specific Integrated Circuit

G- Programming Graphical Programming

GUI Graphical user interface

DMA Direct memory access

FIFO First in, first out

cRIO CompactRIO

# LIST OF PRINCIPAL SYMBOLS

i<sub>coil</sub> Tx- coil instantaneous current

L<sub>coil</sub> Tx- coil inductance

R<sub>coil</sub> Tx-coil resistance

V<sub>dc</sub> DC link capacitor voltage

Cdc DC Link Capacitor rating

I<sub>x1</sub> Tx-coil current at the beginning of Mode 2

I<sub>x2</sub> Tx-coil current at the beginning of Mode 3

σ Neper frequency

ω Damped natural frequency

M Dipole Moment

N Number of turns of Tx –coil

P<sub>peak</sub> Power Source peak power

V<sub>ps</sub> Output voltage rating of power source

T<sub>c</sub> Capacitor Charging Time

C<sub>s</sub> Snubber capacitance

I<sub>band</sub> Hysteresis current band

L<sub>stray</sub> DC loop stray inductance

R<sub>s</sub> Snubber resistance

P<sub>RS</sub> Snubber resistor power rating

I<sub>ref</sub> Tx –coil reference current

V<sub>pk</sub> Peak voltage allowed across switches

f<sub>sw</sub> Switching frequency

f'sw Effective switching frequency

T<sub>sim</sub> Simulation time step

T<sub>ctr</sub> Controller sampling time

T<sub>ON</sub> Constant ON-Time for the switch

L<sub>r</sub> Resonant Inductor

C<sub>r</sub> Resonant Capacitor

Z<sub>r</sub> Resonant Impedance

$\omega_{\text{r}} \hspace{1cm} \text{Resonant angular frequency}$

$i_{Lr}$  Instantaneous resonant inductor current

v<sub>Cr</sub> Instantaneous resonant capacitor voltage

$I_{\text{Lr},peak} \hspace{1cm} \text{Resonant inductor peak current} \\$

V<sub>Cr,peak</sub> Resonant capacitor peak current

# **CHAPTER 1. INTRODUCTION**

#### 1.1 AIRBORNE ELECTROMAGNETIC SYSTEMS

Airborne Electromagnetic (AEM) systems were built initially for the use in mining industry to explore new mineral land areas. However over the years, AEM systems find extensive use in natural resource management activities such as ground water salinity or water quality investigations. Also these survey techniques are used to explore new freshwater reserves in various countries. The ever increasing application of AEM systems has led to the need for better and efficient systems that are more powerful with deeper exploration depths and at the same time are lighter to carry by an aircraft or a helicopter. The available literature [1, 2] consolidates the journey of evolution of the Airborne Electromagnetic survey systems over the past 50-60 years.

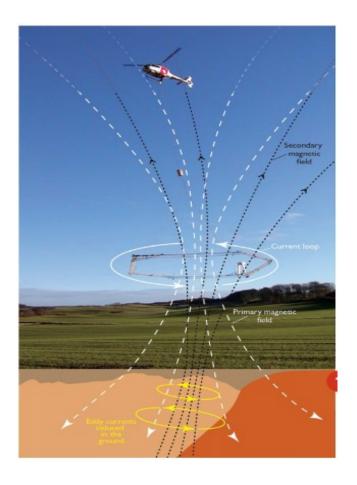

AEM surveys are generally conducted by putting the equipment onboard an aircraft or a helicopter. Time domain electromagnetic (TEM) is the widely used technique in these survey applications [3]. Based on the architecture, the TEM systems are further divided into two categories - Fixed – Wing TEM system and Helicopter TEM system. Due to better spatial resolution and ability to conduct survey in severe terrains, helicopter based systems known as HTEM are preferred over their fixed wing aircraft counterparts. Fig. 1.1 shows a Fixed Wing TEM System and Fig. 1.2 shows a Helicopter TEM system.

Fig. 1.1 Fixed Wing TEM System<sup>1</sup>

Fig. 1.2 Helicopter Time Domain Electromagnetic (HTEM) system<sup>2</sup>

Image Source: 1. Earth & Space Sciences Publication Highlights, web link- <a href="http://ees.lanl.gov/images/Cap">http://ees.lanl.gov/images/Cap</a> Review/Earth%20Science%20Publications%20Highlights.pdf

2. The SkyTEM method for mapping groundwater resources, web link - http://danishresponsibility.dk/skytem-method-mapping-groundwater-resources

#### 1.2 TEM SYSTEM AND PRINCIPLE

TEM system mainly consists of following three major subparts [1]:

- Power source (which can be a replaceable battery bank) and power converter with the current control loop

- Transmitter coil (Tx-coil)

- Receiver coil (Rx-coil) and the associated recording electronics.

The operating principles of a TEM can be described as follows. First, a sequence of high current pulse (square, triangular or cosine waveform) is made to flow through the Tx-coil at sub harmonic of the power line frequency (50 Hz/60 Hz). At the end of current pulse, current is abruptly turned OFF. This fast changing current results in the induction of eddy currents in the conductive bodies under earth's top layer which in turn results in a secondary magnetic field. This secondary magnetic field is sensed by the receiver coil and is recorded in the data recording system on board. A GPS signature is recorded to relate the recorded magnetic field data with actual map of the land area. Fig. 1.3 shows a graphical representation of the TEM principle.

Fig. 1.3 TEM Principle [4]

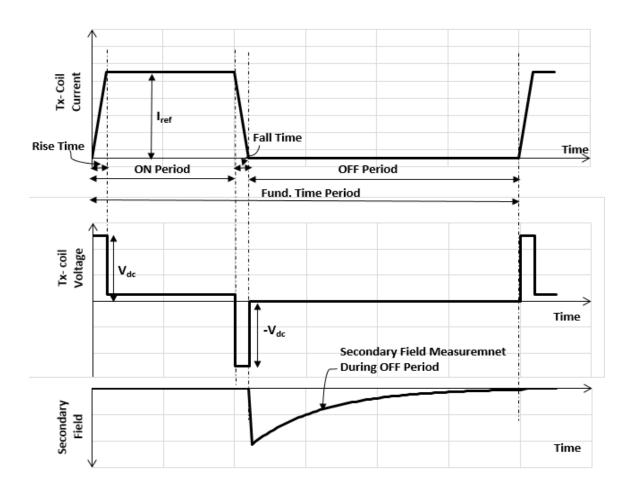

Fig. 1.4 shows the ideal waveforms for Tx- coil current, voltage and secondary field response as recorded by the receiver in TEM systems [5]. It can be seen that the current through the transmitter coil goes from zero to the peak reference value by applying a high DC voltage. This peak reference current is maintained near its reference value by applying current control techniques. After predefined ON period, the current through the coil is made to fall sharply to zero. This sudden fall induces eddy current in the mineral target which in turn produces secondary magnetic field. The secondary field response, as sensed by the receiver is recorded once the OFF period starts. The secondary field due to conductive mineral is highest just after the coil current goes to zero and it decays

exponentially and goes to zero before start of the next pulse sequence. The reason for recording the response during OFF period is to avoid the effect of the primary field on the total field sensed by the receiver coil. In commercially available TEM systems, there are various types of the primary current waveforms implemented along with different settings for ON period (1 ms – 10 ms) and Fundamental Time period (10 Hz, 30 Hz etc.). However, no single system is reported, providing a complete flexibility to control or change system waveform or to alter the ON period or OFF period of the current waveform.

Fig. 1.4 TEM Waveforms

#### 1.3 THESIS OBJECTIVE AND CHALLENGES

This thesis deals with the following objectives

- To design the power converter and control scheme to inject trapezoidal, unipolar current pulses into transmitter coil of the TEM system.

- Minimum current fall times (< 100 μs) for high reference current (200 A) shall be achieved to generate better secondary response from mineral targets.

- The converter control and data acquisition system shall be fast, providing a sampling time in the range of 2  $\mu s$  4  $\mu s$  to provide better data resolution and better current regulation.

- The overall weight and size of the system are limited by the helicopter towing capacity and hence the weight and size of the system shall be kept to minimum (< 200 kg).</li>

- The power losses in the converter shall be minimized.

#### 1.4 THESIS CONTRIBUTIONS

- Design of a power converter and associated control to establish high current trapezoidal pulses in the transmitter coil with current fall time less than 100 μs at high current (200 A) with resultant di/dt of 2000 kA/s.

- Maintaining a predefined constant current magnitude for the duration of predefined pulse width using constant ON-Time control.

- Implementation of LabVIEW based CompactRIO system to perform the data acquisition and current control at a fast sampling rate (500 kHz).

- Balancing the thermal stress in the IGBT switches by interchanging the gating signals in alternate cycles.

- Proposal of zero current switching technique to reduce the switching losses.

#### 1.5 THESIS OUTLINE

The content of this thesis is organized into 5 Chapters.

Chapter 1 presents basic introduction to the AEM methods used in airborne survey systems along with brief explanation of the TEM system components and working principle.

Chapter 2 presents the review of the present power converter topologies used in airborne electromagnetic survey systems along with the advantages and shortcomings of these systems. A brief introduction is presented on the selection of the type of current waveform for the transmitter coil.

Chapter 3 presents the simulation analysis of proposed converter topology with hysteresis current control and constant ON-time control. Different modes of the converter and the associated equations, governing the current waveform are discussed. MATLAB simulation results are presented at low current and high current levels to simulate the converter operation. Design procedure are presented to select DC link capacitor, DC power source and RCD snubber components.

Chapter 4 presents the details about the implementation of the converter control scheme by introducing various subsystems of NI CompactRIO architecture. LabVIEW programming approach is presented for the proposed system in detail. Code optimization is discussed

to show the improvement steps followed during implementation stage to reduce the sampling time. A problem of switch turn OFF delay is discussed along with the solution, implemented using pull down resistors. The test results obtained from the system tests, carried out at low power (125V, 60 A) and high power (500V, 200 A) are presented to show the effectiveness of the designed system.

Chapter 5 presents the selection of the soft switching scheme to reduce the switching power loss in the converter. The operation of soft switching converter topology is discussed using state plane trajectory and design calculations are presented to select the resonant elements considering the design criteria. MATLAB simulation results are presented to verify the zero current switching design.

Chapter 6 summarizes the overall research conducted in this thesis and presents the final conclusions. Suggestions for future work on this topic are presented.

## **CHAPTER 2. REVIEW OF POWER CONVERTER TOPOLOGIES IN**

# **AEM SYSTEMS**

#### 2.1 INTRODUCTION

The AEM applications need a particular attention to the power converter design, to control the excitation of current pulses in the transmitter coil (Tx-coil). Although AEM systems are used for geophysical surveys for a long time and there is great amount of work published and reported in the design optimization and configuration of transmitter coil (Tx-coil) and receiver coil (Rx-coil) but there is very limited work published and reported on the design of the power stage of these systems . However an attempt was made to collect presently available literature pertaining to design of power converters for TEM applications.

#### 2.2 SELECTION OF CURRENT WAVEFORM

One of the starting point to design a TEM survey system is to select a current waveform that results in the maximum response from the mineral target. Different type of current waveforms (Triangular, Trapezoidal, Square, Cosine, Half – sine) are historically used in airborne TEM methods. The previous work by [6] investigates the effect of different transmitter coil waveforms on the system response recorded from the mineral deposit and concludes that for the current pulses of same amplitude and width, the maximum response is generated by a square current waveform. However due to the load time constant, a perfect square waveform cannot be achieved in reality. Therefore in this work the power stage is designed to provide a trapezoidal current pulse.

# 2.3 PRESENT CURRENT CONTROL TOPOLOGIES

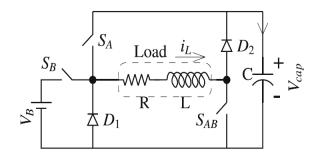

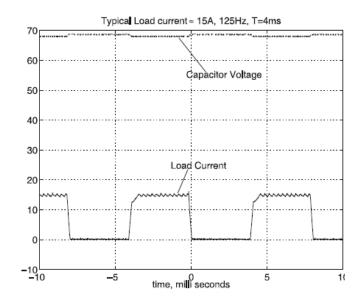

In [7] a converter topology is proposed for TEM application. This paper discusses the requirements of a HTEM system in detail along with its working modes, analysis, control and performance. This topology is only tested for a laboratory scale model (Current = 30A, supply voltage =12V, fall time =200us). A leading edge modulation technique is presented for capacitor voltage control. Fig. 2.1 shows the converter topology used in [7] and Fig. 2.2 shows the experimental load current and the capacitor voltage waveforms.

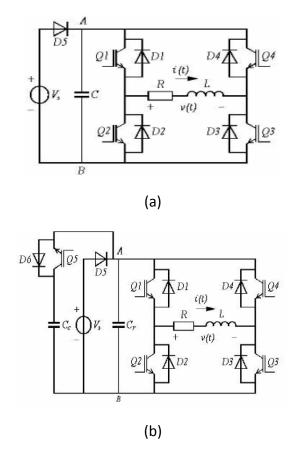

Fig. 2.1 TEM Converter Topology using two energy storage elements [7]

Fig. 2.2 Load Current and capacitor voltage waveforms [7]

#### **Advantages:**

- Use of two energy storage elements reduces the current overshoot irrespective of the sampling rate of the control system.

- 2. Good capacitor voltage regulation at different load current values (low current).

- The topology presents low power loss due to recycling of the coil energy at the end of pulse.

The information on the sampling rate of data acquisition and rate of the control system is not presented.

#### Disadvantages:

- The voltage of the capacitor is regulated to a reference value through energy recovery from load to the capacitor during fall time. At high current levels the capacitor voltage cannot be regulated at the reference value due to losses in the circuit.

- 2. Absence of snubber circuits and implementation with hard switching technique risks system safety.

- 3. The performance at high current levels is highly uncertain with this topology.

- 4. Data is not presented on the use of any special technique for data acquisition and control and an important factor of sampling rate is not considered.

In [8], an inverter topology with clamped and unclamped circuit is presented for airborne surveying systems. The main feature of the proposed topology is the fast reversal of the

current through the transmitter coil. Fig. 2.3 shows the circuit layout of the unclamped and clamped converter topology used in airborne electromagnetic surveying system [8]

Fig. 2.3 Converter Topologies for fast current reversal (a) unclamped topology (b) clamped Topology [8]

Fig. 2.4 shows the load current and capacitor voltage waveforms for the unclamped converter topology. It can be observed that during the polarity reversal, a larger capacitor voltage is achieved due to resonance between the capacitor and load inductor.

Fig. 2.4 Voltage and current waveforms- Unclamped Topology [8]

The advantages and disadvantage of the proposed system are as follows

#### **Advantages:**

- The voltage used for current reversal can be made much larger than the source voltage due to resonance phenomenon. This means that a smaller voltage source can be used while achieving larger voltage magnitudes at current reversal.

- 2. A current reversal time of 200  $\mu s$  was achieved.

#### Disadvantages:

An OFF period is preferred in between the subsequent current pulses because in this case the distortion produced by primary field is negligible on the recorded

- secondary field. However in the present work there is no provision for the OFF period between the subsequent current pulses.

- 2. Clamped topology requires an additional capacitor and controlled switch that adds to the cost, weight and additional losses in the system.

- 3. Bad switch utilization, no snubber protection, no soft switching mechanism available.

#### 2.4 CONCLUSION

Observing the work discussed in literature review it can be summarized that there is a scope to design a new system that comprise a power source, converter topology, transmission coil, receiver coil and data acquisition system that is efficient, utilizes less number of system components, provides better control and performance. With the improvement in semiconductor technology along with wider use of control and acquisition tools such as LabVIEW, a new high power yet lighter and efficient system is proposed. For implementation of the converter control scheme, a trapezoidal current waveform is selected as the desired current waveform.

## **CHAPTER 3. THE PROPOSED POWER CONVERTER – DESIGN**

## **AND SIMULATIONS**

#### 3.1 INTRODUCTION

This chapter presents the detailed design and simulation analysis of the power circuit and the control scheme for controlling the current waveform in the transmitter coil. MATLAB Simulink is used to simulate the performance of the proposed converter and associated control before implementing the system. An attempt is made to provide the information on important starting points defining the scope or the final output. The power converter (Type – D chopper) topology modes are presented along with two current control strategies. First, the current control is achieved by implementing widely used hysteresis current control. However to limit the current overshoots caused by high di/dt and to implement soft switching techniques later in the project work it is very important to have a precise timing control over Turn - ON duration of the switch, which cannot be controlled precisely by hysteresis current control. To achieve better switch timing control, a novel constant ON-time control logic is developed and simulated in MATLAB Simulink and successfully implemented during implementation phase. In the end of this chapter concluding remarks are provided based on the simulation results.

#### 3.2 IMPORTANT CONSIDERATIONS

The following points are considered at the start of the design procedure to define the targeted performance from the system.

- The transmitter coil is designed and optimized in different work. Already known resistance value (55 m $\Omega$ ) and inductance value (200  $\mu$ H) are used for simulation purposes.

- Although a bipolar (positive and negative) current pulse waveform is a preferred

choice to cancel out the noise in the secondary field recorded by the receiver,

unipolar current sequences are considered in this work due to design simplicity

and cost effectiveness of the converter.

- To avoid interference with the power line frequency, the fundamental time period of the current waveform is selected as sub harmonic of the power line frequency (50 Hz/60 Hz) [9]. To implement unipolar current waveforms in this work, the fundamental time period is selected as 50 Hz/60 Hz. In next stage of development, system will be modified to generate bipolar current pulses at 25 Hz/30 Hz fundamental frequency.

- Ideally a square current waveform, to achieve maximum secondary field response

from the mineral target would be used [10]. However due to presence of high coil

inductance, a trapezoidal pulse waveform with sharp rise and fall times is a

practically feasible choice.

- The time for which the current is maintained near the peak reference value is referenced as pulse width and is fixed to 2 ms [11].

- As the final system implementation is based on CompactRIO Platform from NI

hence the simulation time step and the controller time step (same as sampling

time) are selected considering the FPGA clock rate of 25 ns and analogue Input module rate of 500 KS/s/channel respectively.

- The final target for the fall time is fixed at 100  $\mu$ s based on other available system studies [13].

- The ideal Simulink models are considered for the IGBTs, diodes and other passive elements.

#### 3.3 PROPOSED CONVERTER TOPOLOGY

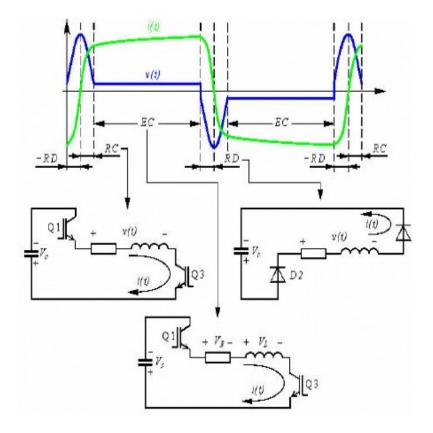

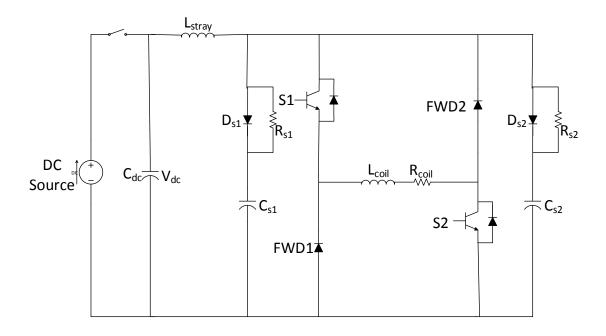

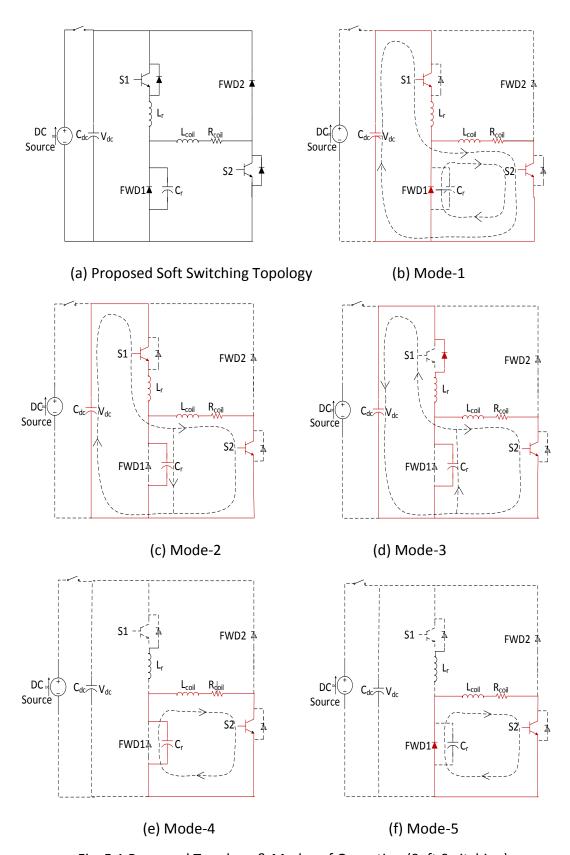

Fig. 3.1(a) shows the proposed converter topology. Here the transmitter coil is represented by a RL-load and is supplied by a high voltage capacitor. A DC source is used to charge the capacitor to a predefined voltage before the start of the pulse.

#### 3.3.1 MODES OF OPERATION (HARD SWITCHING)

The proposed converter topology has 4 modes of operation which are shown in Fig. 3.1 (b) to 3.1 (f).

**Mode1:** The first mode in the cycle of operation starts with turning switches S1 and S2 ON as shown in Fig. 3.1(b). In this mode, full capacitor voltage is applied across the Tx-coil and the coil current (i<sub>coil</sub>) increases. The diodes FWD1 and FWD2 remain OFF. The current through the coil rises from OA to the upper limit set by the reference current.

**Mode2.** Mode 2 corresponds to a free-wheeling period and is initiated when one of the switches is turned off when the current reaches a reference current value set by current control. In this mode current start freewheeling through one of the switches and freewheeling diode. This mode can be implemented in two ways as shown by Fig. 3.1(c)

and Fig. 3.1(d). In first case, switch S2 is kept ON and switch S1 is commutated to maintain the current near the reference value for the required duration of pulse width. In second case, switch S1 is kept ON and switch S2 is commutated to achieve current control. Case 1 and case 2 are applied in alternate pulse cycles to share the switching losses and thermal stress among the two IGBTs.

Mode 3: Once the desired pulse width is reached, both the switches S1 and S2 are turned OFF (Fig. 2(e)). Due to inductive nature of the circuit, diode FWD1 and FWD2 are turned ON at this instant and a negative DC link voltage is applied across the coil. This results in sharp decay in current from reference value to zero. During this mode, part of the energy stored in the coil is fed back to the DC link capacitor. As the current reaches 0A, the diodes are naturally commutated to OFF state and this marks the end of Mode 3.

**Mode 4:** In the next mode, Mode 4, the coil remains isolated form the DC link capacitor hence there is no transfer of energy from the capacitor to coil or vice versa. During this mode the response from the mineral deposit is sensed by the receiver coil and is recorded for post processing. Also at the end of Mode 3, due to energy losses in circuit elements the capacitor voltage is not fully recovered back to the initial value. Hence the power supply is enabled to bring the DC link capacitor voltage back to the reference value. The circuit for this condition is shown in Fig. 3.1 (f). The end of fundamental time cycle marks the end of Mode 4 and initiates next cycle of operation.

Fig. 3.1 Proposed Topology & Modes of Operation (Hard Switching)

#### 3.3.2 CURRENT GOVERNING EQUATIONS

Before starting the simulation of the proposed converter topology, it is important to model the governing equations and then design and select the system components based on the system requirements. First of all as shown in Mode-1 (Fig. 3.1 (b)), the switches S1 and S2 are closed and the circuit becomes a series RLC resonant circuit. The equations governing the series RLC resonance circuit defines the current flow through the load (Tx-coil). The series RLC resonance circuit can be designed to act as over damped, critically damped or underdamped state by selecting the value of circuit elements. However for a given capacitor voltage, the system developed for underdamped conditions will result in least current rise and fall times.

The current through the circuit in Mode-1 can be represented by following exponential rise equation [14] [15]

$$i_{coil} = \frac{V_{dc}}{\omega L_{coil}} e^{-\sigma t} \sin(\omega t)$$

(3.1)

Where

$$\omega = \sqrt{\frac{1}{L_{coil}C_{dc}} - \left(\frac{R_{coil}}{2L_{coil}}\right)^2}$$

(3.2)

$$\sigma = \frac{R_{coil}}{2L_{coil}} \tag{3.3}$$

i<sub>coil</sub> = Instantaneous current through Tx- coil

$V_{dc}$  = DC link capacitor voltage

L<sub>coil</sub>= Tx-coil inductance = 200 μH

$R_{coil}$  = Tx-coil resistance = 55 m $\Omega$

#### C<sub>dc</sub> = DC link capacitor rating

During Mode-2, the coil current freewheels and the zero voltage is applied across the coil, the stored energy is dissipated mainly in the coil resistance. However the resistance of the IGBT switches and the diodes also contribute to some energy loss but for this equation modeling, the small contribution of these factors is not comparable and hence neglected. The current in the Tx-coil during Mode2 is given by following equation [16]

$$i_{coil} = I_{x1} e^{-\sigma' t} \tag{3.4}$$

Where I<sub>x1</sub>= Tx- coil current at the beginning of Mode 2

And

$$\sigma' = \frac{R_{coil}}{L_{coil}} \tag{3.5}$$

Similarly, in Mode-3, when both the switches are turned OFF and the diodes FWD1 and FWD2 conducts, the stored energy of the coil is fed back to the DC link capacitor and coil current decays from its peak value to zero.

The current in this phase is governed by following equation [16]

$$i_{coil} = I_{x2}e^{-\sigma t} \left( (\cos(\omega t) - \frac{\sigma}{\omega}\sin(\omega t)) \right)$$

(3.6)

Where  $I_{x2}$  = Tx-coil current at the beginning of Mode 3.

During Mode 4, the coil remains isolated from the power source and the DC link capacitor. Hence no current flows through the Tx-coil for this period until the two switches are turned ON at the start of next current cycle.

#### 3.3.3 SELECTION OF DC LINK CAPACITOR

The Tx- coil fabricated for this work is a circular coil (stranded copper cable) with 4 turns and diameter of 5m (Area =  $19.6 \text{ m}^2$ ). The dipole moment is fixed to  $15000 \text{ N-m}^2$  after studying the present TEM systems [2]

So the required current can be calculated as

Dipole moment,

$$M = N * I_{ref} * A$$

(3.7)

Where N = No. of turns of Tx-coil

I<sub>ref</sub> = Reference Tx- coil current

A = Area of Tx- coil

By using equation 3.7, the peak DC current is fixed at 200 A.

For driving this current to the coil, the DC link capacitor voltage is fixed to 500 V.

From equation (3.2),  $\omega$  can be represented in terms of  $C_{dc}$ .

From equation (3.5)  $\sigma = 137.5 \text{ Nepers/s}$

Putting t= 100  $\mu$ s,  $I_{x2}$ = 200 A,  $I_{coil}$  = 0 and solving for  $C_{dc}$ , the required value of  $C_{dc}$  is calculated and the closest standard capacitor rating selected is 1000  $\mu$ F.

The capacitor voltage rating is selected considering the future implementations with higher current ratings.

The final capacitor ratings selected is, voltage rating =1500 VDC, Capacitance =1000  $\mu$ F.

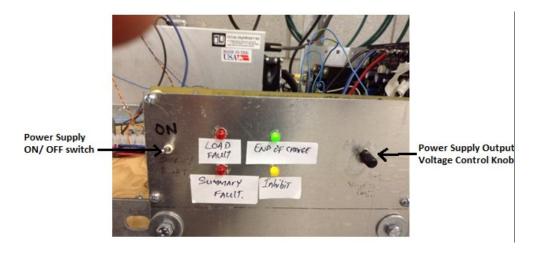

#### 3.3.4 SELECTION OF DC POWER SOURCE

The next step is to select the DC power source that can efficiently charge the capacitor in available time, in-between the current pulses. One of the important point is to select a DC power supply with the provision of remote control i.e. to have a flexibility to control the output voltage of the DC power supply through a user interface. The other important factors to be considered are the output voltage rating and the output current. For this purpose, high power capacitor charging power supplies from TDK Lambda Americas Inc. are found suitable. The equations given in application note [17] are used to select the power source rating for a given charging time of the capacitor.

As per the application note [17], the peak power required from the power source is given by the following equation

$$P_{peak} = \frac{0.5 * C_{dc} * V_{ps} * V_{dc}}{T_c} \tag{3.8}$$

Where  $C_{dc} = DC$  link capacitor rating

V<sub>ps</sub> = Output voltage rating of power source

V<sub>dc</sub> = DC link Capacitor voltage

T<sub>c</sub> = Capacitor Charging Time

As pulse width and fundamental time period for the current pulse is fixed to 2ms and 16.67ms respectively. Therefore the capacitor charging time cannot be more than 16.67ms, if the power supply is always kept connected to the DC capacitor. However it's preferred to connect the power supply only during current OFF period as the power

supply can provide limited amount of current and if it is kept connected to the load all the time the overload protection may cause inhibit action. Effectively maximum value for Tc can be considered equal to 14 ms. Here,  $V_{dc}$  is the difference in the voltage that power supply has to provide in between the current pulses. From the simulation results of next section it can be seen that the drop in the voltage for 500V, 200A operation is around 15V but a part of it is recovered by the energy recovery from the coil. Hence to calculate the power rating of the power supply,  $V_{dc}$  can be considered around 12V. Using the earlier calculated capacitance of DC link capacitor along with  $V_{dc}$ =12 V, and  $T_c$  = 14 ms, in equation (3.8), a value of peak power was calculated for the power source. The power supply finalized was 1KW, 3KV (102-3kV-POS-5V-LP) from TDK Lambda. A 15 pin D-type female connector located on the power source provides the access to connect the remote interface cable from manual control interface to the power source.

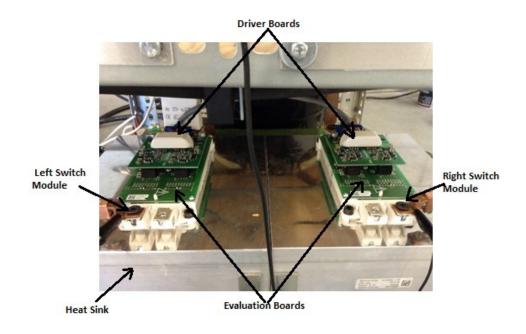

#### 3.3.5 SELECTION OF IGBTS

As in all converter applications to select the IGBT switches, the important aspect is to calculate or fix the current and voltage specifications as per the application needs. However in this application additional constraints are put by weight and size of the power converter and hence attention is given to choose the modular, light yet powerful switch modules. Although there are various IGBT product families available from manufacturers such as Infineon, Powerex and On Semiconductors, but for this application, Semix IGBT modules from Semikron are selected due to their modular and compact design, Cost effectiveness and superior performance at high power levels.

The other advantages of Semix modules are [18]

- Single housing contains the IGBT and free-wheeling diode, and needs only one switch

assembly for each converter leg resulting in compact size and lower cost of the

converter.

- The modular design of Semix IGBT modules result in low inductance design as the

DC link connections can be short, resulting in reduced voltage overshoot.

- Due to directly mounted driver board optimum gate drive performance can be achieved (with minimum noise)

- The reduced solder joints or the connections result in better system reliability.

Considering the future scope of testing at higher power levels, 1200V, 600A IGBT modules are selected. These modules can handle switching frequencies up to 10 KHz with 100% duty cycle. More details on implementation of these IGBT modules is provided in Chapter 4.

#### 3.3.6 SIMULATION RESULTS

The simulation analysis was conducted using MATLAB Simulink. Table 3-1 shows the major parameter values considered for the simulation with hysteresis current control

**Table 3-1 Simulation Parameters**

| Parameter                             | Symbol             | Value | Units |

|---------------------------------------|--------------------|-------|-------|

| Reference Tx- coil current            | I <sub>ref</sub>   | 200   | А     |

| Initial DC link capacitor voltage     | V <sub>dc</sub>    | 500   | V     |

| DC Link capacitor rating              | C <sub>dc</sub>    | 1000  | μF    |

| DC power source peak charging rate    | P <sub>peak</sub>  | 1100  | J/s   |

| DC power source output voltage rating | V <sub>rated</sub> | 3     | KV    |

| Tx-coil inductance                    | L <sub>coil</sub>  | 200   | μН    |

| Bus bar stray inductance              | L <sub>stray</sub> | 200   | nH    |

| Current pulse width                   | T <sub>1</sub>     | 2     | ms    |

| Fundamental time period               | T <sub>2</sub>     | 16.67 | ms    |

| Simulation time step                  | T <sub>sim</sub>   | 25    | ns    |

| Controller sampling time              | T <sub>ctr</sub>   | 2     | μs    |

| Hysteresis band                       | I <sub>band</sub>  | ±5    | А     |

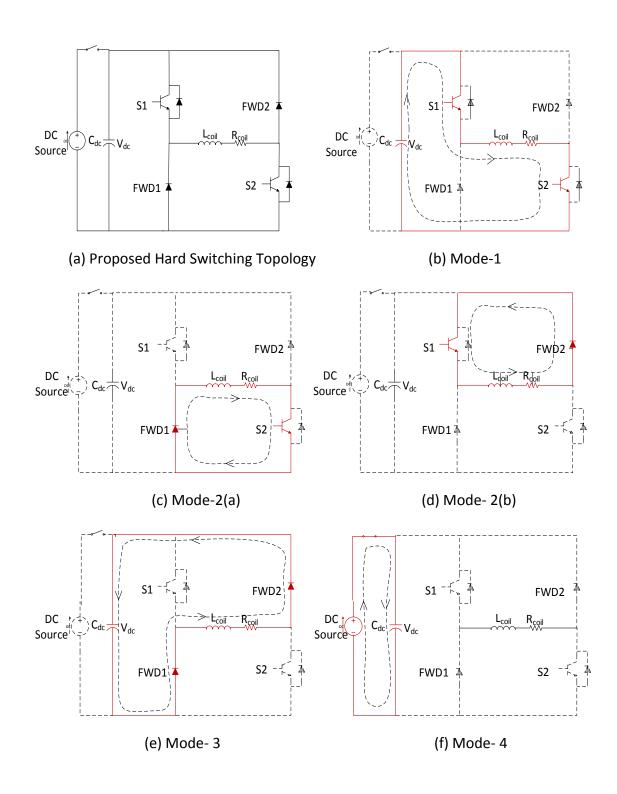

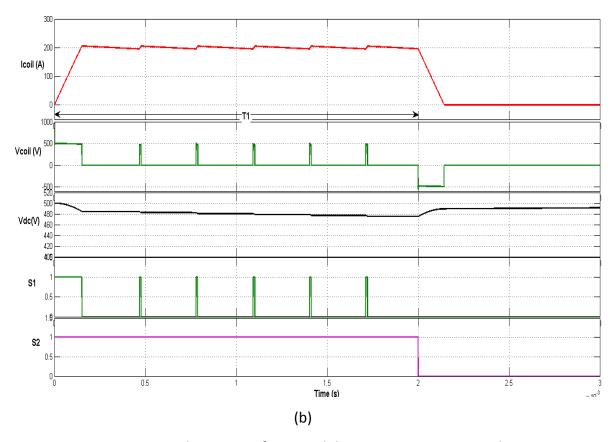

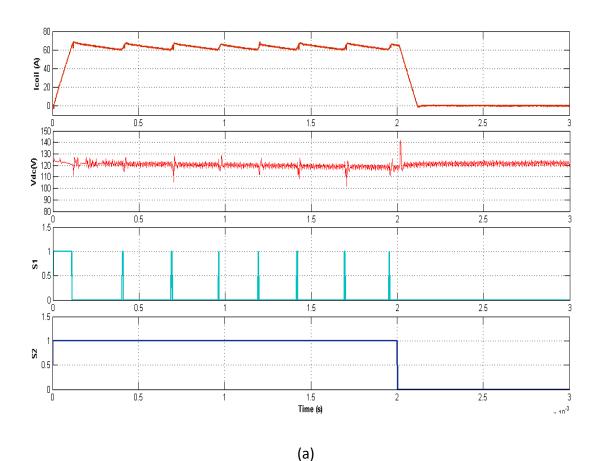

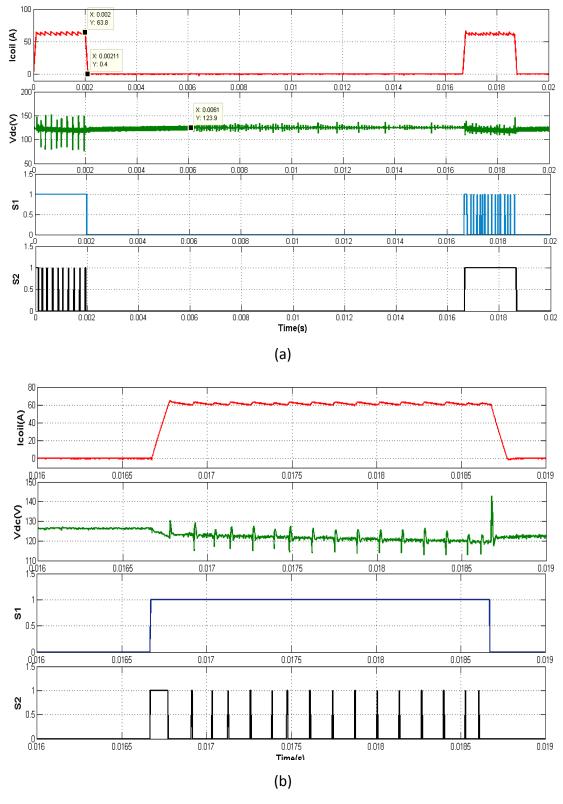

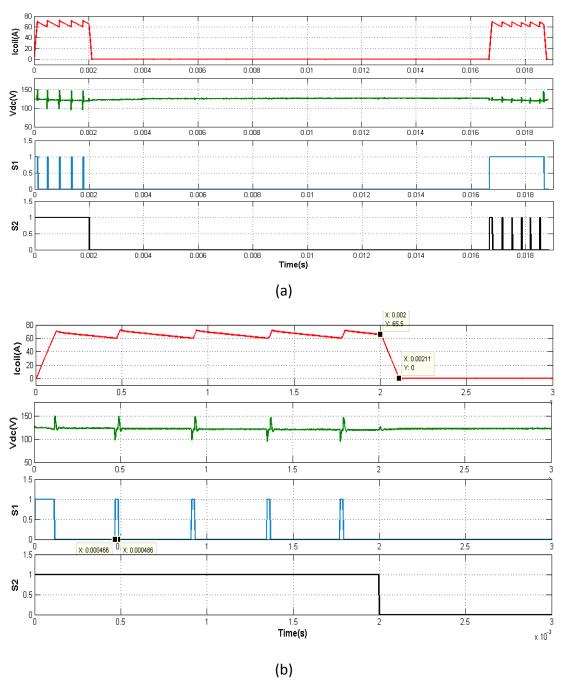

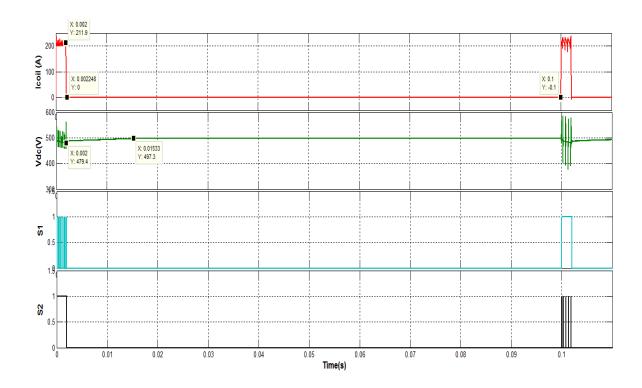

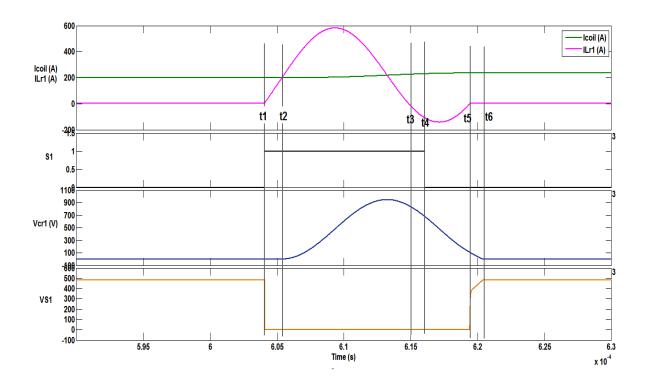

Fig. 3.2 shows the simulated waveforms for the proposed topology with hysteresis current control. Fig. 3.2(a) shows the coil current, coil voltage, DC link capacitor voltage and gating signals for switches S1 and S2. It can be seen that the pulse ON period (T1) is kept to 2ms and fundamental time period of the pulse (T2) is around 16.67ms (for f = 60 Hz). At the beginning of the pulse current rises almost linearly to the preset load value and at the end of pulse ON period current drops sharply to zero. As discussed earlier this sharp decrease in current is important to get an improved field response from the mineral

deposit. Also it is clear from Fig. 3.2(a) that during 1st cycle, switch S2 is kept closed for the duration T1 and Switch S2 commutates to implement hysteresis control. For 2nd cycle, switch S1 is kept closed for the duration T1 and switch S2 commutates.

It is important to note that the DC link capacitor voltage,  $V_{dc}$  is depreciated from its initial value of 500V to 480 V at the end of first pulse. However due to energy recovery from the Tx-coil to the DC capacitor, the voltage is recovered from 480V to around 490 V. Hence almost half of the voltage drop has been recovered back due to energy recovery. The remaining 10V charging can be achieved by enabling the DC power source. It is clear that the DC capacitor is charged back to 500V in 5ms which is quite less than the available zero current period of 14.67ms. Fig. 3.2(b) shows the waveforms with changed resolution to observe the waveforms during the pulse width.

Fig. 3.2 Simulation waveforms with hysteresis current control

(a) Two pulse cycles (b) One pulse cycle (Simulation parameters shown in Table-3-1)

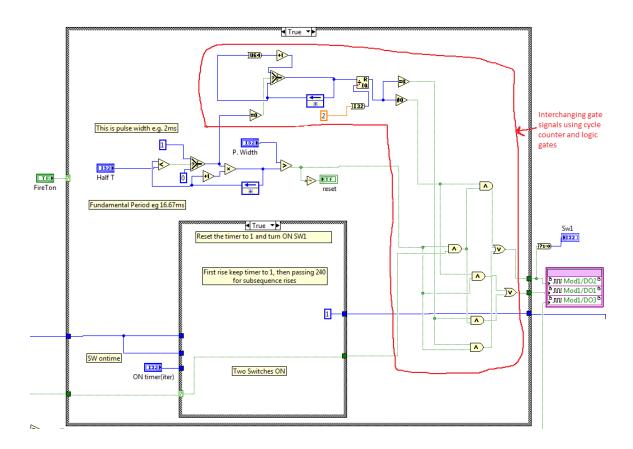

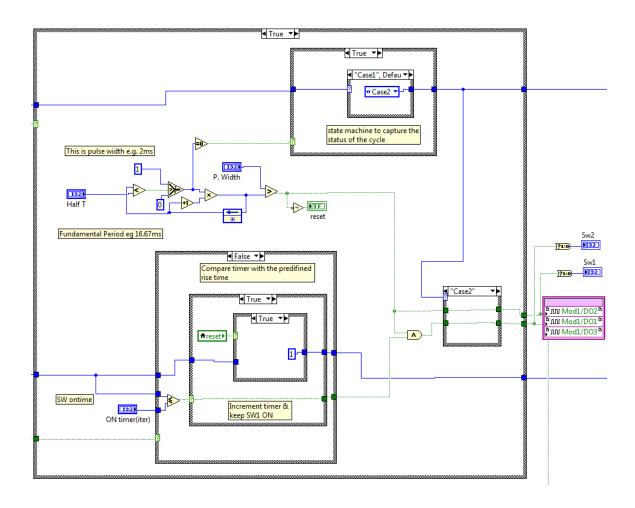

### 3.4 CONSTANT ON - TIME CURRENT CONTROL SCHEME

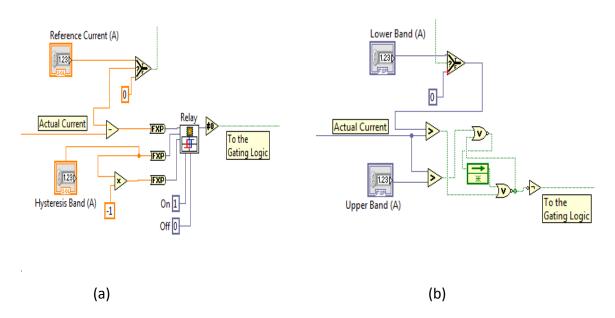

As discussed in earlier sections one of the important requirements of the TEM system is to inject a trapezoidal current pulse through the Tx-coil. The current can be maintained near the reference value by applying widely used digital hysteresis current control. A digital hysteresis current control was implemented using standard *Relay* function of LabVIEW and alternatively by using S-R flip-flop logic. However in each case the minimum achievable sampling time was 6  $\mu$ s. This leads to current overshoot beyond the values set by control input (a common problem associated with hysteresis current control) [19]. Also high sampling times will result in low data resolution of the secondary field survey data

as same system is to be used for recording the secondary field response. The high sampling time is contributed to the more processing power utilized by the control code implementation using flip-flops and Relay function. This condition is also not favorable to design a soft switching scheme for the converter, as the ON- time or OFF time cannot be controlled effectively by employing hysteresis current control.

To avoid these problems, a time based control strategy is needed where the switch is allowed to stay ON for a predefined time interval. To achieve this, a novel control strategy referred as Constant ON time control was conceptualized and implemented.

The main attributes of this new technique are

- Results in a better control where the ON- Time for the IGBT switch is directly controlled by passing a numerical control on the host screen.

- Constant ON- Time logic can be implemented in the LabVIEW using case structure

architecture which uses less processing power of the controller and is fast to

execute as compared to sequential logic control (Hysteresis control using relay VI

or SR flip Flops).

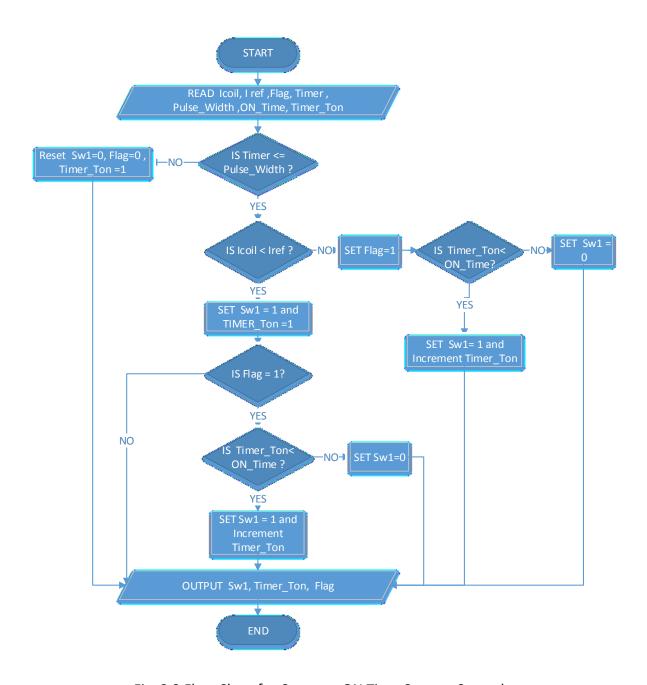

A MATLAB Simulink standard function block was used to write a function to perform this control logic. Fig. 3.3 shows the flow chart explaining the logic of constant ON-time current control scheme.

Fig. 3.3 Flow Chart for Constant ON Time Current Control

Following is brief description of the variables used in the flow chart.

"ON \_Time" is the variable that stores the fixed number of count corresponding to the pre - defined ON Time.

"Timer\_Ton" is the variable that stores the iteration count while the switch is ON.

"Timer" is the counter that counts the number of iterations for the fundamental time period.

"Pulse\_Width" represents the fixed time for which the square current waveform is present.

"Flag" is used as a memory element to store the information when the coil current exceeds the reference current first time. It is activated whenever the coil current crosses the value of reference peak current first time. Variable "Flag" is reset when the end of the desired current pulse is reached.

The operation of the TEM with the constant ON-time current control scheme was simulated in MATLAB Simulink. At the start, the parameters such as coil current, reference peak current, pulse width, flag status and timer values are read from the MATLAB workspace and are passed to the function block containing the constant ON-Time program logic. In the initial phase, when the coil current is less than the reference current, the switch stays ON.

After the initial rise of the current, whenever coil current crosses the reference peak current, "Timer \_Ton" is incremented and is compared with "ON\_Time" for each loop iteration. Switch S1 remains ON until "Timer\_Ton" is less than "ON\_Time", resulting in current rise and "Timer\_Ton" keep on updating. Switch S1 is turned-OFF when "Timer\_Ton" becomes equal to "ON\_Time", resulting in freewheeling of coil current through freewheeling diode and Switch S2. The coil current is decayed slowly and when it reaches a value less than reference peak current the "Timer Ton" is reset, Switch S1 is

turned - ON again and value of "Timer\_Ton" is incremented in subsequent Iterations for the defined duration of "ON\_Time".

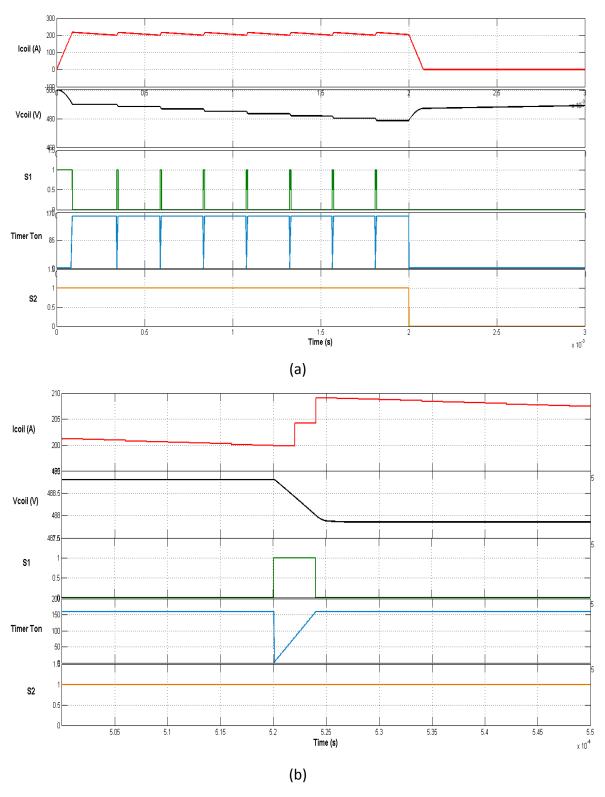

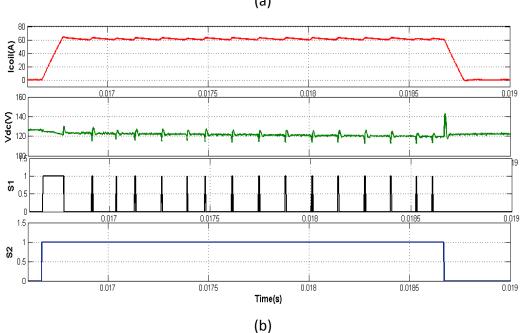

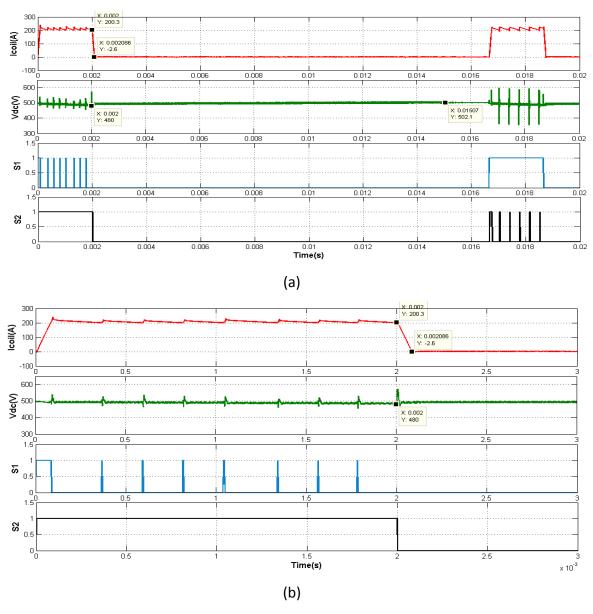

To balance the thermal stress of the IGBT modules, the alternate switch operation (used with hysteresis current control) is retained in constant ON – Time control technique. Fig. 3.4 (a) shows the overall waveforms for one pulse width period. The coil current and DC capacitor voltage waveforms are similar to the one achieved with hysteresis current control. From Fig. 3.4 (b), it can be observed that as soon as the coil current falls below the reference current, the value of "Timer\_Ton" start increasing and Switch S1 is turned ON resulting in increase in coil current. After a time of 4  $\mu$ s the value of "Timer\_Ton" becomes equal to 160 (i.e. 4  $\mu$ s/ 25 ns) and the switch S1 is turned-OFF, and "Timer\_Ton" keeps its value until the coil current falls below reference current. The converter was simulated with different values of ON\_Time and corresponding effect was observed in the simulation results.

Fig. 3.4 Simulation waveforms with Constant ON –Time

(a) One Pulse Period (b) One switching commutation

(Simulation Parameters –  $V_{dc}$  = 500V  $I_{ref}$  =200A,  $T_{sim}$  = 25ns,  $T_{ctr}$ =2 $\mu$ s, ON\_Time = 4 $\mu$ s)

# 3.5 DESIGN OF SNUBBER CIRCUIT

During the discussion of operating modes of the converter in section 3.3.1 the stray inductance due to DC bus was neglected. However in practice, there is always a DC loop stray inductance associated with the DC bus and whenever the IGBT switch is turned OFF, the trapped energy in the stray inductance results in voltage overshoot. In high power applications similar to the case under consideration, this voltage overshoot can reach to a magnitude that can possibly damage the switch and other circuitry. One of the ways to keep the stray inductance to minimum is to keep the DC link conductor lengths to minimum and to carefully design the DC link conductors with minimum overlap lengths.

But these design considerations can't completely eliminate the stray inductance and hence a solution is required to suppress the voltage overshoot at the IGBT terminals. To protect the circuit elements from switching transients the solution proposed in literature [20] [21] is to use a snubber circuit.

#### 3.5.1 ADVANTAGES OF RCD SNUBBER

There are various type of snubber circuits that can be used in different applications and their advantages and disadvantages are discussed in detail in [20]. For this application, RCD snubber is used due to following advantages:

- 1. Suitable for medium and high power applications

- 2. Suitable for high frequency operation.

- Can be implemented by using direct mount snubber modules with minimum circuit length and hence minimum parasitic and stray inductance.

The snubber diode prevents any oscillations between snubber capacitor and DC capacitor. These oscillations are otherwise present in the case of Decoupling Capacitor.[21]

The circuit diagram with RCD snubber is shown in Fig.3.5

Fig. 3.5 Converter circuit with RCD snubber

## 3.5.2 CALCULATION OF SNUBBER CAPACITANCE

The snubber capacitor is given by the following formula [20]

$$C_s = \frac{L_{stray}I_0^2}{(V_{pk} - V_{dc})^2}$$

(3.9)

Here L<sub>stray</sub>= DC loop stray inductance =200 nH

$I_0$  =Maximum coil current to be supplied = 200 A

V<sub>pk</sub>= Peak voltage allowed =650 V

V<sub>dc</sub>= DC bus voltage =500 V

Putting these values in equation (3.9)

$$Cs = 0.35 \mu F$$

A near standard capacitor rating available is 0.47  $\mu F$  and the voltage rating of the capacitor selected is 1200 V

### 3.5.3 CALCULATION OF SNUBBER RESISTOR

The snubber resistor can be calculated by formula [21]

$$R_S = \frac{1}{6 \, C_S f_{SW}} \tag{3.10}$$

Where C<sub>s</sub> = snubber capacitor (calculated above)

f<sub>sw</sub>= switching frequency of Switch S1

Here the switch S1 is commutating for a period of 2 ms and then remains in OFF state till the end of fundamental time period. For a pulse ON period of 2ms and fundamental time period of 16.67ms the switch S1 behavior during switching is observed in the MATLAB simulation. It is seen that for a load current of 200A , DC capacitor voltage 500V and ONTime of 4  $\mu$ s, the switching period of switch S1 is 200  $\mu$ s giving a switching frequency, f<sub>sw</sub>= 5000 Hz. Using this value in equation (3.10) snubber resistor value of 71 ohm is calculated.

Power rating of the snubber resistor is given by

$$P_{RS} = 0.5C_s(V_{pk}^2 - V_{dc}^2)f'_{sw}$$

(3.11)

Here the effective frequency

$$f'_{SW} = f_{SW} * \frac{T_1}{T_2}$$

(3.12)

Where T1 = Pulse ON Time = 2ms

And T2 = Fundamental Time Period = 16.67ms

Hence from equation (3.12),  $f'_{sw} = 588 \text{ Hz}$

Substituting these values in equation (3.11) yield

$$P_{Rs} = 61 \text{ W}$$

A standard resistor with ratings 75ohm, 100W (non- inductive design) with product no. "MP9100-75.0F-ND" from Caddock Electronics Inc. was selected.

While implementing the snubber design, it is always advantageous to keep the parasitic inductance of the snubber circuit layout to minimum. With individual element R, C and diode there will be unavoidable inductance associated with the circuit layout. To effectively implement the snubber design, the direct mount IGBT capacitor module "SCM474K122H8N24-F" from Cornell Dubillier was used .The direct mounting results in minimum parasitic inductance resulting in a better snubber implementation. It is a direct mount module containing snubber capacitor and snubber diode in a single housing and having an external connection to install the snubber resistor. The module's DC voltage rating is 1200V.

### 3.6 CONCLUSION

In this chapter, based on predefined scope the operating modes are discussed for the class -D converter along with the equations defining the current waveform during these modes. A detailed design approach is described to select the system components.

MATLAB Simulink analysis is presented to evaluate the performance of the power

converter. A constant ON –time control technique is explained to achieve better timing control. In the end, to protect the IGBT and the converter circuitry from switching voltage overshoots, a RCD snubber design is presented. The verification of the snubber design cannot be performed in MATLAB simulation due to ideal component behavior. However the effect of snubber circuit is evaluated in experimental tests presented in Chapter 4.

# **CHAPTER 4. HARDWARE IMPLEMENTATION AND**

# **EXPERIMENTAL RESULTS**

#### 4.1 INTRODUCTION

This chapter presents the implementation of the proposed converter scheme along with the associated digital control and data acquisition hardware. The LabVIEW programming logic implemented to control the current waveform is presented in detail. The experiment results are presented to display the performance of the entire system at different development stages. An attempt is made to describe the process of LabVIEW code optimization to achieve least possible sampling rates as per the installed hardware capabilities. A problem of switch turn OFF delay was observed and a solution was implemented using pull down resistances. In the end the conclusions are stated.

**NOTE:** The experimental setup was developed and tested at Laval facility of Geo Data Solutions GDS Inc. Canada.

#### 4.2 INTRODUCTION TO LABVIEW

LabVIEW (Laboratory Virtual Instrumentation Engineering Workbench) is a graphical programming environment that, with help from logic blocks and other components, makes it possible to test, simulate and control flowchart-type model [23]. It is easily integrated with hardware devices such as the FPGA. Mostly the block diagram (where the logic circuit is drawn) and the front panel (the input/output data and the programmatic interface) is used when dealing with this program. Except the fact that a graphical

programming language is more user-friendly, the LabVIEW software has benefits considering the following two big differences from other programming languages:

- Graphical programming is realized with help from graphical icons, combined in a

diagram and is then directly compiled to machine code, so that the processor can

understand and execute the orders created in the diagram.

- Data flow is transmitted in form of data (not lines of text). This makes it easier to control different executions done separately and consecutively

# 4.3 INTRODUCTION TO FPGA

Field-programmable gate arrays (FPGAs) are reprogrammable silicon chips. In contrast to processors in a PC, programming an FPGA rewires the chip itself to implement the functionality rather than run a software application.

# **Benefits of Using FPGAs:**

- Faster I/O response times and specialized functionality

- Exceeding the computing power of digital signal processors

- Implementing custom functionality with the reliability of dedicated deterministic hardware

- Rapid prototyping and verification without the fabrication process of custom ASIC design

- Field-upgradable eliminating the expense of custom ASIC re-design and maintenance

# 4.4 COMPACTRIO SYSTEM ARCHITECTURE

To implement the digital control of the proposed converter and to acquire the current and voltage signals, National Instrument's CompctRIO platform was selected.

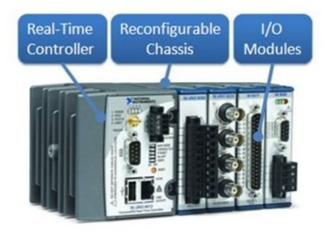

CompactRIO is a reconfigurable embedded control and acquisition system and is vastly used in modern control applications. The CompactRIO system's hardware architecture includes I/O modules, a reconfigurable FPGA chassis, and an embedded real time controller [24]. CompactRIO is programmed with NI LabVIEW graphical programming tools also known as G- Programming.

Due to faster control and data acquisition possible with embedded controller and the modular design approach and the option to expand the cRIO architecture at any time by adding additional input output modules with the same platform, CompactRIO was selected to perform the control and acquisition tasks for this application.

The standard CompactRIO system selected for this application consists of following sub parts [24]:

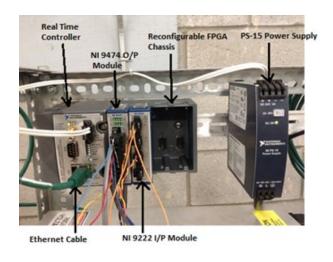

# 4.4.1 REAL TIME CONTROLLER (NI CRIO 9014):

It's an embedded controller that runs the application code in the FPGA target and interfaces FPGA target with C series I/O modules. It has 400 MHz processor, 2GB non volatile storage and 128 MB DRAM. It supports RS 232 serial port for connection to the peripherals. Alternatively an Ethernet port is used in this application for communication between the real time controller and the host Computer. Also a USB slot can be used to attach an external memory.

Fig. 4.1 NI cRIO-9014 RT controller

## 4.4.2 RECONFIGURABLE FPGA CHASSIS (NI CRIO 9111 -4 SLOT)

A four slot reconfigurable chassis is used to provide rugged modular housing to the Real time controller and the C –series I/O modules. A backplane in the chassis contains the FPGA target, and system's data, timing and triggering buses. The FPGA chassis with internal clock frequency of 40MHz is used in this application. In other words, FPGA internal clock runs at a time step of 25ns that correspond to the FPGA tick rate and is used as a unit to check the execution speed of the FPGA code. The application code is written on the host computer and is compiled and downloaded to the reconfigurable FPGA target. Xilinx Virtex-5 LX30 is the type of FPGA used in this chassis. The chassis comes with Din-Rail Mounting or Panel Mounting options. In this application Din-Rail Mounting is selected due to ease of mounting.

Fig. 4.2 NI cRIO-9111 four -slot, reconfigurable embedded chassis

## 4.4.3 ANALOG INPUT MODULE (NI 9222)

To acquire the Tx- coil current and DC capacitor voltage signals, a C- series 4- channel, 16 bit simultaneous analogue input module is selected. It has a sampling rate of 500 KS/s/ch which translates to a sampling time of 2us per channel. The input voltage range for this module is ± 10V and comes with screw terminal connectivity.

Fig. 4.3 NI-9222 Analogue Input Module (4- Channel)

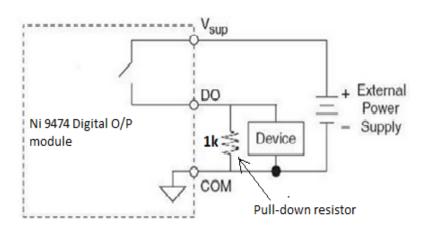

# 4.4.4 DIGITAL OUTPUT MODULE (NI 9474)

After acquiring the data from input channels the program code is executed in the FPGA target and the output signals are generated for the IGBT switches and the Power Supply Control. A C series, 8 channel, 1 us high speed digital output module is used for this purpose. It has an output voltage range of 5 -30V.

Fig. 4.4 NI-9474 Digital Output Module (8- Channel)

# 4.4.5 CONTROLLER POWER SUPPLY (NI PS -15 POWER SUPPLY)

The function of this power supply is to power the CompactRIO controller and associated hardware devices. The nominal input of this power supply is 115/230V AC and the output is regulated 24VDC at 5A.

Fig. 4.5 NI PS-15 Power Supply

Fig. 4.6 shows the example of CompactRIO system assembly

Fig. 4.6 CompactRIO System

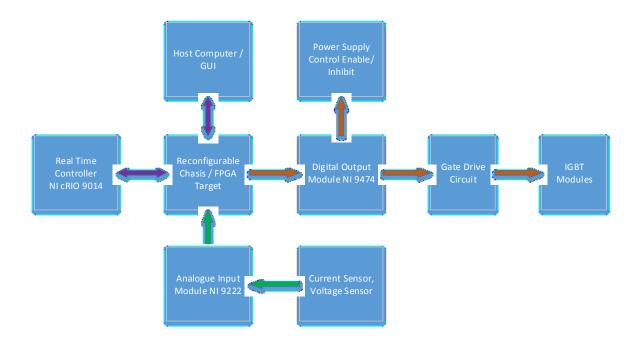

### 4.4.6 COMPACTRIO SYSTEM BLOCK DIAGRAM

Fig. 4.7 shows the overall block diagram of the entire system. The arrows shows the direction of data communication between various components of the system.

Fig. 4.7 System Block Diagram

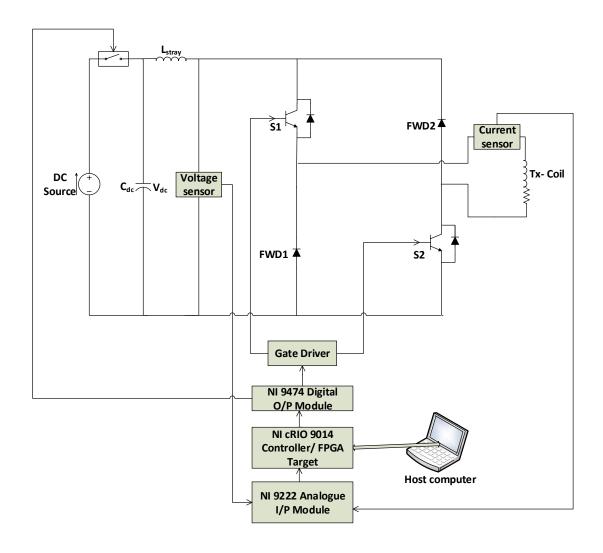

Fig. 4.8 shows the circuit diagram for the experimental setup, the RCD snubbers are omitted in this representation for better visualization of circuit components. As shown in

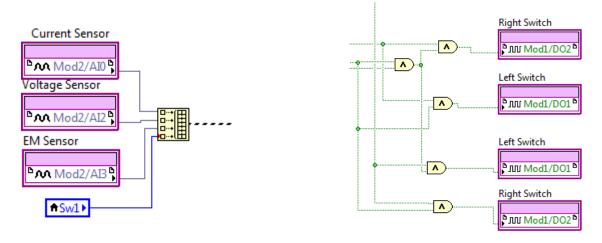

Fig. 4.8, NI 9222 input module is connected to two sensors i.e. current sensor sensing the Tx-coil current and voltage sensor sensing the DC capacitor voltage the same module can be used to connect the input from the Rx-coil sensing the EM response from the target. This input data is passed to the cRIO 9014 digital controller which is connected to the host computer for two way data communication. CRIO9014 executes the control logic in the FPGA target on reconfigurable chassis (FPGA code compiled in the host computer and downloaded to the FPGA memory).Based on the real time input and the control logic, the output control signals are sent to NI 9474 digital output module. There are three output channels used, two to provide the gating pulses to the IGBTs gate drive circuits based on the current control logic and one to enable or inhibit the DC Power Source based on the capacitor voltage level.

Fig. 4.8 Circuit Diagram- Experimental Setup

# 4.5 PROGRAMMING LOGIC IN LABVIEW

As mentioned earlier, the programming in LabVIEW environment mainly consist of two parts, the front panel and the block diagram. The front panel contains the indicators, control inputs and graphs associated with a block diagram code. A block diagram contains the code based on LabVIEW inbuilt functions blocks or nodes. Virtual Instruments (VIs) are the LabVIEW programs that are used for writing the application control logic. Each VI

has three main subparts – the front panel window, the block diagram and the icon/connector pane. The front panel window acts as the user interface for the VI. The front panel window may contains controls and indicators that interact with the VI to pass or receive the data. Block Diagram window is used to write the application code using graphical representation of functions to control the front panel objects. The block diagram window contains the graphical source code for an application. Front panel objects appear as terminals on the block diagram. The connector pane allows to use and view a VI in another VI as a sub –VI.

The LabVIEW program code for this application contains 2 main virtual instruments (VIs)

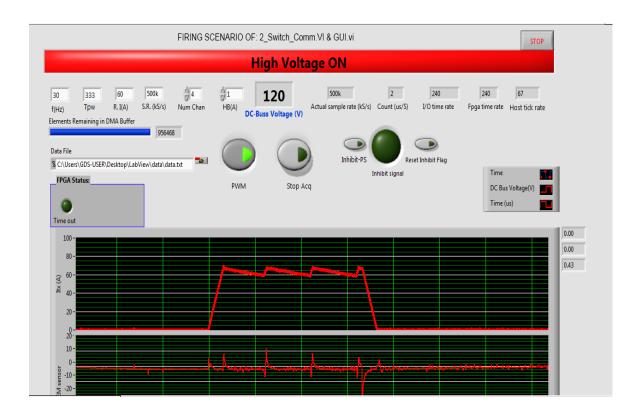

#### 4.5.1 GUI.VI

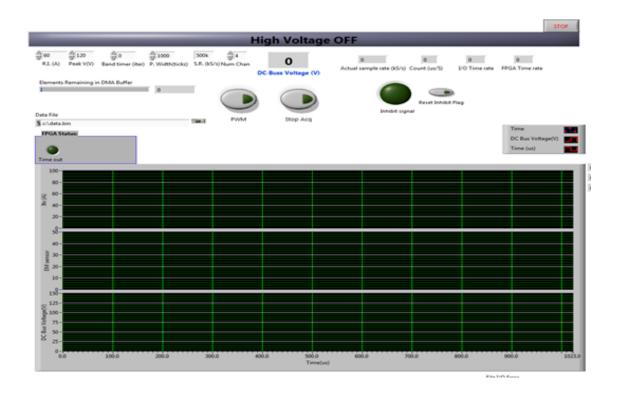

In this work, a separate GUI as shown in Figure 4.9, is created on the host computer to pass the user defined control parameters to the FPGA code (hysteresis current control). GUI shown in Fig. 4.10 is used for the application using constant ON-Time control. The parameters controlled through GUI are reference current, DC bus voltage, ON-time (Band timer), Pulse Width, Sampling Rate and No of channels read by DMA FIFO. Graphical user interface, GUI is also used to display the DC bus voltage, FPGA loop tick rate and actual sampling rate achieved during run time. Three buttons are created with individual function to start the firing of the converter switches, reset the power supply in case the Power Supply goes into inhibit state and to give a stop command to the data acquisition loop. A data file path selection window is provided to select the path where a data file

containing the acquired input data is saved for post processing. The waveform windows are used to show the current and voltage sensor run time waveforms. This data is passed from FPGA target to the host computer by using DMA FIFO as discussed in next section on data acquisition.

Fig. 4.9 GUI.vi Front Panel (Hysteresis Current Control)

Fig. 4.10 GUI.vi Front Panel (Constant ON-Time Control)

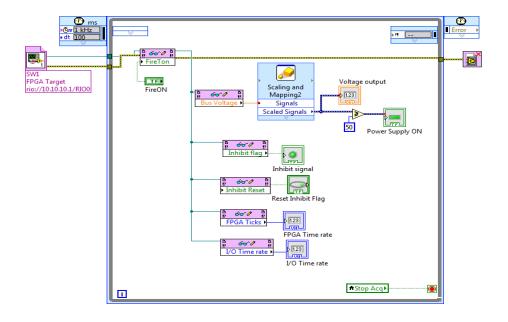

Fig. 4.11 shows the first part of the GUI block diagram that updates the indicators on the GUI front panel by reading their status from the FPGA Target.

Fig. 4.11 GUI.vi Block diagram (Indicators)

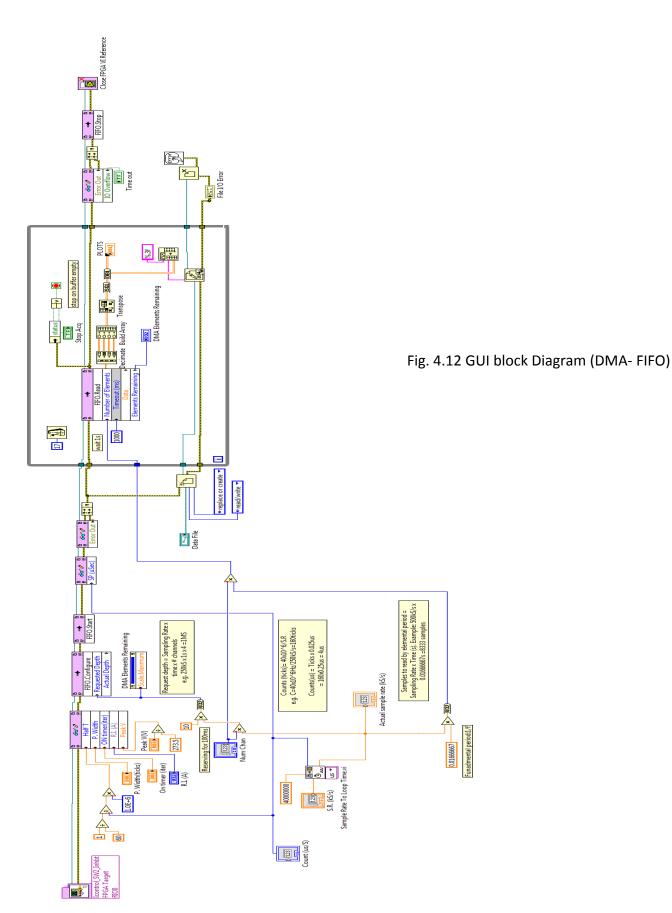

Fig. 4.12 shows the second part of the GUI block diagram where various control parameters are passed to the FPGA and also it contains the host side architecture for DMA FIFO to read the sampled data from analogue input module. The details of data transfer from FPGA to host are discussed in section 4.5.2

### 4.5.2 FPGA.VI (FPGA TARGET)

FPGA target contains the main code that controls the functioning of power converter.

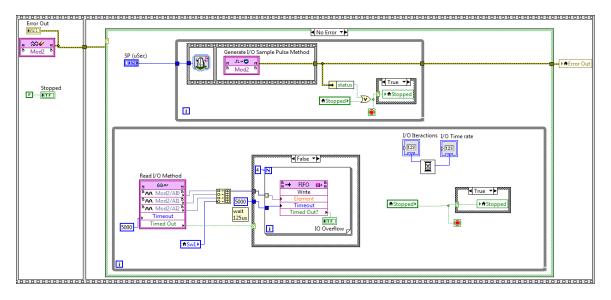

FPGA code is written in LabVIEW graphical language and is compiled and downloaded to the FPGA target on the reconfigurable chassis. The FPGA code for this application contains two major sub parts in terms of two while loops.

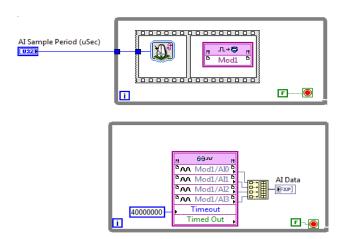

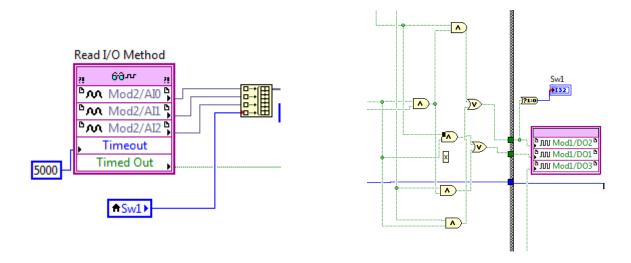

Data Acquisition Loop: The first loop as shown in Fig. 4.13 is the Data Acquisition Loop or DMA FIFO loop where the input data from NI 9222 analogue input module is transferred to the host machine. There are various ways to read the data from an input module. However to have a deterministic data reading and transfer from the input module , user-defined I/O sampling method is described as the best method .By using this method the maximum sampling rate as high as 500 KS/s can be achieved from an analogue input module (NI 9222 in this case). Other methods such as using FPGA I/O node results in a maximum sampling rate of 300 KS/s which results in underutilization of the hardware components. Fig. 4.14 and Fig. 4.15 shows the general architecture for FPGA I/O node and user- controlled I/O sampling to read the input module data.

Fig. 4.13 Data Acquisition using User Controlled I/O sampling on the FPGA target side

Fig. 4.14 Reading Input channels with FPGA I/O node

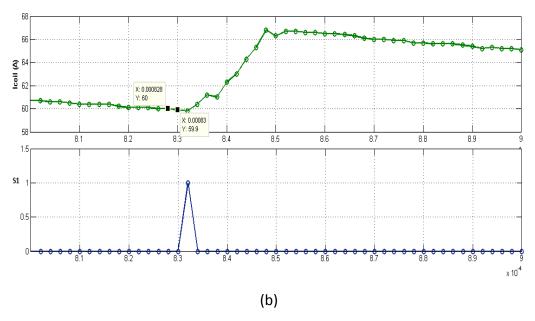

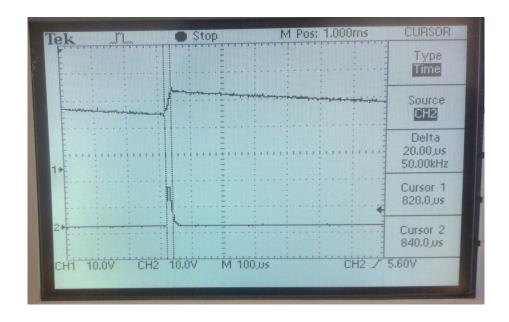

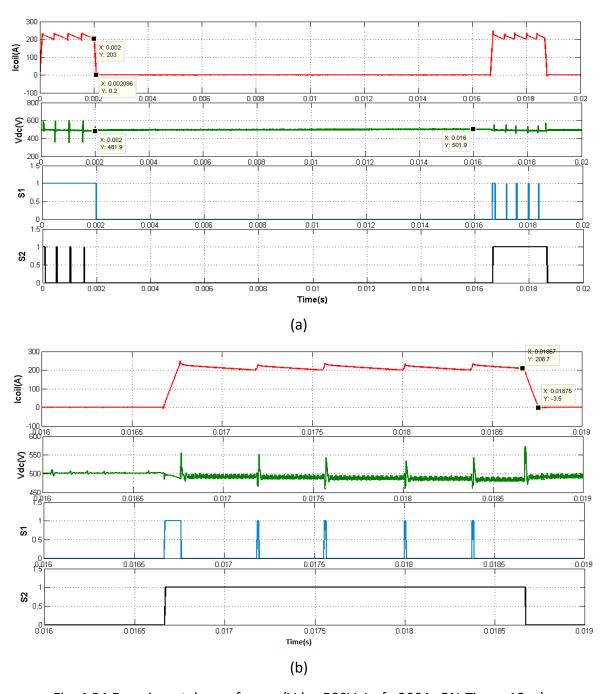

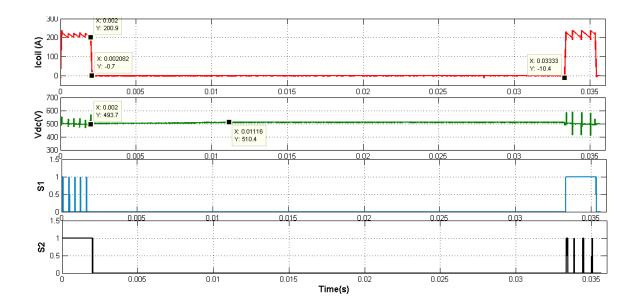

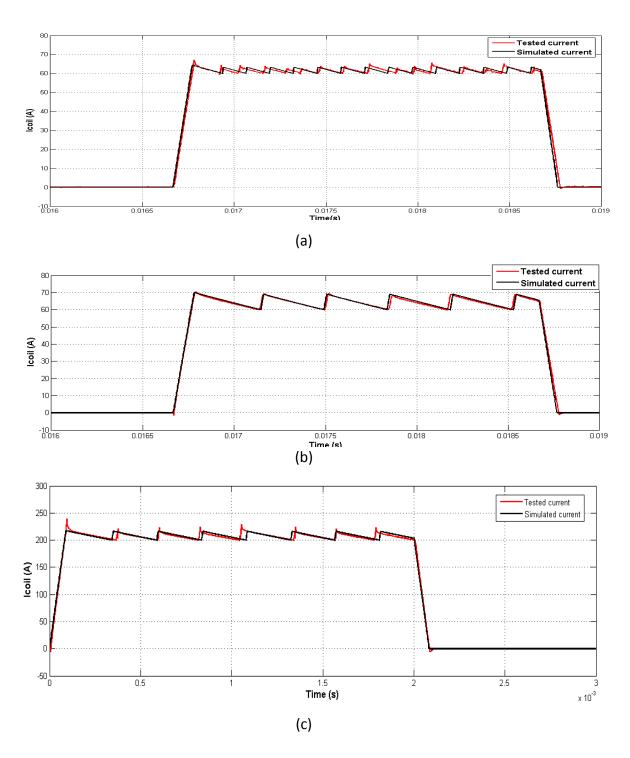

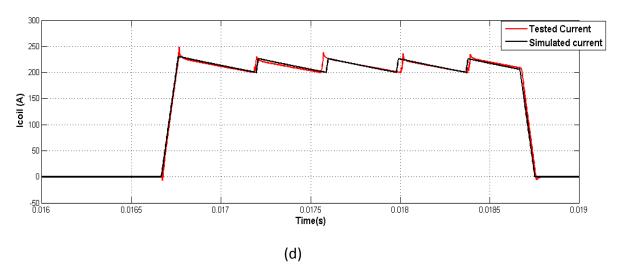

Fig. 4.15 User-Controlled I/O sampling