# **Toward the Implementation of Analog LDPC**

### **Decoders for Long Codewords**

### Shahaboddin Moazzeni

A Thesis

in The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering ) at

Concordia University

Montreal, Quebec, Canada

August 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-63105-8 Our file Notre référence ISBN: 978-0-494-63105-8

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### **AVIS:**

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### ABSTRACT

**Toward the Implementation of Analog LDPC Decoders for Long Codewords**

Shahaboddin Moazzeni

Error control codes are used in virtually every digital communication system. Traditionally, decoders have been implemented digitally. Analog decoders have been recently shown to have the potential to outperform digital decoders in terms of area and power/speed ratio. Analog designers have attempted to fully understand and exploit this potential for large decoders. However, large codes are generally still implemented with digital circuits. Nevertheless, in this thesis a number of aspects of analog decoder implementation are investigated with the hope of enabling the design of large analog decoders.

In this thesis, we study and modify analog circuits used in a decoding algorithm known as the sum-product algorithm for implementation in a CMOS 90 nm technology. We apply a current-mode approach at the input nodes of these circuits and show through simulations that the power/speed ratio will be improved. Interested in studying the dynamics of decoders, we model an LDPC code in MATLAB's Simulink. We then apply the linearization technique on the modeled LDPC code in order to linearize the decoder about an initial state as its solution point. Challenges associated with decoder linearization are discussed.

We also design and implement a chip comprised of the sum-product circuits with different configurations and sizes in order to study the effect of mismatch on the accuracy of the outputs. Unfortunately, testing of the chip fails as a result of errors in either the packaging process or fabrication.

### Acknowledgements

First of all I have to thank my supervisor Dr. Glenn Cowan who dedicated his precious time in sharing his novel ideas and encouraged me to accomplish this thesis. The idea of this work was initially introduced to me by him. Secondly, I am thankful to my cosupervisor Dr. Warren Gross from McGill University. I also want to make this point that I studied the concepts of analog decoding mostly from the Chris Winstead's PhD. dissertation and hereby I indirectly express my best gratitude to him.

I also appreciate two of my best friends, Mr. Alireza Rabbani and Frank Bernardo for their helpful suggestions and assistances especially in the design and implementation of the chip. I am also grateful to Mr. Tadeusz Obuchowicz in the VLSI lab of Concordia University and Mr. Dong (Hudson) An in the Mixed Signal Lab at McGill University.

This work was supported by the Faculty of Engineering and Computer Science at Concordia University, by the Natural Sciences and Engineering Research Council of Canada, by the Regroupement Stratégique en Microsystème du Québec, and by CMC Microsystems.

Finally, I dedicate this work to my parents and whoever else assisted me either physically or mentally.

# **Contents**

| List o  | f Fig | gures                                                          | ix  |

|---------|-------|----------------------------------------------------------------|-----|

| List o  | f Tal | bles                                                           | xii |

| 1. Inti | rodu  | ction                                                          | 1   |

| 1.1     | Ph    | ysical implementations of Analog Decoders                      | 4   |

| 1.2     | Co    | ontributions of the Thesis                                     | 10  |

| 1.3     | Or    | der of the Thesis                                              | 12  |

| 2. Err  | or-C  | Control Codes and Decoding Algorithms                          | 14  |

| 2.1     | Di    | gital communication channels                                   | 14  |

| 2.      | 1.1   | Soft and Hard decision algorithms                              | 15  |

| 2.      | 1.2   | Probability, Likelihood ratio and Log-likelihood ratio Domains | 16  |

| 2.      | 1.3   | The Shannon Capacity                                           | 17  |

| 2.2     | Liı   | near Block Codes                                               | 17  |

| 2.      | .2.1  | G and H matrices                                               | 18  |

| 2.      | 2.2   | Factor and Tanner graphs                                       | 19  |

| 2.3     | So    | me popular Error-Control Codes                                 | 21  |

| 2.      | 3.1   | Turbo Codes                                                    | 21  |

| 2.      | 3.2   | Low-Density Parity Check Codes                                 | 22  |

| 2.      | 3.3   | Block Turbo Codes                                              | 23  |

| 2.4     | Int   | roduction to Decoding Algorithms                               | 23  |

| 2.      | 4.1   | The sum-product algorithm                                      | 24  |

| 2.      | 3.2   | The min-sum algorithm                                          | 29  |

| 3. Ana  | alog  | sum-product circuits                                           | 31  |

| 3.1     | MO    | OS transistor operation regions                                | 32  |

| 3       | 1 1   | Strong inversion region                                        | 32  |

|                                                   | 1.2                                                 | Weak inversion region                                                                                                                                                                                                                                                                                                                       | 33                         |

|---------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.2                                               | The                                                 | e translinear principal                                                                                                                                                                                                                                                                                                                     | 34                         |

| 3.3                                               | The                                                 | e canonical sum-product circuits                                                                                                                                                                                                                                                                                                            | 35                         |

| 3.4                                               | Lo                                                  | w-voltage sum-product circuits                                                                                                                                                                                                                                                                                                              | 40                         |

| 3.5                                               | Des                                                 | sign procedure of the sum-product circuits                                                                                                                                                                                                                                                                                                  | 41                         |

| 3.5                                               | 5.1                                                 | Range of input and output currents                                                                                                                                                                                                                                                                                                          | 44                         |

| 3.5                                               | 5.2                                                 | Adjusting the reference voltages                                                                                                                                                                                                                                                                                                            | 46                         |

| 3.5                                               | 5.3                                                 | Accuracy of results at the extremes                                                                                                                                                                                                                                                                                                         | 47                         |

| 3.5                                               | 5.4                                                 | The effect of Mismatch.                                                                                                                                                                                                                                                                                                                     | 48                         |

| 3.6                                               | Str                                                 | ucture of the Chip                                                                                                                                                                                                                                                                                                                          | 51                         |

| 3.6                                               | 5.1                                                 | Blocks                                                                                                                                                                                                                                                                                                                                      | 52                         |

| 3.6                                               | 5.2                                                 | Voltage-to-Current converters                                                                                                                                                                                                                                                                                                               | 54                         |

| 3.6                                               | 5.3                                                 | Input and Output Switches                                                                                                                                                                                                                                                                                                                   | 55                         |

| 3.6                                               | 5.4                                                 | Digital circuit                                                                                                                                                                                                                                                                                                                             | 57                         |

| 4. App                                            | olica                                               | tion of Active Current Mirrors to Improve the Speed of                                                                                                                                                                                                                                                                                      |                            |

| Ana                                               | log                                                 | Decoders,                                                                                                                                                                                                                                                                                                                                   | 60                         |

|                                                   | -~8                                                 |                                                                                                                                                                                                                                                                                                                                             |                            |

| 4.1                                               |                                                     |                                                                                                                                                                                                                                                                                                                                             |                            |

|                                                   |                                                     | Large LDPC code                                                                                                                                                                                                                                                                                                                             | 61                         |

| 4.1                                               | 1.1                                                 | Large LDPC code  The input resistance of a current-mirror circuit                                                                                                                                                                                                                                                                           | 61<br>65                   |

| 4.1<br>4.1                                        | l.1<br>l.2                                          | Large LDPC code  The input resistance of a current-mirror circuit  Total delay in a block of equality nodes                                                                                                                                                                                                                                 | 61<br>65<br>69             |

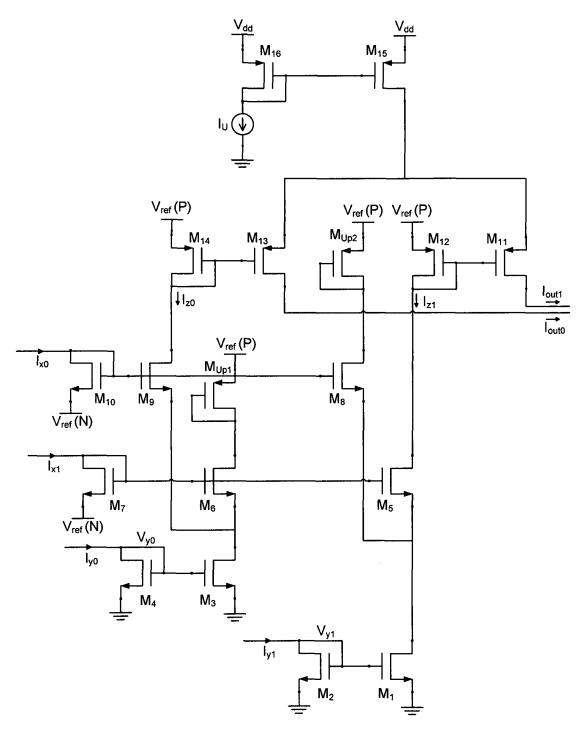

| 4.1<br>4.1<br>4.1                                 | 1.1<br>1.2<br>1.3                                   | The input resistance of a current-mirror circuit  Total delay in a block of equality nodes  Block of equality nodes with Boosted circuits                                                                                                                                                                                                   | 61<br>65<br>69<br>70       |

| 4.1<br>4.1<br>4.1<br>4.2                          | 1.1<br>1.2<br>1.3<br>Bloc                           | Large LDPC code  The input resistance of a current-mirror circuit  Total delay in a block of equality nodes  Block of equality nodes with Boosted circuits  ck of equality nodes with modified input current-mirrors                                                                                                                        | 61<br>65<br>69<br>70<br>71 |

| 4.1<br>4.1<br>4.2<br>4.2                          | 1.1<br>1.2<br>1.3<br>Bloc<br>2.1                    | The input resistance of a current-mirror circuit  Total delay in a block of equality nodes  Block of equality nodes with Boosted circuits  ck of equality nodes with modified input current-mirrors  Modified current-mirror circuit                                                                                                        | 61<br>65<br>69<br>70<br>71 |

| 4.1<br>4.1<br>4.1<br>4.2                          | 1.1<br>1.2<br>1.3<br>Bloc<br>2.1                    | The input resistance of a current-mirror circuit                                                                                                                                                                                                                                                                                            | 61 65 70 71 73             |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2            | 1.1<br>1.2<br>1.3<br>Bloo<br>2.1<br>2.2             | The input resistance of a current-mirror circuit.  Total delay in a block of equality nodes.  Block of equality nodes with Boosted circuits.  ck of equality nodes with modified input current-mirrors.  Modified current-mirror circuit.  Design of the OTA circuit in the modified current-mirror.  Calculation of the Power/Speed ratio. | 61 65 70 71 71 73          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2            | 1.1<br>1.2<br>1.3<br>Bloo<br>2.1<br>2.2             | The input resistance of a current-mirror circuit                                                                                                                                                                                                                                                                                            | 61 65 70 71 71 73          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3     | 1.1<br>1.2<br>1.3<br>Bloc<br>2.1<br>2.2<br>2.3      | The input resistance of a current-mirror circuit.  Total delay in a block of equality nodes.  Block of equality nodes with Boosted circuits.  ck of equality nodes with modified input current-mirrors.  Modified current-mirror circuit.  Design of the OTA circuit in the modified current-mirror.  Calculation of the Power/Speed ratio. | 61 65 70 71 73 75          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3     | 1.1<br>1.2<br>1.3<br>Bloo<br>2.1<br>2.2<br>Cor      | The input resistance of a current-mirror circuit.  Total delay in a block of equality nodes.  Block of equality nodes with Boosted circuits.  ck of equality nodes with modified input current-mirrors.  Modified current-mirror circuit.  Design of the OTA circuit in the modified current-mirror.  Calculation of the Power/Speed ratio. | 61 65 70 71 73 75          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.3<br>5. Non- | 1.1<br>1.2<br>1.3<br>Blood<br>2.1<br>2.2<br>Con-Lin | The input resistance of a current-mirror circuit                                                                                                                                                                                                                                                                                            | 61 65 70 71 73 75 77 79    |

| 5.2.2      | The issue of linearization point | 87  |

|------------|----------------------------------|-----|

| 6. Testing | the chip                         | 92  |

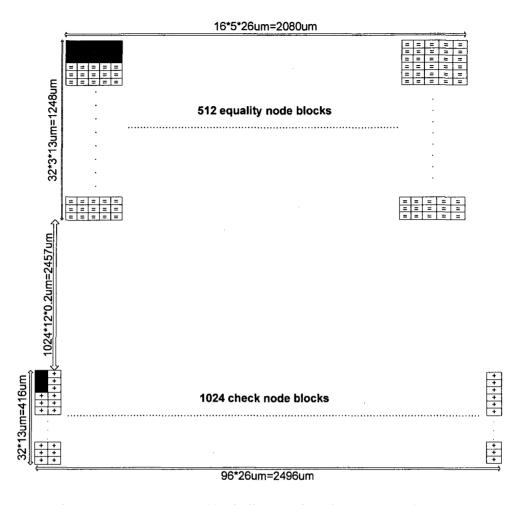

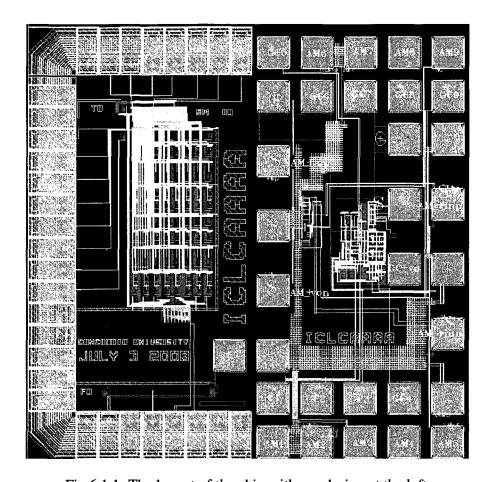

| 6.1 Th     | ne internal view of the Chip     | 92  |

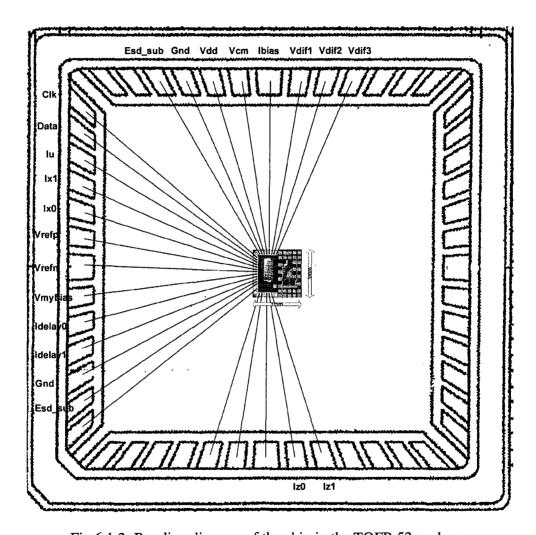

| 6.1.1      | Arrangement of the pins          | 94  |

| 6.1.2      | The Test plan                    | 96  |

| 6.2 Me     | easurement process               | 97  |

| 6.2.1      | Simple measurements              | 100 |

| 7. Conclus | The internal view of the Chip    | 102 |

| Bibliograp | phy                              | 106 |

# **List of Figures**

| Fig 2.1.1: A model for a digital communication system                                                                 |

|-----------------------------------------------------------------------------------------------------------------------|

| Fig 2.2.1: A simple factor graph corresponding to $f(x, y, z) = f_1(x, y, z) \cdot f_2(x, y, z) \cdot \dots \cdot 19$ |

| Fig 2.2.2: The normal graph of $f(x, y, z) = f_1(x, y, z) \cdot f_2(x, y, z) \cdot \dots 20$                          |

| Fig 2.2.3: The normalized Tanner graph for the presented <i>H</i> -matrix                                             |

| Fig 2.4.1: Function node and its associated constraint                                                                |

| Fig 2.4.2: Illustrating the sum-product algorithm; a) Step 2, b) Step 3                                               |

| Fig 3.1.1: Basic MOS transistor                                                                                       |

| Fig 3.2.1: A basic translinear loop                                                                                   |

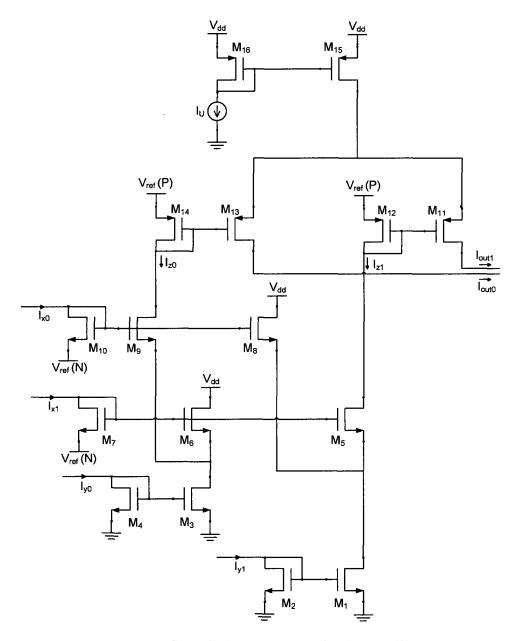

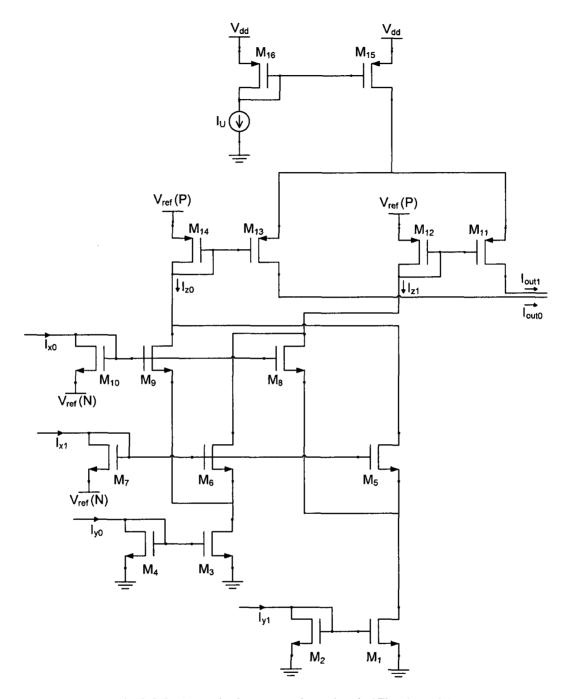

| Fig 3.3.1: Canonical sum-product circuit (Equality node)                                                              |

| Fig 3.3.2: Canonical sum-product circuit (Check node)                                                                 |

| Fig 3.4.1: Low-voltage equality and check nodes including the dummy transistors 41                                    |

| Fig 3.5.1: Symmetrical equality node by adding diode-connected PMOS loads                                             |

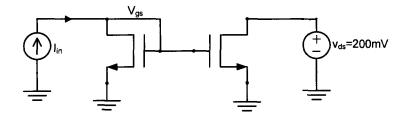

| Fig 3.5.2: Current-mirror circuit used to determine the range of input current                                        |

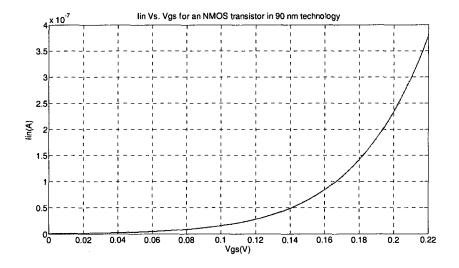

| Fig 3.5.3: Plot of $I_{in}$ versus $V_{gs}$ for an NMOS diode-connected transistor in 90 nm                           |

| technology with $W = 1.2 \mu \text{m}$ and $L = 1 \mu \text{m}$ of a current-mirror circuit where $V_{ds}$ for the    |

| second transistor has been set to 200 mV                                                                              |

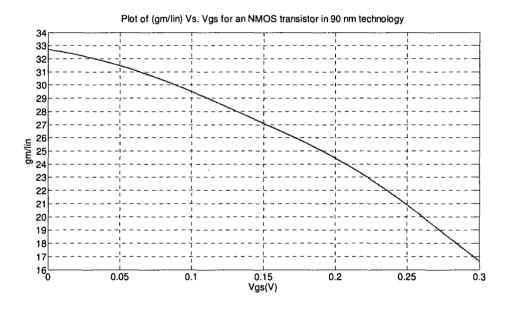

| Fig 3.5.4: Plot of $(g_m/I_{in})$ versus $V_{gs}$ for the diode-connected NMOS transistor with $W =$                  |

| 1.2 um and $L = 1$ um in 90 nm technology                                                                             |

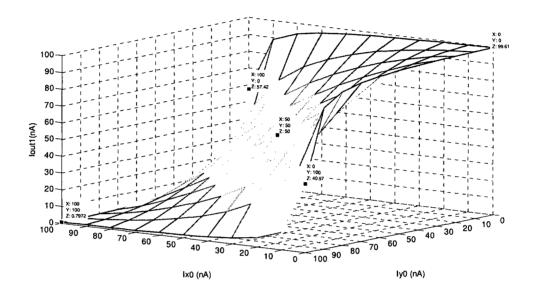

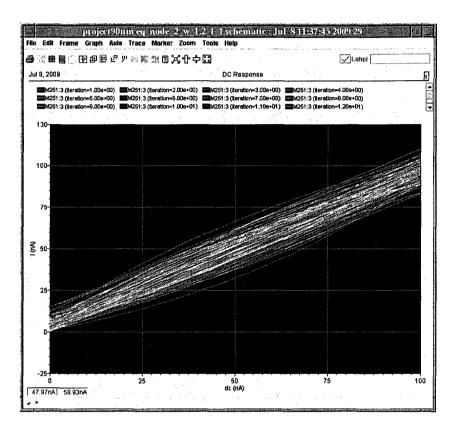

| Fig 3.5.5: Results of simulation for the output probability of 1 in the equality node when     |

|------------------------------------------------------------------------------------------------|

| the input probabilities of 0 are varied from 0 to 100 nA                                       |

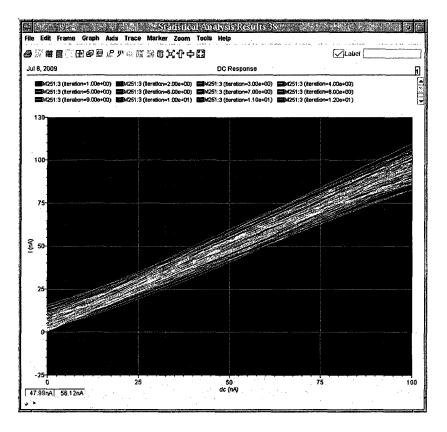

| Fig 3.5.6: Simulation results for 100 iterations of process variation and mismatch for the     |

| equality node with $\frac{W}{L} = \frac{1.2}{1}$                                               |

| Fig 3.5.7: Simulation results for 100 iterations of process variation and mismatch for the     |

| equality node with $\frac{W}{L} = \frac{2.4}{2}$                                               |

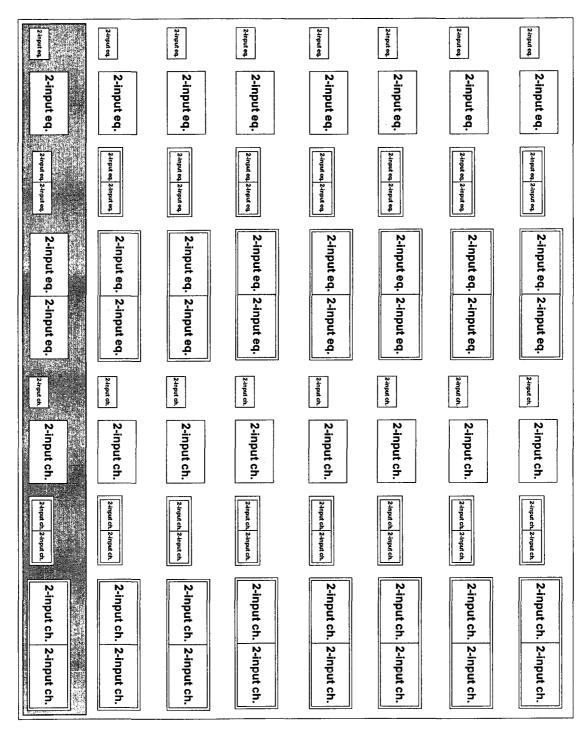

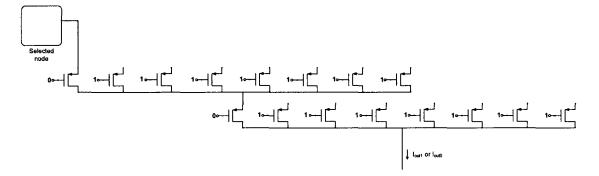

| Fig 3.6.1: Diagram of 8 similar blocks each containing 8 equality and check nodes with         |

| different topologies and sizes. Shaded area in a column indicates one of the 8 blocks 53       |

| Fig 3.6.2: A differential pair served as the voltage to current converter at the input 55      |

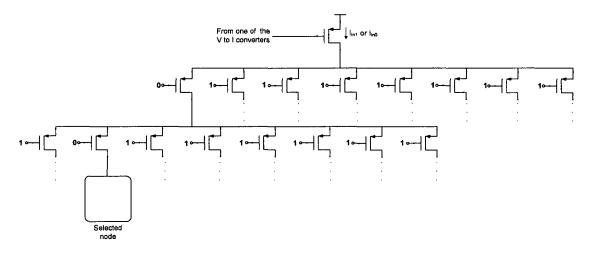

| Fig 3.6.3: Configuration of one set of input switches used to feed one of the inputs           |

| (probability of one or zero) which belongs to one of the 64 nodes in the chip 56               |

| Fig 3.6.4: Configuration of one set of output switches (probability of one or zero) coming     |

| from the output of one of the 64 nodes in the chip                                             |

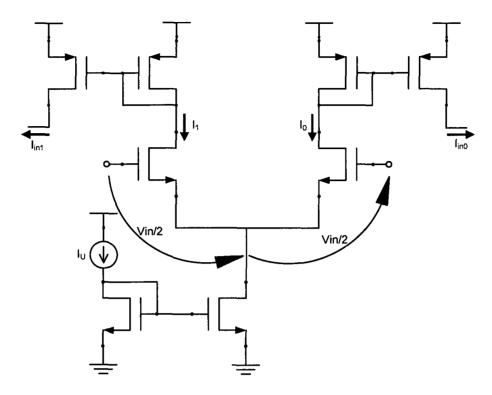

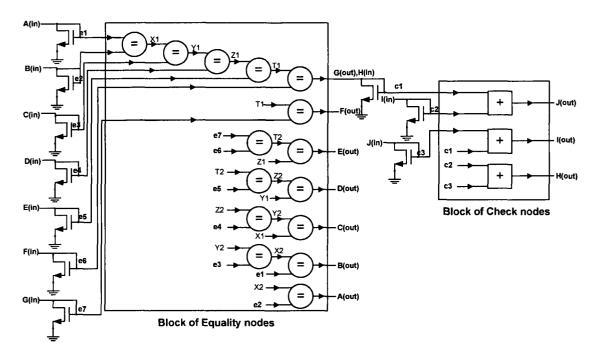

| Fig 4.1.1: Blocks of equality and check node for a large LDPC code and a sample                |

| connection between them                                                                        |

| Fig 4.1.2: Approximate block diagram for a large LDPC decoder                                  |

| Fig 4.1.3: Basic current-mirror circuit used at the inputs of an equality or check node with   |

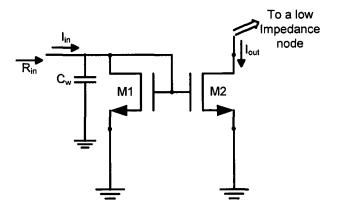

| the modeled wiring capacitance $C_w$                                                           |

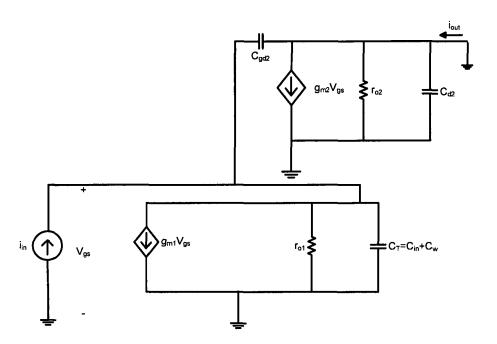

| Fig 4.1.4: Small signal circuit of the basic current-mirror                                    |

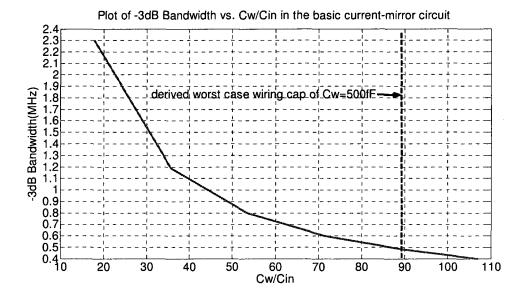

| Fig 4.1.5: Plot of -3dB Bandwidth vs. $C_w/C_{in}$ for the basic current-mirror circuit in the |

| equality node69                                                                                |

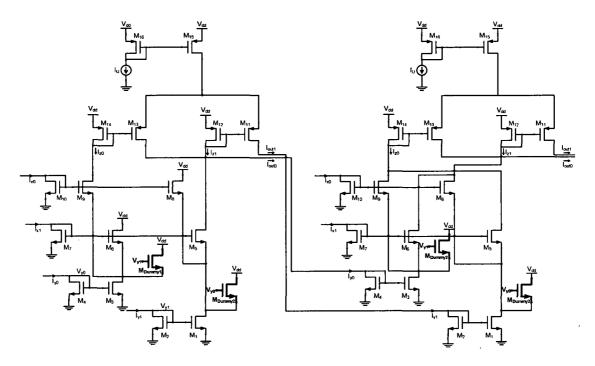

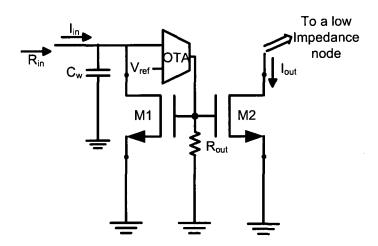

| Fig 4.2.1: Modified current-mirror circuit with the OTA feedback                               |

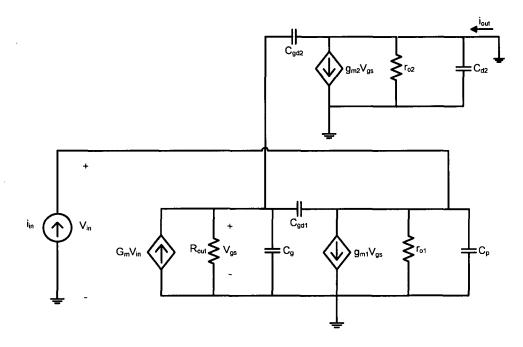

| Fig 4.2.2: Small signal circuit of the modified current-mirror                        |

|---------------------------------------------------------------------------------------|

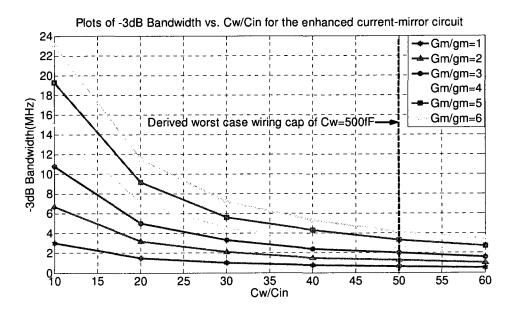

| Fig 4.2.3: Plots of -3dB Bandwidth vs. $C_w / C_{in}$ for the modified                |

| current-mirror circuit in the equality node                                           |

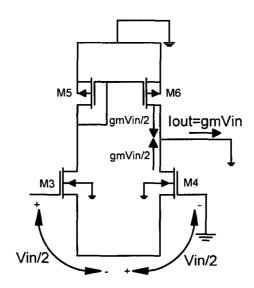

| Fig 4.2.4: Modified topology for the current-mirror circuit                           |

| showing the schematic of the OTA                                                      |

| Fig 4.2.5: Small signal analysis of the OTA circuit                                   |

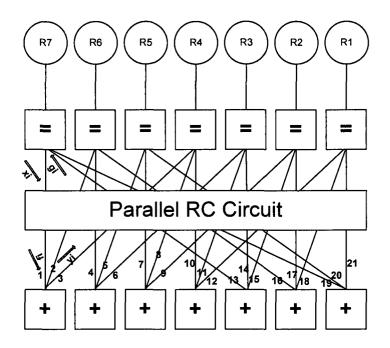

| Fig 5.1.1: Tanner graph for a regular LDPC code with the parallel RC delay circuit 81 |

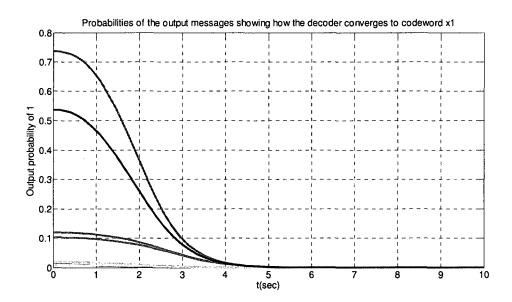

| Fig 5.1.1: Output probabilities of 1 for the simulated LDPC decoder showing the       |

| convergence to the zero codeword <u>x1</u>                                            |

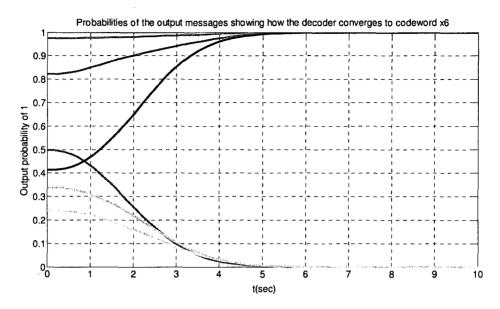

| Fig 5.1.2: Output probabilities of 1 for the simulated LDPC decoder showing the       |

| convergence to the zero codeword <u>x6</u>                                            |

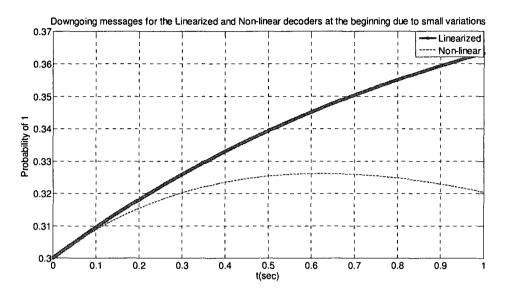

| Fig 5.2.1: Same slopes for the down going messages in linearized and non-linear       |

| decoders due to small variations of the input bits                                    |

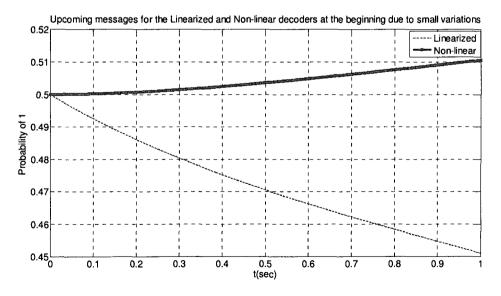

| Fig 5.2.2: Different slopes for the upcoming messages in linearized and non-linear    |

| decoders due to small variations of the input bits                                    |

| Fig 6.1.1: The layout of the chip with our design at the left                         |

| Fig 6.1.2: Bonding diagram of the chip in the TQFP-52 package                         |

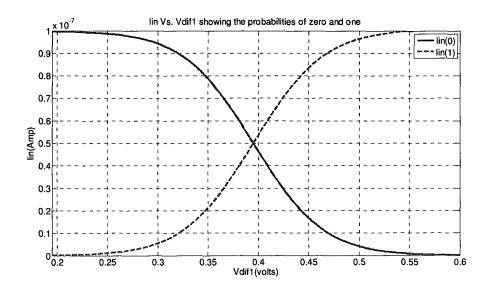

| Fig 6.1.3: Variations of the input currents with respect to Vdif1                     |

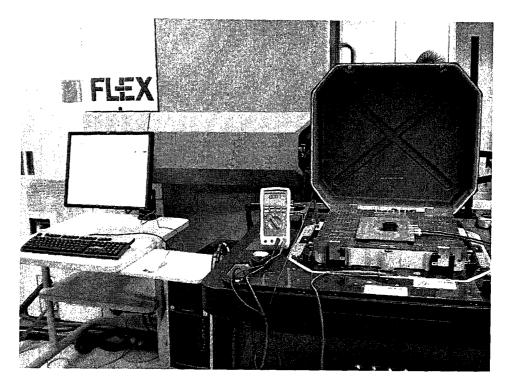

| Fig 6.2.1: The Mixed Signal Lab at McGill University                                  |

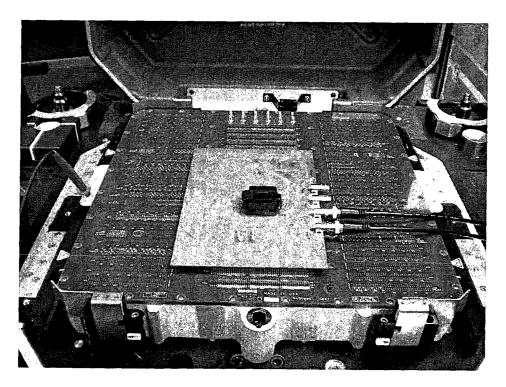

| Fig 6.2.2: The test board mounted on the Teradyne tester                              |

# **List of Tables**

| Table 1.1.1: Summary of published iterative Digital and Analog decoders                 | . 9 |

|-----------------------------------------------------------------------------------------|-----|

| Table 3.6.1: Input data and corresponding selected nodes                                | 57  |

| Table 4.2.1: Summary of results for the equality nodes block with the basic, boosted an | nd  |

| modified mirrors in a large (6,3) LDPC analog decoder                                   | 77  |

| Table 6.1.1: Area distribution of the chip                                              | 93  |

### Chapter 1

### Introduction

Error correcting codes play an important role in modern data transmission systems and digital communication channels including wireless, copper wire and also optical applications. The purpose of coding the information before transmitting them through a noisy channel is that we want to have a reliable set of information at the receiver. The reliability of the received bits or in fact the performance of any error control system depends on the complexity of the coding algorithm which is limited by the well-known statistical limit called the *Shannon Channel Capacity* [1]. Channel capacity is considered as the ultimate rate of communication [2]. There has been a lot of effort among designers to somehow achieve this limit by discovering new coding techniques.

One of the first error-controlling codes which can correct a significant number of errors due to the additive Gaussian noise channel is the *Turbo Code*. Once this code was discovered in 1993 [3], designers tried to produce other types of codes based on *Turbo codes*. They showed that there are other sorts of error controlling codes like Low Density Parity Check codes discovered by Gallager [4] and Block Turbo codes which achieve the performance fairly close to the Shannon Capacity [5, 6, 7, and 8].

In the implementation of decoders, designers have dealt with several issues such as complexity, power consumption, are and speed. A serially implemented decoder must

sequentially process each bit of information through the decoding procedure for many times to achieve good performance. In this way, *iterative* decoding would be time consuming and therefore high-speed decoding cannot be achieved. The frequency of clocking the data must be increased to obtain large data rates and this would burn more power. The concept of parallel implementation hence emerged as an alternative approach for performing high-speed iterated estimation of transmitted messages.

Parallel architectures have their own problems. However a very high speed decoding could be achievable as a result of the large parallel implementation. On the other hand it may require a lot of chip area due to the complexity of wiring in digital decoders which results in an increased fabrication cost and again high power consumption.

It was soon discovered that *Analog circuits* can resolve the issue of complexity in digital decoders since very difficult computations can be implemented by very simple analog circuits. However there would still be the same number of blocks in an analog decoder as in a digital decoder. For this reason, many researchers focused their research on analog decoders to eliminate the complexity and high power dissipation of digital circuits and to profit from the energy and area efficient advantages of analog decoders.

Since by its very nature decoding is non-linear [70], it involves non-linear analog circuits to implement decoding operations. Certain analog implementation of weak inversion transistors can be used to implement the required non-linear operation. Analog circuits in this region are in fact turned off and the drawn current from the circuit is very small.

Attracted to the new area of analog decoding, researchers were interested to explore and fully exploit their potentials. Analog Viterbi decoders [17], [18] were the first

constructed decoders which outperformed digital implementations by a wide margin [9, 10, 11, 12, and 13]. After Viterbi decoders, iterative codes such as Turbo codes [3], LDPC codes [4], [6] and similar codes [14], like Block Product codes [15] were implemented using analog iterative decoders [32, 37, 40, and 57].

In their investigations, researchers noticed that several important algorithms in the area of error-control coding, signal processing, and computer science can be explained as instances of a general algorithm which operates through message passing on a graph called a factor graph. This algorithm is called *the sum-product algorithm* [4], [21] and several soft-information algorithms such as the Bahl–Cocke–Jelinek–Raviv or (BCJR) algorithm [16] are shown to be instances of this general algorithm. The sum-product algorithm operates on *soft messages* which are described in terms of probability distributions [22, 23, 24, and 25].

Complexity in digital implementations of iterative Turbo codes and low-density parity check codes arises from the complexity of real-number arithmetic of sum-product modules. In contrast, once the sum-product algorithm is implemented with analog circuits, iterations no longer exist and the decoder will be considered as just a continuous-time network which stabilizes when a transmitted codeword has been detected.

Many works have been done in the area of analog decoding. However when compared to digital implementations of similar codes, analog decoders have demonstrated an evident superiority in terms of area and power consumption, yet one cannot find as large codes as have been constructed with digital circuits. The reason can be explained as follows. Since as mentioned before, most analog decoding circuits are composed of transistors that operate in weak-inversion mode (although there are analog decoders that

are not in subthreshold region), and by knowing the fact that in this mode, bandwidth is low due to the low drive currents of analog circuits, therefore the throughput (speed) of analog decoders is inherently low. Nevertheless designers have overcome this obstacle through *parallelism*.

A problem with parallel implementation is that the wirings between the modules of sum-product circuit become important. Since the number of sum-product circuit modules increases with the code length, wiring different modules that could be millimeters apart for a large code involves taking into account the unwanted wiring capacitances which will have significant effect on the throughput of decoder. Accordingly, any attempt in order to reduce this effect which corresponds to an increase in the *convergence* speed of the analog decoder would be valuable. One way to reduce the effect of long wires could be the use of buffers to feed the signals.

There are other reasons for not having very large analog codes including the effect of mismatch, lack of automation tools, imperfections of analog circuits and absence of reliable simulation tools for predicting throughput and performance of decoder.

### 1.1 Physical implementations of Analog Decoders

The earliest physical implementations of analog decoders appeared in 1998 when Hagenauer presented the first actual analog decoder [20]. In 1999 Lustenberger, Loeliger et. all published the results for the second fabricated chip [19]. Right after them, in 2000 Moerz, Hagenauer et. all published another real chip results [26]. In all these chips, bipolar junction transistors performed the decoding operation. However, they gave the idea in their papers that subthreshold design also would be possible.

In 2001, Chris Winstead et al. designed a fully-CMOS analog decoder chip [27]. In his thesis, he claimed that his chip has demonstrated micropower analog decoding in a standard CMOS process. In the same year Lustenberger reported a larger BiCMOS analog decoder which employed digital to analog converters at the input in order to simplify the testing however it failed to function correctly [28]. In 2001, again Chris Winstead fabricated a new design of analog decoder circuit including an array of serial to parallel sample and hold capacitors [29, 30].

Gaudet and et. al. were the pioneers in designing the first analog Turbo decoder in 2002 [31] which followed by a complete report for the implemented chip in 2003 [32]. Their Turbo code had a coded length of 48 bits and employed multiple serial input channels which made it possible for the decoder to perform well at higher speeds.

Exploiting the high speed characteristics of SiGe transistors, in 2002, Mores et. al. designed a very high speed analog decoder up to 10 Gbit/sec, however, it implemented a small, weak code [33]. One year later, Huang et. al. from the University of Virginia proposed a high speed SiGe analog Turbo decoder, but due to the failure in their digital-to analog converters at the input, their design was not successful [34,35].

In 2002, the work results of several research groups comprising of researchers at Torino, Padova, and ST Microelectronics led to a design of an analog Turbo decoder used for magnetic recording channels with a codeword length of 500 bits [36]. A revision of the aforementioned decoder was done by Amat et. al. in 2003 by implementing a standard Turbo decoder of 120 length. The fabricated design of this Turbo decoder which was the largest and best performing analog decoder until that date, was published in 2004 [37].

The other significant work on the implementation of analog decoding circuits was the 40 bit length CMOS analog Block Turbo decoder proposed by Perenzoni et. al in 2003 [38]. Their implemented decoder circuit used a serial analog input interface circuit and 16-bit digital output interface. It also included variable gain amplifiers (VGAs) in order to adjust the gain according to the signal to noise ratio of the channel.

Chris Winstead in collaboration with researchers at the University of Utah reported the measurement results for their analog Turbo product decoder in 2004 [30]. This decoder which had been already proposed in 2001 [24] showed a superior performance over known digital designs.

The concept of low-voltage analog decoder circuit took place in 2004 by Nguyen and other researchers at the University of Alberta [22] where for the first time, previously used high power supplies for analog decoders were replaced with the energy efficient power supplies of less than one volt. In the same year, Gioulekas, Birbas and Biliouis designed a low power high speed analog Turbo decoder as one of the first decoders in SiGe technology however to the author of this thesis it is unknown if the implementation results were successful [39].

In the recent years, the area of analog decoding has witnessed numerous valuable works. For instance, in 2005, Hemati and Banihasehmi demonstrated a CMOS analog Min-Sum iterative decoder for an LDPC code [40]. At that time all previously reported analog decoders were based on the exponential characteristic of bipolar or subthreshhold MOS transistors. The proposed circuit was capable of being used for strongly inverted CMOS analog decoders. The implementation results and error correcting performance of

the chip in steady state was close to simulation results based on continuous-time iterative decoding and exceeded that of conventional discrete-time decoding.

In 2006, Amat. et. al. and other prominent researchers in this field, proposed a fully analog iterative decoder for a serially concatenated, convolutional code [41]. Their proposed decoder was reconfigurable in both block length and code rate. They also reported the behavioural analysis as well as the impact of precision and mismatch on the performance of their decoder. Amat. et. al., Bendetto and others attempted a CMOS analog decoder for the block length 40 UMTS Turbo code in 2006 [42]. The implementation of the rate-1/3 UMTS turbo code is defined by the 3GPP standard. They also presented a discrete-time model of analog decoding networks which allows very fast simulations as well as predicting complex chip performance in very short time, however the latter has been verified through circuit-level simulations yet this model may give circuit optimization guidelines for complex analog decoder for which circuit-level simulations is impossible. In 2007, Winstead, Gaudet and Schlegel presented a technique for testing analog iterative decoders [43]. They employed digital circuit inside their chip as self-testing equipment which lowered the cost and the complexity compared to alternative mix signal built-in self test techniques. Although this technique was not feasible at the system level, they clearly showed that their decoder core was able to detect catastrophic errors in microseconds.

A novel semi iterative analog Turbo decoding algorithm and its corresponding 40 bits up to 2432 bits decoder architecture configurable were presented in 2007 by Mattieu Arzel and other researchers [44]. The proposed algorithm benefited from a partially continuous exchange of extrinsic information in order to improve decoding speed and

correction performance. They also showed that the on-chip area is one tenth of conventionally fully parallelized analog slice turbo decoder.

In 2008, the first integrated realization of a convolutional decoder employing the modified feedback decoding algorithm (MFDA) was presented by Billy Tomatsopoulos and Andreas Demosthenous [45]. The designed decoder uses an analog current-mode computational core and features low-complexity and low-power consumption. Chip measurements were successful and the authors claimed that this approach can be easily extended to the design of an all-analog, soft-decision convolutional decoder.

In order to estimate the performance of decoders including digital and analog, designers compare them in terms of size, speed, power and speed to power ratio which is consumed energy for a decoded bit. Table 1.1.1 summarizes the implemented or synthesized digital and analog iterative decoders from the earliest to very recent.

Table 1.1.1: Summary of published iterative Digital and Analog decoders

| Reference | Year | Analog/ | Decoding Type        | Code Length | Technology | Size   | Speed     | Power  | J/bit |

|-----------|------|---------|----------------------|-------------|------------|--------|-----------|--------|-------|

|           |      | Digital |                      |             |            | (mm²)  | (bit/sec) | (W)    |       |

| [47]      | 1995 | Digital | PCCC Turbo           | 2048        | 0.8µm      | 78.32  | 40M       | 1.6    | 160n  |

| [48]      | 2002 | Digital | 3GPP Turbo           | 5114        | 0.18µm     | 9      | 2.5M      | 306m   | 123n  |

| [49]      | 2002 | Digital | LDPC                 | 2048        | 0.16µm     | 52.5   | 1G        | 690m   | 690p  |

| [50]      | 2003 | Digital | 3GPP Turbo           | 5114        | 0.18µm     | 14.5   | 24M       | 1.45   | 60n   |

| [51]      | 2003 | Digital | PCCC Turbo           | 432         | 0.18µm     | 14.7   | 75.6M     | 657m   | 8.7n  |

| [52]      | 2004 | Digital | 3GPP Turbo           | 2048        | 0.13µm     | 1.07   | 5M        | 6.63m  | 1.3n  |

| [53]      | 2004 | Digital | 3GPP Turbo           | 5114        | 0.18µm     | 0.6    | 5M        | 63m    | 12.6n |

| [54]      | 2006 | Digital | TDMP LDPC            | 2048        | 0.18µm     | 14.3   | 640M      | 787m   | 1.23n |

| [55]      | 2007 | Digital | LDPC                 | 1024        | 90µm       | 5      | 3,2G      | -      | -     |

| [56]      | 2008 | Digital | LDPC                 | 1944        | 0.1µm      | 7.39   | 250M      | 76m    | 304p  |

| [19]      | 1999 | Analog  | Tailbiting BCJR      | 9           | 0.8µm      | 1.19   | 100M      | 50m    | 500p  |

| [26]      | 2000 | Analog  | Tailbiting BCJR      | 8           | 0.25µm     | 1.68   | 160M      | 20m    | 125p  |

| [27]      | 2000 | Analog  | Tailbiting BCJR      | 4           | 0.5µm      | 2.25   | 20M       | 3.33m  | 165p  |

| [32]      | 2003 | Analog  | PCCC Turbo           | 16          | 0.35µm     | 1.386  | 13.3M     | 185m   | 13.9n |

| [37]      | 2004 | Analog  | 3GPP Turbo           | 40          | 0.35µm     | 4.07   | 2M        | 7.6m   | 3.8n  |

| [30]      | 2004 | Analog  | Tailbiting BCJR      | 4           | 0.5µm      | 0.083  | 2M        | 1m     | 500p  |

| [22]      | 2004 | Analog  | Hamming Decoder      | 4           | 0.1µm      | 0.043  | 444K      | 283u   | 0.64n |

| [40]      | 2005 | Analog  | LDPC                 | 8           | 0.18µm     | 0.57   | 80M       | 5m     | 60p   |

| [57]      | 2005 | Analog  | Tailbiting BCJR      | 11          | 0.18µm     | 0.0266 | 135M      | 2.69m  | 20p   |

| [57]      | 2005 | Analog  | Turbo Product        | 121         | 0.18µm     | 2.85   | 1G        | 86.1m  | 86p   |

| [41]      | 2006 | Analog  | SCCC                 | Up to 2400  | 0.18µm     | 36     | 100M      | 40m    | 400p  |

| [42]      | 2006 | Analog  | UMTS Turbo           | 40          | 0.35µm     | 9      | 2M        | 10.3m  | 11.2n |

| [43]      | 2007 | Analog  | Hamming              | 4           | 0.18µm     | 0.138  | 3.7M      | 13m    | 3.5n  |

| [44]      | 2007 | Analog  | Semi iterative Turbo | Up to 2432  | 0.25µm     | 37     | 310K      | 12.48m | 40n   |

| [45]      | 2008 | Analog  | Convolutional  MFDA  | Up to 1024  | 0.6µm      | 0.5    | 1M        | 2.45m  | 2.45n |

From the table there is not a significant superiority in terms of chip area, total power consumption and power to speed ratio of the analog decoders compared to the digital decoders especially for large codes, yet analog implementation have the potential to excel the digital decoders in the mentioned aspects. That is ignoring the block length for a particular code, the analog designs outperform their digital counterparts in terms of size, power and power/speed by several orders of magnitude. However, there is still a limitation in the block length for the analog implementations due to the wiring complexity and the issue of speed. Most of the industrial applications deal with larger bit lengths (i.e. a few thousand). In order to remedy this problem some designers have attempted hardware solutions like reusing analog hardware and performing the interleaving in the digital domain [44], [46] and by doing so they significantly lowered the complexity of the component decoder.

#### 1.2 Contributions of the Thesis

The present work can be observed from two aspects. Firstly in this thesis, the basic circuits for an iterative analog de

coder based on the sum-product algorithm, which are equality and check nodes, have been redesigned in 90 nm technology. The original transistor-level design of such circuits is illustrated in [57]. After a complete study and a thorough survey on the designed circuits in 0.18 µm technology, the two circuits were resized for a new technology. In this survey, the effect of mismatch on the outputs of individual block with different sizing was also studied which followed by implementing a chip comprised of these circuits.

Apart from the chip design experience which can be considered as a physical contribution of this thesis, the main contributions of this thesis are the following theoretical contributions:

- Applying a technique used in current mode circuits to improve the speed of analog decoders. This technique can also be applied to other analog circuits for which the input impedance is quite high and therefore the speed is low. The input impedance of the equality and check nodes plays an important role in determining the decoding speed since as a result of wiring these circuits in a real decoder, large wiring capacitance can be added to the input nodes which may have a significant effect on the overall speed. Hence it seems essential to somehow lower this input impedance. It is shown in this thesis that current mode techniques can be applied to solve this issue.

- ➤ Having the dimensions for the layout of an individual equality and check node, the worst case wiring capacitance for the longest path in a large code has been estimated.

- Applying the linearization technique to a given LDPC decoder with intent to better study the dynamics of decoders. Thus far there has been no such analytical expression in the literature. It is assumed that by merely having the *H*-matrix for a particular code such as LDPC code and by modelling the interconnecting wiring capacitances as well as the input impedances of every block as RC circuits, one can write the linearized equations which is supposed to provide the required information regarding the dynamics of the system. In fact, the concept of statespace has been employed in the linearization of the non-linear LDPC decoder. It

turned out though that the initial state of the linearized decoder affects the decoding operation that is for the uniform probability mass as the initialization point the decoder fails to function properly. Initial states other than this point (expect other valid codewords which has not been studied in this work) would also mislead the decoding from its correct direction.

### 1.3 Order of the Thesis

Chapter 2 of this thesis gives a brief review on the fundamental of error-control coding and decoding algorithms in a digital communication channels including the principle definitions and basic theorems of coding theory. The tanner graph is also presented as a graphical representation of codes which is used to satisfy the parity check constraints between the bits of a codeword. An introduction to typical decoding algorithms including the sum-product and min-sum algorithms is given. Furthermore, a summary of the known error-controlling codes such as Turbo codes, LDPC codes and Block Turbo codes is presented. The structure of regular and irregular LDPC codes is discussed and a general mathematically-graphically described procedure for decoding LDPC codes based on the sum-product algorithm is presented.

In Chapter 3, translinear circuits and principles of CMOS translinear circuits are introduced. Two fundamental nodes for realizing the sum-product algorithm or the canonical CMOS sum-product circuits (equality and check nodes) are shown. The modified circuits of equality and check nodes for an LDPC decoder based on Winstead's thesis [57] in 90 nm technology are presented. The author has already designed and implemented a chip comprising various configurations for the equality and check nodes

with different transistors sizes to observe the effect of mismatch on the performance of these nodes. However, the chip failed to work properly due to possible problems in layout, packaging bounding, etc.

Chapter 4 presents a technique which is normally used in current mode circuits to improve the speed of analog decoders. This approach is in fact a modified current-mirror circuit with an OTA in feedback used to lower the high input impedance of basic current-mirrors in the circuits of analog decoder thereby improving the speed.

In Chapter 5, the author simulates an LDPC decoder in the MATLAB by expressing the parity equations of its *H*-matrix and by taking into account the delay between the nodes of the corresponding factor graph. Moreover by applying the linearization technique for non-linear systems, it is attempted to linearize the LDPC decoder around a linearization point. The idea of linearization finally results in a failure due to a problem with the initialization point which is illustrated thoroughly at the end of this chapter.

Chapter 6 presents the test plan for the implemented chip which is already introduced in Chapter 3 and explains what simple measurements suggested that something is not right with the chip. Finally, Chapter 7 gives conclusions and proposes future work.

## Chapter 2

## **Error-Control Codes and Decoding**

## **Algorithms**

### 2.1 Digital communication channels

Any digital communication channel is prone to be corrupted by noise. Thus the receiver should have the capability to somehow detect and correct the errors. An error-control decoder is one of the important components in a digital receiver which is used to perform this task.

Typically the transmitting device encodes data by adding parity-check information. If we assume the number of data bits as k, the encoder would add-up n-k parity bits so that the total number of encoded bits of information becomes n. This encoded information is then sent through a channel to the receiving device. Due to the noisy structure of the channel, the receiving information will no longer be the same as the original one. For example, in an additive white Gaussian noise (AWGN) channel which is of great interest in communication systems, the received message at the receiver is the original distinct bits of information plus a zero-mean, Gaussian distributed noise, thus a decoder is employed in this system to generate a good estimation of the original encoded

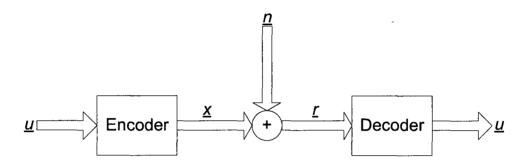

information message. Fig 2.1.1 depicts a model for a digital communication system where  $\underline{u}$  and  $\underline{x}$  represent the information and encoded messages respectively,  $\underline{n}$  is the additive noise of the channel and  $\underline{r}$  is the channel observation by the receiver. The complete model of a communication system may include some extra components such as a modulator and a demodulator at the transmitter and the receiver sides respectively, however they are not included in our discussion.

Fig 2.1.1: A model for a digital communication system

In order to have an estimation on the channel observation  $\underline{r}$ , two types of error-control algorithms can be employed; *soft-decision* and *hard-decision* algorithms which will be studied here.

### 2.1.1 Soft and Hard decision algorithms

In a hard decision algorithm, a decoder must judge on every single bit after digitizing the received data from the channel. In other words, error detection in this kind of receiver will be made after an analog to digital conversion has been done on the received analog information with one bit of resolution.

Unlike hard decision algorithm, the soft decision algorithm either use more than one bit of resolution or keep the analog nature of  $\underline{r}$ , while translating the analog information into probability format. The decoder could detect the error by performing probability calculations on these soft information bits.

### 2.1.2 Probability, Likelihood ratio and Log-likelihood ratio Domains

In soft decision receivers, there are three main distinct domains in which decoding is defined; *probability*, *likelihood* and *log-likelihood* domains.

In the probability domain, information bits are treated as zero and one probabilities of  $p_0$  and  $p_1$  respective for performing probability calculation in the soft decision algorithm. The ratio of  $\frac{p_0}{p_1}$  for every bit is defined as the likelihood ratio (LR) and this representation domain is called the likelihood ratio domain. Finally, the Napierian logarithm of the likelihood ratio  $\ln(\frac{p_0}{p_1})$  is presented in the log-likelihood ratio (LLR) domain. The application of each of these domains will be discussed later in the thesis.

Let's consider antipodal transmissions such as *Binary Phase-Shift Keying* (BPSK) modulation in an *Additive White Gaussian Noise* (AWGN) channel. Each element of  $\underline{r}i$  would then have a Gaussian distribution with mean  $\pm 1$  and variance  $N_0/2$ , where  $N_0$  is the power density of the channel's noise. Then it can be shown that the log likelihood ratio (LLR) for the received sample  $\underline{r}i$  has the following equation [57].

$$\ln(\frac{p_{-1}}{p_1}) = \frac{4}{N_0} r_i = X_i \tag{2.1.1}$$

LLR and probability representation domains are related to each other by the following equations:

$$p_{-1} = \frac{e^{X_i}}{1 + e^{X_i}} \tag{2.1.2}$$

$$p_1 = \frac{e^{-X_i}}{1 + e^{-X_i}} \tag{2.1.3}$$

### 2.1.3 The Shannon Capacity

In communication theory, the *Shannon capacity* or the *Shannon limit* is presented as a statistical limit for the transmission rate of a specific channel. Claude Shannon showed in 1948 that in order to achieve a reliable transmission over a noisy channel by employing error-control codes, the transmission rate of information bits should not be greater than the channel's capacity which is called the Shannon limit [58]. The performance of error-control codes are preferred to be close to this limit. Turbo codes and LDPC codes are known as Shannon capacity approaching codes.

### 2.2 Linear Block Codes

A linear block code refers to a block code which is defined in a linear space. For example if  $\underline{x}_1$  and  $\underline{x}_2$  are two different codewords in the space of a linear block code,  $\underline{x}_3 = \underline{x}_1 + \underline{x}_2$  also belongs to this space. Here, we limit our discussion to binary linear block codes for which the addition is defined in the binary domain. Even number of 1's add up to 0 while odd number of 1's in binary addition gives 1.

#### 2.2.1 G and H matrices

Based on the communication system model presented in Fig 2.1.1, an encoder is located at the transmitter side in order to convert binary vector  $\underline{u}$  to another binary vector  $\underline{x}$  in the linear code space. For this reason a Generator matrix or G-matrix is used to map the uncoded vector u to a codeword.

If  $\underline{u}$  is a  $1 \times k$  binary vector and G is a  $k \times n$  matrix where n is the number of bits in a codeword, then the matrix product would form a  $1 \times n$  codeword vector  $\underline{x}$  in the new space.

$$\underline{x} = \underline{u}. G \tag{2.2.1}$$

The coding procedure is done by adding parity bits to the input bits in a logical manner which also defines the *code rate* for specific coding algorithm. The term code rate or information rate is defined by ratio of the non-redundant bits of information to the total bits of information. For example if the code rate is k/n, the code generator may generate a total of n bit of data where only n-k of them are redundant.

At the receiver, we need to recover the original bits of information  $\underline{u}$ . Thus, a decoder must detect the errors caused by the channel noise and perform the best estimation on the received bits. *Parity check matrix* or *H-matrix* for the a linear block code is defined based on G matrix and satisfies  $G.H^T = 0$ . Therefore, for any codeword  $\underline{x}$  we must have

$$\underline{x}.H^T = 0 \tag{2.2.2}$$

In order to find the transmitted codeword, several algorithms have been presented which will be discussed in Section 2.3.

### 2.2.2 Factor and Tanner graphs

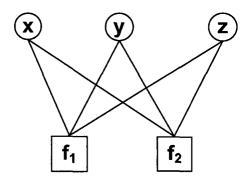

One common way to graphically represent the linear space of codewords is through factor graphs on which the Boolean constraint functions are satisfied. Below a simple factor graph for the following constraint is shown.  $f(x, y, z) = f_1(x, y, z) \cdot f_2(x, y, z)$  has been presented through its factor graph in Fig 2.2.1. It is observed that a factor graph is comprised of two distinct nodes; variable nodes and constraint nodes which are located at the top and at the bottom respectively. They are also intermediate lines called edges which connect different nodes of the graph based on the constraint functions.

Fig 2.2.1: A simple factor graph corresponding to  $f(x, y, z) = f_1(x, y, z) f_2(x, y, z)$

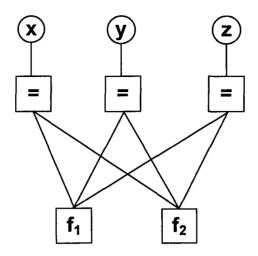

By convention, variable nodes are preferred to be connected to only one constraint node. In order to satisfy this rule, we modify the factor graph by adding new constraint nodes called the equality nodes such that there will be only one edge between each variable node and its corresponding equality node. This new graphical representation is called a *Normal graph* [59] and is depicted in Fig 2.2.2.

Fig 2.2.2: The normal graph of  $f(x, y, z) = f_1(x, y, z).f_2(x, y, z)$

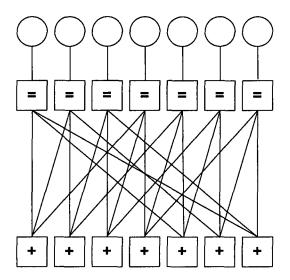

If the parity-check equation for a binary block code is presented through the factor and the normal graph, we will come up with new graphical representations called a *Tanner graph* and a *Normalized Tanner graph* respectively. Since for a codeword  $\underline{x}$  to be verified by the decoder,  $\underline{x}.H^T = 0$ , the Tanner graph will be the constraint graph for H. For instance assume that a parity check matrix H is as below:

$$H = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 0 & 1 \\ 1 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}$$

It turns out that there are seven parity check equations for this *H*-matrix which are derived by multiplying every row of  $\underline{x}$  by  $H^T$ . For example the first equation which corresponds to the first row of *H* or the first column of  $H^T$  would be  $\underline{x}_1 + \underline{x}_2 + \underline{x}_4 = 0$ . This implies that constraint nodes at the bottom of the Tanner graph should be replaced by binary addition or Exclusive-OR nodes since we deal with only 0 and 1 bits in

communication systems. These parity nodes whose function is to check the parity equation are known as *check nodes*. The corresponding normalized Tanner graph for the above *H*-matrix has been shown in Fig 2.2.3.

Fig 2.2.3: The normalized Tanner graph for the presented *H*-matrix

### 2.3 Some popular Error-Control Codes

In this section some of the widely used error-control codes will be briefly presented.

#### 2.3.1 Turbo Codes

The introduction of the original turbo codes has been as early as 1993 when *Parallel Concatenated Convolutional Codes* (PCCC) was presented [3]. After that many other classes of turbo code were discovered including Serially Concatenated Convolutional Codes and Repeat-Accumulate Codes [41].

One of the most significant advantages of turbo codes is that as stated earlier, this code together with LDPC code has the closest performance to the Shannon limit. However, relative high decoding complexity as well as the inevitable latency due to wiring of such codes could make them inappropriate for very fast applications.

### 2.3.2 Low-Density Parity Check Codes

Low density parity check codes or LDPC codes are a class of large linear block codes. The name of low density comes from the fact that the density of 1s is small in comparison with the number of 0s in the *H*-matrix. In other words, they have a sparse parity check matrix.

These codes were first introduced by Gallager in his PhD thesis in early 1960s [4]. But due to the complicated computations required to implement the decoder and encoder for such codes, LDPC codes were forgotten for a few decades. It was not until the work of MacKay [6], that the full potential of these powerful codes became well-known. Basically, there are two different methods to represent LDPC codes; *matrix and graphical representations*.

The very first LDPC codes were introduced through their parity check matrices by Gallager. Based on [62], a Gallager code (LDPC code) is defined by (dv,dc) where dv is the number of 1s in every column and dc is the number of 1s at each row of the parity check matrix. For an  $(m \times n)$  parity check or H-matrix, if n represents the code length, then the number of rows m can be found from m = ndv/dc if and only if it is a regular LDPC code, otherwise it is an irregular LDPC code. The  $(7 \times 7)$  H-matrix example in Section 2.2.1 is the matrix representation for a 7-bits length regular LDPC decoder for

which dv and dc are both equal to 3. The iterative message passing decoding or the sumproduct algorithm which will be presented later can be directly applied to the graphical representation or the Tanner graph of LDPC codes.

#### 2.3.3 Block Turbo Codes

There are other types of error-control codes in the literature such as *Block Turbo Codes* (BTC), which are also known as *Block Product Codes*. These sorts of codes have a two-dimensional construction including simple linear block codes. BTC is iterative in nature, which is why the term Turbo has been used for it. Their codeword is comprised of row codes and column codes which finally results in a rectangular codeword structure. Another thing to know about BTCs is that since they are comprised of simple block codes, they are easy to construct. Moreover, some BTCs with very short block lengths have been shown to approach the Shannon limit while other iterative codes such as LDPC codes need to be significantly larger to approach this limit [57].

### 2.4 Introduction to Decoding Algorithms

Among various algorithms, we are interested in two common algorithms which operate on factor or Tanner graphs. They are namely the *sum-product algorithm* and the *min-sum algorithm* which will be studied in this section.

### 2.4.1 The sum-product algorithm

One of the well-known decoding algorithms which has been widely used by designers is the sum-product algorithm [21]. Since the functionality of this algorithm is based on probabilities which are also known as soft messages or beliefs, it is often referred to probability algorithm. Shannon capacity approaching codes such as Turbo and LDPC codes are often decoded based on this algorithm.

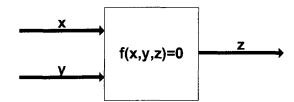

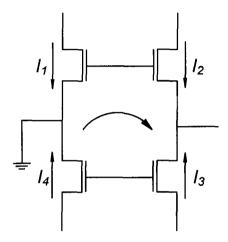

Most sum-product factor graphs are comprised of nodes each having three edges. Nodes with more than three edges can be replaced with the cascade of several nodes having only three edges. More than three edges nodes can be modified to the cascade of several three edges nodes. The sum-product algorithm computes the overall conditional probabilities by calculating or processing local constrains at every node iteratively. That means for every single equality node or check node in a sum-product circuit, local processing should be performed in order to satisfy the specific constraint related to that node. If we assume a three-edge node having two inputs x, y and one output z as shown in Fig 2.4.1, the local constraint associated to this node would be f(x, y, z) = 0.

Fig 2.4.1: Function node and its associated constraint

In a factor or Tanner graph of the sum-product algorithm, the function of equality and check nodes must be defined in the three aforementioned domains. If  $P_1$  and  $P_0$  denote

the probabilities of one and zero for every edge of the graph in probability domain, the equality node is defined as

$$P_{0z} = \eta P_{0x} P_{0y} \tag{2.4.1}$$

$$P_{1z} = \eta P_{1x} P_{1y} \tag{2.4.2}$$

where  $\eta$  is a positive constant for which  $P_{0z} + P_{1z} = 1$  and thereby  $\eta = \frac{1}{P_{0x}P_{0y} + P_{1x}P_{1y}}$ .

And for a check node we have

$$P_{0z} = P_{0x}P_{0y} + P_{1x}P_{1y} (2.4.3)$$

$$P_{1z} = P_{1x}P_{0y} + P_{0x}P_{1y} (2.4.4)$$

If we substitute  $\frac{P_0}{P_1}$  of every edge by Y in the likelihood ratio domain, the above equations

can be rewritten as:

$$Y_{z} = Y_{x} \times Y_{y} \tag{2.4.5}$$

for the equality nodes and

$$Y_{z} = \frac{1 + Y_{x}Y_{y}}{Y_{x} + Y_{y}} \tag{2.4.6}$$

for the check nodes.

Similarly by replacing  $\ln(\frac{P_0}{P_1})$  with X in the log-likelihood ratio domain, one will arrive

at the following expressions for equality and check nodes respectively.

$$X_z = X_x + X_y (2.4.7)$$

$$X_z = 2 \tanh^{-1} (\tanh(X_x/2) \times \tanh(X_y/2))$$

(2.4.8)

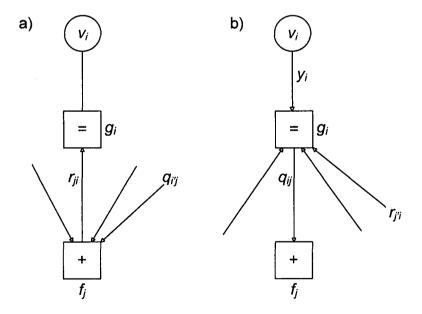

So far we have defined the local constraints for the two function nodes (i.e. equality and check nodes). Before presenting the algorithm lets introduce some notation.

- Variable nodes and received messages are denoted as  $v_i$  and  $y_i$  respectively.

- The equality nodes are presented as  $g_i$  while the check nodes are indicated as  $f_j$ .

- Probability of the received information bits through variable nodes is shown as Pi which is equal to the probability of individual variable node provided that the particular  $y_i$  has been received by that node. Thus we can use the following notation for Pi as the probability of being one at the input:  $Pi = P(v_i = 1 | y_i)$ .

- Down going messages from the equality node  $g_i$  to the check node  $f_j$  is labeled as  $q_{ij}$ .

- Upcoming message from check node  $f_i$  to equality node  $g_i$  is denoted as  $r_{ii}$ .

Fig 2.4.2: Illustrating the sum-product algorithm; a) Step 2, b) Step 3

The sum-product algorithm can be described through following steps:

- 1. All variable nodes and their subsequent equality nodes send their  $q_{ij}$  messages to the corresponding check nodes. Since this is the first iteration of the algorithm and no information other than the probabilities of received bits are available, therefore  $q_{ij}(1) = P_i$  and  $q_{ij}(0) = 1 P_i$ . Note that even if the initially received information bits from the channel form a valid codeword, they should be passed down to the check nodes since no hard decision can be made as this point.

- 2. Once all the check nodes receive  $q_{ij}$  messages, they calculate their response messages  $r_{ji}$  back to the equality nodes. For a three-edge check node  $(f_j)$ , we assume  $q_{1j}$  and  $q_{2j}$  each including the probabilities of zero and one as the two inputs coming from different equality nodes. The output probability of zero  $r_{ji}(0)$  which goes back to the corresponding equality node  $(g_i)$  can be found based on (2.4.3) as:

$$r_{ii}(0) = q_{1i}(1)q_{2i}(0) + q_{1i}(0)q_{2i}(1)$$

(2.4.9)

If in the above equation we replace  $q_{1j}(0) = 1 - q_{1j}(1)$  and  $q_{2j}(0) = 1 - q_{2j}(1)$ , one would end up with the following formula:

$$r_{ji}(0) = \frac{1}{2} + \frac{1}{2}(1 - 2q_{1j}(1))(1 - 2q_{2j}(1))$$

(2.4.10)

Consequently for check nodes with more than two edges (2.4.10) can be extended as:

$$r_{ji}(0) = \frac{1}{2} + \frac{1}{2} \prod_{i \in f, \lambda i} (1 - 2q_{i'j}(1))$$

(2.4.11)

and

$$r_{ii}(1) = 1 - r_{ii}(0)$$

(2.4.12)

Equations (2.4.11) and (2.4.12) compute the returning messages to the equality node  $g_i$  by calculating sum of the products for all  $q_{i'j}$ 's except  $q_{ij}$  which has also been illustrated in Fig 2.4.2a.

3. At this point, two updates must be done. Firstly, the down going messages from the equality nodes that is shown graphically in Fig 2.4.2b must be computed through following equations:

$$q_{ij}(0) = \eta_{ij}(1 - Pi) \prod_{j \in g_i \setminus j} r_{ji}(0)$$

(2.4.13)

$$q_{ii}(1) = 1 - q_{ii}(0) (2.4.14)$$

where  $\eta_{ij}$  is a positive constant to ensure that  $q_{ij}(0) + q_{ij}(1) = 1$ .

At this step the first iteration is completed. Now the decoder will also update its current estimation of variable  $v_i$  based on the following equations.

$$Q_i(0) = \eta_{ij}(1 - Pi) \prod_{j \in g_i} r_{ji}(0)$$

(2.4.15)

$$Q_i(1) = \eta_{ij} Pi \prod_{j \in g_i} r_{ji}(1)$$

(2.4.16)

Hard decision will be made by comparing  $Q_i(1)$  and  $Q_i(0)$  and by voting for the bigger one. This is usually done within the analog comparators at the output of the decoder.

$$\hat{v}_{i} = \begin{cases} 1 & if \quad Q_{i}(1) > Q_{i}(0) \\ 0 & else \end{cases}$$

(2.4.17)

Upon matching of the estimated codeword to the valid codeword and hence fulfilling the parity check equation, decoding algorithm may terminate at this stage, otherwise go to step 2. Here, we say that if one iteration was enough, then the initially received bits of information have been a valid codeword that can be decoded at this step. However, if more than a single iteration was required for this algorithm, it means that the error-correction needs to be done prior to the final hard-decision.

The above explained algorithm is the basis of the sum-product algorithm used in decoders either analog or digital.

#### 2.3.2 The min-sum algorithm

Another graphically based decoding algorithm is the min-sum algorithm that can be performed with minor modification to the sum-product algorithm [60]. The min-sum algorithm is also known as a variant of the *maximum-likelihood* (ML) sequence decoding rather than the *a posteriori probability* (APP) decoding which is the most straightforward applications of the sum-product algorithm. The reader could study about ML and APP algorithms in [57]. If we assume that l indicates the number of iteration in the min-sum algorithm which is positive, then the messages passing between equality node  $(g_i)$  and check node  $(f_i)$  are given in the log-likelihood ratio domain by [40]:

$$q_{ij}^{(l)} = Pi + \sum_{j \in g_i \setminus j} r_{ji}^{(l-1)}$$

(2.4.18)

$$r_{ji}^{(l)} = \left(\prod_{i \in f_j \setminus i} sign(q_{ij}^{(l)})\right) \min_{i \in f_j \setminus i} (|q_{ij}^{(l)}|)$$

(2.4.19)

where sign(.) function is -1 for negative numbers and is +1 for non-negative numbers.

Note that although the same notation as in the sum-product equations has been applied in (2.4.18) and (2.4.19), here the variables should be considered as log-likelihood values.

The output of individual variable node will be updated after each iteration just as in the sum-product algorithm. A hard decision will be made upon satisfying the valid codeword which determines the termination of decoding or up to given maximum iteration number. The variable nodes are updated by the following equation:

$$Q_i^{(l)} = Pi + \sum_{j' \in g_i} r_{j'i}^{(l-1)}$$

(2.4.20)

Other types of decoding algorithms exist, most of which are based on the sum-product algorithm. As an example, Margin propagation (MP) algorithm that is presented in [61] can be used for approximating the log-sum factors in a conventional sum-product based LDPC decoding algorithm. It was also shown in [61] through simulations that BER performance of margin propagation based LDPC decoders is nearly identical to the sum-product decoders and is superior to the min-sum LDPC decoders.

In the following chapters we will study the analog implementation of the sum-product algorithm which was introduced here. Throughout the rest of the thesis, we will be more concerned about the dynamics of the analog circuits used in the analog decoders.

# **Chapter 3**

# **Analog sum-product circuits**

For an analog decoder based on the sum-product algorithm, equality and check nodes with reasonable precision and speed must be designed. In order to have a correct hard decision on the decoded data, the individual block of equality or check node must deliver its output to the following block with a reasonable accuracy. Also, the timing delay associated with each of these nodes can affect the total convergence speed of the decoder. Therefore, designing equality and check nodes are of great importance.

In this chapter, a complete procedure for the design of the canonical sum-product circuits, equality and check nodes is presented. Here, circuits presented in [57] that are in  $0.18 \mu$  m technology are modified for 90 nm technology. The effect of mismatch on the outputs of individual blocks with different sizing will be studied. At the end of this chapter, we will present the internal view of an implemented chip comprising equality and check nodes with different topologies and sizes that unfortunately failed to function properly, as we discuss later in Chapter 6.

Before explaining the design procedure, we are going to study the operating regions of a MOS transistor. Later, we will introduce the *Translinear principle* and *Translinear circuits* which are the basis for the analog sum-product circuits.

## 3.1 MOS transistor operation regions

Three regions of operation can be defined for MOS transistors including strong inversion, weak inversion also called the sub-threshold region, and the moderate-inversion region.

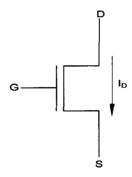

A three terminal MOS transistor is shown in Fig 3.1.1. Here we are going to have a quick review of each of the mentioned regions.

Fig 3.1.1: Basic MOS transistor

#### 3.1.1 Strong inversion region

A MOS transistor is in strong inversion region once its gate-source voltage is greater than the threshold voltage (i.e.  $V_{gs} >> V_{th}$ ). Hence the transistor is said to be ON which means a channel has been made between the drain and source terminals.

If in this condition the drain-source voltage becomes high enough so that  $V_{ds} > V_{gs}$  -  $V_{th}$ , then we say the transistor is *saturated* and the current is governed by:

$$I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (v_{gs} - V_{th})^2$$

(3.1.1)

Where W and L represent the width and length of the transistor and  $\mu$  and  $C_{ox}$  are the mobility of the carriers and the oxide capacitance, respectively.

For  $V_{ds} < V_{gs}$  -  $V_{th}$ , MOS transistor is not saturated anymore and behaves as a voltage dependant resistor which is linear for very small drain-source voltages.

#### 3.1.2 Weak inversion region