# Towards the Automated Modelling and Formal Verification of Analog Designs

# William Denman

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montréal, Québec, Canada

April 2009

© William Denman, 2009

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-63248-2 Our file Notre référence ISBN: 978-0-494-63248-2

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### ABSTRACT

Towards the Automated Modelling and Formal Verification of Analog Designs

#### William Denman

The verification of analog circuits remains a very time consuming and expensive part of the design process. Complete simulation of the state space is not possible; a line is drawn by the designer when it is deemed that enough sets of inputs and outputs have been covered and therefore the circuit is "verified". Unfortunately, bugs could still exist and for safety critical applications this is not acceptable. As well, a bug in the design could lead to costly recalls and a loss of revenue. Formal methods, which use mathematical logic to prove correctness of a design have been developed. However, available techniques for the formal verification of analog circuits are plagued by inaccuracies and a high level of user effort and interaction. We propose in this thesis a complete methodology for the modelling and formal verification of analog circuits. Bond graphs, which are based on the flow of power, are used to automatically extract the circuit's system of Ordinary Differential Equations. Subsequently, two formal verification methods, one based on automated theorem proving with MetiTarski, the other on predicate abstraction based model checking with HybridSal, are then used to verify functional properties on the extracted models. The methodology proposed is mechanical in nature and can be made completely automated. We apply this modelling and verification methodology on a set of analog designs that exhibit complex non-linear behaviour.

#### ACKNOWLEDGEMENTS

There are two people who I attribute my success at Concordia. Firstly, my supervisor, Dr. Sofiène Tahar who gave me the chance of a lifetime to join his research group even though I had no research experience. His continued support goes above and beyond what is required by a thesis supervisor and has been critical to my success and enjoyment at the post graduate level. Secondly, I would not be at this point without the help of my colleague, Dr. Mohamed Zaki, who took me under his wing when I entered into the program. Not even four months into my research, he allowed me to collaborate with him as well as be first author on one of our submitted work. I know now that this is not the norm in academia, and for his trust and confidence in me I will forever be in debt.

I would like to thank Dr. Behzad Akbarpour for his great support of the MetiTarski tool. Thank you Naeem Abbasi for taking the time to go over the thesis multiple times.

I would like also thank the members of my thesis committee, Dr. Glenn Cowan, Dr. Anjali Awasthi and Dr. Dongyu Qiu for their comments and feedback on the thesis.

I would like to thank my girlfriend for her continued emotional support as well as keeping me alive during the thesis writing.

Lastly but not least, I would like to thank my parents for putting me on the path to success. Without them, I could have never made it this far.

To Mom, Dad, Teresa, and the memory of my grandparents

# TABLE OF CONTENTS

| LI | ST O | F FIG   | URES                                  | ix  |

|----|------|---------|---------------------------------------|-----|

| LI | ST O | F TAB   | BLES                                  | X   |

| LI | ST O | F ACR   | RONYMS                                | xii |

| 1  | Intr | oduct   | ion                                   | 1   |

|    | 1.1  | Motiv   | ration                                | 1   |

|    | 1.2  | Relate  | ed Work                               | 4   |

|    |      | 1.2.1   | Formal Modelling of Analog Circuits   | 4   |

|    |      | 1.2.2   | Formal Verification of Analog Designs | 5   |

|    | 1.3  | Propo   | osed Methodology                      | 8   |

|    | 1.4  | Thesis  | s Contribution                        | 10  |

|    | 1.5  | Thesis  | s Outline                             | 11  |

| 2  | Bon  | ıd Gra  | aph Modelling of Analog Circuits      | 13  |

|    | 2.1  | Introd  | luction                               | 13  |

|    | 2.2  | Relate  | ed Work                               | 14  |

|    | 2.3  | Prelin  | ninaries                              | 16  |

|    |      | 2.3.1   | SPICE and Schematic Capture           | 16  |

|    |      | 2.3.2   | Bond Graph Theory                     | 17  |

|    |      | 2.3.3   | Dymola Modelling Laboratory           | 21  |

|    |      | 2.3.4   | Mathematica                           | 23  |

|    | 2.4  | Model   | lling Methodology                     | 23  |

|    | 2.5  | Illustr | rative Example                        | 25  |

|    |      | 2.5.1   | Spice to Bond Graph                   | 25  |

|    |      | 2.5.2   | Simplifications                       | 26  |

|    |      | 2.5.3   | Causality Assignment                  | 27  |

|    |      | 2.5.4   | Extracting the System of Equations    | 28  |

|   | 2.6 | Summ     | nary                                                         | 30         |

|---|-----|----------|--------------------------------------------------------------|------------|

| 3 | Ver | ificatio | on by Automated Theorem Proving                              | 31         |

|   | 3.1 | Introd   | luction                                                      | 31         |

|   | 3.2 | Prelin   | ninaries                                                     | 32         |

|   |     | 3.2.1    | Theory Behind MetiTarski                                     | 32         |

|   |     | 3.2.2    | MetiTarski Input Syntax                                      | 34         |

|   |     | 3.2.3    | Piecewise Linear Approximations                              | 36         |

|   |     | 3.2.4    | Inverse Laplace Transform for Solving Linear Analog Circuits | 37         |

|   |     | 3.2.5    | Maple Computer Algebra System                                | 38         |

|   | 3.3 | Verific  | cation Methodology                                           | 39         |

|   | 3.4 | Applie   | cations                                                      | 42         |

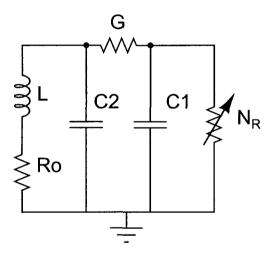

|   |     | 3.4.1    | Tunnel Diode Oscillator                                      | 42         |

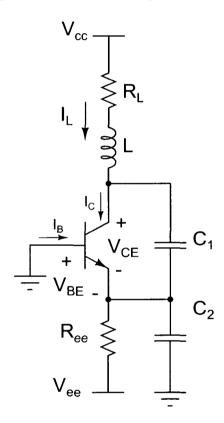

|   |     | 3.4.2    | BJT Colpitts Oscillator                                      | 47         |

|   |     | 3.4.3    | Chua's Oscillator                                            | 49         |

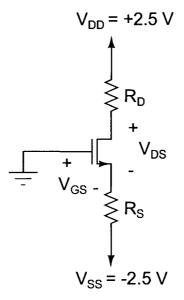

|   |     | 3.4.4    | MOSFET Circuit                                               | <b>5</b> 2 |

|   | 3.5 | Summ     | nary                                                         | 56         |

| 4 | Ver | ificatio | on by Predicate Abstraction                                  | 58         |

|   | 4.1 | Introd   | luction                                                      | 58         |

|   | 4.2 | Prelin   | ninaries                                                     | 59         |

|   |     | 4.2.1    | Property Definition                                          | 59         |

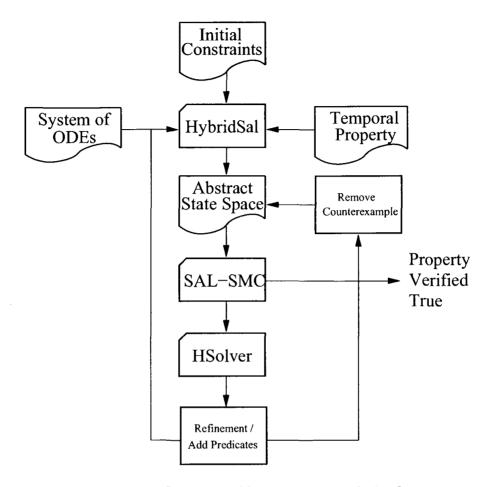

|   |     | 4.2.2    | HybridSal Abstractor                                         | 60         |

|   |     | 4.2.3    | SAL-Symbolic Model Checker                                   | 62         |

|   |     | 4.2.4    | HSolver Constraint Solver                                    | 62         |

|   |     | 4.2.5    | Predicate Abstraction                                        | 63         |

|   | 4.3 | Verific  | eation Methodology                                           | 64         |

|   | 4.4 | Applie   | cations                                                      | 65         |

|   |     | 111      | Tunnal Diada Oscillator                                      | 65         |

|                  |        | 4.4.2 Colpitts BJT Oscillator | 70         |

|------------------|--------|-------------------------------|------------|

|                  | 4.5    | Summary                       | 73         |

| 5                | Cor    | nclusion and Future Work      | <b>7</b> 6 |

|                  | 5.1    | Conclusion                    | 76         |

|                  | 5.2    | Future Work                   | 78         |

| $\mathbf{B}_{i}$ | ibliog | graphy                        | 81         |

# LIST OF FIGURES

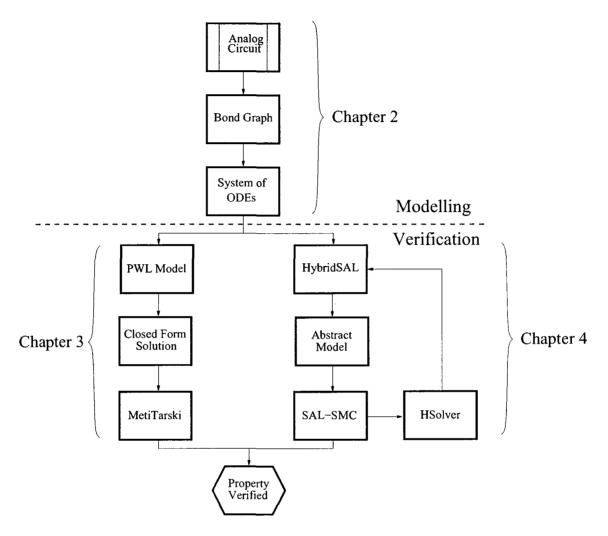

| 1.1  | Modelling and Verification Methodology                                                        | S  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.1  | A Basic SPICE Deck                                                                            | 16 |

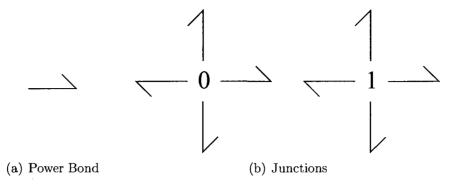

| 2.2  | Basic Bonds                                                                                   | 18 |

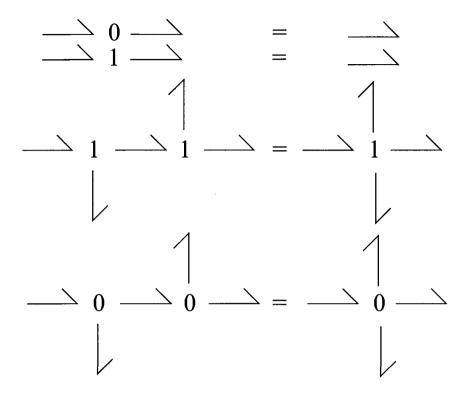

| 2.3  | Simplification Rules for Junctions [8]                                                        | 19 |

| 2.4  | Bond Graph Basics                                                                             | 20 |

| 2.5  | Modelica Syntax                                                                               | 21 |

| 2.6  | Mathematica Simplify Command                                                                  | 23 |

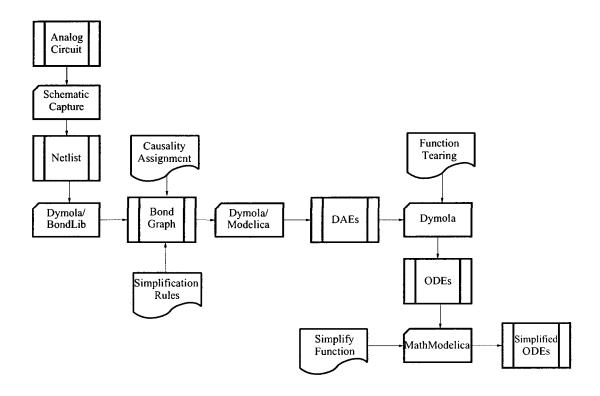

| 2.7  | Bond Graph Modelling Methodology                                                              | 24 |

| 2.8  | Tunnel Diode Oscillator                                                                       | 26 |

| 2.9  | Initial Bond Graph                                                                            | 26 |

| 2.10 | Tunnel Diode Bong Graph Simplifications                                                       | 27 |

| 2.11 | Tunnel Diode Causal Simplified Bond Graph                                                     | 28 |

| 2.12 | System of ODEs generated by Dymola                                                            | 29 |

| 3.1  | MetiTarski Syntax                                                                             | 34 |

| 3.2  | Tunnel Diode Current Linearization [15]                                                       | 37 |

| 3.3  | Overview of the Verification Methodology                                                      | 39 |

| 3.4  | Determining the Closed Form Solutions for Each Mode                                           | 40 |

| 3.5  | Tunnel Diode Oscillator                                                                       | 42 |

| 3.6  | The Hybrid Model of the Tunnel Diode Current                                                  | 43 |

| 3.7  | Meti<br>Tarski Input For the Verification of Mode 1                                           | 45 |

| 3.8  | BJT Colpitts Oscillator                                                                       | 47 |

| 3.9  | ${\it MetiTarski\ Input\ for\ the\ Verification\ of\ Mode\ 1\ of\ the\ Colpitts\ Oscillator}$ | 49 |

| 3.10 | Chua's Circuit                                                                                | 50 |

| 3.11 | Basic MOSFET Circuit [56]                                                                     | 53 |

| 3.12 | MetiTarski Input for Verifying the Mode of Operation               | 55 |

|------|--------------------------------------------------------------------|----|

| 3.13 | Revised MOSFET Circuit MetiTarski Input                            | 56 |

| 4.1  | Example HybridSal Description                                      | 61 |

| 4.2  | Example HSolver Description                                        | 63 |

| 4.3  | Predicate Abstraction Based Verification                           | 65 |

| 4.4  | HybridSal Tunnel Diode Description                                 | 66 |

| 4.5  | SAL Description for the Abstract Model of the Tunnel Diode Circuit | 67 |

| 4.6  | SAL-SMC Generated Counterexample from the SAL Code in Figure       |    |

|      | 4.5                                                                | 68 |

| 4.7  | H<br>Solver Code for the Counterexample Validation of Figure 4.6   | 69 |

| 4.8  | Partial Colpitts Oscillator HybridSal Description                  | 71 |

| 4.9  | Predicates from the abstract Model of the Colpitts Oscillator      | 72 |

| 4.10 | SAL-SMC Generated Counterexample for the Colpitts Oscillator       | 73 |

| 4 11 | HSolver Counterexample Validation of the Colpitts Oscillator       | 75 |

# LIST OF TABLES

| 2.1 | Basic Objects of Bond Graphs                               | 17 |

|-----|------------------------------------------------------------|----|

| 3.1 | Formal Definitions [52]                                    | 33 |

| 3.2 | TPTP Syntax Guide for Figure 3.1                           | 35 |

| 3.3 | Useful Maple Functions                                     | 38 |

| 3.4 | Tunnel Diode Oscillator Verification Runtimes (in seconds) | 46 |

| 3.5 | Colpitts Oscillator Verification Runtimes (in seconds)     | 50 |

| 3.6 | Chua's Oscillator Verification Runtimes (in seconds)       | 52 |

| 3.7 | MOSFET Circuit Verification Runtimes (in seconds)          | 56 |

| 4.1 | LTL temporal operators                                     | 60 |

| 5.1 | Comparison of the Verification Methods                     | 79 |

#### LIST OF ACRONYMS

AMS Analog and Mixed-Signal

BJT Bipolar Junction Trasistor

CTL Computational Tree Logic

DAE Differential Algebraic Equation

DC Direct Current

EDA Electronic Design Automation

FSM Finite State Machine

IGBT Insulated Gate Bipolar Transistor

KCL Kirchoff Current Law

KVL Kirchoff Voltage Law

LTL Linear Temporal Logic

MOC Model Of Computation

MOSFET Metal Oxide Semiconductor Field Effect Transistor

ODE Ordinary Differential Equation

PVS Property Verification System

PWL Piecewise Linear

QEPCAD Quantifier Elimination Procedure

by Cylindrical Algebraic Decomposition

RCF Real Closed Fields

SAL Symbolic Analysis Laboratory

SAT Boolean Satisfiability

SCAP Sequential Causality Assignment Procedure

SMC Symbolic Model Checking

SPICE Simulation Program with Integrated Circuit Emphasis

SRI Stanford Research Institute

TPTP Thousands of Problems for Theorem Provers

VHDL Very High Speed Integrated Circuits

Hardware Design Language

# Chapter 1

# Introduction

# 1.1 Motivation

Embedded systems have become an important part of many devices that we use every day including mobile phones, television set-top boxes and digital cameras. They are also responsible for controlling systems that protect us on a daily basis. Devices such as traffic light, airplane landing gear and elevator break controllers are all implemented using embedded systems. These devices are increasingly becoming complex to design because of the necessary interaction with the physical world. Because of the unpredictable nature of this outside influence, the devices are required to operate over a high number of different modes that can be particularly difficult to determine, isolate and verify. For safety critical systems, where verification is required to ensure that an accident will not occur, this situation can be particularly problematic.

Beyond the problems of verifying the combinations of user input to a device, another critical problem facing the current generation of embedded systems are the effects arising from the reduction in fabrication size. Parasitics, current leakage and signal noise change the functionality of analog designs in unexpected ways. This can cause major problems for the verification engineer because it is time consuming to

build an appropriate model that accounts for this additional behaviour. Additionally, a great deal of expertise is required by the designer to extract and verify the properties of interest from the newly defined models. It is therefore of great utility to both the designer and the verifier to have models at their disposal that preserve the required behaviour of a device, yet remain simple enough to be verified using tools that are available.

The Electronic Design Automation (EDA) industry has developed sophisticated tools to aid engineers in the design and verification of digital circuits. This has allowed digital designs to grow in size and complexity without putting a larger burden on the designers knowledge of the lower level functionality. For analog designers, there has not been the same amount of progress on their tools or methodologies. The design flow has remained essentially the same for the past twenty years. A schematic capture program is used to hand design abstract models, a netlist is extracted and then a circuit simulator is used to verify the design. This is repeated until the desired specifications are met [56]. For the moment, this methodology is adequate since there is ongoing work to make simulators faster and more efficient. Unfortunately, this cannot go on for ever. What happened with digital circuits in the late 1990's is starting to occur again with analog circuits. The complexity of some basic circuit elements is starting to overwhelm engineers and errors at the initial design stage are increasing [14].

Traditionally, simulation has been used to verify analog designs. Unfortunately, verification by simulation is inherently informal because the state space search (set of inputs and expected outputs) is incomplete due to the continuous range of parameter values. Even when using reduced-accuracy simulators, large circuit transistor-level simulations require days or even weeks to complete [14]. As a consequence, simulation methods lack the rigor to ensure the complete correctness of the design.

Before a circuit can be simulated, a test-bench must be constructed where a

set of input and expected outputs are chosen. In the best case scenario, the designer will understand the design perfectly and will choose the test points that represent the limit of operation of the design. But this is far from reality, the questions that the verifier will have trouble answering are "How do we choose the test set?" and "How do we know when we have covered enough of the state space?". One viable option is to use random points for simulation, but again there is no absolute way to know if enough test points have been analyzed to verify a design to a proper level of conformity.

To address the incomplete verification of designs via simulation, formal methods have been developed to increase this confidence level. Formal methods [42] are based around applying mathematical expressions and reasoning to prove correctness of a design. A formal specification is constructed and is used to verify a model using mathematical logics and formal reasoning. There are two main areas of formal verification: model checking and theorem proving. In model checking [18] there is an exhaustive search of the state space. For large designs that contain many variables, most model checking techniques fail to produce an answer because of what is commonly called a "State Space Explosion" [10]. This is where the amount of computer memory required to hold the state information is too large. In theorem proving [49], a complete proof is constructed by hand using a base set of axioms and conjectures. Incredibly powerful, it can be theoretically used to solve any logical problem. Unfortunately, great manual effort is required on part of the verifier to construct the proofs since the method is interactive and thus labour intensive.

With all of its advantages, formal verification seems like the ideal method to solve all possible verification problems. But in fact, they can only assure correctness of a design with relation to a formal specification. The final circuit can still fail because there is no guarantee that the formal specification is correct. As well, errors can also be produced because of defects in fabrication. Notice though, that these problems are also encountered with simulation. Therefore, formal verification

should ideally be combined with simulation methods to increase the confidence level of design beyond of what is presently capable by simulation alone.

To take advantage of what formal methods offer to the verification of analog circuits we address two broad goals:

- Appropriately model the analog circuit so that its continuous-time behaviour can be easily extracted for verification.

- Simplify and automate the methodology for the formal verification of analog designs. The limitations due to the state space explosion problem with model checking and the high level of user interactivity required by theorem proving must be addressed.

To address the first goal, we want to develop in this thesis a modelling method for the automatic extraction of the system of equations from an analog circuit that will aid the flow from the design to the verification stage. For the second goal, we want to develop formal verification techniques that address the stated limitations. In the next section, an overview of the related work in the domains of analog modelling and formal verification will be presented and then our methodology will be outlined in detail.

# 1.2 Related Work

# 1.2.1 Formal Modelling of Analog Circuits

One of the main challenges for the formal verification of analog designs, is the development of models that preserve the behaviour of real devices. One precise way to model analog behaviour is via mathematical systems of equations that are defined over a continuous state space. Nodal analysis techniques have been developed to extract equations from a circuit netlist. However, the resulting equations are in

general, very large and too complicated to be used for a behavioural analysis. For example, the authors of [57] relied on the symbolic analysis toolbox Analog Insydes [29] to obtain the system of equations necessary for verification. In their case, they relied on several iterations of algebraic simplifications that introduce errors in the final result.

Another approach used by Dastidar [22] generated a finite state machine (FSM) from a set of simulation traces to define a formal model. A similar approach was proposed by Little et al. in [44], where they generated from simulation data a hybrid petri net at the front-end to their verification program. The issue of concern with their method is that the model cannot be automatically produced, thresholds must still be defined making the specification only semi-formal in nature.

In this thesis we will use the Bond Graph [50] modelling framework to model analog circuits. Bond graphs are domain independent and they can be used to model any system that has flow of power. The primary benefit of using bond graphs to model analog circuits for subsequent formal verification is that the connections between components are related by the concept of energy conservation. By keeping track of power, models can be easily specified at multiple levels of abstraction, while preserving the topological organization of the design under consideration. In comparison with conventional symbolic extraction methods [66] and the techniques mentioned above, bond graph based modelling allows for a precise symbolic extraction of the system equations thus raising the confidence in verification.

# 1.2.2 Formal Verification of Analog Designs

#### Theorem Proving

In an early attempt at using theorem proving for the formal verification of synthesized analog circuits, Ghosh and Vermuri [32] prove the equivalence of analog designs that contain linear components and components with behaviour that can

be represented by piecewise linear (PWL) models. The PVS higher-order logic theorem prover is then used to prove the implication between implementation and behavioural specification built in VHDL-AMS [16].

In a similar work with theorem provers, Hanna [37] uses formal logic to define the behaviour of predicates over voltage and current waveforms. The basic behaviour of components such as resistors, power supplies and transistors are defined and then used to verify the behaviour of a NOT gate.

These early attempts are mostly based around heuristics for constructing the circuit component models and for determining the specification of the observed behaviour. They cannot be automated and are therefore not suited for larger applications. The methodology we present in this thesis uses a newly developed automated theorem prover called MetiTarski [4] and therefore could be applied to more than just basic academic problems.

### Model Checking

Promising approaches for the formal verification of analog circuits consist of using heuristics to subdivide the reachable state space and then using functions and computational methods to represent the transitions between them. Since the continuous state space is being transformed into a discrete representation, model checking tools can be use to verify the resulting model.

For instance, in the early work in [43], Kurshan and McMillan extract finite state models from an analog circuit using what they call homomorphic functions. Their techniques attempt to reduce the computational complexity, yet at the same time preserve the behaviour of the real circuit. However, their method is only applicable to circuits with a conservative size because of the expensive space requirements. In [38], Hartong, Klausen and Hedrich introduce an extension to Computational Tree Logic (CTL) called CTL-A which defines additional operators that take into account the continuous behaviour of analog circuits. They use a similar method to [43], by

using intervals to construct the abstract state space, while using heuristics to identify transition relations. They apply their methodology on a Schmitt trigger and tunnel diode oscillator. Their techniques too are effected by a state space explosion. In [35], Greenstreet and Mitchell proposed a solution to the space requirements of [43] and [38], by reducing the dimension of the state space. Their methods are sound, but at the cost of the precision of the verification results. Building on these results, several model checking tools including d/dt [19], Checkmate [36] and PHaver [28] have been developed. They have been used to verify several examples including voltage controlled oscillators, a biquad low-pass filter [19], and a  $\Delta\Sigma$  modulator [36]. Methodologies using Petri nets have been developed [46] for modelling and computing the transitions between abstract states, with promising results. In [67], the authors proposed a non-linear approximation for the state space. Taylor approximations are then used for the state space exploration algorithm to verify properties of a voltage controlled oscillator. As with many of the formal analog verification techniques, their methods are limited to circuits of minimal size and complexity.

The most recent research on analog formal verification work is concerned with transforming the analog verification problem to one that can be solved with Boolean satisfiability (SAT) solvers. In [64], the authors have developed a methodology for formulating a SPICE style simulation into a format that can then be passed to a SAT solver. In particular this technique can capture at the transistor level, the non-linear behavior of the design under test.

Many of the formal methods mentioned above limit the verification of the circuit to a set amount of time because of an explicit state exploration. In contrast, we propose in this thesis to use a predicate abstraction and symbolic model checking based method for the construction and verification of abstract models, which is valid over all time. In addition we enhance the symbolic model checking with a counterexample refinement procedure using constraint solving. Further details on related work on analog and mixed signal designs can be found in [68].

# 1.3 Proposed Methodology

In this thesis we propose a framework for the automated modelling and formal verification of analog designs. As a general guideline, we use a syntax and semantic that is familiar to the analog designer, so that the methodology could be adopted as quickly and painlessly as possible. Therefore, the starting point of the methodology (see Figure 1.1) is a circuit described using a SPICE deck [55]. This SPICE description is then systematically translated into a bond graph using the Dymola Modelling Laboratory [21] and the BondLib library [12]. Simplification rules are applied to reduce the bond graphs into their most optimal form and causality is automatically assigned. The system of equations can then be extracted from the bond graph using Dymola. If a set of ordinary differential equations (ODEs) is obtained, then we can move on to the verification step. Generally speaking, the equations representing the continuous time behaviour of an analog circuit are differential algebraic equations (DAEs). In this case, the DAEs must be transformed into their corresponding ODEs using symbolic manipulation.

Next, the optimal ODE model that was extracted from the bond graph, is used to determine the properties of interest to verify them. We propose two verification methods in this thesis, one based on theorem proving the other on model checking. Normally, proofs generated using theorem proving require a great deal of effort to conduct a proof. MetiTarski, an automatic theorem prover for real-valued analytical functions, can automatically use deduction to prove properties over inequalities in terms of trigonometric and exponential functions.

We first convert any non-linear components into their piecewise linear approximation. Using the piecewise linear (PWL) approximation, we can then generate a closed form solution of each mode using an inverse Laplace transform. Then the property of interest is turned into an inequality over the closed form solution. Meti-Tarski [4] can then indicate whether the inequality is true and if so will generate a full proof of its claim. In the case a closed form solution for the system cannot be

Figure 1.1: Modelling and Verification Methodology

found we can consider models that are not defined in terms of ODEs but continuous time equations. In this case, we can automate the paper-and-pencil analysis that is usually done on such models. In the case that the proof does not complete because of extreme values of the special functions, we must turn to the second method.

For the model checking method, we combine predicate abstraction and constraint solving. Using the HybridSAL [63] abstractor, the continuous analog state space is turned into a discrete Boolean state space which is verified using the SAL Symbolic model checker. This method is suitable for designs which fail normal model checking techniques due to a state space explosion. This abstraction comes at the

cost of the precision of the verification that can lead to counterexamples that do not exist in the real circuit. To eliminate the possible false negatives we use the HSolver [54] constraint solver to perform a counter-example check verification.

Two methods are used in this thesis because neither technique is perfect for all verification cases. The theorem proving method can successfully automate very specific problems, such as the determination of the mode of operation of a transistor, because it supports a large set of functions. In the case of our predicate abstraction method, HybridSal can only support polynomial functions. Additionally, an automated theorem prover will provide a complete logical proof of its claims. On the other hand, if our theorem proving methodology is not successful, then no further information is returned thus making it impossible to say where the problem with the model lies. As well, the MetiTarski tool is limited to specifying basic properties as inequalities over closed form solutions. The HybridSAL tools allow for models defined using differential equations that can be used directly after being extracted from the bond graph model and we can define more complex properties using Linear Temporal Logic (LTL). In the case of verification failure, a counterexample is returned giving a direct way to determine the error in the design. The potential problem is that the generated counterexample could be caused by the over approximation of the abstracted model. Even with a counterexample and refinement strategy, this methodology might still not terminate.

# 1.4 Thesis Contribution

In this thesis we have developed a complete methodology for the automated and formal verification of analog designs. The contribution of the thesis can be summarized as follows:

- A method that uses bond graphs to model analog circuits to aid in the extraction of formal specifications. We subsequently used it to generate automatically the system of ODEs.

- An approach that uses the MetiTarski theorem prover to verify functional properties.

- A technique that combines predicate abstraction, abstract model checking and constraint solving to perform the verification and a counterexample refutation.

- Application of the developed modelling and verification methodology on several analog circuits including a tunnel diode, Chua's circuit and Colpitts oscillators.

## 1.5 Thesis Outline

The rest of this thesis is organized as follows: Chapter 2 will present the bond graphing methodology for automatically extracting the state equations from an analog model. The basic concepts of bond graphs along with the background on the tools that are used in their construction is presented. This initial chapter is wrapped up with a complete illustrative example presented as further motivation behind bond graphs for the modelling of analog circuits. In Chapter 3, the methodology for using the MetiTarski theorem prover is developed and presented. We will discuss in detail the internals of MetiTarski and its decision procedure for proving inequalities over real functions. Furthermore, the results of several verification examples including the Tunnel Diode, Chua's Circuit and Colpitts Oscillator will be summarized. In Chapter 4, we will present the predicate abstraction methodology for the discretization of the state space and subsequent formal verification using a symbolic model checker. We will analyze in detail both the techniques employed by the HybridSAL abstractor, the SAL Symbolic Model Checker and the HSolver constraint solver in

the verification methodology. An analysis of the same circuit examples from the theorem proving chapter will be done for a comparison of the verification methodologies. Finally we present the conclusion and future work in Chapter 5.

# Chapter 2

# Bond Graph Modelling of Analog Circuits

# 2.1 Introduction

In this chapter we will describe the theory behind bond graphs in detail as well as the computer environments used to build, verify and simplify them. Continued emphasis will be put on the motivation behind their role in our methodology. This will be further supported with a detailed illustrative example that goes through the steps of automatically extracting the ODEs from an analog circuit.

Bond graphs were introduced in 1961 by Paynter of MIT [50] who believed that "energy and power alone are the fundamental dynamical variables, the ultimate currency of all physical interaction and transaction." Multi-port elements, which at the time were common in circuit diagrams, were combined with bi-directional connectors (a precursor to the name "bond") to model the flow of energy between abstract systems. His work was extended by Karnopp and Rosenberg [40] to develop a standard reference on bond graph notation for the professional engineer. Their motivation to use Paynter's energy notation was the ability to analyze multiple domains concurrently using a single formalism.

Bond graphs define a set of primitives for the modelling of a wide range of practical systems. They are a domain independent framework that allow for the universal treatment of different physical domains. By using the concepts of energy flow, effort and conservation models can be constructed at several levels of abstraction. Since the causal relationships of bond graphs can be algorithmically generated [51], the model's system of equations can be automatically extracted. A further causality analysis can also minimize the computational complexity of the properties to be verified [47]. Moreover, since bond graphs are object oriented, larger models can be built from simpler blocks reducing the need for a complex equation layer [13]. The ability of bond graphs to preserve the computation as well as topological organization of analog circuits makes them an attractive technique for verification.

# 2.2 Related Work

The main application of bond graphs for modelling has been in the area of systems where two or more different physical domains interact. A wide range of examples are available, including a hydraulic motor [12], an enclosed biosphere thermal dissipation simulation [12], a siphon pump [58], and a car wheel suspension system [47] just to name a few. The research on using bond graphs for modelling analog circuits has not yet matured.

In [51], Perelson developed an algorithm for the automatic conversion of an electrical circuit into a bond graph. It is shown that for certain complex series-parallel networks, bond graphs represent a better and more efficient model than circuit diagrams. Additionally, it is shown that when causality is assigned, the state variables and state equation can be automatically determined.

To address accuracy problems encountered when dealing with power devices, Besbes [7] successfully modelled an Insulated Gate-Bipolar Transistor (IGBT) using bond graphs. The present day IGBT models were plagued by poor accuracy in representing switching behaviour. By isolating each doping region, the internal structures were properly modelled by combining equivalent circuit models with semiconductor equations. This was possible because of the modular and power flow based nature of bond graphs. Characteristic properties, such as the stored charge in the base of the BJT, were correctly handled by the bonds instead of equivalent circuits models that added stray capacitances to account for the behaviour. The work demonstrates the expressive power of bond graphs and the results indicate that bond graphs are a suitable candidate for modelling analog devices for verification. This is because of the precision obtained without introducing complex equations or relations.

In [47], Torsten and Vachoux propose to add a bond graphing model of computation (MOC) to the SystemC-AMS [2], system level modelling language. Their goal is to improve its modelling and simulation capabilities, using the domain independent nature of bond graphs to avoid the setup of complex systems of equations. Since the power bonds integrate easily with block diagrams a full formal specification can be created for analog and mixed signal designs.

On the verification side, there has been limited but promising progress with using bond graphs for verifying hybrid systems. In [58] Stromber et. al. use bond graphs as a front-end to the formal verification of an airplane landing gear system. By modelling the hydro-mechanically regulated pump that controls the wheel bay doors using bond graphs, they were able extract precise DAE models. In one bond graph they assume that the hydraulic power supply system behaves as an ideal constant pressure source. In the other, they explicitly model the hydro-mechanic regulator that keeps the pressure constant. The concepts of bond graphs allow for this multi abstraction based description of physical systems. Depending on which model was used, different parts of the system could be isolated and analyzed.

# 2.3 Preliminaries

# 2.3.1 SPICE and Schematic Capture

It has already been stated that the most common way to ensure that a designed circuit works properly is through simulation. The tool of choice for the simulation of analog circuits is the Simulation Program with Integrated Circuit Emphasis (SPICE). The benefit of this software package is that it is open source and thus there are several versions for both academic and industrial uses. The initial versions were entirely text based, where a circuit was described using a text based netlist description called a *deck*. For example, a single resistor connected in series with a single DC voltage supply could be described using the deck file shown in Figure 2.1.

```

V1 1 0 DC 0.3

R1 1 0 50

```

Figure 2.1: A Basic SPICE Deck

In this case, each node of the circuit is represented by a number. The DC voltage supply has a value of 0.3 volts and the resistor has a resistance of 50  $\Omega$ .

Since much effort is required to construct netlists by hand for complex designs, graphical schematic capture programs have been developed for the automatic generation of netlists from abstract models. Schematic capture programs work in the same way as if the circuit was being drawn with paper and pencil. Circuit symbols and external models called subcircuits can be connected with lines that represent wires. The schematic capture programs save much time for the designer since the circuit netlists can be automatically generated for input into a SPICE simulator.

## 2.3.2 Bond Graph Theory

There exists nine basic bond graph elements (as shown in Table 2.1) that can be used to model any possible physical component. The storage group contains the elements for capacitive storage (C type) and inductive storage (I type). The supply group contains the sources of effort and flow. The reversible transformation group contains a transducer and gyrator. The irreversible transformation group contains the elements for thermal losses and entropy producing processes. While the distribution group contains junctions that represent the generalized domain independent Kirchoff Voltage Laws (KVL) and Kirchoff Current Laws (KCL).

Table 2.1: Basic Objects of Bond Graphs

| Group                       | Components                      | Electrical Domain Example     |  |

|-----------------------------|---------------------------------|-------------------------------|--|

| Storage                     | Capacitive/Inertial             | Capacitance/Inductance        |  |

| Supply                      | Source of effort/Source of flow | Voltage source/Current source |  |

| Reversible transformation   | Transducer/Gyrator              | Transformer                   |  |

| Irreversible transformation | Entropy producing process       | Thermal Resistance            |  |

| Distribution                | 0 and 1 junctions               | KVL, KCL                      |  |

#### Connections

Bond graphs are based on the first principle of energy conservation. The most basic element of a bond graph is the power bond (Figure 2.2(a)). It is the energy link between two components. It is represented graphically by a harpoon (half arrow), which points in the direction of positive power flow. The bond represents two variables, effort and flow. In the electrical domain, the effort variable is represented by voltage and the flow by current. It follows that the product of the effort and flow variables represents the power flowing through the bond. Additional variables can also be derived from the bonds. The displacement and momentum energy variables are related to the energy and flow by their time derivatives.

Figure 2.2: Basic Bonds

The other basic component is the junction, which represents a circuit node or mesh (Figure 2.2(b)). At the 0 or common-effort junction the efforts are equal, which is analogous to a node in a circuit. At the 1 or common-flow junction, the flows are equal, which is analogous to a mesh in a circuit.

#### **Elements**

Using the bonds and junctions, it is possible to connect discrete elements together in a bond graph. There are different types of single and multi port interfaces that can be used to represent many possible configurations. The first basic elements are the sources of effort or flow. They are analogous to voltage and current sources in circuit diagrams. Additional single port components are used to represent resistors, capacitors and inductors. They are denoted using the letters R, L or C (see Figure 2.4(a)).

#### Simplifications

There exists two levels of simplification that can be performed on bond graphs. Firstly, there are equivalence rules for the junction objects. These rules are used to reduce the number of bonds in a circuit and are based on the simplification of the underlying power equations. The equivalence rules can be performed automatically to a bond graph (see Figure 2.3).

Figure 2.3: Simplification Rules for Junctions [8]

The second level of simplification is analogous to the concept of combining many resistances into one equivalent resistance. The similar idea can also be applied in the physical domain to two rigidly connected bodies that can be combined into a single mass [31]. By choosing to combine certain bond graph elements, it is possible to reduce the complexity of the system without affecting the overall function. This can result in simpler DAEs that are extracted from the reduced bond graph model. By using a simpler model, the number of states can be reduced, allowing for a less complex verification problem.

#### Causality

Causality is the determination and representation of the directional relationship between an input and an output [8]. In fact, the causality concept is very important as it allows to detect any inconsistency in the circuit settings such as trying to connect two voltage sources with different voltage levels. By adding a causal bar to the end of a bond, the system equations that represent the two variables of effort and flow can be indicated explicitly. There are many rigorous explanations on how to assign the causality of a bond and how it relates to the system as a whole [8, 27, 40]. Fortunately, a simple definition exists that can be used for the direct translation of circuit diagrams. The causal stroke is attached to the side of the bond that computes the flow variable [12] (Figure 2.4(b)). It is important for the modeler to know how to assign causality manually because it can aid in the development of complex bond graphs. However, in general causality is applied automatically using techniques like sequential causality assignment procedures (SCAP) leading to the construction of the causal bond graphs [47].

Figure 2.4: Bond Graph Basics

The causality stroke determines at which point the flow variable is to be calculated. Causality can be computed automatically, but it is recommended to use causal bonds since they can help in analyzing the model when designing larger systems. Certain bond graph elements only have a set number of causalities that can be assigned. For instance, at 0 junctions the efforts are equal which indicates that only one causality stroke is assigned because of the single flow equation defining the junction. Similarly, at 1 junctions the flows are equal, which indicates that there should be only one bond without a causality stroke because of the single effort equation defining the junction. For capacitors and inductors causality is chosen so that differential equations are generated. The stroke is away from capacitors and towards for inductors.

In summary, causality assignment is advantageous as it provides computational information of the system like the number of state space variables which leads to the automatic derivation of the system equations. It also aids in checking for the presence of algebraic loops during the model execution, which results in complex DAEs. Additionally, causality analysis is very useful in detecting ill posed models and can give insight to the correctness and consistency of designs.

# 2.3.3 Dymola Modelling Laboratory

Dymola [21] is an advanced tool for the complete modelling and simulation of physical systems including electrical, thermal and mechanical domains. It comprises of a graphical user interface (GUI) that allows connections between abstract models. As well, it contains a simulator that employs advanced symbolic manipulation techniques to produce a solution to the system equations. At its core is the open source Modelica language [61] that defines the libraries and components. The automatically generated symbolic solution to the system equations is also represented in the Modelica syntax. A tunnel diode can be defined at the equation level using the syntax in Figure 2.5.

```

model TunnelDiode

extends Modelica.Electrical.Analog.Interfaces.OnePort;

equation

i = v^3 - 1.5*v^2 + 0.6*v;

end TunnelDiode;

```

Figure 2.5: Modelica Syntax

Since Modelica is object oriented, the TunnelDiode model must extend from a previously defined "OnePort" object that defines a generic input/output relation. The

tunnel diode in this example is modelled by a third order polynomial where i represents the current through the diode and v the voltage drop across it.

The Modelica language and consequently Dymola are object oriented. This allows for component reuse as well as the ability for external libraries to be easily built. The Dymola Bond Graphing Library (BondLib) is an example of one such library. Developed by Cellier et al. [12], BondLib demonstrates the benefit of object oriented modeling with bond graphs. The transistor models for BJTs and MOSFETS contained in the library can be set to different levels of complexity [12]. At each level, parasitics, current leakages and non-ideal effects can be added to the model by specifying the correct parameters in Dymola. The parameters are available to the modeler to dynamically alter the bond graph. For example, the difference between the MOSFET level 0 and 1 bond graphs is that the capacitances between the source, drain, gate and body are set to zero. With the help of bond graphs and BondLib the designer is able to maintain a deep understanding of the dynamics of the design under verification.

The symbolic manipulation performed by Dymola is quite advanced. By correctly ordering the equations and determining the constraints of the model, the final state calculation can be simplified. For example, in the physical domain Dymola will determine that two rigidly connected bodies can be represented by a single state variable [23]. Similarly, in the electric domain this is analogous to multiple capacitors that are connected in parallel or series being lumped together into a single effective capacitance. Function tearing [25] of non linear equations is also used to "break" algebraic loops and reduce the dimension of sub-models. This further decreases the number of state variables in the final solution. By combining the domain independent properties of bond graphs as well as the advanced symbolic manipulation of Dymola, the automatic extraction of ODEs from an analog circuit is possible.

## 2.3.4 Mathematica

The tearing function described for reducing the dimension of the differential equations comes at a computational cost. The symbolic methods employed by Dymola can potentially create quite a large number of "dummy" variables that are used to effectively "break" the algebraic loops. The only problem is that for large systems, the resulting Modelica description can be very complicated. Since Dymola does no internal simplification, the determination of the differential equations by hand can be quite taxing. Therefore, it is necessary to use an algebraic system such as Mathematica [3] to automatically simplify and remove the redundant equations. Mathematica, an advanced complete algebra system, contains functions such as "Simplify" (see Figure 2.6) that can be used to perform algebraic transformations on a set of generic expressions.

```

In[1] := Simplify[Sin[x]^2+Cos[x]^2]

Out[1]:= 1

```

Figure 2.6: Mathematica Simplify Command

MathModelica [39] is a software bridge between Modelica and Mathematica. It enables the use of the Mathematica "Simplify" function directly onto the Modelica description. By combining Dymola, Modelica, Mathematica and Mathmodelica the path to the automated extraction of the system of differential equations is complete.

# 2.4 Modelling Methodology

In the following, we present the methodology for automatically extracting the system of ODEs from an analog circuit. By using bond graphs we are able to conveniently model the topology of an analog circuit, which can aid at both the design and verification stages. The methodology is depicted in Figure 2.7.

Figure 2.7: Bond Graph Modelling Methodology

Based on what behaviour or functionality is required in the design, the analog circuit is first constructed by hand with a Schematic Capture program that uses common symbols to represent the necessary components. This high level abstraction is then automatically transformed into a SPICE circuit model by macros contained within the schematic capture program. Using the Dymola Modelling Laboratory in conjunction with the BondLib library, a bond graph is created directly from the SPICE model by using a one-to-one mapping between the nodes and components. At this point, the bond graph is not in its simplified form. Using the rules described before, the bond graph is reduced. With the bond graph in its reduced form we are assured that the computational complexity is at a minimum. Next, the preferred causality is assigned to the bonds to ensure that during the extraction stage, differential equations are produced instead of integrals. Once the simplified and causal bond graph is formed, then Dymola is used again to automatically generate the

Modelica description that contains the differential equations. For smaller designs the equations can be easily read directly from it. In other cases, when the design is more complex, the Modelica description may contain redundant equations due to the conversion process from DAEs to ODEs. In this case, the simplification rules in the algebraic system Mathematica are employed to automate the ODE extraction.

### 2.5 Illustrative Example

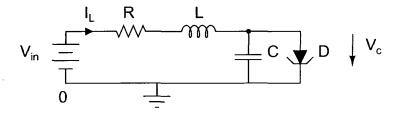

The tunnel diode oscillator circuit in Figure 2.8.(a), which has been used by many researchers (e.g.,[36, 38]) as a benchmark in formal verification research, will be used as an illustrative example to demonstrate the modelling methodology.

The tunnel diode oscillator demonstrates the effect of resonant tunneling that causes a negative resistance to appear at small forward bias voltages. Essentially, for some range of voltages the current through the tunnel diode decreases with increasing voltage. This negative resistance can be used to create a reliable oscillator that functions under many different operating conditions.

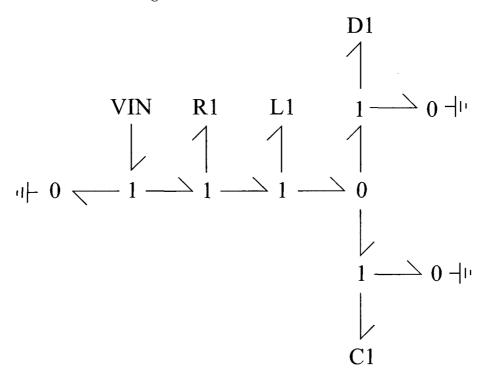

### 2.5.1 Spice to Bond Graph

Figure 2.8.(b) is a SPICE representation of the tunnel diode oscillator. Each node is represented by a number and each component is represent by an alphanumeric name. As expected, the conversion is a one to one mapping of the circuit diagram to the SPICE model. An external subcircuit model defines the behaviour of the tunnel diode.

The transformation from a circuit diagram to bond graph is comparable to the previous HSPICE example. Each circuit diagram component is transformed into its bond graph counterpart. They are then interconnected by transforming nodes into 0 junctions and meshes into 1 junctions as shown in Figure 2.9. This is preformed according to the bond graphs rules described in Section 2.3.2.

.MODEL TunnelDiode TD

VIN 1 0 DC 0.3

R1 1 2 50

L1 2 3 1u

C1 0 3 1p

D1 0 3 TunnelDiode

.END

(a) Circuit Diagram

(b) HSPICE Code

Figure 2.8: Tunnel Diode Oscillator

Figure 2.9: Initial Bond Graph

### 2.5.2 Simplifications

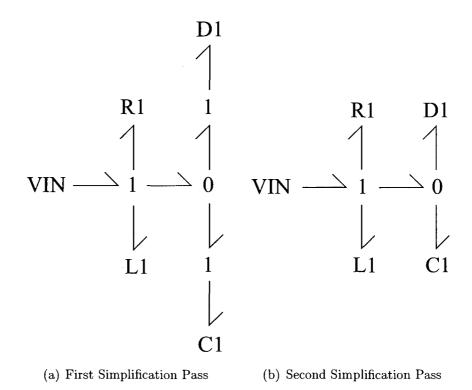

Simplifications of the bond graph in Figure 2.9 can be made. The removal of the bonds that are connected to ground can be removed since the voltage at those nodes is zero, indicating that the power flow is zero. Since the flows at 1 junctions are equal, 1 junctions in series can be merged together. The resulting simplified bond

graph is given in Figure 2.10(a).

As a final step to the simplification process, any junction that has only two bonds connected to it can be removed since no power that flows through a two port junction can divert to another component as shown in Figure 2.10(b).

Figure 2.10: Tunnel Diode Bong Graph Simplifications

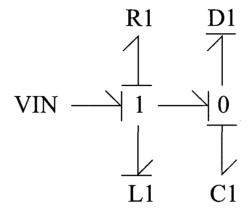

### 2.5.3 Causality Assignment

The next step in the conversion process is to add a causality stroke to each bond. The C and I components have a preferred causality that is assigned first with the current being calculated at the inductor and away from the capacitor. The same idea is used to determine the placement of the causal bars at the 0 and 1 junctions. Since at the 1 junction there is a single effort equation since the flows are equal there should be only one bond without a causal bar. For the 0 junction where there is a single flow equation and the efforts are equal, there should be only one causal

bar. The causality of the resistor and the tunnel diode are arbitrary. The final bond graph is defined as shown in Figure 2.11.

Figure 2.11: Tunnel Diode Causal Simplified Bond Graph

### 2.5.4 Extracting the System of Equations

Once the bond graph is built, the set of system equations can be extracted and simplified. To remove redundant equations we use the rewriting functions of Mathematica.

The analog design can then be described by the system of ODEs as follows:

Consider a set of variables  $x_k(t) \in \mathbb{R}$ ,  $i \in \{1, ..., d\}$ ,  $t \in \mathbb{R}$ , an ODE is a system consisting of a set of equations of the form:

$$\dot{x_k} = \frac{dx_k}{dt} = \dot{x} = F_k(\mathbf{x}(t), \mathbf{u}(t), t)$$

where  $\mathbf{x}(t)$  are variables defining the voltage across the capacitances and the current through the inductances.  $\mathbf{u}(t) \in \mathbb{R}^m$  are variables defining the input signals, with the vector fields  $F_k$ .

Using the Dymola environment, the bond graph for the tunnel diode is constructed. The BondLib library contains graphical modules for bonds and nodes. Dymola then converts the bond graph into a Modelica simulation description. Index reduction, function tearing and further algorithms then automatically transform

the DAEs to ODEs from the Modelica description as shown in Figure 2.12. In particular, the symbolic solution to the system of equations can be read directly from the Modelica description. There are cases where it is not as simple to determine the equations. Since Dymola uses dummy variables to aid in the conversion from DAEs to ODEs, many extra variables may be present in the final output. By using rewriting rules in Mathematica, the system of DAEs can be simplified.

```

// Dummy Variables

resistor.v := resistor.R*inductor.i;

resistor.n.v := constantVoltage.V-resistor.v;

inductor.v := resistor.n.v-capacitor.v;

capacitor.p.i := inductor.i-tunnelDiode.p.i;

tunnelDiode.p.i = capacitor.v^3 - 1.5*capacitor.v^2 + 0.6*capacitor.v;

// Symbolic solution

/* Original equations

inductor.L*der(inductor.i) = inductor.v;

-capacitor.C*der(capacitor.v) = -capacitor.p.i;

*/

der(inductor.i) := inductor.v/inductor.L;

der(capacitor.v) := capacitor.p.i/capacitor.C;

```

Figure 2.12: System of ODEs generated by Dymola

With the simplified equations, we can now focus on the current  $I_L$  and the voltage  $V_C$  across the tunnel diode in parallel with the capacitor of the serial RLC circuit (Figure 2.8). The extracted simplified ODEs are given as  $\dot{V}_C = \frac{1}{C}(-I_d(V_C) + I_L)$  and  $\dot{I}_L = \frac{1}{L}(-V_C - \frac{1}{G}I_L + V_{in})$ , where  $I_d(V_C)$  describes the non-linear tunnel diode behaviour.

### 2.6 Summary

Bond graphs have been characterized as "the most basic graphical modeling paradigm that is fully objected-oriented" [12]. It follows that the concept of encapsulation can be applied to bond graphs to model systems at different levels of complexity. The benefit being that there is no need for single complex equation layer to define a system and thus the system of equations can be extracted from the model.

Now that a method for extracting the system of ODEs from a model has been presented, the next chapter will describe in detail a method for formally verifying properties on the extracted models. If during verification, the models need to be changed to take into account different topologies, the bond graphs can be quickly modified and the new system equations obtained.

## Chapter 3

# Verification by Automated Theorem Proving

### 3.1 Introduction

In this chapter we will present the work on using the MetiTarski theorem prover for the verification of properties on the system of ODEs that were extracted from the analog circuit bond graph model. There is a great need for research in this area since there has been limited advancement on this front. We strongly believe that automated methods should be developed to take advantage of the high confidence in results provided by theorem proving, where a complete proof with logical inference steps is generated. The main hurdle is the great deal of expertise needed to interactively guide a proof to fruition.

MetiTarski [4] is an automatic theorem prover for real-valued analytical functions, including trigonometric and exponential functions. It works by a combination of resolution inference and algebraic simplification, invoking a decision procedure (QEPCAD) [9] to prove polynomial inequalities. Since many of the circuit equations we deal with in the analog domain contain exponentials, it is a viable option

for formally verifying the properties of interest. The output of MetiTarski is a complete proof that contains algebraic simplification and decision procedure calls that can be verified using other tools.

In the last decade a new engineering field has emerged: hybrid system theory. It encompasses techniques for the automatic design and analysis of systems with real-time and continuous behavior. In [5], the authors use MetiTarski to solve various hybrid system verification problems including collision avoidance, navigation and biological mutant examples. In their methodology, they model the hybrid systems over several modes of operation. In each mode, the variables of the system vary according to a set of ODEs. By using the inverse laplace transform they solve for closed form solutions of each mode of operation. Properties are then proven in each mode using MetiTarski. By taking advantage of hybrid system theory, theorem proving is now emerging as a serious candidate for the verification of analog systems. This is because an analog circuit verification can be viewed as a hybrid system if it is defined using a proper model.

### 3.2 Preliminaries

### 3.2.1 Theory Behind MetiTarski

There exists few methods to automatically prove statements involving elementary functions such as ln, exp, sin, cos and sqrt. In their MetiTarski tool, Akbarpour and Paulson [4] use the decidability of real closed fields to automatically prove inequalities over elementary functions. MetiTarski replaces the functions with upper and lower bounds in an attempt to reduce the problem so that a decision procedure can be used to automatically prove the property of interest. Before delving into its internals, it is important to understand some basic formal method terminology (see Table 3.1).

Table 3.1: Formal Definitions [52]

| Quantifiers       | $\exists, \forall$ (There exists and For All)           |

|-------------------|---------------------------------------------------------|

| Axioms            | Logical Statements                                      |

| Theory            | Set of Axioms                                           |

| Model             | Abstract Structure that satisfies a Theory              |

| Consistent Theory | The theory has at least one model                       |

| Complete Theory   | Every model that is true can be proven                  |

| Decidable Theory  | An algorithm exists for evaluating the truth of a model |

An algebraic field is an abstract structure that contains the operators of addition, subtraction, multiplication and division. To be called real closed, the field must satisfy a set of axioms defined by the operators as well as be able to represent atomic polynomial formulas that contain inequalities. These formulas can also contain conjunctions, disjunctions, negations and quantifiers. A real closed field must also be ordered and thus meet following axioms [52]:

-1: is negative

$\forall x : x \text{ or } -x \text{ is positive}$

$\forall x, y \text{ positive } : x + y, x * y \text{ are positive }$

Alfred Tarski proved in 1930 that RCF was decidable by presenting quantifier elimination procedure [11]. Given an RCF quantified formula, an equivalent formula that has no  $\forall$  or  $\exists$  components can be produced. Take for instance,

$$a \neq 0 \wedge (\exists x) : (ax^2 + bx + c = 0)$$

from the rules governing the solution of the quadratic equation [33], we know that for there to be a real solution the discriminant must be greater than or equal to zero or

$$b^2 - 4ac \ge 0$$

and by using this result, we can remove the quantifiers to produce the following result

$$(a \neq 0 \land b^2 - 4ac \ge 0) \lor (a = 0 \land b \ne 0) \lor (a = b = c = 0)$$

This example is trivial, but for more complex equations his method could not be implemented in practice. There has been further work on the decision procedure of RCF by McLaughlin, Harrison and Hormander [48]. Their implementations are more efficient than Tarski's but fail to work on polynomials with a degree greater than six. QEPCAD-B [9] is a recent and efficient decision procedure for the complete theory of RCF. It uses cylindrical decomposition to extract polynomials from an input formula and then uses abstraction techniques to generate an r-dimensional space, where r is the number of variables in the input formula. The abstract regions are then arranged in a cylindrical domain which allows an efficient removal of quantifiers via linear algebraic methods.

### 3.2.2 MetiTarski Input Syntax

MetiTarksi operates on the first-order formula in the Thousands of Problems for Theorem Provers (TPTP) format that includes the corresponding axioms. Take for instance the following code.

Figure 3.1: MetiTarski Syntax

"fof" indicates to MetiTarski that the logic language used is a first-order formula. It

is then followed by a label of the proof as well as the keyword "conjecture" indicating that the following formula is to be proved with the included axioms. The conjecture is read as follows: For all (!) X between 0 and  $2.39 \times 10^{-9}$  the formula is always less than 0.03. For a complete syntax guide see Table 3.2.

Table 3.2: TPTP Syntax Guide for Figure 3.1

| fof | First order logic formula        |

|-----|----------------------------------|

| !   | Universal Quantifier $(\forall)$ |

| X   | Quantified Variable              |

| &   | Logical AND                      |

| exp | e (exponential function)         |

| <   | Less Than                        |

#### Axioms

In addition to the problem definition, axioms must be appended to tell MetiTarksi what clauses to use when performing the special function to polynomial substitution.

Fortunately, this is automated using external scripts, but it is still necessary to indicate what family of axioms is required. It is very important that only the necessary axioms files are included in the TPTP description, since each set adds computational complexity to the final proof. For example, there are two sets of axiom declarations for the exponential function. One for regular bounds and one for extended bounds. There are cases where including the extended bounds will make the inequality under test unsolvable. In reality, removing the extra axioms will enable MetiTarski to complete the proof. The converse is also true, if for instance the TPTP description contains trigonometric functions and those axioms are not included, then the proof will also be unsolvable.

### Range Reduction

Since the elementary functions are being replaced by polynomials, it is necessary that the bounds on the quantified variables vary closely around 0. If the quantified variables get too high or too low, the accuracy of the polynomials is greatly diminished. Therefore, MetiTarski uses internal range reduction methods to properly scale the value of the variables to ensure that the polynomials are an accurate approximation to the real function.

There are cases though when the internal range reduction is not enough. When dealing with closed form solutions that contain trigonometric functions with bounds that are very large (greater than  $6\pi$ ). Then manual range reduction is required. Since the trigonometric functions are cyclical, it is possible to remove or add multiples of  $2\pi$ . By doing this, MetiTarski will be able to complete proofs that fail otherwise.

### 3.2.3 Piecewise Linear Approximations

The first thing to note is that the input to MetiTarksi is a closed form solution that can contain any number of analytical functions. To obtain closed form solutions we have used the inverse Laplace Transform on the system of equations representing the behaviour of the system. Therefore, it is necessary that the ODEs be linear and thus we must use piecewise linear models for the analog component. PWL models are adequate to be used to model the components for the following reasons [15]:

- Piecewise-linear circuits are the simplest class of nonlinear circuits.

- The behaviour of many op-amp and diodes and switch circuits can be reasonably approximated as piecewise-linear.

- Linear methods are substantially more tractable than non-linear ones, even when they divide the problem into multiple modes.

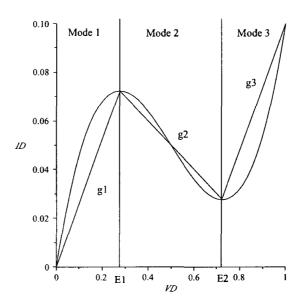

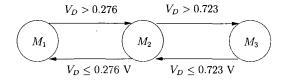

Take for instance the behaviour of the tunnel diode. As shown in Figure 3.2, the behaviour can be correctly approximated by a piecewise linear model that operates over three modes of operation.

Figure 3.2: Tunnel Diode Current Linearization [15]

# 3.2.4 Inverse Laplace Transform for Solving Linear Analog Circuits

A common way to solve the variables of a circuit is to perform nodal analysis, by using KVL and KCL to work through the circuit solving for node voltages and currents. The problem is that many equations must be solved for required several computation steps. The inverse Laplace transform method is an another efficient way to solve for the closed form solutions of an analog circuit. Any circuit can be described by n first order differential equations [65]. By extracting the differential equation for each energy storing element (capacitors and inductors) and then assembling the "state model" matrix, an inverse Laplace transform can be used to solve for the currents and voltages. The benefit of using this method is that it is a

one step process, to go from equations to solution instead of solving many equations encountered when using the Kirchoff circuit laws. The standard circuit state model [65] is

$$\dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}$$

Where the **x** vector represents the state variables from the energy storing elements. A is the *circuit matrix* because it contains the values of the circuit parameters. The **B** matrix is called the *distribution matrix* because it contains values that depend on the location of the power sources.

Let X denote the Laplace transform of  $\mathbf{x}$   $(X = \mathcal{L}x)$ ; then  $sX - x_0 = AX + \frac{B}{s}$ , and solving for X we have  $X = (sI - A)^{-1}(x_0) + \frac{B}{s}$ . With the state model defined, we can take the inverse Laplace Transform of X to solve for the closed form solution of the circuit equations.

### 3.2.5 Maple Computer Algebra System

Maple [1] is a full computer algebra system that can be used to efficiently manipulate many types of data. As well there are internal functions that are available to perform many actions on matrices, solving equations and symbolically evaluating expressions. The functions in Table 3.3 are used to solve the closed form solutions of the ODEs that were obtained from the bond graphs.

Table 3.3: Useful Maple Functions

| Function     | Description                  | Example           | Result             |

|--------------|------------------------------|-------------------|--------------------|

| fsolve()     | Uses numerical approxima-    | fsolve(x=0.1,t)   | Value of $t$ where |

|              | tion techniques to find a    |                   | x(t)=1             |

|              | decimal approximation to     |                   |                    |

|              | the solution to the equation |                   |                    |

| eval()       | Evaluates an expression      | $eval(x^2, x=2)$  | Will output the    |

|              |                              |                   | value 4            |

| invlaplace() | Takes the inverse laplace    | invlaplace(X,s,t) | Returns $x(t)$     |

|              | transform of vector X        |                   |                    |

### 3.3 Verification Methodology

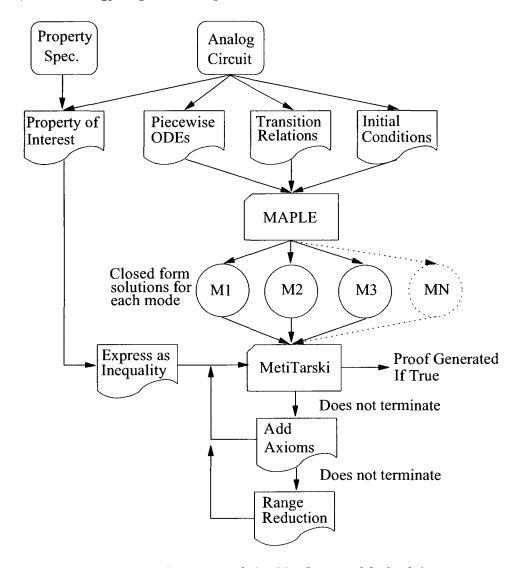

In the following, we demonstrate a methodology for the automatic verification of functional properties of analog designs using MetiTarski. An overview of the proposed, methodology is given in Figure 3.3.

Figure 3.3: Overview of the Verification Methodology

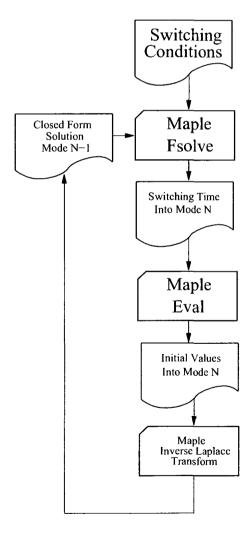

We first obtain the system of differential equations from the circuit of interest. Any non-linear elements are transformed into their PWL models. The transition relation between each mode of the PWL model is determined and differential equations (ODEs) are constructed over each mode of operation. Starting in any mode, the ODEs and initial conditions are supplied to the computer algebra system Maple and an inverse Laplace transform is performed to find a closed form solution for each state variable as a function of time. Using the transition relations, Maple is used to find the time instance where the system switches modes. At that time, the initial conditions for the next mode are calculated and an inverse Laplace transform is performed to again find a closed form solution. This is repeated until each mode has been visited as shown in Figure 3.4.

Figure 3.4: Determining the Closed Form Solutions for Each Mode

We then turn the verification property into an inequality over special functions. A first-order formula in the Thousands of Problems for Theorem Provers (TPTP) format (see Chapter 3.2.2), including the corresponding axioms, is then supplied to MetiTarski. MetiTarski uses an extension of the TPTP format, including infix notation for the arithmetic and relational symbols [59, 60].

If MetiTarski is successful, it delivers a proof and we are done. If unsuccessful, it will run until terminated by the user. Additional axioms are then added or removed to aid MetiTarski in formulating a proof. There are certain axioms that are available for special functions that take on extreme values. Including them unnecessarily in proofs will increase the computation time. If still unsuccessful, range reduction is applied to the trigonometric functions to further eliminate any extreme values that can cause problems for MetiTarski's decision procedure.

In cases when MetiTarksi still does not terminate, it could be because the functions take on values that are beyond the limits of the deduction methods. There are also cases when a closed form solution to the ODEs cannot be computed, due to trigonometric or non-linear terms. As well, it is possible the loss of precision of the PWL modelling could be affecting the results. In these cases a different approach altogether must be taken.