# Efficient Algorithm and Architecture for Implementation of Multiplier Circuits in Modern FPGAs

**Jacques Laurent Athow**

Department of Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for

Degree of Master of Applied Science

Concordia University, Montréal, Canada

November 2008

© Jacques L Athow, 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-63306-9 Our file Notre référence ISBN: 978-0-494-63306-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

#### **ABSTRACT**

## Efficient Algorithm and Architecture for Implementation of Multiplier Circuits in Modern FPGAs

#### Jacques L Athow

High speed multiplication in Field Programmable Gate Arrays is often performed either using logic cells or with built-in DSP blocks. The latter provides the highest performance for arithmetic operations while being also optimized in terms of power and area utilization. Scalability of input operands is limited to that of a single DSP block and the current CAD tools provide little help when the designer needs to build larger arithmetic blocks. The present thesis proposes an effective approach to the problem of building large integer multipliers out of smaller ones by giving two algorithms to the system designer, for a given FPGA technology. Large word length is required in applications such as cryptography and video processing. The first proposed algorithm partitions large input multipliers into an architecture-aware design. The second algorithm then places the generated design in an optimal layout minimizing interconnect delay. The thesis concludes with simulation and hardware generated data to support the proposed algorithms.

#### **ACKNOWLEDGEMENTS**

I would like to take the opportunity and thank everyone that made my research possible, which culminated with this thesis. In particular, I am indebted to my professor Asim who always encouraged me. He guided me during my thesis with his useful insight in the field of FPGAs and low level interconnects. He would always make me think out-of-the-box with his no-nonsense approach. To my many professors that I had throughout my stay at Concordia University including Professors Tahar, Amer, Lam, the late Gohary and Ted Obuchowicz, without whom I would never have known the world of VHDL. Indirectly to Peter Alfke and Ray Andraka for their work and guidance on the FPGA usenet forum. To the staff at the AITS helpdesk and the librarians at the Webster library. Finally, to my parents who initially made everything possible and were always there to provide moral support.

## TABLE OF CONTENTS

| L  | IST OF | FIGURESix                                            |

|----|--------|------------------------------------------------------|

| L  | IST OF | TABLESxii                                            |

| 1. | INT    | TRODUCTION1                                          |

|    | 1. 1   | Contribution3                                        |

|    | 1.2    | Thesis Organization4                                 |

| 2  | Fiel   | d Programmable Gate Arrays5                          |

|    | 2. 1   | Basic Multiplication8                                |

| 3  | FPC    | GA Multiplication Algorithms                         |

|    | 3. 1   | Serial-Parallel Signed Multiplier                    |

|    | 3. 2   | Carry Save Array Multiplier11                        |

|    | 3. 3   | Constant Coefficient Multiplier                      |

|    | 3. 4   | Partial Product Look-Up Table Multiplier             |

|    | 3. 5   | Partition Multiplication Algorithm (Shuli-Gao et al) |

|    | 3.6    | Summary of Multiplication Algorithms                 |

| 4  | Xili   | nx Virtex Family FPGA22                              |

|    | 4. 1   | Logic Cells                                          |

|    | 4. 2   | Virtex Hardware Arithmetic                           |

|    | 4. 3   | Xilinx DSP48 Arithmetic Block                        |

|    | 4. 4   | Interconnect                                         |

|    | 4. 5   | Congestion                                           |

|    | 4. 6   | Summary of Techniques                                |

| 5  | Part   | tition Algorithm for Virtex-4 FPGA35                 |

|    | 5. 1   | Details of Operation                                 |

|                  | 5. | . 2   | Arit                        | hmetic Cell A Block                         | 39 |

|------------------|----|-------|-----------------------------|---------------------------------------------|----|

|                  | 5. | . 3   | Arit                        | hmetic Cell B Block and Cascade Register    | 40 |

| 5. 4 Partition A |    | Part  | ition Algorithm Description | 41                                          |    |

|                  | 5. | . 5   | Res                         | ources Utilization                          | 44 |

|                  | 5. | . 6   | Peri                        | formance Equations                          | 44 |

|                  | 5. | . 7   | Nor                         | n-Pipeline Design                           | 45 |

|                  | 5. | . 8   | Res                         | ults                                        | 48 |

|                  |    | 5.8.  | 1                           | Combinational path delay                    | 49 |

|                  |    | 5.8.2 | 2                           | Virtex-4 logic slice utilization            | 50 |

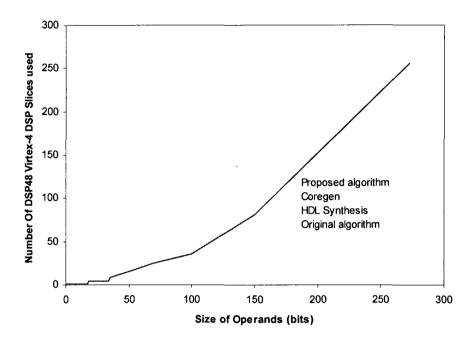

|                  |    | 5.8.3 | 3                           | Virtex-4 DSP48 slice usage                  | 51 |

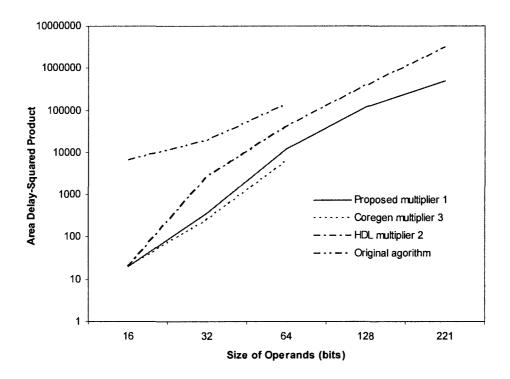

|                  |    | 5.8.4 | 4                           | Area delay (AT <sup>2</sup> ) product       | 52 |

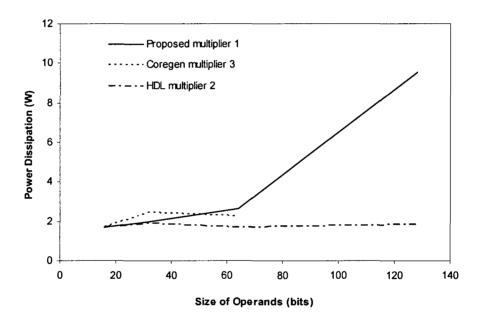

|                  |    | 5.8.  | 5                           | Power dissipation                           | 53 |

|                  |    | 5.8.6 | 5                           | Other results                               | 54 |

|                  | 5. | 9     | Sum                         | nmary                                       | 56 |

| 6                |    | Plac  | emei                        | nt algorithm for large-unsigned multipliers | 57 |

|                  | 6. | 1     | Intro                       | oduction                                    | 57 |

|                  | 6. | 2     | Plac                        | ement Problem Formulation                   | 59 |

|                  | 6. | 3     | Rela                        | ated Work on Placement Algorithms           | 61 |

|                  |    | 6.3.  | 1                           | Placement algorithms for FPGA               | 61 |

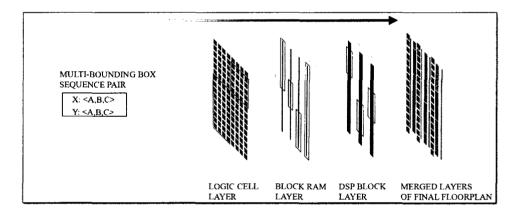

|                  |    | 6.3.2 | 2                           | Heterogeneous Floorplanner for FPGA         | 63 |

|                  |    | 6.3.3 | 3                           | HPLAN Heterogeneous Floorplanner            | 63 |

|                  |    | 6.3.4 | 4                           | HPLAN problem formulation                   | 64 |

|                  |    | 6.3.5 | 5                           | Comments                                    | 66 |

|                  | 6. | 4     | Rela                        | ative Placement Macros                      | 67 |

|                  | 6  | 5     | Are                         | a delay and Power Heuristics                | 69 |

|   |    | 6.5.  | 1      | Area                                               | . 69 |

|---|----|-------|--------|----------------------------------------------------|------|

|   |    | 6.5.2 | 2      | Delay                                              | 70   |

|   |    | 6.5.3 | 3      | Power                                              | 70   |

|   | 6. | . 6   | Prop   | oosed Placement Algorithm                          | 71   |

|   |    | 6.6.  | 1      | Area constraints formulation                       | .72  |

|   |    | 6.6.2 | 2      | Congestion Factor                                  | .74  |

|   |    | 6.6.3 | 3      | Objective function                                 | .75  |

|   |    | 6.6.4 | 1      | Graph theory                                       | 75   |

|   | 6. | . 7   | Prop   | osed Placement Algorithm                           | 76   |

|   | 6. | . 8   | Resu   | ılts                                               | .79  |

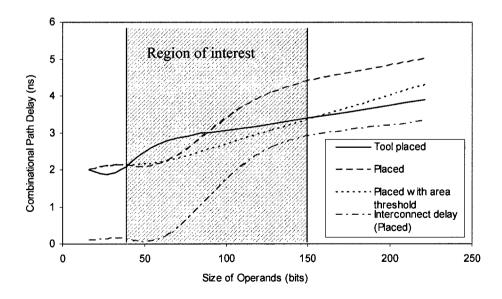

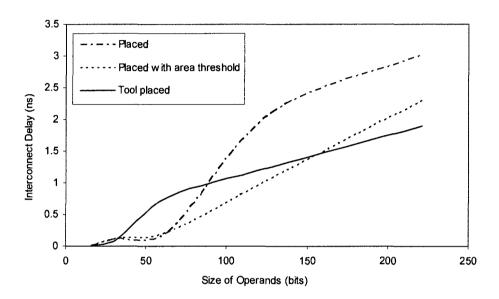

|   |    | 6.8.1 | 1      | Combinational path delay                           | 80   |

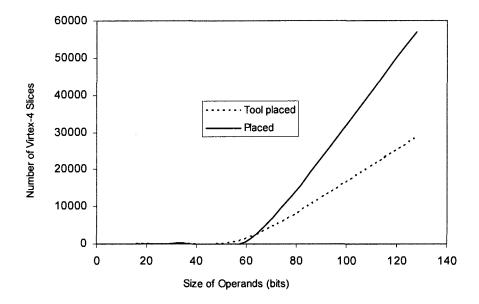

|   |    | 6.8.2 | 2      | Virtex-4 logic slice utilization for placed design | 81   |

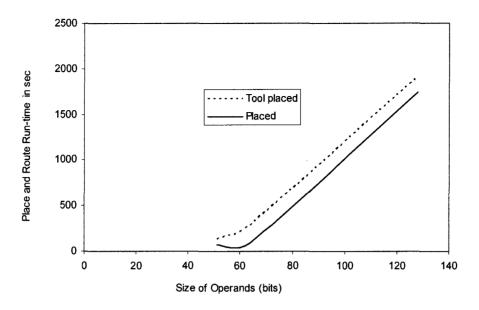

|   |    | 6.8.3 | 3      | Place-and-route tool runtime                       | 82   |

|   | 6. | 9     | Sum    | mary                                               | 83   |

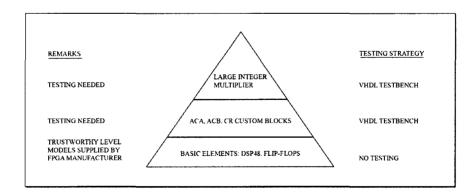

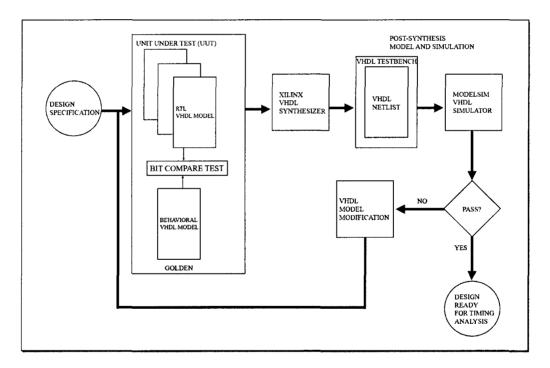

| 7 |    | Test  | ing st | trategy                                            | 84   |

|   | 7. | 1     | Beha   | avioural Testing                                   | 85   |

|   | 7. | 2     | Timi   | ing Analysis                                       | 86   |

|   | 7. | 3     | Plac   | ement Algorithm Testing                            | 86   |

| 8 |    | Cone  | clusio | on and future work                                 | 87   |

|   | 8. | 1     | Parti  | tion Algorithm                                     | 87   |

|   | 8. | 2     | Place  | ement Algorithm                                    | 87   |

|   | 8. | 3     | Cone   | clusion                                            | 88   |

|   | 8. | 4     | Futu   | re Work                                            | 89   |

| R |    |       |        | S                                                  |      |

|   |    |       |        | , VHDL MODELS                                      |      |

|   |    |       |        |                                                    |      |

| v | i | i | i |  |

|---|---|---|---|--|

|   | • | • | • |  |

| APPENDIX B, C++ SOURCE CODE11 | 0 |

|-------------------------------|---|

|-------------------------------|---|

## LIST OF FIGURES

| Figure 2.1 Current FPGA technologies and trend towards built-in DSP blocks 6          |

|---------------------------------------------------------------------------------------|

| Figure 2.2 Virtex Family FPGA with amount of DSP blocks                               |

| Figure 3.1 Serial Parallel N-bit multiplier architecture                              |

| Figure 3.2 Carry Save Array multiplier architecture                                   |

| Figure 3.3 N-bit constant coefficient unsigned multiplier                             |

| Figure 3.4 Architecture for Partial-Product Look-up Multiplier using 6bits LUT 14     |

| Figure 3.5 Long-Integer Multiplication Decomposition according to [4]16               |

| Figure 3.6 Sequence of addition operation for algorithm [4] when m is even and odd    |

|                                                                                       |

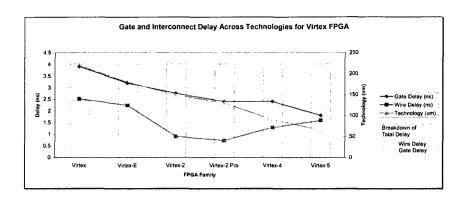

| Figure 3.7 Graph of gate and interconnect (wire) delay versus technology for Virtex   |

| FPGA for a 16x2bit unsigned multiplier                                                |

| Figure 4.1 Trend for Xilinx FPGA during past 16 years                                 |

| Figure 4.2 Xilinx FPGA logic cell evolution during past 15 years25                    |

| Figure 4.3 Hardware dedicated for arithmetic operations in Virtex FPGA26              |

| Figure 4.4 Internal view of Virtex-4 DSP48 tile (block) [15]                          |

| Figure 4.5 DSP48 slice to CLB area ratio, as shown in Xilinx FPGAEDITOR28             |

| Figure 4.6 Different interconnect classes found in the Virtex family of FPGA [19]. 32 |

| Figure 5.1 Technology mapping of [4] into proposed architecture for a 68bits          |

| unsigned multiplier37                                                                 |

| Figure 5.2 DSP48 tile internal configuration                                          |

| Figure 5.3 Internal view of Arithmetic Cell A block                                   |

| Figure 5.4 Internal view of Arithmetic Cell B block                                   |

| Figure 5.5 Internal view of Cascade Register block                                    |

| Figure 5.6 Long-integer 68x68bit multiplier generated by proposed algorithm 43        |

|---------------------------------------------------------------------------------------|

| Figure 5.7 Area-Delay product for non-pipeline multipliers                            |

| Figure 5.8 Combinational path delay for different sized inputs                        |

| Figure 5.9 Amount of Virtex-4 slices used against different sized inputs50            |

| Figure 5.10 Number of DSP48 slices against different sized inputs                     |

| Figure 5.11 Area Delay product (AT <sup>2</sup> ) performance measure                 |

| Figure 5.12 Power dissipation for different sized inputs                              |

| Figure 5.13 Routing performance degradation for higher word length54                  |

| Figure 5.14 Layout of placed 136x136bit multiplier circuit inside a Virtex-4 FX140    |

| FPGA55                                                                                |

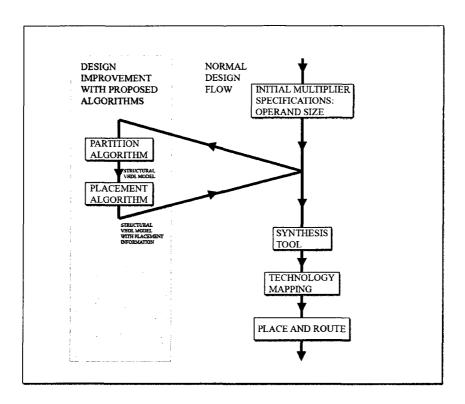

| Figure 6.1 Design using proposed set of algorithm                                     |

| Figure 6.2 Example of floorplan generated using HPLAN                                 |

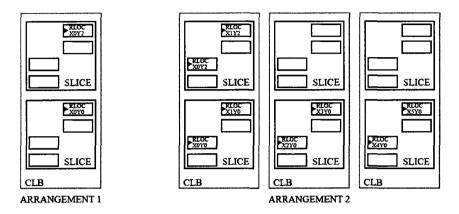

| Figure 6.3 Usage of Relative Location in hardware descriptive language67              |

| Figure 6.4 Internal logic slice arrangement using RLOC attribute                      |

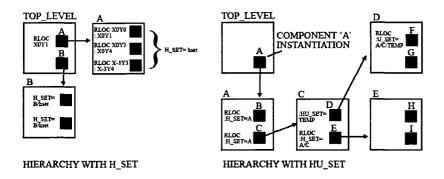

| Figure 6.4 Hierarchy representation using H_SET and HU_SET69                          |

| Figure 6.5 ACA, ACB, CR Macro blocks internal placement                               |

| Figure 6.6 Macro blocks physical dimensions                                           |

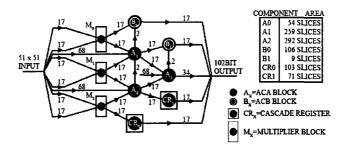

| Figure 6.7 51Bit Multiplier graph                                                     |

| Figure 6.8 51Bit multiplier physical layout graph, as generated by proposed partition |

| algorithm79                                                                           |

| Figure 6.9 Combinational path delay for designs initially placed using proposed       |

| placement algorithm80                                                                 |

| Figure 6.10 Interconnect delay in placed multiplier designs                           |

| Figure 6.11 Logic slice utilization for placed multipliers designs                    |

| Figure 6.12 Place-and-route run-time for different multiplier designs                 |

| xi |

|----|

|    |

| Figure 7.1 Testing hierarchy for multiplier partition algorithm | 84 |

|-----------------------------------------------------------------|----|

| Figure 7.2 Test setup for multiplier designs                    | 85 |

## LIST OF TABLES

| Table 1.1 Performance of HDL, Coregen, Algorithm [1] and Proposed Algorithm2          |

|---------------------------------------------------------------------------------------|

| Table 4.1 Valid opmode for dsp48 block, with respect to z multiplexer [18]29          |

| Table 4.2 Valid opmode for dsp48 block, with respect to x and y multiplexer [19] . 30 |

| Table 4.3 Carryinsel control bits with corresponding opmode operation [20]30          |

| Table 5.1 OPMODE/CARRY configuration bits for Slice0 and Slice139                     |

| Table 5.2 Performance results for combinational delay, non-pipelined designs 46       |

| Table 5.3 Performance results for area utilization, non-pipelined designs             |

#### 1. INTRODUCTION

Binary multiplication operations are at the center of many system level blocks used in high performance applications. The efficiency of the operation is crucial in order to have an edge over the competition. As an example, one of the latest television standard developed, the high-definition television (HDTV) is based on the MPEG-2 compression algorithm [1]. This works at a lower level with Discrete Cosine Transforms (DCT) and Inverse DCTs which are bottom-line Fast Fourier Transform (FFT) operations [2]. The performance of FFT [3] is measured by the number of multiplication and addition operations per second. The higher the number, the higher the amount of frame compressed in unit time, hence a better quality. An HD-DVD recorder built around an efficient MPEG compression unit will generally perform better than one made up of conventional system blocks. Other applications of long integer multipliers include cryptography and hardware accelerator for software mathematic packages and algorithms.

Presently there is a lack of Computer Aided Design (CAD) tools available to the system designer, which solve the problem of creating high-performing long-word multiplier circuits in Field Programmable Gate Array chips (FPGA). Current solutions include using the multiplication operator in Hardware Descriptive Languages (HDL) or using CAD applications such as Xilinx COREGenerator, to generate pre-built netlist files. Both solutions have limitations; using the VHDL multiplication operator will request from the HDL synthesizer the corresponding netlist. In most cases, the generated multiplier will not be based on high performance arithmetic blocks

available in the FPGA or will be un-pipelined. The current COREGenerator software has limitation in terms of size of input operands allowed and is constrained to a maximum of 64bits. The following table summarizes the performance of various methodologies available to implement unsigned multipliers.

TABLE 1.1 PERFORMANCE OF HDL, COREGEN, ALGORITHM [4] AND PROPOSED ALGORITHM.

| Methodology           | HDL       | CORE<br>Generator | GENERIC<br>ALGORITHM [4] | PROPOSED<br>ALGORITHM [5] |

|-----------------------|-----------|-------------------|--------------------------|---------------------------|

| Maximum Frequency     | MEDIUM    | HIGH              | HIGH                     | VERY HIGH                 |

| Pipelining            | LIMITED   | OPTIMUM           | OPTIMUM                  | OPTIMUM                   |

| Maximum Word<br>Width | UNLIMITED | 64 Bits           | UNLIMITED                | UNLIMITED                 |

The focus of this thesis is the implementation of unsigned long-word hardware multipliers more specifically using Xilinx Field Programmable Gate Array (FPGA) chips. As shown in Table 1.1, the proposed algorithm improves the generic algorithm [4] by increasing performance in terms of maximum frequency of operation. The size of the largest multiplier which can be implemented is limited only by the size of the FPGA, in terms of logic cells and arithmetic blocks used. The proposed partitioning algorithm thus increases utilization of high performance Digital Signal Processing (DSP) blocks available in Xilinx FPGA chips by breaking down long word operands into small subsets and performing multiplications on them.

#### 1. 1 Contribution

This thesis presents two algorithms which will help a system designer develop high performance unsigned long-integer word multiplier using Xilinx Virtex-4 family of FPGA. The first proposed algorithm [7] shows how to adapt the Virtex-4 architecture, in particular, DSP48 blocks, to the generic partition multiplier algorithm presented by Shuli Gao et al [4]. A second algorithm [8] further improves solutions generated by the partition algorithm by addressing the problem of placement associated with macro cells used by the proposed partition algorithm and results in an optimal arrangement reducing power, delay or area. The algorithms presented here have been verified for functionality and increase in performance. Algorithms are presented as high-level C++ source code.

#### 1. 2 Thesis Organization

This thesis is organized as follows. Chapter 2 introduces Field Programmable Gate Array technology along with a simple multiplication procedure. In Chapter 3, multiplication algorithms that are optimized for FPGA architectures are presented while Chapter 4 gives details about the architecture and arithmetic speed-up techniques available in the Xilinx Virtex FPGA. Chapter 5 elaborates on the proposed partition algorithm which is the central part of the thesis. Furthermore, Chapter 6 gives a new placement algorithm that solves the problem associated with the floorplanning of large multiplier circuits in modern FPGA. Chapter 7 demonstrates how verification was done and how results were obtained. Finally, Chapter 8 concludes the thesis and offers directions for future work.

#### 2 FIELD PROGRAMMABLE GATE ARRAYS

FPGA devices provide an ideal platform to design and test digital systems without the hassle associated with fabrication usually required for gate arrays and Application Specific Integrated Circuits (ASIC) technologies. For a long time though, FPGAs were limited to system clocks not exceeding a few hundreds megahertz but today, with the advent of smaller process technologies, a well pipelined design can go beyond the 400MHz boundary while arithmetic operations such as multiplication can easily reach 550MHz on the latest FPGA generation. In order to achieve the half Gigahertz level, FPGA designers resorted to custom sub-circuits built on the same FPGA die. These low level blocks are optimized for arithmetic operations (DSP) and data processing (microprocessor). The algorithm presented in this thesis employs arithmetic blocks, more precisely Xilinx DSP48, to perform long word multiplication in hardware.

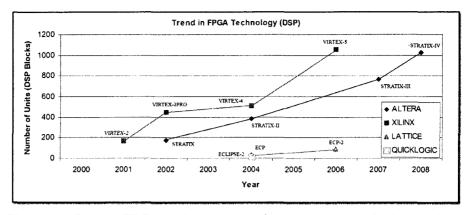

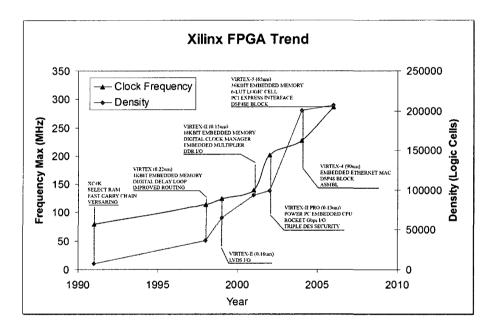

Initially, an analysis of FPGA technologies was performed with the conclusion that FPGA manufacturers had started integrating dedicated and highly optimized subcircuits into FPGA chips. This trend, which is shown in Figure 2.1, is due to the fact that smaller process technology allows for a denser FPGA and the list of practical innovations includes having high performance application-specific blocks on-chip.

Figure 2.1 Current FPGA technologies and trend towards built-in DSP blocks

Being on the same hardware support also provides the designer with the most flexible, performing, cost effective, space and power efficient solution. A microprocessor built in the FPGA chip would allow an optimal placement of the support circuitry while incurring the least amount of delay and would not require any area from the printed circuit board. As for power consumption, the microprocessor being a standard cell built using the latest process technology would give reasonable energy utilization. The choice of specialized circuits built in FPGA chips offered by manufactures includes DSP blocks, high-speed I/O, embedded memory and microprocessor blocks.

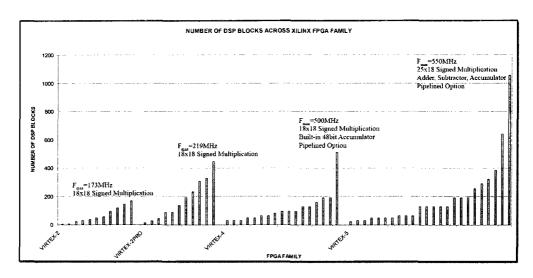

Figure 2.2 shows the trend in DSP technology for the Xilinx Virtex FPGA family across 4 generations. It clearly indicates that more DSP blocks are provided in the latest FPGA along with rising functionality and performance. From Figure 2.1, it can also be said that generally, the inclusion of these DSP blocks is done by most FPGA manufactures. Thus, it is safe to develop a suitable algorithm to solve the problem of long-word unsigned integer multiplication.

Figure 2.2 Virtex Family FPGA with amount of DSP blocks

#### 2. 1 Basic Multiplication

Multiplication is fundamentally based on a sequence of addition operations. We shall define for the purpose of explanation three positive integer variables: X (Multiplicand), Y (Multiplier) and Z (Result).

| General Multiplication Using Iterated         | Decimal Long     | Binary Long    |

|-----------------------------------------------|------------------|----------------|

| Summation                                     | Multiplication   | Multiplication |

| $Z = X \times Y$                              | 1234567          | 101010         |

| Z = 0  if  Y = 0  or  X = 0, Z = X  if  Y = 1 | 890 <sup>×</sup> | 010            |

| Z = X + X + X, Y times                        | 000000000        | 0000000000     |

| $Z = \sum_{i=1}^{Y} X_i$                      | 0111111030       | 0001010100     |

|                                               | 0987653600       | 000000000      |

|                                               | 1098764630       | 0001010100     |

One way to achieve multiplication is by iterating Y times the summation of X with itself, keeping along the way the running sums of previous steps. The time complexity of such an algorithm is N, meaning that N additions are required before a valid result is obtained. Another approach is to perform a series of base multiplications and additions. The latter is less efficient requiring the knowledge of base multiplication and powers. This is also known as the long multiplication method with time complexity of  $n\log(n)$ . With the advent of binary computers though, it became easy to implement long multiplication algorithm in hardware. The performance was also better since multiplying by the binary base is a left shift operation and the multiplication itself results in either the operand or zero. Hence the time complexity reduces to only  $\log(n)$  additions. This is an improvement over the iterated addition multiplication.

The proposed partition algorithm is based on the large-integer multiplication algorithm presented by Shuli Gao et al [4]. Presented here is an extension of the algorithm with details about an efficient technology mapping using DSP48 blocks. The placement problem which arises with the proposed partition algorithm is also solved with a greedy algorithm where area and delay are used as objective functions.

#### 3 FPGA MULTIPLICATION ALGORITHMS

Different techniques for integer multiplication in FPGA exist in literature. We will investigate only those that are required for a good understanding of the proposed algorithm as well as to provide basis for comparison since the presented architectures in the examples are all designed for FPGA technologies. Serial and array based hardware multipliers are simple algorithms that fit well FPGA implementations. The regular layout and constant amount of routing give reasonable gate delays. Moreover, specific FPGA structures such as look-up tables were initially used to accelerate multiplication operations and are based on the concept of long-hand multiplication.

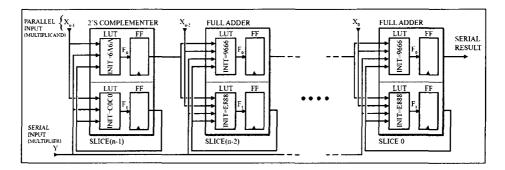

#### 3. 1 Serial-Parallel Signed Multiplier

The serial-parallel signed multiplier offers a compact implementation of the shift-and-add algorithm with very little combinational path delay. Figure 3.1 shows the regularity of the design together with little amount of interconnection between adjacent modules which allows a straight forward FPGA implementation. The system consists of parallel inputs for the multiplicand part which drive a wide bit-multiplier implemented as AND gates. This eventually feeds the first operand of cascaded Carry Save Adder (CSA) cells. The sign-extended multiplier operand is furthermore applied serially to the other input of the serial adder. The final product is obtained after m+n clock cycles, m and n being the size of the input operands.

Figure 3.1 Serial Parallel N-bit multiplier architecture

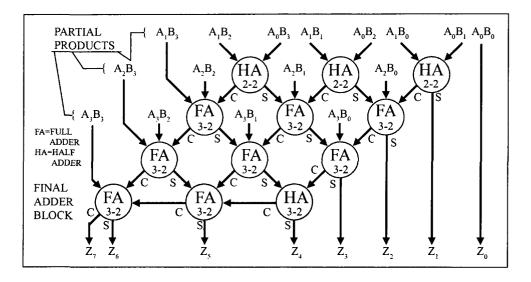

#### 3. 2 Carry Save Array Multiplier

The Carry Save Array (CSA) multiplier [7], as shown in Figure 3.2, is based on the carry save adder architecture where carry bits are propagated down the array instead of being rippled horizontally to adjacent adder cells. In principle, CSA multipliers include extra AND gates at the input of the parallel adder to create partial product words. The adder which consists of Full-Adder (FA) and Half-Adder (HA) compresses further the information into carries and sums. For each partial product row, bits are processed independently and in O(1). The final multiplication row is summed using a carry ripple adder. An FPGA implementation of a CSA multiplier involves the use of cells laid as a regular structured parallelogram. For an N x N multiplier, where N is the size of the input operands, the design is in  $O(n^2)$  cells in area. CSA multipliers have better timing characteristics compared to the classical ripple carry array multiplier with a decrease of 33% in delay.

Figure 3.2 Carry Save Array multiplier architecture

## 3. 3 Constant Coefficient Multiplier

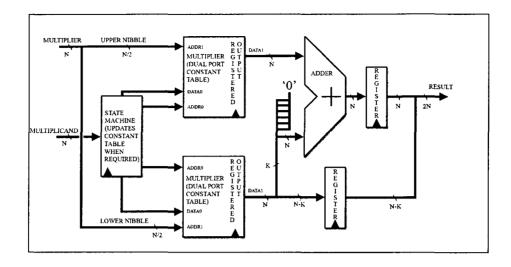

In [9], an unsigned binary multiplication technique using dynamically updated tables is described. This approach is suitable when one operand is mostly kept constant. Applications, such as video color-space conversion [8], benefit from the high throughput offered by this concept. The generated solution has a small path delay since the only arithmetic operation required is the addition of partial products. The multiplication itself is generated from RAM and hence is in O(1) time delay. The drawback of this algorithm is that in the worst case scenario 2<sup>N</sup> writes are needed to update one RAM table, N being the input size of the table. Figure 3.3 presents the architecture and makes use of two dual-ports memory blocks and a parallel adder.

Figure 3.3 N-bit constant coefficient unsigned multiplier

#### 3. 4 Partial Product Look-Up Table Multiplier

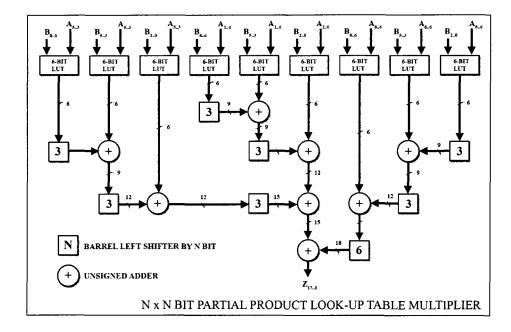

Another approach involves the use of LUTs to store permanent tables of multiplication [10], similar to algorithm [9]. As shown in Figure 3.4, partial products obtained from the table are shifted and added together as in the long-hand multiplication method. Since the table length storage depends on the input number radix, it is advantageous to use symmetric inputs so that LUT utilization is maximized. A hexadecimal-radix input will have 4 inputs for each operand, multiplicand and multiplier while containing 256 entries in the look-up table. In order to construct an arbitrary size input multiplier  $M \times M$ , one would need to use  $\lceil M/N \rceil^2$  LUTs, where N is the input size of the LUT. The intermediate stage consists of barrel shifters and cascaded parallel adders.

Figure 3.4 Architecture for Partial-Product Look-up Multiplier using 6bits LUT

The multiplier's performance depends on various factors. The number of partial products generated, how intermediate and final adders are implemented, and the relative distance between blocks all affect the critical path of the multiplier, hence the performance. Furthermore, the use of small adders helps to limit the combinatorial delay while pipelining also decreases delay but adds latency to the system. This architecture gives a very good idea how to construct large unsigned integer multiplier from smaller input multipliers.

#### 3. 5 Partition Multiplication Algorithm (Shuli-Gao et al)

The paper titled "Efficient Realization of Large Integer Multipliers and Squarers" [4] presents a methodology on how to decompose large integer unsigned multipliers using smaller size multipliers. The idea is not new and the novelty resides in the

application of FPGA technologies with embedded multiplier blocks. The performance gain from doing the decomposition is significant considering the drawbacks of alternative means such as HDL arithmetic operator (inflexible) and COREGenerator solution (limited operand size). The algorithm presented in the paper is generic and applies to any  $n \times n$  bit multiplier block, although the authors used  $18 \times 18$  bits multipliers in their model. They also showed that the same approach can be further extended to implement unsigned squarers.

The original partition algorithm is explained below. The arithmetic base used is binary. Assuming that the size of the input operand is k and is greater than n, the size of the small multiplier and k is partitioned into m segments where  $n(m-1) < k \le n \times m$ , we have therefore:

1. Inputs X and Y in binary format:

$$X = [x_{k-1}x_{k-2}...x_n...x_1x_0]; Y = [y_{k-1}y_{k-2}...y_n...y_1y_0]$$

2. X and Y grouped into k segments each sized n:

$$X = [X_{m-1}X_{m-2}...X_1X_0]^n; Y = [Y_{m-1}Y_{m-2}...Y_1Y_0]^n$$

3. X as a summation of shifted segmented binary weights

$$X = 2^{(m-1)n} X_{m-1} + 2^{(m-1)n} X_{m-2} + ... + 2^n X_1 + X_0$$

4. Y as a summation of shifted segmented binary weights

$$Y = 2^{(m-1)n} Y_{m-1} + 2^{(m-1)n} Y_{m-2} + \dots + 2^n Y_1 + Y$$

- 5. Multiplication  $Z = X \times Y$

- 6. Z in terms of binary operands X and Y:

$$Z = [x_{k-1}x_{k-2}...x_n...x_1x_0].[y_{k-1}y_{k-2}...y_n...y_1y_0]$$

7. Z in terms of binary segmented operands X and Y:

$$Z = (2^{(m-1)n} X_{m-1} + 2^{(m-1)n} X_{m-2} + \dots + 2^n X_1 + X_0).$$

$$(2^{(m-1)n} Y_{m-1} + 2^{(m-1)n} Y_{m-2} + \dots + 2^n Y_1 + Y_0)$$

8. Finally, Z fully expanded and aligned as partial products:

$$\begin{split} Z &= (2^{2n(m-1)}X_{m-1} \cdot Y_{m-1} + 2^{2n(m-2)}X_{m-2} \cdot Y_{m-2} + \ldots + 2^{2n}X_1Y_1 + X_0Y_0) + \\ (2^{2n(m-2)+n}X_{m-1} \cdot Y_{m-2} + 2^{2n(m-3)+n}X_{m-2} \cdot Y_{m-3} + \ldots + 2^{3n}X_2Y_1 + 2^nX_1Y_0) + \\ (2^{2n(m-2)+n}Y_{m-1} \cdot X_{m-2} + 2^{2n(m-3)+n}Y_{m-2} \cdot X_{m-3} + \ldots + 2^{3n}Y_2X_1 + 2^nY_1X_0) + \\ \ldots \\ (2^{nm}X_{m-1} \cdot Y_1 + 2^{n(m-2)}X_{m-2} \cdot Y_0) + (2^{nm}Y_{m-1} \cdot X_1 + 2^{n(m-2)}Y_{m-2} \cdot X_0) + \\ (2^{n(m-1)}X_{m-1} \cdot Y_0) + (2^{n(m-1)}Y_{m-1} \cdot X_0) \end{split}$$

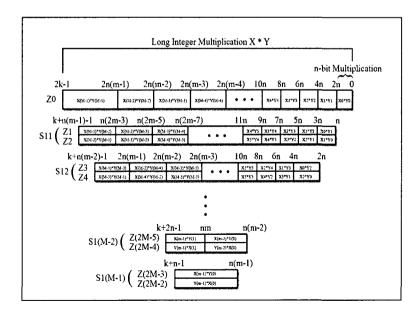

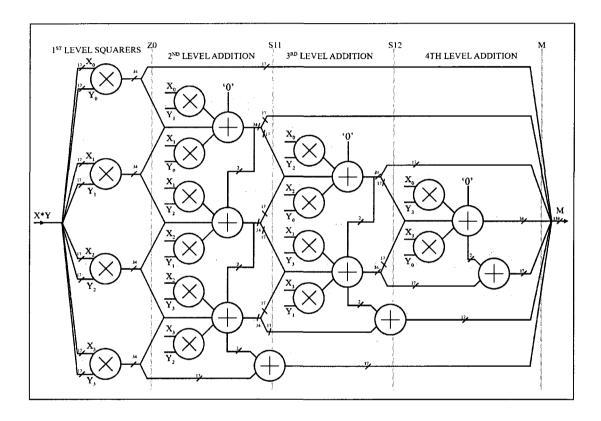

In the first statement from equation 8, all segments are squared and shifted as in  $2^{2n(m-1)}X_{m-1}\cdot Y_{m-1}$ . The second level aligns elements that are m segment off each other. This operation of alignment and addition is repeated for every pair until the furthest elements,  $X_{m-1}\cdot Y_0$  and  $Y_{m-1}\cdot X_0$  are summed at the final step. These steps are shown in Figure 3.5, where the multiplication is done on X and Y using n-bit small multiplier blocks.

Figure 3.5 Long-Integer multiplication decomposition according to [4]

As a simple example, we shall consider the multiplication of two 5bits unsigned binary number. We shall also assume that n=2 and m=3, where n is the size of the small multiplier and m is the number of partitions, obtained from  $\lceil 5/2 \rceil = 3$ . Assuming

$$X = 13_{10} = 01101_2$$

and  $Y = 25_{10} = 11001_2$ , we have  $Z = X \times Y = 325_{10} = 101000101_2$ .

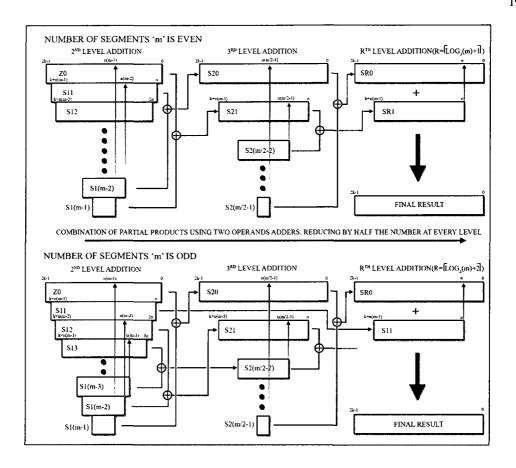

The alignment of the partial products with respect to each other is essential when using the algorithm outlined in [4]. There are mainly two situations that need to be considered: when m is even and when it is odd. In the former, the execution of the addition operation happens pair-wise with  $S_1(m-1)$  aligned with  $Z_0$ ,  $S_1(m-2)$  aligned with  $S_{11}$  and so on. In other words, for an even number m, the algorithm always aligns the smallest adder through all partial products pairs while propagating un-used bits to

the result. In other words, the symmetry obtained through the second level operands is used to efficiently perform the addition. The scheme presented in [4] reduces the number of additions by half in each stage, given m is even.

On the other hand, when m is odd, the operands are no longer in pairs. Consequently, the grouping operation which is used when m is even fails. To compensate for that, the algorithm is modified and includes an extra level of addition. Initially,  $Z_0$  is added to  $S_1(m-1)$ , skipping  $S_{11}$  and  $S_{12}$  is added to  $S_1(m-2)$ . This is iterated, with the summation of the second partial product postponed and performed at the third level. Adding the first partial product to the last guarantees the use of the smallest adder, similarly to having an even number of segments. In both cases, the total number of addition levels required by the algorithm is  $L = \lceil \log_2 m + 1 \rceil$ .

Figure 3.6 shows the addition levels needed when the number of segments 'm' is even and odd. The algorithm implements the adders in a binary tree format hence reducing combinational delay. Since the adders are made out of logic cells, the largest available in the design (S11) will constitute the critical path of the system in a pipelined design. The critical delay obtained from adder S11 is represented by [16]:

$$t_{ADDER} = t_{OPCY} + t_{BYP} \cdot (k + n(m-2)) + t_{SUM}$$

where  $t_{ADDER}$  is the total propagation time delay of the adder,  $t_{OPCY}$  is the propagation delay from the output of the function generator to the carry chain and  $t_{SUM}$  is the propagation delay from the carry chain onto the output.

FIGURE 3.6 SEQUENCE OF ADDITION OPERATION FOR ALGORITHM [4] WHEN M IS EVEN

AND ODD

Even though the algorithm outlined in [4] tries to minimize adder lengths, it does not control their implementation. More specifically, the methodology presented by Shuli Gao et al. lacks implementation details at the architectural level. The authors state that in their approach, adders at same level operate in parallel. Their algorithm was demonstrated on the Spartan-3 FPGA which contains multiplier blocks only. Also, for an m-segment multiplier,  $\lceil \log_2 m + 1 \rceil$  adder levels are needed to sum all concatenated partial products generated by the small multipliers. The Spartan-3 FPGA unfortunately does not include any high-speed adder block to perform the arithmetic operation. This is one motivation around this thesis as it is believed that the use of

embedded high-speed adders will increase the performance of the system. The DSP48 block available in newer FPGA such as Virtex-4 provides this technological edge. The algorithm outlined in this thesis also shows precisely how parallelism is achieved by pipelining the system in a systematic way.

The performance of the method presented in [4] indicates better combinational path delay and a smaller number of 4-input LUT used, compared to classical implementations such as using the VHDL multiplication operator or the Xilinx COREGenerator utility. The method in [4] relies heavily on parallelism and hence implicitly makes use of a high number of registers. This amount relies on the size of the input operand as well as the number of stages. For [4], this number is:

$$R = 2 \sum_{i=1}^{i=\lceil \log_2 m \rceil} (k - i \cdot n)$$

where R=total register count, k=size of large multiplier, n=size of small multiplier, m=number of segments. This number is non-negligible for large-input operands and negatively affects the performance of the system by increasing the amount of interconnects used in the FPGA while also raising power consumption.

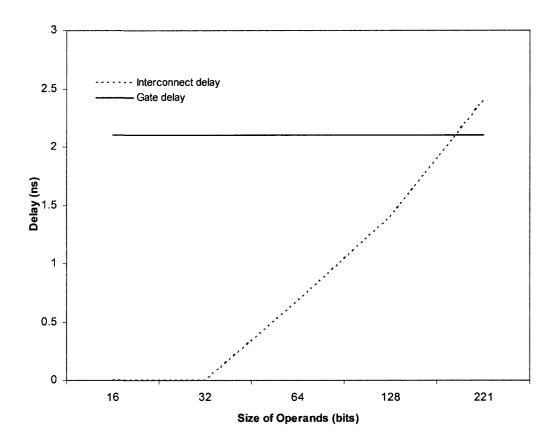

Figure 3.7 shows that with smaller process technology such as 90nm (Virtex-4) and 65nm (Virtex-5), interconnect delay contributes more to the overall system delay, hence affecting overall system performance more than in past technologies[14]. Having a good placement of multiplier blocks together with pipeline registers will in theory yield better overall performance compared to just algorithmic [4] and architectural improvements.

Figure 3.7 Graph of gate and interconnect (wire) delay versus technology for Virtex FPGA for a 16x2bit unsigned multiplier

## 3. 6 Summary of Multiplication Algorithms

This section introduced different long-integer unsigned multiplier architectures that are suitable for FPGA implementation. These techniques use architecture-specific enhancements that compensate for the main drawbacks of FPGA, which are limited interconnect resources as well as large interconnect delay. In some cases, we even see performance improvements when compared to other classic implementations such as carry-look-ahead style multipliers, which when built using the constant-coefficient method for example, will be much faster while requiring less space. Hence, knowing the basic building blocks available in the FPGA will give a deep understanding and the appropriate knowledge of how to fine-tune the device for an optimum operation. The next section presents these features that are typical in modern FPGA which are used extensively in arithmetic operations.

#### 4 XILINX VIRTEX FAMILY FPGA

The Virtex FPGA family currently at its sixth generation evolved from the XC4000E and XC5200 FPGA series. The first member of the family brought many advanced features such as Delay-Locked Loops (DLL) and discrete RAM blocks (BRAM). The internal wire bus was also re-designed to give a more accurate delay model while providing shorter run time for the routing algorithm. Features like JTAG programming and dedicated multiplication acceleration logic in the Configurable Logic Block (CLB) [11] were also built in. Two generations later, the Virtex-2 series were to incorporate discrete embedded multiplier blocks, which allowed faster DSP operations such as digital filtering. Today, the newest Virtex-5 FPGA family is built around third generation DSP blocks supported by fast routing busses and large amount of embedded memory. The proposed set of algorithms uses DSP48 blocks released in the Virtex-4 series, along with fast routing to improve on speed, area and power.

Modern FPGA chips consist of full-custom Intellectual Property (IP) blocks surrounded by an array of logic elements interconnected by an intricate network of busses. At the lowest level, the Logic Cell (LC) lays the foundation for digital synthesis providing basic structures such as Look-up Tables (LUT), Flip-Flops (FF), fast carry chains and multiplexers. Going up the hierarchy are pre-built high performance IP blocks to execute DSP operations, discrete microprocessors for data handling, high-speed interfacing and clock synthesis and re-conditioning. The underlying interconnect also designed as a hierarchy, provides up to six different types

of routing. These are segmented and have switch boxes to control the flow of data from one point to another.

FPGA are evolving every year as shown in Figure 4.1, with the newest Virtex-5 capable of 1,056 DSP48E slices along with 149,760 LUTs and FFs. The considerable amount of DSP slices together with a high DSP-to-FF ratio (1:141) enables newer algorithms to solve the problem of high speed long-word multiplication more efficiently with the help of pipelining.

Figure 4.1 Trend for Xilinx FPGA during past 16 years

### 4. 1 Logic Cells

The logic cell allows implementations of either combinational or sequential circuits or a mixture of both. Combinational systems are implemented using 4-inputs (up to 6 in Virtex-5) LUTs while state machines and registers are created out of built-in Flip-Flops. The LUT element can also act as dynamic storage devices turning into

16bits shift registers. A group of logic cells sharing arithmetic resources is called a slice. In a Virtex FPGA, logic cells within a slice have dedicated carry lines as well as shared inputs. This enables the designer to implement arithmetic operations such as addition and multiplication with small delay penalty while extending the size of the operation. Also, slices are grouped into Configurable Logic Blocks (CLB) and share routing structures.

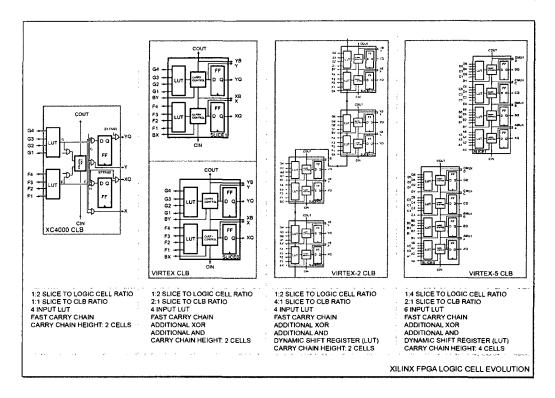

The basic structure of the logic cell has evolved from a simple two-cell CLB to four then eight cells. The progression among the Xilinx Virtex FPGA family is shown in Figure 4.2, where differences between architectures are highlighted. In addition, arithmetic capability is enhanced with the inclusion of XOR and AND gates for arithmetic addition (Full-Adders based) and 1-bit multiplication respectively. Initially, the XC4000E FPGA included a dedicated carry path that introduced little delay in arithmetic operations. This has since then been added to all subsequent FPGA families. Finally, the newest Virtex-5 FPGA provides faster overall arithmetic operation since the carry path spans four logic cells compared to two in the previous families. This reduces by half the amount of interconnect delay that would be present should the operation be implemented in previous Virtex families.

Figure 4.2 Xilinx FPGA logic cell evolution during past 15 years

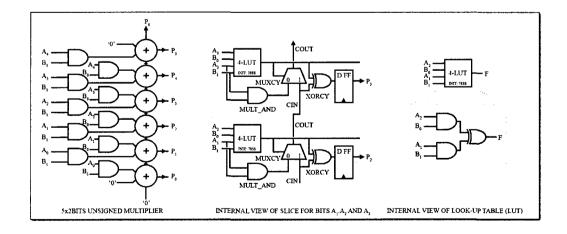

## 4. 2 Virtex Hardware Arithmetic

High performance arithmetic operation is achieved through different architectural speed-up techniques built in the Virtex architecture. A logic cell contains extra 2-inputs AND and XOR gates, which process incoming bits, for multiplication and addition without committing an LUT [12]. This makes the design area efficient while reducing the combinational delay. Since most hardware multiplication algorithms are addition based, performance gain is further obtained when multiplication operations use adder blocks. The knowledge of FPGA infrastructures also enables an efficient implementation of arithmetic operations. For instance, addition operations are accelerated through the use of high-speed carry chains [15] which span the vertical

height of the chip while proper placement of arithmetic cells decreases interconnect delay if adjacent cells are packed together in a CLB. The proposed placement algorithm combines layout information with the HDL code so that an optimum placement is achieved within the CLB. The algorithm then places larger CLB based blocks in an optimal arrangement so as to decrease interconnect delay.

Figure 4.3 gives the internal structure of a CLB built in the Virtex FPGA. It shows how a single slice can implement a 3 x 1 bit multiplier using the adder cell (4-LUT, XORCY, MUXCY) together with an extra AND gate (MULT\_AND). This can be furthermore cascaded to extend the length of the multiplier. The critical path is along the carry propagate chain and is obtained from:

$$t_{MULT-2N} = t_{ILO} + t_{BXCY} \cdot n(t_{BYP}) + t_{ILO} + t_{BXCY}$$

where  $t_{MULT\_2N}$  is total propagation delay of the 2xN multiplier,  $t_{ILO}$  is the propagation delay of the 4-inputs look-up table (LUT),  $t_{BXCY}$  is the propagation delay of output BX of LUT onto the carry chain and  $t_{BYP}$  is the propagation delay per carry-chain multiplexer.

Figure 4.3 Hardware dedicated for arithmetic operations in Virtex FPGA

Conventional synthesis tool such as XST uses this technique to create adders and eventually allows multipliers of arbitrary length to be created. This is a limitation since higher performance can be achieved if the tool is aware of implementations based on dedicated arithmetic blocks such as the DSP48.

#### 4. 3 Xilinx DSP48 Arithmetic Block

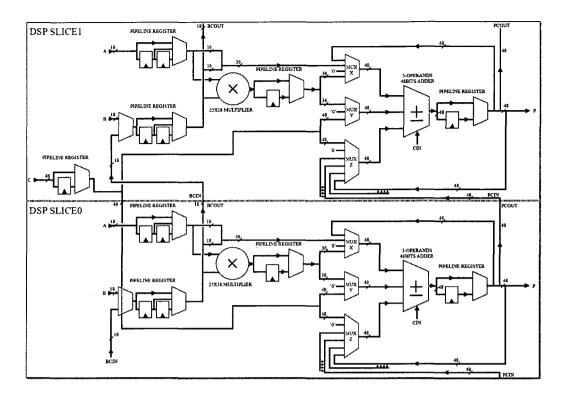

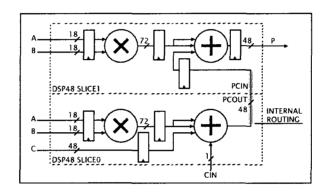

The partition algorithm outlined in this thesis is based on the DSP48 block found in the Virtex-4 FPGA. Also known as DSP48 tile, the block contains a multifunctional arithmetic unit capable of 18bits signed multiplication as well as three operands 48bits sign-extended addition-subtraction-accumulator. The unit is optimized for low power, high speed operation and offers pipelining at inputs, intermediate levels and outputs. Internally, the DSP48 tile includes two slices each with a set of multiplier and adder. The slice pair also shares internal connections which are used when arithmetic operations exceeding the normal size of the slice are implemented.

As shown in Figure 4.4, the internal structure of a DSP48 slice reveals that the three operands 48bits adder can only add two operands if used with the multiplier since the two partial products generated from the multiplier block are combined by the adder. The proposed algorithm uses internal pipelining registers when required for the highest performance.

Figure 4.4 Internal view of Virtex-4 DSP48 tile (block) [17]

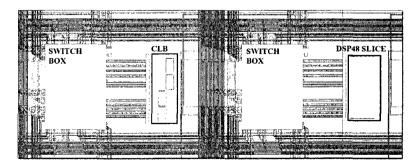

Figure 4.5 gives the internal view of a Xilinx Virtex-4 FPGA chip, as obtained from FPGAEDITOR [30]. The height of a DSP48 tile is equivalent to that of four CLBs [34], or eight slices. Since one tile consists of two DSP48-slices, we can calculate the height of a single DSP48 slice to be that of 4 logic-slices, with a width of 1 logic-slice. This is clearly indicated in Figure 4.5.

Figure 4.5 DSP48 slice to CLB area ratio, as shown in Xilinx FPGAEDITOR [35]

The internal operation of the DSP48 tile is fully programmable with the help of OPMODE and CARRY bits. The OPMODE defines how inputs X, Y and Z are used. X and Y each has two bits dedicated to their internal configuration and can be programmed in six different modes. The output from the X multiplexer can be zeroed, coming from the first partial-product multiplier, coming from port P or be concatenated with B. Similarly, the Y multiplexer allows only three valid combinations; zeroed, propagating the second partial-product or outputting port C. The OPMODE also controls the Z multiplexer and has 3bits reserved for it. Out of eight possibilities, only six are used with the actual combination shown in Table 4.1.

TABLE 4.1 VALID OPMODE FOR DSP48 BLOCK, WITH RESPECT TO Z MULTIPLEXER [18]

| OPMODE<br>PROGRAMMING BITS |    |    | Z MULTIPLEXER OUPUT<br>DRIVING |  |  |

|----------------------------|----|----|--------------------------------|--|--|

| Z                          | Y  | X  | ADDER/SUBTRACTOR               |  |  |

| 000                        | XX | XX | ZERO (DEFAULT)                 |  |  |

| 001                        | XX | XX | PCIN                           |  |  |

| 010                        | XX | XX | P                              |  |  |

| 011                        | XX | XX | С                              |  |  |

| 100                        | XX | XX | ILLEGAL SELECTION              |  |  |

| 101                        | XX | XX | PCIN SHIFT                     |  |  |

| 110                        | XX | XX | P SHIFT                        |  |  |

| 111                        | XX | XX | ILLEGAL SELECTION              |  |  |

Table 4.2 gives the configuration bits of the second and third operand multiplexes driving the adder (MUX X, MUX Y). In order to program the DSP block to perform  $f = P \pm (A \times B + C_{IN})$ , the following bits would be needed in the OPMODE register: 0100101.

TABLE I. TABLE 4.2 VALID OPMODE FOR DSP48 BLOCK, WITH RESPECT TO X AND Y MULTIPLEXER [19]

| OPMODE BITS |    | ITS | Z MULTIPLEXER OUPUT<br>DRIVING           |  |  |  |

|-------------|----|-----|------------------------------------------|--|--|--|

| Z           | Y  | Х   | ADDER/SUBTRACTOR                         |  |  |  |

| XXX         | XX | 00  | ZERO (DEFAULT)                           |  |  |  |

| XXX         | 01 | 01  | MULTIPLIER OUTPUT<br>(PARTIAL PRODUCT 1) |  |  |  |

| XXX         | XX | 10  | P                                        |  |  |  |

| XXX         | XX | 11  | A CONCATENATE B                          |  |  |  |

| XXX         | 00 | XX  | ZERO (DEFAULT)                           |  |  |  |

| XXX         | 01 | 01  | MULTIPLIER OUTPUT<br>(PARTIAL PRODUCT 2) |  |  |  |

| XXX         | 10 | XX  | ILLEGAL SELECTION                        |  |  |  |

| XXX         | 11 | XX  | С                                        |  |  |  |

Finally, Table 4.3 shows configuration bits for the CARRYINSEL register which controls how the carry input is connected to the adder. Furthermore, the mode of operation for the carry input is dependent on the value entered in the OPMODE register.

${\sf TABLE~4.3~CARR\,YINSEL~CONTROL~BITS~WITH~CORRESPONDING~OPMODE~OPERATION~[20]}\\$

| CARRY-<br>INSEL [1:0] | OPMODE                                                 | CARRY<br>SOURCE        | COMMENTS                                                        |

|-----------------------|--------------------------------------------------------|------------------------|-----------------------------------------------------------------|

| 00                    | xxxxxxx                                                | CARRYIN                | GENERAL FABRIC CARRY<br>SOURCE (REGISTERED OR NOT)              |

| 01                    | Z MUX OUTPUT = P OR<br>SHIFT (P)                       | ~P[47]                 | ROUNDING P OR SHIFT(P)                                          |

| 01                    | Z MUX OUTPUT = PCIN OR<br>SHIFT(PCIN)                  | ~PCIN[47]              | ROUNDING CASCADED PCIN OR<br>SHIFT(PCIN) FROM ADJACENT<br>SLICE |

| 10                    | X AND Y MUX OUTPUT =<br>MULTIPLIER PARTIAL<br>PRODUCTS | A[17]<br>XNOR<br>B[17] | ROUNDING MULTIPLIER (MREG<br>PIPELINE REGISTER DISABLED)        |

| 11                    | X AND Y MUX OUTPUT =<br>MULTIPLIER PARTIAL<br>PRODUCTS | A[17]<br>XNOR<br>B[17] | ROUNDING MULTIPLIER (MREG<br>PIPELINE REGISTER ENABLED)         |

| 10                    | X MUX OUTPUT = A:B                                     | ~A[17]                 | ROUNDING A:B (NOT<br>PIPELINED)                                 |

| 11                    | X MUX OUTPUT = A:B                                     | ~A[17]                 | ROUNDING A:B (PIPELINED)                                        |

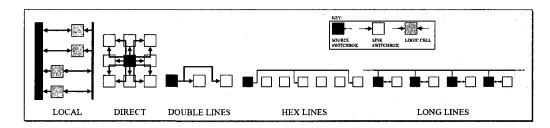

#### 4. 4 Interconnect

The present work describes a placement algorithm which requires a clear understanding of the wire infrastructure available in the Virtex FPGA. The interconnect network can be seen as a hierarchy of wire connecting CLBs, DSP48s, clock generators, Input/Output ports and so on together.

## Hierarchy of interconnect [13]:

- (a) Local Routing (High speed)

- 1.1 Connection between LUTs, Flip-Flops and General Routing Matrix (GRM) switch box.

- 1.2 Internal CLB feedback routes connecting output to LUT input with minimum delay.

- 1. 3 Direct path between horizontal adjacent CLBs (Virtex).

- 1. 4 Direct path between adjacent CLBs in sixteen directions (Virtex-II and above) [21].

- (b) General Purpose Routing (Low-medium speed)

- 1. 5 Routing between GRM switch boxes.

- 1. 6 Single-length lines connecting adjacent GRMs in four directions.

- 1. 7 Buffered Hex lines connecting GRM to other GRMs placed six blocks further in each of the four directions.

- Buffered Longlines bidirectional wires that span the full length of the FPGA chip either horizontally or vertically.

- (c) Global Routing (Low skew)

- 1. 9 Primary global routing includes high-fanout signal lines such as clock networks and are designed to have minimal skew.

- 1. 10 Secondary global routing is mainly secondary clock routing consisting of backbones lines distributed across the top and bottom portion of the FPGA. They connect to Longlines interconnect.

- (d) Dedicated Routing (High speed)

- 1. 11 Constrained interconnect for the arithmetic carry chain.

- 1. 12 Horizontal routing for three-state busses.

- 1. 13 Dedicated SOP chain for each slice row [21].

- 1. 14 Shift-chain routing, one per CLB [21].

The proposed placement algorithm relies on adjacently placed CLBs to minimize interconnect delay and consequently falls into the Local Routing class. Moreover, Dedicated Routing is implicitly used by the carry chain infrastructure in the realization of adders and DSP48 blocks. Figure 4.6 shows fives types of routing technologies found in the Virtex-2 FPGA. Since the Virtex-4 is based on the same routing infrastructure, a placement algorithm that first uses local, then direct, double, hex and finally long lines will reduce overall interconnect delay and hence improve on timing performance.

Figure 4.6 Different interconnect classes found in the Virtex family of FPGA [21].

## 4. 5 Congestion

Congestion is a concentration measure of active interconnects in part of the routing resource. It negatively affects performance since a congested region is very unlikely to allow free routing of wires or would provide so with heavy delay penalty. Congestion also decreases area utilization because CLB is eventually used in the most congested regions as passthrough logic, logic that acts as simple wires to add extra routing resources. This quick-fix increases the interconnect delay significantly and should be used as a last resort.

Anticipating congestion and increasing the region allocated to routing resources minimize most of the effect. The placement algorithm uses congestion as an objective function, where a slack region between CLBs is added if congestion is high. The placement algorithm models congestion using graph theory with congestion defined as the number of vertices sourced or sank at a node per unit area.

## 4. 6 Summary of Techniques

This chapter presented the Virtex FPGA family at the low level, giving information about logic cell, arithmetic implementation techniques, the DSP48 block, the routing infrastructure and finally congestion. The focus of this thesis is to present an algorithm that will increase performance of long-integer multiplication operations. Using DSP48 blocks provide the user with processing elements that have the lowest delay, power and area. On the other hand, care should be taken in order not to increase

interconnect delay which would negate the use of DSP48 blocks. Hence, knowledge of the routing hierarchy as well as an understanding of congestion is essential.

#### 5 PARTITION ALGORITHM FOR VIRTEX-4 FPGA

The algorithm for partitioning unsigned multiplication operations is originally proposed by Shuli-Gao et al [4] and solves the problem using small but high-performing DSP blocks abundantly found in modern FPGAs. The algorithm is generic in nature and hence does not specify with what technology the actual addition and multiplication operations are implemented. The algorithm is also modified depending on whether m is even or odd, m being  $\lceil k/n \rceil$ , k being the size of the large multiplier input operand and n being the size of the small multiplier input operand. In case of m being odd, an extra adder level is needed. Finally, the generated multiplier relies on pipelining to reduce combinational delay as the circuit is in the form of an array multiplier, similar to the Carry Save Array multiplier. The algorithm can be expressed as:

$$Z = X.Y = \sum_{i=0}^{m-1} 2^{(k.i)} X_i \sum_{i=0}^{m-1} 2^{(k.i)} Y_i, m = \left\lceil \frac{k}{n} \right\rceil - 1$$

$$= \sum_{i=0}^{m-1} 2^{2ni} X_i \cdot Y_i + \sum_{i=0}^{m-1} \sum_{j=0}^{m-i-1} 2^{(i+1+2j)n} [(X_{i+j+1} \cdot Y_j) + (X_j \cdot Y_{i+j+1})]$$

where Z is the output of the large integer multiplier, k is size of the operand at the large multiplier input and n is size of the small multiplier.

Our proposed algorithm adapts [4] to use the more efficient DSP48 block available in Virtex-4 FPGAs. This gives better overall performance since DSP48 is superior to the multiplier circuits available in the Spartan-3 FPGA. The physical location of hardware blocks is also crucial in order to get an optimal result. Using DSP48 allows the software mapper to lock blocks in reserved vertical regions which

minimizes the amount of interconnect. Since the partition algorithm does not include locality information, a second algorithm is described in this thesis that adds placement information. This reduces interconnect delay caused by pipelining structures used by the partition algorithm as well as in groups participating in the critical path.

## 5. 1 Details of Operation

From the original algorithm, dataflow can be separated into different operation levels. This is also true in the proposed partition algorithm and initially, the multiplication of all sub-words of length m, m being the length of our DSP48 block operand, into their respective squares,  $Z_0$ , is summed to the product of  $X_i$  with  $Y_{i+1}$  and  $X_{i+1}$  with  $Y_i$ , where  $0 \le i < N$ , N=number or levels of multiplication,  $X_i$  and  $Y_i$  are sub-words from the long-integer numbers, into the partial word,  $Z_1$ . At the third level,  $Z_1$  is added with  $X_i * Y_{i+2}$  and  $X_{i+2} * Y_i$  where  $0 \le i < N-1$ . Additions at each stage is repeated in the same way until only a single addition/multiplication level is left which happens at i=0. This generates the middle range values for the multiplication. At each level, an extra adder is required to sum the carry bit of the current level with the most significant bit of the previous partial product.

Since DSP48 multipliers operate with signed 18bits values, our implementation can only use the lower 17bits with the sign (most significant) bit connected to logic '0'. This results in the length of the input operand 'm' being equal to 17. The proposed algorithm performs all the required steps for partitioning long integer numbers including the creation of interconnects between DSP48 blocks and inclusion of intermediate pipeline registers.

The multiplier as well as adder blocks can be reorganized as shown in Figure 5.1. There is also a noticeable change in the proposed architecture, which removes the necessity of having to deal with odd and even number of segments (m). This is required because the original architecture does not allow for a direct combination of adders and multipliers blocks into a unified module.

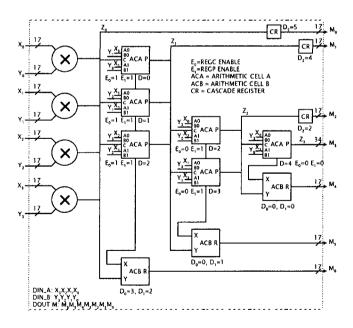

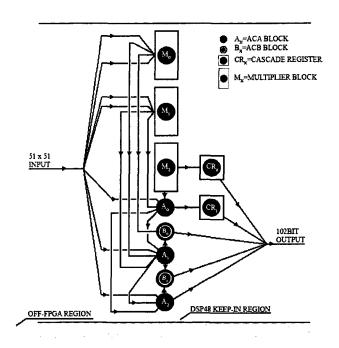

Figure 5.1 Technology mapping of [4] into proposed architecture for a 68bits unsigned multiplier

As presented in this algorithm, the innovative aspect is the mergence of the addition block together with the multiplication block into a single entity: the Arithmetic Cell A (ACA). This is very different from the architecture proposed in [4], where no implementation details are given. A single DSP48 tile can therefore be

effectively used as a three operands adder with two inputs coming from 17bits multipliers. The resulting architecture shown in Figure 5.2 uses built-in pipeline registers and takes advantage of the dedicated routing infrastructure by making use of internal connection for data propagation between adjacent DSP48 slices. Using internal pipeline registers also decreases the amount of interconnect hence reducing congestion. Overall power consumption is also reduced when using built-in pipeline registers since the DSP48 tile is power optimized.

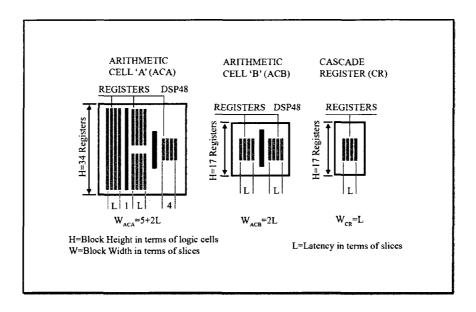

Figure 5.2 DSP48 tile internal configuration

The DSP48 block is configured to perform the sum of three operands with two of them obtained from unsigned multipliers. The operation is speed-up by the use of built-in high-speed adders with integrated carry chain. The main drawback present in the original algorithm which was implemented in the Spartan-3 FPGA is thus mitigated with the use of the more powerful Virtex-4 DSP48 block. Internally, SLICE0 is configured to multiply the words A0 and B0 with the resulting product added to the summation of CIN with the C input. The result at the output of the DSP48 tile includes a carry out as the two most significant bits along with the final sum of length 2m, m being the length of the DSP48 input operand.

The functionality of the DSP48 block is programmed at compilation time with attributes for the operation mode and carry type written as attributes in the hardware descriptive language source. Table 5.1 gives binary values for the OPMODE as well as that of the CARRY register. Once set, they will control how the internal datapath of the DSP48 is setup and also, which registers are enabled.

TABLE 5.1 OPMODE/CARRY CONFIGURATION BITS FOR SLICE0 AND SLICE1

| SLICE         |        | CONFIGURATION BITS |   |       |   |   |   |   |   |

|---------------|--------|--------------------|---|-------|---|---|---|---|---|

| CONFIGURATION | OPMODE |                    |   | CARRY |   |   |   |   |   |

|               | 6      | 5                  | 4 | 3     | 2 | 1 | 0 | 1 | 0 |

| SLICE0        | 0      | 1                  | 1 | 0     | 1 | 0 | 1 | 0 | 0 |

| SLICE1        | 0      | 0                  | 1 | 0     | 1 | 0 | 1 | 0 | 0 |

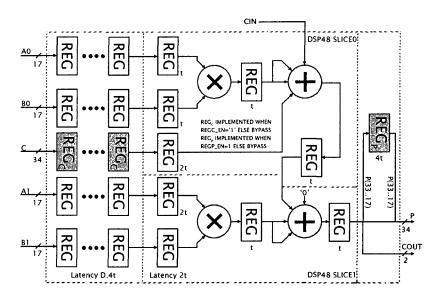

## 5. 2 Arithmetic Cell A Block

The proposed algorithm defines two types of arithmetic cells which are based on the Virtex-4 DSP48 block. Arithmetic Cell A (ACA) (Figure 5.3) encapsulates the operation:

$$P = (A_0 \cdot B_0) + (A_1 \cdot B_1) + C$$

Eq. 1

The total latency is equal to that of SLICE0 combined with SLICE1 and results in 4 registers. The external registers on A0, B0, C, A1, B1 inputs are needed in order to synchronize the arrival of data at the DSP48 tile, with respect to their internal latency. Furthermore, registers REG<sub>C</sub> and REG<sub>P</sub> are optional. REG<sub>P</sub> is needed when ACA is used internally and not in the last column while REG<sub>C</sub> is required at the second level only. The proposed algorithm generates the correct ACA block with the use of E<sub>0</sub> (Enable of REG<sub>C</sub>) and E<sub>1</sub> (Enable of REG<sub>P</sub>). REG<sub>P</sub> is also of constant depth (4 registers) which equals to the latency of one DSP48 tile. The input of REG<sub>P</sub> is taken

from the most significant 17bits of output P and ranges from bit P<sub>17</sub> to bit P<sub>33</sub>. The output of REG<sub>P</sub> is then reconnected to signal P, hence delaying only the upper part of P when needed. If REG<sub>P</sub> is disabled, then the output of the DSP48 tile bypasses REG<sub>P</sub> and connects directly to the product P. COUT represents carry-out bits and connects the two most significant bits of P to adjacent ACA and ACB blocks. CIN is the carry input of ACA and is internally pipelined by the DSP48 slice.

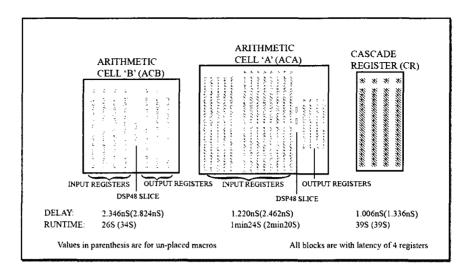

Figure 5.3 Internal view of Arithmetic Cell A block

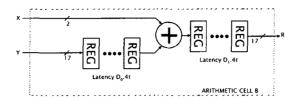

## 5.3 Arithmetic Cell B Block and Cascade Register

The Arithmetic Cell B (ACB) (Figure 5.4) performs the operation R = X + Y (Eq. 2). Input X is unregistered and connects directly to the first operand of the adder block. Input Y conversely has registers m-bits wide and of depth  $D_0$  which connects to the second operand of the adder. The result R at the output can also be registered with a depth of  $D_1$ . A single DSP48 slice is sufficient to perform the addition operation

together with some pipelining (4 registers). Alternatively, the adder can be constructed using logic cells.

Figure 5.4 Internal view of Arithmetic Cell B block

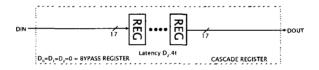

The proposed partitioning algorithm finally makes use of a third type of block, the Cascade Register (CR) (Figure 5.5). It consists of a series of cascaded registers of fixed width (m) and of variable depth D<sub>2</sub>.

Figure 5.5 Internal view of Cascade Register block

## 5. 4 Partition Algorithm Description

When run at a high level, the time complexity of the algorithm is in  $O(N^2)$  while requiring constant amount of space, hence in O(1) space-wise. Initial parameters are needed for the input length of operands (n) and the size of the small multiplier (m). The algorithm is described in pseudo code format in the Algorithm 1a listing. First, the number of levels (N) is calculated in line 1. Then, input segments of length m are squared together to produce  $Z_0$  (lines 2 to 4). This is accomplished by using N

unsigned multipliers created from DSP48 tiles, where N=number of levels, resulting in an aggregated 2mN partial product word, where m is the small multiplier operand size, representing the square of the input values grouped with length 2m.

```

Algorithm 1a Proposed Partition Algorithm

1.

2.

For i=0 to N-1 loop

Z_0(2m(i+1)-1...2mi)=DIN_A(m(i+1)-1...mi)*DIN_B(m(i+1)-1...mi)

3.

4.

End for

M(16..0)=Z_0(16..0)

5.

Latency D_2=2N-1

7.

For i=0 to N-1 loop

For j=i to N-1 loop

8.

9.

Generate Arithmetic Cell A (ACA)

10.

If i=0 then E_0=1 else E_0=0

11.

If i=N-1 then E_1=0 else E_1=1

12.

Latency D=i+i

A0=DIN \ A(m(j-i+1)-1 ... m(j-i))

13.

14.

B0=DIN B(m(j+2)-1 ... m(j+1))

AI = DIN_A(m(j+2)-1 ... m(j+1))

15.

B1=DIN B(m(j-i+1)-1 ... m(j-i))

16.

C=Z_i(2m(j-i+1)+m-1 .. m(2(j-i)+1))

17.

18.

Z_{i+1}(2m(j-i+1)-1 ... 2m(j-i))=P

19.

CIN=C_i(2(j-i)); C_i(2(j-i+2)-1 ... 2(j-i+1))=COUT

20.

End for

Generate Arithmetic Cell B (ACB)

21.

If i=0 then D_0=3 else D_0=0; D_1=N-i-1

22.

X=CIN(2(j-i+1)-1 ... 2(j-i))

23.

24.

Y=Z_i(m(2(j-i)+2)-1 ... m(2(j-i)+1))

25.

M(m(2N+2-i)-1 ... m(2N-i+1))=R

26.

Generate Cascade Register (CR)

27.

D_2=2(N-i-1)

DIN=Z_{i}(16..0)

28.

M(m(i+2)-1 ... m(i+1))=DOUT

29.

30. End for

```

Line 6 represents the first partial product generated, as obtained from  $Z_0$  and completes part of the output M of the large multiplier. Two nested loops (lines 7,8) then take care of producing the main array multiplier. Iterator 'i' goes from 0 to N-1 while 'j' starts from i and ends at N-1. The main purpose of j is to generate multipliers across a particular level while i iterates through the levels. Furthermore, blocks of type ACA (line 9), ACB (line 21) and CR (line 26) will be generated at each level. For the first level (line 10), pipeline registers are present on all inputs of the ACA blocks. In

every step, the latency D of the block is calculated with the formula D = i + j, while inputs to the ACA block are taken either from the large input word (m) or from the result obtained at the previous level (line 13 through 17). The output at each ACA block from one level consists of  $Z_{i+1}$  and carry-lines, which are propagated through adjacent ACA blocks. At each level, an ACB-CR block pair is required to sum the current carry information with the previous data obtained and to delay the resulting data respectively (line 21 to 28). ACB blocks are positioned at the end of the column while CR blocks are placed at the beginning. Finally, the output from both CR and ACB blocks drives the final output of the large multiplier (M).

Figure 5.6 shows a long-integer multiplier of size 68bits generated using the proposed algorithm. The structure consists of 4 levels, including the squarers at the input, and intermediate levels consisting of ACA, ACB and CR blocks. The output is obtained at M after 5 latency cycles.

Figure 5.6 Long-integer 68x68bits multiplier generated by proposed algorithm

## 5. 5 Resources Utilization

The amount of FPGA resources needed for a multiplier generated by the algorithm can be derived in terms of the input word length n, the DSP48 operand size m and the number of levels N.

| Number of levels (N) = $\left\lceil \frac{n}{m} \right\rceil - 1$          | Eq. 3  |

|----------------------------------------------------------------------------|--------|

| Number of input multipliers = N+1                                          | Eq. 4  |

| Number of Arithmetic Cell A blocks = $\frac{N(N+1)}{2}$                    | Eq. 5  |

| Number of Arithmetic Cell B blocks = N                                     | Eq. 6  |

| Number of DSP48 slices used (ACB implemented with logic cells) = $(N+1)^2$ | Eq. 7  |

| For a pipelined design, the algorithm further defines the following terms: |        |

| DSP48 block latency (L) = 4                                                | Eq. 8  |

| Number of Cascade Register blocks = N                                      | Eq. 9  |

| Total pipeline latency = $4(2N-1)$                                         | Eq. 10 |

# 5. 6 Performance Equations

The following equations describe the performance of the proposed partition algorithm when the width 'n' is changed, while m, the size of the DSP48 input is kept constant. In the equations, L=4 and represents the latency of a DSP48 block.

Number of levels (N) =

$$\left\lceil \frac{n}{m} \right\rceil - 1$$

Eq. 11

Number of multiplier blocks =

$$\frac{N^2}{2} + 3N + 1$$

Eq. 12

Number of registers for pipeline design=

$$mL((\sum_{j=0}^{N-1}\sum_{i=j}^{N-1}4(i+j)+1)+N^2-N-1)$$

Eq. 13

Worst case combinational delay

$$T_P = T_{DSPDO-BPL}$$

ns Eq. 14

Maximum frequency of operation

$$F_{MAX} = \frac{1}{T_{DSPCKO\_PCOUTP} + T_{DSPDO\_BPL} + T_{DS}}$$

MHz Eq. 15

,where  $T_{\rm DSPDO\_BPL}, T_{\rm DSPCKO\_PCOUTP}$  and  $T_{\rm DS}$  are defined in [33].

## 5. 7 Non-Pipeline Design

From Eq. 13, a generated design has an area that exhibits a quadratic behaviour in N. Instead, the design can also be used with less pipelining stages. This is a trade-off of area against speed of operation. As such, the proposed partition algorithm is modified for a non-pipelined design, with the configuration of the DSP48 blocks also changing in order to reflect this, as shown in Algorithm 1b.

```

Algorithm 1b Proposed Partition Algorithm (Non-Pipelined)

```

```

1.

2.

For i=0 to N-1 loop

Z_0(2m(i+1)-1...2mi)=DIN_A(m(i+1)-1...mi)*DIN_B(m(i+1)-1...mi)

3.

4.

End for

5.

M(16..0)=Z_0(16..0)

For i=0 to N-1 loop

7.

For j=i to N-1 loop

8.

Generate Arithmetic Cell A (ACA)

9.

A0=DIN_A(m(j-i+1)-1 ... m(j-i))

10.

B0=DIN B(m(j+2)-1 ... m(j+1))

11.

A1=DIN A(m(j+2)-1 ... m(j+1))

12.

B1=DIN B(m(j-i+1)-1 ... m(j-i))

13.

C=Z_i(2m(j-i+1)+m-1 .. m(2(j-i)+1))

14.

Z_{i+1}(2m(j-i+1)-1 ... 2m(j-i))=P

15.

CIN=C_i(2(j-i)); C_i(2(j-i+2)-1 ... 2(j-i+1))=COUT

16.

End for

17.

Generate Arithmetic Cell B (ACB)

X=CIN(2(j-i+1)-1 .. 2(j-i))

18.

19.

Y=Z_i(m(2(j-i)+2)-1 .. m(2(j-i)+1))

20.

M(m(2N+2-i)-1 ... m(2N-i+1))=R

21.

Generate Cascade Register (CR)

22.

M(m(i+2)-1 ... m(i+1))=Z_i(16 ... 0)

23. End for

```

Synthesis results as obtained from the Xilinx ISE tool [30] show that timing performance for the proposed algorithm decreases when compared to an implementation such as using the multiplication operator as obtained from the HDL library. The timing result of our proposed implementation is still better than solutions obtained from COREGenerator.

TABLE 5.2 PERFORMANCE RESULTS FOR COMBINATIONAL DELAY, NON-PIPELINED DESIGNS

| Multiplier Width                                  | 34bits   | 64bits   | 136bits  | 221bits   |

|---------------------------------------------------|----------|----------|----------|-----------|

| Proposed Algorithm                                | 10.195ns | 22.948ns | 73.069ns | 111.428ns |

| Implementation using VHDL multiplication operator | 9.514ns  | 15.190ns | 21.925ns | 28.485ns  |

| COREGenerator                                     | 10.596ns | 40.742ns | N/A      | N/A       |

TABLE 5.3 PERFORMANCE RESULTS FOR AREA UTILIZATION, NON-PIPELINED DESIGNS

| Multiplier Width                                  | 34bits    | 64bits     | 136bits    | 221bits     |  |

|---------------------------------------------------|-----------|------------|------------|-------------|--|

| Proposed Algorithm                                | 16 Slices | 64 Slices  | 256 Slices | 676 Slices  |  |

| Implementation using VHDL multiplication operator | 16 Slices | 143 Slices | 800 Slices | 2288 Slices |  |

| COREGenerator                                     | 16 Slices | 64 Slices  | N/A        | N/A         |  |

As shown in Table 5.3, a design generated by our algorithm (non-pipelined) does not consume any logic cell with all arithmetic operations taking place in DSP48 blocks. The table uses the logic slice to DSP48 slice ratio of 4:1, as introduced in Chapter 4.3.

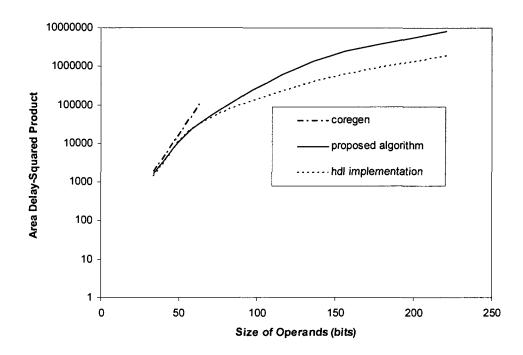

The delay product (AT<sup>2</sup>) is given in Figure 5.7 and shows the performance of three non-pipeline implementation methods. When measured in AT<sup>2</sup>, the proposed algorithm for non-pipelined designs is actually worse than HDL and Coregen implementations. This is so since the DSP48 block is highly optimized for pipelining operations, which is not the case here.

Figure 5.7 Area-Delay product for non-pipeline multipliers

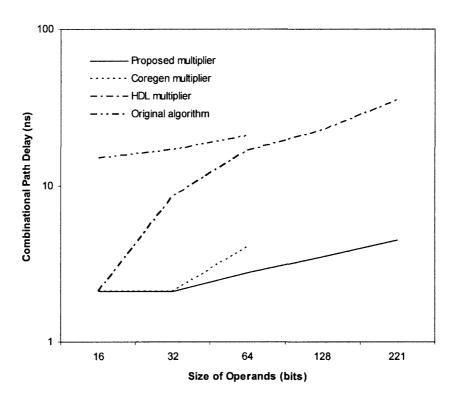

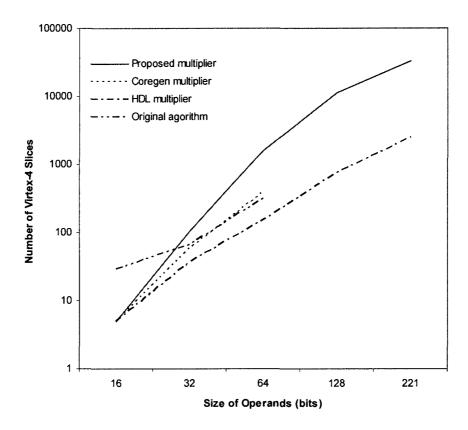

#### 5. 8 Results

The partition algorithm presented was originally designed to use a pipelined architecture. This was decided since the building block itself, the DSP48, is optimized for pipelining under which it will operate at a theoretical 500MHz. With the following figures, the reader will get an idea of how well multipliers generated by the algorithm perform against classical implementations which are readily available to the designer. For comparison, designs with input width of 34bits, 68bits, 136bits and 221bits were chosen because they are very close to practical multiplier lengths while at the same time, are multiplies of the DSP48 block input size. Classical implementations were obtained from two sources:

- (a) Components generated from the COREGenerator utility [30].

- (b) VHDL synthesis of the multiplication operator, as provided by the language's arithmetic library.