## Design and Hardware Implementation Of a Cooperative Communication System

Binbin Jia

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science (Electrical Engineering) at

Concordia University

Montreal, Quebec, Canada

March 2007

© Binbin Jia, 2007

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-28917-4 Our file Notre référence ISBN: 978-0-494-28917-4

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **ABSTRACT**

# Design and Hardware Implementation Of a Cooperative Communication System

#### Binbin Jia

Multiple Input, Multiple Output (MIMO) antenna systems have been widely studied. They play a key role in the next generation communication systems because of their capability to provide an extremely high capacity. However, the cost of using a large number of antennas should be considered when MIMO is put into practice. In order to reduce the cost of devices, there is another method called cooperative communication.

In a cooperative communication system, each single antenna (node) shares its information with its nearby antennas (nodes), and then those antennas transmit together their data towards the destination, therefore, they generate a virtual MIMO system. In this thesis, we present a new framework, which is a combination of the detect-forward cooperative method, channel coding, and space time coding methods. We assume that the cooperative system includes an inter-user channel (between nodes) and an uplink channel (from the nodes to the destination) that are subject to independently distributed, slowly-varying and flat Rayleigh fading. Due to the fact that the inter-user channel is less noisy than the uplink channel, we apply the 16 QAM modulation in the inter-user channel in order to acquire higher data rate. In the uplink channel, one user and its collaborator send bits together to the destination. Therefore, Alamouti space time code can be used. To

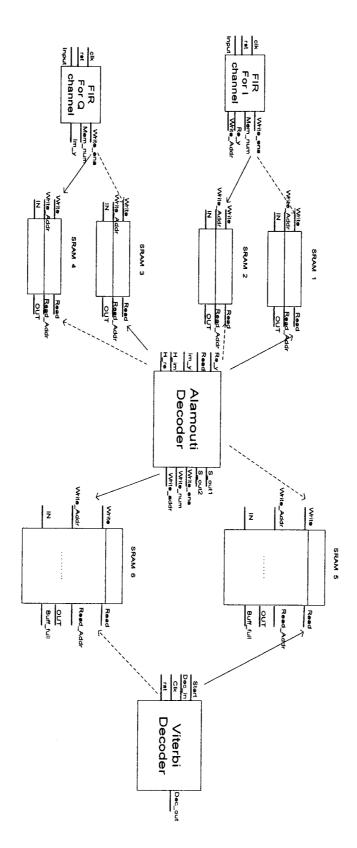

obtain a better performance and keep the same bandwidth, we utilize a Rate-compatible punctured convolutional code (RCPC). Simulation shows that improved performance can be achieved compared with that of a non-cooperative system. Based on this new system scheme, we implement the uplink receiver, which consists of a pair of parallel Square Root Raise Cosine (SRRC) filters, the Alamouti decoder, and the Viterbi decoder for decoding of the RCPC codes. In order to save the area, a parallel sequence of Alamouti decoder is controlled by the Moore state machine; a simplified method of the Branch Metric Unit (BMU) is introduced; the in-place scheduling is used in the Path Metric Unit (PMU).

The design is modeled in Very high speed integrated circuit Hardware Description Language (VHDL) and synthesized on a single chip FPGA (Xilinx Virtex 2 Pro). According to the RTL level and the gate level simulation results, the receiver can work at a speed of 12 Mbps with Virtex 2 pro FPGA.

### **ACKNOWLEDGEMENTS**

Foremost, I am deeply indebted to my supervisor, Dr. M. Reza. Soleymani, for giving me the opportunity to work with him. His continuous support and valuable suggestions helped me all the time during my research. I also would like to express my gratitude to him for creating a convenient research environment and providing all advanced development tools and devices for my research works.

My parents and my grandmother, though not with me in Canada, deserve special acknowledgements. They have supported me with their love, care and encouragement. Owing them my success, I will never be able to thank them enough. I also want to thank my boyfriend Yan Liu, who always encourages me to strive for my objective.

Special thanks would go to all specialist, administrators and technical staff for their great assistance in using design tools. Finally, I want to express my thanks to all the students in our Wireless Satellite and Communication Lab. I benefited a lot from their friendly help.

## TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                            | VII      |

|----------------------------------------------------------------------------------------------------------------------------|----------|

| LIST OF TABLES                                                                                                             | Х        |

| LIST OF ABBREVIATIONS                                                                                                      | X        |

| CHAPTER ONE INTRODUCTION                                                                                                   | 1        |

| 1.1 Development of Cooperative Communication                                                                               | 2        |

| 1.2 Development of FPGA                                                                                                    | 4        |

| 1.3 Contribution of the Thesis                                                                                             | 6        |

| 1.4 Outline of the Thesis                                                                                                  | 7        |

| CHAPTER TWO BACKGROUND AND SOME EXTENSIONS                                                                                 | 9        |

| 2.1 Channel Capacity                                                                                                       | 10       |

| 2.2 Fading Channel Capacity                                                                                                | 10       |

| 2.3 Several issues of the Multi-Antennas Channel 2.3.1 Spatial multiplexing (SM) 2.3.2 Space-Time Coding 2.3.3 Beamforming | 12<br>14 |

| 2.4 Cooperative communication System                                                                                       | 17<br>20 |

| 2.5 Extension summarization of Ad-Hoc networks                                                                             | 30       |

| CHAPTER THREE VIRTUAL SPACE TIME CODINGFOR COOPER SYSTEM                                                                   |          |

| 3.1 Proposed System Model                                                                                                  | 33       |

| 3.2 Inter-user channel transmission                                                                                        |          |

| 3.3 Uplink channels transmission                                                                                           |          |

| 3.3.2 Alamouti's 2X1 Space Time Coding                          | 40        |

|-----------------------------------------------------------------|-----------|

| 3.4 Energy Distribution                                         | 41        |

| 3.5 Error Performance Simulation                                | 42        |

| CHAPTER FOUR UPLINK RECEIVER HARDWARE IMPLEMENT                 | 'ATION 44 |

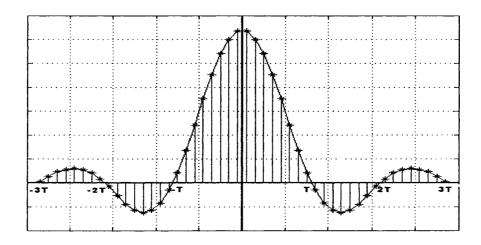

| 4.1 Finite Impulse Response(FIR) filter Implementation          | 46        |

| 4.1.1 Square Root Raised Cosine Filter                          | 46        |

| 4.1.2 Finite Impulse Response Filter                            |           |

| 4.1.3 Implementation of the FIR filter                          | 49        |

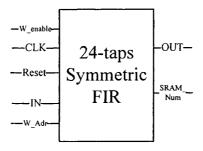

| 4.1.4 Input/Output Interface Description                        | 51        |

| 4.1.5 Multiply Accumulate Unit                                  | 52        |

| 4.1.6 Registers and Memory                                      | 52        |

| 4.1.7 Implementation Result                                     | 53        |

| 4.2 Alamouti Decoder Implementation                             | 55        |

| 4.2.1 Alamouti Decoder 2 X 1 Implementation                     | 55        |

| 4.2.2 Input/ Output Interface                                   | 56        |

| 4.2.3 Top Level Finite State Machine (FSM) for Alamouti Decoder | 57        |

| 4.2.4 Arithmetic Logic Units Implementation                     | 59        |

| 4.2.5 Extension to Alamouti Decoder 2 X 2                       | 61        |

| 4.2.6 Implementation Result                                     | 62        |

| 4.3 Viterbi Decoder Implementation                              | 63        |

| 4.3.1 Description of the Viterbi Algorithm                      | 63        |

| 4.3.2 Design Specification                                      | 65        |

| 4.3.3 Arithmetic Logic Units Specification                      | 65        |

| 4.3.4 Memory Unit Specification                                 | 74        |

| 4.3.5 Input/Output Interface                                    | 76        |

| 4.3.6 RTL Level Simulation                                      | 77        |

| 4.3.7 Overall Architecture of the Receiver                      | 80        |

| CHAPTER FIVE CONCLUSION                                         | 83        |

| 5.1 Suggestions for Future Research                             | 85        |

| DEEDDENCES                                                      | 07        |

## LIST OF FIGURES

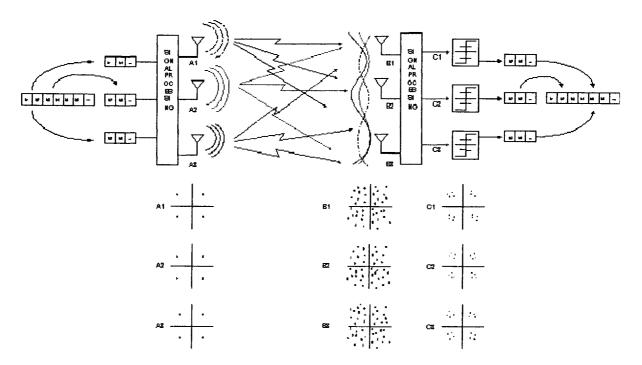

| Figure 2-1 Spatial Multiplexing Method                                          | 13 |

|---------------------------------------------------------------------------------|----|

| Figure 2-2 Beamforming Method in MIMO system                                    | 15 |

| Figure 2-3 Beamformer Realization                                               | 16 |

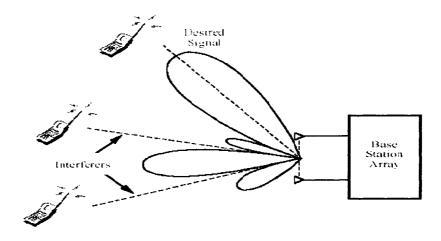

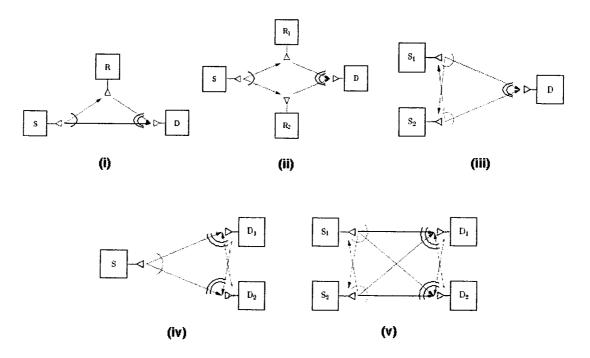

| Figure 2-4 Various relaying in wireless networks                                | 18 |

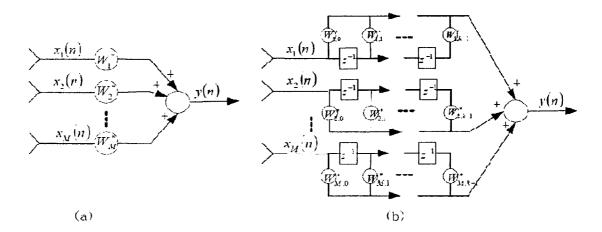

| Figure 2-5 Cooperative Communication                                            | 22 |

| Figure 2-6 Amplify and forward scheme                                           | 25 |

| Figure 2-7 Detected and Forward scheme                                          | 26 |

| Figure 2-8 Channel mode for the detected and forward scheme                     | 26 |

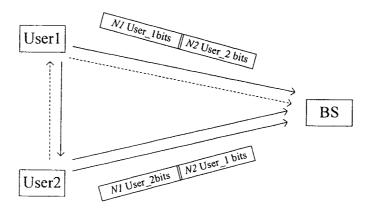

| Figure 2-9 Code cooperation scheme                                              | 28 |

| Figure 2-10 Transmission sequence in unlink channel of Coded cooperative system | 29 |

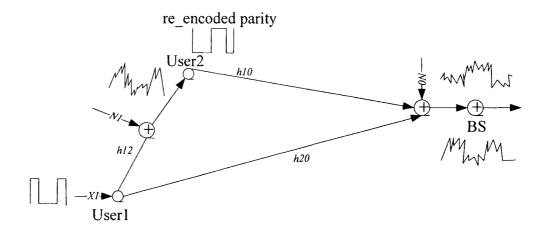

| Figure 3-1 Virtual MISO cooperation system scheme                               | 33 |

| Figure 3-2 Sixteen-QAM Constellation                                            | 37 |

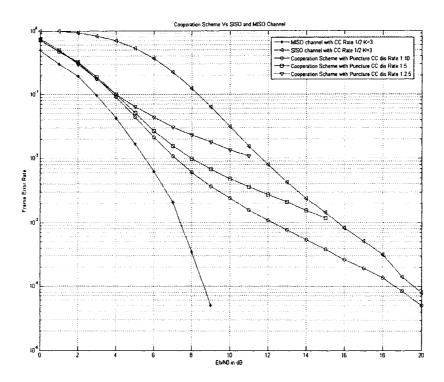

| Figure 3-3 The Comparison of Cooperative and Non-Cooperative Simulation Result  | 43 |

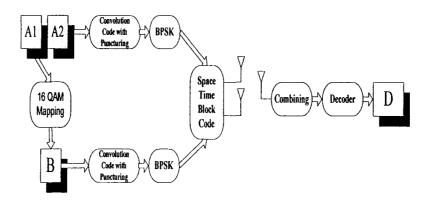

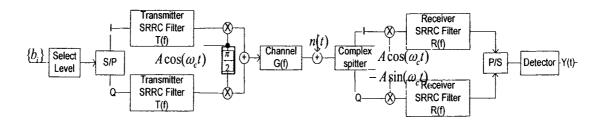

| Figure 4-1 Receiver block diagram                                               | 44 |

| Figure 4-2 Basic elements of a transmission system                              | 47 |

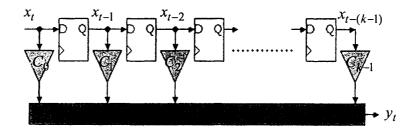

| Figure 4-3 Non-symmetric FIR filter                                             | 48 |

| Figure 4-4 Sampling the SRRC pulse                                              | 49 |

| Figure 4-5 I/O interface of 24 taps symmetric FIR                               | 51 |

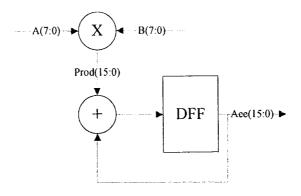

| Figure 4-6 The MAC architecture                                                 | 52 |

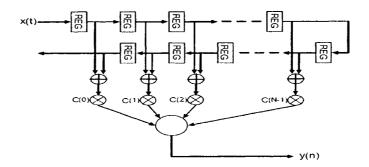

| Figure 4-7 Even Symmetric FIR                                                   | 53 |

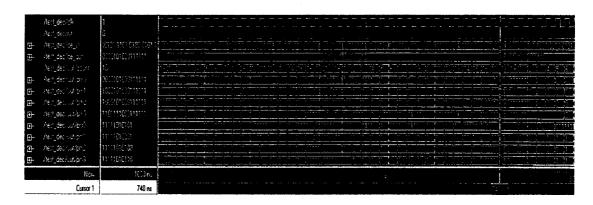

| Figure 4-8 Simulation result for 24 symmetric FIR                               | 54 |

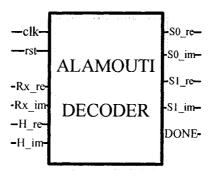

| Figure 4-9 I/O layout of Alamouti Decoder                                       | 56 |

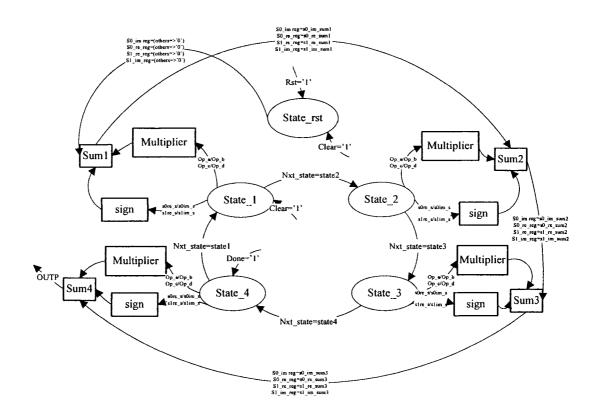

| Figure 4-10 Top Level State Diagrme of FSM for Alamouti Decoder                 | 58 |

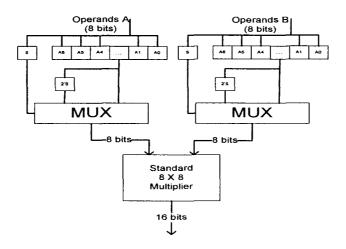

| Figure 4-11Architecture of 8X8 Multiplier                      | . 59 |

|----------------------------------------------------------------|------|

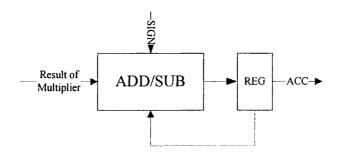

| Figure 4-12 Structure of ADD/SUB Unit                          | 60   |

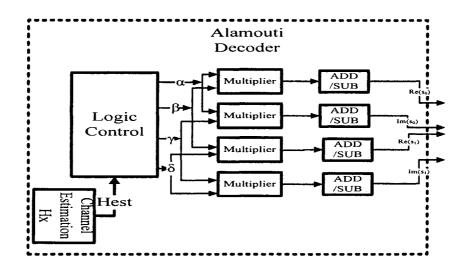

| Figure 4-13 Overall Architecture of Alamouti Decoder           | 60   |

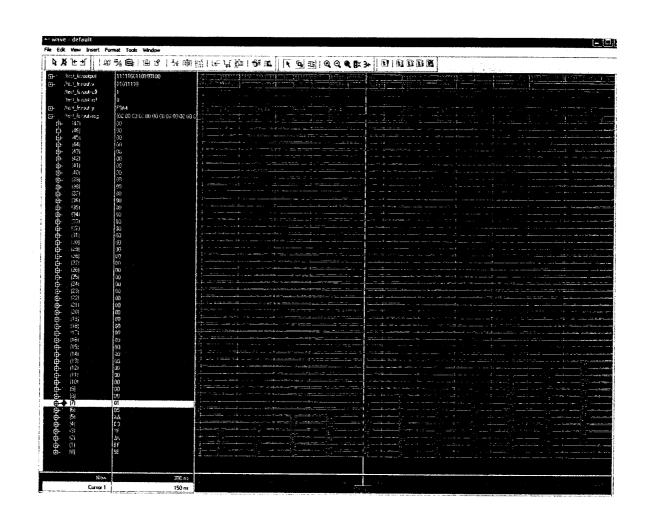

| Figure 4-14 Alamouti Decoder RTL Level Simulation Result       | 62   |

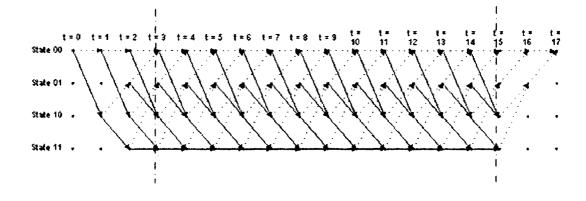

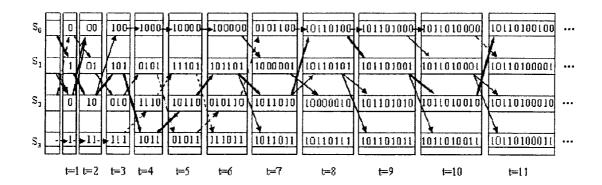

| Figure 4-15 Trellis diagram for a (2, 1, 2) code with $L = 15$ | 63   |

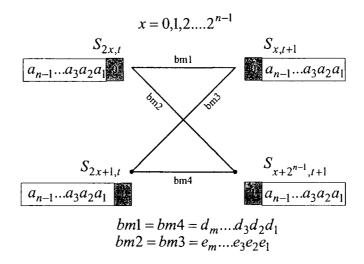

| Figure 4-16 Butterfly module                                   | 66   |

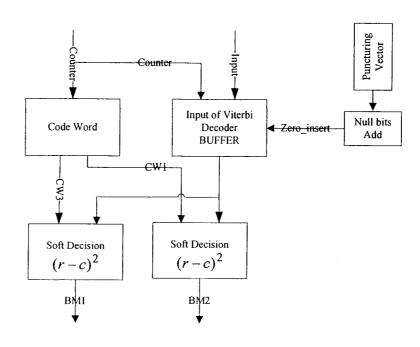

| Figure 4-17 Block Diagram of BMU for soft decision             | 69   |

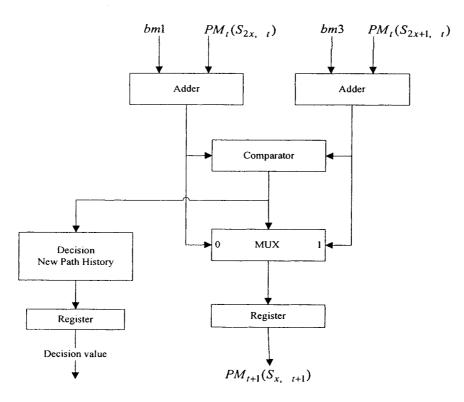

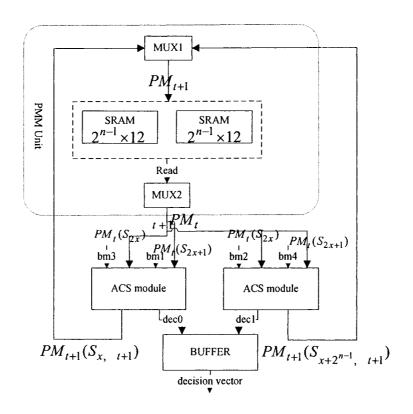

| Figure 4-18 The ACS module                                     | 70   |

| Figure 4-19 The PMM with ACS for Butterfly Unit                | 72   |

| Figure 4-20 Register Exchange(RE) Method                       | 73   |

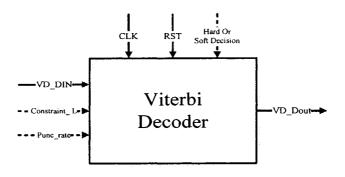

| Figure 4-21 I/O interface for Vitebi Decoder                   | 76   |

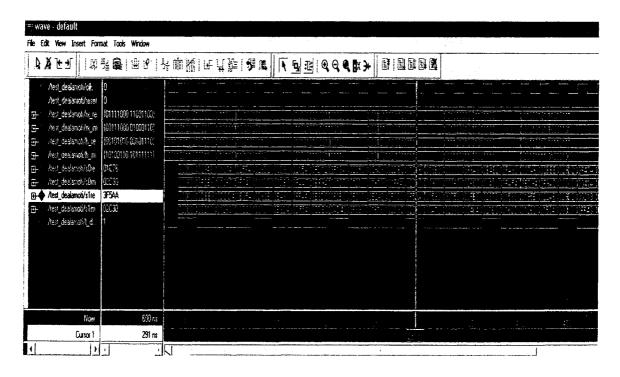

| Figure 4-22Viterbi Decoder K=7 simulation wave form            | 77   |

| Figure 4-23Viterbi Decoder with punctuation ratio 4/7          | 78   |

| Figure 4-24 The Architecture of the Uplink Receiver            | 79   |

| Figure 4-25 Uplink Receiver RTL level simulation Result        | 81   |

| Figure 4-26 Hardware Design Summary                            | 82   |

## LIST OF TABLES

| Table 4.1: Values of 2's complement for the 24-taps symmetric coefficients     | 50 |

|--------------------------------------------------------------------------------|----|

| Table 4-2: Specification of 24 taps symmetric FIR                              | 51 |

| Table 4-3: The usage and control sequence of Paths in Each State               | 56 |

| Table 4-4: The particular speccifiations for I/O Layout of Alamouti decoder    | 57 |

| Table 4-5: The usage of Paths in Each State for 2X2 Alamouti Decoder           | 62 |

| Table 4-6: Viterbi Decoder Parameters                                          | 65 |

| Table 4-7: Simplification Process in the calculation of the Euclidean distance | 69 |

| Table 4-8: Viterbi Decoder Interface parameter                                 | 76 |

## LIST OF ABBREVIATIONS

GSM Global System for Mobile Communications

CDMA Code division multiple access

2G Second Generation

3G Third Generation

4G Fourth Generation

W-CDMA Wideband code division multiple access

OFDM Orthogonal Frequency Division Multiplexing

VLSI Very Large Scale Integration

SNR Signal noise ratio

CRC Cyclic Redundancy Check

ASIC Applicant Specific Integrated Circuit

FPGA Field Programmable Gate Array

PLDs Programmable Logic Devices

PLA Programmable Logic Array

PAL Programmable Array Logic

JTAG Joint Test Action Group

CLB Configurable Logic Blocks

LUT Lookup Table

GAL Generic PAL

PCI Peripheral Component Interconnect

QAM Quadrature amplitude modulation

BPSK Binary phase-shift keying

QPSK Quadrature phase-shift keying

8PSK Eight phase-shift keying

VHDL VHSIC Hardware Description Language

RTL Register Transfer Language

MIMO Multiple Input and Multiple Output

RCPC Rate Compatible Punctured Convolutional Codes

BER Bit Error Rate

SM Spatial multiplexing

STC Space Time Code

LST Layered Space-Time Codes

STBC Space-Time Block Codes

STTC Space-time trellis codes

BLAST Layer space time coding

LAN Local Area Network

BS Base Station

Wi-Fi Wireless Fidelity

LLR Log-Likelihood Ratio

MISO Multiple Input and Single Output

VA Viterbi algorithm

AWGN Additive White Gaussian Noise

ADC Digital Converter

DAC Digital to Analogy Converter

LNA Lower Noise Amplifier

DSP Digital Signal Processing

FIR Finite Impulse Response

SRRC Square Root Raised Cosine

ISI InterSymbol Interference

UMTS Universal Mobile Telecommunications System

MAC Multiply-Accumulate

FSM Finite State Machine

ADD/SUB Addition/Subtract

BMU Branch Metric Unit

ACS Add Compare Select Unit

SMU Survivor Memory Unit

PM Path Metric

BM Branch Metric

MSB Most Significant Bit

PMM Path Metric Memory Unit

RE Register Exchange

TB Trace Back

OFDM Orthogonal Frequency-Division Multiplexing

## **CHAPTER ONE**

## **INTRODUCTION**

Digital communication plays an important role in our daily life. The combination of advanced wireless communication algorithms and integrated circuit technology makes the realization of many new services feasible.

The wireless communication has gone through its first and second generation systems. While still a few first generation systems exist, most services are now second generation, e.g., Global System for Mobile Communications (GSM). Code division multiple access (CDMA) is an advanced technique used in some 2G systems and accepted for almost all third generation systems. Third generation (3G) is posed to provide enhanced broadband voice, video, data access. More specifically, W-CDMA is used as a wideband spread-spectrum mobile air interface. It utilizes the CDMA signaling method to achieve higher rates and to support more users. Beyond 3G, there are two candidates enabling technologies to be used in the fourth generation systems. These are Orthogonal Frequency Division Multiplexing (OFDM) and Multiple Input, Multiple Output (MIMO) systems. OFDM reduces the impact of fading by spreading out signals over an interval of time. MIMO depends on multipath to send multiple versions of data streams that are transmitted from several antennas. By doing this, the spectral efficiency is greatly

increased. Meanwhile, the rapid development of Very Large Scale Integration (VLSI) and computer technology allows increasingly complex and powerful wireless devices to be implemented. To meet the requirement of multimedia communication, new schemes have been proposed in order to gain diversity. Cooperative communication is one of the new approaches used for single- antenna mobiles sharing their own antennas in a multiuser environment. In this thesis, our focus is on cooperative communication system design and the implementation of the receiver for this system.

#### 1.1 Development of Cooperative Communication

Cooperation is a generalization of the relay channel; multiple sources with information to transmit also serve as relays for each other. Combinations of relaying and cooperation are also possible and are often referred to as "cooperative communications."

The classical relay channel model is comprised of three terminals: a source that transmits information, a destination that receives the information, and a relay that both receives and transmits information to enhance communication between the source and destination. Problems in general relay channel appeared early in the area of information theory. Van der Meulen originally introduced three terminal communication in [1], [2], Cover and El Gamal provided the upper and lower bounds on the capacity for the relay channel in [3]. More recently, models with multiple relays have been examined. In order to make the relay channel symmetric, a parallel relay channel mode with coding strategies was introduced by Schein and Gallager [4], [5]. More sophisticated channels were also studied: the cooperative scheme with two transmitters and receivers was analyzed by Cover and El Gamal [3]. Willem and others extended the above model to the

multiple-access channels. All of these models fall within various cooperation with generalized feedback [6], [7], [8], [9]; Kramer, Wijingaarden [10] and Sendonaris et al [11], [12], [13] examined a channel model where the mobiles share the same relay between themselves and the base station.

Although we have an increased understanding of the benefits of multi-antenna systems in wireless channels [14], transmitting diversity may be impractical due to the cost, size, power and hardware limitations. Many have come to the realization that multiple relays can emulate the strategies designed for multiple transmit antenna systems and offer significant network performance enhancements in terms of various metrics, including: increased capacity (or larger capacity region), improved reliability because of diversity gain, diversity-multiplexing tradeoffs, and reduced frame or symbol error probabilities.

Therefore, cooperative communication is introduced in order to provide spatial diversity in a fading environment, as well as envision a collaborative scheme where both terminals help one another to communicate by acting as relays for each other. Various proposed schemes have been provoked by the potential advantage of cooperative communication. Three frequently used methods are called amplify-and-forward, detectand-forward, and code-cooperative, respectively.

The amplify-and-forward method was first introduced by Lanemen et al [15]. As the name implies, the idea of this method is that one user simply amplifies noisy signal versions it received from the other user and retransmits these amplified signals to the destination. Although this scheme makes it challenging to sample, amplify and retransmit signals, it leads more opportunities for the further research. The detect and forward method is one of the closest to the traditional relay. It was developed by Sendonaris et al

[16], [17], [18]. Each mobile receives a noisy version of the partners' transmitted signal, and combine it with its own information bits to transmit towards the base station. The full diversity can be achieved by introducing CDMA implementation. The application of the spreading codes creates two separate channels, while, time diversity between the mobiles has been gained in [18]. Moreover, Laneman et al [15], [19] proposed a hybrid detectand-forward method to overcome the problems of the original scheme. The method is that when the base station has no idea about the optimal detection for the inter-user channel, the partner may forward an erroneous version of the user's bits. It is shown that the user only applies the detect-and-forward method when the channel has high SNR but communicates under non-cooperative mode when the channel has low SNR. The coded cooperation [20], [21], [22] is a scheme to utilize channel coding. It is assumed that each user has M information bits per frame, which is encoded into N bits per frame that is divided into N1 and N2. The transmission of the N coded bits takes two steps. First, the users broadcast the NI bits both to its partner and the base station. And during the second step, if a user can decode a partner's message, determined by the CRC code, the user will compute and transmit N2 bits for the partner, whereas, it will send the rest of N2 bits. In our work, we proposed a new scheme in cooperative communication with a combination of the detect-forward method, channel coding, and space time coding.

### 1.2 Development of FPGA

An Application Specific Integrated Circuit (ASIC) is a circuit which performs a specific function in a particular application. It is often optimized for the area and the performance. Almost all ASICs and programmable logic chips today use CMOS

technology. To reduce the time it takes to produce for market, Field Programmable Gate Arrays (FPGAs) can be used instead of ASICs. ASICs have the fastest speed, more power efficiency and optimal resource saving; however, they require a longer design cycle and are more costly. Therefore, they are not suited for prototype products and products with small volumes of production.

FPGAs are the continuation of the trend starting with the introduction of Programmable Logic Devices (PLDs). PLDs were introduced thirty years ago. Different from microprocessors, the idea was to construct a combinational logic circuit that was programmable. In other words, a PLD is a general purpose chip and its hardware can be reconfigured to meet particular specifications.

The evolution of PLDs can be classified into three stages. The first PLDs, namely Programmable Array Logic (PAL) or Programmable Logic Array (PLA) used only logic gates but without flip-flops, so they only implemented combination circuits. Then, registered PLDs were developed with one flip-flop at each circuit's output to get the sequential function. In the beginning of the 1980s, Macrocells were introduced. Besides the flip-flop, Macrocells provide logic gates, multiplexers, feedback signal that create greater flexibility. They were also programmable. All the chips mentioned above as well as generic PAL (GAL) are included in Simple PLDs (SPLD). The next wave, was the introduction of the popular approach known as Complex PLD (CPLD) is derived by using JTAG support and logic standard interface. Finally, FPGAs were introduced by Actel, Xilinx, and others in the mid 1980s. They focused on the implementation of large and high performance circuits.

An FPGA contains a matrix of Configurable Logic Blocks (CLB), which are interconnected by an array of switch matrices. Its operation is based on a Lookup Table (LUT). A number of flip-flops support more sophisticated sequential architecture. Different from the CPLDs' non-volatile feature, most FPGAs are volatile because they use SRAM instead of EEPROM, and a similar Flash that is used by CPLDs. Moreover, some FPGA chips also include clock multiplication (PLL or DLL), PCI interface, multipliers, DSPs, etc. Several companies manufacture FPGAs, such as Xilinx, Actel, Altera, Quicklogic, Atmel and so on.

Many researchers focus on the issues of hardware implementation for various elements of the receivers. These include filters [23], [24], [25] decoders [26], [27], and so on. Our design architecture is associated with the requirement of our proposed cooperative communication scheme. We chose Xilinx Virtex 2 pro series FPGA for our implementation. The clock frequency of this FPGA can reach as high as 100 MHZ.

#### 1.3 Contribution of the Thesis

The contribution of this thesis is to construct a virtual space time coding for a cooperative system that is developed from the traditional detect-forward approach and combined with well known space time block coding and channel coding. The corresponding hardware implementation is also introduced.

By assuming that the cooperative system contains both an inter-user channel (between users) and an uplink channel (from users to the destination), we applied 16 *QAM* modulations for inter-user channel in order to achieve higher data rates. The log likelihood ratio approach is used for detecting signals in the inter-user channel. Then, for

the uplink channel, one user and its partner, i.e, the node with which it cooperates, will send bits together to the destination. Therefore, the application of Alamouti space time coding in the uplink channel is justified. For obtaining a better performance and keeping the same bandwidth, we utilized a rate-compatible punctured convolutional code for both the source and its partner (the relay). Improved better performance can be achieved compared to the non-cooperative system.

For the receiver hardware implementation, we present the complete VLSI design for the uplink receiver, which consists of a pair of parallel Square Root Raise Cosine Filters, the Alamouti decoder controlled by the Moore state machine, and the Viterbi decoder for RCPC code. The design is modeled with VHDL (VHSIC Hardware Description Language) in RTL (Register Transfer Language) level and the simulation is performed by Modelsim. After synthesizing with Xilinx tools, placing and routing has been verified by gate level simulation.

#### 1.4 Outline of the Thesis

In Chapter 2, the background of cooperative communication and related issues is presented. First, we discuss different issues relate to the multiple input multiple output (MIMO) system. Then, the relay channel is reviewed as an example of a cooperative communication scheme. Finally, the proposed approaches for cooperative communication are summarized. In addition, the ad-hoc networking is introduced at the end.

In Chapter 3, we present our new framework where the virtual space time coding for cooperative communication is employed. Starting with the overall system model illustration, the protocol and algorithm used in our scheme will be introduced. Moreover,

at the end of the chapter, simulation results showing the performance of the proposed scheme is presented and conclusion is provided.

In Chapter 4, the detail hardware architecture of the uplink receiver is addressed and the implementation details of differences including the components, including the Square Root Raised Cosine Filter, Alamouti Decoder, and Viterbi Decoder for RCPC coding, are specified clearly.

Then, an efficient architecture that combines the different components is given. Meanwhile, the result of RTL lever simulation is presented. The total hardware design summary shows that the total area, consumption on the test FPGA board and the estimated achievable receiving speed.

In Chapter 5, the conclusion and future work are presented.

## **CHAPTER TWO**

## **BACKGROUND AND SOME EXTENSIONS**

The purpose of this chapter is to provide an overview of the background for this thesis. In the first three sections, we give an introduction of the channel capacity and some further work on the capacity of fading channels. Then, the development of Multiple Input and Multiple Output antenna system is discussed. Furthermore, we provide a systematic overview of in the Cooperative Communication; the pros and cons of various schemes are summarized. Then, some issues about Ad-hoc networking are mentioned in the end of this chapter.

#### 2.1 Channel Capacity

One of the most famous results of information theory is Shannon's theorem [35]. It states that given a noisy channel with channel capacity C and information transmitted at a rate R, if

There exists a code that allows the probability of error at the receiver to be made arbitrarily small. This means that theoretically, it is possible to transmit information without error at any rate below a limiting rate, C. The converse is also important. If

an arbitrarily small probability of error is not achievable. All codes will have a probability of error greater than a certain positive minimal level, and this level increases as the rate increases. So, information cannot be guaranteed to be transmitted reliably across a channel at rates beyond the channel capacity.

### 2.2 Fading Channel Capacity

Since there are a lot of conditional constraints in wireless communication, several different characteristics for the Shannon capacity extend depending on different channels conditions. A lot of research has been done on different fading channels. There are several cases studied when the fading process is ergodic. An interleaved fading channel whose state is known to the receiver is analyzed by Thomas H.E. Ericson [30]. If the receiver can share channel state information with the transmitter, by means of a separate feedback channel, then the transmitter can adapt transmitted signals to the channel states. The capacity of this fading channel with channel side information is studied by Andrea

J. Goldsmith and Pravin P. Varajya.[31]. Abou-Faycal et. al [28], [29] were the first to examine the case where the channel state information is available neither to the transmitter nor to the receiver. However, when the fading process turns to non ergodic, the wireless channel is appropriately modeled as a family of channels which is called a compound channel [32]. The Shannon capacity will be arbitrarily small or zero since the effects of multipath fading may be small or zero. Thus, Shannon capacity is not a useful tool for system design in such scenarios.

#### 2.3 Several issues of the Multi-Antennas Channel

Since the available radio spectrum is limited, the communication capacity requirements cannot be achieved without increasing spectral efficiency. A number of methods are utilized in the single antenna channel, for example, turbo coding [33] and parity check coding [34], to approach the Shannon capacity limit [35]. However, in recent years, there is a new trend for the communication which involves multi-antenna physical arrays at the transmitters and/or receivers in a wireless system. These multi-antenna systems are theoretically able to provide increased throughput, and better error performance than traditional systems.

The particular aspect that is used by MIMO systems is called Multi-Path propagation. It is the propagation phenomenon that occurs when the radio signals sent from the transmitter bounce off some intermediate objects before reaching the receiver. As a result, the signals may reach the receiving antenna by several paths, and at different times. But in traditional single antenna systems, multi-path propagation degrades the performance of the system. The multiple propagation paths can cause multiple "copies"

of a signal to arrive at the receiver at different times. These time delayed signals then become interference when trying to recover the signal of interest. However MIMO systems aim to use this multiple path propagation to obtain performance improvement.

Wireless MIMO communication can be sub-divided into three main categories, spatial multiplexing [36] for enhancing the peak data transmission rate, transmitting diversity methods such as space-time coding [37] for enhancing the robustness of the transmission, and beamforming [38] technologies for improving received signal gain and reducing interference to other users. Thus, it is possible to construct a MIMO system with both spatial multiplexing and diversity benefits.

#### 2.3.1 Spatial multiplexing (SM)

It is an advanced transmission technology that increases the bit rate in a wireless radio link without additional power or bandwidth consumption. In addition, spatial multiplexing provides linear increase of the performance with the number of antennas.

Assuming that N antennas are used at the transmitter and receiver respectively; at the transmitter, the streams of information symbols are split into N substreams (see in Figure 2-1) and allocated to N transmit antennas. Since there are different obstructions in the environment, each signal suffers multi-path propagation. Eventually, receiver antennas receive noisy signals with random phase and amplitude. For every substream, the set of N received phases and N received amplitudes constitutes its spatial signature.

At the receiving array, the spatial signature of each of the N signals is estimated. Based on this information, a signal processing technique is then applied to separate the signals, Linear or non-linear receivers can be used providing a range of performance

trade-off. For example, a linear SM receiver can be viewed as a bank of superposed spatial weighting filters where every filter aims at extracting one of the multiplexed substreams by spatially nulling the remaining ones. This assumes that the substreams have different signatures.

When there are different numbers of the antennas in transmitter and receivers (i.e., M antennas in the transmitter while N antennas in the receiver), the rate improvement factor allowed by SM is the minimum of these two numbers. Additional antennas on the transmitter or on the receiver are then used for diversity purposes and improve further the link reliability.

Figure 2-1 Spatial Multiplexing Method

#### 2.3.2 Space-Time Coding

A space-time code (STC) is a method employed to improve the reliability of data transmission by using multiple transmitting antennas. Basically, STCs works by transmitting multiple, redundant copies of information bits to the receiver, in order to provide the possibility that at least some information bits can be received in a good condition and decoded reliably. There are three main categories of STCs: Layered Space-Time Codes (LST), Space-Time Block Codes (STBC) and Space-time trellis codes (STTC).

The distinguishing feature of LST is that it allows processing of multidimensional signals in the space domain in dimension of space. The method relies on powerful signal processing techniques at the receiver and conventional one dimension channel codes. The work of Foschini and Gans [39], [40] on the BLAST system is a notable achievement; Space—time block codes (STBCs) [41], [42] act on a block of data at once (similarly to block codes) and provide diversity gain. The work of Alamouti [41] on simple block codes that achieve full diversity and have particularly simple, but efficient linear decoding algorithms; Space—time trellis codes (STTCs) distribute a trellis code over multiple antennas and multiple time-slots to provide both coding gain and diversity gain. We can refere to the work of Tarokh et. al [43] on space-time trellis codes.

#### 2.3.3 Beamforming

Beamforming in MIMO systems is to extend the range of existing data rates by transmitting and receiving beamforming. Using an array of antennas, one can receive a number of signals, which are broadcasted from different locations at same time. By linear

combining the antenna outputs, desired signals can be restored from the interference of the other signals and noise. The task of the adaptive beamformer is to compute and derive the proper weight vectors using adaptive beamforming algorithms.

Figure 2-2 Beamforming Method in MIMO system

The beamforming method steers the gain pattern of an adaptive array according to a desired direction through either beam steering or null steering signal processing algorithms. Adaptive beamforming can provide substantial gains (of the order of 10log(M) dB, where M is number of array elements) as compared to omni-directional antenna system.

Figure 2-3 Beamformer Realization

(a) For narrow band signal

(b) For broad band signal

### 2.4 Cooperative communication System

Next generation wireless communication (third generation and beyond) will bear little similarity in mainly voice cellular systems to first- and second- generation systems. In order to meet the demands of multimedia communication, next generation cellular system must employ advanced algorithms and techniques that not only increase the data rate, but also enable the system to guarantee the quality of service desired by various media classes. The techniques currently being investigated for meeting these goals include advanced signal processing, modulation, detection, source and channel coding, specifically for the wireless environment, and using various forms of diversity [44], [45], [46], [55], [56]. Among these techniques, diversity is principal importance due to the nature of the wireless environment.

In wireless communication, the signal attenuation from mobiles varies from one to another since the mobile radio channel suffers from fading. By transmitting or processing independent copies of the signal, applying diversity is a great method that can effectively combat the deleterious effects of fading. There are some well known forms of diversity, which are called spatial diversity, temporal diversity, and frequency diversity. In particular, spatial diversity relies on transmitting signals from different locations.

Therefore, it allows independently faded versions of the signal at the receiver.

We begin by reviewing work on the relay channel since it is the origin of the cooperative communication. Then, we draw an outline for cooperative communication, and the fundamental construction is presented in subsection 2.5.2. Next, in subsection 2.5.3, we cite several various architecture schemes which have been further studied

#### 2.4.1 Relay Channels

Relay channels and their multi-terminal extensions play a leading role as the root of cooperative diversity. Much of the work on these channel models to date has focused on discrete or additive white gaussian noise channels, and examined performance in terms of the well-known Shannon capacity (or capacity region) [47]. Only the more recent work has considered the issue of multi-path fading.

Figure 2-4: Various relaying in wireless networks:

- (i) classical relay channel

- (ii) parallel relay channel

- (iii) multiple-access channel with relaying

- (iv) broadcast channel with relaying

- (v) Interference channel with relaying.

Here, single arc means a broadcast channel, while double arcs mean a multiple access channel.

The classical relay channel models a class of three terminal communication channels originally introduced and examined by van der Meulen [1], [2]. This relay channel model, containing source, destination and relay, is the root of multi-hop communication's information theory. The distinctive property of relay channels is that certain terminals called "relays", receive, process, and re-transmit some information signal(s) of interest in order to improve performance of the system. As we illustrate in Fig. 2-4, in some cases, additional terminals in the network serve as relays without transmitting or receiving any information, while in other cases transmitting and/or receiving terminals can cooperate by serving as relays for one another. Cover and El Gamal provided a number of relaying

strategies, found achievable regions and developed lower and upper bounds on the capacity of the degraded relay channel, in which the communication channel between the source and the relay is physically better than the source-destination link. Generally these lower and upper bounds are unrealistic, but they are achievable in the class of degraded relay channels [3]. Although the class of degraded relay channels is mathematically convenient, we emphasize that none of the wireless channels in this class exist in practice.

The lower bounds on capacity, named achievable rates, are obtained from three different random coding schemes, referred to in [3] as facilitation, cooperation, and observation, respectively. The facilitation scheme is nothing special: the relay does not help the source actively, but rather, supports the source transmission by inducing as little interference as possible. However, the cooperation and observation schemes are more positive. In the cooperation scheme, the relay completely decodes the source message, and retransmits some information bits about that signal to the destination. Practical implementations of this cooperation scheme can be obtained with suitable configurations of multi-level codes [48]. Cover and El Gamal proposed the observation scheme, in which the relay encodes a quantized version of its received signal. On the receiving side, the destination combines information about the relay received signal with its own in order to create a better estimate of the source message. It is shown that the destination can essentially average to two observations of the source message in Gaussian noise channels.

Parallel relay channels and multiple-access channels with relaying, refer to Figure 2-4, are the most popular studied in this area. In order to make the relay channel symmetric,

Schein and Gallager [4] introduced the parallel relay channel model which includes many coding techniques in various regimes [5], and improved tighter converse results for certain discrete alphabet channels based on using distributed source coding [49]. Willems and others [6], [7], [8], [9] have studied the multiple-access channel with various degrees of cooperation and created feedback between the transmitting terminals. Also in a multiple-access channel model [10], the mobiles share a common relay between themselves and the base station as examined by Kramer and Wijngaarden. Sendonaris et. al [11], [12], [13]. They have taken count of the cooperative diversity for a multiple-access channel with relaying and fading. The cooperation scheme where each transmitter and receiver employs two users is issued in [3]. If the signal-to-noise ratio (SNR) between the transmitting terminals is high, cooperative diversity of this case is to increase the achievable sum rate when transmitters and receivers have knowledge of the fading in ergodic fading, and to improve outage performance for non-ergodic fading [12], [13]. In addition, a number of results for extensions to multiple relays have developed in the work of Gupta, Gastpar, and others [50], [51], [52], [53].

#### 2.4.2 Cooperative Communication

It is quite obvious that the advantage of multiple-antenna systems have been widely acknowledged. Specifically, some transmit diversity methods, such as Alamouti Coding have been utilized into wireless communication standards. However, the advantage of transmit diversity requires more than one antenna at the transmitter to implement. Therefore, many devices that are limited to one antenna could not make use of this feature. However a new class of approach, called cooperative communication, has been

widely studied in recent years. It makes single- antenna mobiles in a multi-user environment to share their antennas and generate a virtual multiple-antenna transmitter that allows them to achieve transmit diversity. In this section, we present the developments of this method in this emerging field.

In wireless communication, the signal attenuation from mobiles is varying from one to another since the mobile radio channel suffers from fading. By transmitting or processing independent copies of the signal, one can use diversity to effectively combat the effects of fading. There are some well known forms of diversity, which are called spatial diversity, temporal diversity, and frequency diversity. In particular, spatial diversity relies on transmitting signal from different locations, thus allowing independently faded versions of the signal at the receiver.

Although transmit diversity is clearly advantageous on a cellular base station, it may be impractical for any other scenarios. For example, in the uplink of a cellular system by the limitation of cost, size, power, and hardware, a wireless user may not able to support multiple transmit antennas. In order to overcome this shortcoming, cooperative communication generates diversity in a new way by imitating transmit antenna diversity.

In the following context, we are going to take a systemic overview of cooperative communication. The basic idea dates back to multi-hop communications, which is also the original idea of ad-hoc wireless networks. Without a fixed infrastructure, the ad-hoc networks works by the relaying operation that overcome the path loss incurred over large distances. By the same idea, multi-hop is also wildly utilized in cellular and wireless LAN systems to provide higher quality of service, power saving and extended coverage.

In most case of multi-hop systems, the destination only processes the signal coming from the relay despite that the information theoretic model allows for the destination to listen to both the source and the relay. When the source is much further away from the destination than the relay, the received signal at the destination due to the source would be much weaker than the relay signal. Moreover, if the fading is taken into account, a considerable loss, especially in diversity, will be caused by this scheme. But on the other hand, the destination processes both signals from source and relay may not only overcome path loss, but also to provide diversity.

Therefore, cooperative communication is motivated by two principle ideas. First of all, it uses relays (or multi-hop) to provide spatial diversity in a fading environment. Second, envision a collaborative scheme where the relay also has its own information to send so both terminals help one another to communicate by acting as relays for each other (called "partners").

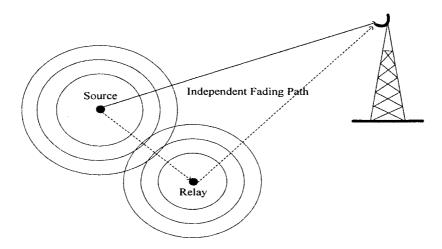

Figure 2-5: Cooperative Communication

We first refer to Figure 2-5, there are two mobile nodes communicating with the same destination; each mobile node has only one antenna and cannot individually generate spatial diversity. While it is possible for one mobile to receive the signals from the other, in which case it can forward some version of "overhead" information along with its own data. Since the fading paths from two mobile nodes are statistically independent, intuitively, cooperation communication refers to processing this overhead information at the surrounding nodes and to retransmission towards the destination to create spatial diversity. This provides extra observations of the source signals at the destinations, one antenna mobile in the multiple users' environment can share their antennas by creating a virtual MIMO system. Although the elements of this array are not co-located and are connected via noisy, fading links, some of the researches have already shown the benefits it gains, in terms of significant error performance, diversity and achievable data rate.

There are a lot of proposed schemes aimed at using the potential advantages of cooperative communication, where the higher throughput and reliability can be obtained. Several significant milestones have been achieved, and meanwhile, research and development of the concerned aspects is on the upswing.

#### 2.4.3 Proposed Scheme of cooperative communication

In a cooperative communication system, mobile users may increase their effective quality of service that includes bit error rates, frame error rates, or outage probability. One wireless user is assumed to both transmit data and act as a cooperative agent for another mobile user. Maybe it is not true at every given point, but it is valid considering a stable statistical environment.

At this point, we try to briefly address the feasibility of cooperative communication. In cooperative communication, each user transmits both its own bits, as well as some information bits for its partner. Therefore, each user requires more bandwidth, but the spectral efficiency for each mobile node improves and the channel code rates can be increased due to cooperation diversity. On the other hand, it may seem that more power is needed because of power consumption used on transmitting for both itself and its partner. However, the point to be made is that the gain in diversity from cooperation allows the users to reduce their transmitting power and maintain the same performance. Therefore, the tradeoffs in the code rate and transmission power are observed.

Several studies have proved the usefulness of the cooperative approach. We now go over several of the main cooperative signaling methods. For the purpose of illustration, we consider two mobile nodes helping each other, but generally, it is quite possible that there are more than two nodes, which is another popular topic in ongoing research called partner assignment. There are three frequently used methods in the cooperative signaling. They are called amplify and forward, detect and forward and code cooperative, respectively.

A. Amplify- and- Forward Methods

Figure 2-6: Amplify and forward scheme

Within the diversified approaches of the cooperative communication, the most ordinary method first developed by Lanemen et al [15], [19]. In this condition, for example, each user receives a noisy version of the signal transmitted by its partner (Figure 2-6). Then, the user simply amplifies its received signal, as an amplifying repeater [4], and retransmits these adjusted versions to the destination. The base station will combine the information sent by the user and partner and will make a final decision on the transmitted bits.

This method has both advantages and drawbacks. Although the noise of the partner is amplified in this scheme, on the receiver side, the base station is still able to make a better decision for the transmitted bits, because the information bits, which got in the receiver, are coming from two independently faded versions. On the other hand, this scheme brings technology challenges in sampling, amplifying, and retransmitting analog values. But this simple method makes a good example for further research in cooperative communication system.

#### B. Detect-and-Forward Methods

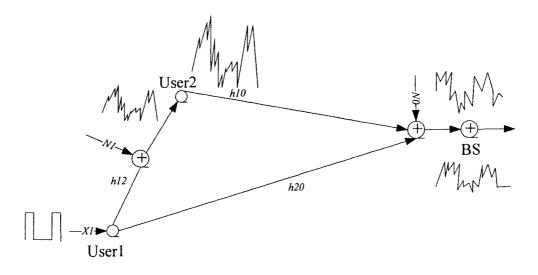

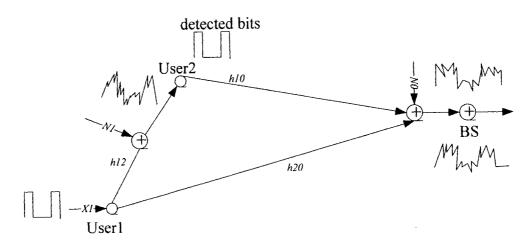

Figure 2-7: Detected and Forward scheme

The channel model can be illustrated in Figure 2-7. This is an example of detect-and-forward signaling introduced by Sendonaris et al [16], [17], [18].

Figure 2-8: Channel mode for the detected and forward scheme

As we can see, each mobile receives a noisy version of the partner's transmitted signal, and then it combines with its own signal to transmit towards the destination called the

base station. This approach is one of the closest to the traditional idea of relay. The whole process can be represented by the following formulas:

$$Y_0(t) = F_{10}X_1(t) + F_{20}X_2(t) + N_0(t)$$

$$Y_1(t) = F_{21}X_2(t) + N_1(t)$$

$$Y_2(t) = F_{12}X_1(t) + N_2(t)$$

(2-3)

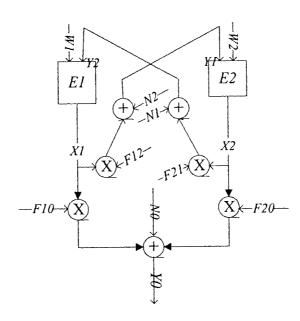

where  $Y_0(t), Y_1(t)$ , and  $Y_2(t)$  are the base band models of the received signals at the BS. By employing two users,  $X_i(t)$  is the signal transmitted by user i, for i = 1,2, and  $N_i(t)$  are the noisy version at the BS, user 1 and user 2 respectively, for i = 0,1,2. The fading coefficient,  $\{F_{ij}\}$ , keep constant over at least one symbol period.

The CDMA implementation is also introduced by using spreading codes to create two separate channels, also time diversity among the mobiles was investigated in [18], then full diversity can be provided. Each user has its own spreading code, which denoted as  $C_1(t)$  and  $C_2(t)$ . And  $P_{i,j}$  indicates power allocation on various signaling. The two user's data bits are denoted as  $Q_i^{(n)}$ , where i = 1,2 are the user indices; and n denotes the time index of information bits. In addition,  $Q_i^{\Lambda(n)}$  represents the partner's hard-detected estimation of user i's bit. By defining  $X_1(t)$ ,  $X_2(t)$  as the signals of user1 and user2 respectively, we introduce the two users' transmit signals

$$X_{1}(t) = P_{11}Q_{1}^{(1)}C_{1}(t), \quad P_{12}Q_{1}^{(2)}C_{1}(t), \quad P_{13}Q_{1}^{(2)}C_{1}(t) + P_{14}Q_{2}^{(2)}C_{2}(t)$$

$$X_{2}(t) = \underbrace{P_{21}Q_{2}^{(1)}C_{2}(t)}_{PeriodI}, \quad \underbrace{P_{22}Q_{2}^{(2)}C_{2}(t)}_{PeriodII}, \quad \underbrace{P_{23}Q_{1}^{(1)}C_{1}(t) + P_{24}Q_{2}^{(2)}C_{2}(t)}_{PeriodIII}$$

(2-4)

Sending data to the BS is processing in *Period I*. While, *Period II* is in charge of both sending data to the BS and to each user's partner. After this data is detected by each user's partner, each user creates a cooperative signal to send to the BS during *Period III*.

The transmitted power is an inconstant value for three different periods. This approach contributes a power adaptability to channel condition. In other words, when the inter-user channel is in good condition, more power may be allocated to cooperative communication, however, the inter-user channel is not in good condition, more power may be used in it.

In this scheme, the base station needs to know the optimal detection for the inter-user channel. Otherwise, the partner forwards an erroneous version of the user's bit that may bring a detrimental problem. Then, Laneman et al [15], [19] proposed a hybrid detect-and-forward method. It is indicated that users only have to detect and forward their partner's data when the fading channel has high SNR, whereas users recover to a non-cooperative mode when that fading channel has low SNR.

#### C. Coded-Cooperation Methods

Figure 2-9: Code cooperation scheme

As the name implies, coded cooperation [20], [21], [22] is an approach to utilize channel coding. The idea of coded cooperation is to use the same overall rate for coding

and transmission; the redundancy for each partner is transmitted by the corresponding user.

It is assumed that each user has M information bits per block, and the information bits of each user are encoded into a code word with N bits per block, so that the code rate R = M/N. After being punctured, each codeword of length N is divided into two segments of lengths NI and N2, which also satisfy NI + N2 = N. Then, the transmission of the N coded bits is divided into two successive time periods. During the first time period, the sub-codeword of rate RI = K/NI is broadcast by the user; and a noisy version of the coded message is received by the base station and the corresponding partner as well.

Figure 2-10: Transmission sequence in unlink channel of Coded Cooperative system

During the second time period, if a user can decode a partner's message, determined by the CRC code, the user will compute and transmit the N2 bits for the partner. Whereas if a user cannot correctly decode a partner, N2 additional parity bits for the user's own data will be transmitted. By the end of these two periods, there are four possible cases [22], [54] for the result of the second time period: In Case 1, both users successfully decode each other, therefore they each transmit for their partner in the second frame, resulting in the fully cooperative scenario. In Case 2, none of the user successfully

decodes their partner's first frame; the system reverts to the non-cooperative case automatically. In Case 3 and 4, first user successfully decodes its partner, but the second user does not successfully decode its partner. As a result, both the first and second users transmit N2 bits for the second user. These two independent copies of the second user's bits are optimally combined.

There is an additional condition that the destination must know which of these four cases has occurred in order to correctly decode the received bits. Two methods have been utilized on this issue [60]. One is that the base station decodes according to the assumption of all the case until CRCs indicate successive decoding. Probabilistic analysis shows that it brings tiny average increase in computational complexity. The other way is by adding one additional bit which represents each user to indicate its state to the base station.

#### 2.5 Extension summarization of Ad-Hoc networks

As we have emphasized, the development of cooperative diversity arise primarily in networks of radio terminals. We now summarize important results obtained in ad-hoc networks.

A wireless ad-hoc network is a computer network in which the communication links are wireless. Different from previous network technologies in which some designated nodes, usually with custom hardware to perform the task of forwarding the data, the network is ad-hoc because each node is willing to forward data for other nodes, and so the determination of which nodes forward data is made dynamically based on the network connectivity. Minimal configuration and quick deployment make ad hoc

networks suitable for emergency situations. A mobile ad-hoc network is a kind of wireless ad-hoc network, and the routers are free to move randomly and organize themselves arbitrarily; therefore, the network's wireless topology may change rapidly and unpredictably. Such a network may operate alone, or may be connected to the larger Internet.

Ad-hoc networks became a popular subject for research as laptops and 802.11/Wi-Fi wireless networking became widespread. It is a self-configuring network of mobile routers and associated hosts connected by wireless arbitrary topology. It was first introduced in [63], [64] as a wireless extension of packet switching in wire-line networks. Many of the academic papers evaluate protocols and abilities assuming varying degrees of mobility within a bounded space; and recent work in the information theory community has contributed some fundamental performance and scaling laws.

Gupta and Kumar, in a paper [65], prove that certain fixed ad-hoc networks containing M stationary terminals have total throughputs per terminal that decay to zero with increasing M in a constant area. The fixed protocol maximizes transport capacity (bit-meters/second) by having terminals transmit to their nearest neighbors. Shepard [66] draws essentially the same conclusion that terminals should transmit only to their nearest neighbors, by examining the asymptotic behavior of the interference from non-nearest neighbors. A mobile ad-hoc network is examined by Grossglauser and Tse [67]. They prove that a suitable cascade transmission policy which is a so-called multi-user diversity effect: each time the destination terminal receives that it will very likely be near either the original source terminal or an intermediate terminal carrying packet for the source.

## **CHAPTER THREE**

# VIRTUAL SPACE TIME CODING FOR COOPERATIVE SYSTEM

In this chapter, we present a new framework, which is a combination of detect-forward, channel coding, as well as space-time coding methods. First, we describe the overall system model. Then, the protocol and algorithms used in our scheme will be illustrated. Finally, we provide the analysis and simulation of this system's performance.

#### 3.1 Proposed System Model

For simplicity, we consider a system consisting of a source, a relay and a destination. The distance between the source (relay) and destination is several times larger than the distance between the source and relay. In cooperative wireless communication, each node can act either as a transmitter or a relay. It is usually hard to distinguish between its spontaneous and supportive transmission. In order to avoid time conflict, we assume that the nearby node can only listen when one node is sending the information bits.

Figure 3-1: Virtual MISO cooperation system scheme

Figure 3-1 shows the entire communication divided into two steps. In the first time slot, source (A) transmits the information bits (A1) towards the nearby relay (B). The relay detects bits by coherent detection. During the second time slot, while source transits the information bits (A2) to the destination, relay (B) transmits the bits it has detected to the destination simultaneously.

We assume that the cooperative system includes an inter-user channel (between nodes) and uplink channels (from nodes to destination), that are subject to independent

distributed, slowly-varying and flat Rayleigh fading. In our simulations, we assume that the channel state information is known at the receivers. The path gains between source-relay, source-destination and relay-destination are  $h_{AB}$ ,  $h_{AD}$  and  $h_{BD}$ , respectively.

#### 3.2 Inter-user channel transmission

In the first time slot, we focus on the channel between the source and the nearby node. To acquire higher data rate, we choose 16QAM modulation [58]. Therefore, we use  $\log_2 M = \log_2 16 = 4$  bits that can be represented by  $(r_1, r_2, r_3, r_4)$  to represent a symbol. For instance, the symbol with coordinates (-d,3d) maps the 4-bit combination  $r_1 = 1, r_2 = 0, r_3 = 0, r_4 = 1$ . As we can see from the above, the channel coefficient between the source and relay is  $h_{AB}$ , the received signal Y corresponding to the transmitted symbol  $S_{A1}$  can be written as

$$Y = h_{AB}S_{A_1} + N \tag{3-1}$$

Here  $h_{AB}$  is the complex fading channel coefficient with  $E\{\|h\|^2\}=1$  and r.v's h for different symbols are assume to be i.i.d Raleigh distributed, and  $N=N_I+jN_Q$  is a complex Gaussian r.v of zero mean and variance  $\sigma^2/2$  per dimension.

Before going further, let us take a look at the log-likelihood ratio (LLR) for the 16 QAM modulation.

#### 3.2.1 LLR for 16 QAM in a Flat Fading Channel

The received symbol y corresponding to the transmitted symbol a can be expressed as

$$y = ha + n \tag{3-2}$$

The log likelihood ratio can be expressed as

$$LLR(r_i) = \log \left( \frac{\Pr\{r_i = 1 \mid y, h\}}{\Pr\{r_i = 0 \mid y, h\}} \right)$$

$$r_i, i = 1, 2, 3, 4$$

(3-3)

The optimum decision is  $\hat{r_i} = 1$  if  $LLR(r_i) \ge 0$ , and 0 otherwise. We define two sets,  $S_i^{(1)}$  and  $S_i^{(0)}$ , where  $S_i^{(1)}$  comprises symbols with  $r_i = 1$  and otherwise  $S_i^{(0)}$  comprises symbols with  $r_i = 0$  in the constellation, we have

$$LLR(r_i) = \log \left( \frac{\sum_{\alpha \in S_i^{(1)}} \Pr\{\alpha = \alpha \mid y, h\}}{\sum_{\beta \in S_i^{(0)}} \Pr\{\alpha = \beta \mid y, h\}} \right)$$

(3-4)

In our system, we assume that all the symbols are equally likely and that fading is independent of the transmitted symbols. Bayes' rule is used, and then we have

$$LLR(r_{i}) = \log \left( \frac{\sum_{\alpha \in S_{i}^{(1)}} f_{y|h,a} \{ y \mid h, a = \alpha \}}{\sum_{\beta \in S_{i}^{(0)}} f_{y|h,a} \{ y \mid h, a = \beta \}} \right)$$

(3-5)

Since  $f_{y|h,a}\{y \mid h, a = \alpha\} = \frac{1}{\sigma\sqrt{\pi}} \exp(-\frac{\|y - h\alpha\|^2}{\sigma^2})$ , the function (3-5) can be written as

$$LLR(r_{i}) = \log \left( \frac{\sum_{\alpha \in S_{i}^{(1)}} \exp(-\frac{\|y - h\alpha\|^{2}}{\sigma^{2}})}{\sum_{\beta \in S_{i}^{(0)}} \exp(-\frac{\|y - h\beta\|^{2}}{\sigma^{2}})} \right)$$

(3-6)

After approximating by  $\log(\sum_{j} \exp(-X_{j})) \approx -\min_{j}(X_{j})$ , Equation (3-6) can be written as

$$LLR(r_{i}) = \frac{\left\{ \min_{\beta \in S_{i}^{(0)}} \|y - h\beta\|^{2} - \min_{\alpha \in S_{i}^{(1)}} \|y - h\alpha\|^{2} \right\}}{\sigma^{2}}$$

(3-7)

We define that  $x \triangleq \frac{y}{h} = a + \frac{n}{h} = a + \hat{n}$ , where  $\hat{n}$  is also a complex Gaussian R.V. with variance  $\frac{\sigma^2}{\|h\|^2}$ . Substituting x into Equation (3-7) and normalizing  $LLR(r_i)$  by  $4/\sigma^2$ ,

$$LLR(r_{i}) = \frac{\|h\|^{2}}{4} \left\{ \min_{\beta \in S_{i}^{(0)}} \|x - \beta\|^{2} - \min_{\alpha \in S_{i}^{(1)}} \|x - \alpha\|^{2} \right\}$$

$$= \frac{\|h\|^{2}}{4} \left\{ \min_{\beta \in S_{i}^{(0)}} \left( \|\beta\|^{2} - 2x_{I}\beta_{I} - 2x_{Q}\beta_{Q} \right) - \min_{\alpha \in S_{i}^{(1)}} \left( \|\alpha\|^{2} - 2x_{I}\alpha_{I} - 2x_{Q}\alpha_{Q} \right) \right\}$$

(3-8)

Since the sets  $S_i^{(1)}$  and  $S_i^{(0)}$  are partitioned by either vertical or horizontal boundaries, two symbols in different sets closet to the received symbol lie on the same row when the boundaries are vertical, while, lie on the same column when the boundaries are horizontal.

As a consequence, for the bit  $r_1$ , the two constellation symbols in  $S_1^{(1)}$  and  $S_1^{(0)}$  having closest distances to the received symbol satisfy the condition  $\alpha_Q = \beta_Q$ .

Therefore, for bit  $r_1$

$$LLR(r_1) = \begin{cases} -\|h\|^2 x_I d & |x_I| \le 2 \cdot d \\ 2\|h\|^2 d(d - x_I) & x_I > 2 \cdot d \\ -2\|h\|^2 d(d + x_I) & x_I < -2 \cdot d \end{cases}$$

(3-9)

where 2d is the minimum distance between pairs of signal points.

Following the same rule, for bit  $r_2$ ,

$$LLR(r_2) = \begin{cases} -\|h\|^2 x_Q d & |x_Q| \le 2 \cdot d \\ 2\|h\|^2 d(d - x_Q) & x_Q > 2 \cdot d \\ -2\|h\|^2 d(d + x_Q) & x_Q < -2 \cdot d \end{cases}$$

(3-10)

For bit  $r_3$ , we have

$$LLR(r_3) = ||h||^2 d\{x_t | -2d\}$$

(3-11)

And for bit  $r_4$

$$LLR(r_4) = ||h||^2 d\left\{x_Q - 2d\right\}$$

(3-12)

Finding  $(r_1, r_2, r_3, r_4)$  from the  $LLR(r_i)$ , i = 1, 2, 3, 4, we can find the symbol from the constellation as shown in Figure 3-2.

Figure 3-2: 16-QAM Constellation

Defining  $z \triangleq \frac{Y}{h_{AB}} = S_{A1} + \frac{N}{h_{AB}} = S_{A1} + \hat{N}$ , where  $\hat{N}$  is a complex Gaussian R.V with

variance  $\sigma^2 / \|h_{AB}\|^2$ , the LLR equations for each bit of the symbol in our inter-channel can

be presented by:

$$LLR(r_i) = \begin{cases} -\|h_{AB}\|^2 dz_j & |z_j| \le 2d\\ 2\|h_{AB}\|^2 d(d-z_j) & |z_j| > 2d\\ -2\|h_{AB}\|^2 d(d+z_j) & |z_j| < 2d \end{cases}$$

(3-13)

$$j = \begin{cases} I(when & i = 1) \\ Q(when & i = 2) \end{cases}$$

And

$$LLR(r_i) = \|h_{AB}\|^2 d \left\{ z_j \middle| -2d \right\}$$

$$j = \begin{cases} I(when \quad i=3) \\ O(when \quad i=4) \end{cases}$$

(3-14)

Following the LLR approach, we can easily detect and make a decision at node B. When the relay is close to the source, most of the bits can be detected by the relay node. This provides an ideal condition for the next stage of data transmission.

#### 3.3 Uplink channels transmission

After detecting the bits transmitted by the source at the relay node, in the collaborative transmission phase, source and relay will send bits together to the destination. If the channel between the source and relay is good enough; then relay can detect a vast majority of original bits with no error. From the situation described above, it is easy to associate communication in the second time slot with a virtual MISO channel; therefore, the application of Alamouti space-time coding [59] is intuitively justified.

In order to get a better performance and keep the same bandwidth, we use a punctured convolutional code which is called Rate-compatible punctured convolutional codes in both transmission parts (i.e., source and relay to destination).

#### 3.3.1 Rate-compatible punctured convolutional codes

Puncturing is the process of removing certain symbols from the code-word, therefore, reducing the codeword length and increasing the overall code rate. Rate-compatible punctured convolutional (RCPC) codes were first introduced by Hagenauer [60]. RCPC is a special case of punctured convolutional codes that has flexible rates and requires adaptive decoder.

RCPC codes can be obtained by adding a rate-compatibility restriction which implies that a high rate code is embedded in the lower rate codes. Mathematically, a family of RCPC codes can be described by a mother code and a sequence of puncturing matrices. We assume that the generator matrix is  $G = (g_{i,j})_{S \times (M+1)}$  with rate R = 1/S and memory order M. We also assume that the puncturing matrices are  $a(l) = (a_{i,j}(l))_{S \times P}$  for  $l = 1, \dots, (S-1)P$ , with the puncturing period P, and  $a_{i,j}(l) \in \{0,1\}$  where 0 implies puncturing.

The rate-compatibility restriction implies

If

$$a_{i,j}(l_0) = 1$$

, then  $a_{i,j}(l) = 1$  for all  $1 \le l_0 \le l$ .

Meanwhile, the rate of a RCPC code is R(l) = P/(P+l). Therefore, a code with a large value of l has more powerful error correction capability.

As shown in [61], the example of family of RCPC code with rate 1/2 convolutional code and M=2 is punctured periodically with P=4. The generator polynomial of the mother code is  $G(D) = \{D^2 + D + 1, D^2 + 1\}$ , and a sequence of puncturing tables is

$$a(1) = \begin{pmatrix} 1 & 1 & 1 & 0 \\ 1 & 0 & 0 & 1 \end{pmatrix}$$

with code rate 4/5

$$a(2) = \begin{pmatrix} 1 & 1 & 1 & 0 \\ 1 & 1 & 0 & 1 \end{pmatrix}$$

with code rate 2/3

$$a(3) = \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 1 \end{pmatrix}$$

with code rate  $4/7$

$$a(4) = \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & 1 & 1 & 1 \end{pmatrix}$$

with code rate 1/2 (3-15)

Their code rates are shown on the right hand side.

On the received side, the decoder can use the Viterbi algorithm (VA) with a trellis modified by the current puncturing matrix a(l). Suppose X is sent and Y is received. For binary transmission over an additive white Gaussian noise (AWGN) channel, the VA will find the path  $\hat{X}^m$  which satisfies

$$\max_{m} \left( \sum_{i=1}^{J} \sum_{i=1}^{S} a_{i,j} \hat{X}_{i,j}^{m} Y_{i,j} \right)$$

(3-16)

Where  $a_{i,(j+P)} = a_{i,j}$  is the (i, j)th entry of a(l), and J is the trellis length.

#### 3.3.2 Alamouti's 2X1 Space Time Coding

Following PSK modulation, the Alamouti's 2×1 STC codeword is employed.

The transmitted  $2 \times 1$  virtual space time codeword X can be demonstrated as below:

$$X = \begin{bmatrix} x_{A_20} & -x_{A_21}^* \\ x_{B1} & x_{B0}^* \end{bmatrix}$$

(3-17)

The signals in each column represent the symbols transmitted in each adjacent period.

The received signal vector at the destination at adjacent times  $t_0$  and  $t_1$  is

$$r_{D} = \begin{bmatrix} r_{0,} & r_{1} \end{bmatrix} = \begin{bmatrix} h_{AD} & h_{BD} \end{bmatrix} \cdot X + n$$

$$= [h_{AD} \cdot x_{A20} + h_{BD} \cdot x_{B1}, -h_{AD} \cdot x_{A21}^{*} + h_{BD} \cdot x_{B0}^{*}] + [n_{AD,} n_{BD}]$$

(3-18)

Then linear combiner calculates

$$\begin{bmatrix} \tilde{x}_0 & \tilde{x}_1 \end{bmatrix} = \begin{bmatrix} h_{AD}^* & -h_{BD} \\ h_{BD}^* & h_{AD} \end{bmatrix} \begin{bmatrix} r_0 \\ r_1 \end{bmatrix}$$

$$\widetilde{x_{0}} = |h_{AD}|^{2} x_{A_{20}} + |h_{BD}|^{2} x_{B0} + h_{AD}^{*} h_{BD} (x_{B1} - x_{A_{21}}) + h_{AD}^{*} n_{AD} + h_{BD} n_{BD}^{*}$$

$$\widetilde{x_{1}} = |h_{AD}|^{2} x_{A_{21}} + |h_{BD}|^{2} x_{B1} + h_{BD}^{*} h_{AD} (x_{A_{20}} - x_{B0}) - h_{AD} n_{BD}^{*} + h_{BD}^{*} n_{AD}$$

(3-19)

Eventually, at the receiving side, received signal will be detected after the linear combination and Viterbi decoding.

#### 3.4 Energy Distribution

It has been shown that MIMO system can support higher data rates under the same transmit power budget and bit-error-rate performance requirements as a SISO system. In order to comparison, we assume that the total energy consumed in our cooperative virtual space time coding scheme is as the same as a SISO system. For the sake of simplicity, we do not consider the circuit energy consumption of Analog to Digital Converter (ADC), Digital to Analogy Converter (DAC), Mixer, Lower Noise Amplifier (LNA), Frequency Synthesizer, Power Amplifier, and base band DSP.

We consider BPSK-based between the SISO channel where the number of bits in each frame is n, the distance from the source to the destination is defined as d, and the distance between the source and relay is ad(a < 1). We assume that the energy spent on

the inter user channel is  $E_s(QAM)$  per bit; and the energy used in the uplink channel is  $E_s(BPSK)$  per bit. Meanwhile,  $E_s'(BPSK)$  represents the energy of each bit in the SISO non-cooperative channel. Then, the energy allocation can be expressed by the following:

$$E_{s}(QAM_{D=a\cdot dis})\cdot n/4 + E_{s}(BPSK_{D=dis})\cdot n\cdot 2 = E_{s}'(BPSK_{D=dis})\cdot n$$

(3-20)

The left side of equation (3-20) is the total energy consumption in the whole cooperative system. We assume error free transmission in both inter-channel (16 QAM) and SISO channel (BPSK); when  $BER=10^{-5}$ . By normalizing the energy of SISO channel  $E_{siso}(BPSK)$  into unity, we can calculate the approximate value of energy that should distributed on both in inter-user channel and uplink channels.

#### 3.5 Error Performance Simulation

For comparison, we present the simulation result with 100,000 frames, where each frame contains 160 bits. Frame error rate of our scheme is studied and compared to the performance of the convolutional code in both SISO and MIMO systems. We assume that the bits we detected from Node B are error free (BER=10<sup>-5</sup>). Energy allocation has been done through estimation before sending. In order to retain the same bandwidth as that of the convolutional code (rate 1/2), we employ a simple but effective RCPC (Rate-compatible punctured convolutional) code with code rate 4/7 [61]. It can be observed that there is around 4 dB improvement using our scheme compared to a non-cooperative system. Moreover, the effect of the distance between the source and relay on the achieved

improvement is also shown. It is clear that the scheme's performance improves with the reduction of this distance. In other words, instead of spending energy on inter-node communication, we consume more energy to ensure a better performance on the uplink channel.

Figure 3-3: the Comparison of Cooperative and Non-Cooperative Simulation Result

### **CHAPTER FOUR**

# UPLINK RECEIVER HARDWARE IMPLEMENTATION

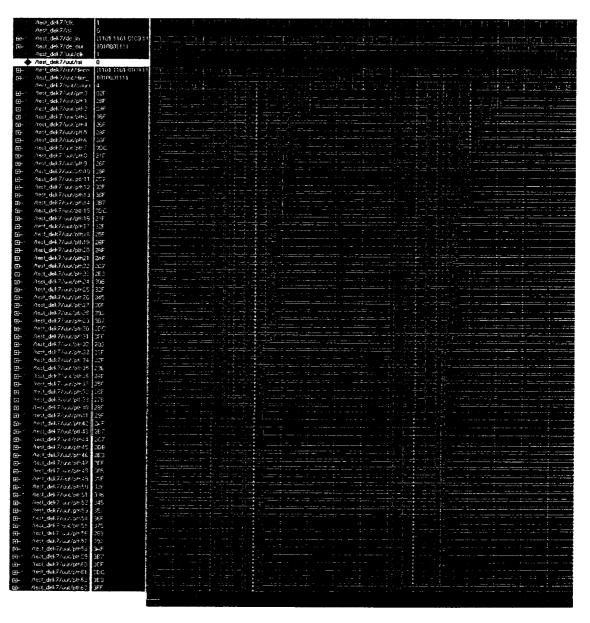

The algorithm of the receiver part introduced in the previous section can be described using the block diagram shown in Figure 4-1. First of all, the received signal is passed through a Matched Filter that contains two RRC filters for both in-phase and quadrature-phase channels. After being transferred into an Alamouti Decoder, 4-bit quantization is used. Finally, we utilize a Viterbi decoder for decoding of the RCPC code.

Figure 4-1: Receiver block diagram

This chapter is organized in the follow way. Section 4.1 presents the detailed process of the Square Root Raised Cosine Filter implementation; then in the next section, we introduce a parallel approach that utilizes the Moore state machine to construct a logic control unit. Moreover, the architecture of the Viterbi decoder for the the RCPC code is illustrated in Section 4.3. Finally, the architecture of the whole receiver is given in the last section. In addition, the results of the RTL level simulation are given in each section, and the overall hardware design summary will be shown in the last section.

#### 4.1 Finite Impulse Response(FIR) filter Implementation