## Design and FPGA Implementation of an OFDM System Based on 3GPP LTE Standard over Multipath Fading Channel

Ahmed Almajdoob

A Thesis

In

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montréal, Québec, Canada

November 2012

©Ahmed Almajdoob, 2012

#### CONCORDIA UNIVERSITY SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

By: Ahmed Almajdoob

#### Entitled: "Design and FPGA Implementation of an OFDM System Based on 3GPP LTE Standard over Multipath Fading Channel"

and submitted in partial fulfillment of the requirements for the degree of

#### **Master of Applied Science**

Complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

Dr. R. Raut

Dr. I. Hassan (MIE)

To the Program

Examiner

Examiner, External

Chair

Dr. A. K. Elhakeem

\_ Supervisor

Dr. Y. R. Shayan

Approved by:

Dr. W. E. Lynch, Chair Department of Electrical and Computer Engineering

20

Dr. Robin A. L. Drew Dean, Faculty of Engineering and Computer Science

#### ABSTRACT

#### Design and FPGA implementation of an OFDM System Based on

#### **3GPP LTE Standard over Multipath Fading**

#### Ahmed Almajdoob

Orthogonal Frequency Division Multiplexing (OFDM) is an appealing multi-carrier modulation technique for achieving high-data-rate transmission over multipath fading channel. Due to the set of orthogonal subcarriers and time interval between symbols, OFDM provides high bandwidth efficiency and robustness against Intersymbol Interference (ISI). By applying OFDM, several requirements of standards for advanced communications systems can be fulfilled leading to wide adoption and utilization commonly used in wireless systems. Field programmable gate arrays (FPGAs) offer high-performance and low-cost DSP solution for digital communication system implementation and verification. Due to their flexibility and upgradeability, FPGAs have become widely used in implementation of DSP functions

In this thesis, an OFDM system is designed and implemented on an FPGA platform in accordance with the design flow methodology. Based on 3rd Generation Partnership Project (3GPP) Long Term Evolution (LTE) parameters, extended and normal-CP OFDM systems are modeled and simulated in MATLAB to examine the systems using BER performance. The OFDM system with extended-CP has been selected for the design because of its better robustness against wireless Rayleigh multipath fading channels. The extended-CP OFDM system is transformed to a Simulink model and analyzed.

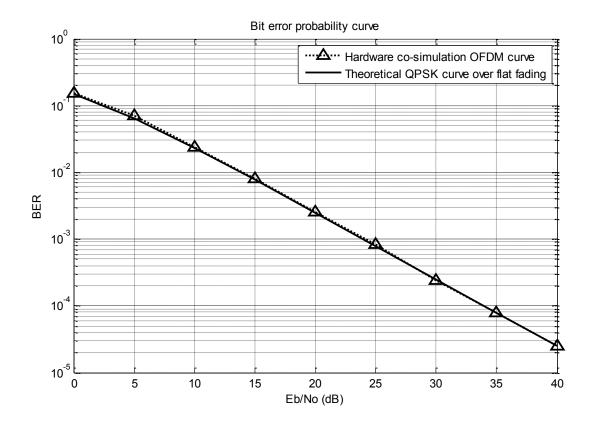

Using Xilinx System Generator, the OFDM system is designed and tested in Simulink before the compilation for hardware co-simulation. This Xilinx system at a clock speed of 100 MHz has a throughput of 20 Mbps and an intermediate frequency of 25 MHz for OFDM transmission. Since Xilinx XtremeDSP platforms provide a rich set of DSP algorithms, the Xilinx-based OFDM design is implemented in hardware using Xilinx Virtex-5 FPGA ML506 board. This design has utilized 56% of Flip-flops, 33% of LUTs, 24 % of block RAMs and 10% of DSP48Es available on Virtex-5 device. The system verification is performed by simulating and analyzing the hardware co-simulation results showing the resistance of the OFDM system to Rayleigh multipath fading channel.

### Acknowledgements

The success of any project depends largely on the guidance and encouragement of many people. This thesis would not have been possible without their support. Therefore, I take this opportunity to express my sincere gratitude to my supervisor, Dr. Yousef R. Shayan, for his unwavering support, enthusiastic supervision and invaluable assistance with the development and completion of this research. He has shared his technical expertise and guided me diligently in the arduous process of thesis writing. His availability and patience have proven a great inspiration to me throughout my master's studies at Concordia University.

I also wish to express my deep gratitude and love to my beloved parents for their understanding and enormous support through the duration of my studies. Their consistent encouragement has motivated and guided me on the path towards my degree completion.

Last but not the least, I am deeply indebted to my friends and colleagues who have helped me adapt to a new life in a foreign country and provided the moral support needed for the fulfillment of my academic goals.

# **Table of Contents**

| List of Figures                             | ix  |

|---------------------------------------------|-----|

| List of Tables                              | xi  |

| List of Acronyms                            | xii |

| Chapter 1 Introduction                      |     |

| 1.1 Background                              | 1   |

| 1.2 OFDM History and Development            |     |

| 1.3 Thesis Motivation and Contribution      |     |

| 1.4 Thesis Organization                     | 7   |

| Chapter 2 OFDM System and Wireless Channel  |     |

| 2.1 Introduction to OFDM Modulation         | 9   |

| 2.2 QPSK Baseband Modulation                |     |

| 2.3 Overview of OFDM System                 |     |

| 2.3.1 Guard Interval and Cyclic Prefix      |     |

| 2.3.2 Pulse Shaping                         |     |

| 2.3.3 Peak to Average Power Ratio           |     |

| 2.4 Wireless Fading Channel                 |     |

| 2.4.1 Small-Scale Fading Channel            |     |

| 2.4.2 Frequency Dispersion                  |     |

| 2.4.3 Time Dispersion                       |     |

| 2.4.4 Impulse Response of Fading Channel    |     |

| 2.5 LTE Physical Layer Downlink Parameters  |     |

| 2.6 Summary                                 |     |

| Chapter 3 OFDM System Design and Simulation |     |

| 3.1 Design Flow                                        |    |

|--------------------------------------------------------|----|

| 3.2 Floating-Point Modeling and Simulation in MATLAB   |    |

| 3.2.1 Random Data Generation                           |    |

| 3.2.2 QPSK Modulation                                  |    |

| 3.2.3 Serial to Parallel Conversion                    |    |

| 3.2.4 Zero Padding                                     |    |

| 3.2.5 Inverse Discrete Fourier Transformer             |    |

| 3.2.6 Adding Cyclic Prefix                             |    |

| 3.3 Channel Modeling                                   |    |

| 3.4 MATLAB Simulation Results                          |    |

| Experiment 1: The Effect of Flat Fading Channel        |    |

| Experiment 2: The Effect of 30-Path Channel            |    |

| Experiment 3: The Effect of 100-Path Channel           |    |

| Experiment 4: The Effect of 140-Path Channel           |    |

| 3.5 Floating-Point Modeling and Simulation in Simulink |    |

| 3.6 Simulink Simulation Results                        |    |

| 3.7 Summary                                            |    |

| Chapter 4 OFDM Hardware Design and FPGA Implementation | 55 |

| 4.1 Xilinx OFDM Transmitter                            |    |

| 4.1.1 Random Data Generation                           |    |

| 4.1.2 QPSK Modulation                                  |    |

| 4.1.3 Zero-Padding                                     |    |

| 4.1.4 OFDM Modulation                                  |    |

| 4.1.5 Digital Up-Conversion                            |    |

| 4.2 Rayleigh Fading Channel                            |    |

| 4.3 AWGN Channel                                 |     |

|--------------------------------------------------|-----|

| 4.4 Xilinx OFDM Receiver                         |     |

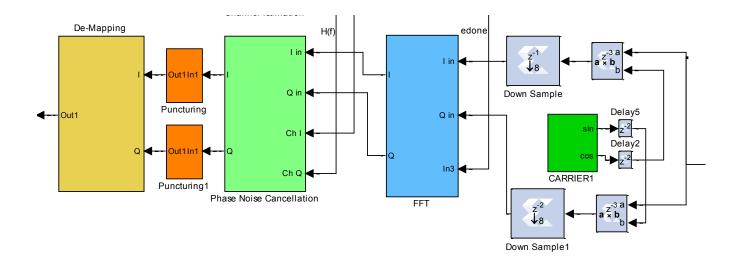

| 4.4.1 Down-Conversion and OFDM Demodulation      | 74  |

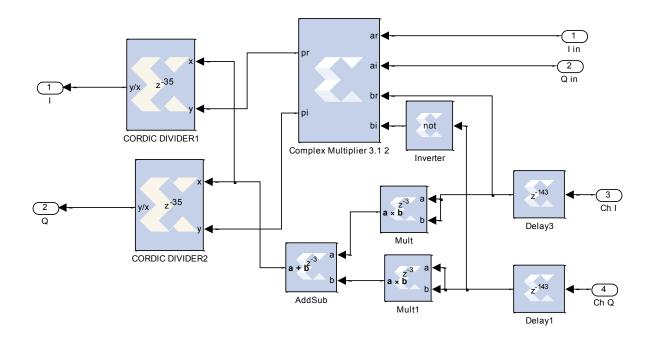

| 4.4.2 Phase Noise Cancellation                   |     |

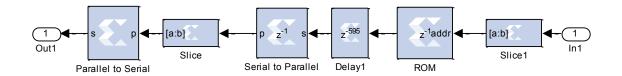

| 4.4.3 Puncturing                                 |     |

| 4.4.3 QPSK Demodulation                          | 80  |

| 4.5 Summary                                      |     |

| Chapter 5 Hardware Verification and Test Results |     |

| 5.1 The Simulation Results of Xilinx OFDM System |     |

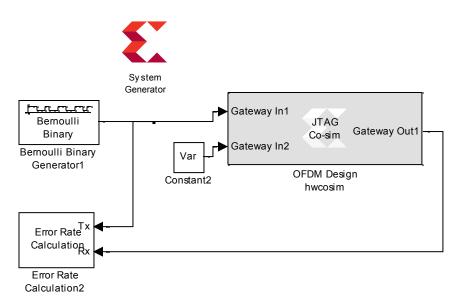

| 5.2 Hardware Co-Simulation                       | 85  |

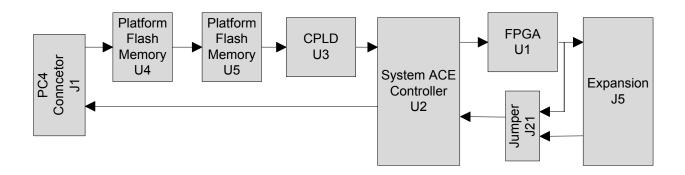

| 5.2.1 Introduction of XtremeDSP board            | 86  |

| 5.2.2 Hardware Co-Simulation Setup               |     |

| 5.3 Hardware Co-Simulation Results               |     |

| 5.4 Hardware Utilization                         |     |

| 5.5 Summary                                      |     |

| Chapter 6 Conclusion and Future Work             |     |

| Bibliography                                     | 101 |

# **List of Figures**

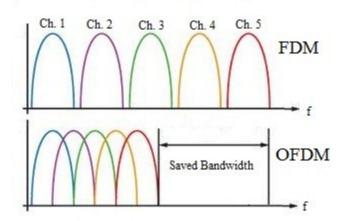

| Figure 2-1: Bandwidth comparison between FDM and OFDM               |    |

|---------------------------------------------------------------------|----|

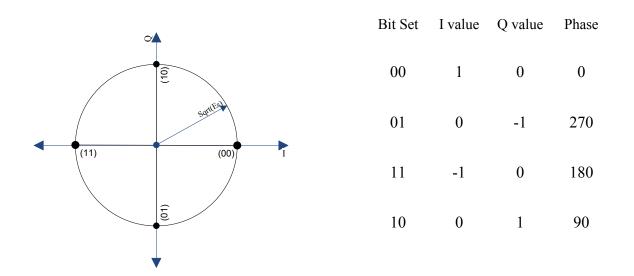

| Figure 2-2: QPSK signal constellation                               |    |

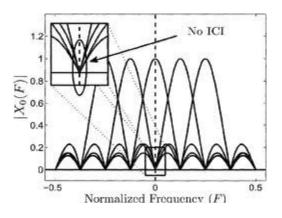

| Figure 2-3: OFDM frequency spectrum                                 | 15 |

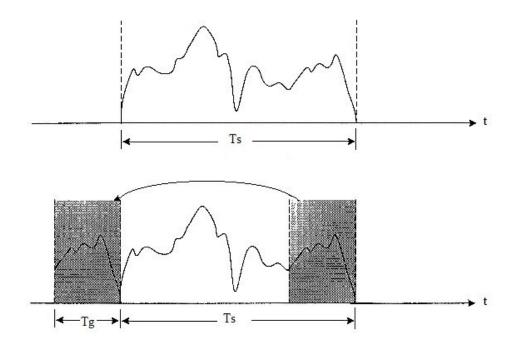

| Figure 2-4: OFDM cyclic prefix                                      | 17 |

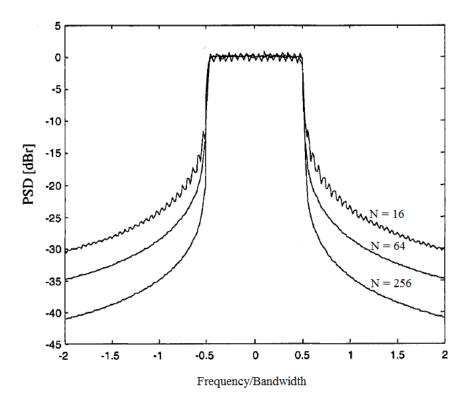

| Figure 2-5: OFDM Power spectrum density for different N subcarriers |    |

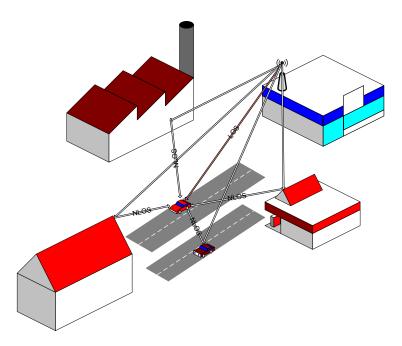

| Figure 2-6: Multipath fading                                        | 21 |

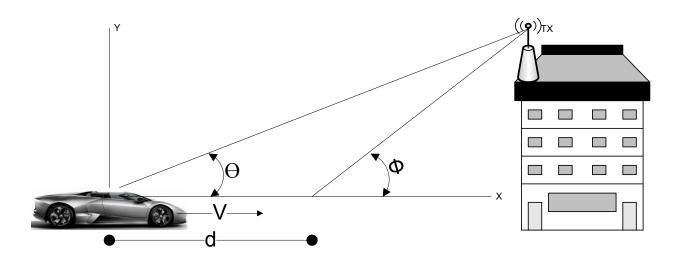

| Figure 2-7: Doppler effect on a mobile station                      |    |

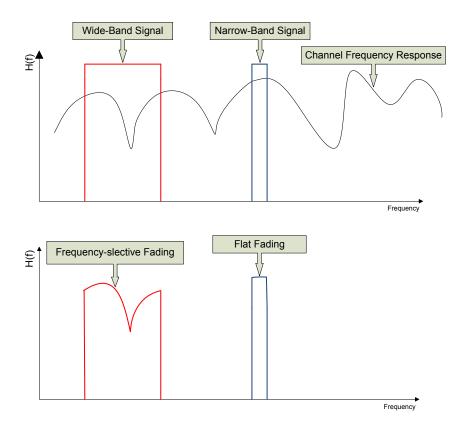

| Figure 2-8: Flat and frequency-selective fading                     |    |

| Figure 2-9: Radio frame structure type 1                            |    |

| Figure 3-1: Implementation design flow                              |    |

| Figure 3-2: Block diagram of an OFDM transceiver                    |    |

| Figure 3-3: Exponential and 2-ray models                            |    |

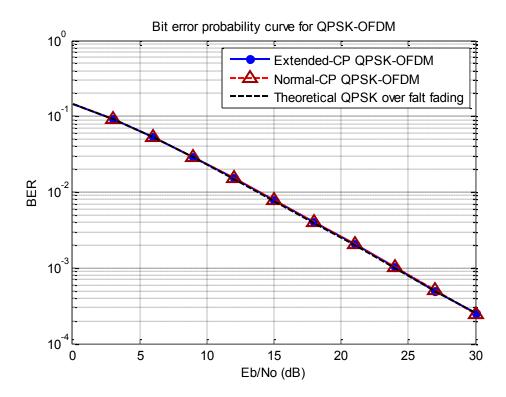

| Figure 3-4: BER of the OFDM systems under flat fading channel       |    |

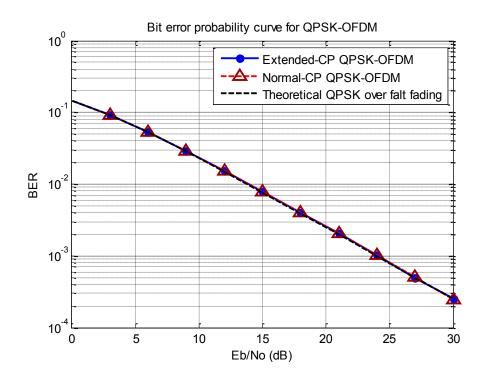

| Figure 3-5: BER of the OFDM systems under 30-path channel           |    |

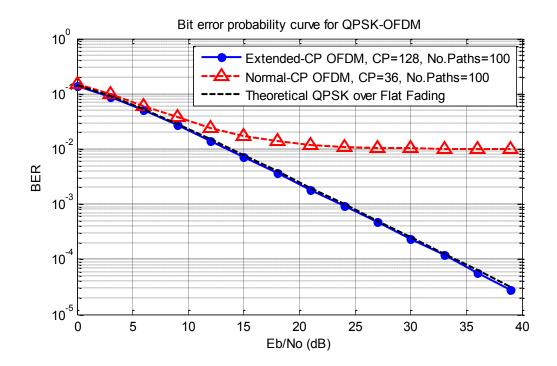

| Figure 3-6: BER of the OFDM systems under 100-path channel          |    |

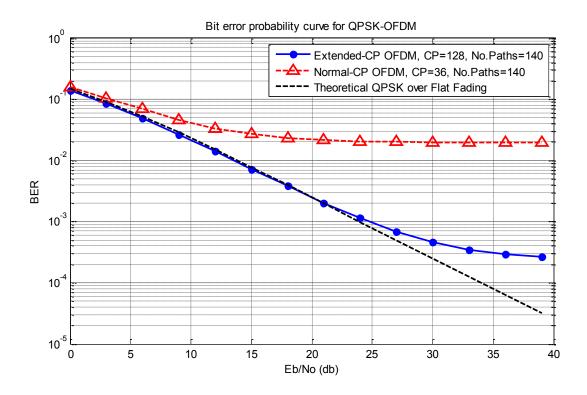

| Figure 3-7: BER of the OFDM systems under 140-path channel          |    |

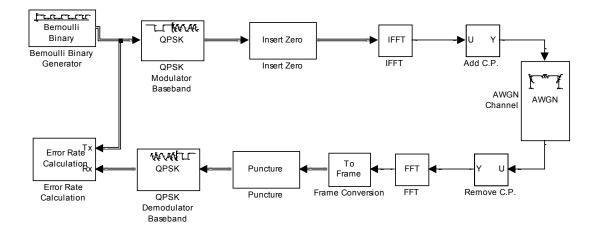

| Figure 3-8: QPSK-OFDM model in Simulink                             | 51 |

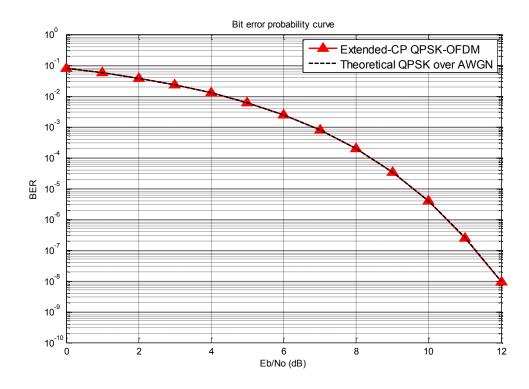

| Figure 3-9: BER of the QPSK-OFDM system under AWGN channel          |    |

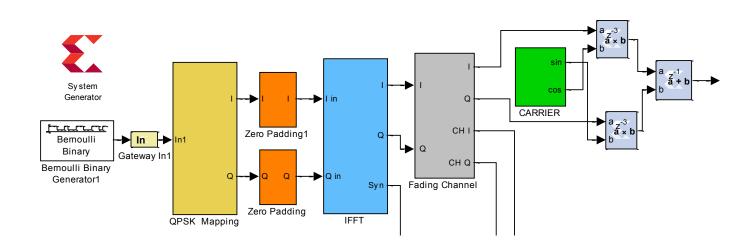

| Figure 4-1: Block diagram of Xilinx OFDM transmitter                |    |

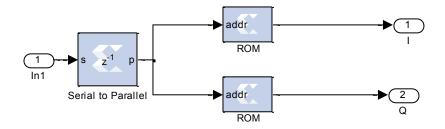

| Figure 4-2: Xilinx QPSK modulator                                   |    |

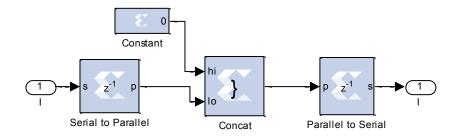

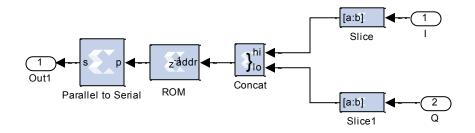

| Figure 4-3: Xilinx Zero-padding design                              | 59 |

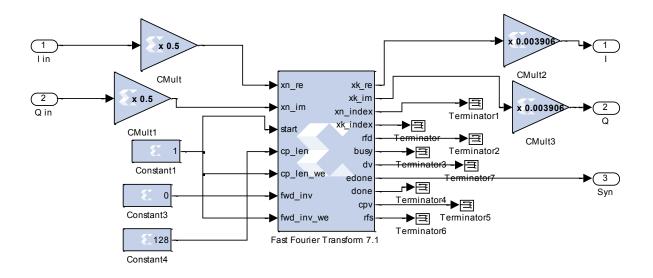

| Figure 4-4: Xilinx FFT V7.1 block with unscaled output                           | 62 |

|----------------------------------------------------------------------------------|----|

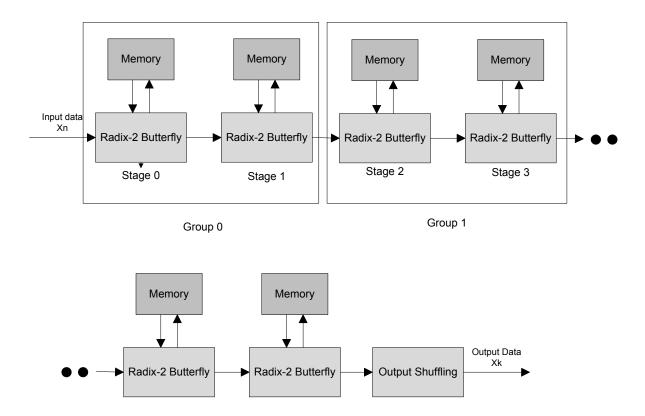

| Figure 4-5: Pipelined Stream I/O Architecture                                    | 63 |

| Figure 4-6: Xilinx OFDM modulator design                                         | 65 |

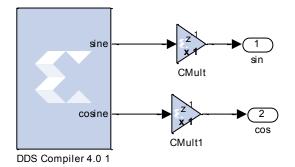

| Figure 4-7: Carrier signal generator                                             | 66 |

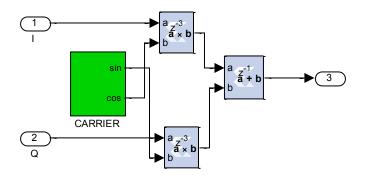

| Figure 4-8: I and Q Xilinx digital modulator and up-converter                    | 68 |

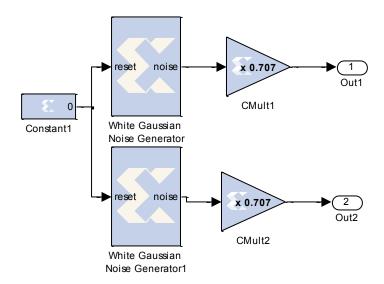

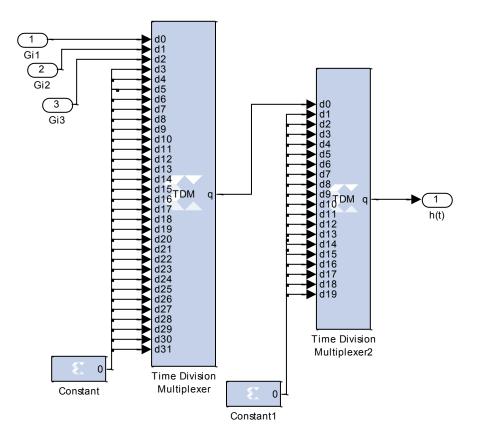

| Figure 4-9: Xilinx fading noise generator                                        | 69 |

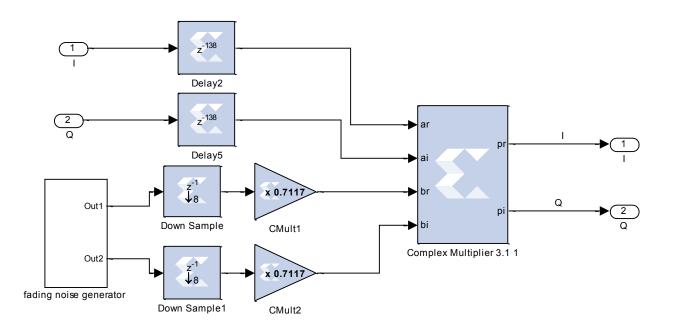

| Figure 4-10: The first path of Xilinx 3-paths Rayleigh fading channel design     | 70 |

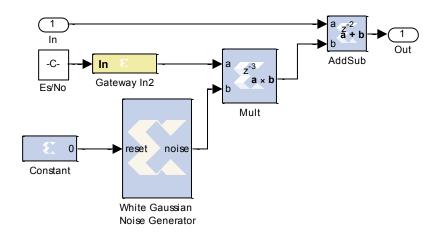

| Figure 4-11: AWGN channel Design                                                 | 73 |

| Figure 4-12: Xilinx QPSK-OFDM receiver                                           | 74 |

| Figure 4-13: Xilinx design for the real component of channel response            | 77 |

| Figure 4-14: Xilinx Complex Divider Design                                       | 78 |

| Figure 4-15: Xilinx Puncturing Design                                            | 79 |

| Figure 4-16: Xilinx QPSK demodulator                                             | 80 |

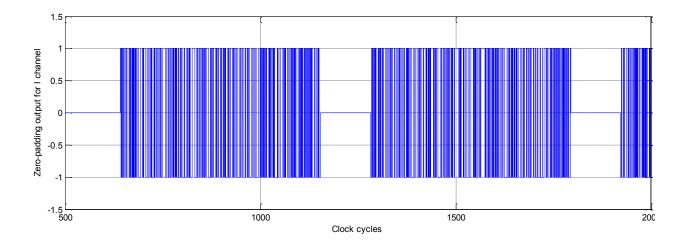

| Figure 5-1: In-phase component of zero-padding output                            | 83 |

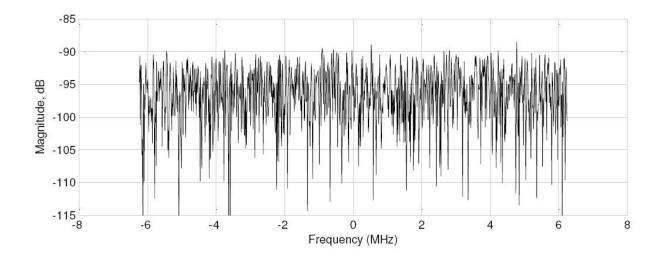

| Figure 5-2: OFDM signal spectrum                                                 | 84 |

| Figure 5-3: XtremeDSP development platform -Virtex-5 FPGA ML506 Edition          | 86 |

| Figure 5-4: JTAG chain                                                           | 89 |

| Figure 5-5: OFDM model for hardware co-simulation                                | 91 |

| Figure 5-6: BER comparison between hardware co-simulation and theoretical curves | 93 |

## **List of Tables**

| Table 2-1: Typical parameters for downlink transmission             | 28             |

|---------------------------------------------------------------------|----------------|

| Table 5-1: Design utilization summary                               | 95             |

| Table 5-2: Comparison between our design and work published in 2010 | <del>)</del> 6 |

# List of Acronyms

| Acronym | Expansion                               |

|---------|-----------------------------------------|

| ADC     | Analog to Digital Converter             |

| ADSL    | Asymmetric Digital Subscriber Line      |

| ASIC    | Application Specific Integrated Circuit |

| BER     | Bit Error Rate                          |

| BPSK    | Binary Phase Shift Keying               |

| CORDIC  | Coordinate Rotation Digital Computer    |

| СР      | Cyclic Prefix                           |

| DAC     | Digital to Analog Converter             |

| DDC     | Digital Down-Converter                  |

| DDR     | Double Rate Data                        |

| DFT     | Discrete Fourier Transform              |

| DSP     | Digital Signal Processing               |

| DSPs    | Digital Signal Processors               |

| DUC     | Digital Up-Converter                    |

| DVB     | Digital Video Broadcasting              |

| EEPROM | Electrically Erasable Programmable Read Only Memories |

|--------|-------------------------------------------------------|

| EPROM  | Erasable Programmable Read Only Memories              |

| FDM    | Frequency Division Multiplexing                       |

| FFT    | Fast Fourier Transform                                |

| FPGA   | Field Programmable Gate Array                         |

| HDSL   | High-bit-rate Digital Subscriber Lines                |

| ICI    | Inter Carrier Interference                            |

| IF     | Intermediate frequency                                |

| IFFT   | Inverse Fast Fourier Transform                        |

| ISI    | Inter-Symbol Interference                             |

| LTE    | Long Term Evolution                                   |

| LUT    | Look-Up Table                                         |

| MIMO   | Multiple-Input Multiple-Output                        |

| Msps   | Mega-Sample per Second                                |

| OFDM   | Orthogonal Frequency Division Multiplexing            |

| PAPR   | Peak-to-Average Power Ratio                           |

| PDF    | Probability Density Function                          |

| PROM   | Programmable Read Only Memories                  |

|--------|--------------------------------------------------|

| PSC    | Parallel to Serial Converter                     |

| PSF    | Pulse Shaping Filter                             |

| PSK    | Phase-Shift Keying                               |

| QAM    | Quadrature Amplitude Modulation                  |

| QoS    | Quality of Service                               |

| QPSK   | Quadrature Phase Shift Keying                    |

| ROM    | Read Only Memory                                 |

| SISO   | Single-Input Single-Output                       |

| SNR    | Signal to Noise Ratio                            |

| SODIMM | Small Outline Dual In-line Memory Module         |

| SPC    | Serial to Parallel Converter                     |

| VHDL   | Very-High-Speed Integrated Circuits or VHSIC HDL |

| WLAN   | Wireless Local Area Network                      |

| 3GPP   | 3 <sup>rd</sup> Generation Partnership Project   |

## **Chapter 1**

## Introduction

#### 1.1 Background

Wireless communication systems demand data-intensive applications such as data transfer, multimedia services, audio and video stream. The need of these applications has made high-date rate the main requirement for wireless networks as well as broadcasting standards. Dealing with channel distortion at high data rate communications is very complicated and requires a very complex receiver structure using channel estimation algorithms and equalization. For high-date-rate communications, the interest is focused on modulation techniques that can provide broadband transmission over various wireless channels. Standard single-carrier modulation techniques, such as Phase Shift-keying (PSK) and Quadrature Amplitude Modulation (QAM), are applied for flat channels, whereas multicarrier modulation techniques can deal with non-flat broadband channels.

As a multicarrier modulation, orthogonal frequency division multiplexing (OFDM) splits high-rate data stream into a number of low rate streams or sub-channels transmitted simultaneously over orthogonal subcarriers. As a result, the frequency-selective wide-band channel is transformed into a group of non-frequency-selective narrowband channels. In this way, standard PSK or QAM can be used for each subchannel and only a simple equalizer is adequate for channel estimation. Compared with other multicarrier modulation methods, OFDM uses the frequency spectrum very efficiently. By preserving orthogonality, it is considered a bandwidth-efficient signaling scheme with reasonable complexity and high performance. The OFDM modulation has some advantages over the traditional frequency division multiplexing modulation techniques which are summarized below [1].

- Simple hardware realization using FFT implementation

- Robustness against intersymbol interference leading to low complex receiver structure

- No guard band between subchannels leading to an efficient use of spectrum

- Different modulation schemes can be used in one OFDM system.

- Resistant to co-channel interference.

- Supports frequency diversity.

Therefore, a worldwide convergence has occurred for the use of OFDM modulation due to its high data rate transmission and ability to combat against frequency-selective fading. Many wireless standards, such as Wi-Max, IEEE802.11a/g/n, 3rd Generation Partnership Project (3GPP) Long Term Evolution (LTE) and Digital Audio Broadcast (DVB), have adopted OFDM technology. Moreover, OFDM technique has been applied not only in wireless digital communication systems but also in wired digital communication as in Asymmetric Digital Subscriber Line (ADSL) technology.

#### **1.2 OFDM History and Development**

First existence of OFDM-based systems was during the Second World War in highfrequency US military systems, KINPEPLEX, ANDEFT and KATHRYN [2]. Using PSK modulation, these systems had up to 34 parallel sub-channels generated by a frequency multiplexing set of subchannels. The first theoretical way to transmit parallel data simultaneously was proposed by Robert W. Chang in December 1966 [3]. Chang proposed the principle concept of OFDM in such a way that data stream can be divided to sub-bands and transmitted through band-limited channels without experiencing Intersymbol Interference (ISI) and Intercarrier Interference (ICI). Due to his publication, he successfully obtained the first US patent on OFDM in January 1970 [4].

In December 1967, Saltzberg analyzed the OFDM performance [5] as well as demonstrating OFDM methodology of dividing the available bandwidth to sub-channels modulated with different carrier frequencies. The paper proved that the use of multiple independent narrow channels deters the signals from encountering the channel distortion due to intersymbol interference. Based on OFDM concept, the orthogonal subcarriers are overlapped with the neighbor subcarriers in a way that the orthogonality is preserved. The use of a large number of subcarriers in that time was difficult and complicated since it required a large number of oscillators for parallel data transmission. Therefore, the number of subcarriers for these traditional OFDM systems was limited.

In 1971, Weinstein and Ebert proposed a discrete Fourier Transform (DFT) for OFDM modulation. It was a major breakthrough in the history of OFDM. They used DFT to perform baseband OFDM modulation and demodulation, which reduces significantly the complexity of implementation. Focusing on an efficient process for OFDM, they proposed a model that modulated and demodulated baseband signals by applying IDFT and DFT, respectively. This approach has reduced the system complexity by replacing subcarrier oscillators with IDFT and DFT for efficient OFDM implementation. Up to 1980, OFDM systems used a conventional guard time interval of redundancy added to OFDM symbols to eliminate intersymbol interference. Peled and Ruiz presented a new approach and introduced cyclic prefix (CP) or

cyclic extension for OFDM [6]. They proved that the use of CP instead of guard time interval maintains the orthogonality among subcarriers. During the 1980s, some minor proposals were represented to suppress ISI and ICI [7], and to reduce the sub-channel and multipath interference [8].

Due to its advantages, OFDM was applied for high-data-rate communication systems in the 1990s such as ADSL, DVB and high-bit-rate digital subscriber lines (HDSL). Also several wireless local area networks (WLAN) standards such as IEEE 802.11a/g/n have adopted OFDM technology on their physical layer [9]. In addition, broad-band wireless access standard IEEE 802.16e (WiMAX) utilizes OFDM modulation in its physical layer operating at the range of 10 to 56 GHz. Moreover, the OFDM technology is expected to play a more prominent role in future wireless communications, as 4G mobile broadband 3GPP LTE standard employs OFDM for the down link.

#### **1.3 Thesis Motivation and Contribution**

Wireless multimedia communication requires high-bit-rate transmission for reasonable quality of service (QoS). The demand of high data rate for future wireless communications has given us the inspiration of designing a communication system that can achieve high-bit-rate transmission. It has been found that many digital modulation schemes cannot provide high-speed single-carrier wireless transmission when there is frequency-selective fading in the channel, whereas OFDM modulation scheme has the ability to deal with this channel efficiently.

Most of publications related to OFDM focus on the theoretical part and analysis of OFDM and its advantages. There are a limited number of publications that have implemented OFDM systems in hardware with reasonable performance due to its complexity. The most of the existing papers [10], [11], [12] and [13] have proposed the design and implementation of the OFDM transmitter only by using either HDLs coding or Xilinx System Generator blockset. Limited work has been done on the complete design of OFDM transceiver. In the 2010 conference paper [14], an OFDM transceiver is implemented on an FPGA by using Xilinx blockset libraries. The OFDM modulation has only 64 subcarriers modulated with 16-QAM scheme. This performance of system is evaluated over AWGN channel provided by Simulink. Neither CP addition nor fading channel is applied to OFDM system. Instead of designing Xilinx demodulator, a MATLAB code is used in Xilinx M-Code block for 16-QAM de-mapping. Although IFFT and FFT have a small size of 64 points with 16-bit fixed point representation, there was a difference between the Bit Error Rate (BER) curve of FPGA fixed point and the MATLAB floating-point curve (theoretical curve).

In journal paper [15] published in April 2012, a QAM-OFDM system was implemented on Virtex-2 Pro using Xilinx ISE tool. This system wasn't tested under any noise to evaluate the system performance. The waveforms of transmitted and recovered signals were investigated to imply the system design has met the theoretical observations. The BER performance could not be provided for evaluation due to nonexistent channel.

The main objective in this thesis is to design and implement in hardware an OFDM communication system including CP addition, and to evaluate its performance over multipath fading channel. The FFT size in the OFDM system has to be large for better bandwidth spectrum efficiency. The QPSK digital modulation scheme is applied in the OFDM design as a popular modulation technique utilized in many digital signal processing (DSP) systems. Our design of QPSK-OFDM system is based on the 3GPP LTE specifications in terms of FFT size and CP length.

The growth of high-bandwidth mobile applications has driven the demand for mobile broadband. As the next step forward in cellular services, LTE is a 3GPP standard for wireless communication of high-speed data for mobile phones. The target of LTE is to improve the interface capabilities between the base station and the user equipment. The 3GPP defined initial requirements of the LTE physical layer, which have to support peak data rates of more than 100 Mbps for the downlink and 50 Mbps for the uplink. Also LTE should support scalable transmission bandwidth ranging from 1.4 to 20 MHz. To fulfill these requirements, OFDM modulation technique is employed by the LTE downlink physical layer.

Field Programmable Gate Array (FPGA), however, has made a significant improvement in the development of DSP applications. With high performance FPGA components from Xilinx and Altera, DSP solutions can be deployed with low cost. Modern FPGA devices provide extensive DSP support for intensive signal processing applications. In this thesis, Xilinx Virtex-5 device is chosen for efficient FPGA-based implementation of QPSK-OFDM system. Actually this device has many high-capability building blocks known as XtremeDSP DSP48 slices, which support digital signal algorithmic processing. Using Xilinx design tools, our OFDM system is designed and implemented on Xilinx Virtex-5. By implementing and testing OFDM system in hardware, the robustness of OFDM against multipath fading channel is verified. This work offers a complete documentation of design and implementation for DSP algorithms. In fact, this thesis provides a modern methodology of design and implementation rather than the traditional method using the standard register transfer logic flow. In this methodology, a DSP algorithm design is transformed from high level design to RTL model by going through various design steps. However, this project has been implemented using equipment provided in Wireless Design Lab at Concordia University, and it will be the basis for many future works of the lab.

Compared with recent conference paper [14], the implementation of OFDM system in this work has included not only cyclic prefix but also the wireless fading channel model to verify the system performance over multipath fading channel. Therefore, this work is hoped to be a reference point for OFDM implementation including wireless fading channel.

In brief, the contributions of this thesis are detailed in the following points:

- Design and implementation of QPSK-OFDM system in hardware based on downlink physical later parameters for 3GPP LTE standard with throughput of 20 Mbps.

- Proposing a new design flow methodology of different stages from modeling and simulation to hardware implementation for system design and FPGA implementations.

- Comparative analysis of extended and normal CPs for 3GPP LTE standard and selection of the most robust parameters based on simulations.

- Providing a technique for Xilinx implementation of CP insertion and removal in OFDM system using Xilinx System Generator DSP design tool.

- Modeling and FPGA implementation of multipath fading channel utilizing uncorrelated AWGN generators as requirement for OFDM system design verification in wireless channel environment.

- Accomplishment of high performance for OFDM implementation with FFT size of 512 on ML506 Virtex-5 device, which verifies the OFDM resistance against frequencyselective fading.

#### **1.4 Thesis Organization**

The second chapter of this thesis begins with introduction of digital communication systems showing the benefits of using OFDM modulation over traditional FDM modulations. A

typical OFDM system is overviewed explaining each part of the transmitter and the receiver. The theoretical background of each stage is provided to clarify signal processing for OFDM system. That includes the techniques and algorithms used in OFDM modulation for better performance and less complexity. Moreover, Wireless fading channel and QPSK modulation are described and analyzed. The physical layer parameters for LTE downlink are overviewed.

The third chapter introduces the design flow methodology utilized in this work in order to implement the QPSK-OFDM system. Following this strategy, the OFDM system with 3GPP LTE parameters is modeled in MATLAB with floating-point representation. The exponential model is proposed for wireless Rayleigh frequency-selective fading channel. Two MATLAB-based models for OFDM systems different in CP are simulated to examine their performance over multipath fading channels. Also a QPSK-OFDM model is created and tested over AWGN channel in Simulink.

In Chapter 4, the extended-CP OFDM design is implemented using Xilinx blockset libraries provided by Xilinx System Generator. This chapter gives a complete description for each Xilinx component and subsystem used in Xilinx OFDM design. The techniques applied for implementation, synchronization and optimization are illuminated among the description. The wireless channel model is also implemented in the fixed-point OFDM model.

Chapter 5 is dedicated to hardware co-simulation and the experimental results. Introduction to the hardware platform is provided as well as the hardware co-simulation steps. The BER performance is presented and analyzed to illustrate the design performance. This dissertation includes the design summary showing the device utilization. Chapter 6 summarizes the work, and concludes the thesis with some recommendations for future research.

8

## **Chapter 2**

## **OFDM System and Wireless Channel**

#### **2.1 Introduction to OFDM Modulation**

As the wireless communication industry evolves rapidly, the demand for high data rates increases making the issues with unpredictable wireless communication channel more complicated. Since the channel distortion at high data rate is more considerable, recovering highrate transmitted data is difficult or impossible in some cases requiring a very complex expensive receiver [16]. One of the advantages of Frequency Division Multiplexing (FDM) is the capability of dealing with frequency-selective fading by turning into flat fading and making one-tap equalizer in the receiver sufficient for channel estimation. In fact, FDM modulation is one of the implementations for multiple carrier communication as it transmits multiple low-rate signals using separate carrier frequencies for each signal. To avoid overlapping among signals, the space between the various carrier frequencies has to be efficiently specified to reduce the complexity of filters at the receiver side. This communication scheme is also used for wide-band single wireless channel by breaking it into sub-channels to counter the signal from intersymbol interference. When the bandwidth of the sub-channels is narrower than the bandwidth of the wireless channel, they will tolerate only flat fading. In other words it turns frequency-selective fading channel into flat fading channel. Since the ISI is minimized by using the FDM technique, there is no more need for costly complicated equalizer, only one-tap equalizer is required for channel estimation and signal recovery. To avoid overlapping and simplify the structure of filters at the receiver, spectrum spaces between sub-channels are needed to separate the various carrier

frequencies. One of disadvantages of FDM, however, is that the spectrum efficiency is very low since the total bandwidth of separated wireless sub-channels is much more than the bandwidth needed for a wide-band signal wireless channel.

The Orthogonal Frequency Division Multiplexing (OFDM) technique was proposed for high data rate communications in selective fading channel. In fact, OFDM is a special case of multicarrier transmission, where a number of low-rate parallel subcarriers are transmitted regularly over the frequency band to ensure orthogonality [17]. In OFDM the sub-channels are overlapping each other but there is no interference between them as the orthogonality property is achieved. Compared with the classical non-overlapping FDM systems, OFDM technique saves almost 50% of the bandwidth [18].

Figure 2-1: Bandwidth comparison between FDM and OFDM

By dividing the energy into small portions, each subcarrier is transmitted using a sinusoidal generator. This requires a bank of generators for transmission and reception. However, the use of Discrete Fourier Transform (DFT) has simplified the structure of OFDM by replacing the banks at the transmitter and receiver, leading to a very important reduction of the complexity of the OFDM system's implementation. In OFDM systems, input data is converted from one stream

data to N parallel data stream by using serial to parallel converter (SPC), and then they are modulated by Inverse Fast Fourier Transformer (IFFT). Thereby, the wide-band signal is broken into N narrow-band parallel signals when the rate of the input signal is divided by N to become the rate of each sub-signal. At the receiver, however, the data streams demodulated by Fast Fourier Transformer (FFT) are converted to one data stream using parallel to serial converter.

In OFDM digital communication systems, the high-rate input data can be digitally modulated by one or more digital modulate scheme such as BPSK, QPSK, 16-QAM and 64-QAM. In this case the digital signal is mapped according to the modulation scheme and then is broken into low-rate sub signals using serial to parallel converter to be fed to inverse fast Fourier transformer. Multi-input signals can also be mapped separately with multiple modulation schemes and fed to the same OFDM modulator but when they are converted from serial to parallel, all the outputs of low-rate sub-signals have to have the same bit. In this thesis, QPSK modulation has been discussed and used with OFDM modulation to create our QPSK-OFDM system.

As OFDM has many advantages over single-carrier schemes, it has become very popular for wideband digital communications and has been adopted for many communication systems and standards such as Digital Video Broadcasting (DVB), Digital Audio Broadcasting (DAB), Digital Subscriber Line (DSL), 4<sup>th</sup> generation mobile communication and wireless networks IEEE802.11a, g, n.

#### 2.2 QPSK Baseband Modulation

Since linear digital modulation techniques are bandwidth-efficient, they are widely used in wireless communication systems. PSK modulation techniques, such as BPSK, QPSK and 8PSK are linear modulations in which the phase of the transmitted signal varies according to the input data. In QPSK modulation, every two bits are modulated to be one QPSK symbol and that saves more bandwidth compared with BPSK modulation. The original signal stream with values of 1 and 0 is mapped and divided into two streams in-phase and Quadrature streams as values of  $\pm 1$ , which have the half bit rate of the original data. The QPSK symbol can be only in one of four states which are different in phase and equally spaced by  $\pi/2$  such as 0,  $\pi/2$ ,  $\pi$  or  $3\pi/4$ . The figure below depicts the constellation of QPSK symbol in two dimensions.

Figure 2-2: QPSK signal constellation

where  $E_s$  is the symbol energy and  $E_s$  is equal to twice  $E_b$  (bit energy). As shown in Figure 2-2, all QPSK symbols have the same energy  $E_s$  but they have different phases. The probability of bit error for coherent QPSK over additive white noise channel can be expressed [19] as

$$P_{QPSK} = Q\left[\sqrt{\frac{Es}{N_0}}\right]$$

where  $Q(X) = \frac{1}{\sqrt{2\pi}} \int_{x}^{\infty} \exp(-\frac{u^2}{2}) du$  and  $N_0$  is noise spectral density.

#### 2.3 Overview of OFDM System

OFDM was proposed as a Single-Input and Single-Output (SISO) technique to boost the resilience over multipath frequency-selective fading. Each signal can be transmitted using one orthogonal subcarrier or more when the signal has a high rate and needs to be divided into many sub-channels. By applying the orthogonality theory for the transmitted subcarriers, OFDM modulation provides high bandwidth efficiency. In this section basic analysis for OFDM is discussed.

In the traditional multicarrier system, the transmitter consists of a set of modulators with different carrier frequencies. Assuming N complex symbols  $S_k$  are to be transmitted by OFDM modulation where k = 0, 1, 2, ..., N - 1, where N is the number of subcarriers. The OFDM signal can then be shown [20] as

$$S(t) = \sum_{K=0}^{N-1} S_k e^{j2\pi f_k t}, \text{ for } 0 \le t \le T_S$$

$$f_k = f_0 + k\Delta f$$

whereas  $\Delta f$  is the subchannel frequency space and  $T_S$  is symbol duration.

In OFDM the symbol duration must be  $T_S = \frac{1}{\Delta f}$  to fulfill the orthogonality condition and avoid any interference.

At the receiver side, the demodulated OFDM signal can be expressed as below

$$\frac{1}{T_s} \int_0^{T_s} s(t) e^{-j2\pi f_l t} dt = \frac{1}{T_s} \int_0^{T_s} \left( \sum_{k=0}^{N-1} S_k e^{j2\pi f_k t} \right) e^{-j2\pi f_l t} dt$$

$$= \frac{1}{T_s} \int_0^{T_s} (\sum_{K=0}^{N-1} S_k) e^{j2\pi (f_k - f_l)t} dt$$

$$= (\sum_{K=0}^{N-1} S_k) \frac{1}{T_s} \int_0^{T_s} e^{j2\pi (k-l)\Delta ft} dt$$

Since the subcarriers are orthogonal, we can derive the following equation:

$$\frac{1}{T_s} \int_0^{T_s} s(t) e^{-j2\pi f_l t} dt = (\sum_{k=0}^{N-1} S_k) \,\delta(k-l)$$

where  $\delta(k-l) = \frac{1}{T_s} \int_0^{T_s} e^{j2\pi(k-l)\Delta ft} dt = \begin{cases} 1 & when \ k = l \\ 0 & otherwise \end{cases}$

$$\frac{1}{T_s}\int_0^{T_s} s(t)e^{-j2\pi f_l t} dt = S_l$$

As the processes of the modern communication systems are often represented digitally these days, the OFDM signal can also be expressed digitally in a sampled-data style by substituting  $nT_h$  for t where  $T_h$  is the sampling interval [21].

$$S(nT_h) = \sum_{K=0}^{N-1} S_k e^{j2\pi f_k nT_h}$$

Assume  $f_k = kf_s$ , where  $f_s$  is the frequency spacing ( $\Delta f$ ) and OFDM is a digital baseband modulation.

$$S(nT_h) = \sum_{K=0}^{N-1} S_k e^{j2\pi k f_s nT_h}$$

Let  $T_h = \frac{T_S}{N}$  and  $f_S = \Delta f = \frac{1}{T_S}$  to satisfy the orthogonality condition.

$$S(nT_h) = \sum_{K=0}^{N-1} S_k e^{j2\pi kn/N} = S_n$$

The input signal  $S_{in}$  can be a real or complex symbol modulated by any digital modulation scheme such as Binary Phase Shift Keying (BPSK), Quadrature Phase Shift Keying (QPSK) or Quadrature Amplitude Modulation (QAM). The wideband input signal  $S_{in}$  is divided to N parallel narrowband data stream  $S_k$  by serious to parallel converter. In case of zero-padding  $S_{in}$  is broken into M number of data streams where M is less than or equal to N, the size of IFFT. The process of modulating these data streams to generate OFDM symbol is performed by using IFFT, which makes the implementation of OFDM systems inexpensive and simple. In fact, the FFT algorithm reduces the number of complex multiplications from  $N^2$  to  $\frac{N}{2} log_2 N$  for an Npoint DFT [2]. Since the spectrum of a square function is a sinc function, the frequency spectrum shape of the subcarriers is a *sinc* shape unless OFDM symbol is shaped or windowed to limit its bandwidth. As the amplitude of  $sinc(\pi fT_s)$  function is zero when f is equal to  $\frac{m}{T_c}$ and m is any integer number, any subcarrier has zero value wherever other subcarriers have the maximum amplitude, and therefore the subcarriers do not interfere with each other. To get no interference by satisfying the orthogonality property, the frequency space  $\Delta f$  between the subcarriers has to be equal to  $\frac{1}{T_s}$ . Otherwise, there will be intercarrier interference (ICI).

Figure 2-3: OFDM frequency spectrum

#### 2.3.1 Guard Interval and Cyclic Prefix

Since OFDM symbol is made of multi narrow-band signals that have long symbol, OFDM modulation is robust against multi-path delay spread when the delay is considered very small compared with the symbol duration. To make OFDM completely resistant to the multipath delay spread in radio channel, guard intervals can be inserted between long OFDM symbols with a length enough to be larger than the maximum delay spread. At the receiver side, these guard intervals which include the time-domain symbol interference will be removed, and the adjacent symbols will be interference-free.

However if zero signal is sent during the guard time, intercarrier interference (ICI) will occur and as a result the orthogonality property between the subcarriers can no longer be preserved. To solve this problem, the OFDM symbol is extended cyclically in the guard interval by replicating a part of OFDM symbol but it has to be an integer number of IFFT sampling time and larger than the maximum expected delay spread. In this case the transmitted OFDM signal will still be periodic as it is very significant to maintain the orthogonality.

The cyclic extension can be done by three different ways; cyclic prefix, suffix or timing advance. The common way is cyclic prefix since it is simple to implement and does not need to rotation processes at the receiver side as in the cyclic suffix. Adding guard intervals between OFDM symbols, however, reduces the spectral efficiency.

Figure 2-4: OFDM cyclic prefix

#### 2.3.2 Pulse Shaping

As OFDM signal consists of N number of unfiltered sinc-shaped subcarriers, the frequency spectrum of OFDM can be band-limited depending on the number of subcarriers. While the sinc-shaped subcarriers are orthogonal and overlapping each other, the spectrum of OFDM side-lobes decreases rapidly where it is close to the band. Therefore, the larger number of subcarriers is the more rapidly the spectrum decreases. Figure 2-5 shows the power spectrum density of QAM- OFDM signal with different number of subcarriers.

Figure 2-5: OFDM Power spectrum density for different N subcarriers

Moreover the length of the extended interval has an effect on the spectrum of an OFDM signal. The out of band spectrum also decreases more rapidly when the OFDM symbol is extended with a cyclic prefix [2]. If OFDM bandwidth has to be band-limited with specified boundaries, spectrum masks have to be applied for each channel before IFFT. This technique is called windowing, when the signals pass through rectangular filters to eliminate undesired sidelobes and limit the transmission spectrum. As a result, the spectrum of windowed OFDM symbol goes down to zero more rapidly at the boundaries depending on window type and specifications. The raised cosine window is commonly used and popular in wireless communications. Its form is defined as

$$W(t) = \begin{cases} 0.5 + 0.5 \cos\left(\pi + \frac{\pi(t + N_g T_s)}{\beta T_s}\right) & -N_g T_s \le t \le (-N_g T_s + \beta) \\ 1 & (-N_g + \beta) T_s \le t \le N_g T_s \\ 0.5 + 0.5 \cos\left(\frac{\pi(t - N T_s)}{\beta T_s}\right) & N T_s \le t \le (N + \beta) T_s \end{cases}$$

where  $N_g$  and N are the number of samples for guard interval and OFDM symbol respectively. The parameter  $\beta$  is the roll-off factor. Besides windowing, a conventional low-pass filter can be applied to the baseband OFDM signal to suppress the out of band sidelobes. Compared to lowpass digital filtering, the windowing technique is less complex to implement since fewer multiplications are needed in time domain rather than convolution in case of filtering technique.

#### 2.3.3 Peak to Average Power Ratio

Since OFDM signal is a summation of multiple sinusoidal signals, occasionally high amplitudes of the sinusoidal signals can be added concurrently when they form an OFDM signal. Consequently the amplitude of ODFM signal gets a very high level compared to the average amplitude level. As a result, the complexities of both Digital to Analog Convertors (DACs) and Analog to Digital Converters (ADCs) increase to deal with the high level of signal, and radio frequency efficiency decreases. As a matter of fact, when this OFDM signal with high amplitude passes a power amplifier in the transmitter side, nonlinear amplification occurs as the power amplifier. This OFDM problem of large peak is known as Peak to Average Power Ratio (PAPR) considered as a disadvantage of using OFDM modulation. PAPR can be defined by the formula shown below [21].

$$PAPR = \frac{\max[s(t)]^2}{E\{[s(t)]^2\}}$$

Many approaches have been proposed to reduce the PAPR, such as coding, signal distortion and scrambling techniques.

#### 2.4 Wireless Fading Channel

Using wireless communications technology has given many advantages over wire communication systems in term of mobility, simplicity of accessing and installation but it is still limited in some characteristics such as spectrum, capacity and reliability. There are many unpredictable factors that can affect a signal transmitted into a wireless radio channel. The channel variations and the user movement make the wireless radio channel time-varying and dynamic. The wireless radio fading channel can be classified under different categories such as small or large fading, flat or frequency selective fading and slow or fast fading. In this section the multipath fading channels will be discussed to show the advantages of using OFDM modulation.

#### 2.4.1 Small-Scale Fading Channel

In mobile radio channel, a signal is transmitted as an electromagnetic wave with radio frequency (RF) and is affected by different physical phenomena: reflection, diffraction and scattering. Therefore, the transmission signal takes two or more different paths to get to the receiver due to the wireless channel environment. When different versions of the transmission signals arrive at the receiver antenna, the received signal will be a combination of signals that have different delays and attenuations.

Figure 2-6: Multipath fading

The figure above is an example of multipath fading when the cell phone of the driver receives many versions of the transmission signal including the line-of-sight (LOS) propagation. Also there is some non line-of-sight (NLOS) propagation when the signal does not travel to the receiver in a straight line as it may be reflected, diffracted or refracted in the radio channel environment.

In multipath fading, the received signal is rapidly fluctuating in amplitude, phase and frequency [21]. The fading phenomenon can have two versions which are small-scale and large-scale fading [22]. In large-scale fading, the channel has a large scale of attenuation that occurs as path loss and shadowing, as it is the case with mobile station user moving in a large distance. The small-scale fading, on the other hand, occurs when different versions of the transmission signal arrives at the receiver with a slight difference in time. In other words, the channel rapid

variation will be in a small region when the movement of the mobile station is in a small distance.

Due to the destructive and constructive interference of multipath, the received signal rapidly varies in strength, delay and frequency. Receiving many versions of the transmission signal at different times causes a variation of the amplitude and phase of the received signal, which is a combination of the multipath waves. The random change in frequency is caused by the variation of Doppler shifts on different multipath signals. Small-scale fading is influenced by many physical factors such as the speed of mobile station, transmission bandwidth of the signal, multipath propagation and speed of surrounding objects [19]. The most significant small-scale fading effects in radio channel can be characterized by two sorts of dispersions that are frequency dispersion and time dispersion [21].

#### **2.4.2 Frequency Dispersion**

In wireless communication systems if one of the receivers, transmitters or the scatters moves around during the communication, Doppler spread will occur in the received signal due to the frequency dispersion. In other words, the receiver signal will have shifted spectrum and that frequency shift depends on the speed of the moving stations and the angle between the directions of the movement and signal reception. Figure 2-7 illustrates the frequency dispersion between two stations.

Figure 2-7: Doppler effect on a mobile station

Assuming that a car is moving towards the transmitter antenna with a constant speed of V as depicted in the figure, the frequency change in the received signal is defined as

$$f_d = \frac{v \cos(\theta)}{\lambda}$$

where  $f_d$  is Doppler frequency shift and  $\lambda$  is the wavelength of the carrier frequency [19]. In practice, several paths can be between the stations as in Figure 2-7. In this case, the Doppler spread will be limited between  $f_c - f_m$  and  $f_c + f_m$ , where  $f_m$  is the maximum Doppler frequency ( $f_m = V/\lambda$ ).

Time-varying small-scale fading channel can be defined either as slow or fast fading according to the coherence time, which is inversely proportional to maximum Doppler frequency [19]

$$T_c \approx \frac{0.423}{f_m}$$

where  $T_c$  is the coherence time of wireless channel. Basically coherence time is a time interval when the characteristics of fading channel remain unchanged. If the channel impulse response does not change significantly during the one or more symbol period  $T_s < T_c$ , the small-scale fading is considered slow.

#### **2.4.3 Time Dispersion**

When a signal is sent wirelessly, many version of that signal with different power arrive at the receiver at different times due to distinctive paths they take. The delay spread resulting from distinctive paths causes interference between symbols, which is known as intersymbol interference. The coherence bandwidth can be calculated by measuring the delay spread of wireless channel. In fact the root mean square of delay spread  $\Delta t_{rms}$  is inversely proportional to coherence bandwidth  $B_c$  [21].

$$B_c \alpha \frac{1}{\Delta t_{rms}}$$

According to the relationship between the coherence bandwidth and the delay spread, a wireless channel with large delay spread has a narrow coherence bandwidth. As a result a signal that has a wide bandwidth  $B_s$  wider than the coherence bandwidth  $B_c$  will endure frequency selective fading causing inter symbol interference, whereas a signal with bandwidth much smaller than the coherence bandwidth  $B_c$  will endure flat fading. In other words, the ratio between coherence bandwidth and signal bandwidth can imply if the signal tolerates flat or frequency-selective fading. Therefore radio channel can be under one of two categories: flat or frequency-selective fading. Figure 2-8 illustrates how dissimilar-band signals can endure different types of fading.

Figure 2-8: Flat and frequency-selective fading

In OFDM communication system, however, the transmitted signal experiences flat fading although the OFDM signal has a large bandwidth since it is broken into small narrow bands. For that reason, OFDM communication system has proved its robustness over frequency-selective fading channel.

# 2.4.4 Impulse Response of Fading Channel

In mobile radio channel, the transmission signal varies according to the impulse response of the time-variant channel, which can be modeled as a linear filter with a time varying impulse response. Actually modeling wireless channel is very useful to anticipate the performance of different mobile communication systems. In multipath channel, two or more multipath signals arrive with different amplitude, frequency and time. The channel impulse response can be expressed as

$$h(t, T) = \sum_{i=0}^{N-1} a_i(t) \exp(j\theta_i(t)) \, \delta(T - T_i)$$

where T is the time delay;  $\theta_i$  is the phase shift;  $\delta$  is the unit impulse function;  $a_i$  is the path gain; *i* is the path index; and N is the number of multi paths [19] [23]. Since the multipath channel works like a band-limited band-pass filter, the received signal will be equal to the transmission signal convolved with the impulse response of the channel as depicted in the equation below [24].

$$y(t) = \int_{-\infty}^{\infty} h(t, T) x(T-t) = h(t, T) * x(t)$$

In the small-scale fading, the channel impulse response can be time-invariant over certain time or area, and that simplifies the radio channel modeling. In digital wireless communications, the channel can be modeled as a linear finite impulse response filter. This type of modeling will be discussed in Chapter 3 when the channel is needed to be modeled to verify the performance for wireless communication systems.

#### **2.5 LTE Physical Layer Downlink Parameters**

Since our OFDM is based on the LTE downlink physical layer, some basic parameters have to be specified according to the 3GPP specifications. The initial LTE requirements were defined by 3GPP in a way that LTE physical layer should support data rate of 100Mbps and

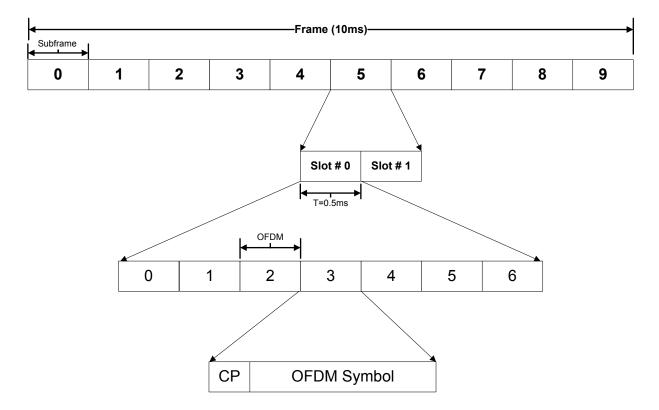

50Mbps for downlink and uplink, respectively. To fulfill these requirements, OFDM is employed as a modern technique for mobile communications. Due to the channel variation in time and frequency domains, the LTE interface supports Frequency Domain Duplexing (FDD) and Time Domain Duplexing (TDD). The LTE transmission is segmented into frames. Based on radio frame structure type1, each frame has a time duration of 10 ms, and it consists of 10 sub-frames [25] [26]. As depicted in Figure 2-9, a sub-frame consists of two slots with time duration of 0.5 ms.

Figure 2-9: Radio frame structure type 1

One slot is composed of seven or six OFDM symbols depending whether an extended or normal CP is used. These symbols have subcarriers ranging from 128 to 2048 determined by the transmission bandwidth.

As LTE supports a scalable transmission bandwidth, the number of subcarrier can be different according to the transmission bandwidth assuming the same subcarrier spacing of 15 kHz. In fact the LTE PHY specification is designed to have multiple transmission bandwidths from 1.4 MHz to 20 MHz [27]. Each bandwidth specifies the number of occupied subcarriers, which is related to FFT size. Different FFT sizes of 128 to 2048 are supported depending on the transmission bandwidths as demonstrated in Table 2-1 [28]. Two types of CP, normal and extended CPs are allowed in LTE specifications depending on the extensive delay spread of the environment.

| Transmission BW |          | 1.4 MHz | 3 MHz | 5 MHz | 10 MHz | 15 MHz | 20 MHz |

|-----------------|----------|---------|-------|-------|--------|--------|--------|

| DFT Size        |          | 128     | 256   | 512   | 1024   | 1536   | 2048   |

| No of CP        | Normal   | 9       | 18    | 36    | 72     | 108    | 144    |

| samples         | Extended | 32      | 64    | 128   | 256    | 384    | 512    |

Table 2-1: Typical parameters for downlink transmission

In case of 5 MHz bandwidth, the FFT size and sampling frequency could be 512 and 7.68MHz respectively for efficient implementation. The normal and extended CPs have lengths of 36 and 128 samples respectively. Based on the 5MHz-bandwith LTE specifications, our OFDM is modeled and implemented in the following chapters.

# 2.6 Summary

In this chapter, introduction of OFDM modulation was presented with its advantages compared with traditional FDM modulations. The concept of QPSK modulation was presented

with some background information. In fact, OFDM modulation and demodulation was explained theoretically with the equations of signal processes for IFFT and FFT. Cyclic prefix and pulse shaping were illustrated. Peak to Average Power Ratio (PAPR) was illuminated as a disadvantage of OFDM modulation. Wireless channel was analyzed in details including small-scale fading, impulse response, time dispersion and frequency dispersion. Finally the 3GGP LTE downlink PHY layer parameters were provided specifying our OFDM system parameters as the basis for further modeling and implementation. In the following chapters, the OFDM system based on the LTE parameters is modeled, simulated and implemented according to design flow methodology.

# **Chapter 3**

# **OFDM System Design and Simulation**

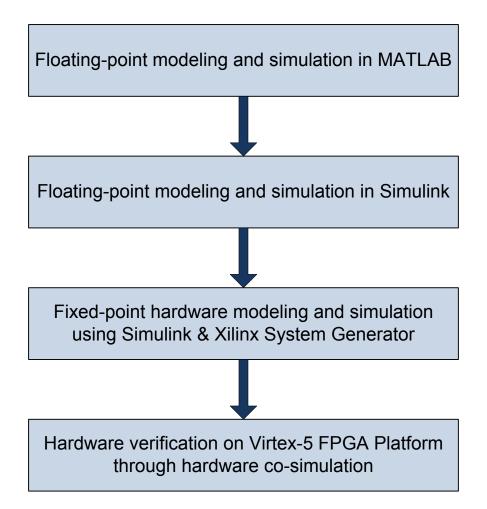

In order to design and implement an OFDM system, four stages are taken according to design flow illustrated in Figure 3-1. In each stage, the OFDM system is modeled and simulated to obtain simulation results that achieve high performance before going onto the next stage. In this chapter, the design flow of an OFDM system is proposed. The first two stages of the design flow, which are MATLAB and Simulink modeling and simulation, are discussed in this chapter.

# 3.1 Design Flow

As shown in Figure 3-1, the design flow of OFDM system is composed of four stages. The first stage is to model and simulate in MATLAB two OFDM systems that have different cyclic prefixes. Based on the mathematical basis of OFDM system expressed in Chapter two, two OFDM systems are modeled and simulated in MATLAB based on parameters for 3GPP LTE. Using floating-point representation, these two systems are verified under different wireless fading channels to show the difference between these OFDM systems.

Figure 3-1: Implementation design flow

To evaluate the performance of communication systems, the bit error rate versus bit energy to noise spectral density  $(E_b/N_0)$  is found using Monte Carlo simulation. By comparing the BER curve of simulation results for QPSK-OFDM systems with the theoretical QPSK BER curve, the performance of each OFDM system is evaluated and analyzed.

In the second stage, the OFDM system with extended cyclic prefix is modeled based on LTE downlink parameters and simulated in the Simulink environment. Unlike MATLAB, many parameters in Simulink environment such as the sampling period have to be determined. As OFDM model has different sampling rates, OFDM model-based design is divided into multi-rate subsystems. In fact, Simulink is a graphical extension to MATLAB for the modeling and simulation of multi-rate system with different simulation time steps. Using the Simulink communication library, the OFDM system is modeled based on the model in MATLAB. Each Simulink block represents a mathematical formulation that has already been implemented in MATLAB. The model-based design is simulated using floating-point representation. In order to draw the BER curve of the OFDM design, the input and output data of the Simulink is stored in MATLAB workspace for analyzing and visualization. This Simulink OFDM model is considered the basis for Xilinx based implementation by replacing the Simulink blocks with Xilinx blocks. However, some Simulink blocks such as data source and sinks are still required for hardware co-simulation.

Designing an OFDM system using Xilinx blocks is the third stage of the design flow. In this stage the float-point Simulink blocks are replaced by fixed-point Xilinx blocks if possible. Some Xilinx subsystems are designed to have the same functionality of the Simulink blocks. Using fixed-point representation leads to a compromise between the system performance and the size of Xilinx OFDM design since the number of assigned bits in fixed-point representation affects the system performance. The larger number of assigned bits, the more complex hardware design. The number of assigned bits is chosen to make the size of hardware design suitable for Xilinx Virtex-5 FPGA implementation with high performance.

The final stage of the design flow is to verify the Xilinx-based design in actual hardware. First, the design is compiled to a hardware co-simulation block using Xilinx system generator that coverts Xilinx designs into bit streams ready to be downloaded on an FPGA. The hardware co-simulation block is then tested in Simulink environment although the design is actually running on Xilinx Virtex-5 FPGA. In other words, the hardware design is incorporated in Simulink design. As result, the Xilinx OFDM design is tested and verified on Xilinx Virtex-5 FPGA through hardware co-simulation. Evaluating the system performance is done by comparing the BER of hardware co-simulation and theoretical QPSK modulation under frequency-selective fading.

#### **3.2 Floating-Point Modeling and Simulation in MATLAB**

In order to perform tasks in digital communications and digital signal processing, MATLAB software has been efficiently used for simulation, testing and evaluation of the system performance. OFDM system design has to be tested before it can be implemented to avoid any design error. Therefore, our OFDM system is modeled and simulated in MATLAB and Simulink, before the VHDL code is generated and downloaded to ML506 Virtex-5 board for implementation. For better understanding of signal modulation processes, each stage in OFDM modulation is described and elaborated in this chapter. Since the receiver performs the inverse processes of the transmitter, only the transmitter blocks are detailed.

The LTE downlink transmission scheme is based on OFDM modulation. To model an OFDM system based on 3GPP LTE parameters, the OFDM specifications have to be defined according to the transmission bandwidth. Using the LTE 5MHz-bandwidth downlink parameters, two OFDM systems with normal and extended CP are modeled in MATLAB with fixed-point representation. As explicated in Table 2-1, the IFFT size of 5 MHz transmission bandwidth is 512 which represent the number of OFDM subcarriers. The normal and extended CP samples are 36 and 128 samples respectively.

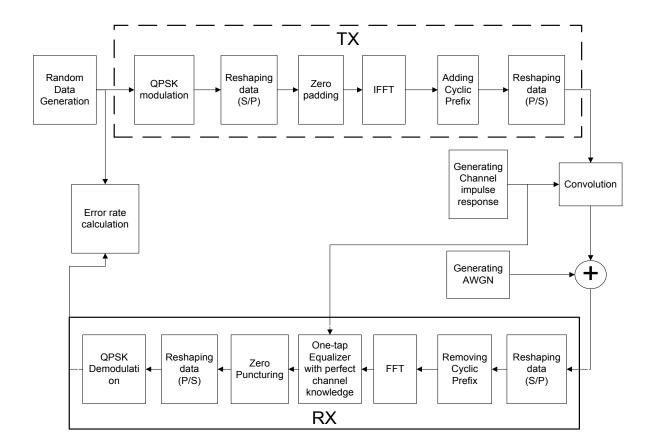

Figure 3-2: Block diagram of an OFDM transceiver

# 3.2.1 Random Data Generation

In the first stage an m-by-n digital random data matrix is generated with the condition that it has to have only scalar values of either 0 or 1 with the same probability in order to be similar to the original digital signal in digital communication. To determine the size of the matrix, many factors have to be considered such as number of OFDM symbols, FFT size, number of zeros padded and modulation technique. A large size of input matrix can cause the computer to run out of memory, depending on the RAM of the computer. In our design, FFT has a size of 512, the number of OFDM symbols is 10<sup>5</sup> and QPSK modulation is used. Assuming 256 zeros are padded in one OFDM symbol, the number of bits per OFDM symbol is represented as (512-256)\*k = 512, where k =2 is the modulation index for QPSK. As a result, the size of the random matrix is defined as

$$M * N = N_{OFDM \ sym.} * (FFT \ size - N_{Zeros \ per \ sym}) * K$$

For simplicity, *N* number of columns is assumed to be 1, so *M*, number of rows is  $6*10^7$ . Actually, this determination of the random matrix size is to ensure that the number of QPSK symbols after zero padding can be reshaped to be a multiple number of FFT size with no remains. However, the number of OFDM symbol per matrix can be as small integer value as one, but many matrices have to be generated to reach the number of OFDM symbols required to draw BER curve. Assuming the original message  $b_n$  where n is from 1 to M, the original data matrix is represented as

$$b_n = \{b_1 \ b_2 \ b_3 \ b_4 \ \dots \ b_N\}^T$$

where  $b \in \{0, 1\}$ .

#### **3.2.2 QPSK Modulation**

The data to be sent on each carrier is mapped into a QPSK format before it is modulated by OFDM. Every two serial bits of the original digital data are mapped onto a corresponding QPSK symbol that is different in phase angles 0, 90, 180 or 270. Each two bit group is encoded to In-phase or Quadrature axis. Therefore, each QPSK symbol can be represented as a complex number  $S_I+j S_Q$  where  $S_I, S_Q \in \{-1, 0, 1\}$  if the constellation in Figure 2-2 is used for mapping. The constellation with zero phase-offset is used in our implementation. According to phase shift keying modulation, the amplitude of PSK symbols is constant, so QPSK symbols have the same energy, although they have different phases. The original data matrix is modulated into a matrix of complex numbers as QPSK symbols and the size is equal to the half size of the original matrix. The modulated data matrix *S* is depicted as

$$S = \{ S_{1,I} + j S_{1,Q}, S_{2,I} + j S_{2,Q}, S_{3,I} + j S_{3,Q}, \dots \dots S_{\frac{N}{2},I} + j S_{\frac{N}{2},Q} \}^{T}$$

where  $S_I + j S_Q$  is a QPSK symbol represented in a complex number.

# 3.2.3 Serial to Parallel Conversion

In this section the serial data is converted to parallel data. The modulated matrix S, as the input matrix, is reshaped to be a matrix that has 256 columns. In this case, each row of 256 QPSK symbols is considered to be parallel data. These 256 QPSK symbols are grouped to be modulated to create an OFDM symbol. Actually the purpose of reshaping is to form the S matrix to be ready for OFDM modulation using IFFT. The new form of modulated matrix can be expressed as

# 3.2.4 Zero Padding

For better performance, the frequency spacing between the subcarriers in OFDM frequency domain can be decreased when the sampling rate increases. To increase the sampling rate, oversampling is used by appending zeros to the end of the original data sequence. As zeros are padded in a signal, the number of samples in time domain increases which also increases the size of FFT. As a result of extending FFT samples, OFDM symbol will have a higher resolution needed for digital signal processing such as digital to analog and analog to digital conversions. Oversampling process has to follow the Nyquist sampling theorem to avoid aliasing problem that may happen in frequency domain. Therefore the Nyquist rate has to be at least twice the highest frequency in the sampled signal [29]. As the number of samples for FFT is 256, the number of zeros appended has to be at least 256 to meet the Nyquist theorem. To ensure that non-zero data are mapped onto subcarriers close to zero frequency and zero data are mapped onto the high positive/negative-frequency subcarriers, these zeros should be padded in the middle of each parallel IFFT data input.

The oversampled matrix D can be illustrated as

$$\begin{pmatrix} S_{1,I}+j S_{1,Q}, \dots, \dots, S_{128,I}+j S_{128,Q}, 0, 0, \dots, \dots, 0, 0, S_{129,I}+j S_{129,Q}, \dots, S_{256,I}+j S_{256,Q} \\ S_{257,I}+j S_{257,Q}, \dots, S_{384,I}+j S_{384,Q}, 0, 0, \dots, \dots, 0, 0, S_{385,I}+j S_{385,Q}, \dots, S_{512,I}+j S_{512,Q} \\ \vdots \\ \vdots \\ S_{(\frac{N}{2}-254),I}+j S_{(\frac{N}{2}-254),Q}, \dots, S_{(\frac{N}{2}-128),I}+j S_{(\frac{N}{2}-128),Q}, 0, 0, \dots, 0, 0, S_{(\frac{N}{2}-127),I}+j S_{(\frac{N}{2}-127),Q}, \dots, S_{\frac{N}{2},I}+j S_{\frac{N}{2},Q} \end{pmatrix}$$

#### **3.2.5 Inverse Discrete Fourier Transformer**

To generate multiple orthogonal subcarrier signals overlapped in spectrum, Discrete Fourier Transformer (DFT) and Inverse Discrete Fourier Transformer (IDFT) processes should be used. In MATLAB, FFT and IFFT have been used to implement DFT and IDFT processes. In fact, the FFT function in MATLAB uses several algorithms in combination including Cooley-Tukey [30], splid-radix [31] and prime factor algorithms [32]. To use decimation-in-time, the number of IFFT points N has to be an integer of power 2, and that is why the modulated matrix is reshaped to have 256 columns and then zero padded to have 512 columns which meets the requirement of decimation-in-time algorithms. As result the transpose of IFFT output matrix is represented as matrix X shown below.

$$X = \begin{cases} X_{1,l} + j X_{1,Q} , & X_{2,l} + j X_{2,Q} , \dots \dots & X_{512,l} + j X_{512,Q} \\ X_{513,l} + j S_{513,Q} , & X_{513,l} + j X_{513,Q} , \dots \dots & X_{1024,l} + j X_{1024,Q} \\ \vdots & \vdots & \ddots & \\ \vdots & \vdots & \vdots & \vdots \\ X_{\binom{N}{2} - 511),l} + j X_{\binom{N}{2} - 511),Q} , & X_{\binom{N}{2} - 510),l} + j X_{\binom{N}{2} - 510),Q} , \dots \dots & X_{\frac{N}{2},l} + j X_{\frac{N}{2},Q} \end{cases} \end{cases}$$

Each row of X matrix is representing OFDM symbol, which is periodic with a period of 512 samples.

# **3.2.6 Adding Cyclic Prefix**

In this stage OFDM symbol is cyclically extended to eliminate ISI between consecutive symbols. The process of prefixing an OFDM symbol by repeating the end of OFDM is known as cyclic prefix. In order to make the OFDM system robust to multipath fading, the cyclic prefix should be larger than the maximum delay spread. Using the OFDM modulation parameters for 3<sup>rd</sup> Generation Partnership Project Long term Evolution (3GPP LTE), two cyclic prefix lengths

are used to compare the system performance over different multipath fading channels [28]. The normal CP added to OFDM symbol is 36 samples, while the extended CP is 128 samples. In fact an extended CP is more suitable, when the environment has very extensive delay spread. As two different CPs are deployed, two OFDM symbol matrices  $X_{Long.CP}$  and  $X_{Short.CP}$  represent different OFDM modulation designs as depicted

# **3.3 Channel Modeling**

Many types of wireless channels can be modeled using MATLAB depending on the channel specifications. To show the main advantage of OFDM modulation, small-scale fading channel should be modeled and implemented in our OFDM design. As explained in the previous chapter, fading channel can be specified according to the channel characteristics and the transmission scheme. Doppler spread and multipath delay spread are the main parameters used to

define wireless channel. Also depending on the signal parameters, the wireless channel can vary for signals that have different parameters such as bandwidth and symbol period [22]. For instance, the same wireless channel can be frequency-selective fading for a signal that has a wide bandwidth, and it can be frequency-non-selective fading for a signal that has a narrow bandwidth. To facilitate generating fading channel, wireless environments can be either LOS or NLOS, which are considered to follow Racian and Rayleigh distributions respectively. In NLOS environment, the fading can be represented as a complex Gaussian random variable  $G_1+jG_2$ where  $G_1$  and  $G_2$  are identically-distributed independent Gaussian random variables with a zero mean and variance of  $\sigma^2$ . Assuming **Z** Rayleigh random variable is the amplitude of the complex random variables, the probability density function of Z is represented as

$$f(Z) = \frac{Z}{\sigma^2} e^{\frac{Z^2}{2\sigma^2}}$$

Where  $Z = \sqrt{G_1^2 + G_2^2}$  and  $\sigma^2$  is the variance of  $G_1$  and  $G_2$ .

To generate the Rayleigh random variable Z using MATLAB, two Gaussian random variables with zero mean and unit variance,  $U_1$  and  $U_2$ , are generated using built-in MATLAB function.

$$Z = \sigma \cdot \sqrt{U_1^2 + U_2^2}$$

The average power of the Rayleigh random variable is  $E[Z^2] = 2\sigma^2$ . As the transmitted signal has zero-dB power, the fading variable has to have the same average power of the transmitted signal. Therefore, the Rayleigh random variable generated by MATLAB is divided by  $\sqrt{2}$ .

In LOS environment, a constant is added to complex Gaussian random variables to represent a strong direct path between the transmitter and the receiver  $Z = c + G_1 + jG_2$ .

The QPSK-OFDM design has single input and single output, and the channel model is also Single- Input Single-Output (SISO). Assuming low mobility in a small coverage area, the fading channel used in the design is modeled to be an indoor channel that can be static or quasistatic. The characteristics of static channel do not change during the data transmission at given time and location, while the characteristics of quasi-static channel change during the symbol duration.

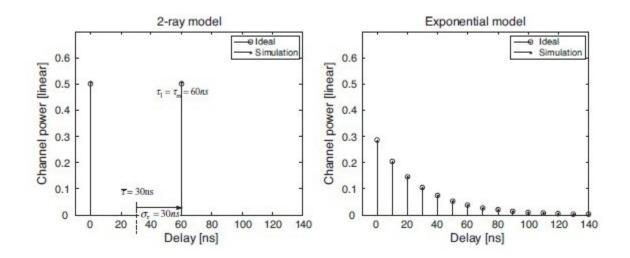

To implement multipath fading channel, some aspects are important to define the channel model such as number of paths, type of propagation, maximum Doppler shift, time delay and path gain. As an indoor channel is used in the QPSK-OFDM design, the two popular indoor, 2-ray model and exponential model are discussed below.

One approach to model the wireless channel is Two-ray model. In this model, two rays with the same power are used to represent the channel paths; one path with zero delay and other path with the maximum excess delay  $\tau_m$ . The maximum excess delay is twice the mean excess delay  $\bar{\tau}$ . Since there are only two paths and one of them has zero delay, the mean excess delay is equal to the root mean square (RMS) delay  $\tau_{RMS}$ . As the first path has always constant power and zero delay, the parameters of the second path determine the channel characteristics. In practice the second path has less power than the first path but in 2-ray model both paths have the same power for simplicity. Therefore, when accuracy is needed, 2-ray model might not be a good choice for channel modeling [22].

Another method for modeling the wireless channel is exponential model. In the exponential model, there are more than two paths that have different powers decreasing exponentially with the channel delay. This type of model is highly likely used to represent an indoor channel since the average channel power decreases rapidly as the delay increases. The power delay profile (PDP) for the exponential model is expressed as

$$P(\tau) = \frac{e^{-\tau/\tau_{RMS}}}{\tau_{RMS}}$$

As a discrete-time model is required in MATLAB, the PDP of exponential model that depends on the delay can be represented with sampling time  $T_s$  as

$$p(n) = P(0)e^{-nT_s/\tau_{RMS}}$$

,  $n = 0, 1, 2, ..., n_{max}$ .

where *n* is the discrete time index,  $n_{max} = \tau_m/T_s$  is the last path index and  $P(0) = 1/(total Power * \tau_{RMS})$  is the first path power.

Figure 3-3: Exponential and 2-ray models

As the exponential model is more accurate than 2-ray model, the wireless fading channel is modeled using the exponential model. Many wireless fading channels that have different delays are modeled to evaluate the robustness of the two OFDM systems, extended-CP and normal-CP OFDMs, against frequency-selective fading. While the delay spread determines the PDP, the maximum excess delay and the sampling time define the number of paths for each channel. In other words, the channel characteristics for exponential model depend on sampling period, RMS and maximum excess delays.

To implement Wireless channel using MATLAB, time-variant channel impulse response h(t) is generated according to the delay spread and sampling period. However, we assume that the fading is slow, so channel remains invariant with no change during the period of OFDM symbol. That means that the coherent time of the wireless channel is smaller than the symbol period.

Firstly a 1-by-  $n_{max}$  matrix of complex Gaussian random values with zero mean, unit variance and normalized power is generated to create Rayleigh random values Z(n). Those values are then multiplied by the PDF values,  $P(0), P(1), ...P(n_{max})$  to create the impulse response h(n) of the particular channel. However this procedure is repeated for each OFDM symbol to ensure channel variation in the time domain.

$$Z = \begin{bmatrix} Z_0, Z_1, Z_2, \dots, Z_{n_{max}} \end{bmatrix}$$

$$h = [Z_0, P_0, P_1Z_1, P_2Z_2, \dots, P_{n_{max}}, Z_{n_{max}}] = [h_0, h_1, h_2, \dots, h_{n_{max}}]$$

When a channel model has n taps, it does not mean that the channel has n paths. What it means is that channel impulse response has non-negligible values at the sampling time kTs (k =  $(0,1, \dots n)$ . There may be two or more propagation paths with different delays in a wireless channel that can be modeled as an *n*-tap discrete-time model.

Secondly each OFDM symbol is convolved with each channel impulse response *h* generated as if the wireless channel works as a filter for the transmission signal, except that the channel impulse response varies for every OFDM symbol. Since there are two OFDM systems, extended-CP and normal-CP, the same channel is applied on both OFDM systems.

The final part of modeling is adding Additive White Gaussian Noise (AWGN) to the convolved signal. To do so, two matrices  $N_L$  and  $N_S$  of AWGN with the same size of matrices  $X_{Long.CP}$  and  $X_{Short.CP}$  respectively are generated in MATLAB to be added to the two matrices of convolved OFDM symbols as following

$$Y_{Short.CP} = X_{Short.CP} * h + N_S$$

$$Y_{Long.CP} = X_{Long.CP} * h + N_L$$

Since the transmission signal is complex, the AWGN is complex with power level that depends on the signal to noise ratio for OFDM symbol SNR. However, SNR can be determined from the ration of QPSK symbol energy to noise power spectral density  $E_s/N_o$

$$E_s/N_o(dB) = E_b/N_o(dB) + 10 Log_{10}(k)$$

where  $E_b/N_o$  is the bit energy to noise power spectral density and k is the number of information bits per symbol. If  $T_{OFDM-sym}$  is the OFDM symbol period and  $T_{sample}$  is the sampling period,

$$T_{OFDM-sym} = 512 * T_{sample} = 512 * T_{QPSK-sym}$$

However, zero-padding has an effect on OFDM symbol power since the OFDM symbol will be consisting of QPSK symbols and zeros. Therefore, the OFDM symbol power will be less if there is no zero-padding. In other words, zero-padding has to be under consideration to define the AWGN channel noise level to specify the variance added per symbol.

Adding cyclic prefix to the OFDM symbol does not have an effect on the AWGN channel level since the OFDM symbol extension is a part of OFDM symbol. On the other hand, the number of information bits per symbol *K* is influenced by the code rate if channel coding is used in the communication system.

#### **3.4 MATLAB Simulation Results**