# Cryptanalysis and Secure Implementation of Modern Cryptographic Algorithms

### Abdel Alim K. Farag

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

July 2012

© Abdel Alim K. Farag, 2012

### **CONCORDIA UNIVERSITY**

### SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

| Ву:              | Abdel Alim K. Farag                                 |                                              |

|------------------|-----------------------------------------------------|----------------------------------------------|

| Entitled:        | Cryptanalysis and Secure<br>Cryptographic Algorithm | Implementation of Modern<br>s                |

| and submit       | ted in partial fulfillment of the r                 | requirements for the degree of               |

| ]                | DOCTOR OF PHILOSOPHY (E                             | lectrical & Computer Engineering)            |

| _                | ith the regulations of the Univer                   | rsity and meets the accepted standards with  |

| Signed by tl     | he final examining committee:                       |                                              |

|                  |                                                     | Chair                                        |

|                  | Dr. D. Dysart-Gale                                  |                                              |

|                  | Dr. H. Wu                                           | External Examiner                            |

|                  | Dr. K. Galal                                        | External to Program                          |

|                  | Dr. K. Galai                                        |                                              |

|                  | Dr. O. Ait Mohamed                                  | Examiner                                     |

|                  | - W.W                                               | Examiner                                     |

|                  | Dr. M. Mannan                                       |                                              |

|                  | Dr. A. Youssef                                      | Thesis Supervisor                            |

|                  |                                                     |                                              |

| Approved b       | у                                                   |                                              |

|                  | Dr. John X. Zhang, G                                | raduate Program Director                     |

| September (      | 5 2012                                              |                                              |

| ~ 3p *********** | Dr. Robin A.I                                       | L. Drew, Dean gineering and Computer Science |

# **Abstract**

# Cryptanalysis and Secure Implementation of Modern Cryptographic Algorithms

Abdel Alim K. Farag, PhD Concordia University, 2012

Cryptanalytic attacks can be divided into two classes: pure mathematical attacks and Side Channel Attacks (SCAs). Pure mathematical attacks are traditional cryptanalytic techniques that rely on known or chosen input-output pairs of the cryptographic function and exploit the inner structure of the cipher to reveal the secret key information. On the other hand, in SCAs, it is assumed that attackers have some access to the cryptographic device and can gain some information from its physical implementation.

Cold-boot attack is a SCA which exploits the data remanence property of Random Access Memory (RAM) to retrieve its content which remains readable shortly after its power has been removed. Fault analysis is another example of SCAs in which the attacker is assumed to be able to induce faults in the cryptographic device and observe the faulty output. Then, by careful inspection of faulty outputs, the attacker recovers the secret information, such as secret inner state or secret key. Scan-based Design-For-Test (DFT) is a widely deployed technique for testing hardware chips. Scan-based SCAs exploit the information obtained by analyzing the scanned data in order to retrieve secret information from cryptographic hardware devices that are designed with this testability feature.

In the first part of this work, we investigate the use of an off-the-shelf SAT solver, CryptoMinSat, to improve the key recovery of the Advance Encryption Standard (AES-128) key schedules from its corresponding decayed memory images which can be obtained using cold-boot attacks.

We also present a fault analysis on both NTRUEncrypt and NTRUSign cryptosystems. For this specific original instantiation of the NTRU encryption system with parameters (N,p,q), our attack succeeds with probability  $\approx 1 - \frac{1}{p}$  and when the number of faulted coefficients is upper bounded by t, it requires  $O((pN)^t)$  polynomial inversions in  $\mathbb{Z}/p\mathbb{Z}[x]/(x^N-1)$ . We also investigate several techniques to strengthen hardware implementations of NTRUEncrypt against this class of attacks. For NTRUSign with parameters  $(N,q=p^l,\mathcal{B},standard,\mathcal{N})$ , when the attacker is able to skip the norm-bound signature checking step, our attack needs one fault to succeed with probability  $\approx 1 - \frac{1}{p}$  and requires  $O((qN)^t)$  steps when the number of faulted polynomial coefficients is upper bounded by t. The attack is also applicable to NTRUSign utilizing the transpose NTRU lattice but it requires double the number of fault injections. Different countermeasures against the proposed attack are also investigated.

Furthermore, we present a scan-based SCA on NTRUEncrypt hardware implementations that employ scan-based DFT techniques. Our attack determines the scan chain structure of the polynomial multiplication circuits used in the decryption algorithm which allows the cryptanalyst to efficiently retrieve the secret key.

Several key agreement schemes based on matrices were recently proposed. For example, Álvarez *et al.* proposed a scheme in which the secret key is obtained by multiplying powers of block upper triangular matrices whose elements are defined over  $\mathbb{Z}_p$ . Climent *et al.* identified the elements of the endomorphisms ring  $End(\mathbb{Z}_p \times \mathbb{Z}_{p^2})$  with elements in a set,  $E_p$ , of matrices of size  $2 \times 2$ , whose elements in the first row belong to  $\mathbb{Z}_p$  and the elements in the second row belong to  $\mathbb{Z}_{p^2}$ . Keith Salvin presented a key exchange protocol using matrices in the general linear group,  $GL(r,\mathbb{Z}_n)$ , where n is the product of two distinct large primes. The system is fully specified in the US patent number 7346162 issued in 2008. In the second part of this work, we present mathematical cryptanalytic attacks against these three schemes and show that they can be easily broken for all practical choices of their security parameters.

# Acknowledgments

I would like to thank my supervisor, Dr. Amr Youssef, for his patient guidance, and encouragement. I have been extremely lucky to have a supervisor who cared so much about me and my work, and who responded to my questions and queries so promptly.

I also would like to express my deepest gratitude for the constant support, understanding and love that I received from my mother, my father, my wife, and my family during the past years. Completing this work would have been all the more difficult were it not for the support and friendship provided by my colleagues in the Crypto Lab at CIISE. I am indebted to them for their help. I also would like to thank Tadeusz Obuchowicz for his help and support in the area of hardware implementations using VHDL.

Finally, I am very grateful for the financial support of the Mission Sector in the Egyptian Ministry of Higher Education.

ABDEL ALIM K. FARAG

# **Table of Contents**

| List of l | Figures       |                                       | xi  |

|-----------|---------------|---------------------------------------|-----|

| List of   | ist of Tables |                                       |     |

| List of A | Acronyı       | ns                                    | xv  |

| Chapte    | r 1 Int       | troduction                            | 1   |

| 1.1       | Motiva        | ation                                 | 1   |

| 1.2       | Thesis        | contributions                         | 3   |

| 1.3       | Outlin        | e of the thesis                       | 5   |

| Chapte    | r 2 Ba        | ckground and Literature Review        | 7   |

| 2.1       | Introd        | uction                                | 7   |

| 2.2       | Classi        | fications of side channel attacks     | 8   |

|           | 2.2.1         | Controls over the computation process | 8   |

|           | 2.2.2         | Ways of accessing the module          | 9   |

|           | 2.2.3         | Methods used in the analysis process  | 10  |

| 2.3       | Examp         | bles of side channel attacks          | 10  |

|           | 2.3.1         | Timing attack                         | 10  |

|           | 2.3.2         | Fault attacks                         | 12  |

|           | 2.3.3         | Power analysis attacks                | 13  |

|           | 2.3.4         | Electromagnetic attacks               | 13  |

|           | 2.3.5         | Cold-boot attacks                     | 14  |

|           | 226           | Coon board attacks                    | 1.5 |

|        | 2.3.7              | Acoustic attacks                                                 | 15 |

|--------|--------------------|------------------------------------------------------------------|----|

| 2.4    | Count              | ermeasures against side channel attacks                          | 15 |

|        | 2.4.1              | Preventing timing attacks                                        | 16 |

|        | 2.4.2              | Preventing power analysis attacks                                | 17 |

|        | 2.4.3              | Preventing fault attacks                                         | 17 |

|        | 2.4.4              | Preventing cold-boot attacks                                     | 18 |

| 2.5    | The SA             | AT problem                                                       | 18 |

| Chapte | r 3 A <sub>l</sub> | oplications of SAT Solvers to AES Key Recovery from Decayed Key  | 7  |

| Sch    | edule In           | nages                                                            | 20 |

| 3.1    | Introd             | uction                                                           | 20 |

| 3.2    | The Sa             | AT problem and its applications to cryptanalysis                 | 22 |

| 3.3    | Structu            | ure of the AES-128 key schedule                                  | 23 |

| 3.4    | Formu              | lating the AES key schedule as a SAT problem                     | 25 |

| 3.5    | Experi             | mental results                                                   | 27 |

| 3.6    | Conclu             | asion                                                            | 30 |

| Chapte | r 4 Fa             | ult Attacks Against the NTRU Cryptosystems and their Countermea- | -  |

| sure   | es                 |                                                                  | 31 |

| 4.1    | Introd             | uction                                                           | 31 |

| 4.2    | Fault a            | analysis of NTRUEncrypt cryptosystem                             | 34 |

|        | 4.2.1              | Description of the NTRUEncrypt encryption algorithm              | 34 |

|        | 4.2.2              | Proposed attack                                                  | 37 |

|        | 4.2.3              | Complexity and success probability of the proposed attack        | 38 |

|        | 4.2.4              | Proposed countermeasures                                         | 39 |

|        | 4.2.5              | FPGA implementation results                                      | 48 |

| 4.3    | Fault a            | analysis of NTRUSign digital signature scheme                    | 52 |

|        | 4.3.1              | Description of NTRUSign                                          | 52 |

|        | 4.3.2              | Proposed attack                                                  | 53 |

|        | 4.3.3              | Proposed countermeasures                                         | 60 |

| 4.4    | Conclu             | usion                                                            | 64 |

| Chapter | 5 Ap             | plication of Scan-based SCAs on NTRUEncrypt Cryptosystems          | 66    |

|---------|------------------|--------------------------------------------------------------------|-------|

| 5.1     | Introdu          | ection                                                             | . 66  |

| 5.2     | Hardw            | are implementation options for NTRUEncrypt                         | . 68  |

| 5.3     | The pro          | oposed scan-based attack                                           | . 72  |

|         | 5.3.1            | Summary of the attack                                              | . 73  |

|         | 5.3.2            | Recovering the secret key                                          | . 74  |

| 5.4     | Experi           | mental Results                                                     | . 83  |

| 5.5     | Conclu           | sion                                                               | . 85  |

| Chapter | 6 Cr             | yptanalysis of Key Exchange Schemes Based on Matrix Algebra        | 87    |

| 6.1     | Introdu          | action                                                             | . 87  |

| 6.2     | Crypta           | nalysis of Álvarez et al. key exchange scheme                      | . 88  |

|         | 6.2.1            | Description of the Álvarez et al. key exchange scheme              | . 89  |

|         | 6.2.2            | The proposed attack                                                | . 91  |

| 6.3     | Crypta           | nalysis of a key exchange protocol based on the endomorphisms ring |       |

|         | $End(\mathbb{Z}$ | $\mathbb{Z}_p	imes\mathbb{Z}_{p^2})$                               | . 96  |

|         | 6.3.1            | Description of Climent et al. key exchange scheme                  | . 97  |

|         | 6.3.2            | The proposed attack                                                | . 98  |

| 6.4     | Crypta           | nalysis of a $GL(r, \mathbb{Z}_n)$ -based Public Key System        | . 103 |

|         | 6.4.1            | Description of Salvin's key exchange scheme                        | . 103 |

|         | 6.4.2            | The proposed attack                                                | . 105 |

| 6.5     | Conclu           | sion                                                               | . 110 |

| Chapter | 7 Co             | nclusions and Future Research Directions                           | 112   |

| 7.1     | Summa            | ary and Conclusions                                                | . 112 |

| 7.2     | Future           | works                                                              | . 113 |

| Appendi | ix A A           | n FPGA Implementation of the NTRUEncrypt Cryptosystem              | 115   |

| A.1     | Hardw            | are implementation of the NTRUEncrypt cryptosystem                 | . 115 |

| Appendi | ix B E           | nhanced Implementation of the NTRUEncrypt Algorithm Using Graj     | ph-   |

| ics C   | ards             |                                                                    | 123   |

| Bibliography |     | 135                                        |     |

|--------------|-----|--------------------------------------------|-----|

| I            | 3.3 | Implementation options for the NTRUEncrypt | 128 |

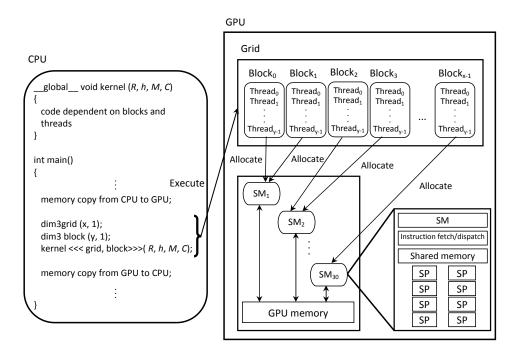

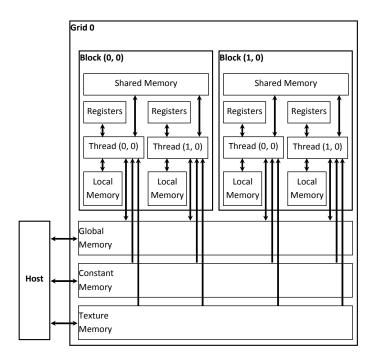

|              |     | B.2.1 Thread organization and memory model | 125 |

| I            | 3.2 | The CUDA framework                         | 125 |

| I            | 3.1 | Introduction                               | 123 |

# **List of Figures**

| 2.1 | The cryptographic model including examples for side-channels                           | 8  |

|-----|----------------------------------------------------------------------------------------|----|

| 3.1 | The key schedule of the AES-128                                                        | 24 |

| 3.2 | Algebraic normal form of the first coordinate function of the AES s-box                | 25 |

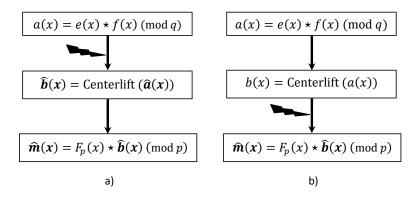

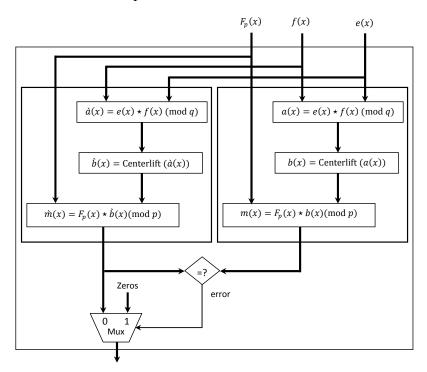

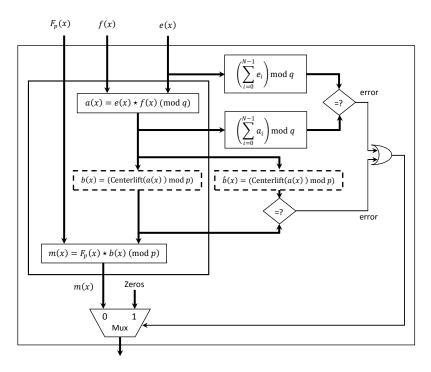

| 4.1 | The decryption process after inducing faults: a) before the centerlift operation       |    |

|     | or b) after the centerlift operation                                                   | 37 |

| 4.2 | Detecting errors using the duplication method (decryption followed by decryp-          |    |

|     | tion). When temporal redundancy is used, $\grave{a}(x)$ is calculated at the same time |    |

|     | with $m(x)$ using the same hardware used to calculate $a(x)$                           | 40 |

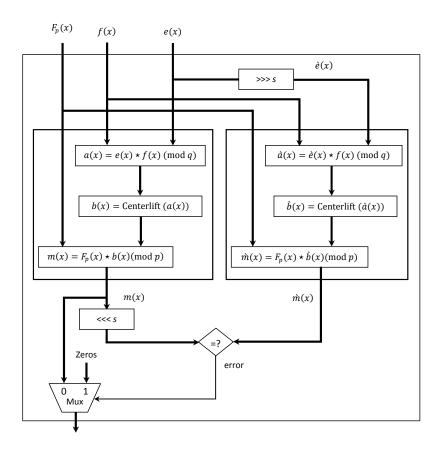

| 4.3 | Detecting errors by using the duplication method (decryption of a ciphertext           |    |

|     | and its rotated version)                                                               | 42 |

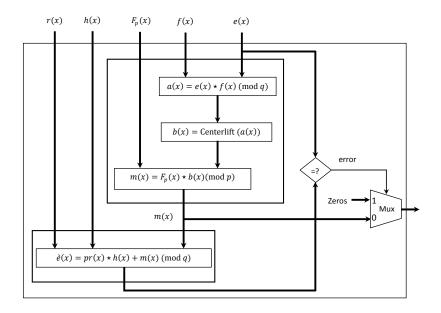

| 4.4 | Detecting errors by using the duplication method (decryption followed by en-           |    |

|     | cryption)                                                                              | 43 |

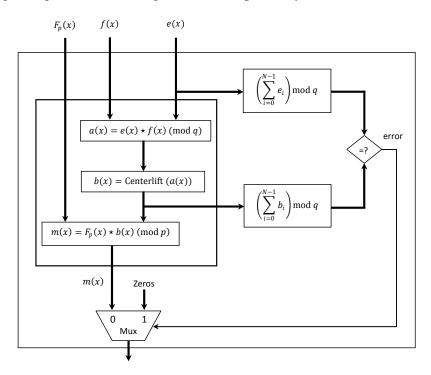

| 4.5 | Detecting errors by using checksum EDC from Lemma 4.2                                  | 45 |

| 4.6 | Detecting errors using checksum EDC and spatial redundancy                             | 48 |

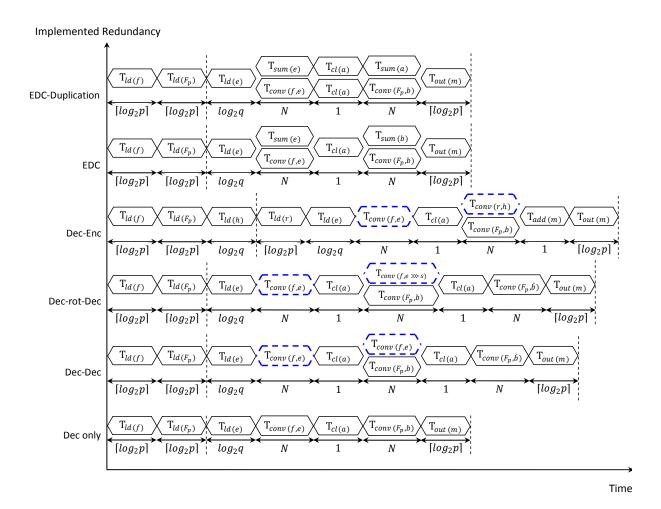

| 4.7 | Time-line (not to scale) of operations performed by the proposed architectures.        |    |

|     | Operations performed using resource sharing are shown in dotted lines                  | 50 |

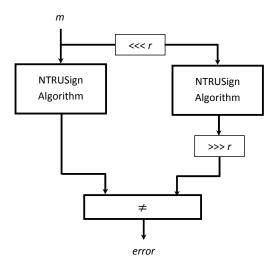

| 4.8 | Fault injection in the NTRUSign algorithm                                              | 55 |

| 4.9 | Fault detection by recomputing with cyclically shifted messages                        | 62 |

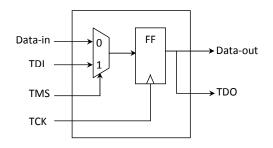

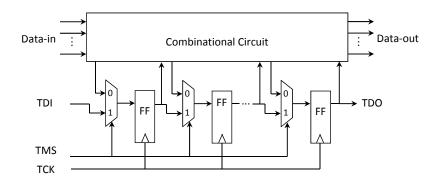

| 5.1 | An illustration for a scan flip-flop (SFF)                                             | 67 |

| 5.2 | An illustration for a scan chain                                                       | 67 |

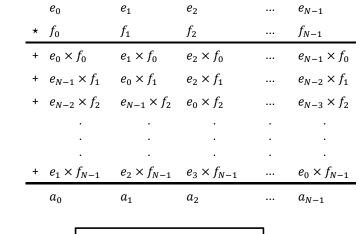

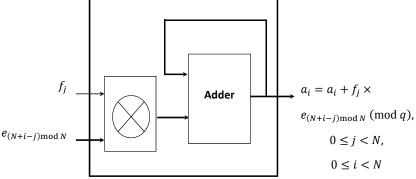

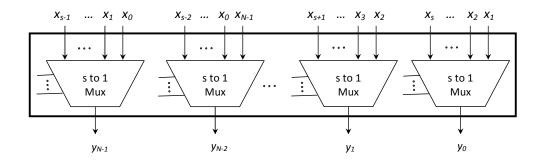

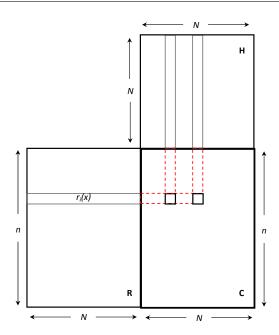

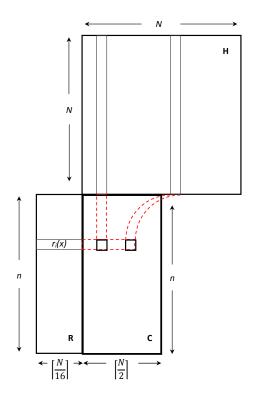

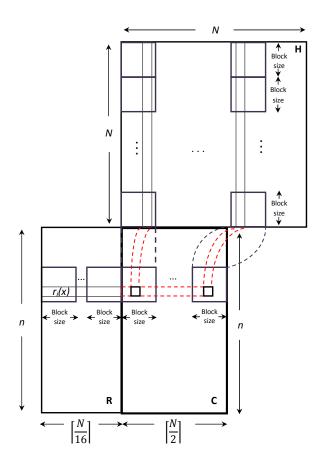

| 5.3         | A typical low area implementation of the convolution multiplication ( $f(x)$ $\star$   |     |

|-------------|----------------------------------------------------------------------------------------|-----|

|             | $e(x)$ ) in $N^2$ clock cycles. For each $0 \le i < N, j$ varies from $0$ to $N-1.$    | 70  |

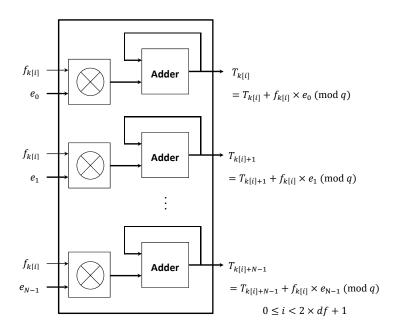

| 5.4         | The convolution multiplication between the polynomials $f(x)$ and $e(x)$ in $2 \times$ |     |

|             | $d_f-1$ clock cycles                                                                   | 71  |

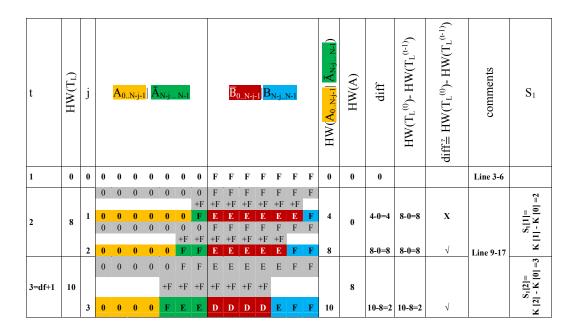

| 5.5         | The computation steps in Algorithm 4 for Example 5.1                                   | 80  |

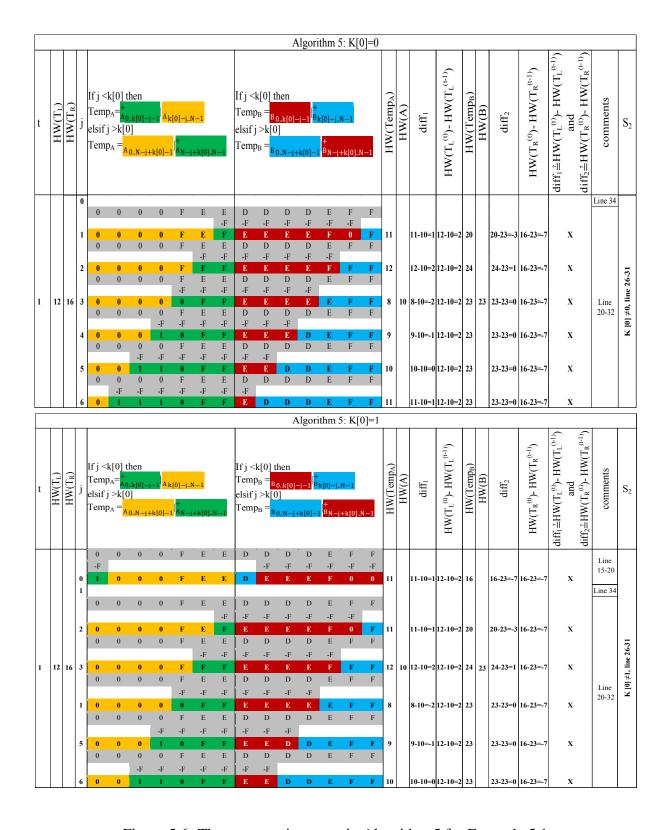

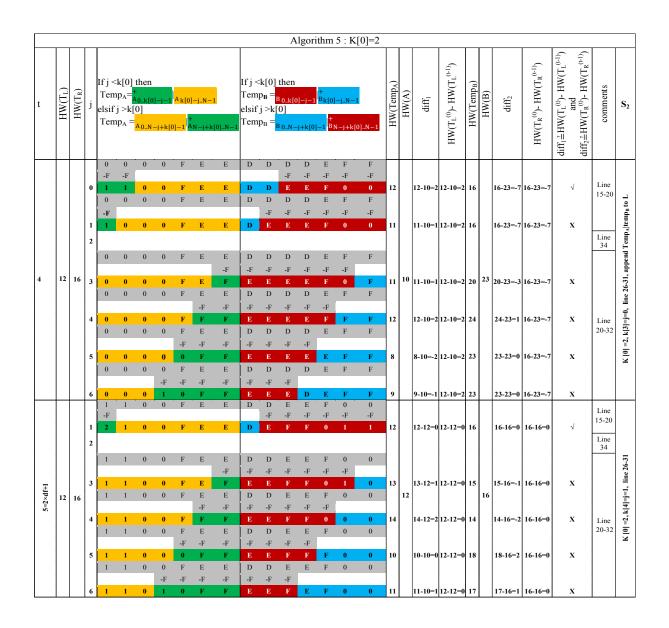

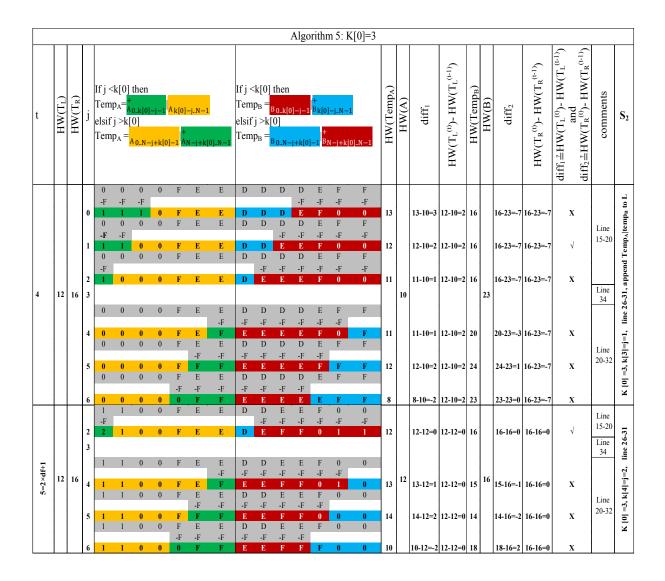

| 5.6         | The computation steps in Algorithm 5 for Example 5.1                                   | 81  |

| 5.7         | The computation steps in Algorithm 5 for Example 5.1: Continued from Figure            |     |

|             | 5.6                                                                                    | 82  |

| 5.8         | The computation steps in Algorithm 5 for Example 5.1: Continued from Figure            |     |

|             | 5.7                                                                                    | 83  |

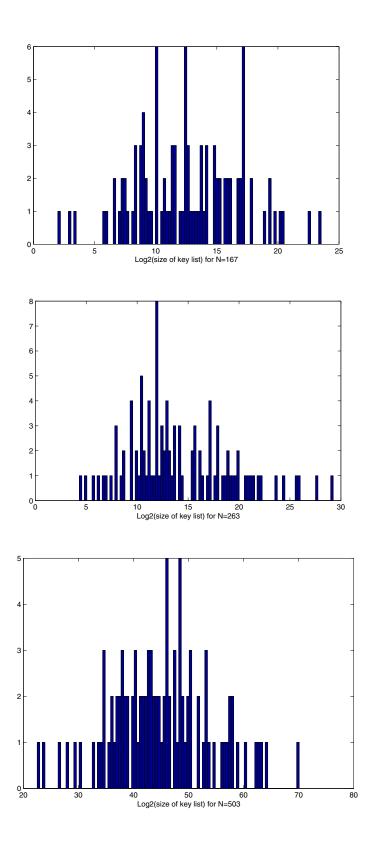

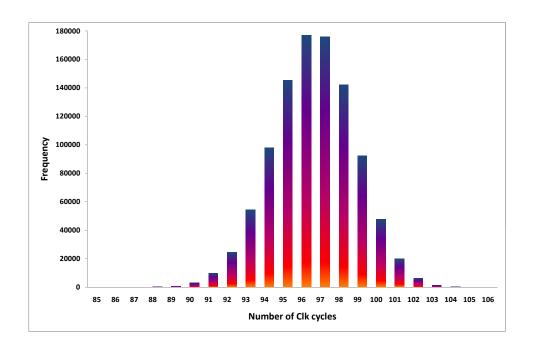

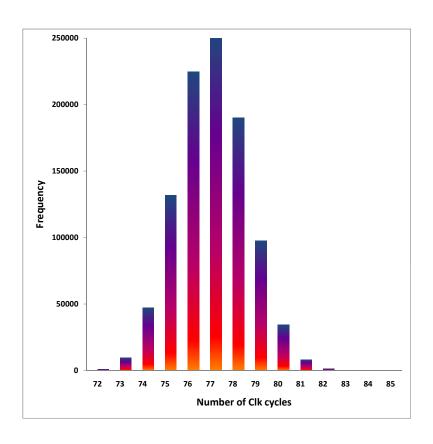

| 5.9         | Histogram distribution for the size of the list of suggested keys                      | 86  |

| <b>A</b> .1 | Example of $(N,s)$ -shifter                                                            | 117 |

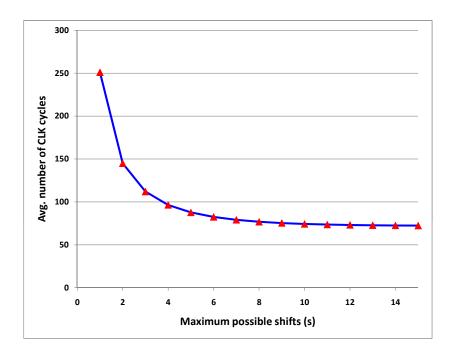

| A.2         | Average value of $T_{conv(s)}$                                                         | 118 |

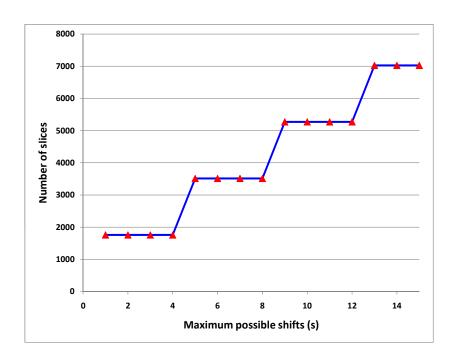

| A.3         | The number of slices for $(251,s)$ -shifter                                            | 119 |

| A.4         | Histogram of $T_{conv(s=4)}$                                                           | 120 |

| A.5         | Histogram of $T_{conv(s=8)}$                                                           | 121 |

| B.1         | The CUDA programming model                                                             | 126 |

| B.2         | The CUDA memory model                                                                  | 127 |

| B.3         | The convolution operation using NP, NC, and GM                                         | 130 |

| B.4         | The convolution operation using NP, BP, and GM                                         | 131 |

| B.5         | The convolution operation using NP, NC, and SH                                         | 132 |

| B.6         | The convolution operation using NP, BP, and SH                                         | 133 |

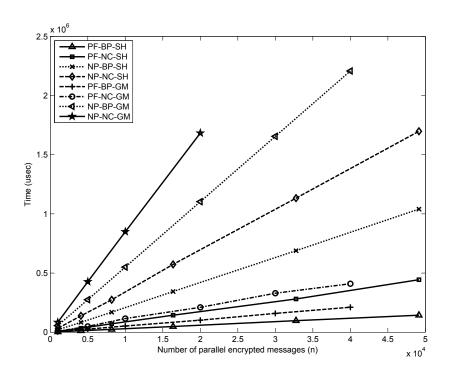

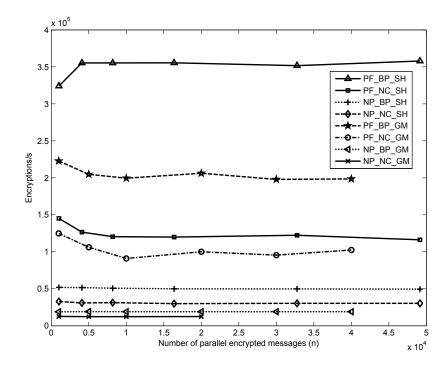

| B.7         | Total time required to encrypt $n$ messages in parallel                                | 134 |

| B.8         | The number of parallel encrypted messages per second.                                  | 134 |

# **List of Tables**

| 3.1 | CryptoMinSAT input corresponding to Example 3.1                                                         | 27  |

|-----|---------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Run-time statistics for decay factors 30%, 40%, 50%, 60%, and 70%                                       | 29  |

| 3.3 | Run-time statistics for decay factors 72%, 74%, 76%, 78%, and 80%                                       | 29  |

| 4.1 | The parameter sets for NTRU in [85]                                                                     | 36  |

| 4.2 | FPGA implementation results for the raw NTRUEncrypt decryption with pa-                                 |     |

|     | rameters $(N, p, q, df, dg, dr) = (167, 3, 128, 61, 20, 18) \dots \dots \dots \dots \dots$              | 51  |

| 4.3 | Experimental results for NTRUSign with $(N, q, df, dg, \mathcal{B}, \text{"type"}, \mathcal{N})$ =(251, |     |

|     | 128, 73, 71, 0, standard, 310)                                                                          | 57  |

| 4.4 | Experimental results for NTRUSign with $(N, q, df, dg, \mathcal{B}, \text{"type"}, \mathcal{N})$ =(251, |     |

|     | 128, 73, 71, 1, standard, 310)                                                                          | 57  |

| 4.5 | Experimental results for NTRUSign with $(N, q, df, dg, \mathcal{B}, \text{"type"}, \mathcal{N})$ =(251, |     |

|     | 128, 73, 71, 0, transpose, 310)                                                                         | 58  |

| 4.6 | Experimental results for NTRUSign with $(N, q, df, dg, \mathcal{B}, \text{"type"}, \mathcal{N})$ =(251, |     |

|     | 128, 73, 71, 1, transpose, 310)                                                                         | 58  |

| 4.7 | Experimental results for NTRUSign with the set of parameters in [82,83]                                 | 59  |

| 5.1 | The Hamming weight of $T_L$ and $T_R$ as obtained from JTAG scan chain output                           |     |

|     | in example $5.1$                                                                                        | 79  |

| 5.2 | The Hamming weight of $T_L$ and $T_R$ as obtained from JTAG scan chain output                           |     |

|     | in example 5.2                                                                                          | 84  |

| 5.3 | Average and median size of the list of suggested keys                                                   | 85  |

| A.1 | Implementation results using the naïve polynomial multiplication algorithm                              | 121 |

A.2 Implementation results using the proposed approach for s=4 and s=8 . . . . 122

# **List of Acronyms**

AES Advanced Encryption Standard

ANF Algebraic Normal Form

BDD Binary Decision Diagrams

BP Bit Packing

CBA Constant Based Attack

CNF Conjunctive Normal Form

CSP Conjugacy Search Problem

CPU Central Processing Unit

CRT Chinese Remainder Theorem

CUDA Compute Unified Device Architecture

DEMA Differential Electromagnetic Analysis

DES Data Encryption Standard

DFT Design-For-Test

DLP Discrete Logarithm Problem

DPA Differential Power Analysis

DRAM Dynamic Random Access Memory

DSA Digital Signature Algorithm

DSCA Differential Side Channel Attacks

EDC Error Detecting Code

EESS Efficient Embedded Security Standards

EMA Electromagnetic Analysis

FHDA Fixed Hamming Distance based Attack

FPGA Field Programmable Gate Array

FSMD Finite State Machine Data path

GCHQ Government Communications Headquarters

GF Galois Field

GGH Goldreich-Goldwasser-Halevi cryptosystem

GL General Linear Group

GM Global Memory

GPU Graphics Processing Unit

ISE Integrated Software Environment

JTAG Joint Test Action Group

LFSR Linear Feedback Shift Register

LUT Look Up Table

MI5 Military Intelligence, Section 5

MUX Multiplexer

NC Normal Coefficients Representation

NIST National Institute of Standards & Technology

NP Normal Polynomial Form

NSA National Security Agency

NTRUEncrypt NTRU Encryption Algorithm

NTRUSign NTRU Digital Signature Scheme

PF Product Form

RAM Random Access Memory

RBT Redundancy Based Technique

RFID Radio Frequency Identification

ROM Read Only Memory

RSA Rivest-Shamir-Adleman cryptosystem

SAT Satisfiability Problem

SCAs Side Channel Attacks

SEMA Simple Electromagnetic Analysis

SH Shared Memory

SIMD Single Instruction Multiple Data

SIMT Single Instruction Multiple Thread

SM Streaming Multiprocessor

SP Streaming Processor

SPA Simple Power Analysis

SRAM Static Random Access Memory

SSCA Simple Side Channel Attacks

TCK Test Clock

TDI Test Data In

TDO Test Data Out

TMS Test Mode Select

TRST Test Reset

VHSIC Very High Speed Integrated Circuits

VHDL VHSIC Hardware Description Language

# Chapter 1

# Introduction

### 1.1 Motivation

In the academic cryptanalysis literatures, a "break" of a cryptosystem is defined quite conservatively: if the effort required by the attacker is less than the effort required by naïve exhaustive search, then the cryptosystem is said to be broken. This conservative definition, while can be arguably justified, led to many published mathematical attacks that require impractical amounts of time, memory, or known/chosen plaintext-ciphertext pairs. On the other hand, in many practical scenarios, the attackers may have access to the cryptographic device. In such scenarios, SCAs allow the attackers to break these cryptosystems using a relatively small amount of computational resources and a small number of known/chosen plaintext-ciphertext pairs.

The basic idea behind SCAs is not new. For example, Wright [190] reported an early application of acoustic cryptanalysis. During his employment with GCHQ in 1965, the British intelligence agency (MI5) tried to break a cipher used by the Egyptian embassy in London. In order to reduce the computational resources required to break the cipher, Wright suggested placing a spy microphone near the rotor-cipher machine used by the Egyptians to detect the click-sound produced by the machine. By listening to the clicks of the rotors as cipher clerks

reset them each morning, MI5 successfully deduced the core position of some of the machines rotors which reduced the computation effort needed to break the cipher, and MI5 was able to spy on the embassys communication for years. Another example is given in a recently declassified National Security Agency (NSA) document [172] which reveals that in 1943, an engineer with Bell Telephone observed decipherable spikes on an oscilloscope associated with the decrypted output of a certain encrypting teletype.

Currently, the wide spread of unprotected software or hardware cryptographic implementations offers various possibilities for side channel attacks. Such attacks are practical; they do not even require expensive equipments. For example, Skorobogatov and Anderson [10] carried out fault analysis attacks using a flashgun bought second-hand from a camera store for \$30 and with an \$8 laser pointer. They also developed relatively simple techniques to set or reset any individual bit of SRAM in a microcontroller. Thus, unless suitable effective countermeasures are taken, vulnerability to this class of attacks poses a big problem for the industry, especially with the wide spread of smart cards, RFIDs, and embedded devices.

In the first part of this thesis, we investigate the application of several SCAs against both AES [59] and NTRU [84]. In particular, we study the use of an off-the-shelf SAT solver, CryptoMinSat, to improve the key recovery of the AES-128 key schedules from its corresponding decayed memory images resulting from applying the cold-boot attack. We present a fault analysis on NTRUEncrypt and NTRUSign and propose several hardware countermeasures. Proof of concept FPGA implementations for NTRUEncrypt are also presented. Furthermore, we present a scan-based SCA on NTRUEncrypt hardware implementations that employ scan-based DFT techniques.

Public-key cryptography [124] provides key exchange mechanisms in which secret keys can be exchanged between users over insecure communication channels. These key exchange mechanisms are usually based on number theory problems such as the discrete logarithm problem (DLP) [57], integer factorization [158] and elliptic curve DLP [26]. However, such systems require a large number of arithmetic operations, which makes them hard to implement in most

resource constrained applications. To overcome this problem, key exchange protocols based on efficient matrix algebra have been proposed. For example, Álvarez *et al.* [5] proposed a scheme in which the secret key is obtained by multiplying powers of block upper triangular matrices whose elements are defined over  $\mathbb{Z}_p$ . Climent *et al.* [40] identified the elements of the endomorphisms ring  $End(\mathbb{Z}_p \times \mathbb{Z}_{p^2})$  with elements in a set,  $E_p$ , of matrices of size  $2 \times 2$ , whose elements in the first row belong to  $\mathbb{Z}_p$  and elements in the second row belong to  $\mathbb{Z}_{p^2}$ . Keith Salvin [175] presented a key exchange protocol using matrices in the general linear group,  $GL(r,\mathbb{Z}_n)$ , where n is the product of two distinct large primes. The system is fully specified in the US patent number 7346162 issued in 2008. In the second part of this work, we present mathematical cryptanalytic attacks against these three schemes and show that they can be efficiently broken for all practical choices of their security parameters.

#### 1.2 Thesis contributions

In this thesis, we investigate the application of several side channel attacks on different ciphers. We also propose some countermeasures against these types of attacks. Some implementations of theses countermeasures are presented. We also present cryptanalysis of some recently proposed key exchange schemes. The contribution of this thesis can be summarized as follows:

- 1. We investigate the use of an off-the-shelf SAT solver, CryptoMinSat, to improve the key recovery of the AES-128 key schedules from its corresponding decayed memory images. By exploiting the asymmetric decay of the memory images and the redundancy of key material inherent in the AES key schedule, rectifying the faults in the corrupted memory images of the AES-128 key schedule is formulated as a Boolean satisfiability problem which can be solved efficiently for relatively large decay factors. Our experimental results show that this approach improves upon the previously known results.

- 2. We present a fault analysis attack on NTRUEncrypt. The fault model in which we analyze

the cipher is the one in which the attacker is assumed to be able to fault a small number of coefficients of the polynomial input to (or output from) the second step of the decryption process but cannot control the exact location of injected faults. For this specific original instantiation of the NTRU encryption system with parameters (N,p,q), our attack succeeds with probability  $\approx 1 - \frac{1}{p}$  and when the number of faulted coefficients is upper bounded by t, it requires  $O((pN)^t)$  polynomial inversions in  $\mathbb{Z}/p\mathbb{Z}[x]/(x^N-1)$ . We also investigate several techniques to strengthen hardware implementations of NTRUEncrypt against this class of attacks. In particular, by utilizing the algebraic structure of the cipher, we propose several countermeasures based on error detection checksum codes, and spatial/temporal redundancies. The error detection capabilities of these countermeasures, as well as their impact on the decryption throughput and area, are also presented.

- 3. We present a fault analysis attack on NTRUSign. The utilized fault model is the one in which the attacker is assumed to be able to fault a small number of coefficients in a specific polynomial during the signing process but cannot control the exact location of the injected transient faults. For NTRUsign with parameters  $(N, q = p^l, \mathcal{B}, standard, \mathcal{N})$ , when the attacker is able to skip the norm-bound signature checking step, our attack needs one fault, succeeds with probability  $\approx 1 \frac{1}{p}$  and requires  $O((qN)^t)$  computation steps when the number of faulted polynomial coefficients is upper bounded by t. The attack is also applicable to NTRUSign utilizing the transpose NTRU lattice but it requires double the number of fault injections. Different countermeasures against the proposed attack are investigated.

- 4. We present a scan-based SCA on NTRUEncrypt hardware implementations that employ scan-based Design-For-Test (DFT) techniques. Our attack determines the scan chain structure of the polynomial multiplication circuits used in the decryption algorithm which allows the cryptanalyst to efficiently retrieve the secret key.

- 5. We show that breaking the key exchange scheme proposed by Álvarez et al. [8] with

security parameters (r, s, p) is equivalent to solving a set of  $3(r + s)^2$  linear equations with  $2(r + s)^2$  unknowns in  $\mathbb{Z}_p$ , which renders this system insecure for all the suggested practical choices of the security parameters.

- 6. Climent et al. [40] identified the elements of the endomorphisms ring  $End(\mathbb{Z}_p \times \mathbb{Z}_{p^2})$  with elements in a set,  $E_p$ , of matrices of size  $2 \times 2$ , whose elements in the first row belong to  $\mathbb{Z}_p$  and the elements in the second row belong to  $\mathbb{Z}_{p^2}$ . By taking advantage of matrix arithmetic, they proposed a key exchange protocol using polynomial functions over  $E_p$  defined by polynomials in  $\mathbb{Z}[X]$ . We show that this key exchange protocol is insecure; it can be broken by solving a set of 10 consistent homogeneous linear equations in 8 unknowns over  $\mathbb{Z}_{p^2}$ .

- 7. Keith Salvin [175] presented a key exchange protocol using matrices in the general linear group,  $GL(r, \mathbb{Z}_n)$ , where n is the product of two distinct large primes. The system is fully specified in the US patent number 7346162 issued in 2008. In the patent claims, it is argued that the best way to break this system is to factor n. Furthermore, for efficiency reasons, it is suggested to use r = 2. We show that this cryptosystem can be easily broken by solving a set of consistent homogeneous  $r^2$  linear equations in 2r unknowns over  $\mathbb{Z}_n$ .

The contributions made throughout this work have been published in [99–109].

### 1.3 Outline of the thesis

The rest of the thesis is organized as follows. In chapter 2, we provide a brief overview of side channel attacks. A classification of these attacks, examples, and proposed countermeasures are also presented. We also briefly review the Boolean satisfiability (SAT) problem. In chapter 3, we show how to use an off-the-shelf SAT solver, CryptoMinSat, to improve the key recovery of the AES-128 key schedules from its corresponding decayed memory images. Chapter 4 presents our fault analysis attacks against NTRUEncrypt and NTRUSign cryptosystems.

Different countermeasures are also presented. In chapter 5, we describe our proposed scan-based side channel attack on the NTRUEncrypt cryptosystem. The simulation results and their analysis are also provided. Chapter 6 provides cryptanalysis of the three key exchange schemes proposed by Álvarez *et al.* [8], Climent *et al.* [40], and Keith Salvin [175]. Our conclusions and some suggestions for future research directions are given in chapter 7. An architecture that offers different area-speed trade-off for NTRUEncrypt is presented in Appendix A together with a proof of concept FPGA implementation results. Results on implementing NTRUEncrypt on the NVIDIA GTX275 GPU, using the CUDA framework are presented in Appendix B.

# Chapter 2

# **Background and Literature Review**

### 2.1 Introduction

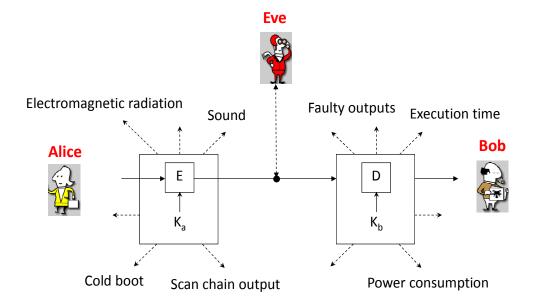

The classical focus of cryptography has been communication security. Consequently, traditional cryptanalytic techniques focused on information flowing over the communication channel rather than the endpoint cryptographic devices. This view has changed dramatically with the introduction of SCAs in the open literatures. Cryptography is now widely deployed in many devices ranging from pay TV units, cell phones, prepaid cards and smart cards. Because these cryptographic devices are easily obtainable, attackers can study the internal structure of the hardware to learn specific details about their implementations. Knowledge of the implementation may then be used to carry out attacks on the system without directly attacking the mathematics of the algorithms. In other words, even when totally secure algorithms and protocols are employed, attackers might still be able to learn valuable secret information due to the specific software or hardware implementation of the system. Figure 2.1 shows a modern view of the cryptographic model including different side channel information that can be obtained from the endpoint devices.

In this chapter we provide a brief overview of side channel attacks. A classification of SCAs is given in the next section. Examples of these attacks and proposed countermeasures

are presented in section 2.3 and 2.4, respectively. Finally, in section 2.5 we briefly review the Boolean satisfiability (SAT) problem.

Figure 2.1: The cryptographic model including examples for side-channels

### 2.2 Classifications of side channel attacks

SCAs can be classified according to (i) the attackers capabilities to control the computation process, (ii) the way of accessing the cryptographic module and (iii) the method used in the analysis process [196].

### 2.2.1 Controls over the computation process

SCAs can be divided based on the control over the computation process by attackers into two main categories: passive attacks and active attacks. Passive attacks refer to those that do not interfere with the operation of the target system, i.e., the attacker is assumed to be able to collect some information about the operation of the target system without disturbing its behavior. In contrast, in active attacks, the adversary can affect the behavior of the target system, while the attacked system may or may not be able to detect such influence.

#### 2.2.2 Ways of accessing the module

Anderson *et al.* [10] classified side channel attacks into three classes: invasive attacks, semi-invasive attacks and non-invasive attacks.

#### A. Invasive attacks

Invasive attacks require a direct physical access to the internal components of the cryptographic modules. A classic example of this class of attacks is when attackers may get access to the inner layer of the cryptographic module and place a probing needle on the data bus to record and later analyze the data transferred. Several defensive measures are usually implemented in hardware to counter such invasive attacks effectively. For example, some cryptographic modules with higher security level reset all their memories when tampering is detected [60].

#### B. Semi-invasive attacks

The notion of semi-invasive attack was first introduced by Skorobogatov and Anderson [174]. This type of attacks involves access to the device, but without physical access or damage to the layer that contains the cryptographic module. For example, in fault-induced attacks, the attacker may use a laser beam to ionize the device in order to change some of its memory contents and consequently change the output of the device.

#### C. Non-invasive attacks

Non-invasive attacks require close examination or manipulation of the device's behavior. This class of attacks exploits information that is unintentionally leaked. A classical example of such attacks is timing analysis which measures the time consumed by a device to perform an operation and analyze it to deduce the secret keys. One of the main characteristics of a non-invasive attack is that it is completely undetectable. For example, a tamper resistant smart card cannot figure out that its running time is currently being measured. Furthermore, contrary to invasive attacks that require individual processing of each attacked device, non-

invasive attacks are often low-cost to deploy on a large scale. Therefore, non-invasive attacks present more threat for embedded devices and smart cards.

#### 2.2.3 Methods used in the analysis process

Based on the methods used in the analysis process of the sampled data, SCA attacks are divided into Simple Side Channel Attack (SSCA) and Differential Side Channel Attack (DSCA). SSCA exploits the side channel output primarily depending on the performed operations. Typically, a single trace is used in an SSCA analysis, and therefore the secret key can be directly read from the side channel trace. If the SSCA is not successful due to noise in the measurements, DSCA can be used. DSCA exploits the correlation between the processed data and the side channel output. Since this correlation is often very small, statistical methods are used to exploit it efficiently.

# 2.3 Examples of side channel attacks

Side channel attacks exploit the information leaked by the physical characteristics of the cryptographic modules during execution of the algorithm. This extra information can be extracted from timing, power consumption or electromagnetic radiation characteristics. Other forms of side channel information can also be available as a result of hardware or software failures, changes in frequency or temperature, and computational errors.

# 2.3.1 Timing attack

The majority of optimized implementations of cryptographic algorithms execute the computations in a non-constant time. If these operations involve secret parameters, these timing variations can leak some information that can provide enough knowledge of the implementation. A careful statistical analysis sometimes could even lead to the total recovery of the secret parameters. Timing attacks were first introduced in 1996 by Kocher [115] who demonstrated

the feasibility of these attacks against the RSA system. Later, Schindler [160] presented timing attacks on implementations of RSA exponentiation that employ the Chinese Remainder Theorem (CRT). Afterwards, several experimental results on various cryptographic algorithms have been reported (e.g., [52,78]).

In order to illustrate the idea of the timing attack, consider an RSA cryptosystem where the encryption operation involves the computation of  $R = y^x \mod n$  where n is the public modulus, and y is the message being encrypted. The goal of the attacker is to find the secret key x.

Algorithm 1 shows the modular exponentiation algorithm which is typically used to computes  $R = y^x \mod n$ , where x is w bits long. Kocher [115] shows that an attacker who can record the message received and the time taken to respond to each y, will be able to predict the operations of the algorithm. In particular, the timing attack described by Kocher allows someone who knows the exponent bits  $0 \cdots (b-1)$  to find bit b. This is because when the first b bits are known, the attacker can compute the first b iterations of the for loop to find the value of  $s_b$ . In the next iteration, the first unknown bit will be tested. If it is set,  $R_b = (s_b \cdot y) \mod n$  will be computed, else this operation will be skipped. If the total modular exponentiation time for the iteration is ever fast when  $R_b = (s_b \cdot y) \mod n$  is slow then bit b must be zero. Conversely, if the modular exponentiation time is slow, then the bit must be set. The same set of timing measurement can be used to determine the rest of the exponentiation bits.

#### Algorithm 1 Modular Exponentiation Algorithm [115]

```

1: Let s_0 = 1.

2: for k = 0 to w - 1 do

if (bit k of x is 1) then

3:

4:

Let R_k = (s_k \cdot y) \bmod n

5:

else

Let R_k = s_k

6:

end if

7:

Let s_{k+1} = R_k^2 \mod n

8:

9: end for

10: Return (R_{w-1})

```

A special class of timing attacks is cache based attacks which involve monitoring the

movement of data into and out of the cache. Cache profiles can be used to recover the secret key information of a cryptographic algorithm. Such attacks usually consist of a collection phase that provides the attacker with profiles of execution, and an analysis phase which recovers the secret information. Cache based attacks can be categorized as trace driven attacks [152] or time driven attacks [185, 186]. Trace driven attacks rely on the ability of the attacker to capture a profile of cache activity that results from running the algorithm. That is, in order to perform a successful attack, the adversary needs a cache trace which shows cache hits or misses for every memory access. Time driven attacks rely on the fact that the execution time is mainly affected by memory accesses since cache hits result in a lower execution time and cache misses result in a comparably higher execution time.

#### 2.3.2 Fault attacks

If the attacker is able to induce a fault or error during the operation of the cryptographic module, then the faulty behavior may provide the attacker with valuable side channel information that can greatly increase the cipher's vulnerability to cryptanalysis. Fault cryptanalysis presents practical and effective attacks against cryptographic hardware devices such as smart cards. The threat posed by these attacks was first demonstrated in the open literatures by Boneh *et al.* [29,30] who showed that it is easy to extract the private RSA decryption/signing keys by inducing errors in the CRT implementation and observing the faulty output. Since then, many cryptographic algorithms have been broken by using such types of attacks. In [25], Biham and Shamir presented fault analysis attacks on the DES symmetric-key encryption scheme. Shamir *et al.* [79] developed general fault analysis techniques which can be used to attack the standard constructions of stream ciphers based on LFSRs.

A special type of fault analysis can be performed when the adversary is able to manipulate the program counter to skip instructions of an algorithm. In these fault models, we assume that the fault injection allows the attacker to skip the targeted instruction with a specific probability, i.e., we assume that the fault injection may also cause other instructions to be skipped or

other variables to be changed randomly. Thus, an adversary must be able to check, whether the fault injection was successful or not. In practice, these fault attacks can be launched by introducing power glitch or spikes or by clocking the module with a clock rate outside the allowed range. Various experimental results confirming the above ideas were verified (e.g., [161]).

#### 2.3.3 Power analysis attacks

In addition to the computation time and the faulty behavior, the power consumption of a cryptographic device can also leak useful information about the running operations and their involved secret parameters. Unlike the timing and the fault analysis, power analysis attacks are applicable only to hardware implementations. These attacks proved to be very effective in attacking smart cards and other embedded systems. Generally, power analysis attacks can be categorized into Simple and Differential Power Analysis (referred to as SPA and DPA, respectively). In SPA attacks, the goal is utilize the measured power traces in order to guess which particular instruction is being carried out at a specific time as well as the input and output values of this instruction. For that, the adversary needs to know the exact structure of the implementation in order to apply such an attack. In contrast, DPA attacks do not require knowledge of the implementation details and instead exploit statistical methods in the analysis process. In general, DPA is one of the most powerful SCAs which can be applied using relatively little resources [116, 150]. Experimental results with power analysis attacks on smart cards were reported in [3, 62, 126].

### 2.3.4 Electromagnetic attacks

Similar to any electrical device, the components of cryptographic devices usually generate electromagnetic radiations as part of their execution processes. By analyzing these emanations, the attacker can deduce the relationship between it and the underlying computation and data. This may allow the attacker to extract some useful information about the secret parameters of the cryptographic algorithm. Electromagnetic Analysis (EMA) can also be divided

into two main classes: simple Electromagnetic Analysis (SEMA) and Differential Electromagnetic Analysis (DEMA). Experimental results on electromagnetic analysis attacks on cryptographic devices such as smart cards and comparisons to power analysis attacks were presented in [61, 156].

#### 2.3.5 Cold-boot attacks

A cold-boot attack [72] is a SCA that exploits the fact that data loss of a non-powered random access memory can be retarded by cooling it down. In 2002, Skorobogatov [173] performed experiments to study the temperature dependency of data retention time in static RAM devices. The reported experimental results indicate that many chips may preserve data for relatively long periods of time at temperatures above  $-20^{\circ}$ C which contradicted the common wisdom that was widely believed at that time. The temperature at which 80% of the data remained for one minute varied widely between devices. While some devices required cooling to at least  $-50^{\circ}$ C, others, surprisingly, retained data for this period at room temperature. Memory retention time also varied between devices of the same type from the same manufacturer, most likely, because controlling data retention time is not a part of the chip manufacturing quality process [173].

Thus, one way to launch a cold-boot attack is to remove the memory module, after cooling it, from the target system and immediately plugging it in another system under the adversary's control. This system is then booted to access the memory. Another possible approach to execute the attack is to cold-boot the target machine by cycling its power OFF and then ON without letting it shut down properly. Then a lightweight operating system is instantly booted where the content of targeted memory is dumped to a file. Further analysis can then be performed against the information that is retrieved from memory in order to find sensitive information such as cryptographic keys or passwords.

#### 2.3.6 Scan-based attacks

Scan-based Design-for-Test [34] is a widely deployed technique for testing hardware chips. Using this approach, all flip-flops in the design under test are connected to a scan chain where their states can be scanned out during the testing phase. Scan-based SCAs exploit the information obtained by analyzing the scanned data in order to retrieve secret information from cryptographic hardware devices that are designed with this testability feature.

While scan-based DFT improves the quality of testing, it also opens a powerful side channel against hardware implementations of cryptographic devices that utilize this technique. Despite the fact that the internal structure of the scan chain is usually not known to attackers, exploiting the information obtained from analyzing the scanned data allows cryptanalysts to ascertain this structure and retrieve the secret key information from cryptographic hardware devices implementing various cryptographic algorithms

#### 2.3.7 Acoustic attacks

Most research on side channel attack focused on timing, power consumption, and fault features. However, one of the oldest eavesdropping methods, namely acoustic emanations, has received little attention. Recently, Shamir *et al.* [166] have presented introductory proof-of-concept that confirm the correlation between the sound of a PC and its computation. Although we may consider the technique used by P. Wright in 1965 as one of the primitive acoustic attacks [190], this is a relatively new field of research, and much research is needed to confirm its effectiveness against modern cryptographic algorithms and devices.

# 2.4 Countermeasures against side channel attacks

SCAs primarily focus on the implementation of the cryptographic algorithm. Several software and hardware countermeasures were proposed to combat side channel attacks. Some of these countermeasures make algorithmic changes to the cryptographic primitives so that at-

tacks are provably inefficient on the obtained implementation. Other countermeasures decorrelate the output traces on individual runs. In what follows, we briefly explain how specific countermeasure can be applied in order to thwart different forms of SCAs.

#### 2.4.1 Preventing timing attacks

The most obvious way to prevent timing attacks is to force all operations to consume the same amount of time. When this is not possible, another approach is to make timing measurements extremely inaccurate, e.g., by introducing random timing shifts and wait states, or by inserting dummy instructions. Random delays added to the processing time do increase the number of ciphertexts required by the cryptanalyst, but attackers can compensate for this by collecting more measurements. The number of samples required increases roughly as the square of the timing noise [115]. In [115], Kocher describes a methodology for preventing timing attack based on the techniques used for blinding signature. His approach is to choose a random pair  $(v_i, v_f)$  such that  $v_f^{-1} = v_i^x \mod n$ . Before the modular exponentiation operation, the input message should be multiplied with  $v_f \mod n$ , and afterwards the result is corrected by again multiplying it with  $v_f \mod n$ . The  $(v_i, v_f)$  pair should not be reused since they themselves might be compromised by timing attacks. An efficient solution to this problem is to update  $v_i$  and  $v_f$  before each modular exponentiation step. If  $(v_i, v_f)$  is secret, then the attacker has no useful knowledge about the input to the modular exponentiation.

Wang *et al.* [188] propose two approaches to overcome cache based SCAs. The first approach is to use a partition based approach to eliminate cache interference. The second is based on randomizing cache interference in such a way to guarantee zero information leakage. The authors have also presented a new security aware cache design which consists of Partition Locked cache (PLcache) and Random Permutation cache (RPcache).

#### 2.4.2 Preventing power analysis attacks

Mitigation power analysis attacks can be achieved by modifying the design of the hardware device in such away that its power consumption becomes random or to make the device consume an equal amount of power for all operations and for all processed data values. The data masking technique, which can be introduced at the software or hardware level, is another widely used countermeasure against power analysis attacks [38, 70]. The basic idea of most masking approaches is to randomize the intermediate values that are processed in the computation of the algorithm operation. In case of AES, the SubByte operation is the only nonlinear operation in the AES algorithm. This operation consists of two sub-operations: the inverse operation and the affine operation. Hence, one should focus on the masking of the inverse operation [148]. The idea of masking the inverse operation is to input the value  $A \oplus M$  to the algorithm in such a way that we obtain the output value  $A^{-1} \oplus M$ , where A is the intermediate data, and M is the mask. There are two types of masking: multiplicative masking and additive masking (e.g., see [4, 69, 150, 182, 195]). Techniques to mitigate higher order power analysis are investigated in e.g., [63, 71, 94, 112, 155, 157, 162].

## 2.4.3 Preventing fault attacks

Given the relative ease of injecting faults into cryptographic devices, proper countermeasures must be taken in order to keep theses devices secure. Typically, such countermeasures aim to detect any transient or permanent faults that occur in the cryptosystem and immediately suppress the resulting faulted outputs or reset all the output bits to zeros (or any other arbitrary value) in order to prevent the attacker from observing the output of faulty devices and hence mitigate the susceptibility of the system to these attacks. Numerous approaches to fault detection techniques for ciphers have been proposed. These approaches can be divided into two classes: Error Detecting Codes (EDCs) and Redundancy-Based Techniques (RBT) [20, 117].

#### 2.4.4 Preventing cold-boot attacks

As mentioned above, cold-boot attacks exploit DRAM remanence to acquire memory images from which keys and other sensitive data can be extracted. In order to mitigate the threat of this attack, one should apply some transformations to the key as it is stored in memory in order to make it more difficult to reconstruct in the case of errors [35]. One should also prevent keys from being paged to disks by clearing memory at boot time. Other suggested countermeasures include: (i) physically protecting the memory. For example, DRAM modules could be locked in place inside the machine, (ii) suspending the system safely by powering off the machine completely when it is not in use, (iii) encrypting in the disk controller. This approach differs from typical disk encryption systems in that encryption and decryption are done by the disk controller rather than by software in the main CPU, and that the main encryption keys are stored in the disk controller rather than in DRAM. One example for AES implementations that is secure against this class of attacks is Tresor [136] which is a kernel patch for Linux based operating systems which loads and manipulates key related data directly in the microprocessor and its registers.

# 2.5 The SAT problem

The Boolean Satisfiability (SAT) problem [44] is defined as follows: given a Boolean formula, check whether an assignment of Boolean values to the propositional variables in the formula exists such that the formula evaluates to true. If such an assignment exists, the formula is said to be satisfiable; otherwise, it is unsatisfiable. For a formula with m variables, there are  $2^m$  possible assignments. The Conjunctive Normal Form (CNF) is the most frequently used form for representing Boolean formulas. In CNF, the variables of the formula appear in literals (e.g., x) or their negation (e.g.,  $\overline{x}$ ). Literals are grouped into clauses, which represent a disjunction (logical OR) of the literals they contain. A single literal can appear in any number of clauses. The conjunction (logical AND) of all clauses represents a formula. For example,

the CNF formula  $(x_1) \wedge (\overline{x}_2 \vee \overline{x}_3) \wedge (x_1 \vee x_3)$  contains three clauses:  $x_1, \overline{x}_2 \vee \overline{x}_3$  and  $x_1 \vee x_3$ . Two literals in these clauses are positive  $(x_1, x_3)$  and two are negative  $(\overline{x}_2, \overline{x}_3)$ . For a variable assignment to satisfy a CNF formula, it must satisfy each of its clauses. For example, if  $x_1$  is true and  $x_2$  is false, then all three clauses are satisfied, regardless of the value of  $x_3$ .

Given a set of equations of a system which we want solve, the higher degree are handled by noting that, for example, the logical expression

$$(x_1 \vee \overline{T})(x_2 \vee \overline{T})(x_3 \vee \overline{T})(x_4 \vee \overline{T})(T \vee \overline{x}_1 \vee \overline{x}_2 \vee \overline{x}_3 \vee \overline{x}_4)$$

(2.1)

is tautologically equivalent to  $T \Leftrightarrow (x_1 \wedge x_2 \wedge x_3 \wedge x_4)$ , or the GF(2) equation  $T = x_1x_2x_3x_4$ . Similar expressions exist for higher order terms. Thus, the system of equations obtained in this step can be linearlized by introducing new variables.

# Chapter 3

# Applications of SAT Solvers to AES Key Recovery from Decayed Key Schedule Images

# 3.1 Introduction

A cold-boot attack [72] is a SCA that exploits the fact that data loss of a non-powered RAM can be deployed by cooling it down. In 2002, Skorobogatov [173] performed experiments to study the temperature dependency of data retention time in static RAM devices. The reported results indicated that many chips may preserve data for relatively long periods of time at temperatures above  $-20^{\circ}$ C which contradicted the common wisdom that was widely believed at that time. The temperature at which 80% of the data remained for one minute varied widely between devices. While some devices required cooling to at least  $-50^{\circ}$ C, others, surprisingly, retained data for this period at room temperature. Memory retention time also varied between devices of the same type from the same manufacturer, most likely, because controlling data retention time is not a part of the chip manufacturing quality process.

Thus, one way to launch a cold-boot attack is to remove the memory module, after cool-

ing it, from the target system and immediately plug it in another system under the adversary's control. This system is then booted to access the memory. Another possible approach to execute the attack is to cold-boot the target machine by cycling its power OFF and then ON without letting it shut down properly. Then a lightweight operating system is, instantly, booted where the content of targeted memory is dumped to a file. Further analysis can then be performed against the information that is retrieved from memory in order to find sensitive information such as cryptographic keys or passwords.

Because of the nature of cold-boot attacks, it is realistic to assume that only a corrupted image of the contents of memory will be available to the attacker, i.e., a fraction of the memory bits will be flipped. Halderman et *al.* [72] observed that, within a specific memory region, the decay is overwhelmingly asymmetric, i.e., either  $0 \to 1$  or  $1 \to 0$ . When trying to retrieve cryptographic keys, the decay direction for a region can be determined by comparing the number of 0s and 1s since, in an uncorrupted key, the expected number of 0s and 1s should approximately be equal.

Given this asymmetric decay, rectifying these faults can be achieved by further exploiting the redundancy of key material inherent in many widely used cryptographic algorithms. For example, in [75], Heninger *et al.* showed that an RSA private key with small public exponent can be efficiently recovered given a 0.27 fraction of its bits at random. In [72], Halderman *et al.* have developed a recovery algorithm for the 128-bit version of the Advanced Encryption Standard (AES-128) that recovers keys from 30% decayed AES-128 Key Schedule images in less than 20 minutes about half the time. Tsow [184] further improved upon this proof of concept and presented a heuristic algorithm that solved all cases at 50% decay or less in under half a second. At 60% decay, Tsow recovered the worst case in 35.500 seconds while solving the average case in 0.174 seconds. At the extended decay rate of 70%, recovery time averages grew to over 6 minutes with the median time at about five seconds. Nearly half of the 17.4 day run was consumed by solving the worst case of the test suite; the second slowest case was over six times faster.

It should be noted, however, that the algorithm developed by Tsow is complex and is certainly uneasy to develop and fine tune. On the other hand, the relations that have to be satisfied between the different subround key bits in the AES key schedule can be easily formulated as a Boolean SAT problem which lends itself naturally to SAT solvers. In this chapter, we explore the use of CryptoMiniSAT SAT solver [176] on the above problem, i.e., to recover AES-128 keys from its decayed key schedule images.

# 3.2 The SAT problem and its applications to cryptanalysis

While the SAT problem is NP-complete [44], efficient heuristics exist that can solve many real-life SAT formulations. Furthermore, the wide range of target applications of SAT have motivated advances in SAT solving techniques that have been incorporated into freely-available SAT software tools (e.g., [18,55,67,77,132]. Also see the international SAT competitions web page [19].)

Given the versatility and effectiveness of SAT solving techniques, the use of SAT solvers in cryptanalysis has recently attracted the attention of many cryptanalysts. In the area of cryptanalysis of block ciphers, Courtois *et al.* [46] presented an attack on the KeeLoq block cipher. They showed that when about  $2^{32}$  known plaintexts are available, KeeLoq becomes very week and for 30% of all keys, the full key can be recovered with complexity of  $2^{28}$  KeeLoq encryptions. Erickson *et al.* [58] used the Gröbner basis attacks [32] on SMS4 equation system over GF(2) and GF( $2^{8}$ ) and used the SAT solver over the GF(2) model. They implement their design in Gröbner basis using a Magma tool and in SAT solver using the MiniSAT tool. In [45], 6 rounds of DES are attacked with only a single plaintext-ciphertext pair.

SAT solvers have also been applied to the cryptanalysis of stream ciphers. Eibach *et al.* [56] presented experimental results over a slightly modified version of Trivium (Bivium) using a SAT solver, an exhaustive search, a BDD based attack, a graph theoretic approach, and Gröbner basis. The results indicate that the initial state of the cipher is recovered and the use of

SAT solver is faster than the other attacks. The full key of Hitage2 stream cipher is recovered in a few hours when using MiniSat 2.0 [47]. In [48], the full 48-bit key of the MiFare Crypto-1 algorithm was recovered in 200 seconds on a PC, given one known Initialization Vector (IV) (from one single encryption).

Mironov and Zhang [129] described some initial results on using SAT solvers to automate certain components in cryptanalysis of hash functions of the MD and SHA families. They generated full collisions for MD4 and MD5. De *et al.* [51] presented heuristics for solving inversion problems for functions that satisfy certain statistical properties similar to those of random functions. They demonstrate that this technique can be used to solve the hard case of inverting a popular secure hash function and inverted MD4 up to 2 rounds and 7 steps in less than 8 hours.

In this work, we use the CryptoMiniSat [176], which is an extension of MinSat (a state-of-the-art DPLL-based [50] SAT solver), refined to understand the XOR operation, which is common in cryptography, besides functions in CNF that is native to many SAT solvers.

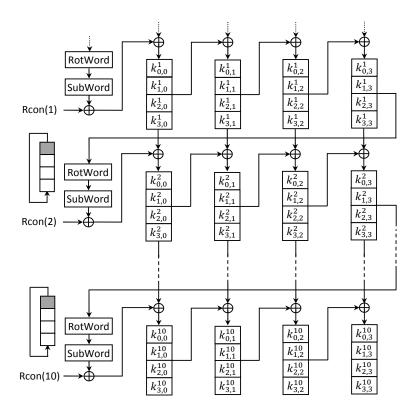

# 3.3 Structure of the AES-128 key schedule

In this section, we briefly review the relevant details of the AES-128 key schedule [49, 59]. Bytes of initial key are denoted by  $K_{i,j}^0$ , where  $0 \le i, j \le 3$  stand for the row index and column index, respectively in the standard AES state matrix representation. Figure 3.1 shows the AES-128 key schedule.

These 16 initial key bytes are bijectively mapped to 10 additional round-keys denoted by  $K_{i,j}^{r+1}$ , where  $0 \le r \le 9$  stands for the number of the subkeys (rounds). The  $r^{th}$  key schedule round consists of the following transformations

$$\begin{split} K_{0,0}^{r+1} &\leftarrow S(K_{1,3}^r) \oplus K_{0,0}^r \oplus \operatorname{Rcon}(r+1) \\ K_{i,0}^{r+1} &\leftarrow S(K_{(i+1) \bmod 4,3}^r) \oplus K_{i,0}^r, \ 1 \leq i \leq 3 \\ K_{i,j}^{r+1} &\leftarrow K_{i,j-1}^{r+1} \oplus K_{i,j}^r, \ 0 \leq i \leq 3, 1 \leq j \leq 3, \end{split} \tag{3.1}$$

Figure 3.1: The key schedule of the AES-128

where  $\mathrm{Rcon}(\cdot)$  is a round-dependent constant and  $S(\cdot)$  denotes the s-box (SubBytes) operation which is performed, on each byte of the state, by first taking the multiplicative inverse in  $GF(2^8)$  using the irreducible polynomial  $x^8+x^4+x^3+x+1$  and then applying an affine transformation over GF(2).

Similar to any Boolean function, each one of the eight coordinate of the s-box,  $S_l$ ,  $l=1,\cdots,8$ , has a unique representation as a polynomial over GF(2), called the Algebraic Normal Form (ANF) which is obtained by summing up distinct products terms of  $x_1,x_2,\ldots,x_n$ , and can be written as

$$S_l(x_1, \dots, x_n) = a_0 \bigoplus_{i=1}^n a_i x_i \bigoplus_{1 \le i < j \le n} a_{ij} x_i x_j$$

$$\bigoplus \dots \bigoplus a_{123...n} x_1 x_2 \dots x_n,$$

where  $a_0, a_i, \dots, a_{123...n} \in GF(2)$ .

# 3.4 Formulating the AES key schedule as a SAT problem

The AES key-schedule, described in the previous section, is the primary source of redundancy utilized to rectify faults in the corrupted memory images of the AES-128 key schedule. The conversion from the key schedule to the Boolean SAT problem proceeds as follows.

First, the system of equations of the AES-128 key schedule are generated according to the pseudocode in Equation (3.1). In each round, the s-box equations in lines 1, 2 of Equation (3.1) are represented in their ANF (e.g., Figure 3.2 shows the ANF of the first coordinate function of the s-box). Then, the terms of quadratic and higher degrees are handled by using the formula in (2.1).

$S_1 = x_1 \oplus x_3 \oplus x_4 \oplus x_6 \oplus x_1 x_3 \oplus x_1 x_7 \oplus x_1 x_8 \oplus x_2 x_4 \oplus x_2 x_6 \oplus x_2 x_8 \oplus x_3 x_5 \oplus x_4 x_6 \oplus x_6 x_7$  $x_2x_3x_4 \oplus x_2x_3x_6 \oplus x_2x_3x_8 \oplus x_2x_4x_6 \oplus x_2x_5x_7 \oplus x_2x_5x_8 \oplus x_2x_6x_7 \oplus x_2x_7x_8 \oplus x_3x_4x_5 \oplus$  $x_3x_4x_8 \oplus x_3x_5x_6 \oplus x_3x_5x_7 \oplus x_3x_5x_8 \oplus x_3x_6x_8 \oplus x_3x_7x_8 \oplus x_4x_7x_8 \oplus x_5x_6x_7 \oplus x_5x_6x_8 \oplus$  $x_1x_2x_3x_4 \oplus x_1x_2x_3x_6 \oplus x_1x_2x_3x_7 \oplus x_1x_2x_4x_6 \oplus x_1x_2x_4x_7 \oplus x_1x_2x_4x_8 \oplus x_1x_2x_5x_7 \oplus x_1x_2x_4x_8 \oplus x_1x_2x_5x_7 \oplus x_1x$  $x_1x_2x_5x_8 \oplus x_1x_3x_4x_7 \oplus x_1x_3x_5x_8 \oplus x_1x_4x_5x_6 \oplus x_1x_4x_5x_7 \oplus x_1x_4x_5x_8 \oplus x_1x_4x_6x_8 \oplus x_1x_4x_5x_8 \oplus x_1x_5x_8 \oplus x$  $x_1x_4x_7x_8 \oplus x_1x_5x_6x_7 \oplus x_1x_5x_6x_8 \oplus x_1x_6x_7x_8 \oplus x_2x_3x_4x_5 \oplus x_2x_3x_5x_8 \oplus x_2x_4x_5x_8 \oplus x_3x_5x_8 \oplus x_3x_5x$  $x_2x_4x_6x_7 \oplus x_2x_4x_6x_8 \oplus x_2x_5x_6x_8 \oplus x_2x_5x_7x_8 \oplus x_3x_4x_6x_7 \oplus x_3x_5x_6x_7 \oplus x_3x_5x_6x_8 \oplus$  $x_3x_6x_7x_8 \oplus x_4x_5x_6x_7 \oplus x_4x_5x_7x_8 \oplus x_4x_6x_7x_8 \oplus x_5x_6x_7x_8 \oplus x_1x_2x_3x_4x_5 \oplus x_1x_2x_3x_4x_7 \oplus x_1x_2x_3x_7 \oplus x_1x_2x_3x_7 \oplus x_1x_2x_7 \oplus x_1x_2x_3x_7 \oplus x_1x_2x_7 \oplus x_1x_7 \oplus x$  $x_1x_2x_3x_5x_7 \oplus x_1x_2x_3x_5x_8 \oplus x_1x_2x_3x_6x_7 \oplus x_1x_2x_3x_7x_8 \oplus x_1x_2x_4x_5x_8 \oplus x_1x_2x_4x_6x_7 \oplus x_1x_2x_4x_7 \oplus x_1x_2x_7 \oplus x_1x_2x_7 \oplus x_1x_2x_7 \oplus x_1x_7 \oplus x_1x$  $x_2x_3x_4x_5x_8 \oplus x_2x_3x_4x_6x_7 \oplus x_2x_3x_4x_7x_8 \oplus x_2x_3x_5x_6x_7 \oplus x_2x_4x_5x_6x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7x_8 \oplus x_2x_4x_6x_7 \oplus x_2x_4x_7 \oplus x_2x_4x_6x_7 \oplus x_2x_4x_7 \oplus x_2x_7 \oplus x_7 \oplus x$  $x_2x_5x_6x_7x_8 \oplus x_3x_4x_5x_6x_8 \oplus x_3x_4x_5x_7x_8 \oplus x_4x_5x_6x_7x_8 \oplus x_1x_2x_3x_4x_5x_7 \oplus x_1x_2x_3x_4x_6x_8$  $x_1x_2x_3x_4x_5x_7x_8$

Figure 3.2: Algebraic normal form of the first coordinate function of the AES s-box

Thus, the system of equations obtained in this step can be linearlized by introducing new variables as illustrated by the following toy example.

**Example 3.1** Suppose we would like to find the Boolean variable assignment that satisfies the following formula

$$x_0 \oplus x_1 x_2 \oplus x_0 x_1 x_2 = 0$$

Using the approach illustrated in (2.1), we introduce two linearization variables,  $T_0 = x_1x_2$  and  $T_1 = x_0x_1x_2$ . Thus we have

$$x_{0} \oplus T_{0} \oplus T_{1} = 0,$$

$$(\overline{T}_{0} \vee x_{1}) \wedge (\overline{T}_{0} \vee x_{2}) \wedge (T_{0} \vee \overline{x}_{1} \vee \overline{x}_{2}) = 1,$$

$$(\overline{T}_{1} \vee x_{0}) \wedge (\overline{T}_{1} \vee x_{1}) \wedge (\overline{T}_{1} \vee x_{2}) \wedge$$

$$(T_{1} \vee \overline{x}_{0} \vee \overline{x}_{1} \vee \overline{x}_{2}) = 1.$$

$$(3.2)$$

Since the CryptoMinSAT expects only positive clauses and the CNF form does not have any constants, we need to overcome the problem that the first line in Equation (3.2) corresponds to a negative, i.e., false, clause. Adding the clause consisting of a dummy variable, d, or equivalently  $(d \land d \cdots \land d)$  would require the variable d to be true in any satisfying solution, since all clauses must be true in any satisfying solution. In other words, the variable d will serve the place of the constant 1. Therefore, the above formula can be reexpressed as

$$d = 1,$$

$$x_0 \oplus T_0 \oplus T_1 \oplus d = 1,$$

$$(\overline{T}_0 \vee x_1) \wedge (\overline{T}_0 \vee x_2) \wedge (T_0 \vee \overline{x}_1 \vee \overline{x}_2) = 1,$$

$$(\overline{T}_1 \vee x_0) \wedge (\overline{T}_1 \vee x_1) \wedge (\overline{T}_1 \vee x_2) \wedge$$

$$(T_1 \vee \overline{x}_0 \vee \overline{x}_1 \vee \overline{x}_2) = 1.$$

Table 3.1 shows the CryptoMiniSat input corresponding to Example 3.1.

In our AES-128 key schedule system, each s-box can be represented by 8 XOR equations corresponding to its 8 Boolean coordinates; and 246 CNF equations corresponding to 246 linearization variables. The total number of clauses corresponding to these CNF equations is equal to 1254. Since, each round in the AES-128 key schedule involves four s-box look-up operations and 96 linear XOR equations (line 3 in Equation (3.1)), then the total number of clauses (including XOR clauses) in each round is equal to  $4 \times (1254 + 8) + 96 = 5144$ . Thus, for the complete 10 rounds key schedule, we have  $10 \times 5144$  clauses +1 dummy variable to present the

Table 3.1: CryptoMinSAT input corresponding to Example 3.1

```

c Lines starting with 'c' are comments

c The first line in the SAT file is in the form:

c 'p cnf # variables # clauses'

c Each line should end with '0'

c Lines starting with 'x' denote XOR equations

c True variables are denoted by numbers

c False variables are denoted by negating these numbers

c In this example, d \to 1, x_0 \to 2 (consequently \overline{x}_0 \to -2)

c x_1 \to 3, x_2 \to 4, T_0 \to 5, T_1 \to 6

p cnf 6 9

0

1

2

5

1 0

6

-5

3

0

-5

4

0

5

-3

-4

0

-6

2

0

-6

3

0

4

-6

0

6

-2

-3

-4 0

```

constant 1.

# 3.5 Experimental results

Similar to the previous work in [72,184], throughout our experimental results, we assume an asymmetric decay model where bits overwhelmingly decay to their ground state rather than their charged state. Using this model, only the bits that remain in their charged state will be useful to the cryptanalyst since one cannot be sure about the original values of the 0 bits, i.e., whether they were originally 0s or decayed 1s. Let  $\beta$  denote the fraction of decayed bits. If the percentage of 0s and 1s in the original key schedule bits is  $p_z$  and  $1 - p_z$ , respectively, then the fraction, f, of key bits that can be assumed to be known by examining the decayed memory of the AES key schedule is given by

$$f = 1 - (p_z + \beta \times (1 - p_z)) = (1 - p_z) \times (1 - \beta).$$

Since in an uncorrupted AES key schedule, we expect the number of 0s and 1s to be approximately equal, i.e.,  $p_z \approx 1/2$ , then we have  $f \approx (1 - \beta)/2$ .

Table 3.2 shows a comparison between our work and the results reported in [184] which recover the AES-128 key schedule from its decayed memory images for a decay factor up to 70%. In this table, for our work, all statistics were generated using 10,000 runs for each decay factor.