# HIGH-SPEED PIPELINE VLSI ARCHITECTURES FOR DISCRETE WAVELET TRANSFORMS

**CHENG JUN ZHANG**

A THESIS

IN

THE DEPARTMENT

OF

ELECTRICAL AND COMPUTER ENGINEERING

PRESENTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

CONCORDIA UNIVERSITY

MONTRÉAL, QUÉBEC, CANADA

MARCH 2012

© CHENG JUN ZHANG, 2012

## CONCORDIA UNIVERSITY

## SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

Cheng Jun Zhang

By:

| Entir<br>Tran | tled:<br>asforms | High-Speed                          | Pipeline    | VLSI     | Architectures                | for    | Discrete    | Wavelet   |

|---------------|------------------|-------------------------------------|-------------|----------|------------------------------|--------|-------------|-----------|

| and           | submitted        | in partial fulfil                   | lment of th | e requir | ements for the d             | egree  | of          |           |

|               | DO               | CTOR OF PHI                         | LOSOPHY     | (Elect   | rical & Comput               | er En  | gineering)  |           |

|               | •                | the regulations<br>sinality and qua |             | versity  | and meets the ac             | cepte  | ed standard | s with    |

| Sign          | ed by the        | final examining                     | g committe  | e:       |                              |        |             |           |

|               | Dr N             | J. Bhuiyan                          |             |          |                              | _Ch    | air         |           |

|               |                  |                                     |             |          |                              | _Ex    | ternal Exa  | miner     |

|               | Dr. P            | .K. Meher                           |             |          |                              |        |             |           |

|               | Dr. C            | .Y. Su                              |             |          |                              | _Ex    | ternal to P | rogram    |

|               |                  |                                     |             |          |                              | _Ex    | aminer      |           |

|               | Dr. M            | I.N.S. Swamy                        |             |          |                              |        |             |           |

|               | Dr. W            | V-P. Zhu                            |             |          |                              | _Ex    | aminer      |           |

|               | - I              | K O A1 1                            |             |          |                              | _ Th   | esis Co-Sı  | ıpervisor |

|               | Dr. M            | I.O. Ahmad                          |             |          |                              |        |             |           |

|               | Dr. C            | . Wang                              |             |          |                              | _ Th   | esis Co-Sı  | ıpervisor |

| Approved b    | ру               |                                     |             |          |                              |        |             |           |

|               |                  | Dr. J                               | I.X. Zhang  | g, Gradı | ıate Program I               | Direct | tor         |           |

| April 5, 201  | 12               |                                     | D. D.       | 1        | D D                          |        |             |           |

|               |                  |                                     |             |          | L. Drew, Dean gineering & Co | mpu    | ter Scienc  | e         |

|               |                  |                                     | Faculty     | y of Eng | gineering & Co               | mpu    | ter Scienc  | e         |

## **ABSTRACT**

# High-Speed Pipeline VLSI Architectures for Discrete Wavelet Transforms

Cheng Jun Zhang, Ph.D.

Concordia University, 2012

The discrete wavelet transform (DWT) has been widely used in many fields, such as image compression, speech analysis and pattern recognition, because of its capability of decomposing a signal at multiple resolution levels. Due to the intensive computations involved with this transform, the design of efficient VLSI architectures for a fast computation of the transforms have become essential, especially for real-time applications and those requiring processing of high-speed data. The objective of this thesis is to develop a scheme for the design of hardware resource-efficient high-speed pipeline architectures for the computation of the DWT. The goal of high speed is achieved by maximizing the operating frequency and minimizing the number of clock cycles required for the DWT computation with little or no overhead on the hardware resources. In this thesis, an attempt is made to reach this goal by enhancing the interstage and intra-stage parallelisms through a systematic exploitation of the characteristics inherent in discrete wavelet transforms.

In order to enhance the inter-stage parallelism, a study is undertaken for determining the number of pipeline stages required for the DWT computation so as to synchronize their operations and utilize their hardware resources efficiently. This is achieved by optimally distributing the computational load associated with the various resolution levels to an optimum number of stages of the pipeline. This study has determined that employment of two pipeline stages with the first one performing the task of the first

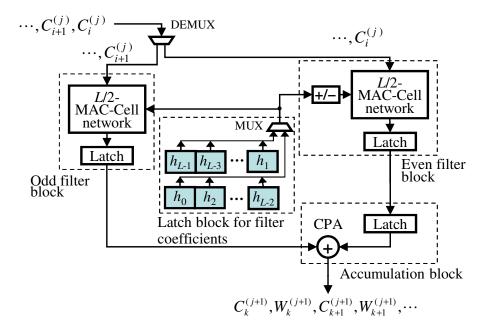

resolution level and the second one that of all the other resolution levels of the 1-D DWT computation, and employment of three pipeline stages with the first and second ones performing the tasks of the first and second resolution levels and the third one performing that of the remaining resolution levels of the 2-D DWT computation, are the optimum choices for the development of 1-D and 2-D pipeline architectures, respectively. The enhancement of the intra-stage parallelism is based on two main ideas. The first idea, which stems from the fact that in each consecutive resolution level the input data are decimated by a factor of two along each dimension, is to decompose the filtering operation into subtasks that can be performed in parallel by operating on even- and odd-numbered samples along each dimension of the data. It is shown that each subtask, which is essentially a set of multiply-accumulate operations, can be performed by employing a MAC-cell network consisting of a two-dimensional array of bit-wise adders. The second idea in enhancing the intra-stage parallelism is to maximally extend the bit-wise addition operations of this network horizontally through a suitable arrangement of bit-wise adders so as to minimize the delay of its critical path.

In order to validate the proposed scheme, design and implementation of two specific examples of pipeline architectures for the 1-D and 2-D DWT computations are considered. The simulation results show that the pipeline architectures designed using the proposed scheme are able to operate at high clock frequencies, and their performances, in terms of the processing speed and area-time product, are superior to those of the architectures designed based on other schemes and utilizing similar or higher amount of hardware resources. Finally, the two pipeline architectures designed using the proposed scheme are implemented in FPGA. The test results of the FPGA implementations validate the feasibility and effectiveness of the proposed scheme for designing DWT pipeline architectures.

## **ACKNOWLEDGEMENTS**

I would like to take this opportunity to express my deep gratitude to my supervisors, Dr. M. Omair Ahmad, and Dr. Chunyan Wang, for their support, encouragement, and invaluable guidance during this research. I am grateful to them for providing me freedom and motivation to explore new ideas in this research. I also thank them for spending countless long hours discussing the research in this thesis, and correcting and improving the writing of this thesis. The useful suggestions and comments provided by the members of the supervisory committee, Dr. M.N.S. Swamy, Dr. Weiping Zhu, and Dr. Chunyi Su, and by the External Examiner, Dr. Pramod K. Meher, as well as those of the anonymous reviewers of my journal papers, are deeply appreciated.

I would like to acknowledge the financial support provided by Concordia University and the Natural Sciences and Engineering Research Council (NSERC) of Canada, which were crucial to completing this research.

## **Table of Contents**

| List of Fig | ures   |                                             | ix   |  |

|-------------|--------|---------------------------------------------|------|--|

| List of Tal | oles   |                                             | xii  |  |

| List of Acr | onyms  |                                             | xiii |  |

| List of Syn | nbols  |                                             | XV   |  |

| Chapter 1   | Introd | duction                                     | 1    |  |

| 1.1         | Backg  | ground                                      | 1    |  |

| 1.2         | Motiva | ation                                       | 3    |  |

| 1.3         | Scope  | of the Thesis                               | 4    |  |

| 1.4         | Organi | Organization of the Thesis                  |      |  |

| Chapter 2   | Backg  | ground Material and Related Previous Work   | 7    |  |

| 2.1         | Funda  | mentals of the Discrete Wavelet Transform   | 7    |  |

|             | 2.1.1  | Definitions of Wavelet Transforms           | 7    |  |

|             | 2.1.2  | Mathematical Formulations                   | 9    |  |

|             | 2.1.3  | Computations of Discrete Wavelet Transforms | 13   |  |

| 2.2         | Reviev | w of the Architectures                      | 17   |  |

|             | 2.2.1  | Categorization of the Architectures         | 17   |  |

|             | 2.2.2  | Architectures for 1-D DWT Computation       | 20   |  |

|             | 2.2.3  | Architectures for 2-D DWT Computation       | 26   |  |

| 2.3         | Summ   | nary                                        | 33   |  |

| Chapter 3 | A Scheme for the Design of Pipeline Architectures for 1-D Discrete |                                                          |       |  |  |

|-----------|--------------------------------------------------------------------|----------------------------------------------------------|-------|--|--|

|           | Wavel                                                              | et Transform                                             | 34    |  |  |

| 3.1       | Formu                                                              | lation of the 1-D DWT Computation                        | 35    |  |  |

|           | 3.1.1                                                              | Matrix Formulation                                       | 35    |  |  |

|           | 3.1.2                                                              | Reformulation of (3.2)                                   | 38    |  |  |

| 3.2       | Choice                                                             | e of a Pipeline for the 1-D DWT Computation              | 39    |  |  |

| 3.3       | Design                                                             | of the Architecture                                      | 43    |  |  |

|           | 3.3.1                                                              | Synchronization of Stages                                | 43    |  |  |

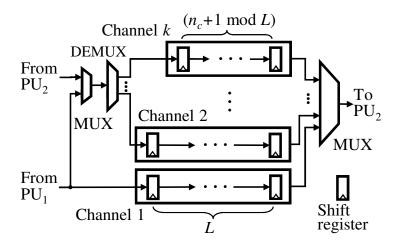

|           | 3.3.2                                                              | Design of Stages                                         | 51    |  |  |

|           | 3.3.3                                                              | Design of L/2-MAC-cell Network                           | 54    |  |  |

| 3.4       | Perfori                                                            | mance Evaluation and FPGA Implementation                 | 60    |  |  |

| 3.5       | Summ                                                               | ary                                                      | 68    |  |  |

| Chapter 4 | A Scho                                                             | eme for the Design of Pipeline Architectures for 2-D Dis | crete |  |  |

|           | Wavel                                                              | et Transform                                             | 70    |  |  |

| 4.1       | Formu                                                              | lations for the Computation of the 2-D DWT               | 71    |  |  |

|           | 4.1.1                                                              | Formulation for the Computation of Four Subbands         | 72    |  |  |

|           | 4.1.2                                                              | Formulation for a Four-Channel Filtering Operation       | 73    |  |  |

| 4.2       | Pipelin                                                            | ne for the 2-D DWT Computation                           | 75    |  |  |

| 4.3       | Design                                                             | of the Architecture                                      | 79    |  |  |

|           | 4.3.1                                                              | Synchronization of Stages                                | 80    |  |  |

|           | 4.3.2                                                              | Design of Stages                                         | 83    |  |  |

| 4.4       | Perfori                                                            | mance Results and Comparisons                            | 92    |  |  |

|           | 4.4.1                                                              | Performance of the Proposed Architecture                 | 92    |  |  |

|           | 4.4.2                                                              | Comparisons of Various 2-D Architectures                 | 96    |  |  |

| 4.5       | Summ                                                               | ary                                                      | 100   |  |  |

| Chapter 5  | Conclusion            | 102   |

|------------|-----------------------|-------|

| 5.1        | Concluding Remarks    | . 102 |

| 5.2        | Scope for Future Work | . 105 |

| References |                       | 107   |

## **List of Figures**

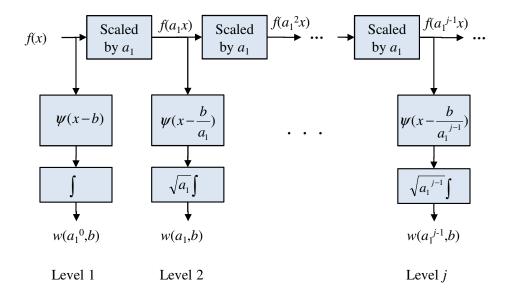

| Figure 2.1:  | Hierarchical structure for the decomposition of a signal $f(x)$ into multiple resolution levels of the wavelet transform.                                              | 9    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

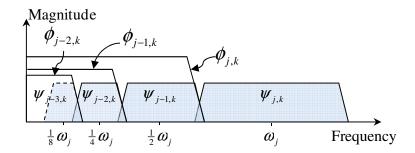

| Figure 2.2:  | Frequency bands covered by the scaling and wavelet functions                                                                                                           | . 11 |

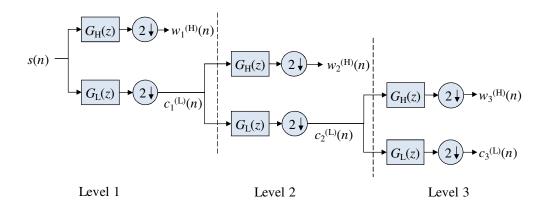

| Figure 2.3:  | Binary tree representation of a 3-level 1-D DWT decomposition                                                                                                          | . 14 |

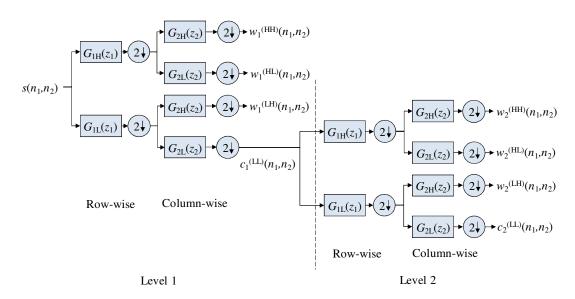

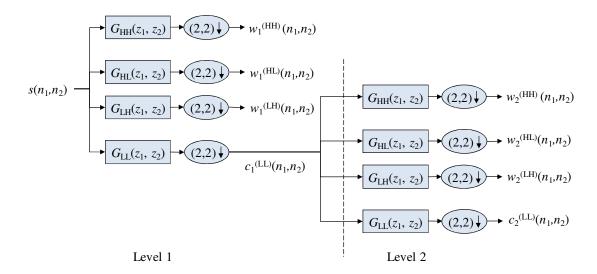

| Figure 2.4:  | Binary tree representation of the computation of a 2-level 2-D DWT based on separable approach.                                                                        | . 15 |

| Figure 2.5:  | Representation of the computation of a 2-level 2-D DWT based on non-separable approach.                                                                                | . 16 |

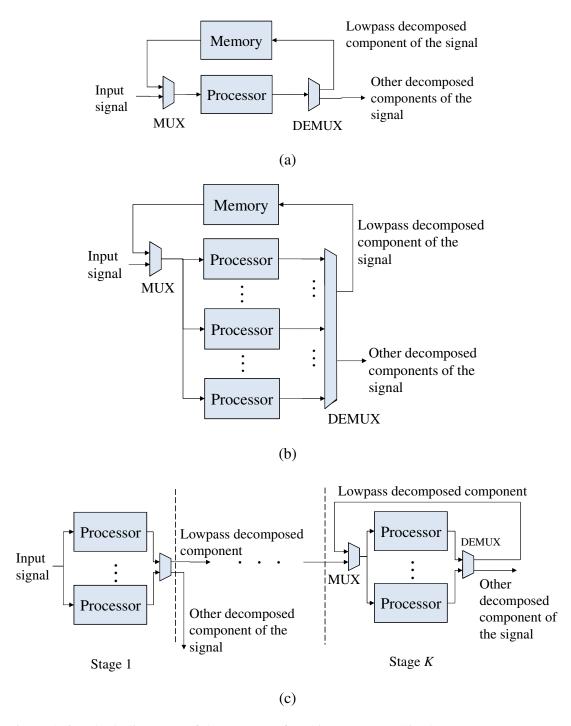

| Figure 2.6:  | Block diagrams of three types of architectures                                                                                                                         | . 19 |

| Figure 2.7:  | An architecture using one multiplier and one adder [42]                                                                                                                | . 20 |

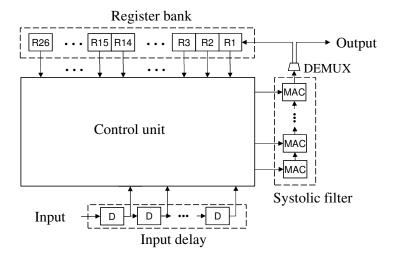

| Figure 2.8:  | An architecture using a processor employing a systolic array of MAC cells [43].                                                                                        | . 21 |

| Figure 2.9:  | A lifting-based architecture using Daub-4 filters. $R_j$ and $D_j$ represent, respectively, the registers and delay units for the computation of the $j$ th level [44] | . 21 |

| Figure 2.10: | A parallel architecture proposed by Chakrabarti and Vishwanath [53]                                                                                                    | . 22 |

| Figure 2.11: | A folded architecture proposed by Parhi and Nishitani [54] using 4-tap filter.                                                                                         | . 22 |

| Figure 2.12: | An architecture proposed by Masud and McCanny [55]                                                                                                                     | . 23 |

| Figure 2.13: | A pipeline architecture proposed by Marino et al. [61]                                                                                                                 | . 24 |

| Figure 2.14: | A scalable 3-stage architecture proposed by Park [62]                                                                                                                  | . 25 |

| Figure 2.15: | A lifting-scheme based pipeline architecture [63].                                                         | 25 |

|--------------|------------------------------------------------------------------------------------------------------------|----|

| Figure 2.16: | A single-processor architecture for the 2-D DWT computation [49]                                           | 27 |

| Figure 2.17: | An architecture proposed by Uzun and Amira [50] for the 2-D DWT computation using 9/7-tap filters          | 27 |

| Figure 2.18: | An architecture proposed by Meher <i>et al.</i> [51] for the 2-D DWT computation using separable approach  | 28 |

| Figure 2.19: | A 2-D DWT architecture proposed by Chakrabarti and Mumford [57]                                            | 29 |

| Figure 2.20: | A parallel-processor architecture proposed by Wu and Chen [58] for the 2-D DWT computation.                | 30 |

| Figure 2.21: | A pipeline architecture proposed by Jou <i>et al.</i> [64] for the 2-D DWT computation.                    | 31 |

| Figure 2.22: | An architecture using a pipeline of 2 <i>J</i> stages [65].                                                | 32 |

| Figure 2.23: | A two-stage pipeline architecture proposed by Marino [66]                                                  | 32 |

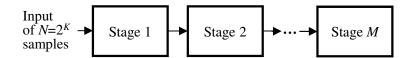

| Figure 3.1:  | Stage-equalized pipeline structure                                                                         | 40 |

| Figure 3.2:  | A one-to-one mapped pipeline structure with <i>I</i> ( <i>I</i> < <i>K</i> ) stages                        | 41 |

| Figure 3.3:  | Pipeline structure with two stages.                                                                        | 42 |

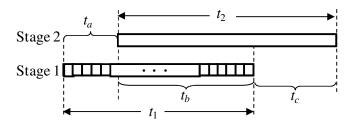

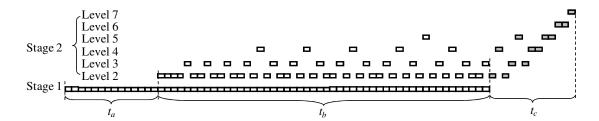

| Figure 3.4:  | Timing diagram for the operations of two stages                                                            | 44 |

| Figure 3.5:  | Synchronization scheme for a 128-point ( $J$ =7) DWT computation using length-4 ( $L$ =4) FIR filter.      | 49 |

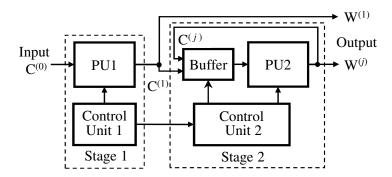

| Figure 3.6:  | Block diagram of the two-stage architecture                                                                | 51 |

| Figure 3.7:  | Block diagram of the processing unit for $L$ -tap filtering computation assuming $L$ to be an even number. | 53 |

| Figure 3.8:  | Structure of the buffer.                                                                                   | 54 |

| Figure 3.9:  | A two-dimensional array of bit-wise additions                                                              | 57 |

| Figure 3.10: | Structure of the <i>L</i> /2-MAC-cell network.                                                             | 60 |

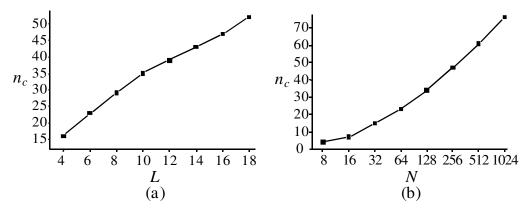

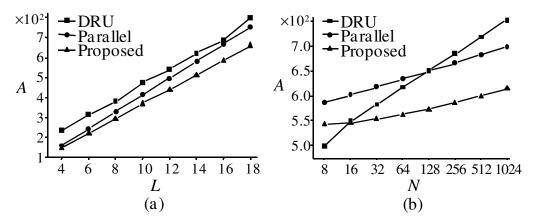

| Figure 3.11: | Estimated values of $n_c$ .                                                                                | 63 |

| Figure 3.12: | Estimated areas of the three architectures.                                                                       | . 63 |

|--------------|-------------------------------------------------------------------------------------------------------------------|------|

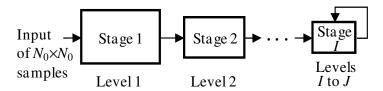

| Figure 4.1:  | Pipeline structure with I stages for J-level computation.                                                         | . 78 |

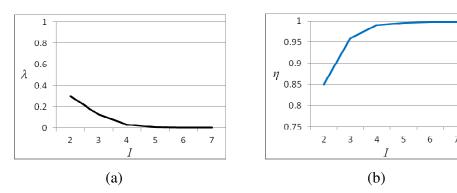

| Figure 4.2:  | Parameters $\lambda$ and $\eta$ plotted as functions of the number of stages $I$ used in a pipeline architecture. | . 79 |

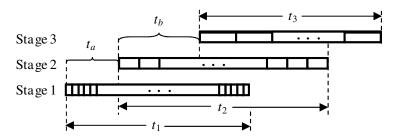

| Figure 4.3:  | Timing diagram for the operations of three stages.                                                                | . 81 |

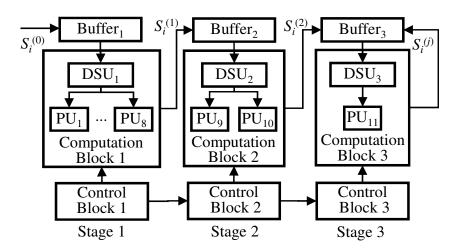

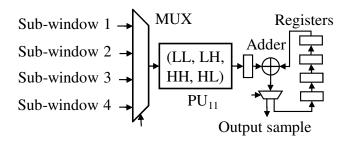

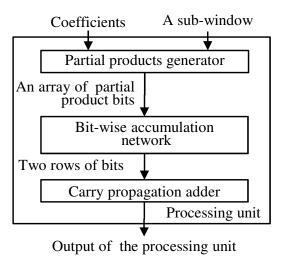

| Figure 4.4:  | Block diagram of the three-stage architecture                                                                     | . 84 |

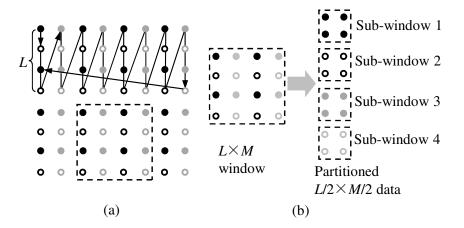

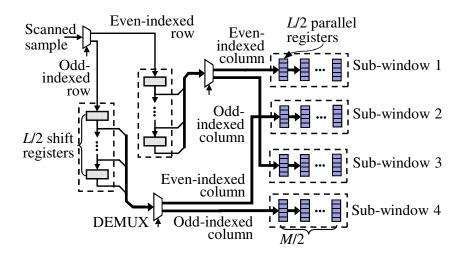

| Figure 4.5:  | Diagram illustrating the data scanning                                                                            | . 85 |

| Figure 4.6:  | Structure of the data scanning unit (DSU).                                                                        | . 86 |

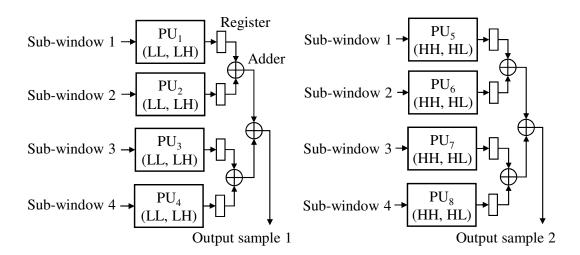

| Figure 4.7:  | Structure of eight processing units employed by stage 1                                                           | . 87 |

| Figure 4.8:  | Structure of two processing units employed by stage 2.                                                            | . 88 |

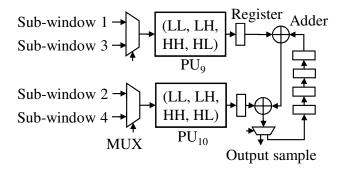

| Figure 4.9:  | Structure of one processing unit employed by stage 3                                                              | . 89 |

| Figure 4.10: | Block diagram of a processing unit.                                                                               | . 91 |

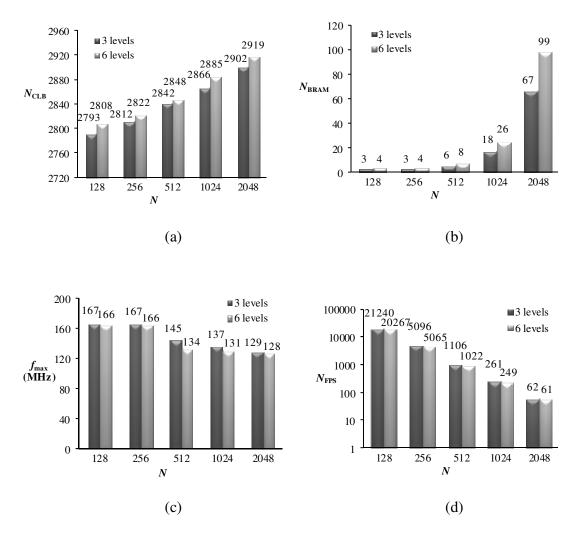

| Figure 4.11: | Results of various FPGA implementations with <i>N</i> =128, 256, 512, 1024,                                       |      |

|              | 2048, and <i>J</i> =3, 6                                                                                          | . 95 |

## **List of Tables**

| Table 3.1: | Indices and numbers of samples computed in time $t_c$                    | 45 |

|------------|--------------------------------------------------------------------------|----|

| Table 3.2: | Comparison of various architectures                                      | 61 |

| Table 3.3: | Evaluation of various architectures                                      | 65 |

| Table 3.4: | Resources used in FPGA devices                                           | 67 |

| Table 3.5: | FPGA implementation results for various 1-D architectures                | 67 |

| Table 4.1: | Performance metrics for the proposed 2-D architecture                    | 92 |

| Table 4.2: | Resources utilized in FPGA device for the circuit implementation for the |    |

|            | 2-D DWT computation when $N=512$ , $L=M=4$ and $J=6$                     | 93 |

| Table 4.3: | Performance metrics for various 2-D architectures                        | 97 |

| Table 4.4: | Comparison of various FPGA implementations                               | 99 |

## **List of Acronyms**

1-D: One-dimensional

2-D: Two-dimensional

BRAM: Block random access memory

CLB: Configuration logic block

CPA: Carry propagation adder

CWT: Continuous wavelet transform

DFF: D-type flip-flop

DRU: Data recorder unit

DSP: Digital signal processing

DSU: Data scanning unit

DWT: Discrete wavelet transform

FIR: Finite impulse response

FPGA: Field programmable gate array

FPS: Frames per second

HH: Highpass-highpass

HL: Highpass-lowpass

IOB: Input/output block

LH: Lowpass-highpass

LL: Lowpass-lowpass

LUT: Look-up table

MAC: Multiply-accumulate

MBPS: Megabytes per second

N/A: Not available

PU: Processing unit

RPA: Recursive pyramid algorithm

SIMD: Single instruction multiple data

VLSI: Very large scale integration

## **List of Symbols**

*a* : Dilation parameter

A: Area

$A_{I}$ : An array of input bits to a layer of MAC-cell network

$A_0$ : An array of output bits from a layer of MAC-cell network

A(m,n): Highpass-highpass subband sample with index (m, n)

*b* : Translation parameter

B(m,n): Highpass-lowpass subband sample with index (m, n)

c(i): Transformed scaling coefficients

D(m,n): Lowpass-highpass subband sample with index (m, n)

$f_{\text{max}}$ : Maximum operational clock frequency

f(.): Function representing an input signal

G(z): Impulse response of a filter

**G**: Transform matrix representing a highpass filtering operation

$g_i$ : The *i*th coefficient of a highpass filter

**H**: Transform matrix representing of a lowpass filtering operation

$h_i$ : The *i*th coefficient of a lowpass filter

$H^{(P)}(k,i)$ : The (k,i)th coefficient of the 2-D filter P

*I*: Number of pipeline stages

*J*: Largest resolution level

*j* : Index of resolution levels

L: Length of filter

$L^2(R)$ : Hilbert space

M: Length of filter

$n_x$ : Number of samples computed in time span  $t_x(x=b \text{ or } c)$

*N*: Number of input samples along one dimension

$N_{ADD}$ : Number of adders

$N_{CLK}$ : Number of clock cycles

$N_i$ : Number of samples at the *j*th resolution level

$N_{MUL}$ : Number of multipliers

$N_{REG}$ : Number of registers

p: Counter for samples computed at resolution level 2

q: Counter for samples computed at resolution levels higher than 2

**Q**(**z**): Transform matrix for two-channel wavelet filters

**S**: Matrix representation of an input signal

S(m,n): Lowpass-lowpass subband sample with index (m, n)

$s_i$ : The *i*th input sample

$t_a$ : Time span during which the first stage operates alone

$t_b$ : Time span during which the stages of a pipeline operate in parallel

$t_c$ : Time span during which the last stage operates alone

$t_i$ : Operating time period of the *i*th pipeline stage (i=1, 2, 3)

*T*: Computation time

$T_c$ : Clock period

$T_s$ : Average time to compute one sample by stage 1

w(i): Transformed wavelet coefficients

X: Wordlength of input samples

*Y*: Wordlength of filter coefficients

Z: Number of layers of a MAC-cell network

$\lambda$ : Parameter representing the design complexity with respect to the

synchronization of pipeline stages

$\eta$ : Parameter representing hardware utilization efficiency

$\psi$  (.) : Wavelet function

$\varphi(.)$ : Scaling function

## **Chapter 1**

## Introduction

## 1.1 Background

In recent years, the discrete wavelet transform (DWT) has been widely and increasingly used in many fields such as image compression, speech analysis and pattern recognition because of its capability of decomposing a signal at multiple resolution levels [1]–[18]. The DWT decomposes a signal into components in different octaves or frequency bands by choosing appropriate scaling and shifting factors where the small scaling factor corresponds to fine details of the signal and the large scaling factor to coarse details, and the shifting factor corresponds to the time or space localization of the signal [19]–[21]. In contrast to other transforms, such as Fourier or cosine transforms where the signals are represented in frequency domain only, the DWT decomposes a signal so that it is represented more efficiently and localized in both time (space) and frequency domains. In other words, in the DWT, the time (space) information is not lost in the transformed signal, which is very attractive for the analysis of signals, especially for signals with non-stationary or transitory characteristics [22], [23].

In accordance with the multiple-level decomposition of a signal, the computation of the DWT can be performed by repeating a process in which a fully scalable window is shifted along the dimensions of the signal with the window size becoming shorter in each repetition. The computing processes of the DWT can be carried out by executing recursively a set of instructions developed in software programs such as SimuWave in Simulink, Wavelet toolbox in MATLAB and WavBox in Toolsmiths [24]–[27]. The software implementation for the computation of the DWT is flexible in setting different values of the parameters of the transform and changing the codes for the algorithms. Regardless of the effort devoted to the design of software algorithms and optimized codes for their implementations, no general-purpose or DSP processor used for their implementation can provide a performance in terms of the computing speed and resource optimization that can possibly be achieved by a hardware implementation [28]–[33].

Hardware implementations, in which the computation of the DWT is performed by a custom hardware circuit, it is possible to address the requirements of specific applications such as the speed, power or size of the circuit. In the literature, there exist a number of design efforts on the development of architectures for the DWT computation that focus on such requirements of applications [34]–[41]. However, many applications of the DWT computation involve large-volume data such as image or video. The fact that the DWT is multiple resolution level operation adds even more to the vastness of the data to be processed, which adversely affects the requirements of speed, power and the circuit area of the architectures for such applications. Thus, it remains a challenging task to design high-speed, low-power and area-efficient VLSI architectures to implement the DWT computation for real-time applications.

## 1.2 Motivation

In the past, several types of architectures have been proposed aimed at providing high-speed computation of the DWT using resource-efficient hardware. The architectures in [42]–[51] employ a single processor to perform the computations of all the resolution levels of the DWT, mostly based on the recursive pyramid algorithm (RPA) [52]. Naturally, by using a single processor in these architectures, the computations of the various resolution levels of the DWT are performed in a sequential manner, since the computation at one resolution level requires the output data from its preceding level. Even though these architectures have low design and hardware complexities, they do not focus on providing a fast computation of the DWT. Therefore, this type of architectures is not attractive for real-time applications. In an effort to overcome the problem of slow computation, architectures that employ two or more parallel processors have been proposed [53]-[60]. In this type of architectures, the computation associated with one level is performed by more than one processor thereby increasing the overall processing speed of the DWT computation. These type architectures even though provide parallelism to the computations associated with a given resolution level, they do not have parallelism between the resolution levels. In order to further improve the parallelism for the DWT computation, and hence the computational speed, the architectures that employ a number of pipelined stages, each performing the task of one or more resolution levels of the DWT, have been proposed [61]-[67]. The focus in the design of these architectures is on introducing some parallelism in the computations associated with the multiple resolution levels of the DWT, thus aiming at providing a high throughput and overall a short computing time.

From the foregoing discussion, it is clear that pipeline architectures are well suited for the DWT computation of large-volume data. However, no systematic approach seems to exist in determining the number of stages, mapping of the resolution levels to the stages and the design of the stages themselves so as to minimize the computation time and maximize the utilization of the hardware resource of the pipeline.

## 1.3 Scope of the Thesis

The operation of discrete wavelet transform has the characteristic of getting the amount of computations in successive resolution levels reduced by a factor of two along each dimension of the signal. This thesis in conformity with this inherent feature of the DWT undertakes a study of designing fast and hardware resource-efficient pipeline architectures for the computation of the 1-D and 2-D discrete wavelet transforms. With this overall objective, the mapping of the computational tasks associated with the various resolution levels of the DWT to an optimum number of pipeline stages is first investigated, and then an efficient design of the stages are explored from the standpoint of maximizing the inter-stage and intra-stage parallelisms of the pipeline architectures with an efficient utilization of the hardware resources employed.

## 1.4 Organization of the Thesis

The thesis is organized as follows.

In Chapter 2, first, discrete mathematical models for the computation of 1-D and 2-D wavelet transforms are presented and the methods for their computation are described.

The existing architectures for the computation of these transforms are then reviewed and classified.

In Chapter 3, a study for developing a scheme aimed for the design of a resource-efficient pipeline architecture for fast computation of the 1-D DWT is undertaken. With this goal in mind, the number of stages of the pipeline is first determined so as to map the computational tasks of the various resolution levels of the DWT to the pipeline stages in a most optimal manner. The second part of this chapter then focuses on the design of the pipeline stages themselves so as to maximize the inter-stage and intra-stage parallelisms. A case study for the design and FPGA implementation of a pipeline architecture is undertaken to illustrate and validate the proposed scheme and to compare it with other existing schemes for the design of architectures for the 1-D DWT computation.

Since the complexities in two-dimensional signal processing are generally quite different from that in 1-D case and they often call for a different approach for their solutions, in Chapter 4, an investigation is undertaken for developing a scheme for a pipeline architecture for the computation of the 2-D DWT. Various components of the design of pipeline architecture are looked into with the overall goal being the same as that in the design of the 1-D DWT pipeline architectures, namely, the development of a fast resource-efficient pipeline architecture. A circuit for a 2-D DWT computation is designed, simulated and implemented in FPGA, and the simulation and implementation results are then compared with those for the existing architectures to validate the efficiency of the proposed design.

Chapter 5 concludes the thesis by summarizing the work contained therein, highlighting the contributions made, and stating the scope of some possible future work arising from the work of this thesis.

## Chapter 2

## **Background Material and Related Previous Work**

This chapter provides background material necessary for the development of the architectures of the 1-D and 2-D discrete wavelet transforms undertaken in the following chapters. First, the mathematical formulations of the 1-D and 2-D discrete wavelet transforms are presented, and methods for their computations are described. This is followed by a review of the various existing architectures, classified as single-processor, parallel-processor and pipeline architectures for the 1-D and 2-D DWT computations.

## 2.1 Fundamentals of the Discrete Wavelet Transform

#### 2.1.1 Definitions of Wavelet Transforms

The wavelet transform was first introduced by Jean Morlet in 1981 [68]. The continuous wavelet transform (CWT) of a signal  $f(x) \in \mathbf{L}^2(R)$  (Hilbert space) is an integral operation defined as

$$w(a,b) = \frac{1}{\sqrt{a}} \int_{-\infty}^{+\infty} f(x) \psi(\frac{x-b}{a}) dx$$

(2.1)

where w(a,b) are the wavelet coefficients,  $\psi(\frac{x-b}{a})$  are the wavelets generated by a basic wavelet function  $\psi(x) \in \mathbf{L}^2(R)$ , the so-called the *mother wavelet*, a is the dilation parameter that scales the wavelet function by compressing or stretching it, and b is the translation parameter that locates the position of the wavelet function by shifting it. It is seen from this definition that the wavelet transform is a linear operation. By changing the variable x = ax' and expressing the dilation parameter as  $a = a_1^{v_j}$ , where  $a_1$  and  $v_j$  (j=1, 2, 3, ...) are real numbers, (2.1) becomes

$$w(a_1^{\nu_j}, b) = \sqrt{a_1^{\nu_j}} \int_{-\infty}^{+\infty} f(a_1^{\nu_j} x') \psi(x' - \frac{b}{a_1^{\nu_j}}) dx'$$

(2.2)

Therefore, the wavelet transform can be seen as a decomposition of the signal f(x) into a number of resolution levels with  $j=1,2,3,\cdots$ . Fig. 2.1 shows a hierarchical structure for the decomposition of a signal f(x) into multiple resolution levels of the wavelet transform. It is seen from this figure that, in order to obtain the wavelet coefficients  $w(a_1^{v_j},b)$  of a certain resolution level j, the signal f(x) is first scaled by a factor of  $a_1^{v_j}$ , and then integrated with a dilated and translated wavelet function  $\psi(x-\frac{b}{a_1^{v_j}})$  followed by a multiplication by the magnitude factor  $\sqrt{a_1^{v_j}}$ . It is also seen from this figure that the wavelet transform is very suitable for analyzing the hierarchical structure of the function f(x) because of its mathematical microscopic property that allows a signal to be represented by a number of functions with automatic scalability [69].

Figure 2.1: Hierarchical structure for the decomposition of a signal f(x) into multiple resolution levels of the wavelet transform.

#### 2.1.2 Mathematical Formulations

#### (a) Expression for the 1-D DWT

According to (2.1), continuous wavelet transform may use an infinite number of wavelets  $\psi(\frac{x-b}{a})$ . Thus, it is not practical in analysis of a signal due to the redundant calculation resulting from the dilation and translation parameters [70]. Discrete wavelets are introduced to address this problem. Discrete wavelets are not continuously scalable and translatable, but can be scaled and translated in discrete steps as denoted by

$$\psi_{j,k}(x) = a_0^{j/2} \psi \left( a_0^{j} x - k b_0 \right)$$

(2.3)

where  $a_0$  and  $b_0$  are scale and translation factors, respectively, and k and the scale index j are two integers. Generally, the value of the scale factor  $a_0$  is chosen as two so as to achieve a dyadic sampling along the frequency axis, and the translation factor  $b_0$  has a

value of unity so as to achieve a dyadic sampling along the time axis. Note that the function  $\psi_{j,k}(x)$  has fine scale or high frequency when the scale index j becomes large. Discrete wavelets are still continuous functions of x but discretized in the time-scale space. The discrete form of the wavelet transform can now be formulated as

$$w(j,k) = \int_{-\infty}^{+\infty} f(x) \psi_{j,k}(x) dx$$

(2.4)

A dilation of wavelet functions by a factor of two in the time domain leads to a reduction of their frequency by one-half. Since the wavelet functions have a feature of a band-pass filter, in order to cover the entire frequency band down to zero when decomposing a signal, an infinite number of levels would be required. To solve this problem, a scaling function  $\phi(x)$ , also called the *father wavelet*, was introduced by Mallat in 1989 [71]. The scaling function  $\phi(x)$  has a feature of a lowpass filter, and must satisfy the two-scale dilation property given by

$$\phi(x) = \sqrt{2} \sum_{k} h(k) \phi(2x - k)$$

(2.5)

$$\psi(x) = \sqrt{2} \sum_{k} g(k) \phi(2x - k)$$

(2.6)

where h(k) and g(k) are the coefficients of two digital filters. If functions  $\phi_{j,k}(x) = 2^{j/2}\phi(2^jx - k)$  and  $\psi_{j,k}$  are orthogonal, the coefficients h(k) and g(k) are the inner products  $\langle \phi_{0,0}, \phi_{-1,k} \rangle$  and  $\langle \psi_{0,0}, \phi_{-1,k} \rangle$ , respectively.

Since the scaling function has the feature of a lowpass filter, it sets a low bound on frequency for the decomposition of a signal. For the decomposition of any given scale index j, the scaling functions  $\phi_{j,k}$  and wavelet functions  $\psi_{j,k}$  share the entire frequency band, and only the frequency band of the scaling functions  $\phi_{j,k}$  will be covered by further

decompositions of the scale index j-1, as shown in Fig. 2.2 [72]. Therefore, by combining the scaling and wavelet functions, the entire frequency band is covered with a limited number of resolution levels.

Figure 2.2: Frequency bands covered by the scaling and wavelet functions.

Due to the dilation property of the scaling and wavelet functions and their relations given by (2.5) and (2.6), for any scale index j, a signal f(x) can always be expanded in terms of the scaled and translated wavelet and scaling functions,  $\psi(2^j x - k)$  and  $\phi(2^j x - k)$ , as

$$f(x) = \sum_{k} c(j,k)\phi(2^{j}x - k) + \sum_{k} w(j,k)\psi(2^{j}x - k)$$

(2.7)

where c(j,k) and w(j,k) are, respectively, the scaling and wavelet coefficients associated with a scale index j. In order to obtain the coefficients c(j,k) and w(j,k), we need to compute the inner products  $\langle f(x), \phi(2^j x - k) \rangle$  and  $\langle f(x), \psi(2^j x - k) \rangle$ , respectively. Using (2.4)–(2.7) and after some manipulation, we can obtain the coefficients, c(j,k) and w(j,k), as

$$c(j,k) = \sum_{m} h(m-2k)c(j+1,m)$$

(2.8)

$$w(j,k) = \sum_{m} g(m-2k)c(j+1,m)$$

(2.9)

It is seen from the above two equations that the wavelet or scaling coefficients at a resolution level with the scale index j are formulated as a convolution of the coefficients of a digital filter and the scaling coefficients at the resolution level with the scale index (j+1).

#### (b) Expression for the 2-D DWT

In order to decompose a 2-D signal, the 1-D scaling and wavelet functions have to be extended to two dimensions. A 2-D function can be obtained simply by multiplying two 1-D functions along x and y directions, respectively. Thus, the 2-D scaling function can be generated from the 1-D scaling functions, as

$$\phi(x, y) = \phi(x)\phi(y) \tag{2.10}$$

Using (2.10) in the manner similar to that for obtaining (2.8), the 2-D scaling coefficients associated with the scale index j for the 2-D DWT can be obtained as

$$c(j, k_x, k_y) = \sum_{m_x} \sum_{m_y} h(m_y - 2k_y) h(m_x - 2k_x) c(j + 1, m_x, m_y)$$

(2.11)

Similar to (2.10), three types of 2-D wavelet functions, namely, vertical wavelet  $\psi^{(v)}(x)$ , horizontal wavelet  $\psi^{(h)}(x)$ , and diagonal wavelet  $\psi^{(d)}(x)$ , can be obtained using the 1-D scaling and wavelet functions as

$$\psi^{(v)}(x, y) = \phi(x)\psi(y)$$

(2.12)

$$\psi^{(h)}(x,y) = \psi(x)\phi(y) \tag{2.13}$$

$$\psi^{(d)}(x, y) = \psi(x)\psi(y) \tag{2.14}$$

which lead to three types of wavelet coefficients given by

$$w^{(v)}(j,k_x,k_y) = \sum_{m_x} \sum_{m_y} g(m_y - 2k_y) h(m_x - 2k_x) c(j+1,m_x,m_y)$$

(2.15)

$$w^{(h)}(j,k_x,k_y) = \sum_{m_x} \sum_{m_y} h(m_y - 2k_y) g(m_x - 2k_x) c(j+1,m_x,m_y)$$

(2.16)

$$w^{(d)}(j,k_x,k_y) = \sum_{m_x} \sum_{m_y} g(m_y - 2k_y) g(m_x - 2k_x) c(j+1,m_x,m_y)$$

(2.17)

It is seen from (2.11) and (2.15)–(2.17) that four components of the 2-D DWT at the resolution level with a scale index j are produced using the scaling coefficients at the level with a scale index (j+1). It should be noted that if the 2-D scaling and wavelet functions used in the 2-D DWT are non-separable in terms of x and y, the product of two 1-D filter coefficients in the right side of (2.11) and (2.15)–(2.17) will be replaced by a 2-D filter coefficient.

## 2.1.3 Computations of Discrete Wavelet Transforms

#### (a) Computation of the 1-D DWT

According to (2.8) and (2.9), the method for computing the 1-D DWT can be viewed as a sequence of operations along a binary tree consisting of a set of two-channel filter banks [73]. Fig. 2.3 shows an example of a binary tree for a 3-level DWT computation of 1-D signal s(n). It is seen from this figure that the decomposition at any level of the DWT is computed by using a two-channel filter bank consisting of one highpass filter  $G_H(z)$  and one lowpass filter  $G_L(z)$ , followed by a decimation operation by a factor of two in each channel. For a given resolution level j (j=1, 2, 3), the output samples of the two channels consist of a lowpass component  $c_j^{(L)}(n)$  and a highpass component  $w_j^{(H)}(n)$ , of which only the component  $c_j^{(L)}(n)$  is used as input for the decomposition at the next level j+1. The computation for the resolution level j has a complexity of  $O(N_0L/2^{j-1})$ , where  $N_0$  and L are, respectively, the number of samples of the input signal s(n) and the length of

each of the two filters. It should be noted that as the resolution level j increases, the dilation parameter of the wavelets associated with the resolution level j becomes smaller and smaller, which results in representing the signal by functions having a coarser scale.

Figure 2.3: Binary tree representation of a 3-level 1-D DWT decomposition.

#### (b) Computation of the 2-D DWT

The computation of the 2-D DWT is more involved than that of the 1-D DWT, both in terms of the amount of processing as well as the complexity of the algorithm used for the computation.

## (i) Separable Approach for the 2-D DWT Computation

A straightforward way to perform the computation of the 2-D DWT is to use a separable approach. In the separable approach, the impulse response  $G(z_1, z_2)$  of each 2-D filter used for the DWT computation is product separable, i.e.,  $G(z_1, z_2) = G_1(z_1)G_2(z_2)$ , The filter  $G_1(z_1)$  is used to process the 2-D data of successive rows (columns). Then, the resulting 2-D data is processed successively along the columns (rows) using the filter  $G_2(z_2)$ . A binary tree representation for a 2-level DWT computation of 2-D signal  $S(n_1, n_2)$  based on the separable approach is shown in Fig. 2.4. It is seen from this figure that the

computation for the decomposition of a given level j consists of two decomposition steps: row-wise decomposition of the 2-D input data using and column-wise decomposition of the 2-D data resulting from the row-wise decomposition. In the row-wise decomposition, each row of the 2-D input data is filtered using the two-channel horizontal filter bank  $(G_{1H}(z_1))$  or  $G_{1L}(z_1)$  and then downsampled by a factor of two, to produce horizontal highpass and lowpass components, each component having one-half of the numbers of samples in the rows of the 2-D input data. In the column-wise decomposition, each column of the two resulting components is filtered by using the two-channel vertical filter bank  $(G_{2H}(z_2))$  or  $G_{2L}(z_2)$  and downsampled by a factor of two so that in total four components, specified as the HH component  $w_j^{(HH)}(n_1, n_2)$ , LH component  $w_j^{(LH)}(n_1, n_2)$ , HL component  $w_j^{(LH)}(n_1, n_2)$  and LL component  $c_j^{(LL)}(n_1, n_2)$ , are obtained as outputs of the given level j. Among the four outputs, only the LL component  $c_j^{(LL)}(n_1, n_2)$  is used for the computation of the next resolution level, which is an iteration of the above two steps.

Figure 2.4: Binary tree representation of the computation of a 2-level 2-D DWT based on separable approach.

It should be noted that each of the four resulting components has one-quarter of the number of samples of the 2-D input data to the *j*th level. The computation of the resolution level *j* has a complexity of  $O(N_0M_0L/4^{j-1})$ , where  $N_0$  and  $M_0$  are the numbers of the rows and columns of the 2-D input data.

## (ii) Non-separable Approach for the 2-D DWT Computation

Obviously, separable approach is a simple way to compute the 2-D DWT. However, separable filters being a special class of 2-D filters are not capable to approximate well all arbitrary frequency responses. In this regard, a non-separable approach of the 2-D computation provides more flexibility. In the non-separable approach depicted in Fig. 2.5, the DWT of a 2-D signal  $s(n_1, n_2)$  is computed by carrying out four separate 2-D filtering operations using four 2-D filters: a highpass-highpass (HH) filter  $G_{HH}(z_1, z_2)$ , a highpass-lowpass (HL) filter  $G_{LL}(z_1, z_2)$ , a lowpass-highpass (LH) filter  $G_{LH}(z_1, z_2)$ , and a lowpass-lowpass (LL) filter  $G_{LL}(z_1, z_2)$ . The output signals of these four filters are then

Figure 2.5: Representation of the computation of a 2-level 2-D DWT based on non-separable approach.

decimated by a factor of two in the horizontal and vertical directions producing, respectively, the HH, HL, LH and LL components. The computation of the resolution level j using the non-separable approach has a complexity of  $O(N_0M_0L^2/4^{j-1})$ , where  $N_0$  and  $M_0$  are, respectively, the numbers of rows and columns of the 2-D input data, and  $L^2$  is the number of coefficients in each of the  $L \times L$  2-D filters.

## 2.2 Review of the Architectures

## 2.2.1 Categorization of the Architectures

In recent years, many architectures have been proposed for the DWT computation [74]–[109]. These architectures aim at providing high performances, in terms of their speed, area, throughput, latency and power consumption. The filtering operation involved in the DWT computation is usually the convolution operation, that is, FIR filtering. The structure of the filter could be a direct realization, or it could be a systolic, lattice, bitwise or lifting based realization depending on the way that the basic convolution operation is manipulated or formulated [110]–[128]. For example, the lifting scheme proposed by Sweldens [129], [130] exploits the relationship that exists between the lowpass filter  $G_L$  and the highpass filter  $G_H$  for the computation of the DWT. In this case, the polyphase matrix  $\mathbf{Q}(\mathbf{z}) = [G_L G_H]^T$  can then be factorized as

$$\mathbf{Q}(\mathbf{z}) = \begin{bmatrix} K & 0 \\ 0 & 1/K \end{bmatrix} \prod_{i=1}^{m} \begin{bmatrix} 1 & 0 \\ t_i(z) & 1 \end{bmatrix} \begin{bmatrix} s_i(z) & 1 \\ 1 & 0 \end{bmatrix}$$

(2.18)

where K is a constant, and the two so called Laurent polynomials  $s_i(z)$  and  $t_i(z)$  have low orders. It is seen from (2.18) that the lifting-scheme based filtering operation requires a

cascade of lifting steps, and thus, leads to a large latency and a long critical path of the resulting lifting architecture.

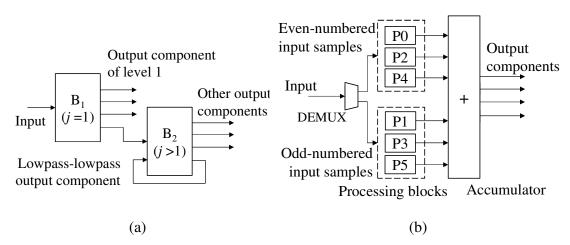

The filtering operation is carried out by using a processor that employs a certain type of filter structure. An architecture may use one or multiple such processors to perform the DWT computation. For the purpose of reviewing these existing architectures, we categorize them as single-processor architectures, parallel-processor architectures and pipeline architectures, depending on their configuration and the number of processors used by them. In a single-processor architecture, only one processor carries out the filtering operation by computing the samples of the DWT in a recursive manner. In a parallel-processor architecture, multiple processors are used to carry out the filtering operations so that more than one sample is computed at a time. In this type of architecture, the filtering operations to decompose the input signal into various components are carried out in parallel, whereas the computations of various resolution levels are still performed recursively by the parallel processors. In a pipeline architecture, a certain number of stages, each consisting of one or more processors, are pipelined so that the computation of each decomposition level as well as that of the multiple resolution levels are performed in parallel. Fig. 2.6 depicts the block diagrams for the three categories of the architectures. In each of these three broad categories, architectures may differ considerably because of the internal structures of processors employed for the filtering operation. In the following, examples of 1-D and 2-D architectures are given for each of the categories, and their salient features discussed.

Figure 2.6: Block diagrams of three types of architectures. (a) Single-processor architecture, (b) parallel-processor architecture, and (c) pipeline architecture.

## 2.2.2 Architectures for 1-D DWT Computation

### (a) Single-processor Architectures

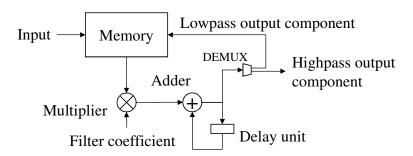

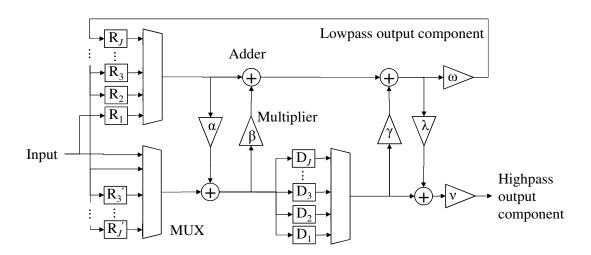

In the single-processor category, the VLSI architecture proposed by Guo *et al.* [42] is an example, in which only a single multiplier and a single adder, as shown in Fig. 2.7, are used, and thus, requires substantially large computation time. Fig. 2.8 depicts another example of this category, in which the processor utilizes a systolic array of multiply-accumulate (MAC) cells and a bank of shift registers for the filtering operations [43]. However, this architecture is slow because of the delays involved in the propagation of the signal through the array of MAC cells. The lifting-scheme based processor, proposed by Liao *et al.* [44], is yet another example of the single-processor architecture, in which the processor consists of a cascade of lifting steps, as shown in Fig 2.9, and it is used to compute the samples of the first resolution level at every other clock cycles and those of the other levels at the intervening clock cycles. However, a cascade of many lifting steps would result in quite a long critical path for this type of architecture.

Figure 2.7: An architecture using one multiplier and one adder [42].

Figure 2.8: An architecture using a processor employing a systolic array of MAC cells [43].

Figure 2.9: A lifting-based architecture using Daub-4 filters.  $R_j$  and  $D_j$  represent, respectively, the registers and delay units for the computation of the *j*th level [44].

### (b) Parallel-processor Architectures

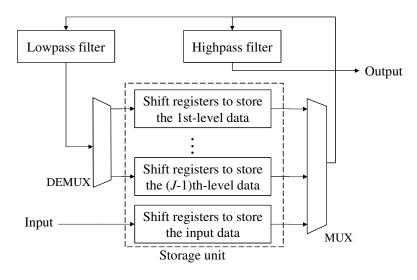

In the parallel-processor category, Chakrabarti and Vishwanath [53] have proposed an architecture that uses two processors operating in parallel, one for lowpass and the other for highpass filtering operations, and one storage unit, as shown in Fig. 2.10. Since this architecture has as many memory blocks as the number of resolution levels for storing the lowpass data, it requires a large memory space.

Figure 2.10: A parallel architecture proposed by Chakrabarti and Vishwanath [53].

The folded architecture proposed by Parhi and Nishitani [54] is an example of a parallel-processor architecture, in which a pair of lowpass and highpass systolic filters and a set of shift registers are used to perform the computations of multiple resolution

Figure 2.11: A folded architecture proposed by Parhi and Nishitani [54] using 4-tap filter.

levels, as shown in Fig. 2.11. This architecture requires complex routing, and has a low throughput rate for large-size filters.

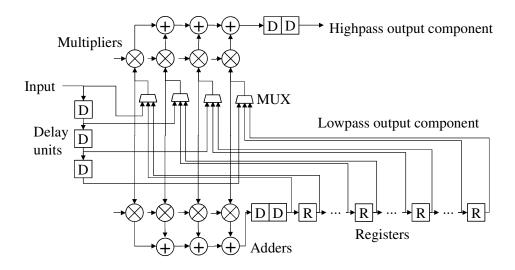

Masud and McCanny [55] have proposed a two-processor architecture, as shown in Fig. 2.12, using L-tap lowpass and highpass filters operating in parallel. However, in this architecture, each of the two filters uses only L/2 MAC cells that operate on odd and even numbered coefficients in consecutive clock cycles. The architecture results in a large computation time and has a complex control unit.

Figure 2.12: An architecture proposed by Masud and McCanny [55].

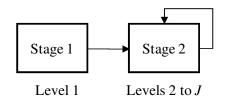

#### (c) Pipeline Architectures

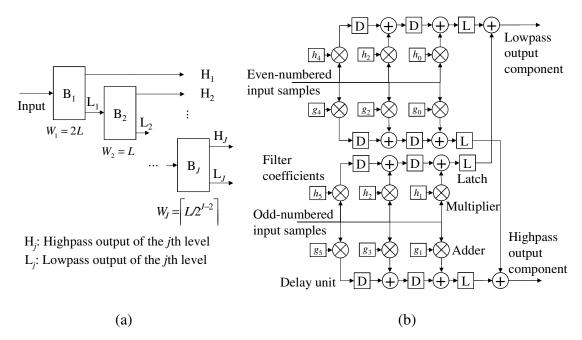

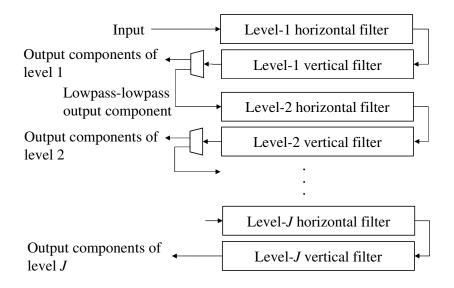

The architecture proposed by Marino *et al.* [61] and shown in Fig. 2.13 is an example of a pipeline architecture, in which a number of pipeline stages  $B_j$  (j=1, 2, ..., J) are employed for the computations of J resolution levels. The computation of the jth resolution level is performed by the jth stage using  $W_j = \left| L/2^{j-2} \right|$  MAC cells, as shown in Fig. 2.13. However, the architecture requires a large amount of hardware resource when the number of resolution levels becomes large. Moreover, since the organization of MAC cells differs from stage to stage, the design complexity is quite high.

Figure 2.13: A pipeline architecture proposed by Marino *et al.* [61]. (a) Block diagram of the architecture. (b) Structure of B1 when a 6-tap filter is used.

Park [62] has proposed a scalable pipeline architecture, in which a certain stage  $B_j$  of the pipeline utilizes the number of parallel multipliers  $M_j$  that is one-half of that of the preceding stage, and uses a data recorder unit (DRU) for constructing the input data sequence, as shown in Fig. 2.14. However, the architecture is restricted for of the computation of the DWT which has three resolution levels and the number of filter length L is divisible by 4.

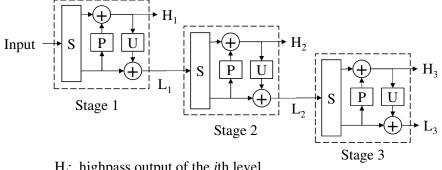

A lifting-scheme based architecture proposed by Chen [63] and shown in Fig. 2.15 is another example of a pipeline architecture, in which a certain number of identical stages, each consisting of splitting, predicting and updating units for the computation of a resolution level, are employed. In this architecture, since the number of computations performed by each stage is not consistent with the amount of hardware resource it employs, the architecture has low utilization of hardware resources.

Figure 2.14: A scalable 3-stage architecture proposed by Park [62]. (a) Block diagram of the architecture. (b) Structure of the first stage.

H<sub>j</sub>: highpass output of the *j*th level

$L_{j}$ : lowpass output of the *j*th level

S: splitting unit; P: predicting unit; U: updating unit

Figure 2.15: A lifting-scheme based pipeline architecture [63].

## 2.2.3 Architectures for 2-D DWT Computation

### (a) Single-processor Architectures

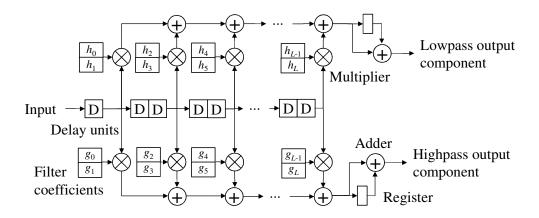

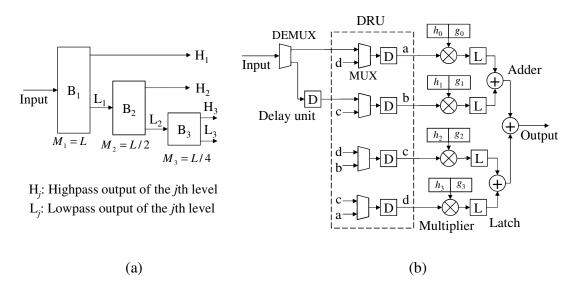

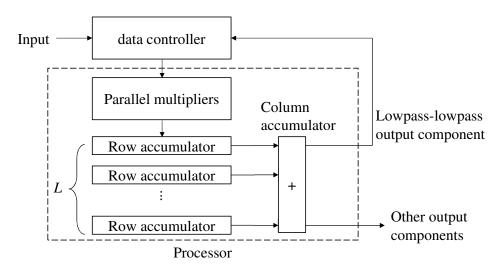

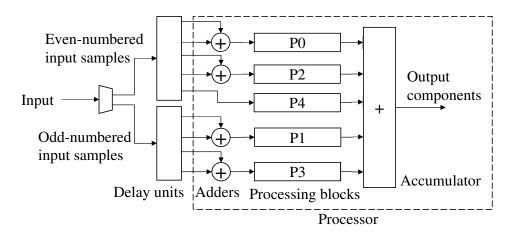

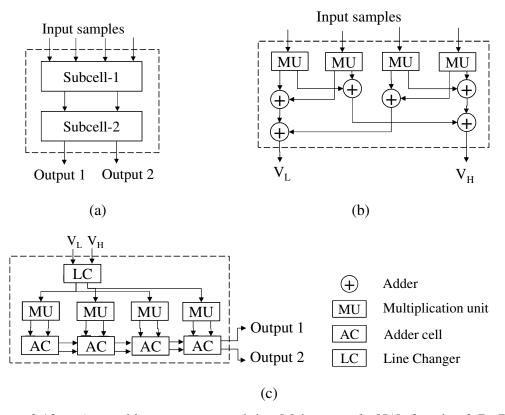

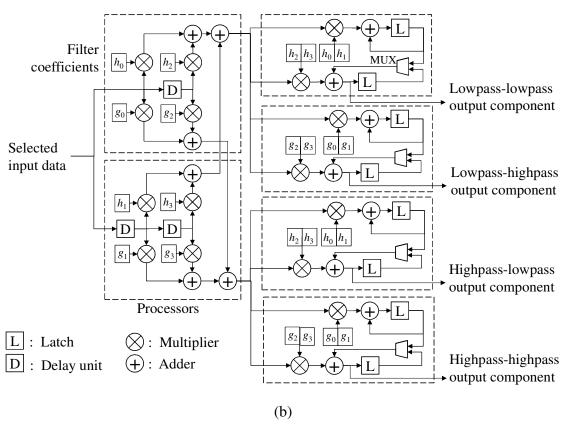

In a single-processor category, the architecture of [47] is an example of a multiplierless architecture, and therefore, is restricted to only certain types of wavelets. Moreover, the architecture is not scalable. The architecture proposed by Movva and Srivivasan [48] is another example in the single-processor category for the 2-D DWT computation that uses the separable approach. In this architecture, the 2-D DWT is obtained by performing a row-wise computation followed by a column-wise computation using a single lifting-scheme based processor. The architecture is a low-speed and requires a large memory space. Hung et al. [49] have proposed a single-processor architecture using the non-separable approach, illustrated Fig. 2.16, in which an  $L \times L$ -tap filtering operation is carried out by a processor consisting of a cascade of three blocks: parallel multipliers, L accumulators along the row direction and one accumulator along the column direction. The architecture has low computational speed, since the samples of the four decomposed components are computed sequentially. The architecture [50] shown in Fig. 2.17 is another example of a single-processor architecture, in which the processor consists of  $\lceil L/2 \rceil$  adders and  $\lceil L/2 \rceil$  parallel processing blocks, where L is the filter length, followed by an accumulator. The architecture requires large storage (delay units) to store the lowpass-lowpass output components of various resolution levels. Fig. 2.18 shows another single-processor architecture proposed by Meher et al. [51] for the computation of the 2-D DWT using separable approach, in which the computation is performed by two blocks, referred to as Subcell-1 and Subcell-2. Subcell-1 employs parallel multiplication units and adders for row-wise filtering operation, whereas

Subcell-2 employs one delay cell and a systolic array of multiplication and adder units for column-wise operation.

Figure 2.16: A single-processor architecture for the 2-D DWT computation [49].

Figure 2.17: An architecture proposed by Uzun and Amira [50] for the 2-D DWT computation using 9/7-tap filters.

Figure 2.18: An architecture proposed by Meher *et al.* [51] for the 2-D DWT computation using separable approach. (a) Top-level architecture. (b) Structure of Subcell-1. (c) Structure of Subcell-2.

### (b) Parallel-processor Architectures

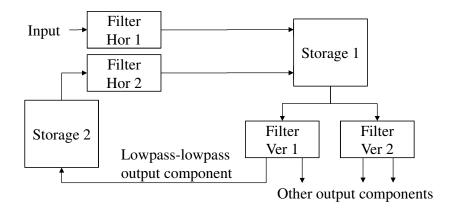

In the category of parallel-processor architectures, Chakrabarti and Mumford [57] have proposed a four-processor architecture, as shown in Fig. 2.19, in which Filter Hor 1 performs the horizontal filtering operation of the resolution level j = 1, Filter Ver 1 and Filter Ver 2 perform, respectively, the vertical lowpass and highpass filtering operations of the resolution levels  $j = 1, 2, 3, \ldots$ , and Filter Hor 2 performs the horizontal filtering operations of the resolution levels  $j = 2, 3, \ldots$ . In this architecture, since the amounts of computations assigned to the four processors are not proportional to the amount of

hardware employed by them, the architecture has drawback of having low hardware utilization.

Figure 2.19: A 2-D DWT architecture proposed by Chakrabarti and Mumford [57].

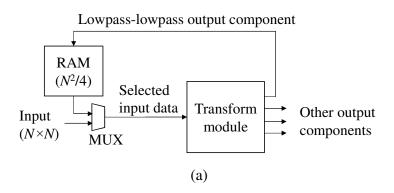

The architecture [58] shown in Fig. 2.20 is another example of parallel-processor architecture for the 2-D DWT computation, in which two processors employing a polyphase decomposition technique are used for row-wise filtering operation, and four other processors employing a filter coefficient folding technique are used for column-wise filtering operation. The architecture has a high design complexity, since the parallel processors have different structures.

Figure 2.20: A parallel-processor architecture proposed by Wu and Chen [58] for the 2-D DWT computation. (a) Top-level architecture. (b) Structure of the transform module with six processors.

### (c) Pipeline Architectures

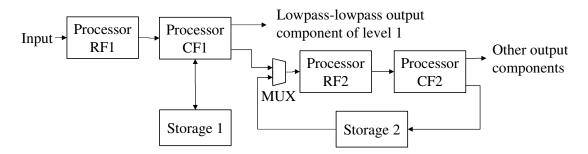

The architecture [64] shown in Fig. 2.21 is an example of a pipeline architecture for the computation of the 2-D DWT. In this architecture, four processors, RF1, CF1, RF2 and CF2, form a pipeline, in which the first two processors are used to perform, respectively, the row-wise and column-wise operations of level 1 and remaining two to perform, respectively, the row-wise and column-wise operations of the remaining levels. The architecture has a large latency and requires large storage space.

Figure 2.21: A pipeline architecture proposed by Jou *et al.* [64] for the 2-D DWT computation.

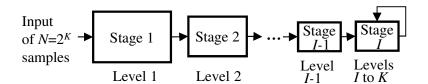

The architecture shown in Fig. 2.22 is another example of a pipeline architecture proposed by Mihić [65]. In this architecture, a *J*-level 2-D DWT is performed using a pipeline of 2*J* processors, each employing a semi-systolic array of MAC cells for row-or column-wise filtering operation of a resolution level. The architecture has a very large latency, and it is not practical for the computation of the DWT with large number of resolution levels.

The architecture of [66] (see Fig. 2.23) is yet another example of a pipeline architecture for the 2-D DWT computation. In this architecture, a pipeline of two stages, one for the computation of the first resolution level and the other for the computation of

Figure 2.22: An architecture using a pipeline of 2*J* stages [65].

all the remaining levels, and each employing L parallel processing blocks, are used. The design complexity of this architecture is high, since the structures of the processing blocks are different. Also, it has a high hardware resource complexity, since each processing block has a large number of MAC cells.

Figure 2.23: A two-stage pipeline architecture proposed by Marino [66]. (a) Top-level architecture. (b) The structure of the stage  $B_1$  for L=6.

# 2.3 Summary

In this chapter, starting with the mathematical definitions of the 1-D and 2-D wavelet transforms, discrete formulations have been provided for their practical computations. These discrete formulations are seen to follow a binary-tree structure for the computation of the 1-D DWT and, depending on the separable or non-separable approaches, a binary-tree or quadtree structures for the computation of the 2-D DWT. For the purpose of reviewing the existing architectures for the computation of the 1-D and 2-D wavelet transforms, they have been classified as single-processor, parallel-processor or pipeline architectures. A number of architectures from the literature in each of the categories, both for the 1-D and 2-D DWT computations, have been briefly reviewed. It has been seen that whereas the architectures in the single-processor and parallel-processor categories are efficient in terms of the speed and employment of hardware resources, respectively, the pipeline architectures are a good compromise between hardware resource complexity and speed.

# Chapter 3

# A Scheme for the Design of Pipeline Architectures for 1-D Discrete Wavelet Transform

In Chapter 2, a number of pipeline architectures [61]–[63] for the computation of the 1-D discrete wavelet transform were briefly reviewed. These architectures employ a large number of pipeline stages or utilize a large number of MAC cells to perform the filtering operations of the stages, and thus, have high complexity in terms of hardware resources [61], [62] or large latency [63]. In other words, the speed provided by these architectures is not commensurate with the hardware resources employed by them, The reason for these drawbacks is that the schemes used for the development of these architectures have not fully exploited certain characteristics inherent in the discrete wavelet transform.

In this chapter, a scheme for design of pipeline architectures for a fast computation of the DWT is proposed [131]–[133]. The goal of fast computation is achieved by minimizing the number and period of the clock cycles. The main idea in minimizing these two parameters is to optimally distribute the task of the DWT computation among the stages of the pipeline, and to maximize the inter- and intra-stage parallelisms of the

pipeline by synchronizing the operations of the stages optimally and by utilizing the available hardware resources judiciously.

The chapter is organized as follows. In Section 3.1, a matrix formulation for the 1-D DWT computation is presented. In Section 3.2, a study is undertaken to determine the number of stages in the pipeline to optimally assign to them the task of the 1-D DWT computation. Based on this study, in Section 3.3, a scheme for the design of a pipeline architecture is developed. In Section 3.4, the performance of the pipeline architecture for the DWT computation using the proposed design scheme is assessed and compared with that of other existing architectures. A specific example of designing an architecture for the DWT computation is also considered and the resulting architecture is simulated and implemented on an FPGA board in order to demonstrate the realizability and validity of the proposed scheme. Section 3.5 summarizes the work of this chapter by highlighting the salient features of the proposed design scheme and the resulting pipeline architectures.

# 3.1 Formulation of the 1-D DWT Computation

### 3.1.1 Matrix Formulation

The 1-D DWT of a signal is computed by performing the filtering operation repeatedly, first on the input data and then on the LL data after decimating it by a factor of two for the successive resolution levels. The filtering operation uses a quadrature mirror filter bank with lowpass and highpass filters to decompose the signal into lowpass and highpass subband signals, respectively. The transform can be expressed using a matrix formulation in order to provide a better insight into the underlining operations of

the DWT as well as to facilitate the proposed scheme for the design of the architecture for its computation.

Let the signal be denoted as  $\mathbf{S} = [s_1, s_2, \cdots, s_{N-1}, s_N]^T$ , where N, the number of samples in the input signal, is chosen to be 2J, J being an integer. Assume that  $h_i$  and  $g_i$  (i = 0,1,...,L-1) are the coefficients of the L-tap lowpass and highpass filters, respectively. Then, by expressing the transform matrices for the lowpass and highpass computations at the jth (j=1,2,...,J) level decomposition as

$$\mathbf{G}^{(j)} = \begin{bmatrix} g_0 \ g_1 \ g_2 \ g_3 \cdots g_{L-1} & 0 & 0 & 0 & \cdots & 0 & 0 & 0 & 0 \\ 0 & 0 \ g_0 \ g_1 \cdots g_{L-3} \ g_{L-2} \ g_{L-1} & 0 & \cdots & 0 & 0 & 0 & 0 \\ & \vdots & \vdots & & & & & \\ 0 & 0 & 0 & 0 & \cdots & & 0 & g_0 \ g_1 \ g_2 \ g_3 \\ 0 & 0 & 0 & 0 & \cdots & & 0 & 0 & 0 & g_0 \ g_1 \end{bmatrix}$$

(3.1b)

respectively, where both  $\mathbf{H}^{(j)}$  and  $\mathbf{G}^{(j)}$  have a size of  $(N/2^j) \times (N/2^{j-1})$ , the outputs of the transform at the *j*th level can be computed from the following:

$$\begin{bmatrix} \mathbf{C}^{(j)} \\ \mathbf{W}^{(j)} \end{bmatrix} = \begin{bmatrix} \mathbf{H}^{(j)} \\ \mathbf{G}^{(j)} \end{bmatrix} \cdot \mathbf{C}^{(j-1)}$$

(3.2)

where  $C^{(j)}$  and  $W^{(j)}$  represent the column vectors of size  $N/2^j$  and consist of lowpass and highpass output samples, respectively, at the resolution level j, with  $C^{(0)}=S$ . It is clear from (3.1a) and (3.1b) that the lengths of the filters and the size of the input samples control the number of non-zero entries of the matrices involved, which in turn, determines the complexity of the DWT computation. If the decomposed signals are

required to be reassembled into the original form without loss of information, the lowpass and highpass filters must satisfy the perfect reconstruction condition given by

$$g_i = (-1)^{i+1} h_{L-1-i} (3.3)$$

A border extension of the input signal becomes necessary for the processing of the samples on or near the border of a finite-length signal. There are generally three ways by which the border can be extended in a DWT computation, zero padding, symmetric padding and periodic padding [134]. Even though from the point of view of hardware cost, zero padding is the least expensive, the periodic padding is the most commonly used method for border extension, since it allows a precise recovery of the original signal at or near the border. This method extends the original sequence  $\bf S$  by appending it with its first L–2 samples as

$$\mathbf{S_p} = [s_1, s_2, \dots, s_{N-1}, s_N, s_1, \dots, s_{L-3}, s_{L-2}]^{\mathrm{T}}$$

(3.4)

Thus, in order to operate on the padded input sequence  $S_p$ , the transform matrices  $\mathbf{H}^{(j)}$  and  $\mathbf{G}^{(j)}$  have to be modified by appending each by additional L-2 columns. The elements of the appended columns in a row of a modified transform matrix assume a zero value, if all the filter coefficients already appear in the corresponding row of (3.1a) or (3.1b). Otherwise, the elements in the row are made to assume the missing values of the filter coefficients so that all the coefficients appear in that row of the modified transform matrix.

### 3.1.2 Reformulation of (3.2)

It is seen from (3.1) that due to the decimation-by-two requirement of the DWT, entries in the successive rows of matrices  $\mathbf{H}^{(j)}$  and  $\mathbf{G}^{(j)}$ , and therefore, in their modified versions, are shifted to right by two positions. This property can be utilized to decompose the arithmetic operations in (3.2) into two parts so that the operations in one part can be performed simultaneously with those of the other one. For this purpose, we now decompose each of the modified transform matrices  $\mathbf{H}^{(j)}$  and  $\mathbf{G}^{(j)}$  by separating the even and odd numbered columns of each matrix into two sub-matrices. The resulting submatrices, taking into account the perfect reconstruction condition specified by (3.3), can be expressed as

$$\mathbf{H}_{even}^{(j)} = \begin{bmatrix} h_0 & h_2 & \cdots & h_{L-2} & 0 & 0 & \cdots & 0 \\ 0 & h_0 & \cdots & h_{L-4} & h_{L-2} & 0 & \cdots & 0 \\ \vdots & & & \vdots & & \vdots \\ 0 & \cdots & & 0 & h_0 & h_2 & \cdots & h_{L-2} & 0 \\ 0 & \cdots & & 0 & 0 & h_0 & \cdots & h_{L-4} & h_{L-2} \end{bmatrix}$$

(3.5a)

$$\mathbf{H}_{odd}^{(j)} = \begin{bmatrix} h_1 & h_3 & \cdots & h_{L-1} & 0 & 0 & \cdots & 0 \\ 0 & h_0 & \cdots & h_{L-3} & h_{L-1} & 0 & \cdots & 0 \\ \vdots & & & \vdots & & \vdots \\ 0 & \cdots & & 0 & h_1 & h_3 & \cdots & h_{L-1} & 0 \\ 0 & \cdots & & 0 & 0 & h_1 & \cdots & h_{L-3} & h_{L-1} \end{bmatrix}$$

(3.5b)

$$\mathbf{G}_{even}^{(j)} = -\begin{bmatrix} h_{L-1} & h_{L-3} & \cdots & h_1 & 0 & 0 & \cdots & 0 \\ 0 & h_{L-1} & \cdots & h_3 & h_1 & 0 & \cdots & 0 \\ \vdots & & & \vdots & & \vdots & & \vdots \\ 0 & \cdots & 0 & h_{L-1} & h_{L-3} & \cdots & h_1 & 0 \\ 0 & \cdots & 0 & 0 & h_{L-1} & \cdots & h_3 & h_1 \end{bmatrix}$$

(3.5c)

$$\mathbf{G}_{odd}^{(j)} = \begin{bmatrix} h_{L-2} & h_{L-4} & \cdots & h_0 & 0 & 0 & & \cdots & 0 \\ 0 & h_{L-2} & \cdots & h_2 & h_0 & 0 & & \cdots & 0 \\ & \vdots & & & \vdots & & & \vdots \\ 0 & & \cdots & & 0 & h_{L-2} & h_{L-4} & \cdots & h_0 & 0 \\ 0 & & \cdots & & 0 & 0 & h_{L-2} & \cdots & h_2 & h_0 \end{bmatrix}$$

(3.5d)

in which the entries in the successive rows are shifted to right by only one position. With this decomposition of the transform matrices, the DWT computation as given by (3.2) can be reformulated as

$$\begin{bmatrix} \mathbf{C}^{(j)} \\ \mathbf{W}^{(j)} \end{bmatrix} = \begin{bmatrix} \mathbf{H}_{even}^{(j)} \\ \mathbf{G}_{even}^{(j)} \end{bmatrix} \cdot \mathbf{C}_{even}^{(j-1)} + \begin{bmatrix} \mathbf{H}_{odd}^{(j)} \\ \mathbf{G}_{odd}^{(j)} \end{bmatrix} \cdot \mathbf{C}_{odd}^{(j-1)}$$

(3.6)

where  $\mathbf{C}_{even}^{(j)}$  and  $\mathbf{C}_{odd}^{(j)}$  are the two sub-vectors consisting of even and odd numbered samples, respectively, in the padded vector of  $\mathbf{C}^{(j)}$ .

It is seen from (3.6) that the operations in each of the two terms are identical, and also, they can be performed independently in parallel. Furthermore, in view of the structures of the decomposed transform matrices as given by (3.5), the filtering operation can be carried out by employing the conventional clocking mechanism used for implementing digital systems.

# 3.2 Choice of a Pipeline for the 1-D DWT Computation

In a pipeline structure for the DWT computation, multiple stages are used to carry out the computations of the various resolution levels of the transform. Thus, the computation corresponding to each resolution level needs to be mapped to a stage or stages of the pipeline. In order to maximize the hardware utilization of a pipeline, the hardware resource of a stage should be proportional to the amount of the computation assigned to the stage. Since the amount of computations in successive resolution levels of the transform get reduced by a factor of two, two scenarios can be used for the distribution of the computations to the stages of a pipeline. In the first scenario, the resolution levels are assigned to the stages so as to equalize the computations carried out by each stage, that is, the hardware requirements of all the stages are kept the same. In the second scenario, the computations of the successive resolution levels are assigned to the successive stages of a pipeline, on a one-level-to-one-stage basis. Thus, in this case, the hardware requirement of the stages gets reduced by a factor of two as they perform the computations corresponding to higher-level decompositions.

Fig. 3.1 shows a stage-equalized pipeline structure, in which the computations of all the  $K=\log_2N$  levels are distributed equally among the M stages. The process of stage equalization can be accomplished by dividing equally the task of a given level of decomposition into smaller subtasks and assigning each such subtask to a single stage and/or by combining the tasks of more than one consecutive level of decomposition into a single task and assigning it to a single stage. Note that generally a division of the task would be required for low levels of decomposition and a combination of the tasks for high levels of decomposition.

Figure 3.1: Stage-equalized pipeline structure.

In a one-to-one mapped structure, the computations of K resolution levels are distributed exactly among K stages, one level to one stage. In practical applications, a structure with less than K stages is used for the computation of a K-level DWT, as shown

in Fig. 3.2. In this structure, the computations of the first I-1 levels are carried out by the stages  $i=1, 2, \dots, I-1$ , respectively, and those of the last K-I+1 levels are performed recursively by the Ith stage. The amount of hardware resources of a stage is one-half of that of its preceding one except for the Ith stage that has the same size as that of the preceding stage.

Figure 3.2: A one-to-one mapped pipeline structure with I(I < K) stages.

The structures of Fig. 3.1 and Fig. 3.2 can be used to perform the computations of multiple levels of decomposition. The computation of each level is performed as an *L*-tap FIR filtering operation by summing the *L* products of the input samples and the filter coefficients, as described by (3.2). Generally, one MAC cell is used to carry out one multiplication of an input sample by a coefficient followed by one accumulation operation. In order to perform an uninterrupted *L*-tap filtering operation with easy control, one can thus use a network of *L* basic units of such a MAC cell. Since all the resolution levels perform *L*-tap filtering operations, it would be desirable that each resolution level performs its filtering operation using this same type of MAC-cell network. However, in the context of one-to-one mapped pipeline structure of Fig. 3.2, in which the requirement is that the hardware resource should get reduced by a factor of two from one stage to the next, the use of the same MAC-cell network for all the stages would not be possible unless the pipeline has only two stages. In other words, the first stage performs the level-1 computation and the second stage performs the computations corresponding to all