### Implementing supervisory control maps with PLC

#### Mohammad Moniruzzaman

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science in Electrical and Computer Engineering at Concordia University Montréal, Québec, Canada

August 2006

©Mohammad Moniruzzaman, 2006

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-20753-6 Our file Notre référence ISBN: 978-0-494-20753-6

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### Abstract

#### Implementing supervisory control maps with PLC

#### Mohammad Moniruzzaman

The supervisory control theory of Discrete-Event Systems (DES) can be used to construct a supervisor for any event-driven system in which the state space is discrete. To implement supervisors we propose to use Programmable Logic Controllers (PLC), which are widely used in industrial applications. In our work, we develop a new conversion algorithm which directly transforms a supervisor represented by a finite automaton to a Ladder Logic Diagram (LLD). To demonstrate the correctness of our proposed approach and discuss the issues that may arise in modeling and development of DES supervisors, we design supervisors for a boiler control system using supervisory control theory of Ramadge and Wonham, convert DES supervisors to PLC controllers using our conversion technique, and verify by setting a virtual plant setup using a PLC simulation software that the converted LLD can be executed by the PLC and that the original behavior of the DES supervisors under PLC implementation can be achieved.

## Acknowledgments

In the first aspect I would like to express my sincere gratitude and thanks to my supervisor Dr. Peyman Gohari for his valuable suggestions, guidance and patience throughout the thesis period. Without his precious privilege and teaching, I would never have acquainted with the realm of the research. Much of this work has been established by his insightful knowledge as an exceptional researcher.

Many thanks to Mr. Liang Du and other members of the group for their friendly co-operation and information. Thanks to Famic Technologies, Canada for their technical support and information about the Automation Studio software. I would like to thank the members of my defense committee Dr. Rabin Raut, Dr. Shahin Hashtrudi Zad and Dr. Ali Dolatabadi for their valuable comments and evaluation.

My roommate M.M.A. Hayder, a Ph.D. student, is the only friend with whom I shared my research experiences and feelings; I do appreciate his friendliness and would like to thank him. Special thanks to my well-wisher Junaid Mohaimin. I would also like to thank those who co-operated and helped me in many ways during my study period.

Finally, I would like to convey my heartiest appreciations and thanks to my family members, especially my parents Mohammad Muklesur Rahman and Kazi Momtaz Begum, and my wife Afsana Siddique, for their continuous support, patience and inspiration, and of course for their long cherished dream about me.

Mohammad Moniruzzaman August 2006.

To my loving parents, wife and son Ridwan Zaman Roddur  $\ldots \ldots$

## Contents

| List of | Figur    | es                                               | viii |

|---------|----------|--------------------------------------------------|------|

| List of | Table    | es es                                            | x    |

| Chapte  | er 1 I   | Introduction                                     | 1    |

| 1.1     | Overv    | riew of the thesis                               | 1    |

| 1.2     | Revie    | w of related works                               | 2    |

| 1.3     | Imple    | mentation procedures and tools                   | 5    |

| 1.4     | Outlin   | ne of the thesis                                 | 6    |

| Chapte  | er 2   I | Preliminaries                                    | 8    |

| 2.1     | Super    | visory control of DES                            | 8    |

|         | 2.1.1    | DES plant, specification and supervisory control | 8    |

|         | 2.1.2    | Operations on DES                                | 10   |

|         | 2.1.3    | DES Supervisor                                   | 12   |

|         | 2.1.4    | TCT: DES supervisor design software              | 12   |

|         | 2.1.5    | Design of DES supervisor using TCT               | 14   |

| 2.2     | Progr    | ammable Logic Controller (PLC)                   | 15   |

|         | 2.2.1    | Ladder Logic Diagrams (LLDs)                     | 17   |

|         | 2.2.2    | Automation Studio: A PLC simulation software     | 22   |

| Chapte  | er 3 (   | Conversion Algorithm                             | 24   |

| 3.1     | Event    | generation and supervisory control               | 24   |

| 3.2     | Event    | interpretation: DES to LLD                       | 25   |

| 3.3     | Motiv    | rating example                                   | 27   |

| 3.4     | Conve    | ersion method                                    | 30   |

|         | 3.4.1    | Assumptions and key observations                 | 30   |

|         | 3.4.2   | First step: Event partition             | 31 |

|---------|---------|-----------------------------------------|----|

|         | 3.4.3   | Second step: I/O selection              | 32 |

| Chapte  | er 4 C  | Case study: boiler control system       | 35 |

| 4.1     | Introd  | uction                                  | 35 |

|         | 4.1.1   | A brief description of boiler           | 35 |

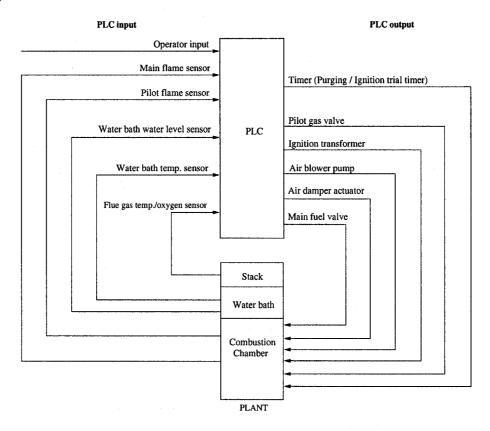

| 4.2     | A typi  | cal boiler control system               | 37 |

|         | 4.2.1   | Design objectives                       | 39 |

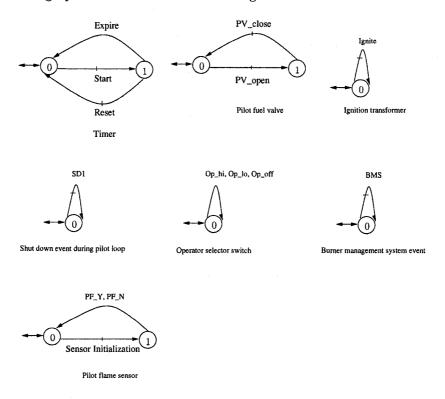

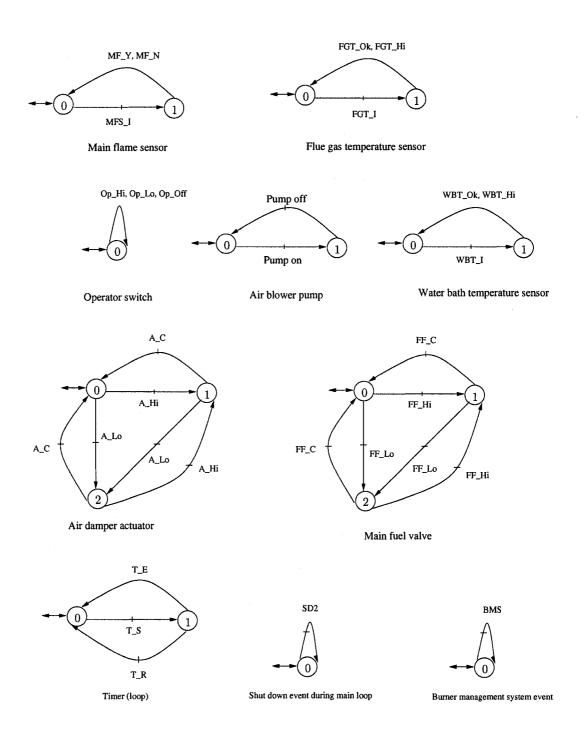

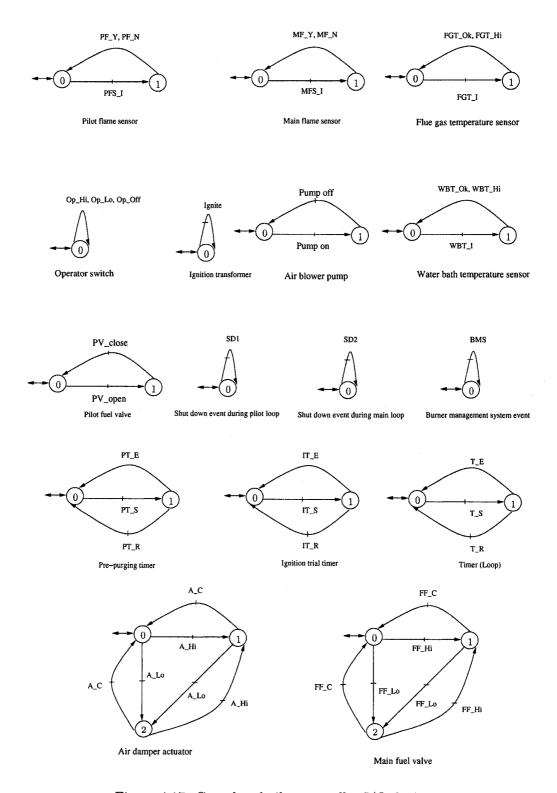

| 4.3     | Model   | ing boiler control devices as DES       | 39 |

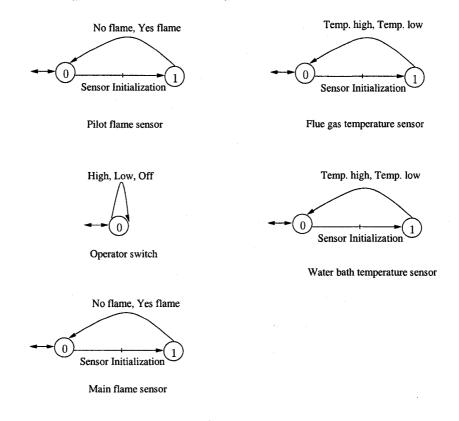

|         | 4.3.1   | Modeling input devices                  | 40 |

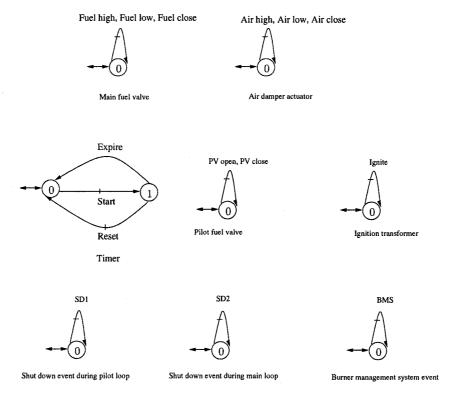

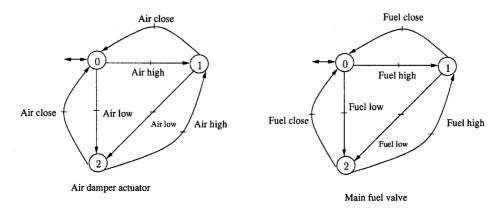

|         | 4.3.2   | Modeling output devices                 | 41 |

| 4.4     | Super   | visor construction                      | 43 |

|         | 4.4.1   | General considerations                  | 43 |

|         | 4.4.2   | Pilot flame controller                  | 44 |

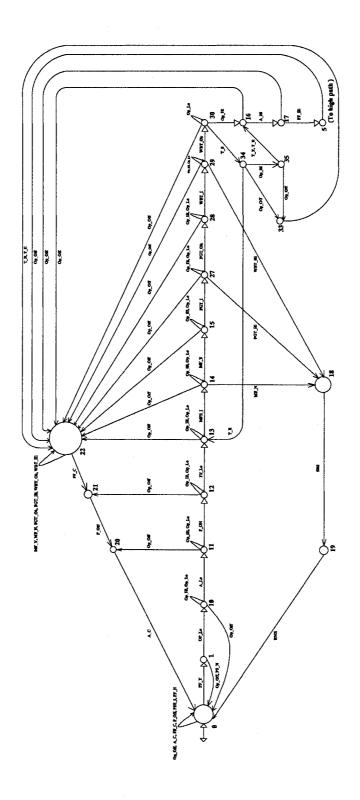

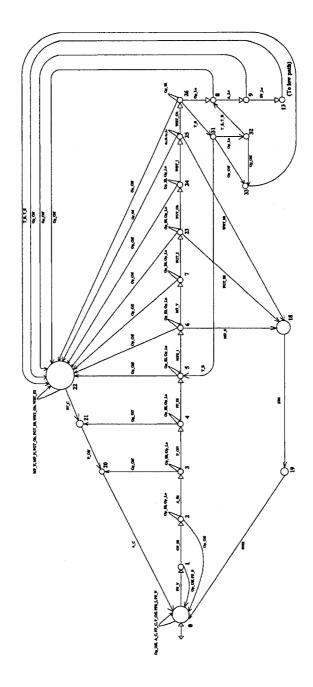

|         | 4.4.3   | Main flame controller                   | 48 |

|         | 4.4.4   | Complete boiler controller              | 51 |

| 4.5     | PLC-b   | pased implementation of the controllers | 53 |

| Chapte  | er 5 (  | Conclusions and future research         | 71 |

| 5.1     | Conclu  | usions                                  | 71 |

| 5.2     | Future  | e research                              | 73 |

| Bibliog | graphy  |                                         | 75 |

| Appen   | dix 1   |                                         | 76 |

| Appen   | dix 11  |                                         | 84 |

| Appen   | dix 111 |                                         | 96 |

# List of Figures

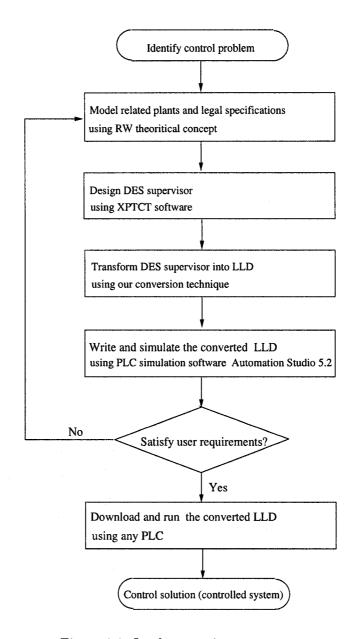

| 1.1 | Implementation sequence                                                                                 | 7  |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 2.1 | Layout of PLC                                                                                           | 15 |

| 2.2 | PLC scan cycle                                                                                          | 16 |

| 2.3 | A simple PLC I/O view                                                                                   | 17 |

| 2.4 | Some LLD components                                                                                     | 18 |

| 2.5 | TIMER ON-DELAY and TIMER OFF-DELAY in LLD                                                               | 19 |

| 2.6 | Contact placement in LLD                                                                                | 20 |

| 2.7 | Contact placement in LLD                                                                                | 21 |

| 2.8 | Contact placement in LLD.                                                                               | 22 |

| 3.1 | Representation of $\alpha_{on}$ and $\alpha_{off}$ by $x_{\alpha_{on}}$                                 | 25 |

| 3.2 | Representation of $\beta_{hi}$ , $\beta_{lo}$ and $\beta_{cl}$ by $x_{\beta_{hi}}$ and $x_{\beta_{lo}}$ | 26 |

| 3.3 | An example of a supervisor represented by an automaton                                                  | 27 |

| 3.4 | Motivating Example in LLD                                                                               | 30 |

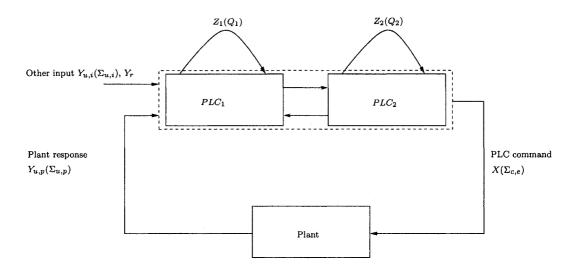

| 3.5 | PLC-based supervisory control                                                                           | 32 |

| 3.6 | A $(n+1)$ -state switch                                                                                 | 33 |

| 4.1 | Water bath boiler                                                                                       | 36 |

| 4.2 | PLC-based boiler controller                                                                             | 38 |

| 4.3 | Some input devices                                                                                      | 40 |

| 4.4 | Some output devices                                                                                     | 41 |

| 4.5 | Alternative model for air damper and main fuel valve                                                    | 42 |

| 4.6 | Pilot controller I/O devices                                                                            | 44 |

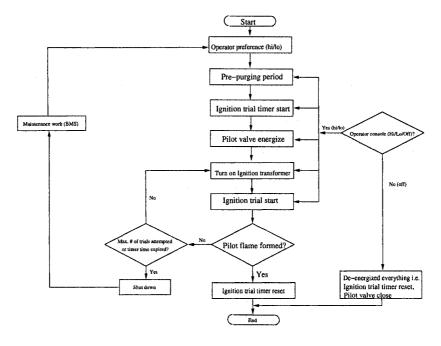

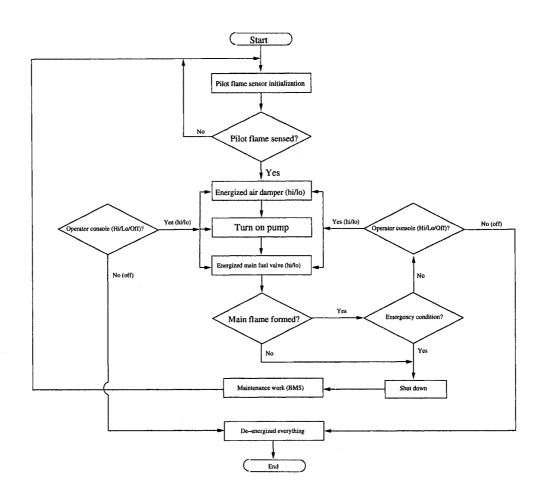

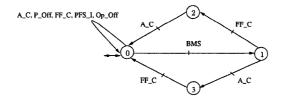

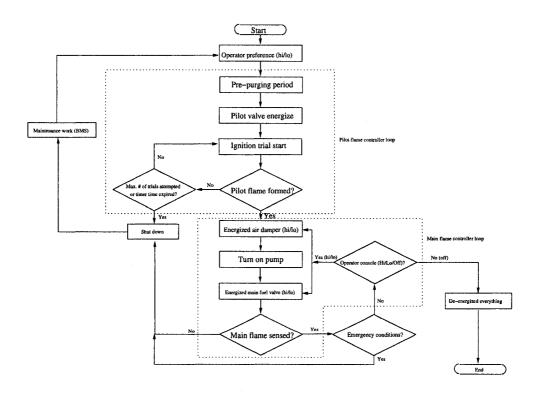

| 4.7 | Operation sequence of Pilot controller                                                                  | 45 |

| 4.8 | Specification for pilot flame supervisor (TCT: PILOTSPEC)                                               | 47 |

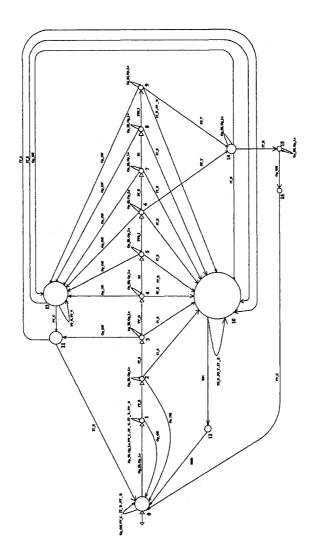

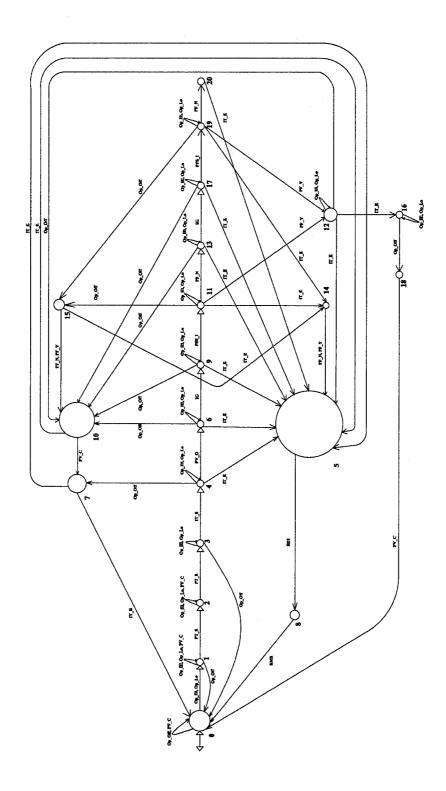

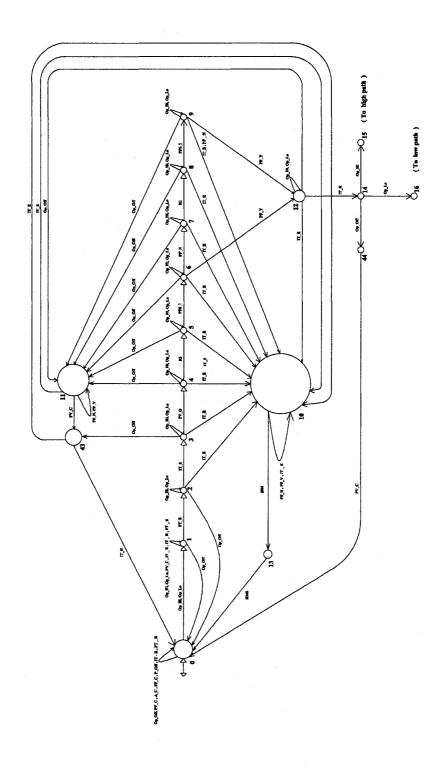

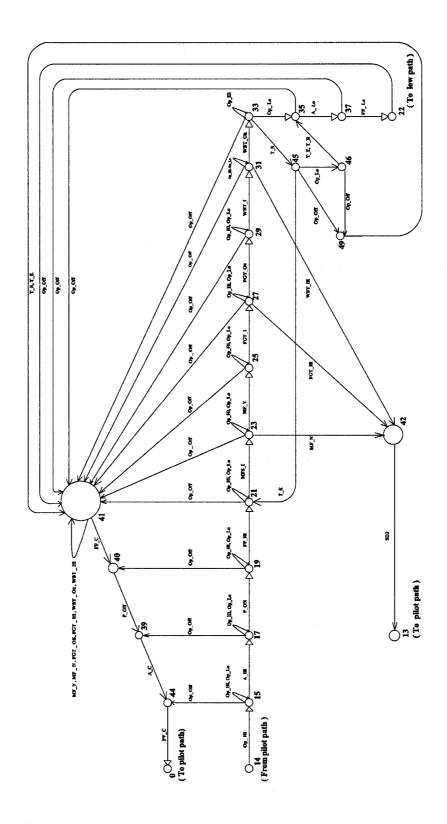

| 4.9 | Pilot flame supervisor (TCT: PILOTSUPERVISOR)                                                           | 55 |

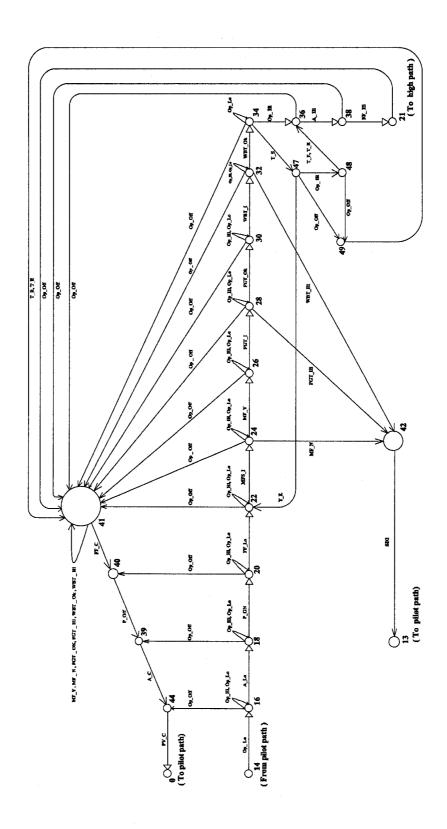

| 4.10 | Main flame controller I/O devices                                    | 56 |

|------|----------------------------------------------------------------------|----|

| 4.11 | Operation sequence of main flame controller                          | 57 |

| 4.12 | Specification for main flame supervisor: Low path (TCT: MAINSPEC1).  | 58 |

| 4.13 | Specification for main flame supervisor: High path (TCT: MAINSPEC1). | 59 |

| 4.14 | Specification for main flame supervisor (TCT: MAINSPEC2)             | 59 |

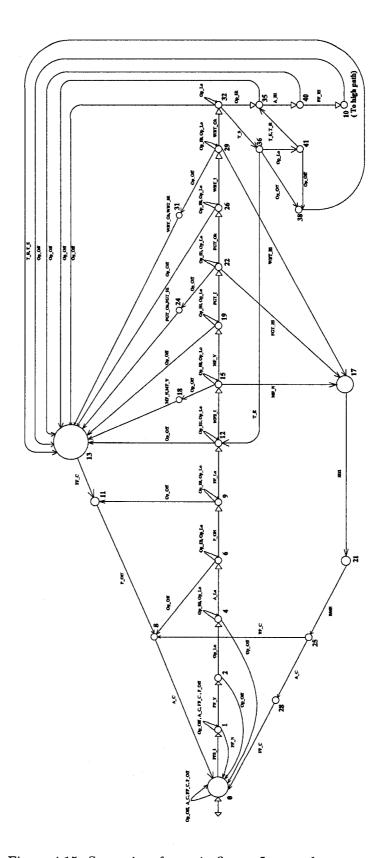

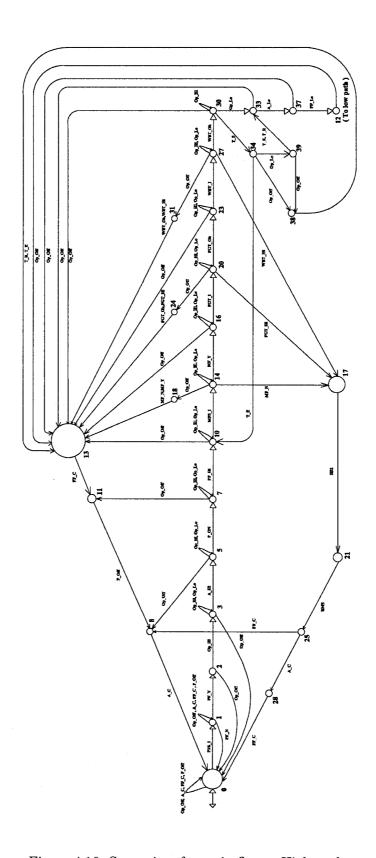

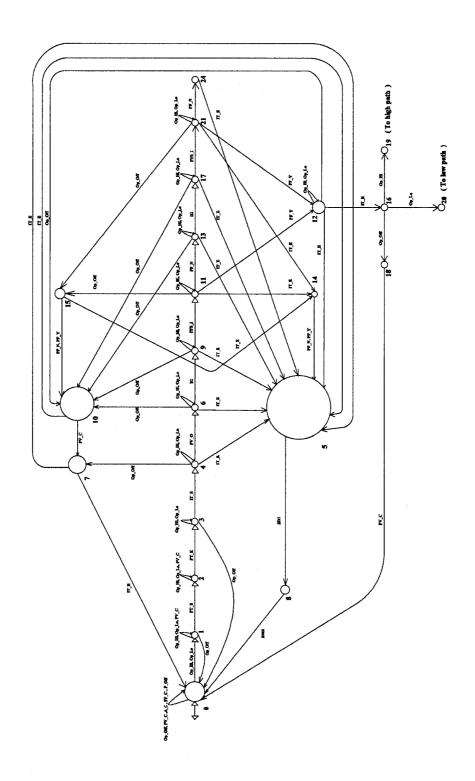

| 4.15 | Supervisor for main flame: Low path                                  | 60 |

| 4.16 | Supervisor for main flame: High path                                 | 61 |

| 4.17 | Complete boiler controller I/O devices                               | 62 |

| 4.18 | Complete boiler controller architecture                              | 63 |

| 4.19 | Typical operation sequence of boiler controller                      | 63 |

| 4.20 | Specification for complete boiler supervisor: Pilot path (TCT: COM-  |    |

|      | SPEC)                                                                | 64 |

| 4.21 | Specification for complete boiler supervisor: Low path (TCT: COM-    |    |

|      | SPEC)                                                                | 65 |

| 4.22 | Specification for complete boiler supervisor: High path (TCT: COM-   |    |

|      | SPEC)                                                                | 66 |

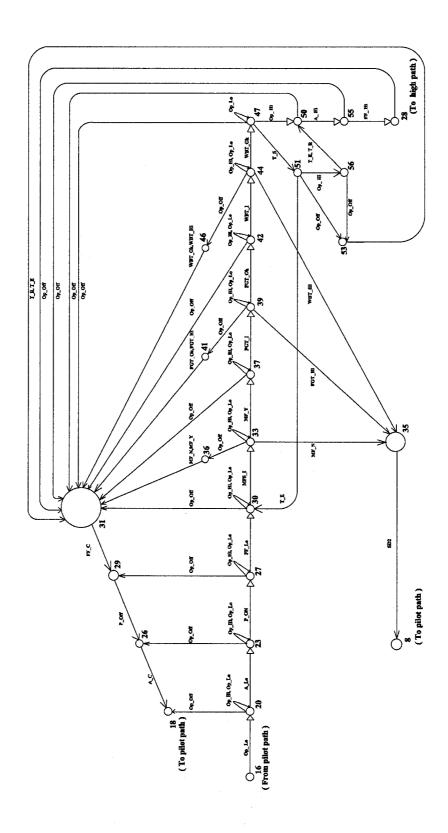

| 4.23 | Complete boiler supervisor: Pilot path                               | 67 |

| 4.24 | Complete boiler supervisor: Low path                                 | 68 |

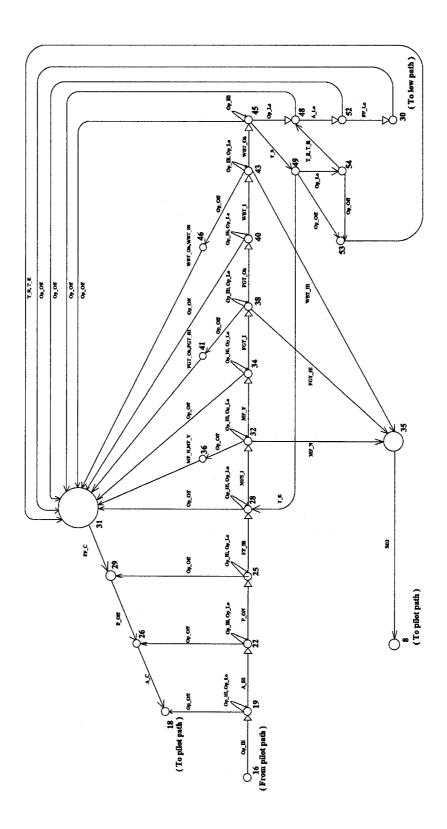

| 4.25 | Complete boiler supervisor: High path                                | 69 |

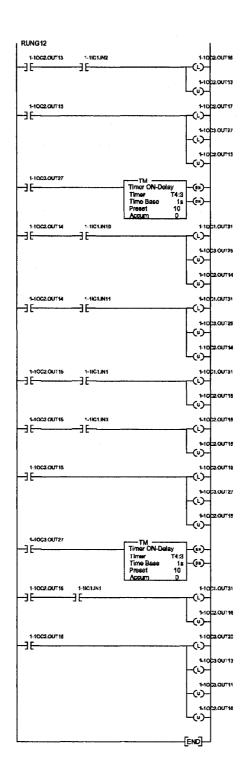

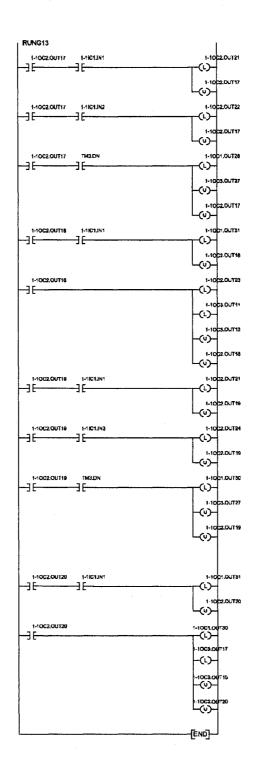

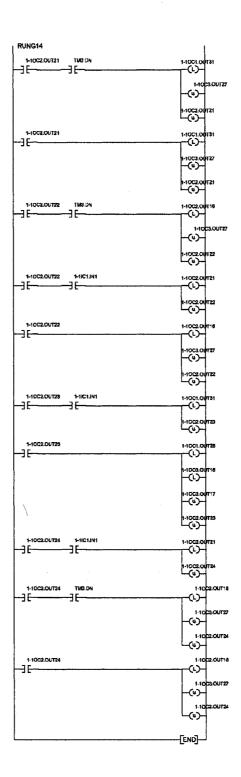

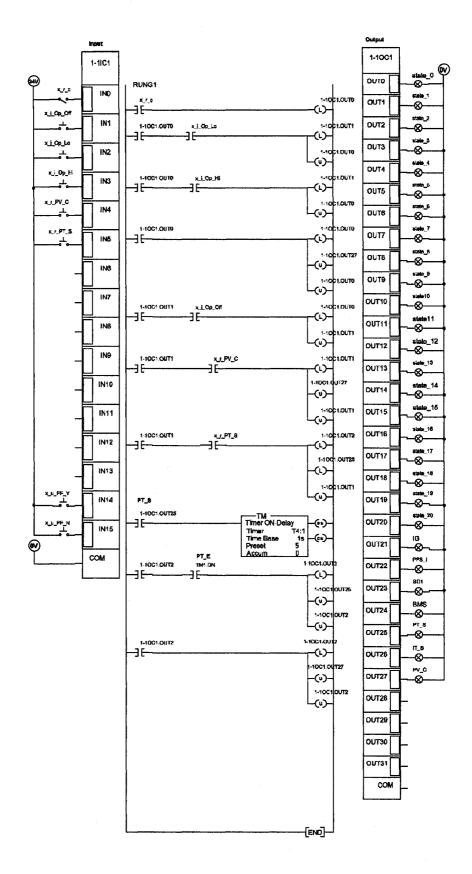

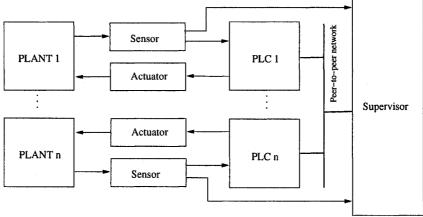

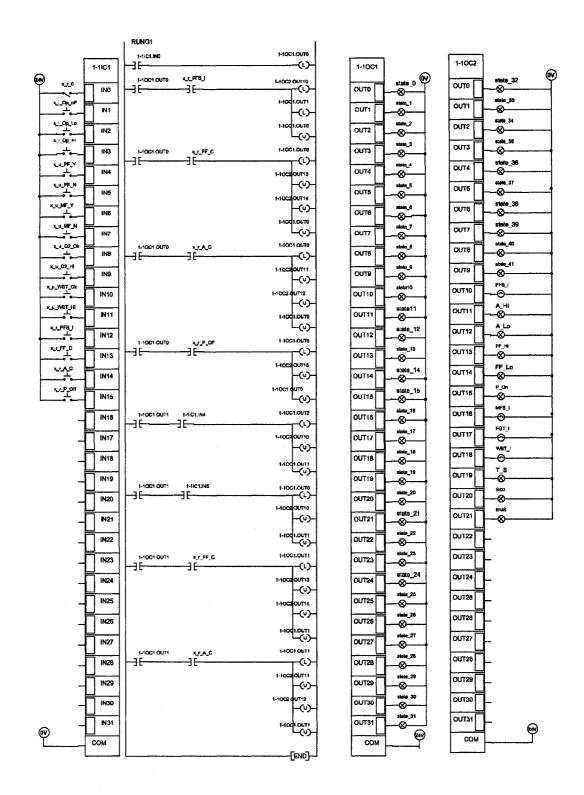

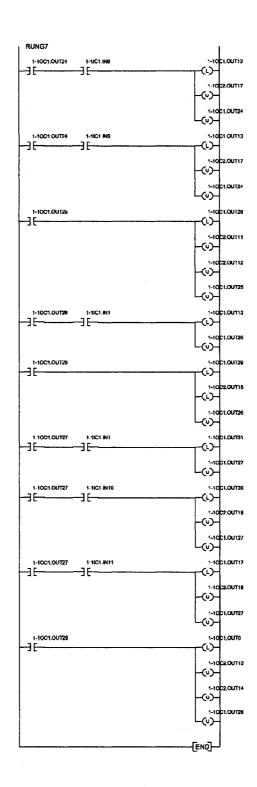

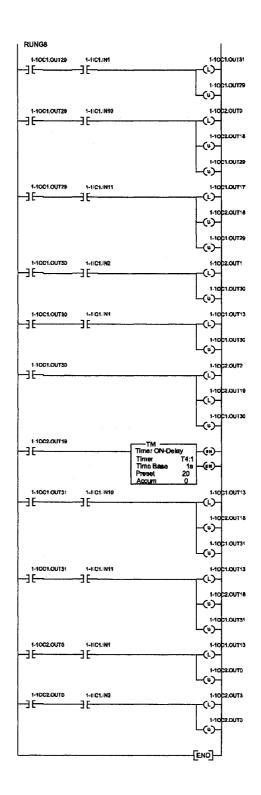

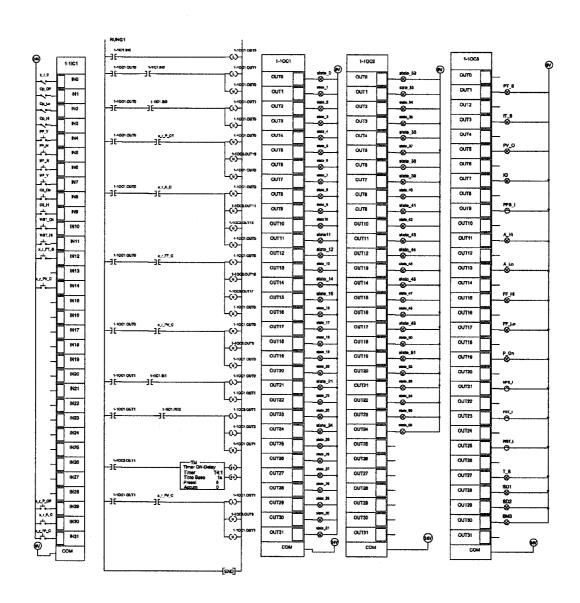

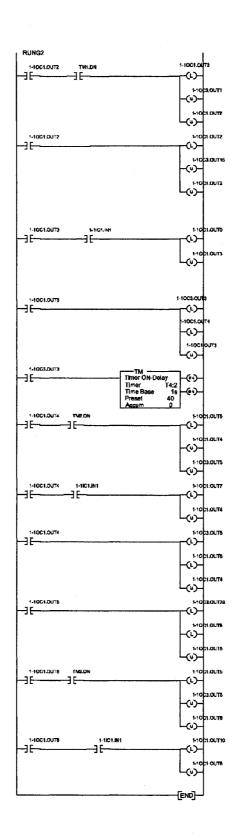

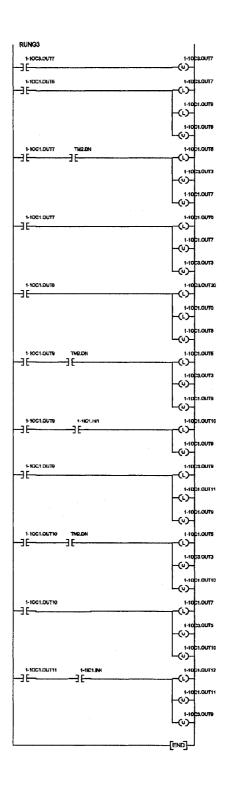

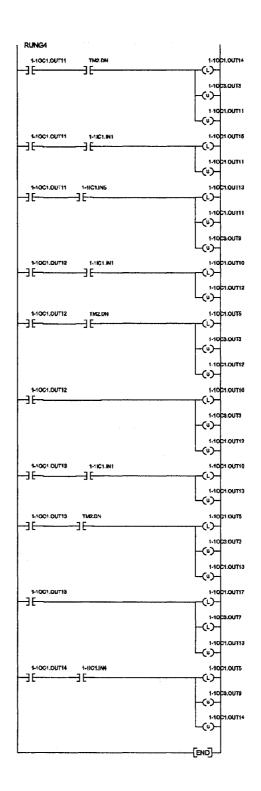

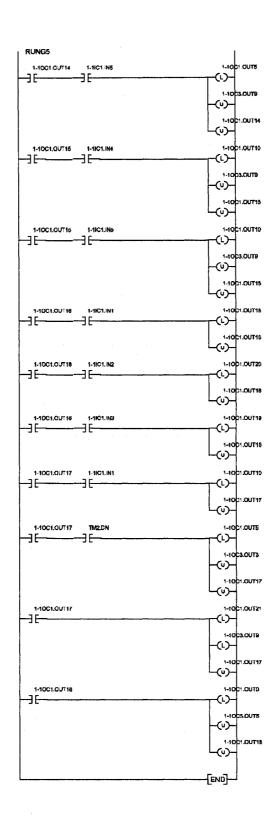

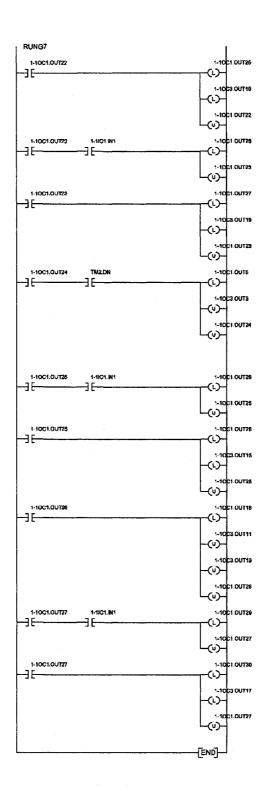

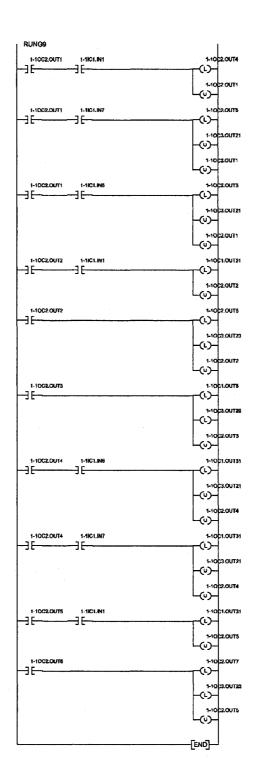

| 4.26 | A sample LLD of Pilot flame controller                               | 70 |

| 5.1  | A typical operation of PLC and DCS                                   | 74 |

## List of Tables

| 3.1 | List of rungs in LLD defining latch/unlatch function | 28 |

|-----|------------------------------------------------------|----|

| 3.2 | List of rungs in LLD defining operator input signals | 29 |

## Chapter 1

## Introduction

#### 1.1 Overview of the thesis

The present thesis follows two objectives. The main objective is to develop a general conversion algorithm which can be used to implement theoretical Discrete-Event System (DES) supervisors using physical devices called Programmable Logic Controllers (PLC). To verify the conversion technique and discuss the issues that may arise in modeling and development of DES supervisors, the real-field application to a boiler control system is investigated.

The Supervisory Control Theory (SCT) of discrete-event systems, introduced by Ramadge and Wonham (RW) [1] is a general theory to design supervisors for a wide range of discrete-event systems found in real-life applications. A (often minimally restrictive) supervisor, modeled by a finite automaton, is designed so that the system under supervision satisfies the specification of some desired behaviors. The supervisor can be implemented using PLC or other specialized hardware.

A PLC is a microprocessor-based specialized computer that performs many types of complex logic-based control functions [2], [3], [4]. PLC programs can be written by LLDs (Ladder Logic Diagrams) or Sequential Function Charts (SFCs) or other PLC programming languages [2], [3], [4]. In our work we choose LLD to program PLC.

The conversion of supervisor's automaton to LLD has already been addressed by many researchers [5], [6], [7], [8]. We observe that the implementation of RW supervisor using PLC lies intuitively on the theory itself, i.e. how controllable and uncontrollable events are translated by the designer, and mapped the actual event interpretations to the real systems using associated devices. We introduce a simple conversion technique which directly converts supervisor's automaton to LLD. We assume that controllable events can only appear in the form of (n+1)-state switches, which are then easily mapped to PLC output signals. A supervisor is described by a state machine which consists of a set of events and states. Supervisor moves from one state to the next in response to the occurrence of events, and specifies which controllable events should be disabled in the new state [9], [10]. PLC's operation can be seen from an input-output perspective [11] where the values of output signals are updated in response to input signals. In contrast to SCT, the PLC plays an "active" role by generating those controllable events that in SCT are generated by the plant and are enabled by the supervisor, and thus the notion of disabling events by a supervisor is replaced with generating enabled controllable events by the PLC controller.

We propose to partition states and events of the supervisor as PLC's input and output signals. As PLC handles signals only, we have to interpret supervisor's states and events as PLC signals. Generally, events occur instantaneously and causing transition from one state to another. We represent the plant events with the rising and falling edges of the input/output signals. By comparing signals between two ladder scan cycles [2], [3], [4], rising or falling edges can be easily detected. Our method clearly portrays how a user can define controllable and uncontrollable events as LLD signals. To test our approach, we design petrochemical boiler controllers using supervisory control theory, convert DES supervisors to LLD using our conversion technique, and finally test our design by setting a virtual plant setup using a PLC simulation software Automation Studio 5.2 [12].

### 1.2 Review of related works

The subject of conversion of RW supervisors to ladder logic diagrams has been well studied and already been addressed by many researchers [5], [6], [7], [8]. The implementation issue of supervisor using PLC has been first investigated by Brandin [5]. Brandin considers that supervisory control consists of three tasks and suggests how these tasks can be implemented by the PLC. These are: 1) Monitoring of the plant behavior: during every program scan, the status of the PLC inputs representing plant behaviors is evaluated. 2) Control evaluation: every state of the supervisor is

represented by an internal label. One such internal label is energized at any time and the supervisor's current state is represented by this internal label. Upon occurrence of events (where the corresponding PLC inputs are energized), these internals are latched and unlatched. Whenever supervisor reaches a state, outputs corresponding to the supervisory control map are energized. 3) Control enforcement: the enforcement of control commands can be carried out by the PLC output modules to energize the given outputs, which in turn enforces the corresponding events and thus their corresponding output devices.

Fabian and Hellgren [6] point out that physical implementation of a supervisor is not straightforward. They identify few problems that immediately arise when implementing the event-based asynchronous automata by the synchronous signal-based PLC. Few problems and the associated solutions they offered are listed below.

Events and signals. When associating events with rising and falling edges of signals, there might be a risk to introduce avalanche effect because of the sequential evaluation of the PLC program, which could be problematic when several states are sequentially stepped through by the occurrence of a single event. Due to this effect, PLC program might skip over a number of states during the same scan cycle. They suggests the problem may be solved by placing of rungs in an 'intelligent' order.

Causality. The SCT states that the plant generates all events, and the supervisor dynamically disables events if plant generates undesirable events. In other words, supervisor controls the plant to stay within the specifications. However, in PLC implementation the signals in the plant change in response to the signal changes generated by the PLC. Thus, the events that are not naturally generated by the plant can be generated by the PLC, and not more than one event should be generated by the PLC at the same time.

Choice. A supervisor is generally nondeterministic: in every state it offers the plant alternative events to choose from. However because of its deterministic nature PLC can only generate one event in every state—any subsequent events will be ignored as the system state may already be left as a result of the occurrence of the first event. If the choice is not explicitly made by the programmer, PLC will make the choice according to the rung order.

Inexact synchronization. When PLC executes its program it does not observe the plant. In general, program scan time is shorter than the plant response time. However, there is no guarantee that the PLC scan cycle time and plant response time are in phase; therefore, there might be a possibility that plant can change its state while the program is being executed. The changed state of the plant may invalidate the command issued by the program. This problem can be solved by the introduction of delay insensitive languages. The supervisor is delay insensitive if its choice is not invalidated by a plant event that can occur while the program is executed by the supervisor. The supervisor can always control the plant if it generates the command, and then wait for the plant response. Indeed, this is natural in PLC implementation.

Most of the suggestions described above are incorporated in our conversion method.

The first generalized conversion method for converting supervisors to LLDs (in the work termed as Relay Ladder Logic (RLL)) was addressed by Leduc and Wonham [8]. The method introduced by Leduc and Wonham first translates RW supervisors to equivalent Clocked Moore Synchronous State Machines (CMSSM), then expresses the boolean logic defining a CMSSM in Relay Ladder Logic (RLL), and finally RLL is run on PLCs. To facilitate the conversion method, a PLC-based testbed [13] is designed to simulate a manufacturing workcell and emphasize the problems of routing and collision. The method illustrates how CMSSM can be used to implement control functions in digital hardware. A CMSSM is represented by a 7-tuple, where all components are encoded by binary numbers implemented using boolean variables: inputs to the state machine, outputs from the state machine, state vector, next state function, output map, the initial or reset state, and period of the clock pulse that drives the state machine. The method introduces few functions to define each of the components of CMSSM. The inputs to the state machine are the DES events  $(\Sigma)$  and the outputs from the state machine are the DES controllable events  $(\Sigma_c)$ . The next state vector is determined by a number of boolean functions in input variables and current state variables; outputs from the state machine are also determined using boolean functions. In both cases, there is no general formula to define next state vectors and outputs.

A method closely related to our work is carried out in [7] by Liu and Darabi. By viewing a manufacturing system as a set of activities and their required resources,

a new event classification is used to formulate the conversion problem. In order to perform a set of activities, at least one resource is required by the manufacturing system. During each activity, a starting event happens as soon as all required resources are obtained by the activity; conversely, when the activity is complete, an activity ending event occurs. When a resource is allotted to an activity, a resource-activity latch event occurs while a resource-activity unlatch event occurs when a resource is freed from an activity. Other than resource latch/unlatch or activity starting/ending events, the events that change manufacturing system's state can be classified as system events i.e a machine breakdown event. The method proposes an overview of the implementation process in three steps. First, by identifying the activities and resources, RW supervisor event set is partitioned into activity and system events. Next, for each activity, missing events are added to complete the activity execution cycle (assigning resources - starting activity - ending activity - freeing resources) resulting in an extended model of RW supervisor. In extended supervisor, activity-resource and state-resource vectors are defined, where activity-resource vector is used to show the utilization of resources by activities, and state-resource vector is used to show the resource utilization status in each state. Finally, a conversion rule is addressed to convert the extended RW supervisor model to an equivalent LLD, where resource latch and unlatch events are identified as outputs, while ending and system events are inputs.

We develop a new conversion method taking our clue from [7]. We identify a given RW supervisor event set with the corresponding PLC Input/Output (I/O) signal sets, and introduce a simpler conversion technique which directly converts supervisor's automaton to LLD.

### 1.3 Implementation procedures and tools

There are different discrete-event controller construction techniques available in academia based on formalisms such as Petri nets and finite automata [7]. We choose finite automata-based controller construction technique, introduced by Ramadge and Wonham (RW) [1], to design our controllers. The constructed controllers are mathematically guaranteed to be controllable and maximally permissive for a given DES plant and specification. Before the synthesis of a PLC-based solution in the DES

framework, we first need to identify the control problem wherein a controller is to be designed so that the controlled system satisfies some desired specifications.

Discrete-event systems cover a wide variety of physical systems such as manufacturing systems, traffic systems, communication protocols, logistic management systems and data communication networks. We design boiler control systems which are used in petrochemical industries to demonstrate our PLC-based implementation. Once plants and legal specifications are specified, one can use XPTCT software (we use version 114 for Windows 95/98/XP) [14] to design DES supervisors. The DES supervisor is then converted into LLD using our conversion technique. Finally the translated LLD is uploaded and simulated using PLC simulation software Automation Studio [12]. Necessary adjustments in the design procedures are carried out until the simulation results meet the specification requirements. If the simulation results satisfy user's requirements, PLC-based solution of the control problem can be developed using required hardware. The step-by-step guide for implementing DES supervisor using PLC is shown in Figure 1.1.

#### 1.4 Outline of the thesis

The rest of this thesis is organized as follows. An overview of supervisory control theory of discrete-event systems and programmable logic controllers is presented in Chapter 2. After elaborately discussing a motivating example, and making some key observations and assumptions, the conversion technique is proposed in Chapter 3. Chapter 4 studies the real-field application of boiler control systems in DES framework. It also includes details of the boiler control plants, discussions of modeling I/O devices as DES, specifications of boiler controllers, construction of the boiler control supervisors using XPTCT software and implementation of the boiler controllers using PLC. Finally, Chapter 5 concludes the thesis and points out directions for future research.

Figure 1.1: Implementation sequence.

## Chapter 2

## **Preliminaries**

### 2.1 Supervisory control of DES

#### 2.1.1 DES plant, specification and supervisory control

The supervisory control theory provides an optimal solution to control a wide variety of physical systems that are discrete in time and state space, asynchronous, and nondeterministic. In Ramadge and Wonham (RW) theory [1], a plant can be thought of as the generator of a formal language and can be modeled as an automaton, which can be graphically represented by a transition graph. Let  $G = (Q, \Sigma, \delta, q_0, Q_m)$  be an automaton representing a DES plant where Q is the set of states,  $\Sigma$  is the events set,  $\delta: Q \times \Sigma \to Q$  is the partial state transition function,  $q_0 \in Q$  is the initial state and  $Q_m \subseteq Q$  is the subset of marker states commonly used to "mark" some states where a certain task is complete. The disjoint subsets  $\Sigma_c$  and  $\Sigma_u$ , where  $\Sigma = \Sigma_c \dot{\cup} \Sigma_u$ , consist of controllable and uncontrollable events, respectively. A language L over  $\Sigma$  is any subset of  $\Sigma^*$ , where  $\Sigma^*$  denotes the set of all finite strings over  $\Sigma$ , including the empty string  $\epsilon$ . The behaviors of G are distinguished as closed and marked. The closed behavior of DES G is the set of all possible event sequences which the plant may generate and is formally defined as

$$L(G) = \{ s \in \Sigma^* \mid \delta(q_0, s)! \}$$

The marked behavior of DES G is comprised of those sequences in the closed behavior which reach some marker states and is formally defined as

$$L_m(G) = \{ s \in \Sigma^* \mid \delta(q_0, s) \in Q_m \}$$

The DES G is said to be *nonblocking* if every reachable state is coreachable (reachable and coreachable states are defined below). When G is nonblocking we have:

$$\overline{L_m(G)} = L(G)$$

A language  $K \subseteq \Sigma^*$  is controllable with respect to G iff

$$\bar{K}\Sigma_u \cap L(G) \subset \bar{K}$$

When K is controllable the prefix closure  $\overline{K}$  is invariant under the occurrence of uncontrollable events in L(G). By specifying a subset of  $\Sigma_c$ , a particular subset of events to be enabled can be selected. Since uncontrollable events are always enabled, all  $\Sigma_u$  events are adjoined to this set. Each such subset of events is called a *control pattern*, and the set of all control patterns is denoted by  $\Gamma = \{\gamma \subseteq \Sigma | \gamma \supseteq \Sigma_u\}$ . A supervisory control for G is any map  $V: L(G) \to \Gamma$ . The pair (G, V) will be denoted as V/G, to suggest 'G under the supervision of V'. The closed behavior of V/G is defined to be the language  $L(V/G) \subseteq L(G)$  defined below:

i.  $\epsilon \in L(V/G)$ ,

ii. If

$$s \in L(V/G) \land \sigma \in V(s) \land s\sigma \in L(G) \Rightarrow s\sigma \in L(V/G)$$

,

iii. No other strings belong to L(V/G).

The map V is nonblocking for G if

$$\overline{L_m(V/G)} = L(V/G)$$

If  $K \subseteq L_m(G)$  is controllable with respect to G and  $L_m(G)$ -closed, then there exists a non-blocking supervisory control map V for G such that L(V/G) = K [1].

Let S be any automaton such that  $L(V/G) = L(S) \cap L(G)$ . Then S is said to implement V. If L(S) is controllable with respect to G and  $\overline{L_m(S) \cap L_m(G)} = L(S) \cap L(G)$ , we say S is a supervisor for G.

Let  $E \subseteq \Sigma^*$  be the specification of some desired behaviors. Then the supervisory control theory articulates how a supervisor S can be designed to control the plant so that the plant under supervision can enjoy maximum freedom while behaving within the specification E. When E is not controllable with respect to G it is shown that a supremal controllable and  $L_m(G)$ -closed sublanguage of E, denoted by  $\hat{K}$  exists. It follows from the main theorem in supervisory control theory [1] that a minimally

restrictive (thus optimal) nonblocking supervisory control  $\hat{V}$  can be designed such that  $L_m(\hat{V}/G) = \hat{K}$ .

Consider two automata  $G_1 = (Q_1, \Sigma_1, \delta_1, q_{10}, Q_{1m})$  and  $G_2 = (Q_2, \Sigma_2, \delta_2, q_{20}, Q_{2m})$ . The synchronous product of  $G_1$  and  $G_2$  is the *reachable* (denoted by 'Rch'; defined below) part of the automaton

$$G_1 \parallel G_2 := Rch(Q_1 \times Q_2, \Sigma_1 \cup \Sigma_2, \delta, (q_{10}, q_{20}), Q_{1m} \times Q_{2m})$$

where for  $(q_1, q_2) \in Q_1 \times Q_2$  and  $\sigma \in \Sigma$ ,

$$\delta((q_1, q_2), \sigma) = \begin{cases} (\delta_1(q_1, \sigma), \delta_2(q_2, \sigma)) & \text{if } \delta_1(q_1, \sigma)! \text{ and } \delta_2(q_2, \sigma)! \\ (\delta_1(q_1, \sigma), q_2) & \text{if } \delta_1(q_1, \sigma)! \text{ and } \sigma \not\in \Sigma_2 \\ (q_1, \delta_2(q_2, \sigma)) & \text{if } \delta_2(q_2, \sigma)! \text{ and } \sigma \not\in \Sigma_1 \\ \text{undefined} & \text{otherwise} \end{cases}$$

#### 2.1.2 Operations on DES

To design a supervisor using RW supervisory control theory, the following operations on languages are carried out.

#### Trim

DES G is trim if it is both reachable and coreachable, that is, all states can be reached from the initial state, and some marker states can be reached from every state. The set of reachable states is formally defined as

$$Q_r = \{ q \in Q \mid (\exists s \in \Sigma^*) \delta(q_0, s) = q \};$$

G is reachable if  $Q_r = Q$ . The set of coreachable states is formally defined as

$$Q_{cr} = \{ q \in Q \mid (\exists s \in \Sigma^*) \delta(q, s) \in Q_m \};$$

G is coreachable if  $Q_{cr} = Q$ .

#### Synchronous product

Synchronous product specifies how several plant components can function jointly, and is denoted by  $\parallel$ . If  $L_1 = L_m(G_1)$  and  $L_2 = L_m(G_2)$ , then  $G_1$  and  $G_2$  can generate

$L_1 \parallel L_2$  only when common events are eligible to occur synchronously in both plants, while individual plant events are allowed to occur whenever they are eligible in their corresponding components. Let  $L_1 \subseteq \Sigma_1^*$ ,  $L_2 \subseteq \Sigma_2^*$ , where  $\Sigma = \Sigma_1 \cup \Sigma_2$ . Define natural projection

$$P_i: \Sigma^* \to \Sigma_i^* \qquad (i=1,2)$$

according to

$$P_i(\epsilon) = \epsilon$$

$$P_i(\sigma) = \begin{cases} \epsilon & \text{if } \sigma \notin \Sigma_i \\ \sigma & \text{if } \sigma \in \Sigma_i \end{cases}$$

$$P_i(s\sigma) = P_i(s)P_i(\sigma) \qquad s \in \Sigma^*, \sigma \in \Sigma$$

The action of natural projection  $P_i$  on a string s is to eliminate all occurrences of  $\sigma$  in s such that  $\sigma \notin \Sigma_i$ . The synchronous product  $L_1 \parallel L_2 \subseteq \Sigma^*$  of two languages  $L_1 \subseteq \Sigma_1^*$  and  $L_2 \subseteq \Sigma_2^*$  is defined according to

$$L_1 \parallel L_2 = P_1^{-1}L_1 \cap P_2^{-1}L_2$$

That is,  $s \in L_1 \parallel L_2$  iff  $P_1(s) \in L_1$  and  $P_2(s) \in L_2$ . Thus synchronous product of two DES  $G_1$  and  $G_2$ , denoted by  $G = G_1 \parallel G_2$ , was previously defined. We have:

$$L_m(G) = L_m(G_1) \parallel L_m(G_2), \qquad L(G) = L(G_1) \parallel L(G_2)$$

#### Meet

Meet is the special case of synchronous product corresponding to  $\Sigma_1 = \Sigma_2$ ; specifically all events are considered shared and synchronization is total. The meet operation blocks any transition which cannot occur in both  $G_1$  and  $G_2$ . Consider two automata  $G_1 = (Q_1, \Sigma_1, \delta_1, q_{10}, Q_{1m})$  and  $G_2 = (Q_2, \Sigma_2, \delta_2, q_{20}, Q_{2m})$ . The meet of  $G_1$  and  $G_2$  is the reachable part of the automaton

$$G_1 \wedge G_2 := Rch(Q_1 \times Q_2, \Sigma_1 \cap \Sigma_2, \delta, (q_{10}, q_{20}), Q_{1m} \times Q_{2m})$$

where for  $(q_1, q_2) \in Q_1 \times Q_2$  and  $\sigma \in \Sigma$ ,

$$\delta((q_1, q_2), \sigma) = \begin{cases} (\delta_1(q_1, \sigma), \delta_2(q_2, \sigma)) & \text{if } \delta_1(q_1, \sigma)! \text{ and } \delta_2(q_2, \sigma)! \\ \text{undefined} & \text{otherwise} \end{cases}$$

Given two DES  $G_1$  and  $G_2$ , the meet operation produces a reachable DES  $G = G_1 \wedge G_2$  such that

$$L_m(G) = L_m(G_1) \cap L_m(G_2), \qquad L(G) = L(G_1) \cap L(G_2)$$

#### 2.1.3 DES Supervisor

A supervisor is an external agent responsible for controlling the system. It monitors and controls the behavior of the system (a set of plants) so that it complies with some specifications; if supervisor observes any possible exit to the illegal behavior, it will restrict the plant's behavior by disabling a subset of controllable events to achieve a maximally permissive control solution. A supervisor can be represented by an automaton:

$$S = (X, \Sigma, \xi, x_0, X_m)$$

The control action of S on G can be visualized as follows: upon arriving at a state  $x \in X$ , an event  $\sigma \in \Sigma$  is enabled if  $\xi(x,\sigma)!$ ; otherwise it is disabled. Note that the uncontrollable events cannot be controlled and thus their occurrence should not be disabled by the supervisor. The closed-loop behavior of the plant G under the supervision of S, denoted by S/G (also called the supervised system), can be formalized by the meet of S and G.

Consider a supervisor S for G which can be represented by an automaton  $S = (X, \Sigma, \xi, x_0, X_m)$ . The closed-loop behavior of the plant G under the supervision of S, denoted by S/G can be formalized by the meet of S and G, that is  $S/G = G \wedge S$ , and therefore:

$$L(S/G) = L(S) \cap L(G)$$

$$L_m(S/G) = L_m(S) \cap L_m(G)$$

#### 2.1.4 TCT: DES supervisor design software

TCT<sup>1</sup> is a design software developed by W. M. Wonham's research team at University of Toronto [14]. TCT is used for the synthesis of supervisory control for untimed discrete-event systems. The descriptions thereafter about TCT procedures are reproduced from [9]. An automaton is represented by a 5-tuple [Size, Init, Mark, Voc,

<sup>&</sup>lt;sup>1</sup>Where XPTCT refers to Windows version of the DES supervisor design software TCT.

Tran], where Size is the number of states and the state set is  $\{0, \dots, \text{Size} - 1\}$ , Init is the initial state (always taken to be 0), Mark lists the marker states, Voc is a list of vocal states, and Tran is the transition table. The automata models in this thesis do not have output and thus Voc is always taken to be empty. A transition is a triple [I, E, J] representing a transition from the exit state I to the entrance state J and having event label E. E is an odd or even nonnegative integer, depending on whether the corresponding event is controllable or uncontrollable, respectively.

In this work we use deterministic automata to model DES: distinct transitions from the same exit state must carry distinct labels.

The following is a list of procedures we use in system design. A complete list can be found in [9].

create prompts the user to define a new discrete-event system.

selfloop augments an existing DES by adjoining selfloops at each state with event labels in a list provided by the user.

trim applied to DES1 constructs the trim (reachable and coreachable) automaton DES2.

sync forms the reachable synchronous product of DES1 and DES2 to create DES3.

meet forms the meet (reachable cartesian product) of DES1 and DES2 to create DES3. Note that DES3 need not be coreachable.

supcon for a controlled generator DES1 and specification DES2 forms a trim recognizer for the supremal controllable sublanguage of the marked language generated by DES2 to create DES3. The resulting DES3 is a proper supervisor for DES1.

minstate reduces DES1 to a minimal state transition structure DES2 that generates the same closed and marked languages. DES2 is reachable but not necessarily conreachable.

isomorph tests whether DES1 and DES2 are identical up to renumbering of states; if so, their state correspondence is displayed.

The following is a list of utilities we use in system design:

edit allows the user to modify an existing DES.

- show SE displays an existing DES, SA a data (condat) table, SX a TXT (text) file. Tables can be browsed with page keys. MAKEIT.TXT keeps a record of user files as they are generated.

- file FE (resp. FA) converts a DES (resp. DAT) file to an ASCII PDS text file (resp. PDT) or Postscript PSS file (resp. PST) for printing. Some printers may only recognize a Postscript file with suffix .PS; in that case, rename the .PSS/.PST files with due care to avoid duplication.

user file directory lists the current user subdirectory.

#### 2.1.5 Design of DES supervisor using TCT

Let the controlled DES G representing the plant be given together with an upper bound  $E \subseteq \Sigma^*$  on admissible marked behavior. Assume that EDES is the specification automaton such that  $E = L_m(EDES)$ . Our objective is to design an optimal supervisor KDES for G. To compute a trim recognizer for the language  $K := \sup C(E \cap L_m(G))$ , the TCT procedure supcon computes a trim representation KDES of K according to

$$KDES = supcon(G, EDES)$$

The set of controllable events that must be disabled by KDES can be found using TCT procedure condat. Specifically, the condat operation returns the control pattern at each state of KDES according to

$$KDAT = condat(G, KDES)$$

If there are n plant components and m specifications, G is the sync of all plant components while EDES is the meet of all specifications. The supervisor is then computed following the above procedures.

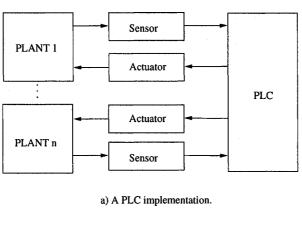

### 2.2 Programmable Logic Controller (PLC)

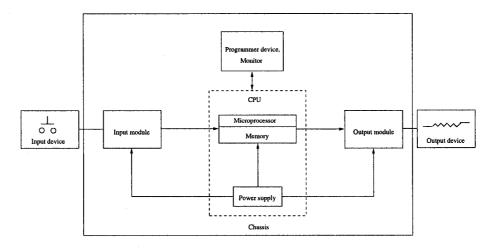

A Programmable Logic Controller (PLC) is a microprocessor-based specialized computer that performs many types of complex logic-based control functions [2], [3], [4]. The main purpose of PLC is to continuously monitor process control parameters and manipulate plant operations by means of stored program set by the user. A PLC is designed to operate in a wide range of industrial environments such as high heat, humidity and vibrations. Their flexibility, reliability, maintainability, affordability and user friendliness make them immensely popular, and thus widely used in many industrial applications. The overall system layout of PLC and interconnection of each part are shown in Figure 2.1.

Figure 2.1: Layout of PLC.

The input module has terminals where plant electrical signals responded by input field devices are received. There are various types of input devices available to be connected to the input module which are mainly on/off switches. The common types of switches are toggle-type switches and pushbutton switches. When a pushbutton switch is pressed, the corresponding input contact becomes TRUE momentarily, while when the toggle-switch is pressed, the corresponding input contact becomes TRUE and remains TRUE until the switch is depressed. Other types of switches have either Normally<sup>2</sup> Open (NO) or Normally Close (NC) configuration. The most commonly used device in this category is the limit switch. When the limit switch is actuated, its electrical contact changes from NO to NC (action can be taken as on/off), or NC

<sup>&</sup>lt;sup>2</sup>Normally means device is in unactuated state.

to NO (action can be taken as off/on). Some other types of input on/off devices are pressure switch, level switch, float switch, magnetic-sensitive switch and inductive-sensitive switch. Other types of input devices, such as potentiometer and transducer, can be used to produce a varying input electrical signal to PLC input module.

Similarly, the output module has terminals from where output signals are sent to activate output field devices. The most common output device is electrical solenoid which is used for on/off control of flow valves such as gas and liquid control valve. Other on/off output devices are relays, motors and various solid-state switching devices. A special type of output devices which can be controlled by PLC are analog output devices such as stepper motors, servomotors and servo valves.

The logic operations are carried out by microprocessor while data, user program and system software are stored and retrieved from memory.

PLC programs can be written by LLDs (Ladder Logic Diagrams) or Sequential Function Charts (SFCs) or other PLC programming languages [2], [3], [4]. A PLC program, often consisting of a set of boolean statements and linking inputs to outputs via their corresponding internal table, is evaluated sequentially from top to bottom and from left to right.

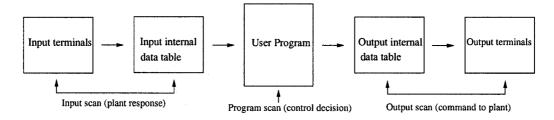

Figure 2.2: PLC scan cycle.

Each PLC operational cycle, called *scan cycle*, is made up of three parts, as shown in Figure 2.2: 1) Reading inputs (whether an input device is energized or de-energized) and updating the input status table. 2) Executing the control logic set by the user program, and updating the output status table. 3) Finally transferring the data associated with the output status table to the outputs (energize/de-energize output devices). Consequently, a PLC's operation can be seen from an input-output perspective where output signals update their states in response to the input signals, as shown in Figure 2.3.

In the PLC, the input scan, program scan and output scan are separate functions.

Figure 2.3: A simple PLC I/O view.

Thus, any changes in the input device status during the program scan or output scan are not accepted by the PLC until the next input scan. Moreover, during the input and program scans, data changes in the output table are not forwarded to the output terminals. The new data which may change the states of the output devices is forwarded only during the output scan. The total response delay for one complete scan cycle, termed as scan time, is a function of the processor speed and length of the user program; typically, scan time may vary from 1 ms to 100 ms [5].

One of the main assumptions about DES is that events occur asynchronously. Due to scan time and the sequential operation of the PLC, the occurrence of events must be interpreted synchronously (one event before the other with at least some time gap) by the PLC. For the purpose of implementation of DES supervisor using PLC, the deviation of implementing the event-based asynchronous automata by the synchronous signal-based PLC could cause timing problems (the time gap between the occurrence of one event to another in PLC implementation, and the time gap between the PLC and plant response since PLCs are faster than plants), and we may refer to this timing problem as transmission delay or response delay. It is quite natural in any PLC implementation that once output data (command) is transferred to output devices by the PLC, PLC is needed to wait for plant response (input) to re-evaluate its output data. This necessity is because nominally PLCs are faster than plants, and therefore, plants response delay can be ignored.

#### 2.2.1 Ladder Logic Diagrams (LLDs)

A ladder logic is made up of many rungs, each consisting of logical checkers (input contacts) which become true or false in response to plant outputs communicated via sensors, and output coils which drive some actuators or hold an internal storage bit that can be used in other parts of the ladder. If the logic statement is true, the contact

can "make" the circuit to energize output coils. If the logic statement is false, the contact can "break" the circuit to de-energize output coils. There are many types of contact and coil functions available for PLC programming. See [2], [3], [4], [5], [6] and [15] for details. In our work, we use normally open contacts and both latch and unlatch functions for output coils, as shown in Figure 2.4.

| Component                | Function                                                                                                                      |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Y                        | Examine if boolean variable $Y$ is TRUE.                                                                                      |

| Y Normally close contact | Examine if boolean variable $Y$ is FALSE.                                                                                     |

| X<br>—(L)—<br>Latch      | If logic statement on the left of the rung is TRUE, boolean variable $X$ becomes TRUE and remains TRUE until it is unlatched. |

| X —(U)— Unlatch          | If logic statement on the left of the rung is TRUE, boolean variable $X$ becomes FALSE and remains FALSE until it is latched. |

Figure 2.4: Some LLD components.

A normally open (NO) contact is used to examine if the boolean variable Y is TRUE. If the left state (TRUE/FALSE) of the contact of the boolean variable Y is TRUE, NO contact can "make" the circuit to energize output coils; otherwise, the right state of the contact is FALSE. Conversely, a normally close (NC) contact is used to examine if the boolean variable Y is FALSE. If the left state (TRUE/FALSE) of the contact of the boolean variable Y is TRUE, NC contact can "break" the circuit to de-energize output coils; otherwise, the right state of the contact is TRUE. After the evaluation of a logic statement, output of a rung is assigned by various kinds of coils such as latch and unlatch coil. These coils can be connected to physical output devices to be operated, or can be used to hold internal storage bits that can be referred to in other parts of the program for logic statements. When the logic statement on the left of the rung is TRUE, boolean variable X of the latch coil becomes TRUE (the associated output device is energized) and remains TRUE until it is unlatched. On the other hand, if the logic statement on the left of the rung is TRUE, boolean variable X of the unlatch coil becomes FALSE (the associated output device is de-energized) and remains FALSE until it is latched.

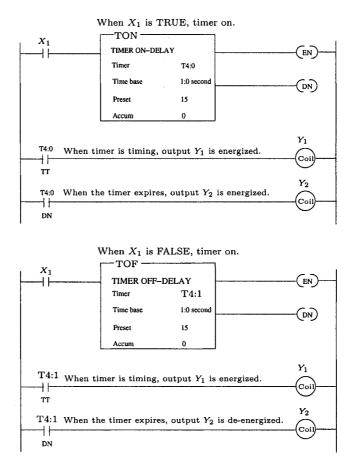

Other than contacts and coils, the most commonly used control device in the

PLC is the timer. Although industrial and digital electronic timers are available to use with PLC, all these timers can be replaced by using various kinds of PLC timer functions such as TIMER ON-DELAY and TIMER OFF-DELAY. An example of TIMER ON-DELAY function in the LLD, which we used in our implementations, is explained in Figure 2.5. TIMER-OFF DELAY is also included in the same figure for completeness.

Figure 2.5: TIMER ON-DELAY and TIMER OFF-DELAY in LLD.

TIMER ON-DELAY works as follows: when  $X_1$  is TRUE, the PLC starts the timer (addressed as T4:0) and the accumulated value of the timer is incremented in 1 second intervals. While the timer is accumulating time, T4:0 TT (timer internal contact) becomes TRUE as well as the output coil  $Y_1$  is energized. When the timer expires, T4:0 TT becomes FALSE as well as the output coil  $Y_1$  is de-energized and T4:0 DN becomes TRUE by which the output coil  $Y_2$  is energized. If the accumulated value reaches 15 seconds (user can preset this value as desired) or  $X_1$  becomes FALSE, the timer will be reset.

TIMER OFF-DELAY works as follows: when  $X_1$  is FALSE, the PLC starts the timer (T4:1). The accumulated value of the timer is incremented in 1 second intervals. While the timer is accumulating time, T4:1 TT becomes TRUE as well as the output coil  $Y_1$  is energized. When the timer expires, T4:1 TT becomes FALSE as well as the output coil  $Y_1$  is de-energized and T4:1 DN becomes FALSE by which the output coil  $Y_2$  is de-energized. If the accumulated value reaches 15 seconds (user can preset this value as desired) or the  $X_1$  becomes TRUE, the timer will be stopped. When  $X_1$  becomes FALSE again, the timer is reset and restarted.

When PLC is programmed using LLDs, the following ladder construction limitations must be taken into account. If incorrectly formatted LLDs are uploaded in the PLC, it will not accept the LLDs and report an error message. These limitations may vary depending on individual PLC manufacturers. It is recommended to consult with the individual operation manuals for proper programming information of a given PLC system. For proper construction of LLDs, we generally follow the guidelines mentioned in [2], [3] for LLD-based programming of Allen-Bradley and Siemens PLCs using PLC simulation software Automation Studio [12]. Since Automation Studio [12] supports only ladder libraries for Allen-Bradley and Siemens PLCs, we use both types of PLCs in our work. The common instructions are given below. The essence of the figures for the LLD instructions is taken from [3].

#### Contact placement.

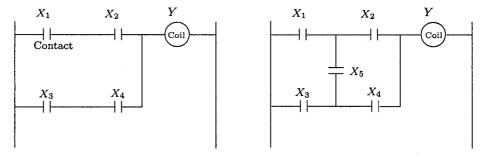

1. A contact must always be placed in the upper left of the rung, as shown in all of the following figures.

- a) All contacts are placed horizontally (correct).

- b)  $X_5$  is placed vertically (incorrect).

Figure 2.6: Contact placement in LLD.

- 2. All contacts must be placed horizontally; contacts are not allowed to be placed vertically. In Figure 2.6 (part b), contact  $X_5$  is placed incorrectly, whereas in the same figure (part a) all contact are positioned correctly.

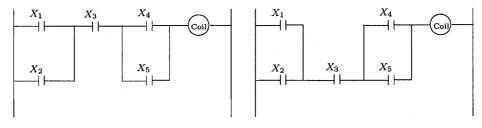

- 3. The number of contacts per matrix (per logic statement) must be within 11 across by 7 down, as shown in Figure 2.7 (part c).

- a) Correct straight across orientation of contacts.

- b) Incorrect straight across orientation of contacts.

Figure 2.7: Contact placement in LLD.

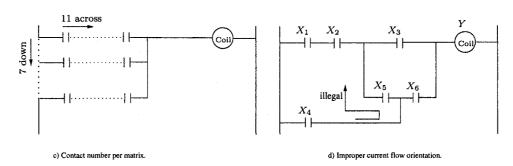

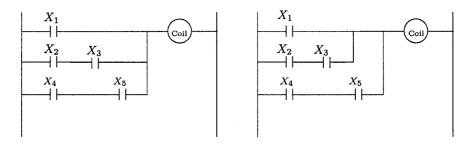

- 4. Contacts must be nested (a branch circuit is placed within a branch circuit) properly, as described in Figure 2.8 (part a and b).

- 5. Contacts must be placed in straight across, as described in Figure 2.7 (part a and b).

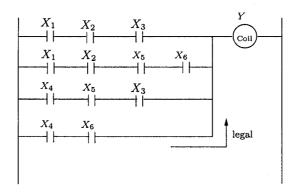

- 6. Contacts must be inserted in the rung such that the current conduction through contacts is considered to flow from left to right. This is shown in Figure 2.7 (part d), Figure 2.8 (part c), and described as follows. When (refer Figure 2.7 (part d)) output for Y is considered as Y = X<sub>1</sub> · X<sub>2</sub> · X<sub>3</sub> + X<sub>1</sub> · X<sub>2</sub> · X<sub>5</sub> · X<sub>6</sub> + X<sub>4</sub> · X<sub>5</sub> · X<sub>3</sub> + X<sub>4</sub> · X<sub>6</sub>, in this case current can flow from right to left through contact number 5 via 4 and 3; therefore this type of contacts placement is not legal. While, in Figure 2.8 (part c) the proper current flow for output Y is considered as Y = X<sub>1</sub> · X<sub>2</sub> · X<sub>3</sub> + X<sub>1</sub> · X<sub>2</sub> · X<sub>5</sub> · X<sub>6</sub> + X<sub>4</sub> · X<sub>5</sub> · X<sub>3</sub> + X<sub>4</sub> · X<sub>6</sub>, in this case current can always flow from left to right; therefore this type of contacts placement is legal.

a) Correct nested program orientation.

b) Incorrect nested program orientation.

c) Proper current flow orientation.

Figure 2.8: Contact placement in LLD.

#### Coil placement.

- 1. A coil must always be placed at the end of a rung, as is the case in all of the figures above.

- 2. One output coil can be assigned to a group of contacts.

- Coil can be used either to drive an output device or hold an internal storage bit that can be referred to in other parts of the rung for logic statements.

### 2.2.2 Automation Studio: A PLC simulation software

Automation Studio [12] is an ISO standard integrated software that can be used to design, simulate, document and animate circuits comprising of various automation technologies such as PLCs, pneumatics, hydraulics, sequential function charts

and electrical controls. Automation Studio allows users to design circuits or simulation platforms using its various libraries and modules such as PLC ladder logic and electrical controls. The PLC (Allen-Bradley and Siemens) ladder logic library includes all ladder logic functions such as contacts, coils and timers. The electrical controls library which comes complete with switches, relays, solenoids, push buttons and power supplies may be required to construct an experimental platform of any complex systems. The libraries of Automation Studio are listed in various groups of component category. The components' list can be searched easily, then the required component can be selected, and dragged and dropped onto the schematics or the program. It is allowed to name components following a suggested guideline. Users can simulate, experiment and implement possibly any virtual plants or control systems using Automation Studio ladder logic library and other appropriate libraries. During simulation, plant components become animated and electrical lines are color-coded according to their states from which the user can observe the simulation results. Users can further manipulate the simulation pace using available functions such as normal/slow motion and step-by-step. By using I/O interface hardware (with a limited number of I/O), users can directly connect Automation Studio to a real PLC I/O or to real equipments such as relays, valves and sensors. Automation Studio can then be used as a replacement of PLC to control the targeted equipments. More software details and sample videos can be found in [12].

## Chapter 3

## Conversion Algorithm

### 3.1 Event generation and supervisory control

In supervisory control of DES a supervisor plays a "passive" role in that it observes discrete evolution of the system and at any point it can disable a subset of controllable events. Thus plant plays the role of generating controllable and uncontrollable events alike, and controllable events can only be disabled by the supervisor. In contrast, in our proposed PLC implementation of supervisory control map represented by the supervisor's automaton, the PLC plays an "active" role by generating those controllable events that in SCT are generated by the plant and enabled by the supervisor, and that the notion of disabling events by a supervisor is replaced with generating enabled events by the PLC controller. This is similar to the idea addressed by Balemi [11] to indicate the fact that for most real systems plant events are not generated spontaneously, but only as the responses to given commands generated by the supervisor. In our method, this idea of identifying the sources of events (which events are generated by the plant, and which events are generated by the supervisor) is implemented.

We observe that this assumption is not restrictive at all: it is quite logical to envisage that a motor cannot be turned on arbitrarily, and something or someone (which is PLC or human operator) must generate such a relevant event according to control specifications to activate/de-activate a motor.

### 3.2 Event interpretation: DES to LLD

The SCT describes that plant events can have symbolic values and occur asynchronously at quasi-random time instants, while PLC deals with Boolean signals and updates their values synchronously. This deviation could cause timing problems. As considered in [16], it is quite realistic for two events to occur between consecutive clock cycles and for implementation purposes, supervisor must interpret these events as simultaneous. Generally, events occur instantaneously and cause transition from one state to another. We represent the plant events with the rising and falling edges of the input/output signals supplied by their corresponding devices. By comparing signals between two ladder scan cycles [2], [3], [4], rising or falling edges can be easily detected.

As usual we write  $\Sigma = \Sigma_{c,e} \dot{\cup} \Sigma_u$ . Further we write  $\Sigma_u = \Sigma_{u,i} \dot{\cup} \Sigma_{u,p}$ , where  $\Sigma_{u,i}$  is the set of *input events* supplied by the operator,  $\Sigma_{u,p}$  is the set of *plant response* events generated by the plant, and  $\Sigma_{c,e}$  is the set of external events representing DES controllable event ( $\Sigma_c$ ) generated by the supervisor. In the boiler control system example of chapter 4, we encounter two types of external controllable events.

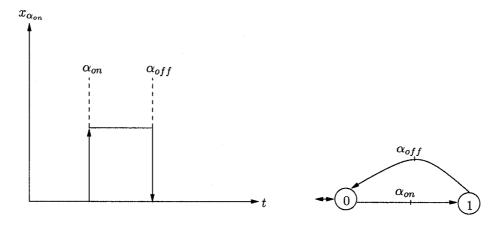

1. Some controllable events have a binary status; for example, corresponding to a binary switch  $\alpha$  we identify two events: the event of turning the switch on  $(\alpha_{on})$  and the event of turning the switch off  $(\alpha_{off})$ . We implement both events by a single boolean signal  $x_{\alpha_{on}}$ :  $\alpha_{on}$  occurs on the rising edge of  $x_{\alpha_{on}}$  while  $\alpha_{off}$  occurs on the falling edge of  $x_{\alpha_{on}}$ . This is shown in Figure 3.1.

Figure 3.1: Representation of  $\alpha_{on}$  and  $\alpha_{off}$  by  $x_{\alpha_{on}}$ .

2. The other type of controllable events that we encounter have a ternary status; for example, a fuel valve  $\beta$  can be either set to high, low or closed, corresponding to controllable events  $\beta_{hi}$ ,  $\beta_{lo}$  and  $\beta_{cl}$ , respectively. We implement these events by two boolean signals  $x_{\beta_{lo}}$  and  $x_{\beta_{hi}}$ :  $\beta_{lo}$  and  $\beta_{hi}$  occur on the rising edge of  $x_{\beta_{lo}}$  and  $x_{\beta_{hi}}$ , respectively, while  $\beta_{cl}$  occurs on the falling edge of  $x_{\beta_{hi}} \vee x_{\beta_{lo}}$ . This is shown in Figure 3.2.

Figure 3.2: Representation of  $\beta_{hi}$ ,  $\beta_{lo}$  and  $\beta_{cl}$  by  $x_{\beta_{hi}}$  and  $x_{\beta_{lo}}$ .

The occurrence of an event  $\gamma$  in the set  $\Sigma_{u,i} \cup \Sigma_{u,p}$  determines the set of actions to be followed: for example, if the temperature drops below a certain threshold (an uncontrollable event) the heater must be turned on. Thus, for such an event we introduce a boolean signal  $x_{\gamma}$  which needs to be 1 only for the duration of a scan cycle, and should drop back to 0 before the start of the next scan cycle to prevent what is called the *avalanche effect* in [6].

# 3.3 Motivating example

The following example takes the above considerations into account to implement a supervisor.

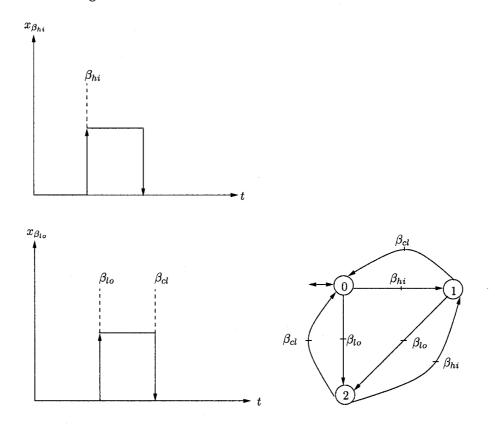

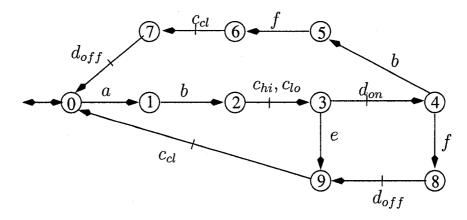

**Example:** Consider the supervisor of Figure 3.3 which we would like to implement using PLC. We have  $\Sigma_{c,e} = \{c_{hi}, c_{lo}, c_{cl}, d_{on}, d_{off}\}, \ \Sigma_{u,i} = \{a\} \text{ and } \Sigma_{u,p} = \{b, e, f\}.$

Figure 3.3: An example of a supervisor represented by an automaton.

Corresponding to external (controllable) events  $\Sigma_{c,e}$  we define

$$X = \{x_{don}, x_{chi}, x_{clo}\}$$

The interpretation is that when  $x_{d_{on}}$  rises from 0 to 1  $d_{on}$  occurs, while when  $x_{d_{on}}$  falls from 1 to 0  $d_{off}$  occurs. Similarly, when  $x_{c_{hi}}$  ( $x_{c_{lo}}$ ) rises from 0 to 1  $x_{c_{hi}}$  ( $x_{c_{lo}}$ ) occurs, while when  $x_{c_{hi}} \vee x_{c_{lo}}$  falls from 1 to 0  $x_{c_{lo}}$  occurs.

For input and plant response events we define

$$Y = \{x^0, x_a, x_b, x_e, x_f\}$$

where  $x^0$  is set by the operator to 1 to start the PLC controller.

Table 3.1 lists the rungs in LLD as a function

$$\Omega: (Q \cup \{\emptyset\}) \times (Y \cup \{\emptyset\}) \to Q \times (X \cup \{\emptyset\}) \times Pwr(X)$$

$$: (q, y) \mapsto (q', x, X')$$

The function  $\Omega$  prescribes that at the current state q ( $q = \emptyset$  when no state is arrived yet) if the event corresponding to  $y \in Y$  occurs ( $y = \emptyset$  when the move to the next state is unconditional) then move to state q', latch the variable x and unlatch all

Table 3.1: List of rungs in LLD defining latch/unlatch function

| Rung # | Current state          | Event                    | Next state | Latch                    | Unlatch                      |

|--------|------------------------|--------------------------|------------|--------------------------|------------------------------|

|        | $Q \cup \{\emptyset\}$ | $(Y \cup \{\emptyset\})$ | Q          | $(X \cup \{\emptyset\})$ | Pwr(X)                       |

| 1      |                        | $x^0$                    | 0          |                          |                              |

| 2      | 0                      | $x_a$                    | 1          | Ø                        | Ø                            |

| 3      | 1                      | $x_b$                    | 2          | Ø                        | Ø                            |

| 4      | 2                      | Ø                        | 3          | $x_{c_{hi}}$             | Ø                            |

| 5      | 2                      | Ø                        | 3          | $x_{c_{lo}}$             | Ø                            |

| 6      | 3                      | $x_e$                    | 9          | Ø                        | Ø                            |

| 7      | 3                      | Ø                        | 4          | $x_{don}$                | Ø                            |

| 8      | 4                      | $  x_b  $                | 5          | Ø                        | Ø                            |

| 9      | 4                      | $x_f$                    | 8          | Ø                        | Ø                            |

| 10     | 5                      | $x_f$                    | 6          | Ø                        | Ø                            |

| 11     | 6                      | Ø                        | 7          | Ø                        | $\{x_{c_{hi}}, x_{c_{lo}}\}$ |

| 12     | 7                      | Ø                        | 0          | Ø                        | $\{x_{don}\}$                |

| 13     | 8                      | Ø                        | 9          | Ø                        | $\{x_{d_{on}}\}$             |

| 14     | 9                      | Ø                        | 0          | Ø                        | $\{x_{c_{hi}}, x_{c_{lo}}\}$ |

variables in X' (x or X' are set to  $\emptyset$  when no signal needs to be latched or unlatched, respectively).

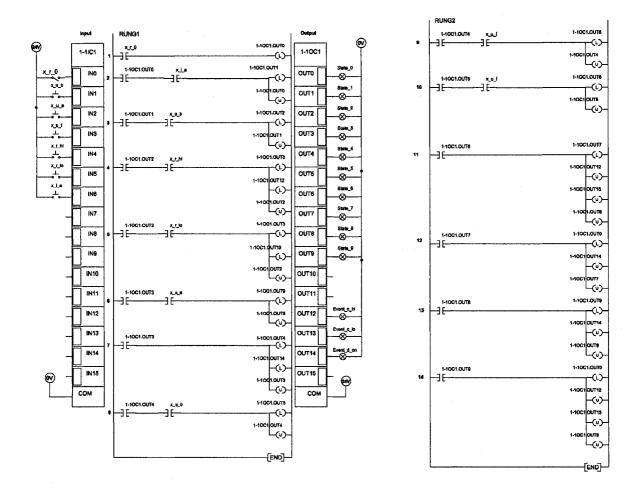

In the LLD implementation of the given example, shown in Figure 3.4<sup>1</sup>, rung 1 is devoted to *initialize* the initial state of the supervisor; in other words, the operator sets the variable  $x^0$  to 1 when he wants to start the PLC controller. After initialization, the supervisor moves from state 0 to state 1 in response to the occurrence of the operator-supplied event a, which is why we place the corresponding variable  $x_a$  in rung 2 as input.

At state 2, two controllable events, namely  $c_{lo}$  and  $c_{hi}$ , can be generated by the supervisor; therefore the operator needs to tell the PLC which variable  $x_{c_{hi}}$  or  $x_{c_{lo}}$  must be latched. If the user does not pick one, the PLC will deterministically choose the one whose rung appears first in the ladder. If it is desired to give user the

<sup>&</sup>lt;sup>1</sup>The devices in the input/output card are used for test purposes only.

Table 3.2: List of rungs in LLD defining operator input signals

| Rung # | Current state          | Event                    | Next state | Latch                    | Unlatch |

|--------|------------------------|--------------------------|------------|--------------------------|---------|

|        | $Q \cup \{\emptyset\}$ | $(Y \cup \{\emptyset\})$ | Q          | $(X \cup \{\emptyset\})$ | Pwr(X)  |

| 4'     | 2                      | $x^{c_{hi}}$             | 3          | $x_{c_{hi}}$             | Ø       |

| 5′     | 2                      | $x^{c_{lo}}$             | 3          | $x_{c_{lo}}$             | Ø       |

freedom to choose the event to be generated, as shown in Table 3.2 we can add two new operator input signals  $x^{c_{hi}}$  and  $x^{c_{lo}}$  in rungs 4 and 5 respectively in order to let the user decide which event  $c_{hi}$  or  $c_{lo}$  is to be generated, respectively. In this case we say the PLC controller is in the manual mode. If there is only one outgoing external controllable event, PLC can automatically generate the event as in the case of rung 7.

Note that since PLC scan time is faster than the plant response time, the rungs corresponding to plant's (uncontrollable) response events are placed above the rungs corresponding to PLC generated (controllable) events. Thus, at state 3 the occurrence of the uncontrollable event e is checked before the controllable event  $d_{on}$  is generated (rungs 6 and 7). If we alter this arrangement, plant events may never get the opportunity to occur.

Rungs 8 and 9, corresponding to uncontrollable events b and f, can be arranged in any order. Here we assume that uncontrollable events do not occur simultaneously; if they do, the event whose rung appears first is selected deterministically by the PLC controller.

To execute LLD on PLC, all input contacts must receive their corresponding signals either from external devices or internal sources, and latch/unlatch coils must send their corresponding signals either to external devices or internal sources. It is evident from Figure 3.4 that all I/O signals have their own sources. We validated the given example by the PLC simulation software Automation Studio 5.2 [12] and verified by running a few test cases that the behavior of the DES supervisor is preserved.

Figure 3.4: Motivating Example in LLD.

# 3.4 Conversion method

## 3.4.1 Assumptions and key observations

We make the following assumptions and key observations about our conversion algorithm.

- 1. For our conversion method, we assume that all supervisors are modeled by deterministic automata [7], [8].

- 2. We ignore the effect of transmission delay in the PLC model. Thus we assume that our I/O devices respond/activate-deactivate instantly and they are completely error-free.

- 3. The self-looped  $(\Sigma_{u,i} \cup \Sigma_{u,p})$  events in the supervisor are omitted in the PLC implementation as they do not change the supervisor's state and thus the set

of enabled events at that state.

- 4. The supervisor must require that an unlatching event be generated before the next corresponding latching event can be generated. This necessitates, for example, resetting all binary-state switches before returning to the initial state of the supervisor.

- 5. PLC can implement a supervisor in two modes: in *automatic mode* once the PLC starts, it will automatically perform its logic to drive the output devices. In *manual mode*, when the PLC starts, it executes its logic in response to the user input to drive the output devices.

- 6. We generally follow a specific rung order in our implementations. In manual mode, rung order does not matter as the user input determines the rung to be executed. In automatic mode, we place rungs corresponding to uncontrollable events first and then we place rungs corresponding to controllable events in arbitrary order. In either case, the rung order evolves according to supervisor states.

Assumption 4 mainly describes why it is important to add all necessary events in the supervisor. This assumption is also essential to directly convert DES supervisor into LLDs. If any event is missing in the DES supervisor, the user may need to construct an extended supervisor by attaching the missing events to the original supervisor as addressed by [7]. To avoid such complications we assume that all necessary events are already included in the supervisor. We now present our conversion algorithm in two steps. First, we partition supervisor event set into three alphabets: plant response alphabet, PLC command alphabet and input alphabet. Second, we convert supervisor's automaton into a ladder logic diagram. In our implementation we clearly define sets of boolean signals corresponding to PLC input contacts (signals) and output variables driving the output coils; we also define rung latch/unlatch function which describes how one can create LLD using the I/O variables. The resulting LLD can then be readily executed by the PLC.

### 3.4.2 First step: Event partition

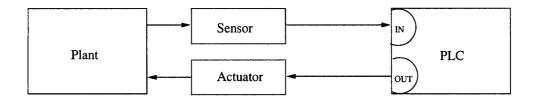

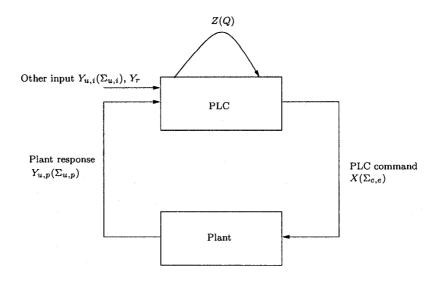

The general architecture of the system is shown in Figure 3.5.

Figure 3.5: PLC-based supervisory control.

Let  $\Sigma = \Sigma_c \dot{\cup} \Sigma_u$  be the alphabet of events. We partition the set of uncontrollable events  $(\Sigma_u)$  into two alphabets  $\Sigma_u = \Sigma_{u,i} \dot{\cup} \Sigma_{u,p}$ .

The alphabet of external events, denoted by  $\Sigma_{c,e}$ , is the collection of controllable events ( $\Sigma_c$ ) that PLC must generate by latching/unlatching output coils which drive their corresponding output devices. The alphabet of input events, denoted by  $\Sigma_{u,i}$ , is the collection of uncontrollable events that are generated by other agents, e.g. an operator. The alphabet of plant response events, denoted by  $\Sigma_{u,p}$ , is the collection of uncontrollable events that are generated by the plant.

## 3.4.3 Second step: I/O selection

We represent a ladder logic diagram by a quadruple:

$$G_c = (X, Y, \Omega, Z)$$

Description of each component as follows.

**PLC commands/outputs.** We assume that all external controllable events are to be generated by the PLC. Recall from the example that switch events with binary status are implemented with one boolean variable, and switch events with a ternary status are implemented using two boolean variables. Some events (such as  $\alpha_{on}$  and  $\beta_{hi}$ ) are triggered on the rising edges of their corresponding variables while other events (such as  $\alpha_{off}$  and  $\beta_{cl}$ ) are triggered on the falling edge of the logical OR of

Figure 3.6: A (n+1)-state switch.

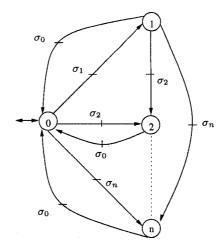

their corresponding variables. In general we model an output device as a (n+1)-state switch shown in Figure 3.6. The switch is deactivated when it is in state 0, while when it is activated it can be in any of the states  $\{1, 2, ..., n\}$ . When the switch is in state  $0 \le i \le n$ , it moves to state j,  $0 \le j \ne i \le n$ , upon the occurrence of  $\sigma_j$ .

For a (n+1)-state switch s define:

$$\Sigma_s := \{\sigma_0, \sigma_1, \sigma_2, \dots, \sigma_n\}$$

Define the corresponding boolean variables as:

$$X_s := \{ x_{\sigma} | \ \sigma \in \Sigma_s \land \sigma \neq \sigma_0 \}$$

where

$$\sigma \text{ occurs} \Leftrightarrow \begin{cases} x_{\sigma} \uparrow & ; \sigma \in \{\sigma_1, \sigma_2, \dots, \sigma_n\} \\ \bigvee_{\sigma' \in \{\sigma_1, \sigma_2, \dots, \sigma_n\}} x_{\sigma'} \downarrow & ; \sigma = \sigma_0 \end{cases}$$

The set of PLC-generated external events is:

$$\Sigma_{c,e} := \bigcup_{s \in S} \Sigma_s$$

where S is the set of all switches. Finally, define the set of boolean signals representing the external events as:

$$X := \bigcup_{s \in S} X_s$$

**PLC inputs.** Corresponding to each  $\sigma \in \Sigma_{u,i} \cup \Sigma_{u,p}$  define a signal  $x_{\sigma}$  that becomes momentarily true when  $\sigma \in \Sigma_{u,p}$  is generated by the plant, or  $\sigma \in \Sigma_{u,i}$  is generated

by the operator. Define:

$$Y_{u,p} := \{x_{\sigma} | \sigma \in \Sigma_{u,p}\}, Y_{u,i} := \{x_{\sigma} | \sigma \in \Sigma_{u,i}\}$$

Also define

$$Y_r := \{x^0\} \cup \{x^{\sigma} | \sigma \in \Sigma_{c,e}\}$$

The user sets  $x^0$  to 1 to initialize the PLC in the beginning of the program. When in the manual mode, or in the automatic mode when two or more external controllable events are possible in a state, an enabled event  $\sigma \in \Sigma_{c,e}$  is generated by the PLC if  $x^{\sigma}$  is set to 1 by the user. Finally, let  $Y := Y_{u,i} \cup Y_{u,p} \cup Y_r$ .

**PLC states.** We define a set of boolean signals to represent the PLC states. Let

$$Z = \{x_q | q \in Q\}$$

The interpretation is that the supervisor is in state q iff  $x_q = 1$ . Thus at any point in time we require that

$$\exists ! q \in Q. \ x_q = 1$$

When the PLC is initialized by the user,  $x_{q_0}$  is latched. When a transition from q to q' takes place,  $x_{q'}$  is latched while  $x_q$  is unlatched.

Rung latch/unlatch function. We define a function  $\Omega$  to model a LLD. It describes how events in  $\Sigma_{c,e}$  are to be generated by latching/unlatching the variables in X. When the function prescribes a state change from  $q_i$  to  $q_j$ , latching of  $q_j$  and unlatching of  $q_i$  are implied.

$$\Omega: (Q \cup \{\emptyset\}) \times (Y \cup \{\emptyset\}) \to Q \times (X \cup \{\emptyset\}) \times Pwr(X)$$

$$: (q, y) \mapsto (q', x, X')$$

The function  $\Omega$  prescribes that at the current state q ( $q = \emptyset$  when no state is arrived yet) if the event corresponding to  $y \in Y$  occurs ( $y = \emptyset$  when the move to the next state is unconditional) then move to state q', latch the variable x and unlatch all variables in X' (x and X' are set to  $\emptyset$  when no signal needs to be latched and unlatched, respectively).

# Chapter 4

# Case study: boiler control system

## 4.1 Introduction

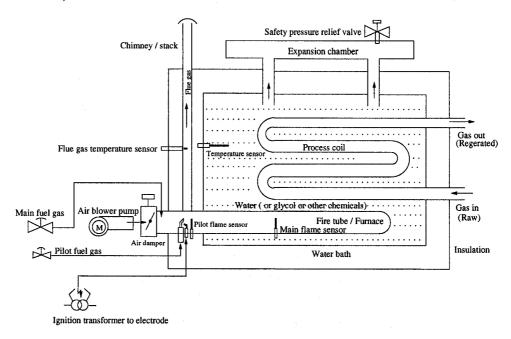

Discrete-event systems encompass a wide variety of physical systems such as manufacturing systems, traffic systems, communication protocols, logistic management systems and data communication networks. Due to its discrete-event nature, a petrochemical boiler control system can be characterized as a discrete-event system. Although boiler controller is commercially available in marketplace, the existing boiler controllers are not constructed within a formal framework. Since there are lots of safety issues and complexities involved in the design of a boiler control system, it is quite appropriate and necessary to synthesize a boiler controller based on formal methodologies such as Petri nets and Ramadge-Wonham Supervisory Control Theory (SCT).

The controllers, which can be synthesized automatically utilizing SCT [1] for a given DES plant and a specification's automaton representing control objectives, are mathematically guaranteed to be safe within the behavioral constraints; and are nonblocking. Therefore, for our test example we choose water bath boiler controller which is widely used in the petrochemical industry. It is now appropriate to provide a brief review of boiler and its control procedures.

## 4.1.1 A brief description of boiler