# A Design for Testability Scheme for Modular and Non-modular Quantum Dot Cellular Automata (QCA) Employing Stuck-at Fault Model

Sayeeda Sultana

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in partial fulfillment of the requirements for the degree of Master of Applied Science at Concordia University

Montreal, Quebec, Canada

September 2006

© Sayeeda Sultana, 2006

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-20755-0 Our file Notre référence ISBN: 978-0-494-20755-0

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **ABSTRACT**

A Design for Testability Scheme for Modular and Non-modular Quantum Dot Cellular Automata (QCA) Employing Stuck-at Fault Model

#### Sayeeda Sultana

Today leading VLSI experts predict a hard wall for CMOS and other conventional fabrication technology due to fundamental physical limits (ultra-thin gate oxide, short channel effects, doping fluctuations, etc.), and increasingly difficult and expensive lithography in nanoscale. Extensive research conducted in recent years at nanoscale aiming to surpass CMOS has proposed Quantum Dot Cellular Automata as a viable alternative for nanoscale computing.

Quantum Dot Cellular Automata (QCA) paradigm is an innovatory approach to computing, which encodes binary information by means of charge configuration of nanostructures instead of current switching devices. The fundamental building block of QCA devices is the QCA cell, and electrostatic interaction between neighboring cells governs the design of all QCA wires and logic gates. The two primary logic elements in QCA technology are: majority voter and inverter. Binary wires and inverter chains are used for interconnection purposes. Logic operation AND, and OR can be achieved by maneuvering inputs to the majority voter. Clocking enables precise control over timing and data flow direction, as well as power gain in QCA circuits. Also proper clocking can achieve computational pipelining and can drastically reduce circuit power dissipation.

Manufacturing of a QCA cell is expected to result in defects like cell displacement, misalignment, and absence of cell or additional cell in circuitry, causing the circuit to exhibit faulty behavior. So a well-defined testing scheme becomes necessary for this technology. Though the technology is different from conventional CMOS design, it is shown to be effective and realistic to use existing testing schemes at this stage. Stuck-at (s-a-v) fault model is quite acceptable in this regard in spite of the fact, that this model does not incorporate all the defective behaviors occurring in the fabrication process. With this in view, single stuck-at value faults have been considered for testing QCA circuits.

In this thesis a new strategy for designing QCA logic, exhaustively testable for single s-a-v faults, is presented. In particular, the method facilitates QCA functionality testing. Any combinational logic can be implemented using only AND-OR gates (with negated signals available), and in QCA this generally results in reduced test set for exhaustive fault detection within the data path. Previously this strategy was used for QCA logic testing considering only primary inputs (either true or complemented, but not both) feeding different majority voters, which fails for general circuits where fanouts are allowed for primary inputs and their complement. Here, a design scheme has been proposed which makes testing possible for any combinational QCA circuit. The extension to modular design testing is also presented.

Two design approaches are proposed for testing modular and non-modular logic. The first design uses 2n ( $n \equiv \text{primary inputs}$ ) 'Test Enable' majority voters, and is tested with two 4-bit vectors regardless of complexity of design and the input size. Second design employs n majority voters for the same purpose, thus requiring lesser number of majority voters, but at the price of increased vector length. Application

specific conditions would decide which design becomes optimal. Without going into the features of a particular QCA fabrication, errors on logic level is addressed, such that the approach achieves generality, and could be applied to any particular implementation of QCA. Also to overcome the fault masking in modular circuit design, a solution has been presented. To verify the scheme, a simulation and layout tool, QCADesigner version 2.0.3 was used. First the fault free circuit was designed and simulated. Then random s-a-v faults were injected in different locations of data path. In all cases, 100% fault coverage was achieved confirming the validity of proposed approach.

## **ACKNOWLEDGEMENT**

I would like to take this opportunity to thank some of the people without whose support this thesis would not have achieved.

I would first like to express my gratitude towards my supervisor Dr. Katarzyna Radecka, who has guided me towards this achievement. She took the time and effort to guide me to finish this project successfully. As my supervisor, she always had time for me and my queries and her knowledge in the subject matter has refined me from time to time. Her encouragement towards this topic and her support, both academic and financial has kept me aiming to excel. I remain ever grateful to her for giving me the opportunity to continue my work in flexible hours after my first baby's birth. If not for her, I doubt I would have come this far.

A special acknowledgement right after my supervisor must be made to Dr. Zeljko Zilic of McGill University, who has extended his helping hands towards me in many ways. His prompt steps regarding any problem in my research have guided me to come to a fruitful end.

I would also like to thank the faculty of the department, specially the teachers with whom I have taken course. I would like to thank Dr. Asim J. Al-Khalili and Dr. Sofiene Tahar for being so supportive during my courses with them and afterwards. I would like to take a moment in remembrance of Dr. Victor Rossokhaty, with whom I did my first course here in Concordia University. His affectionate smile encouraged me to pursue my studies in this field.

At this point I have to thank my family and friends, whose love and affection kept me going. I am grateful to my parents for believing in me and being there always for me, sheltering from whatever and whenever, and mention specially my husband, for being so supportive and understanding during this period when he had his tough time with his thesis. He had been my support and the source of my energy for pursuing this research, and beyond. He has been weathered in the process and still had the energy to absorb all the hardships and have a smile for me. Thanks to my daughter, who was born during this time, for being so patient seeing her parents busy with their thesis, and providing me with the greatest joy of my life. Holding her in my arms, and looking at her face has been worth living for.

Thank you all.

Sayeeda Sultana

# **Table of content**

| List o | of fig    | gure   | s                                          | .ix |

|--------|-----------|--------|--------------------------------------------|-----|

| Chal   | pter      | 1:1    | ntroduction                                | . 1 |

| 1.1    |           | Mot    | tivation                                   | . 4 |

| 1.2    | <u>).</u> | Obj    | ective and Scope of the Thesis             | . 5 |

| 1.3    | }         | The    | sis Organization                           | . 7 |

| Cha    | ptei      | 2: L   | iterature Review                           | 10  |

| 2.1    |           | Phy    | sical and Device Level QCA                 | 12  |

| 2.2    | 2         | Log    | ic Level                                   | 15  |

| 2.3    | }         | Des    | ign Methodology and Tools                  | 20  |

| 2.4    | Į         | Def    | ects and Testing                           | 22  |

| Cha    | ptei      | ' 3: E | Basics of QCA                              | 27  |

| 3.1    |           | The    | Basic Cell                                 | 28  |

| 3.2    | 2         | Kink   | Energy Associated with Coulomb Interaction | 30  |

| 3.3    | 3         | The    | Inverter                                   | 31  |

| 3.4    | 1         | QC     | A Wire                                     | 32  |

| ;      | 3.4.      | l      | Binary Wire in QCA                         | 32  |

| ;      | 3.4.2     | 2      | QCA Inverter Chain                         | 33  |

| ;      | 3.4.3     | 3      | Rippers Cells in QCA                       | 33  |

| ;      | 3.4.4     | 4      | Fan Out                                    | 34  |

| ;      | 3.4.      | 5      | Wire Crossings                             | 34  |

| ;      | 3.4.      | 5      | Multi-layer QCA                            | 36  |

| 3.5    | 5         | The    | Basic Gate: Majority Voter                 | 37  |

| 3.6    | 5         | QC     | A Clocking                                 | 39  |

| 3.7    | 7         | Log    | ric Symbol and Logic Implementation        | 43  |

| ;      | 3.7.      | 1      | Configuration of Four-Input AND Gate       | 44  |

| į      | 3.7.2     | 2      | Configuration of Four-Input OR Gate        | 45  |

| 3.7.3 |        | 3     | Realization of Product-of-Sums Expressions           | 45 |

|-------|--------|-------|------------------------------------------------------|----|

|       | 3.7.4  | 4     | Realization of Sum-of-Products Expressions           | 46 |

| 3     | .8     | QC.   | A Implementation                                     | 46 |

| Ch    | apte   | r 4:  | QCADesigner- Simulation and Layout tool              | 50 |

| 4     | .1. C  | reat  | ing Design                                           | 50 |

| 4     | .2. Lc | ayer  | Ordering of Layout                                   | 51 |

| 4     | .3. Q  | CAE   | Designer Signal Clocking                             | 52 |

| 4     | .4. Si | mulc  | ation Engines                                        | 53 |

|       | 4.4.   | 1     | Coherence Vector Simulation Engine                   | 53 |

|       | 4.4.   | 2     | Bistable Simulation Engine                           | 56 |

| 4     | l.5. D | esig  | n Verification                                       | 58 |

|       | 4.5.   | 1     | Exhaustive Verification                              | 58 |

|       | 4.5.   | 2     | Vector Table Simulation                              | 58 |

| Ch    | apte   | r 5:  | QCA Physical Defects and Abstracted Faults           | 59 |

| 5     | 5.1    | Imp   | olementation-specific Faults: Sources of Defects     | 60 |

|       | 5.1.   | 1     | Metal Dot Implementation                             | 60 |

|       | 5.1.   | 2     | Molecular Dot implementation                         | 61 |

| 5     | 5.2    | Def   | fects Beyond Device Specification                    | 62 |

| 5     | 5.3    | Inte  | er Cellular Defects over Intra Cellular Defects      | 63 |

| 5     | 5.4    | Cel   | I Level Defects in QCA                               | 63 |

|       | 5.4.   | 1     | Cell Displacement                                    | 64 |

|       | 5.4.   | 2     | Cell Misalignment                                    | 64 |

|       | 5.4.   | 3     | Cell Omission                                        | 65 |

| 5     | 5.5    | Def   | fect Analysis                                        | 67 |

| Ch    | apte   | r 6:  | Testing of QCA Circuits - Proposed Scheme            | 69 |

| 6     | 5.1.   | Stu   | ck-at-Value Fault Model: Assumptions and Limitations | 70 |

| 6     | 5.2.   | Tes   | ting of Single Majority Voter                        | 72 |

| ć     | 5.3    | Tes   | ting of Chained MVs                                  | 72 |

| ć     | 5.4    | Tes   | ting of QCA Circuits: Case Study                     | 73 |

|       | 6.4.   | 1. St | ruck-at-0 Fault Testing                              | 74 |

|       | 6.4    | 2. St | uck-at-1 Fault Testina                               | 75 |

| 6.4                                 | .3. General Test Set for a Network of MVs                   | 75  |  |

|-------------------------------------|-------------------------------------------------------------|-----|--|

| 6.5                                 | Testing of Control Lines                                    | 76  |  |

| 6.6.                                | Unique Stuck-at Test Properties of QCA                      | 78  |  |

| 6.7.                                | Fault Masking Due to Inverters: Why the Above Scheme Fails? | 80  |  |

| 6.8.                                | Literal Input AND-OR Logic QCA Implementation               | 81  |  |

| 6.9.                                | Problem of Literal Input AND-OR Scheme                      | 83  |  |

| 6.10.                               | The Proposed Scheme                                         | 84  |  |

| 6.1                                 | 0.1. Design 1: Shorter Test Vector                          | 86  |  |

| 6.1                                 | 0.2. Design 2: Circuit with Fewer Extra Majority Voters     | 87  |  |

| 6.1                                 | 0.3. Modular Design: Fault Masking Due to Cascading         | 88  |  |

| Chapte                              | er 7: Simulation Results                                    | 91  |  |

| 7.1.                                | Design 1:                                                   | 93  |  |

| 7.2. [                              | Design 2:                                                   | 97  |  |

| 7.3. N                              | Modular Design:                                             | 101 |  |

| Chapte                              | er 8: Conclusion and Future Work                            | 105 |  |

| 8.1. Issues in Future QCA Design105 |                                                             |     |  |

| 8.2. F                              | uture Work                                                  | 107 |  |

| Refere                              | nce                                                         | 109 |  |

# List of figures

| Figure 1: NTRS roadmap for devices [63]                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: A possible Quantum dot structure as used in QCA fabrication 4                                                                                                                                                                                                                                                                                               |

| Figure 3: Possible implementation of a QCA cell [1]                                                                                                                                                                                                                                                                                                                   |

| Figure 4: A possible implementation of a 2 dot cell [16]                                                                                                                                                                                                                                                                                                              |

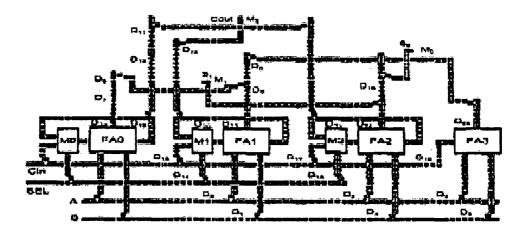

| Figure 5: Bit serial adder layout [30]                                                                                                                                                                                                                                                                                                                                |

| Figure 6: 7-input complex QCA gate proposed in [18]                                                                                                                                                                                                                                                                                                                   |

| Figure 7: Flow chart of (a) CMOS design process, and (b) CMOS based QCA design process [18]                                                                                                                                                                                                                                                                           |

| Figure 8: Snapshot of an arbitrary QCA design with QCADesigner                                                                                                                                                                                                                                                                                                        |

| Figure 9: A 2-bit Adder in QCA implemented as TMRSO [43]                                                                                                                                                                                                                                                                                                              |

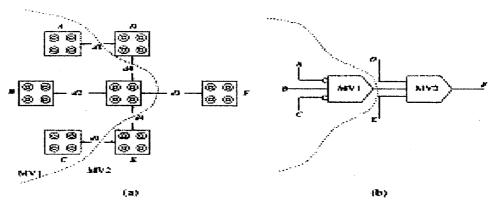

| Figure 10: The AOI gate [26], (a) The QCA implementation, (b) Schematic diagram 26                                                                                                                                                                                                                                                                                    |

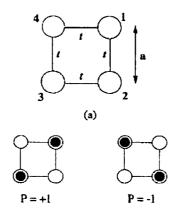

| Figure 11: Schematic of the basic four-site cell. (a) The geometry of the cell. The tunneling energy between two neighboring sites is designated by t, while 'a' is the near-neighbor distance. (b) Coulombic repulsion causes the electrons to occupy antipodal sites within the cell. These two states result in cell polarizations of $P = +1$ and $P = -1$ [1] 28 |

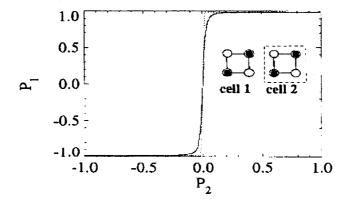

| Figure 12: The cell-cell response. The polarization of cell 2 is fixed and its Coulombic effect on the polarization of cell 1 is measured. The nonlinearity and bistable saturation of this response serves the same role as gain in a conventional digital circuit [11] 29                                                                                           |

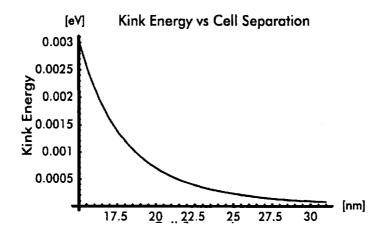

| Figure 13: Kink energy between two cells as the separation between the cells is increased from 15nm to 30nm. We see that this kink energy decays as the fifth power of the separation. This is a general property of quadrupole-quadrupole interaction [31]                                                                                                           |

| Figure 14: QCA inverter                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 15: Binary wire                                                                                                                                                                                                                                                                                                                                                   |

| Figure 16: QCA Inverter Chain                                                                                                                                                                                                                                                                                                                                            |

| Figure 17: Ripper cells placed to extract data from inverter chain                                                                                                                                                                                                                                                                                                       |

| Figure 18: QCA fan out                                                                                                                                                                                                                                                                                                                                                   |

| Figure 19: Wire cross over                                                                                                                                                                                                                                                                                                                                               |

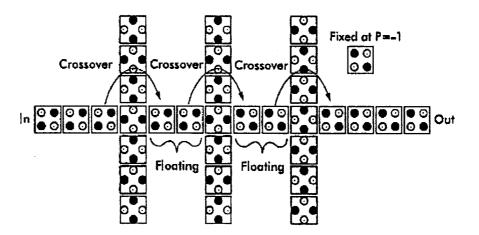

| Figure 20: A section of wire with three coplanar crossovers                                                                                                                                                                                                                                                                                                              |

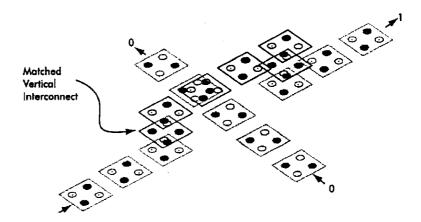

| Figure 21: Multi-layer crossover. The vertical separation between cells can be turned to match design parameters                                                                                                                                                                                                                                                         |

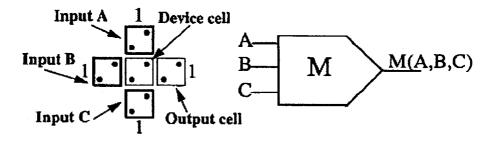

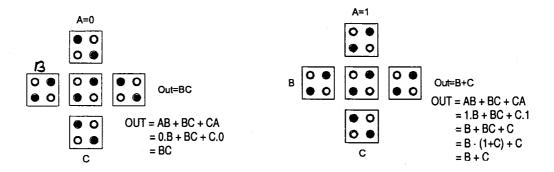

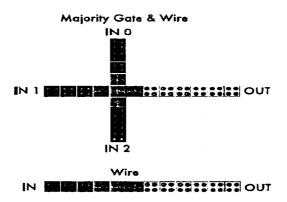

| Figure 22: The 5 cell basic majority gate implementing the logic function $OUT = AB + BC + CA$ (As could be seen in the figure, both A and B are at the same logic value while C is at opposite value. So the center device cell is driven to the state of the majority of the inputs that is the state of A & B and eventually drives the output cell to the same state |

| Figure 23: QCA majority voter configured as AND and OR gate                                                                                                                                                                                                                                                                                                              |

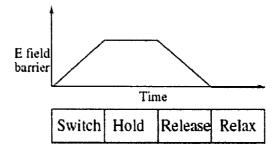

| Figure 24: Adiabatic clocking in QCA                                                                                                                                                                                                                                                                                                                                     |

| Figure 25: A clocked QCA majority voter and binary wire                                                                                                                                                                                                                                                                                                                  |

| Figure 26: Illustration showing an example of adiabatic switching [19] 42                                                                                                                                                                                                                                                                                                |

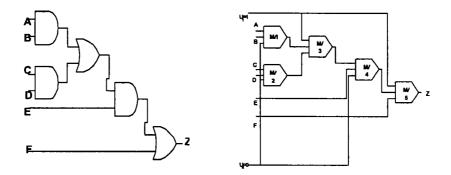

| Figure 27: Logic symbols of QCA. (a) logic symbol of a majority voter, (b) logic symbol of an arbitrary logic implemented in traditional logic circuitry and (c) the same logic implemented in QCA.                                                                                                                                                                      |

| Figure 28: 7-input complex gate                                                                                                                                                                                                                                                                                                                                          |

| Figure 29: 4-input AND gate                                                                                                                                                                                                                                                                                                                                              |

| Figure 30: Product of Sum representation                                                                                                                                                                                                                                                                                                                                 |

| Figure 31: Sum of Product representation                                                                                                                                                                                                                                                                                                                                 |

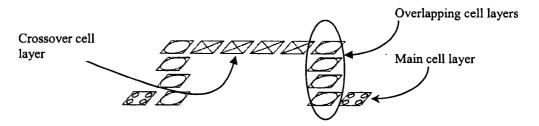

| Figure 32: A multi-level crossover in QCA                                                                                                                                                                                                                                                                                                                                |

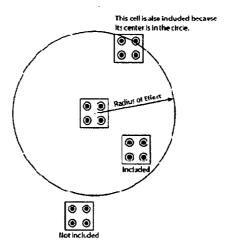

| Figure 33: Radius of effect                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

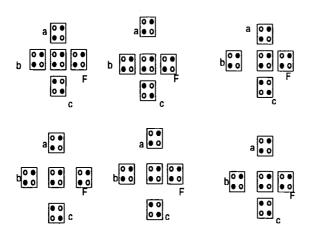

| Figure 34: Different displacement faults of a majority voter,                                                                                                                                            |

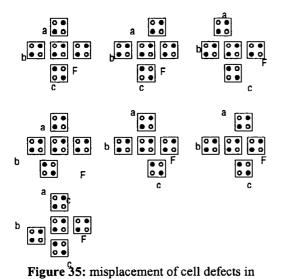

| Figure 35: misplacement of cell defects in QCA majority voter                                                                                                                                            |

| Figure 36: Cell omission fault in QCA majority voter                                                                                                                                                     |

| Figure 37: Defects in binary double wire                                                                                                                                                                 |

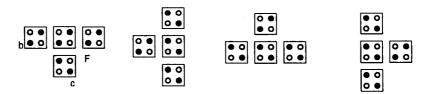

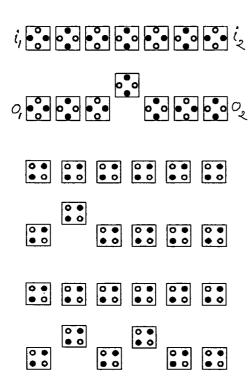

| Figure 38: Testing of a chain of MVs                                                                                                                                                                     |

| Figure 39: An arbitrary function implemented with QCA MVs                                                                                                                                                |

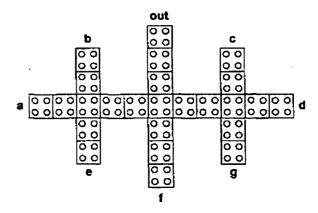

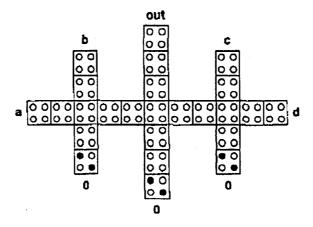

| Figure 40: Testing for stuck-at-074                                                                                                                                                                      |

| Figure 41: Testing for stuck-at-175                                                                                                                                                                      |

| Figure 42: (a) Logic implemented in CMOS, (b) The same logic implemented in QCA                                                                                                                          |

| Figure 43: (a) Inverter in a general CMOS logic, (b) Inverter in QCA MV circuitry81                                                                                                                      |

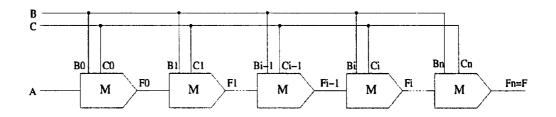

| Figure 44: Block diagram for a literal input QCA AND-OR logic implementation82                                                                                                                           |

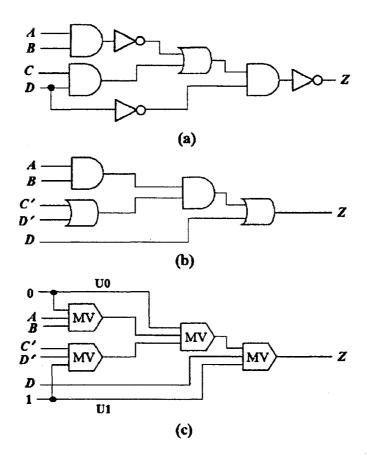

| Figure 45: (a) A general arbitrary inverting logic, (b) The same logic implemented in AND-OR scheme, (c) The same logic implemented as AND-OR scheme in QCA with MVs                                     |

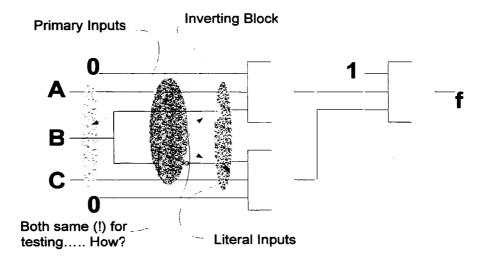

| Figure 46: Problem with literal input AND-OR scheme in a simple circuit involving inverters, two of the literals cannot have the same value at the same time, as required for testing of the circuit.    |

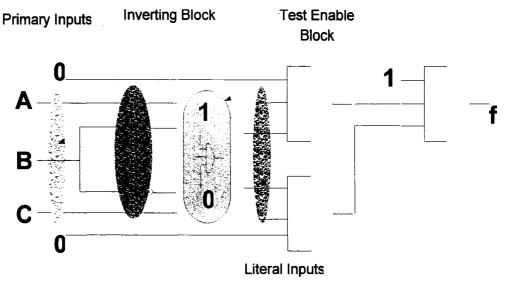

| Figure 47: Problem solved with test enable block for the same simple circuit involving inverters, all the literals can now have the same value at the same time, as required for testing of the circuit. |

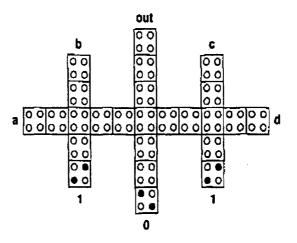

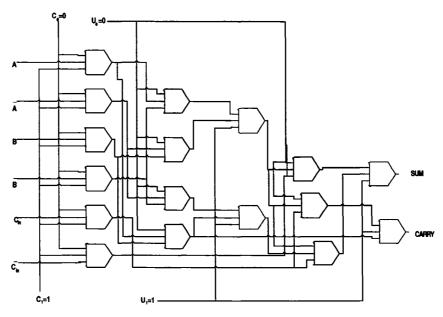

| igure 48: Design 1: A full adder is implemented with test enable block at the beginning of the non-inverting AND-OR block                                                                                |

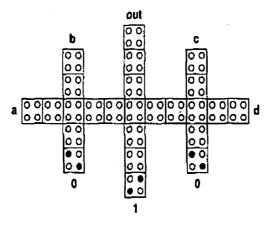

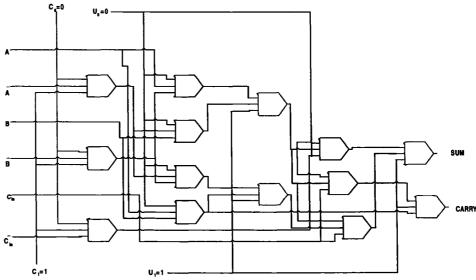

| Figure 49: Design 2: A full adder is implemented with test enable block at the beginning of the non-inverting AND-OR block, but with MVs only in the inverted literals87                                 |

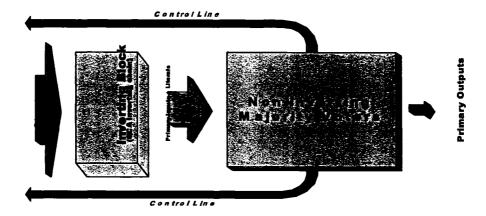

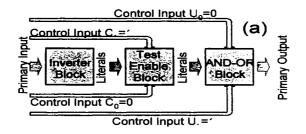

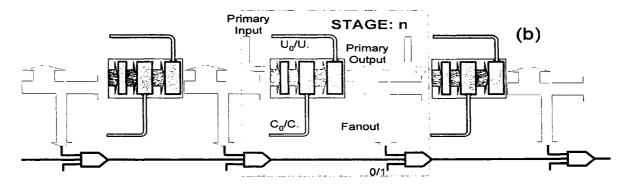

| Figure 50: Block diagram for modular design for testability, (a) Block diagram of a single module, (b) Block diagram of modular design for n-bit with extra fault propagation line.                      |

| Figure 51: 1-Bit full adder with 'Test Enable' (Design scheme 1)                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 52: Design 1 normal operation: simulation results                                                                                   |

| Figure 53: Design 1 s-a-0 fault test detecting no faults for a fault free case: simulation results                                         |

| Figure 55: Design 1 s-a-1 fault test detecting no faults for a fault free case: simulation results                                         |

| Figure 56: Design 1 s-a-1 fault detected in both SUM and CARRY for a fault injection in front of AB operation of bit-1: simulation results |

| Figure 57: 1-Bit full adder with 'Test Enable' block in Design scheme 2                                                                    |

| Figure 58: Design 2 test for s-a-0 fault detecting no fault for a fault free case: simulation results.                                     |

| Figure 59: design 2 test for s-a-0 fault detected in C for a fault site in front of XNORC operation for bit-1: simulation results          |

| Figure 60: Design 2 test for s-a-1 fault detecting no fault for a fault free case in bit-1: simulation results.                            |

| Figure 61: Design 2 test for s-a-1 detecting fault in SUM for a fault site in front of A'B' operation in bit-1                             |

| Figure 62: 2-bit adder modular design for scheme 1                                                                                         |

| Figure 63: 2-bit adder with CTEST to detect masked fault in CARRY <sub>1</sub> output: normal operation                                    |

| Figure 64: 2-bit modular design fault testing for s-a-0 detecting no fault for a fault free case                                           |

| Figure 65: 2-bit modular design test for s-a-0 detecting fault in CTEST line 104                                                           |

| Figure 66: 2-bit modular design fault testing for s-a-1 detecting no fault for a fault free case                                           |

| Figure 67: 2-bit design 1 s-a-1 test detecting fault in CTEST line                                                                         |

# Chapter 1: Introduction

The age of Very Large Scale Integrated (VLSI) circuit fabrication is now about half a century. In this long journey, microelectronics industry has switched from planner to lateral devices, and adopted Complementary Metal Oxide Semiconductor (CMOS) instead of Bipolar Junction Transistor (BJT), enjoying dramatic improvements in the speed and size of electronic devices. This trend has long obeyed Moore's law, which predicts that the number of devices integrated on a chip will be double every 18 months. Adherence to this exponential growth curve has been a monumental task requiring rapid improvements in all aspects of integrated circuit fabrication to permit manufacturers to both shrink the size of the devices and increase chip size, while maintaining acceptable yields. Experts' ardor for yet more speed and miniaturization has brought them to the verge of classical devices, forcing them to peek in an unknown and astonishing world of nanotechnology and quantum devices.

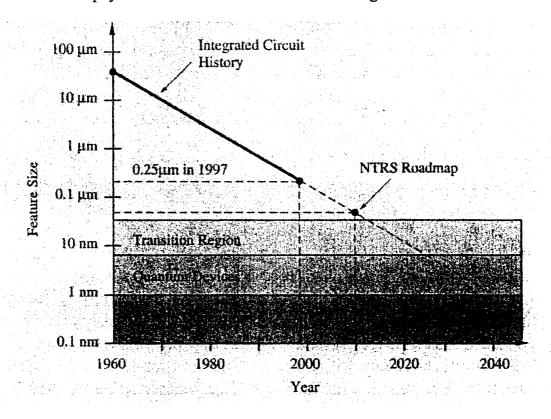

Today's leading VLSI experts predict a hard wall for the CMOS and other conventional fabrication technology in about a decade. This lithography-based technology is facing serious challenges due to the fundamental physical limits of the CMOS technology such as ultra-thin gate oxides, short channel effects, doping fluctuations and the increasingly difficult and expensive lithography in nanoscale regimes. Future trend of the National Technology Roadmap for Semiconductors (NTRS) predicts that it may reach its extreme end as early as 2012 as shown in figure 1 [1]. It then

becomes prudent to look for an alternate paradigm for information processing which will overcome the physical limitations of transistor based designs.

Figure 1: NTRS roadmap for devices [1].

Extensive research conducted in recent years at nano-scale aiming to surpass the conventional CMOS technology has anticipated that these devices might achieve a density of 10<sup>12</sup> devices/cm<sup>2</sup>, and operate in THz frequencies [2]. Among such devices, *Quantum Dot Cellular Automata* (QCA) proposed originally by Dr. Craig Lent [3] offers a new and extremely low powered method of computation. In terms of feature size, it is projected that QCA cell of few *nm* size would be possible in near future [2].

In quantum physics, basic particles such as electrons are associated with wave nature. The principle of uncertainty imposes on such particles to have a minimum positional spreading. The so-called atomic Bohr radius then becomes the minimal size of

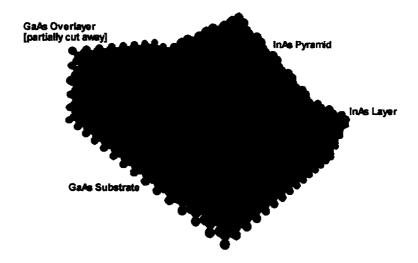

an electron. Whenever one creates a structure with all three dimensions less than that of the atomic Bohr radius of an electron, the electron in such structure becomes confined, its wave function overlaps with itself, and energy quantization occurs. Such 3D confined structures are called quantum dots. These quantum dots has been fabricated and demonstrated in various materials, and as shown in this thesis, have been used for devising computation machines. A quantum dot structure is shown in figure 2.

Figure 2: A possible Quantum dot structure as used in QCA fabrication.

QCA is an innovative device that stores logic states not as voltage levels, but rather in the relative position of individual electrons. The Coulomb interaction between stationary electrons provides the basis for a current-less (no electron flows and hence no current is drawn from the source) computation and data processing. QCA offers the possibility for circuitry to dissipate many orders of magnitude less power than CMOS, is scalable to molecular dimensions, and provides the power gain necessary to restore signal levels. No voltage and current based complicacies are faced; rather somewhat logical reversibility can be reached. In fact, for a very low power overhead, it is possible to eventually reach the absolute reversible logic [4].

There has been considerable research over the past decade on designing combinational and sequential logic devices using QCA cells, as well as finding the suitable fabrication process. In current technology the cells must be aligned precisely at nanoscales to provide correct functionality [2]. Thus proper testing for manufacturing defects and misalignment plays an important role for quality of QCA-based designs. Recent developments in cell manufacturing involving the deposition of molecules on a substrate surface by self-assembly process [5] have indicated that missing or additional cells are inevitable for molecular implementation because the process of cell deposition is very sensitive [6]. A small variation in process parameters may result in a defect. Moreover, these defects have pronounced functional effects when they occur within, or very near to the target device due to strong cell interactions [7]. Therefore testing is an absolute necessity for detecting various types of defects in QCA like cell misplacement, presence or absence of cell etc.

#### 1.1 Motivation

One of the primary issues in the testing community now a day has been the drastic swing in fabrication technology and its effect on test flow. Since the manufacturing process of nano-devices is still ill-defined, it is extremely difficult to address related manufacturing testing problems. However it would be inappropriate to ignore testing of these devices until manufacturing processes are well developed. Instead the trend is to rely on the vast knowledge of testing of CMOS circuits, in attempts to modify and adjust the research from the CMOS world to QCA. It seems that in many cases faults in circuits fabricated in nano-technology exhibit similar properties to fault models of classical

CMOS circuits [8]. Even faults, which exhibit probabilistic nature typical to quantum circuits, can be successfully considered using adjusted classical methods.

The basic logic elements in QCA technology are the majority voter and inverter. Binary wires and inverter chains are used as an interconnect fabrics. Logic elements AND and OR can be obtained by manipulating the majority voter [9]. Though the technology is different from the conventional CMOS designs, it is effective and realistic to use the existing testing scheme at this moment. Over the years the single stuck-at value fault model has been successfully used in case of different technology changes; from BJT to CMOS to Hybrid technology. It has been observed that, test sets generated based on the stuck-at fault model are quite acceptable for testing CMOS-based design even though this model does not incorporate all the defective behaviors occurring in fabrication process [10]. Therefore, in the aspect of QCA circuit testing, the use of this model can be a good option at its very early stage.

# 1.2. Objective and Scope of the Thesis

There is little work done on testing and detecting defects in QCA designs. Fijany and Toomarian proposed a fault tolerant implementation of a majority gate called a *block majority gate* [11]. A block majority gate shows fault tolerance to some of the defects, however, it does not address interconnection faults. Baradaran et al. proposed a testing scheme for QCA based designs [2, 8, 12]. A number of unique testing features have been identified through these studies. For example, the characterization of QCA defects and their effects on logic level are presented, as well as a testing scheme requiring constant

number of test vectors has been demonstrated. However, their approach does not address the generality of application to any combinational circuit. The objective of this thesis is to find a design scheme that will overcome the limitations of Baradaran work. Additionally, the method to extend testing for modular structures is addressed.

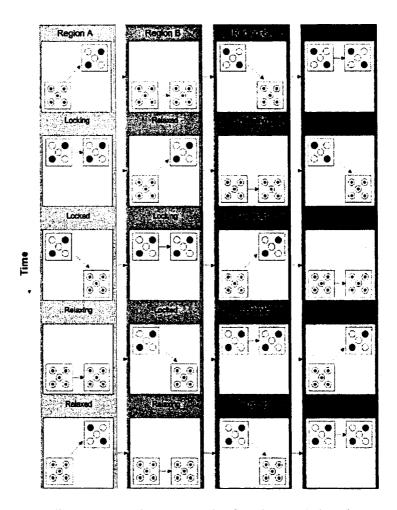

In this thesis a design for testability of arbitrary combinational QCA logic circuit has been proposed. In particular, the method facilitates QCA functionality testing. Any combinational logic can be implemented using only AND-OR gates (with negated signals available), and in QCA this generally results in reduced test set for exhaustive fault detection within the data path. In Baradaran work, this strategy was used for QCA logic testing considering only primary inputs (either true or complemented, but not both) feeding different majority voters in AND-OR block, where it can be possible to set all the inputs having the same logic value for testing purpose. However, this approach fails for general circuits where both primary inputs and their complements may present. Logically it is impossible to set both original and its complement having the same logic simultaneously. So testing of these circuits will not be possible with proposed two test vectors. In this work a design scheme has been proposed that makes testing possible for any combinational QCA circuit. To achieve this, a block of test enable majority voters has been introduced which facilitate to set all inputs to AND-OR block to be of same value. In more complex circuits, sometimes the entire circuit is realized with different small blocks or modules to ease the testability. Such modular design may mask any fault on the cascaded line where the output of one stage goes as input to the next stage. To detect this fault an extra fault propagation path of majority voter has been proposed in this work.

We adopt a single stuck at fault model s-a-v for representing manufacturing defects in QCA, and propose a design scheme for testing modular and non-modular logic. Our results are demonstrated on basic logic circuits like an adder and a multiplier. Without going into the features of a particular QCA fabrication, errors on logic level are discussed, such that the approach achieves generality, and could be applied to any particular QCA implementation. To verify the scheme a simulation and layout tool named QCADesigner version 2.0.3 [13] is used. First the fault free circuit is designed and simulated. Then a number of faults have been injected in different locations of data path to find the faulty behavior. Simulated results show the validity of the approach.

### 1.3 Thesis Organization

The thesis report is organized chapter wise as outlined below:

Chapter 1: Introduction – in this chapter a prologue of the work done, the intensions, motivation, objectives and the scope is briefed. An introduction of a new Quantum Dot Cellular Automata (QCA) technology is presented. This technology is promising to surpass conventional CMOS technology in near future.

Chapter 2: Literature Review -this chapter presents the trend of research community toward QCA physics and designs. There has been considerable research on QCA as a new computing scheme in the nanoscale regimes. A theoretical finding for the root of Quantum Dot Cellular Automata and work done so far for achieving QCA circuits, their implementations, defects in circuit and probable testing scheme is highlighted.

Chapter 3: Basics of QCA – QCA is a relatively new concept in nanotechnology. In order to be acquainted with this technology this chapter presents the very basics of Quantum Dot Cellular Automata. The basic operation of QCA cell and the fundamental logic gates are demonstrated using basic majority voters. The clocking of the QCA circuits and different implementations of this technology are discussed to have a better idea on this novel area.

Chapter 4: QCADesigner: Simulation Tool – QCADesigner is a tool developed at the University of Calgary ATIPS laboratory to rapidly design and simulate new QCA circuits. This tool remains the only CAD tool versatile enough for designing practical QCA circuits and addressing functional issues regarding cell orientation. This chapter illustrates the various features of the tool to properly design and simulate QCA circuits which has been used to verify their correct functionality.

Chapter 5: QCA Physical Defects and Abstracted Faults – In literature it has been found that during the fabrication process different defects may occur in QCA cell causing the circuits to malfunction. This chapter describes such physical defects, their manifested errors and the behavior of them in logic level which have been simulated to reestablish the previous findings. It is necessary to be acquainted with these defects to come up with a proper fault model.

Chapter 6: Testing QCA Circuits - Proposed Scheme - In this chapter logic level testing aspects of QCA circuits are introduced. The unique feature of these circuits useful in easing the testing process, are presented. As single stuck-at fault model is used in this work, a brief overview of this model is also given here. The AND-OR configuration of

QCA circuits which facilitate testing is discussed. The limitations of the testing scheme proposed earlier employing this configuration is highlighted in this chapter. Finally the solutions to this problem are as well as modular design testing proposed in this research work is presented.

Chapter 7: Simulation Results – In this chapter, simulation findings are presented. The proposed design schemes are simulated to check proper functionality. Fault injection at different locations of data path has been exploited to detect faulty behavior. The simulation results validate the schemes presented in Chapter 6.

Chapter 8: Conclusion – This part present the conclusions of the thesis representing the findings in this study, and a directive for future.

# Chapter 2: Literature Review

Up until now, the mainstream in fabrication technology has been CMOS. Whether in microwave, or in optoelectronics or in microelectronics, it has been in the forefront of fabrication technologies [14]. In the last few decades it has attained drastic improvements and tremendous miniaturization leading to submicron dimensions. However, since then, submicron physics is beginning to take over, and CMOS seems to loose its sole grip on fabrication monopoly. New physics resulted in new designs and hence emerged new paradigms of computing. Starting mostly in research oriented environment, nanotechnology is now beginning to find stronghold in its industrial footing.

As smaller and smaller gate lengths are achieved (65nm design and 45nm etch length in 2003 [14]), it is predicted that by 2010 gate length would reach 10nm. This then creates probably the toughest hurdle for CMOS. As researchers look for yet smaller devices, Quantum dot (QD) seems to be the limit in dimensional reduction in mesoscopic systems. Carrier confinement and quantum effects predominate at this level, as well as wave properties of particles becomes the key feature of electronics. Though molecular structures for electronic devices are also being investigated [15], still they do not pose to be the major driving force in near future.

It had been predicted that in densely fabricated quantum dots, the confined carrier wave function of individual dots would overlap, and thereby create miniband structures

[16]. This could be the basis for them to work as elements of cellular neural networks [17]. Fabricated by Fulton and Dolan [18], metal tunnel junction structures exhibited single electron properties. Such properties can be categorized as pseudo quantum dots, as they do not quantize carrier energy, but exhibits ultra small capacitance from the effect of charging one single electron.

The first computing scheme using quantum dot structures was proposed in 1993 [3]. Still emulating the Von Neumann type-computing machine, the quantum dots play a role of central elements, as they respond to the electronic charge condition of the adjoining dots. This proposed scheme is the Quantum Dot Cellular Automata (QCA). It was predicted that semiconductor Quantum Dots would be the forerunner in QCA implementation [19], but later it was found that charge fluctuations caused by impurities and defects tend to make the implementation burdensome. Hence metal tunnel type junctions are now the prime choice for implementation.

Since QCA is an emerging technology much work has been done on the physics of Quantum Dots, their implementations, switching and clocking requirements for proper operation. Different architectures have been proposed. The logical devices based on QCA have been demonstrated as well as design methodology has been introduced. A number of researchers have concentrated on the faults and testing of QCA circuits. Therefore the technical literatures available are discussed in this thesis under four different categories.

# 2.1 Physical and Device Level QCA

Quantum Dots have been demonstrated and fabricated in different materials, and have found their use in a diverse list of frontiers. When fabricated in an orderly cellular fashion, they have shown to be useful for computational device construction. Among such studies, only a few directly related with this work are briefed here.

The Quantum Dot Cellular Automata (QCA) was proposed in [3] as a viable technology. According to this study, QCA consists of an array of quantum device cells in a locally-interconnected architecture. The proposed cell is composed of coupled Quantum Dots occupied by two electrons. An idea of constructing logical gates and inverters is also presented.

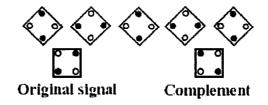

A more detailed demonstration of the possible implementation of logic devices using coupled dot cells is found in [9]. It has been observed that, the charge distribution in each cell tends to align along one of two perpendicular axes, which allows the encoding of binary information using the state of the cell. A line of the cells can be used to design inverters, programmable logic gates, dedicated AND and OR gates, and non-interfering wire-crossings.

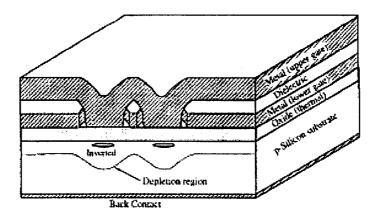

In [20] the authors describe a computing scheme with Quantum Dots and a possible such quantum dot cell is given in figure 3. An adiabatic switching paradigm is developed for clock-controlled pipelined QCA architecture. The binary information is stored as electronic charge as a current less computing is achieved.

Figure 3: Possible implementation of a QCA cell [20].

Other investigators have been extending the theoretical analysis of QCA arrays. Tanamoto et al. [21] have proposed alternative ways of assembling QCA cells into useful devices. Lusth and Jackson [22] have applied graph theoretic analysis to QCA design. Chen and Porod [23] have developed sophisticated finite element models for gate depleted QDs in semiconductors that can relate dot occupancy to particular bias conditions. Fountain et al [24] have been matching the QCA approach with massively parallel processing schemes which require simple computational elements at each node.

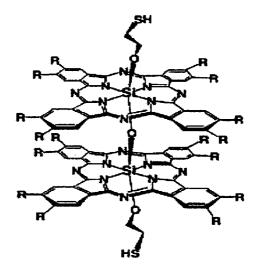

Authors in [25] presented a simple clocked molecular QCA cell. The molecules show intrinsic bistability as a result of dipole charge configuration, which strongly couples to its neighboring molecules. Using local field authors achieved clocked control. The study is elementary, indicative only of the possibility of using molecular QCA. Then again, review of the possibility of implementing QCA in molecular scale or in nanomagnets has been done [14] [26]. Quite a number of molecular structures for QCA have been suggested, and one such 2-dot QCA is given in figure 4.It is predicted that the

ultimate utility of QCA will come from combining currently existing technologies with advanced nanotechnology.

Figure 4: A possible implementation of a 2 dot cell [14].

Experimental implementation of QCA in nanoscale metal dots defined by tunnel barriers is reported in [27]. Here the authors demonstrate a controlled polarization of QCA cell switching agreeing with theoretical predictions. Clocked QCA operation is demonstrated on an example of a two cell shift register. In other study, [28] fanouts are presented. Additionally, authors proved the power gain as one driver cell induced logic in multiple fanned out cells.

Investigations related to switching speed and temperature dependence of QCA have been presented in [29]. Orthodox Coulomb blockade and master equation dynamics approach was taken into consideration for a semi-infinite shift register design. The crucial role of power gain as a function of temperature was shown. The behavior of such circuits as a function of clock speed and temperature is yet to be fully explained [30]. It is found

that circuit speed is limited by RC time constant, so majority voters could work up to  $450^{0}$ K, while semi infinite QCA wire could work up to room temperature.

The QCA physical design problem was addressed in context of VLSI physical design issues in [31]. It presents a comparison between ILP formulation and heuristic solution for problems like QCA partitioning, placement and routing of QCA circuits. It was found that heuristics approach gives the most optimized result. Unidirectionality and metastability problem within a QCA wire is studied, and 3D architecture is proposed in place of asymmetric spacing [32]. The classical calculation carried here showed that 3D configuration could also be the way to overcome metastability problems.

While H-memory is a design developed particularly for QCA, authors propose a new execution model that combines with H-memory for distributing the functionality of the CPU throughout the memory structure [33]. This resulted in efficient designs.

Today QCA is almost always constructed as four dot cells. But it is also reported in five dot and even six dot cell configurations. Instead of the four dot cell, a six dot cell is studied for clocking purpose in [34]. This work shows that more precise control is achieved by clocking the cells with the electric field that is generated by a layout of clocking wires.

## 2.2 Logic Level

Researchers have demonstrated a number of logic designs based on QCA. These designs include combinational circuits like simple XOR gate, 2-to-4 decoder, circuits

realizing various Boolean functions, arithmetic structures like different adders (ripple carry adder, carry-look-ahead adder, carry save adder etc.), multipliers. Not only that, some sequential circuits such as flip-flops, shift registers, barrel shifters, memory unit, microprocessors have also been presented in different literatures. The trends of these studies are addressed in this section.

The arithmetic structures based on QCA is discussed in [35]. As the cost function of QCA realization is dependant on the clocking zones, the total delay only depends upon the number of clocking zones, irrespective of the number of gates in a circuit. Hence a different design approach becomes a necessity for QCA arithmetic design concept. A QCA design methodology is developed in this work, and adder and multiplier circuits are explored, as the examples. Study suggested the serial arithmetic to be preferable to its parallel counterpart for increased interconnect latency and potential implementation technologies for realizing QCA based circuits.

The performance analysis of different types of adders in QCA has been carried out in [36]. It is demonstrated that a QCA-based ripple carry adder and a bit-serial adder outperform carry look ahead and carry select adders. The ripple carry adder is found to be the fastest one, while the bit-select adder is found to be the most area efficient. However, the results are only based upon two input majority voter as primary gates, so different input gates could lead to a reevaluation of performance analysis. The schematic design of the bit serial adder used for this study is given in figure 5.

Figure 5: Bit serial adder layout [36].

In another study [37] the authors presented an improved design for QCA adder using only three majority voters and two inverters. They proposed to connect n 1-bit adders to obtain n-bit carry look ahead adder with reduce hardware using the same clocking scheme and parallel structure of the previously reported designs. In another study [38], the authors propose a pipelined carry look ahead adder (CLA) in QCA. The designs are compared to a ripple carry adder, and a modular layout is presented for CLA. The proposed designs show complexity and area which are roughly proportional to operand sizes. Also the designs give delays that increase at a slightly greater rate than the logarithm of the operand sizes.

With the motivation of finding a systematic way of translating three input Boolean function to majority functions, the authors in [39] have presented an analysis for reduction in gate count in QCA design structures. The study is based on the use of Karnaugh maps to optimize a majority function.

Authors in [40] have presented a method for mapping three variable Sum-of-Product (SOP) expressions to QCA majority logic. They also illustrated a method for reducing the total number of majority voters in a QCA design. The study identified thirteen functions to represent all three input functions, and proposed a gate reduction scheme for QCA circuits. The leading example here is a 1-bit full adder.

A multiple bit serial stream analyzer is presented in [41]. This is functionally equivalent to a shift register and a multiple bit comparator. The quasi-adiabatically switching is quantum mechanically analyzed, and the research suggests that QCA could easily work as a sequential circuit with this type of switching.

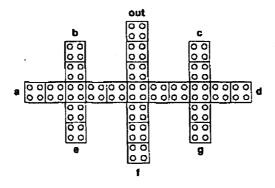

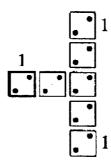

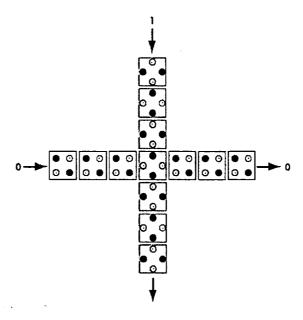

To facilitate the designing of QCA circuits a complex gate using majority voters is proposed in [42]. This complex gate comprises of 7 inputs, and can be configured to work as 4 input AND or OR gate. These gates can be later on used to represent Boolean functions in a popular Sum-of-Products (SOP) or Product-of-Sums (POS) format. Generally three of the inputs act as control inputs, while the remaining four act as data inputs to the gate. An example of such complex gate is given in figure 6 below.

Figure 6: 7-input complex QCA gate proposed in [42].

A study of high-level evaluation of QCA circuit is also carried out [43] with a 4-bit ALU and a 4x4 memory unit. Among few requirements suggested for that type of designs, the most important one is probably the need for multi-layer QCA support as a

replacement for the very unreliable coplanar crossover, and high resolution clocking for each majority voter, independent of its inputs. A parallel memory architecture is proposed in another literature [44]. Its basic operation requires three clocking zones, where the timing of the zones needs two additional clocks to implement a four step reading/writing process. This method of memory design is said to reduce the requirement of overall clocking zones and the required clocking circuitry.

The traditional wire crossings in QCA circuit sometimes cause problem in circuit functionality. To overcome this problem a wire crossing network is presented in [45]. This, so called, crossbar network can be used in PLA structures, and is implemented using parallel to serial converters. Special latching signals determine, at a particular time, signal connections made within the crossbar, so no physical change is required. Hence the same physical design can dynamically be used to realize different logic functions. The network uses parallel-to-serial converters, shift registers, and time-dependent latching devices, so that such elements eliminates the need for rotated cells on an interstitial cell spacing grid of traditional QCA wire crossings.

Researchers have also tried to focus on quantum computing using QCA technology. A quantum computing architecture based on 1D array of QCA cells is proposed in [4]. Basic quantum gates such as NOT, C-NOT, and a 3-bit gate, the modified C-NOT are proposed. Coherence vector formalism was used to describe the system.

### 2.3 Design Methodology and Tools

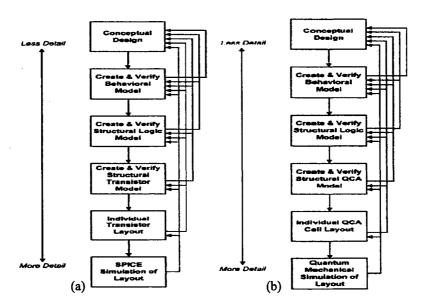

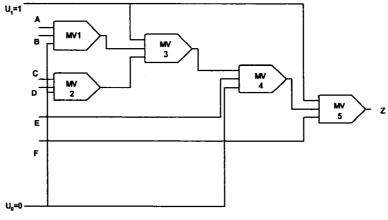

Predicting the end of the CMOS roadmap, studies have been conducted in [46] to propose thorough design methodology to address computationally viable circuits, which will be buildable with QCA. Today most of the QCA designs are done on a cellular basis, which lacks scalability, and ultimately will fail for larger circuit size. To overcome this obstacle, a hierarchical design methodology, similar to that of CMOS, has been proposed in [47] for QCA. It has been suggested that creating and verifying the circuit at higher level of abstraction would reduce design time. Moreover detection of any potential faults at behavioral and structural levels is faster; hence an efficient design can be obtained before a more comprehensive quantum mechanical simulation of adiabatic QCA switching is executed. This process allows optimization related to design efficiency and error detection. Hence error detection in function level becomes prudent. The design process for CMOS and QCA presented in this work is given below in figure 7.

Figure 7: Flow chart of (a) CMOS design process, and (b) CMOS based QCA design process [47].

A design methodology for QCA based on conventional CMOS technology is proposed in [48]. This work utilizes HSPICE to produce a methodology for circuit design flow just like that done in CMOS, with the view to increase design compatibility and a feasible way to design large scale QCA nanodevice.

Also formalism is presented in [49] aimed to modify design of QCA circuits. Here a set of standard circuit elements of uniform layout rules is used. It simplifies the circuit design, and overcomes the input delay sensitivity of QCA logic, as well as increases considerably device density over conventional CMOS design.

A modular design technique based on basic building blocks referred to as *tiles* is presented in [50]. The logic capability of individual tiles is analyzed and the tiles are then used to form the final logic. A 3x3 QCA grid is chosen as the basic block, and five types of tiles are constructed. It is found that the tiles are area efficient, and offers versatile logic operations.

As QCA is an emerging technology, much work has been done with respect to design methodology, with many experimental designs of the same, rather basic, classical arithmetic logic proposed. However, due to the lack of the basic knowledge regarding sneak noise path, many of the primitive designs are prone to functional error and malfunction in real circuits. To overcome this obstacle, several critical vulnerabilities in the QCA gates and interconnects have been addressed, and a disciplinary guideline has been proposed in [51] to prevent plausible erroneous QCA designs. The guideline presents a set of rule which effectively suppress noise in QCA.

In [52] [53], the authors have presented a CAD tool specially build for working with QCA. The tool, QCADesigner has been successfully used to simulate full adders, barrel shifters, random access memories, etc. As QCA logic requires a rapid and accurate simulation and design layout tool, a full functionality check is provided. Several simulation engines are incorporated to facilitate accurate simulation. In fact, QCADesigner is emerging as the main simulation tool for QCA design and layout formation. In the following figure 8, a design layout done with the tool is given with different clock zones, as it is clearly shown in different colors.

Figure 8: Snapshot of a QCA random access memory cell design with QCADesigner [52]

# 2.4 Defects and Testing

Recent developments in QCA fabrication process have indicated that defects are likely to occur in QCA based circuits. Therefore the testing community has extended their investigations toward the possible defects abstraction and testing procedures, as well

as proposing some ways to achieve fault-tolerant circuits. The major propositions in this regard are highlighted in this section as a prelude.

QCA latch and shift registers have been studied for possible errors in [54]. An analysis of the operational error types is presented, and their properties are investigated. The results showed that smaller device size and higher operating frequency drastically reduced the number of errors.

Research has shown that fabrication defects arising from self-assembly of molecules in QCA are highly likely. Hence fault tolerant architectures become necessary. Possible defects occurrence during fabrication has been examined in [55], and their manifestation in logic level has been studied. Additionally, a strategy for understanding how groups of defects affect the system has been proposed. Finally, a prototype tool for fault modeling has been demonstrated.

The probable defect occurring in a molecular implementation of QCA is analyzed in [56]. Unlike that in metal based QCA, defects here could happen due to erroneous deposition of cells on substrate, which might pose different functional error in different QCA logic elements. One interesting observation was that a single missing cell in a wire may cause local non polarization of a particular cell, but due to the strong coupling between non neighboring cells, this fault does not propagate. Instead a weak signal from the previous cell configures the subsequent cells after the fault to have the correct logic. Hence unless there occurs a sequence of missing cells, single cell omission in wire does not pose a functional error, provided that the fault does not occur in a primary output.

The defect tolerance of molecular QCA has also been studied [57]. A QCA SR type flip-flop is proposed accounting to the strict timing issues. Then single additional and missing cell faults are introduced. It has been found that the majority of these defects manifest functional error abstracted mostly by stuck-at value (s-a-v) faults and, in some cases, with unwanted inversion. Inverters are shown to be prone to an addition fault, while majority voters are susceptible to missing cell defect.

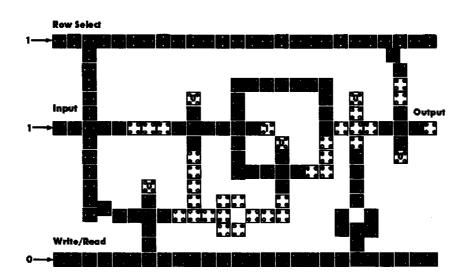

Wire delay dominates logic delay in QCA. Additionally, wires are more prone to faults than gates. Therefore, triple modular redundancy (TMR) based fault tolerance becomes inappropriate for QCA, [58]. In [58], researchers have proposed TMR with shifted operands (TMRSO), and demonstrated it on a full adder to obtain better area utilization and throughput performance. They then suggested implementing TMRSO instead of TMR for fault tolerance aspect. A 2-bit TMRSO adder proposed in the study is given in figure 9 below.

Figure 9: A 2-bit Adder in QCA implemented as TMRSO [58].

The scalability issue, and the defect tolerance henceforth have been studied in [7].

As scaling in QCA is associated with cell dimension and cell to cell spacing,

displacement and misalignment defects are analyzed to study the sensitivity to manufacturing processing variation changing with device scaling. The defects are shown to have definitive behavior, and it is found that the relation between the cell size and smallest distance for an erroneous behavior remains mainly linear. In another study [59], the same issue has been addressed using the QCADesigner tool. It has been found that for displacement and most of the misalignment defects, the relation between the cell size and defect tolerance has a parabolic nature, giving an optimized range of the device size which is the most defect resistant. It is believed that a strong Columbic interaction gives better defect tolerance for smaller devices resulting in a parabolic dependence of defect to a cell size.

Defect characterization of QCA manufacturing process has been studied in [2]. A detailed analysis shows that though faults manifesting themselves in functional level can mostly be abstracted by s-a-v fault model, some faults result in unwanted complementation of the desired function. The success of s-a-v fault model then depends on specific implementation of a particular logic. As in the case of CMOS circuits, different implementations of the same logic generally result in different fault coverage. Some very unique and interesting testing properties are found for QCA. In another study [8], it has suggested that specific implementation of a particular logic must be adopted to achieve high fault coverage with s-a-v fault model. Constant testability of QCA designs has been investigated. MV-based designs offer C-testability in both 1-D and 2-D structures.

Testing of QCA circuits have also been studied. In [12], the authors present a design for testability scheme, in which circuits are implemented with inverting blocks

followed by AND-OR logic. The method requires only two test vectors for complete fault coverage. Unfortunately, the scheme is illustrated on a rather elementary non inverting circuit, which fails drastically for real life more complex inverting logic.

Conventional QCA circuits with majority voters realizing AND-OR functions use inverter. However, these circuits are not area efficient. To minimize area requirement a novel basic QCA gate, AOI (And-Or-Inverter) has been proposed in [60]. This gate is said to be a universal gate with greater area minimization and delay reduction in larger logic circuits. Defects have been studied for this building block too, and a test set is provided for the gate. The study of the defects in functional level suggests that the gate is robust. The proposed AOI gate is illustrated below in figure 10.

Figure 10: The AOI gate [60], (a) The QCA implementation, (b) Schematic diagram.

The defect tolerance and testing schemes mentioned in this section can be employed to have a better and effective design in QCA technology. The rest chapters of this thesis starting with very basics of QCA technology will be presented to accomplish that goal.

# Chapter 3: Basics of QCA

Quantum Dot Cellular Automata (QCA) is a new way of implementing logic and information processing. It is conceptually different from conventional technologies such as CMOS, and so it is absolute essential to have some background study. Fabrication of QCA can be obtained in different technologies, like: metal tunnel junction, semiconductor, self-assembled dots, etc., however the basics would somewhat differ in various implementations. Moreover, as QCA belongs to the new, and still not well analyzed, class of quantum circuits, the understanding of its operation would require rather proficient knowledge of quantum effects such as tunneling, electron charge interaction and of quantum devices such as single electron transistor (SET). The detail theoretical approach of the device and circuitry is presented in this chapter, offering a comprehensive look into this new emerging technology.

This chapter will first present the idea and working of the basic cell, which is the fundamental building block of the system. Then it will focus on the NOT gate implementation and interconnections. Subsequently, this chapter impart the basic gate, a majority voter (MV), which through appropriate set of control inputs reduce to AND or OR gates. An important feature of QCA, the clocking will also be discussed. Some implementation techniques of QCA will be briefed. To accrue the basics of QCA an arbitrary logic and some complex logics implemented by QCA will also be presented.

### 3.1 The Basic Cell

A high level embodiment of the basic four dot QCA cell is given in the figure 11. It consists of four possible positions for electrons, named Quantum Dots, placed in a square configuration. Exactly two extra mobile electrons are loaded into each cell, which can quantum-mechanically tunnel between dots, but not through cells. The charge is fixed and immobile [32]. Tunneling out of the cell is assumed to be completely suppressed by the potential barriers between cells. It is also possible to add a fifth dot at the center of the square. Although such an addition improves the behavior of the cell slightly, for simplicity reasons the attention will mainly be given on the four-dot cell. If the barriers between cells are sufficiently high, the electrons will be well localized on individual dots.

Figure 11: Schematic of the basic four-site cell. (a) The geometry of the cell. The tunneling energy between two neighboring sites is designated by t, while 'a' is the near-neighbor distance. (b) Coulombic repulsion causes the electrons to occupy antipodal sites within the cell. These two states result in cell polarizations of P = +1 and P = -1 [20]

As electrons will repel each other electrostatically, they will be forced to reside in the diagonally opposite dots of the square, and by that obtaining the minimal energy state. For an isolated cell, two energetically minimal equivalent arrangements exist as shown in figure 11(b), which could be denoted as a *cell polarization*. The term "cell polarization"

refers only to such arrangement of charge, and does not imply a dipole moment for the cell. If the charge on a dot i is value  $\rho_i$ , then the polarization is defined [61] as:

$$P = \frac{(\rho_1 + \rho_3) - (\rho_2 + \rho_4)}{\rho_1 + \rho_2 + \rho_3 + \rho_4}.$$

(1)

If the two extra electrons are completely localized in dots 1 and 3, the polarization is + 1 (binary 1); if they are localized in dots 2 and 4, the polarization is - 1 (binary 0), figure 11. The tunneling between dots implies that  $\rho_i$  may not assume an integer or polarization values.

The two polarization states of the cell will not be energetically equivalent if other cells are nearby. Consider two cells close to one another as shown in the inset of figure 12. The figure inset illustrates the case when cell 2 has a polarization of 1. It is clear that in that case the ground state configuration of cell 1 is also a 1 polarization. Similarly if cell 2 is in the state -1, the ground state of cell 1 will match it. The figure shows the nonlinear response of the cell-cell interaction.

Figure 12: The cell-cell response. The polarization of cell 2 is fixed and its Coulombic effect on the polarization of cell 1 is measured. The nonlinearity and bistable saturation of this response serves the same role as gain in a conventional digital circuit [55]

## 3.2 Kink Energy Associated with Coulomb Interaction

The Coulomb interaction between cells allows us to transmit information along interacting arrays of QCA cells. This interaction can be described by the *kink energy*,  $E_{kink}$  associated with the energetic cost of two cells having opposite polarization [20]. The electrostatic interaction between charges in two four-dot cells m, and n is:

$$E^{m,n} = \frac{1}{4\pi\varepsilon_0\varepsilon_1} \sum_{i=1}^4 \sum_{j=1}^4 \frac{q_i^m q_j^n}{|r_i^m - r_j^n|},\tag{2}$$

where  $\varepsilon_r$  is the dielectric constant,  $q_i^m$  is the charge in dot i of cell m, and  $r_i^m$  is the position of dot i of cell m. Since the kink energy represents the energy cost of the two cells having opposite polarization, the energy of the two cells having the same polarization must be subtracted from that of them having opposite polarization:

$$E_{kink}^{m,n} = E_{opposite\ polarisation}^{m,n} - E_{same\ polarisation}^{m,n}.$$

(3)

Although not shown in figure 12, there are background charges of +e/2 in each dot, to ensure that the cell actually bears a neutral charge. These positive charges must be included in the calculations of the kink energy. In general, the interaction between cells can be described by a quadrupole-quadrupole interaction, in which the kink energy decays as the fifth power of the separation between cells as shown in figure 13.

Figure 13: Kink energy between two cells as the separation between the cells is increased from 15nm to 30nm. We see that this kink energy decays as the fifth power of the separation. This is a general property of quadrupole-quadrupole interaction [59]

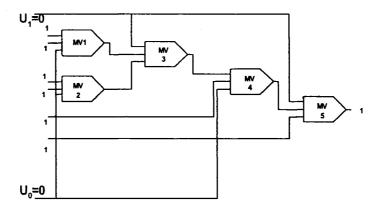

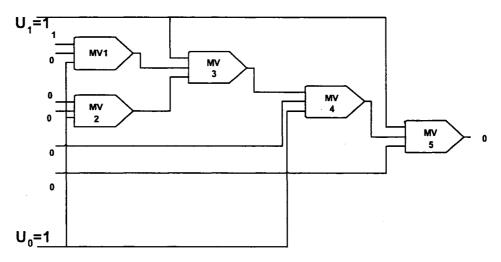

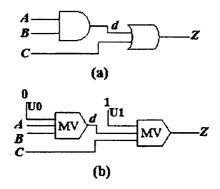

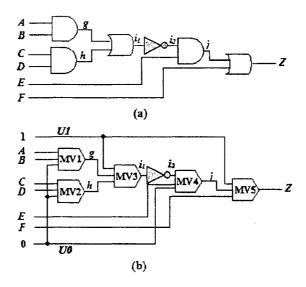

#### 3.3 The Inverter