# Building a Tool for Testing Real Time Systems

By: Manar Abu Talib

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at Concordia University Montreal, Quebec, Canada

March 2004

©Manar Abu Talib, 2004

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-90985-9 Our file Notre référence ISBN: 0-612-90985-9

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la

Bibliothèque nationale du Canada de

reproduire, prêter, distribuer ou

vendre des copies de cette thèse sous

la forme de microfiche/film, de

reproduction sur papier ou sur format

électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

#### **ABSTARCT**

# Building a Tool for Testing the Real Time Systems

# Manar Abu Talib

Real time systems can be defined as systems whose behavior is time dependent. They don't depend only on the values of input and output signals, but also on their time of occurrence. These systems are highly used nowadays, such as in patient monitoring systems, air traffic control systems, and telecommunication systems.

Ensuring the correctness of real time systems before the development and ensuring that it functions correctly within the specified time constraints become a very important task to avoid catastrophic consequences. A number of design issues affect the testing strategies and the testability of the system. In this thesis, we have designed and built a tool that generates the timed test cases by implementing the state characterization technique. The tool consists of the following steps: First, the real-time system is modeled as a Timed Input Output Automaton (TIOA). Its description is written in a file to be parsed by the tool using JAVACC. TIOA has locations, clocks and transitions with time constraints. Second, the tool samples the stored TIOA into sub automaton easily testable, called Grid Automaton. Third, the tool is then responsible for transforming this Grid Automaton into a Non-deterministic Timed Finite State Machine (NFSM). Finally, test cases are generated from NFSM, using the Generalized Wp-method. We have applied many examples to the tool and it demonstrates its ability to detect many possible faults.

# Acknowledgements

The writing of a master thesis should bring feelings of fulfillment, accomplishment and joy. This is surely one of those cases, but it would have been impossible without the help and support of many.

On an academic level, I would like to thank Prof. Rachida Dssouli and Dr. Abdeslam En-Nouaary for their keen constructive criticisms that have guided me in shaping this thesis into its final form as well as for the support and "pats on my back".

On a professional level, I would like to thank all my colleagues at Electrical and Computer Engineering department as well as its staff for their views on the importance of a higher education.

On a personal note I would like to thank the family support from my parents, brothers and sister as well as the patience of my husband Adel in bearing with me throughout the writing process. I would also like to express my thanks to my daughter for her lack of complaint and comprehension.

# **Table of Contents**

| Table of Contents                                                  | v   |

|--------------------------------------------------------------------|-----|

| List of Figures                                                    | ix  |

| List of Tables                                                     | xii |

| CHAPTER I: INTRODUCTION                                            | 1   |

| 1.1 Definition of Real Time Systems                                | 1   |

| 1.2 Verification and Testing                                       | 3   |

| 1.3 The Objective of the Thesis                                    | 5   |

| 1.4 Outline of the Thesis.                                         | 8   |

| t of Figures                                                       |     |

| 2.1 Testing Based on FSM Model                                     | 9   |

| 2.1.1 Transition Tour Method                                       | 11  |

| 2.1.2 Distinguishing Sequence Method                               | 13  |

| 2.1.3 UIO Method                                                   | 15  |

| 2.1.4 W Method                                                     | 17  |

| 2.1.5 The Partial W Method                                         | 19  |

| 2.1.6 The Generalized Wp Method                                    | 21  |

| 2.2 Real Time Systems Testing                                      | 21  |

| 2.2.1 Test Cases Generation for Theory Formulas                    | 22  |

| 2.2.2 Test Cases Generation for FSM Model with Timers and Counters | 23  |

| 2.2.3 Test Cases Generation for Timed Automaton | 24 |

|-------------------------------------------------|----|

| 2.3 Conclusion                                  | 25 |

| CHAPTER III: TIMED TEST CASES GENERATION        | 26 |

| 3.1 Tool Input, Process and Output              | 26 |

| 3.2 TIOA Specification                          | 27 |

| 3.3 Sampling the TIOA                           | 29 |

| 3.3.1 Sampling Process                          | 29 |

| 3.3.2 Sampling Algorithm                        | 31 |

| 3.4 Transforming of Grid Automaton into NFSM    | 33 |

| 3.4.1 Transformation Process                    | 33 |

| 3.4.2 Transformation Algorithm                  | 34 |

| 3.5 Minimizing the NFSM                         | 38 |

| 3.5.1 Minimization Process                      | 38 |

| 3.5.2 Minimization Algorithm                    | 39 |

| 3.6 Generating the Test Cases                   | 41 |

| 3.6.1 Q Process                                 | 42 |

| 3.6.2 Q Data Structure                          | 47 |

| 3.6.2 Q Algorithm                               | 49 |

| 3.6.3 P Algorithm                               | 50 |

| 3.6.4 R Algorithm                               | 50 |

| 3.6.5 Wi Algorithm                              | 51 |

| 3 6 6 W Algorithm                               | 52 |

|   | 3.6.7 Test Suite One Algorithm (Q.W)                  | 53         |

|---|-------------------------------------------------------|------------|

|   | 3.6.8 Test Suite Two Algorithm (R.Wi)                 | 53         |

|   | 3.7. Optimization the Test Cases                      | . 54       |

|   | 3.7.1 Optimization Algorithm                          | 54         |

|   | 3.8 Conclusion.                                       | . 55       |

| C | CHAPTER IV: TOOL IMPLEMETATION                        | . 57       |

|   | 4.1 Design Rationale.                                 | . 57       |

|   | 4.1.1 User Interface                                  | 57         |

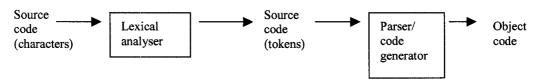

|   | 4.1.2 Why JAVACC?                                     | <b>6</b> 0 |

|   | 4.1.3 Why JAVA?                                       | 64         |

|   | 4.1.4 Loops Issue                                     | 65         |

|   | 4.1.5 Determinism Issue                               | 65         |

|   | 4.1.6 Q Algorithm                                     | 65         |

|   | 4.2 The methodology used in designing the tool        | . 66       |

|   | 4.2.1 Object Oriented Design Methodology              | 66         |

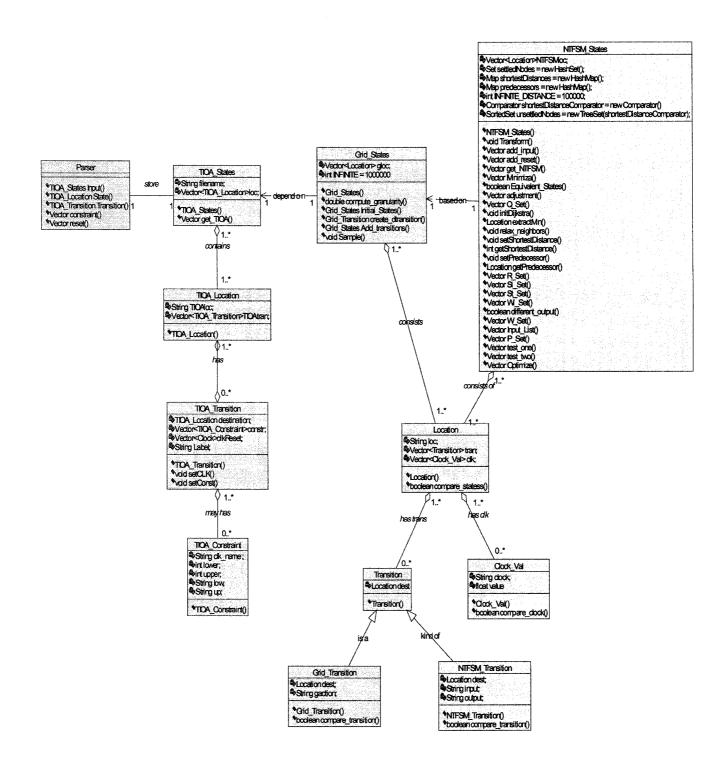

|   | 4.2.2 Overview of Tool's Class Diagram                | 67         |

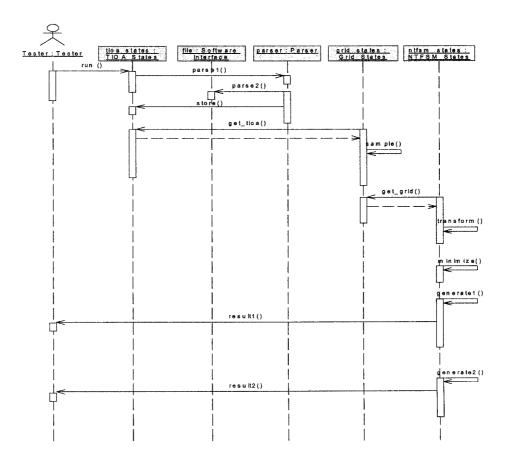

|   | 4.3 Sequence Diagram for Tool Execution               | . 71       |

|   | 4.4 Design Quality and Design Evaluation              | . 73       |

|   | 4.4.1 The Five Factors That Effect the Design Quality | 73         |

|   | 4.4.2 Evaluating our Design (A check list)            | 76         |

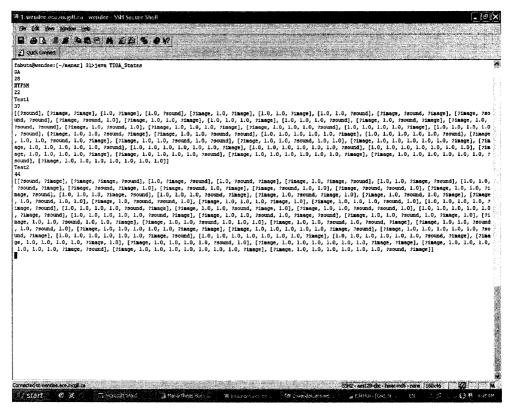

|   | 4.5 Scenario of Execution                             | . 77       |

|   | 4.6 Conclusion.                                       | . 81       |

| CHAPTER V: CASE STUDIES AND EVALUATION | 82  |

|----------------------------------------|-----|

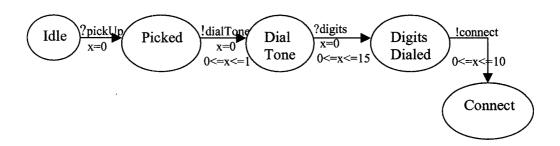

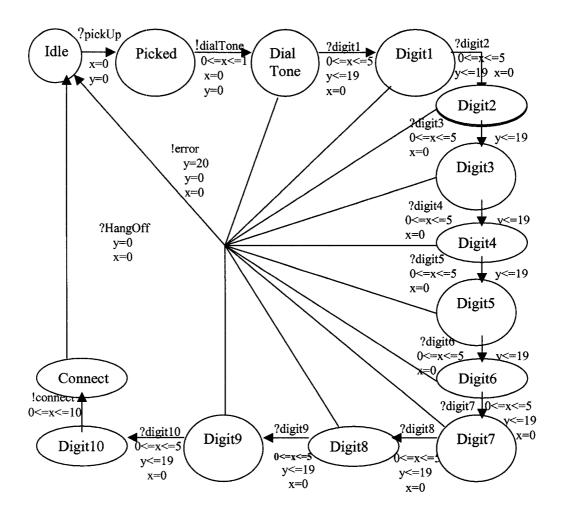

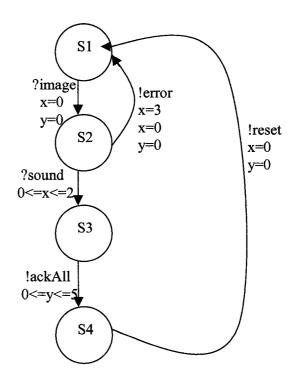

| 5.1 Hypothetical Telephone System      | 82  |

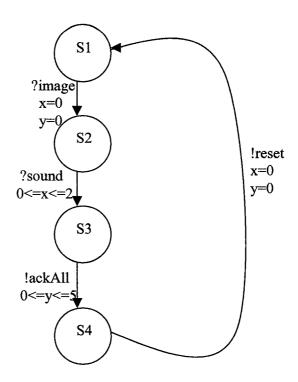

| 5.2 Small Multimedia System            | 84  |

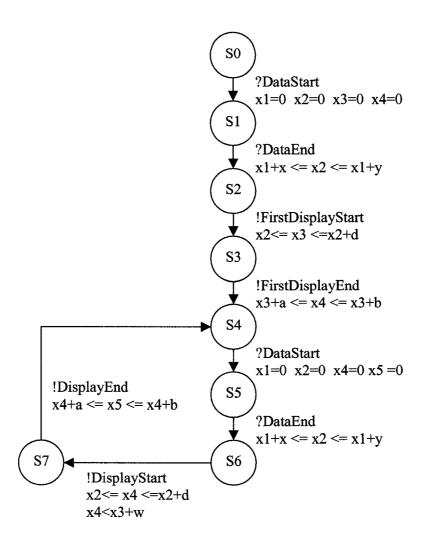

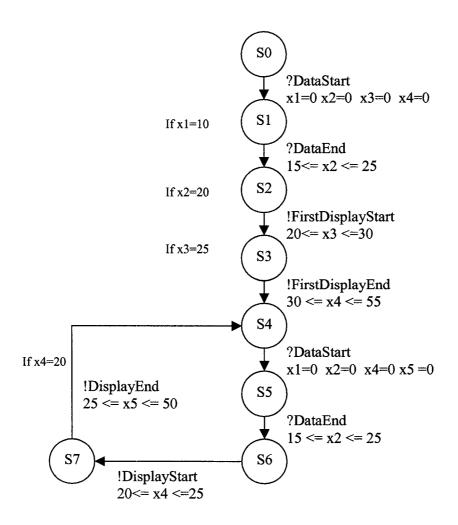

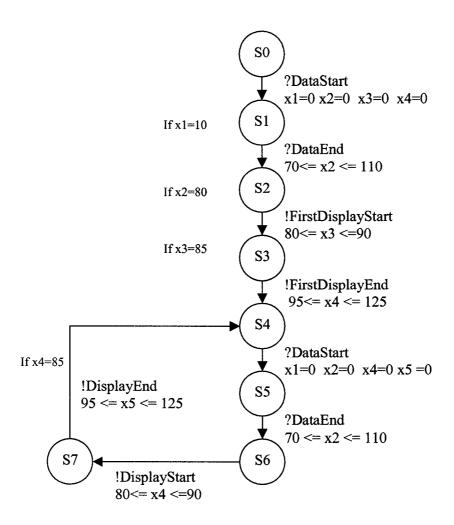

| 5.3 Media Synchronization Protocol     | 86  |

| 5.4 Railroad Crossing System           | 90  |

| 5.5 Results Validation                 | 93  |

| 5.6 Results Analysis                   | 99  |

| 5.7 Conclusion                         | 100 |

| CHAPTER VI: CONCLUSION                 | 101 |

| REFERENCES                             | 103 |

| APPENDICES                             | 107 |

| Appendix A                             | 107 |

| Appendix B                             | 109 |

# List of Figures

| FIGURE 1: TEST ARCHITECTURE                         | 5  |

|-----------------------------------------------------|----|

| FIGURE 2: THE CONTEXT DIAGRAM OF THE DEVELOPED TOOL | 7  |

| FIGURE 3: FSM EXAMPLE (1)                           | 12 |

| FIGURE 4: FSM EXAMPLE (2)                           | 14 |

| FIGURE 5: FSM EXAMPLE (3)                           | 16 |

| FIGURE 6: FSM EXAMPLE (4)                           | 18 |

| FIGURE 7: THE TOOL INPUT, PROCESS AND OUTPUT        | 27 |

| FIGURE 8: FILE FORMAT                               | 28 |

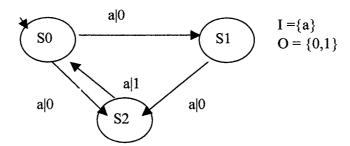

| FIGURE 9: TIOA SPECIFICATION                        | 28 |

| FIGURE 10: TIOA EXAMPLE WITH ONE CLOCK              | 30 |

| FIGURE 11: GRID AUTOMATON OF FIGURE 10              | 31 |

| FIGURE 12: SAMPLING ALGORITHM                       | 32 |

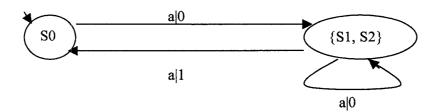

| FIGURE 13: NFSM TRANSFORMATION                      | 33 |

| FIGURE 14: NFSM of FIGURE 11                        | 34 |

| FIGURE 15: TRANSFORMATION ALGORITHM                 | 36 |

| FIGURE 16: NOT OBSERVABLE NFSM                      | 37 |

| FIGURE 17: ONFSM of FIGURE 16                       | 37 |

| FIGURE 18: : NON-MINIMIZED NFSM                     | 39 |

| FIGURE 19: THE MINIMIZED NFSM OF FIGURE 18          | 39 |

| FIGURE 20: MINIMIZATION ALGORITHM                   | 40 |

| FIGURE 21: NFSM UNDER TEST                          | 42 |

| FIGURE 22: SIMPLE GRAPH                             | 43 |

| FIGURE 23:DIJKSTRA ALGORITHM (1)                      | 44 |

|-------------------------------------------------------|----|

| FIGURE 24: DIJKSTRA ALGORITHM (2)                     | 45 |

| FIGURE 25: DIJKSTRA ALGORITHM (3)                     | 45 |

| Figure 26: Dijkstra algorithm (4)                     | 46 |

| FIGURE 27: DIJKSTRA ALGORITHM (5)                     | 47 |

| FIGURE 28: Q ALGORITHM                                | 49 |

| Figure 29: P algorithm                                | 50 |

| FIGURE 30: R ALGORITHM                                | 51 |

| FIGURE 31: WI ALGORITHM                               | 52 |

| FIGURE 32: W ALGORITHM                                | 52 |

| FIGURE 33: TEST SUITE ONE ALGORITHM                   | 53 |

| FIGURE 34: TEST SUITE TWO ALGORITHM                   | 54 |

| FIGURE 35: OPTIMIZATION ALGORITHM                     | 55 |

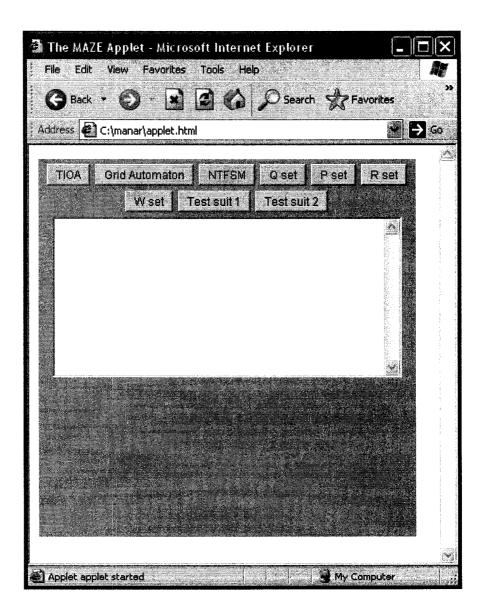

| FIGURE 36: TOOL USER INTERFACE                        | 59 |

| FIGURE 37: COMPILER STRUCTURE                         | 61 |

| FIGURE 38: THE CLASS DIAGRAM OF THE TOOL              | 68 |

| FIGURE 39: THE SEQUENCE DIAGRAM OF THE TOOL EXECUTION | 71 |

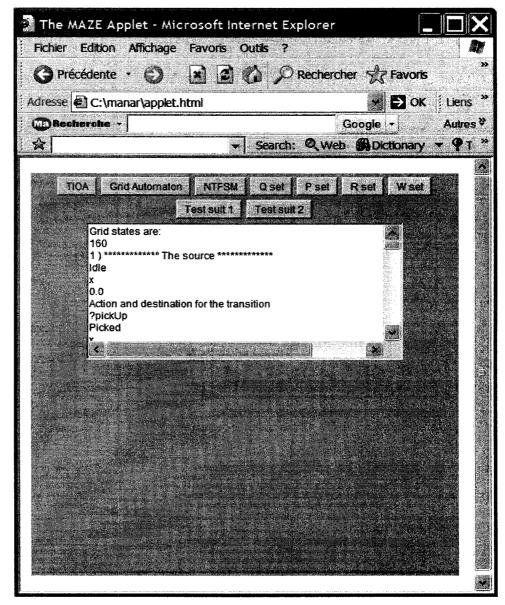

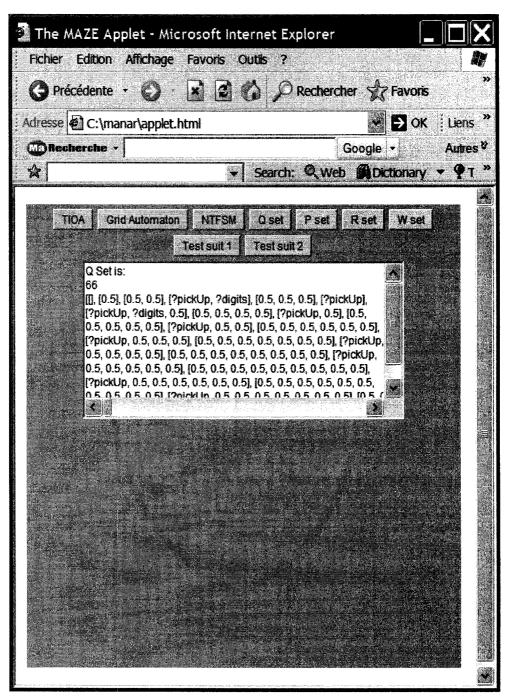

| FIGURE 40: RUNNING THE TOOL (1)                       | 78 |

| FIGURE 41: RUNNING THE TOOL (2)                       | 79 |

| FIGURE 42: RUNNING THE TOOL (3)                       | 80 |

| FIGURE 43: TELEPHONE SYSTEM (1)                       | 83 |

| FIGURE 44: TELEPHONE SYSTEM (2)                       | 84 |

| FIGURE 45: Multimedia system                          | 85 |

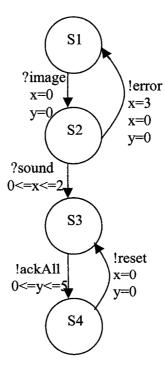

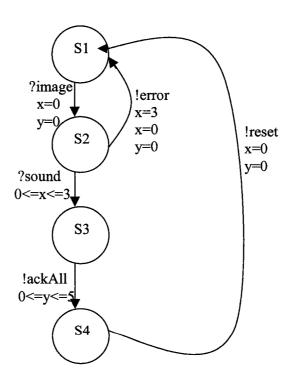

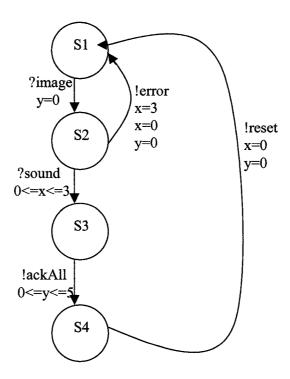

| FIGURE 46: MEDIA SYNCHRONIZATION PROTOCOL (1)           | 87            |

|---------------------------------------------------------|---------------|

| FIGURE 47: MEDIA SYNCHRONIZATION PROTOCOL (2)           |               |

| FIGURE 48: MEDIA SYNCHRONIZATION PROTOCOL (3)           | 89            |

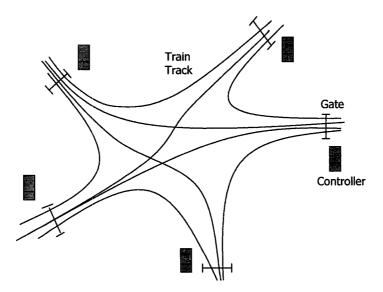

| FIGURE 49: RAILROAD CROSSING SYSTEM                     | 90            |

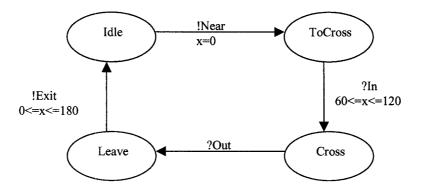

| FIGURE 50: TRAIN                                        | 91            |

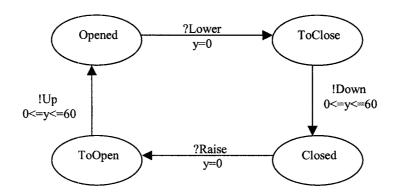

| Figure 51: Gate                                         | 91            |

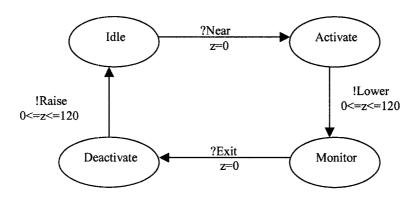

| FIGURE 52: CONTROLLER                                   | 92            |

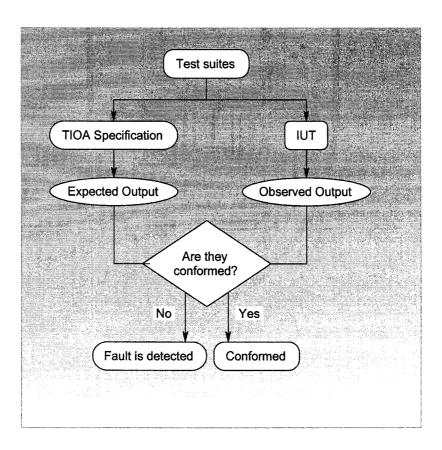

| FIGURE 53: ORACLE METHODOLOGY                           | 94            |

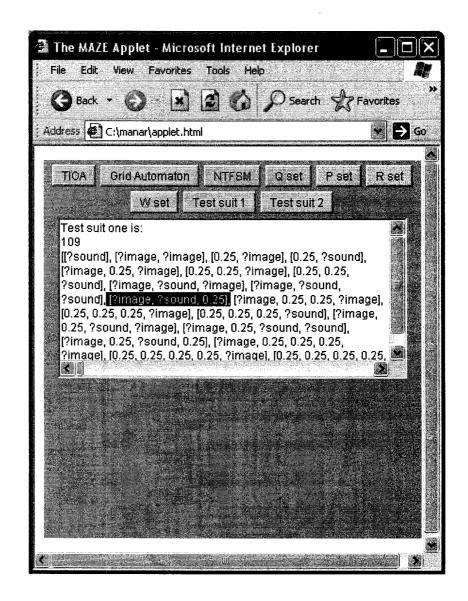

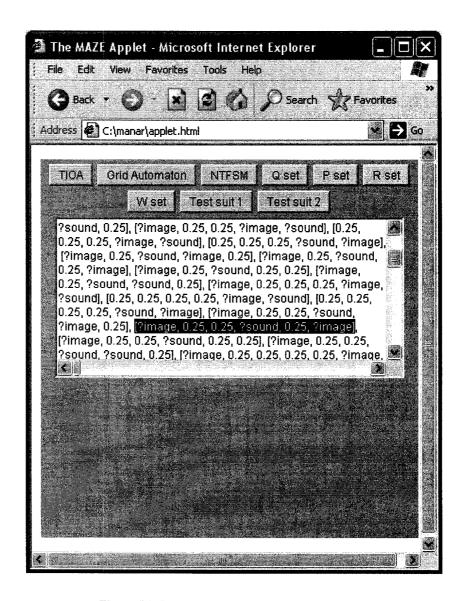

| FIGURE 54: TEST SUITE ONE OF THE MULTIMEDIA SYSTEM      | 95            |

| FIGURE 55: TEST SUITE TWO OF THE MULTIMEDIA SYSTEM      | 96            |

| FIGURE 56: MULTIMEDIA SYSTEM WITH OUTPUT FAULT          | 97            |

| FIGURE 57: MULTIMEDIA SYSTEM WITH TRANSFER FAULT        | 97            |

| FIGURE 58: MULTIMEDIA SYSTEM WITH TIME CONSTRAINT WIDER | NING FAULTS98 |

| FIGURE 59: MULTIMEDIA SYSTEM WITH RESET CLOCK FAULT     | 99            |

| FIGURE 60: TIOA WITH ONE CLOCK                          | 109           |

| FIGURE 61: SAMPLING ACTIVITY DIAGRAM                    | 111           |

| FIGURE 62: TRANSFORMATION ACTIVITY DIAGRAM              | 113           |

| FIGURE 63: MINIMIZATION ACTIVITY DIAGRAM                | 114           |

| FIGURE 64: TEST CASES ACTIVITY DIAGRAM                  | 116           |

| FIGURE 65: Q ACTIVITY DIAGRAM                           | 118           |

| FIGURE 66: WI ACTIVITY DIAGRAM                          | 119           |

# List of Tables

| TABLE 1: DS OF FIGURE 4                                      | 14 |

|--------------------------------------------------------------|----|

| TABLE 2: UIO SEQUENCES OF FIGURE 5                           | 16 |

| TABLE 3: W SET OF FIGURE 6                                   | 18 |

| TABLE 4: W AND WI RESULTS                                    | 20 |

| TABLE 5: DIJKSTRA DATA STRUCTURE                             | 48 |

| TABLE 6: USER INTERFACE ISSUE                                | 58 |

| TABLE 7: PARSER ISSUE                                        | 60 |

| TABLE 8: HIGH LEVEL LANGUAGE ISSUE                           | 64 |

| TABLE 9: Q ISSUE                                             | 65 |

| TABLE 10: TIOA PACKAGE                                       | 69 |

| TABLE 11: GRID AUTOMATON PACKAGE                             | 70 |

| TABLE 12: NFSM PACKAGE                                       | 70 |

| TABLE 13: PARSER PACKAGE                                     | 71 |

| TABLE 14: SEQUENCE DIAGRAM INFORMATION OF THE TOOL EXECUTION | 72 |

| TABLE 15: TELEPHONE SYSTEM RESULTS (1)                       | 83 |

| TABLE 16: TELEPHONE SYSTEM RESULTS (2)                       | 84 |

| TABLE 17: MULTIMEDIA SYSTEM RESULTS                          | 85 |

| TABLE 18: RESULTS OF THE MEDIA SYNCHRONIZATION PROTOCOL (1)  | 88 |

| TABLE 19: RESULTS OF THE MEDIA SYNCHRONIZATION PROTOCOL (2)  | 89 |

| TABLE 20: TRAIN RESULTS                                      | 92 |

| TABLE 21: GATE RESULTS                                       | 93 |

| TABLE 22: CONTROLLER RESULTS                                 | 93 |

# **CHAPTER I: INTRODUCTION**

Although testing principles developed for non-real-time systems are applicable for real-time systems, the fact that time is a parameter in the testing complicates many issues [1]. However, before introducing the testing methods for real time systems, what does real time systems mean? What are their characteristics? What does testing mean? Why is testing important? How to test real time systems? In this chapter, we try to answer the above questions. The objective and the outline of this thesis are also introduced.

# 1.1 Definition of Real Time Systems

Most of the processors produced today are used in the embedded systems [2], [1]. Many of these embedded systems have real-time requirements and therefore are called real time systems (e.g., airplanes, patient monitoring systems, microwave ovens, mobile telephones and toys). This means that the successful operation in such systems is measured not only on the correctness of the result produced but also on the time of response. Real-time systems, therefore, interact with their environment using time constrained input/output signals. Another definition of a real-time system can be in terms of a "real-time task" where a real time system contains at least one real-time task [1], [3]. In theory, a real-time task is a task that must be completed at specific time (not before or after that specific time) [1], [4]. However, in practice, it is usually enough if the real-time task is completed before the specific time, that is, the deadline.

Real-time systems are often classified according to the cost of missing a deadline. Based on that, Locke describes four different classes (soft, firm, hard essential, and hard critical) of real-time systems. "In a soft real-time system, completing a task after its deadline will still be beneficial even if the gain is not as big as if the task had been completed within the deadline and it may be acceptable to occasionally miss a deadline. In a firm real-time system, completing a task after its deadline will neither give any benefits nor incur any costs. In a hard essential real-time system, a bounded cost will be the result of missing a deadline. An example may be lost revenues in a billing system. Finally, missing a deadline of a hard critical system will have disastrous results, for instance loss of human lives" [1].

It is to be noted that different inputs to the real time systems lead to input types. If two inputs have entered the same channel in a system and they only differ in the time of entrance, then they have the same input type [1]. Input types may be very different from each other. Temperature readings, keyboard commands and pushing a call button of an elevator are examples of input types. An input type may be periodic, sporadic or aperiodic. If an event occurs with a regular period, then it is periodic. If inputs occur any time and there is a known minimum inter-arrival time between two consecutive inputs then it is sporadic. Finally, if nothing is known about how often inputs may occur or when it is known that inputs may occur anytime, then it is aperiodic.

Real time systems have many characteristics [5]. They are large and complex. They contain many components with complicated relationships between them. However, they have concurrent control of the system components. They also have facilities for the hardware control. Real time systems should be extremely reliable and safe. They have the ability to fail in such a way to preserve as much capability and data as possible and to detect and correct the failure. A processor failure in a non real time

system may result in reduced level of service; however, in a real time system it may be catastrophic such as life and death, financial loss and equipment damage. For example, when a pilot moves his airplane, the computer-controlled system is expected to change the rudder almost immediately. If the rudder is moved too slowly or too fast, the plane might become instable and crash. Still, to the best of our knowledge, little attention has been devoted to develop an automatic tool for testing real-time systems since the time parameter complicates many issues in the testing [1].

To that end, real time systems can be defined as systems whose behavior is time dependent. These systems are highly used nowadays and software engineering is responsible for controlling safety for these critical systems.

# 1.2 Verification and Testing

Verification and testing are two essential techniques that are used to cope with the correctness of a system. Verification can guarantee the correctness of the system specification. It aims to ensure that the designed specification satisfies predefined functional and timing requirements [6]. Our concern lies on testing, , that is, dynamic execution of test cases [1], [7]. It is an important activity that aims to ensure the quality of the implementation, which verification doesn't guarantee. Testing techniques check whether or not an implementation conforms to its specification [6].

Testing procedure consists of generating test cases and applying them to the implementation, which is referred to as Implementation Under Test (IUT). Three main testing strategies are available, which are white-box testing, black box testing and gray-box testing. Fault model is also another important aspect in the testing of an implementation for a system. It is referred to the potential basic fault that can exist in

an implementation [8] [9] [10] [11] [12]. In fact, some techniques, which generate the test cases, may able to detect all the potential faults, while others may fail in detecting some faults.

Assessing and increasing reliability are the major goals of testing [1], [13]. Based on monitoring the number of encountered failures, the test cases are chosen and executed to assess the reliability. A failure is defined as "a deviation of the software from its expected delivery or service" [1], [7]. To increase the reliability, it depends on selecting test cases that are assumed to be especially likely to detect failures. The observed traces are analyzed to find the cause of the failure, which is the fault [7]. By removing the fault, the reliability is assumed to increase. The power of test cases generation technique to detect faults in an implementation is referred to as fault coverage. Many different test methods exist (e.g. formal methods based on FSM and EFSM [14]) that are all assumed to generate test suites containing test cases especially prone to revealing failures. These test methods can be compared according to their respective fault coverage. One method is more powerful than the other if it has a better fault coverage. In this research, Timed Wp-Method is chosen for the derivation of test cases for real-time systems modeled as a TIOA, a variant of the Alur and Dill timed automat a model [15] [16].

Gray-box testing is applied as efficient strategy to test real time system using Timed Wp-Method. Before explaining that strategy we have to indicate that in white-box testing, the test suite is generated from the implemented structures, while in black-box testing the structure of the implementation is not known and the test cases are generated and executed from the specification of the required functionality at defined interfaces. In gray-box testing, the modular structure of the implementation is known

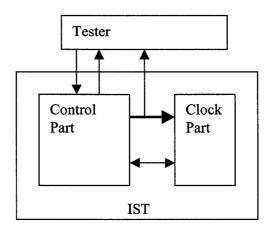

but not the details of the programs within each component. As we can see in Figure 1, the testable model consists of two parts: the control part and the clock part.

Figure 1: Test architecture

The tester knows and reaches some of these parts where he can observe when the clock resets to zero. The control part indicates the interaction between the timed system and its environment by exchanging input and output signals. However, the clock part handles the clock variable, used in the specification of the timed system. There are two channels, which are connecting the two parts. One channel is used to exchange some internal signals after the control part receives an input from the environment and checks with clock part whether or not the input satisfies the time constraint of the specification. In other channel, clock reset signal is sent by control part to the clock part asking it to reset the clock to zero.

# 1.3 The Objective of the Thesis

Based on the work published by Dr. Abdeslam En-Nouaary in [34], this thesis is intended to develop a tool that generates the test cases for testing real time systems

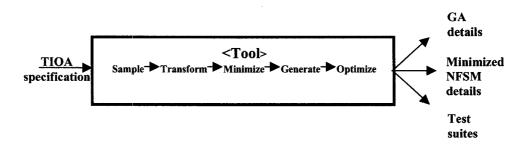

using the Generalized Wp method (Figure 2). The developed methodology is composed of five steps:

- 1. Sampling the Timed Input Output Automaton (TIOA) by using a suitable granularity, in order to have a Grid Automaton, which is a simplified sub automaton that can be easily tested [6].

- 2. The transformation of the Grid Automaton into a Non-deterministic Timed Finite State Machine (NFSM) [6].

- 3. The minimization of the obtained NFSM.

- 4. The generation of test cases based on the generalized WP-method [6].

- 5. The optimization of the obtained test cases. The fault coverage of test cases generation method is then estimated and its ability is shown to detect many possible faults

Figure 2: The context diagram of the developed tool

In this thesis, we have designed the tool and chosen the appropriate algorithms and data structures. We have chosen JAVA language to implement our tool for reasons listed in Chapter 3.

# 1.4 Outline of the Thesis

The rest of this thesis is structured as follows: Chapter 2 provides an overview of some model based testing methods. In order to have a well-designed tool, Chapter 3 explores the data structures and the algorithms. Chapter 4 includes the implementation details and the solutions of the major design decisions and the design quality attributes are introduced. In Chapter 5, many examples are examined and evaluated using the tool. We also validate our results at the end of that chapter. Finally, Chapter 6 provides a conclusion of what was achieved and why the work is important. In addition, pointers for future research are given.

#### CHAPTER II: STATE OF THE ART

The testing phase represents a large effort within the common software development cycle. Generation of the test cases is the first step in testing the software process. The most difficult problems in generating the test cases are finding a test data selection strategy that is both valid and reliable [17]. In this chapter, we present the state of the art of the test cases generation methods.

# 2.1 Testing Based on FSM Model

The Finite State Machine (FSM) model [18] is the base of the most research contributions in test derivation and selection. It was used since 50s in testing the sequential circuits, the communication protocols and the object-oriented systems. One raised problem with the test based on FSM Model is the conformance testing. We want to test whether the implementation Mi conforms to the specification Ms through observing the Input/Output behavior of Ms. To do so, we define a conformance relation to link Mi with Ms. The most conformance relation used is the traces equivalence. It is based on the observable behavior of the implementation after the application of the test suites.

The test cases generation for FSM is often done under certain hypotheses of Ms specification and the fault types that can be presented in Mi implementation. The hypotheses of Ms specification are used in order to ensure that the specifications with the desired properties are treated. The implementations' hypotheses and the concerned possible fault types are used to limit the implementation's domain that will be considered. Without these hypotheses, each FSM can be considered as a possible

implementation of a given specification, thus the number of implementation machines will be infinite.

In general, the specification is supposed to be an FSM that is:

- Deterministic: where  $\delta: S \times I \to S$  is a transfer function,  $\lambda: S \times I \to O$  is an output function, S is a state, I is an input and O is an output.

- Reduced: there are no equivalent states in FSM. Refer to 3.5 section.

- Strongly connected: any state can be reached from the initial state.

- Completely specified: where δ: S x I → S and λ: S x I → O are complete functions that reach to any input. Empty output is also allowed; but the completeness is implicit.

However, the implementation is often supposed to be an FSM that is:

- Having a limited number of extra states.

- Deterministic.

- Strongly connected.

- Completely defined: providing an answer for any input in a limited time.

- Implementing correctly the reset action.

Many of these assumptions can be avoided and methods have been developed for partially specified and nondeterministic behaviors (see the following sections). Now with the above hypotheses, the FSM fault model can be summarized with the following four fault types [19]:

- Output faults: these faults cause a state not to respond with an expected output.

- Transfer faults: these faults cause a state with a specific input or output to enter a state different from the expected one.

- Transfer faults with the additional states: the arrival state of a transition is a new one.

- Transitions' faults (additional or missing transitions): usually, we suppose that the automaton is deterministic and completely specified, which means that for each input of a state, there's exactly one corresponding transition coming out of that state. The absence of this transition is also a fault of this type.

Many methods of test cases generation from FSM were developed. There are two categories: methods based on states' identification and others based on simple path of all transitions. In the following sections, we discuss some of these methods.

# 2.1.1 Transition Tour Method

The transition tour method [20] consists of generating a single input sequence that traverses all the transitions at least once and returns to the initial state. Obviously, the generated sequence can contain many redundant inputs that generate cycles in the sequence. This can be avoided by optimizing the transition tour. Some efficient algorithms such as Chinese Postman Algorithm for the transition tour derivation of certain FSM classes were studied in [21].

The problem of finding the optimal transitions in FSM is a well-known problem in the graph theory. In fact, FSM is seen as oriented graph and optimal transition tour, which seems exactly like Euler tour. An Euler tour in an oriented graph is the transitions' sequence, which starts and ends at the same state and it contains each transition at least once. To have an Euler tour in an oriented graph, the graph has to be:

- Strongly connected.

- Symmetric: a graph is called symmetric if and only if the number of the incoming transitions for each state in the graph is equal to the number of the outgoing transitions for the same state. A non-symmetric graph can be

transformed into a symmetric one by an incremental procedure [22]. This consists of duplicating certain transitions till the graph becomes symmetric.

The fault coverage of the generated test cases by the method of transition tour is not complete. In fact, the range of test cases checks only the transitions' outputs. This is not enough since it has to check the state where the implementation under test exists after each transition. This method has a limited error detection power compared to other methods since it doesn't consider the state verification. However, an advantage of this method is that the test sequences obtained are usually shorter than test sequences generated by the other methods.

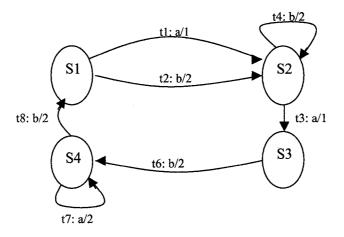

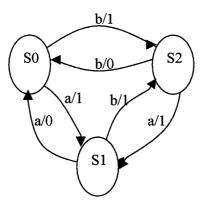

In Figure 3, the possible transition tour is formed by the transitions' sequence:  $t_1$ .  $t_4$ .  $t_3$ .  $t_6$ .  $t_7$ .  $t_8$ .  $t_2$ . No transition needs to be traversed twice. It's clear that the arrival state of the last transition,  $t_2$ , is not checked. As a result, if  $t_8$  transition reaches to S2 instead of S1, this transfer fault will not be detected. In order to systematically detect the transfer faults, one has to identify the state into which the implementation goes after the execution of the tested transition.

Figure 3: FSM example (1)

# 2.1.2 Distinguishing Sequence Method

The distinguishing sequence (DS) method [23] is a state identification sequence and it is applicable if FSM has one distinguishing sequence. A distinguishing sequence is a sequence of inputs that produces a different sequence of outputs for each FSM state: sequence x that produces different output for each state such that for all pairs t, s with  $t \neq s$ :  $\lambda(s, x) \neq \lambda(t, x)$ .

The DS method consists of two steps: the state verification and the transition verification. During the first step in the state verification, the implementation has to provide the observed output to the distinguishing sequence for each state. For example, by applying the sequence of inputs in the current state of FSM such that from the outputs we can identify whether or not that state is where we should go. The second step of the DS method consists of checking each FSM transition.

The states' verification is done by applying the following procedure to each FSM *si* state:

- The implementation is carried out at  $i_i$  state, which is supposed to be isomorphic to  $s_i$  state, by applying the reset action at the initial state followed by the *preamble* from the initial state  $s_0$  to  $s_i$  state.

- The DS sequence is submitted to the implementation to check whether or not the observed output is equal to the excepted output.

This phase ensures that the implementation has at least n states  $i_1$ ,  $i_2$ ,  $i_3$ , ...,  $i_n$ , which are accessible by the same preambles of their isomorphic states  $s_1$ ,  $s_2$ ,  $s_3$ , ...,  $s_n$  in the specification.

However, many transitions are used in the distinguishing sequence preamble during the states' verification. These transitions must be implemented correctly. It's the transitions' verification step that has the role to test each transition  $s_i$  to  $s_j$  according to the following procedure:

- The implementation is carried out at  $i_i$ , which is isomorphic to  $s_i$ , by applying the reset action at the initial state followed by the preamble  $Preamble(s_i)$ ;

- The *i* input is submitted to the implementation and the output is observed to check if it is the same as the expected output;

- By the application of DS sequence, the new implementation state is tested to check if it is  $i_i$ .

The DS method guarantees complete fault coverage (detecting both transfer and output faults). However, the disadvantages of this method is that a DS may not be found for a given. Also applying a fixed length sequence may not lead to the shortest state identification sequence. Table 1 shows that DS = a.a for the FSM shown in Figure 4. The corresponding outputs sequences and the preambles for each state are also shown in the table.

Figure 4: FSM example (2)

Table 1: DS of Figure 4

| State A Making | Output for IOS | AND THE COUNTY OF THE PARTY. |

|----------------|----------------|------------------------------|

| S0             | 0.1            | Null                         |

| S1             | 1.0            | a/0                          |

| S2             | 0.0            | b/0                          |

# 2.1.3 UIO Method

The unique Input/Output sequence (UIO) method consists of generating test sequences that check if the arrival state of each transition is the right one (or the transfer is correct). To do so, it uses the unique Input/Output sequence of the arrival state. It allows distinguishing this state from others.

To apply the UIO method, the FSM specification has to contain an initial state. As in DS method, each state of this FSM must have its own Input/Output sequence. The test procedure done for each transition  $s_i$  to  $s_i$  is as follows:

- Bring the FSM to its initial state,  $s_0$ , using the reset operation.

- Find the shortest path from the initial state to  $s_i$ .

- Apply *i* input to do the transition execution and check if the output is as expected.

- Apply the unique Input/Output sequence of  $s_i$  to check if it's the good state.

It happens sometimes, that the unique Input/Output sequence doesn't exist for a state. In this case, the signature technique is used. The signature of  $s_i$  is a sequence formed of a set of minimal Input/Output sequences,  $IO(s_i, s_j)$ , each one of them starts at  $s_i$  and distinguishes  $s_i$  from another state  $s_j$  ( $j \neq i$ ).

In the original paper where the UIO method was proposed, the authors used only the verification of transitions to generate the range of the test cases because they thought that the transition verification is enough to guarantee good fault coverage. In [24], Vuong took this lack into consideration by showing certain faults that can be hidden from the tester. As a result, he recommended adding the states' verification step to the UIO method, which gives a new method, called UIOv method. This step of states'

verification consists of ensuring that the Input/Output sequences are unique in the implementation under test. To do so, the UIO  $(s_i)$  sequence for  $s_i$  state in the specification is accepted by its isomorphic state in the implementation, and it's rejected for the rest of states. The reject procedure of UIO  $(s_i)$  sequence by a state  $s_j$  is the following:

- Bring the implementation at  $i_j$  state, which is supposed to be isomorphic to  $s_j$  state, by applying the reset action in the initial state followed by the preamble from the initial state  $s_0$  to  $s_j$  state.

- Submit the UIO  $(s_i)$  sequence to the implementation and check if the observed output is really different from the expected one by applying the UIO  $(s_i)$  to  $s_j$ .

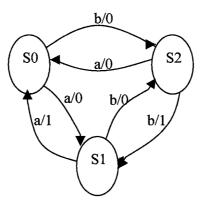

In Figure 5 and Table 2, we present an FSM and its corresponding UIOs for each state.

Figure 5: FSM example (3)

Table 2: UIO sequences of Figure 5

| State | ·UIO (6) IT TO SEE SEE | Manufer and the second |

|-------|------------------------|------------------------|

| S0    | b/1                    | Null                   |

| S1    | a/0.b/1                | a/0                    |

| S2    | a/1                    | b/1                    |

# 2.1.4 W Method

The DS method has the advantage of having complete fault coverage. However, its major disadvantage is that the DS sequence doesn't exist for all FSM. This limits the application of DS method and constitutes a kind of motivation to look for more general method. The W method [17] is a general method, which is applicable for all minimal FSM. It's based on the fact that for all FSM, there exists a set of finite input sequences, called W characterization set, such that the output sequences are unique for each state.

Besides W set, W method has a second set of input sequences, called the *set of transitions cover*. We write P for any set of input sequences (including the empty set), which tests for each transition  $s_i$  to  $s_j$  of the specification. This means, the set P consists of all partial paths and it can be formed from a testing tree, which shows every transition from state  $s_i$  to state  $s_j$  on each input.

The W method produces a set of test cases, which are formed from the concatenation of Z and P sets (e.g. P.Z) where  $Z = (\{ \epsilon \} \cup I \cup I^2 \cup ... \cup I^{m-n}) .W$ . The use of Z set instead of W set is principally due to the fact that the number of states, m, in the implementation can be greater than the number of states, n, in the specification. If m = n, we will have Z = W and accordingly, the range of test cases will be P.W. Each test sequence starts with the initial state and returns to it again.

The assumptions about the implementation under test are that the implementation is minimal, may start in a fixed initial state, and is strongly connected. Under these assumptions a W-set exists, and the W-method gives a set of sequences that are guaranteed to detect any misbehavior of the implementation. However, the disadvantage of using this method is that the W-set may not exist for every FSM,

especially if it is an incompletely specified machine. Therefore, before using this method, if the machine doesn't have a W-set sequence, one should make the machine to be a completely specified. For example, adding an "error" state and declaring all unspecified transitions to lead to this state.

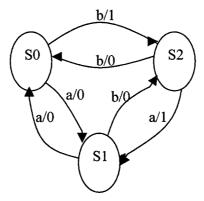

The main goal of the W method is to test whether or not an implementation conforms to FSM specification. To do so, we check for each input sequence whether or not the observed outputs are the same as the expected outputs. The set of tests (P.Z) detects all output and transfer faults since the number of states in the implementation doesn't exceed m. Figure 6 and Table 3 show respectively a reduced FSM and the corresponding W set.

Figure 6: FSM example (4)

Table 3: W set of Figure 6

| State | Output for W = (a, b) | Premile (s): Extent |

|-------|-----------------------|---------------------|

| S0    | {1, 1}                | Null                |

| S1    | {0, 1}                | a/1                 |

| S2    | {1, 0}                | b/1                 |

There are two modes to check the verification [17] of test sequence: the test mode and the walkthrough mode. The test mode is to build the correct responses in the form of the operation sequences, which is based on the specification and the semantics of the

operations. The responses from the design are then derived and compared with the correct or expected version. In the walk-through mode, the input sequences and their corresponding responses from the design are represented as "path programs". The correctness of these programs can be established by a walkthrough procedure based on the specification. When the testing sequences are got from the concatenation of P and W, it can be decided whether or not a path program is correct.

The proof of the fault detection power of W-method is given in [17].

## 2.1.5 The Partial W Method

In [25], the partial W (Wp) method is introduced to determine whether or not a given implementation protocol satisfies the properties required by the specification protocol. The Wp method is a generalization of UIOv method which is always applicable. It is at the same time an optimized and a refined version of W method since it reduces the length and the number of the test cases. Therefore, the assumptions made for Wp method is similar to those made for W method. FSM is strongly connected and deterministic. It also contains no equivalent states and it is a completely specified machine. Instead of using W set to check each reachable state  $s_i$ , only a subset of this set can be used in certain cases. These subsets are called the state identification set (Wi) for  $s_i$ . Wi set is a set of  $s_i$ , if and only if, Wi is minimal and for each state  $s_j$  ( $j\neq i$ ), it exists a sequence of inputs which belong to Wi and generates two different behaviors in  $s_i$  and  $s_j$ . The Union of all Wi produces W characterization.

The Wp method consists of two phases. The first phase checks that all states defined by the specification are identifiable in the implementation, and each si state in the

implementation can be identified by the Wi set. The test cases that allow achieving these objectives are given by Q. ( $\{\epsilon\}\ U\ I\ U\ I^2\ U\ ...\ U\ I^{m-n}$ ). W, where W is the characterization set and, m is the maximal number of states in the implementation, and Q is the cover set of states. The Q set consists of the input sequences that allow reaching the specification states from the initial states. At the same time, the transitions leading from the initial state to these states are checked for the correct output and the state transfer.

The second phase checks the implementation of all specified transitions, which aren't tested in the first step. The test sequences of phase 2 consist of the sequences of P which are not contained in Q, concatenated with the corresponding Wi, written R×W, where R=P-Q, that is the set of all transitions that is not part of Q. It is noted that different test sequences are obtained depending on the choices made for the sets P,Q and Wi.

Finally, the test hypotheses of Wp method are the same as W method and its fault coverage is complete. The following table shows W and Wi sets (i = 0, 1, 2) for FSM in Figure 6 and the corresponding outputs.

Table 4: W and Wi results

| State | Output for | Presurble for | Vi Alinin |        |

|-------|------------|---------------|-----------|--------|

| S0    | {1, 1}     | Null          | {a, b}    | {1, 1} |

| S1    | {0, 1}     | a/1           | {a}       | {0}    |

| S2    | {1, 0}     | b/1           | {b}       | {0}    |

# 2.1.6 The Generalized Wp Method

The generalized *Wp* method, generates test sequences for both non-deterministic and deterministic finite state machines. The generalized *Wp*- method [26] is based on extending the state identification approach used for deterministic finite state machines to non-deterministic finite state machines (NFSM). To do so, the NFSM is transformed to an observable NFSM. ONFSM has a property that a state and an input|output pair uniquely determine the next state, while a state and an input alone do not necessarily determine a unique next state and an output.

The generalized Wp method uses the same sets as Wp method uses but with the fairness hypothesis. This hypothesis means that it's possible to reach all accessible states by one input sequence t in one implementation by applying t on it for n finite times. Without this hypothesis, no set of test cases can guarantee complete fault coverage for a non-deterministic implementation. Refer to 3.6 section for a detailed example of this method.

The generalized *Wp* method is applicable for concurrent systems that are modeled as FSMs, which communicate with each other through channels: first, the FSMs of the system are composed, by using the accessibility analysis, to obtain one FSM. After that, the generalized *Wp* method is applied on that FSM. Refer to 5.4 section for an example.

# 2.2 Real Time Systems Testing

The last three decades have known intensive research activity in the un-timed test domain. However, the computer systems are more specified nowadays with the temporal constraints in order to control their execution. This motivated researchers to

develop new test methods for these systems. In the following, we expose a list of researches about generating the timed test cases.

# 2.2.1 Test Cases Generation for Theory Formulas

This approach [27] consists of generating test cases from a theory formula. The used logic is an extension of the classical timed logic in order to model the real time systems. The time aspect is expressed according to two fundamental constructors, future and past, referring respectively to the moments in the future and the moments in the past. In this theory, one clock is used.

To generate test cases from formula F, F is decomposed in a hierarchical structure in terms of the atomic formulas that contain events only. An event is a couple (L, t) that is formed from L literal and t moment. A set of events that doesn't contain any contradiction and is happening at the same time (the two events (L, t) and  $(\neg L, t)$ ) is called a history. Each leaf, that doesn't contain any of the decomposition tree of a formula F, is considered as F history. A history of the formula F is called "complete" if it contains a unique value of truth for each predicate formula and at any point in the temporal domain. A test case of formula F is a complete history satisfying F in many points of its temporal domain. This domain is discredited in the digital values.

A complete test case of F formula is constructed by the application of the offset and the concatenation operation of the test cases with the small sizes, called elementary test cases. These are directly extracted from F decomposition tree. The offset  $\Delta$  of the test case time unites, which satisfies F formula at t moment, consists of the test case

satisfying F at  $t + \Delta$  moment. Beside that, the concatenation of two test cases  $TC_1$  and  $TC_2$  is the test case  $TC_3$  obtained by the union of  $TC_1$  and  $TC_2$  event sets.

This method of generating the timed test case, suffers from the following lack: the range of the generated test cases can cover only the digital values of the temporal domain for the formula specification logic. The used logic can only serve in describing very restrictive classes of the real time systems (Those which are specified according to one clock).

# 2.2.2 Test Cases Generation for FSM Model with Timers and Counters

This method [28] generates the timed test cases from a specification given as an FSM with timers and counters by using Wp method [25]. First of all, the behavior of each timer and counter is modeled as FSMs. Then, all the FSMs are combined so that they have only one global FSM, which describes the system. Finally, the Wp method is applied on the resulting FSM with certain hypothesis.

# FSM timer is defined by:

- Two states indicating respectively the activity and the inactivity timers;

- An alphabet, which forms the corresponding events in respect to the triggering timer, stop and expiration, and the flow period in which the timer is activated;

- A set of the transitions between the states with the appropriate events.

# FSM counter is defined by:

- A set of the states representing the different counter values;

- Two events representing respectively the reset and the incremental counter;

- A set of the transitions between the states with the appropriate events.

The problem of this approach is being not applicable for all systems such as systems, which have the general shape of the temporal constraint.

# 2.2.3 Test Cases Generation for Timed Automaton

Springintveld and al. [29] present a theoretical framework for generating the test cases from Timed Input Output Automaton (TIOA). They adapt W method [17] with taking into account the temporal aspect of the real time systems. The conformance relation is used to judge whether or not the implementation conforms to its specification [30].

The approach contains many transformations. First of all, we count the number of TIOA region, which is a result from the automaton that is composed of both the implementation and the specification. This aims destructing the maximum traces length of the states' distinction. Then, we construct a sub-automaton from the region graph, called Grid Automaton, by using a "uniform mapping" [31]. This characterizes the relation ~ between the clocks' interpretations. The resulted automaton is finally used to generate the test cases by applying W method.

Grid Automaton is the labeled-transitions system summarizing the region graph behavior, which is necessary for the system exhaustive test. Each state in this automaton has a delay transition. Its period is 2<sup>-n</sup>, where n is the length of the states' distinction trace in the region graph for the automaton (that is composed of the implementation and the specification). In the worst case, n is equal to the number of the clocks in the region graph. The value 2<sup>-n</sup> is selected to allow the test cases, under certain hypotheses, detecting all possible faults in the implementation.

The main result of this work is the proof of the possibility for the exhaustive test to detect all faults in the implementation using the conformance relation. However, the major problems of this method are the restriction of the used model and the number of the generated test cases. The used model is TIOA in which the system outputs can exist in integer values of the clocks' temporal space. This restriction doesn't allow describing a large range of the real time systems where their outputs can be produced within the temporal range and at a specific point. For the sequence of the generated tests, its number is so big, even for a simple academic example. In fact, this big number of test cases is due to the transitions' period of 2<sup>-n</sup> delay used in constructing the Grid Automaton. This period is very small because the number of region clocks in TIOA is exponential to the number of clocks and the constants used for these clocks' constraints.

The authors don't use the exact number of the region clocks, but an approximation number to the superior bound provided by Alur and Dill [32].

### 2.3 Conclusion

In this chapter, we have reviewed the methods of the test cases generation from the most known formal models. More precisely, we have presented the test based on FSMs and the timed test. For each method, we have explained its strengths, its weakness and the conditions of its application. The Generalized *Wp* method will be used in next chapters to be applied in our developed methodology.

In the following chapter, we deeply discuss our developed methodology and its structure and processes. We propose the algorithms and the reasons of using them.

### **CHAPTER III: TIMED TEST CASES GENERATION**

For any tool to be built, it is an important task to go through its structure, functions and goals before designing it. Chapter 3 is based on IEEE standard [33] to point at these issues in order to not miss any small detail. Although it doesn't specify any particular design, it has the advantage of limiting the range of valid design. After having the clear picture of what the tool is, its functions and its goals, the areas of data structures and algorithms are introduced in this chapter. The next aim is not only designing the correct tool but it is more about evaluating the tool design in order to have quality attributes in it. As a result of this chapter, the implementation of the tool is as easy as mapping the data structures and algorithms to the direct code. Figures and examples are represented for understanding the steps of our developed methodology.

## 3.1 Tool Input, Process and Output

The tool should support the Generalized Wp method. The testing of the real time system should be done using the Generalized Wp method.

The steps of the test process are:

- The tool receives the Timed Input Output Automaton specification (TIOA) from the tester.

- > The tool displays its Grid Automaton information, its NFSM information, its test suites and the detailed information about them such as Q set, R set...etc.

- > The tester validates the results by using oracle (see section 5.5) to compare the observed outputs with the expected outputs.

The following figure presents an outside view of the tool. The tool has one primary actor (the tester) who initiates the activity by describing the real time system in terms of TIOA. Therefore, the input of the tool is TIOA specification. The tester is also responsible of running the tool to derive the test cases from the given TIOA based on timing constraints of the system. Therefore, the test suites, the Grid Automaton details and the Minimized NFSM details are the output of the tool.

Figure 7: The tool input, process and output

As we have noticed, the tool needs sufficient memory to store the information related to TIOA, Grid Automaton, NFSM and to run the tool in order to generate the test cases.

In the next sections, we explained in details the steps of our developed methodology, why we need each step, what the selected algorithms are and their time complexity.

### 3.2 TIOA Specification

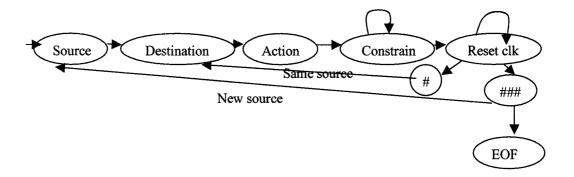

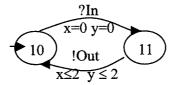

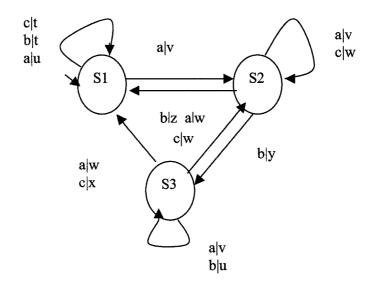

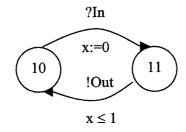

TIOA specification is a file, which needs to be parsed by the tool in order to generate its timed test suites (test cases). A set of locations, a set of inputs, a set of outputs, a set of clocks and data variables and a set of transitions define TIOA. This file must follow a specific format (Figure 8).

Figure 8: File format

The tester starts describing TIOA by going to each location and writes its name (source name), its destination, its action, its constraints and its reset clocks information. One location may have more than one transition, and the tester has to put "#" sign, which indicates that the next transition is following. After specifying the information of the first location, the tester put "###" sign to start the next location in the same manner as explained before by describing the elements of its transitions. Finally, when the tester finishes all the locations, s/he writes EOF, which means the end of the file. For example, the file format of Figure 9 is:

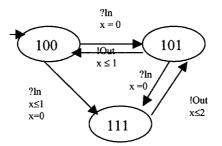

Figure 9: TIOA specification

Source: 10

Destination: 11

Action: ?ln

Constraint: null

Reset clk: x, y

####

###

Source: 11

Destination: 10

Action: !Out

Constraint:  $x \le 2$ ,  $y \le 2$

Reset clk: null

### EOF

## 3.3 Sampling the TIOA

Sampling TIOA into Grid Automaton is the first step of our developed methodology. TIOA specification is the input of this step and Grid Automaton is the output. We need such step since Grid Automaton is sub-automaton that is easily transformed into NFSM.

The Grid Automaton is to represent each clock region with a finite set of clock valuation. This finite set is called "representatives of the clock region" and it is determined from the set of the grid points with the granularity at most 1/(1+n) where n is the number of the clocks. The granularity is determined according to the number of the clocks. By this granularity, the clocks are authorized to pass from one clock region to another one, and the automaton is allowed to make a transition from one location to another [6].

### 3.3.1 Sampling Process

To construct the Grid Automaton of a TIOA, the following operations have to be proceeded [6]: first step, determine the maximal granularity we can use for a specific TIOA. If the number of the clocks is one then the granularity is ½, but if the number of the clocks is greater than one then the granularity is 1/(n+2) where n is the number of the clocks. By this granularity, the relationships between clocks are kept because every delay transition in the region graph is matched with a transition on 1/(n+2) in the Grid Automaton. Therefore, there will be no relationship between clocks when the number of clocks is one. See Figure 10 as an example of a TIOA Specification, which has one clock "x", then the granularity is ½. Second step, create the initial state of the Grid Automaton formed from the initial location of TIOA and a valuation that sets all

clocks to zero. The Initial state of TIOA specification in Figure 11 is "100", which will be the initial grid state that has the valuation of "x" to be equal to zero. Third step, Create all states reachable from the initial state with repetitive 1/ (n+2) (or ½ if number of clocks is one) delay transition. (100, 0) has a reachable state (100, ½) and the delay transition ½ (See Figure 11). Fourth step, for each state, we create all its possible transitions with a condition that for each transition in TIOA, the clock valuation satisfies the clock guard in the Grid Automaton. We noticed that (100, 0) has two transitions. One transition goes to (101, 0) and x to be reset to zero and the second transition goes to (111, 0) since the clock valuation of (100, 0), which is zero, satisfies the clock guard (zero < 1). Finally, we repeat the process starting with the next state. In our case, (101, 0), (111, 0) or  $(100, \frac{1}{2})$  is the next state. The final Grid Automaton of Figure 10 is shown in Figure 11. We noticed that the state  $(100, \infty)$  will not have an input transition that goes to (111, 0) since the bound of the time constraint is  $x \le 1$ . Besides, its delay transition has a destination (100,  $\infty$ ) where  $\infty$  means infinity. Note that the example is for understanding the concept; it may not represent the good real-time system.

Figure 10: TIOA example with one clock

Figure 11: Grid Automaton of Figure 10

# 3.3.2 Sampling Algorithm

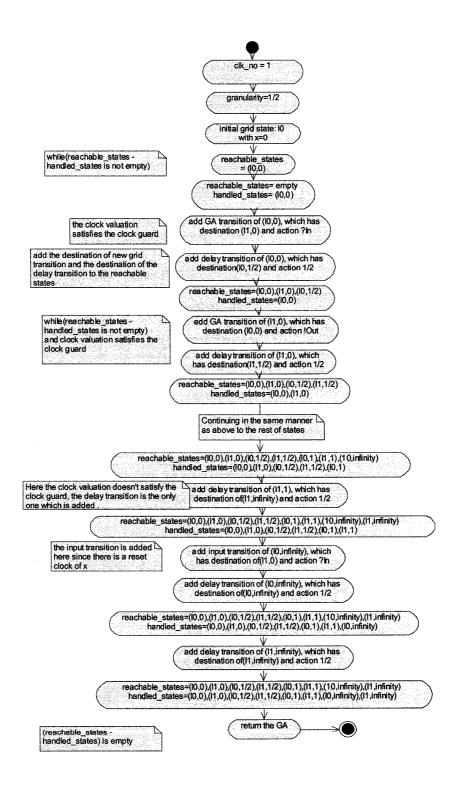

As we have explained the sampling process in the previous section, the corresponding algorithm is stated in this section. The time complexity of the sampling algorithm is: O(C+S\*t) where C is the number of clocks, S is the number of states and t is the number of transitions.

Input: TIOA\_States object

Output: Grid\_States object

**Initially:**

• reachable states and handled states are empty and their types are Grid\_States

- clk\_no is an integer variable that has the number of clocks of a TIOA

- granularity is a double variable that has the granularity of Grid Automaton

```

//find the number of the clocks of the TIOA

clk_no = find_clk_no(TIOA_States);

//compute the granularity of Grid Automaton

Granularity = compute_granularity(clk_no)

Create the initial state of Grid Automaton which has the same location as TIOA initial state

Create its Clk Vector object whose size is equal to clk_no

For each Clk object

Give the clock name //from the TIOA_States information

Give value of 0

} End For

//Add that state g_state to reachable_states

reachable_states.gstate.addElement(g_state);

While (reachable_states - handled_states is not empty)

Get a state s from (reachable states-handled states)

Add s to handled states

For (each transition belongs to TIOA transitions)

If (the clock valuation of s satisfies the clock guard || there is clock reset)

&& (the s location is equal to the source location of that TIOA transition)

Create new Grid transition which has the same information as TIOA transition

Add the transition to the Grid Automaton transitions of s without including constraints and

clock reset information

} End If

If (it doesn't exit)

Add the destination of the transition to reachable_states if it doesn't exist in it

} End If

} End For

If (the delay transition exceeds the bound of the maximum time constraint)

Create delay transition, which has destination with a clock value of infinity

If (if it doesn't exist in Grid Automaton transitions of s)

Add this delay transition of that state s to its Grid Automaton transitions

} End If

} End If

Else

Create delay transition, which has destination with a (clock value + Granularity)

If (if it doesn't exist in Grid Automaton transitions of s)

Add this delay transition of that state s to its Grid Automaton transitions

} End If

} End Else

If (destination of the delay transition is not included in reachable_state)

Add destination of the delay transition to reachable_states

} End If

} End While

Return reachable_states

END

```

Figure 12: Sampling algorithm

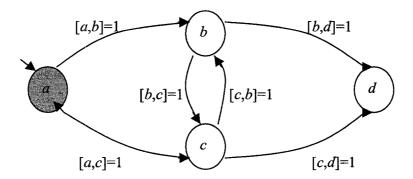

## 3.4 Transforming of Grid Automaton into NFSM

This is the second step of the developed methodology, which takes the Grid Automaton information as input and produces a NFSM as output.

## 3.4.1 Transformation Process

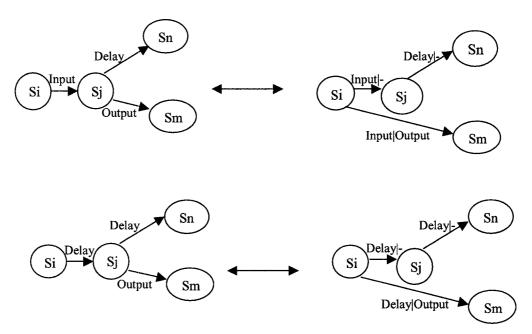

The transformation of the Grid Automaton into a NFSM is based on Figure 13 [6]:

Figure 13: NFSM transformation

The transformation can be explained easily from the above figures. It consists of combining each output with the input or each output with the delay, which is preceding it in the Grid Automaton [6]. Figure 14 shows NFSM of Figure 11. For example, in Figure 11, the Grid Automaton has (100, 0), which has the transition that is going to (111,0) with the input action ?In and (111,0) has the transition that is going to (101,0) with the output action !Out and the clock reset action. The resulted NFSM is a state (100, 0), which has ?In|!Out&Reset action to the destination (101,0). The

transitions with ?In|- action are not shown in the figure to not make it so complicated, however we have to include them in our tool. For instance, (100, 0),  $(100, \frac{1}{2})$ , (100, 1) and  $(100, \infty)$  have such transition, which is going to (101, 0).

Figure 14: NFSM of Figure 11

# 3.4.2 Transformation Algorithm

The corresponding algorithm of the transformation process is introduced in this section. The time complexity of the transformation algorithm is:  $O(S^* t^*t)$  when t>1

and t> C and it is O(S\*t\*C) when C>I and C>t, however, it is O(I\*S\*t) when I>C and

I>t where C is the number of clocks, S is the number of states, t is the number of

transitions and I is the number of input list elements.

You can see that the last part of the transformation algorithm makes NFSM to be

completely specified. To do so, we have to check each state in the produced NFSM if

it contains each input. If not, a transition with that input action is added in that state.

The transition is going to itself without any output action.

Input: Grid\_States object

Output: NFSM States object

Initially: NFSMstate is an empty vector of Location objects

35

```

BEGIN

While not the end of Grid Automaton states

Get a Grid Automaton state s

Make a new NFSM state s

While not the end of transitions of specified state s

Get a transition t

While not the end of transitions of the destination of state s

Get a tt transition

If (tt has an output action which strats with ("!") && (t has either input or delay action)

Make a new NFSM_Transition nt from s to it's transition's destination with action

Input|Output

} End If

If ( nt is not in the NFSM transitions of s)

Add it to the vector of s transitions

} End If

} End while not the end of transitions of the destination

// add the NFSM-delay transitions

Make a new NFSM-delay transition ntd from s to destination of tt with action delay|-

If ( ntd is not in the NFSM transitions of s)

Add it to the vector of transitions of s

} End If

} End while not the end of transitions of specified state s

} End while not the end of Grid Automaton states

//add reset clocks as output actions

While not the end of NFSM states

While not the end of transitions of ss

While not the end of clocks of the t destination

If (the destination has a clock c whose value is zero)

Add reset clock as output action

} End If

} End while not the end of clocks

End while not the end of transitions of ss

} End while not the end of NFSM states

//add input actions for those state, which don't have to make the NFSM more //specified

While not the end of input list

While not the end of NFSM states

While not the end of transitions of s

If (t does have an input action)

Break the loop of s transitions

} End If

If (all t's don't have i as input action) && (it is the end of s transitions)

Make new transition with the destination of s and action of i

Add this transition to s transitions

} End If

} End while not the end of transitions of s

} End while not the end of NFSM states

} End while not the end of input list

END

```

Figure 15: Transformation algorithm

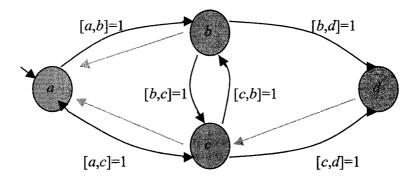

We have to point that our tool doesn't consider the transformation of NFSM to observable NSFM, however, we have to introduce the concept behind it. NFSM is observable if for every state S in NFSM, and every input|output pair a|b, there is at most one transition from S with label a|b. ONFSM's are a typical class of NFSM's where a state and an input|output pair uniquely determine the next state, while a state and an input alone don't necessarily determine a unique next state and an output. Figure 16 is an example of not being ONFSM because state S0 with pair a|0

Figure 16: Not observable NFSM

determines two states which are not unique state, however Figure 17 is ONFSM of the previous figure since state S0 uniquely determines next state. In our testing method, it is assumed that the NFSM is observable.

Figure 17: ONFSM of Figure 16

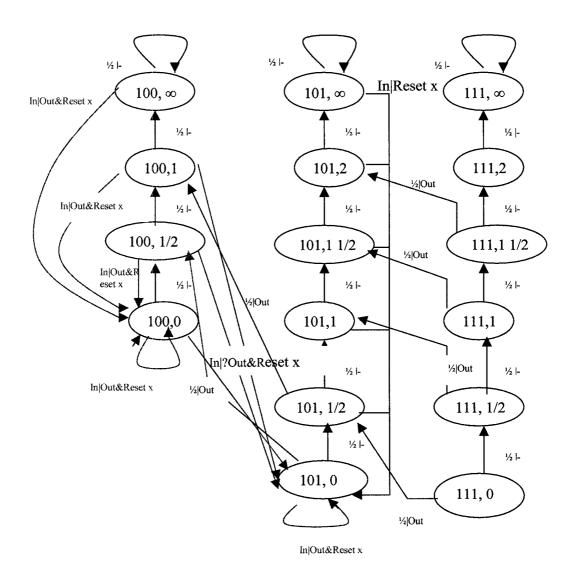

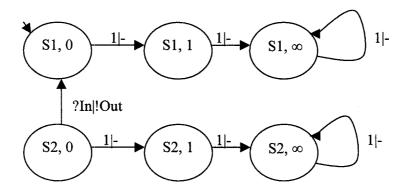

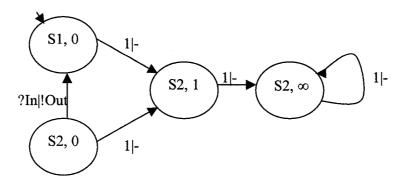

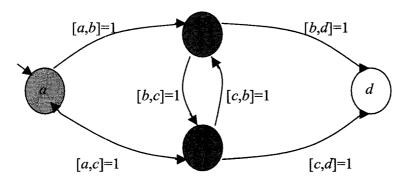

### 3.5 Minimizing the NFSM

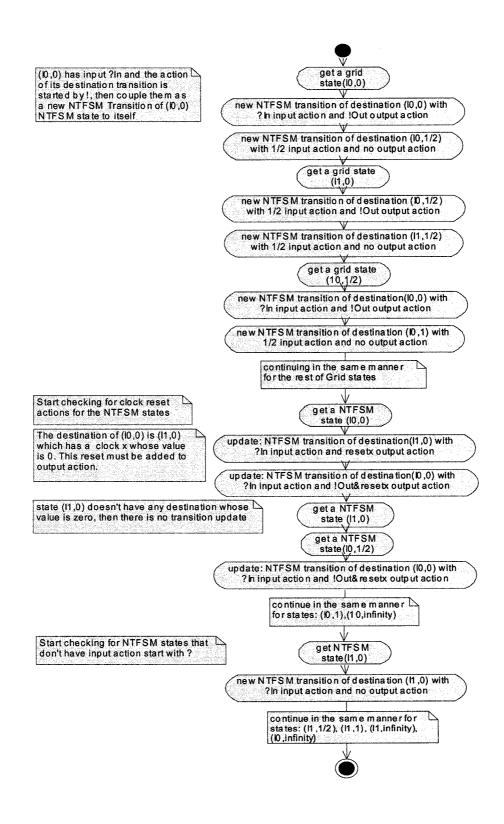

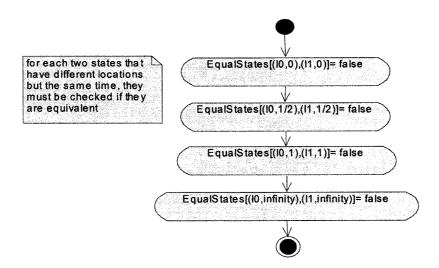

The minimization of NFSM is the third step of our developed methodology. However, this minimization [34] is slightly different from the classical minimization of FSMs because it takes into consideration the time factor. In fact, instead of checking the equivalence for each pair of states, we consider only the pairs of states that have the same clock interpretations and different locations. The input for this Minimization process is NFSM information and the output is the minimized NFSM. How the tool minimizes the given NFSM is introduced in the following sections.

### 3.5.1 Minimization Process

Based on the NFSM information as an input, the equivalent traces are checked only for the states (l, v) and (l', v) such as l is not equal to l'. For that, we get all NFSM states, and for each pair of states (l, v) and (l', v), we check with a recursive manner if they accept the same traces. If one of the two accepts a trace, which doesn't belong to the other one, both of them are judged not equal. So, they are distinguishable by, at least, an entry sequence. However, if all traces of the two states are examined and none of them can distinguish a state from another, both of them are judged as equal states. In the case of the equivalence, we remove one of the two states and its children. Obviously, all the outgoing transitions from the removed state are deleted and all the ingoing transitions are oriented to the equivalent state [34]. The equivalent states are removed to avoid having redundant information. In Figure 18, (S1, 1) and (S2, 1) are equivalent states, since they have the same transition information (1|-). The same case for  $(S1, \infty)$  and  $(S2, \infty)$ .

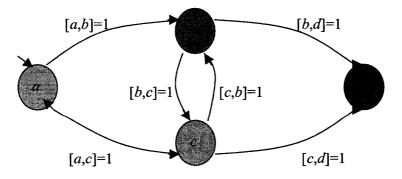

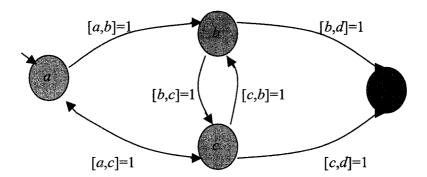

Figure 18: : Non-minimized NFSM

The Minimized NFSM of Figure 18 is represented in Figure 19. It is noticed that state(S1, 0) is not equivalent with the state (S2, 0) since (S2, 0) has a transition ?In|!Out, which (S1, 0) doesn't have.

Figure 19: The minimized NFSM of Figure 18

# 3.5.2 Minimization Algorithm

In this section, we introduce the minimization algorithm supporting of what we have explained earlier. The time complexity of the algorithm is O(S\*S\*t\*t\*t) where S is the number of states and t is the number of transitions. We have used the linear search in

this algorithm, however, searching by sort is better to be used in such context because the search is done only for the states that have the same clock values but different locations and accordingly sorting the states is based on their clock values.

**Input:** a non-minimal NFSM **Output:** a minimal NFSM

```

BEGIN

For (each state s1 of NFSM states)

For (each state s2 of NFSM states)

If ((s1.location! = s2.location) and (s1.clock = s2.clock))

If (EqualStates(s1, s2) = true)

Attach input of s2 to s1 since they are equivalent

Delete s2 state and its children

} End if

} End if

} End for

} End for

END

// EqualStates(s1, s2) function

Function EqualStates(s1, s2) returns Boolean

If (there is no transition included in s1 and s2)

Return true

} End if

For (each transition of s1)

EquiT = false

EquiS = false

Get t1 transition

For (each transition of s2)

Get t2 transition

If (t1.input = t2.input) && (t1.output = t2.output)

EquiT = True

If (s1=t1.destination) && (s2=t2.destination)

EquiS = true

} End if

Else

EquiS = EqualStates(t1.destination, t2.destination)

} End Else

} End if

} End for

If (EquiT = false) or (EquiS = false)

Return false

} End if

} End for

Return true

```

Figure 20: Minimization algorithm

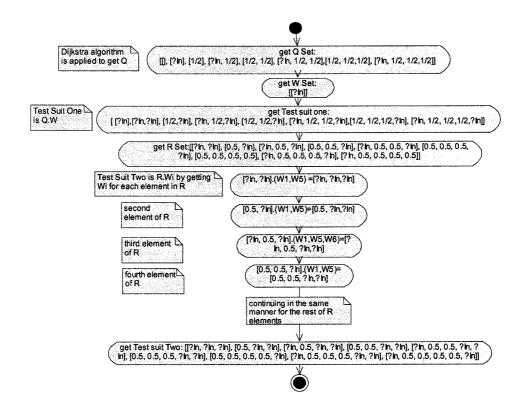

### 3.6 Generating the Test Cases

This is the fourth step of our developed methodology. Based on the minimized NFSM information as input, the generalized WP has the following five steps in order to produce the test cases as the output of the tool [6]:

- 1. Construct the state cover set (Q set). Refer to 3.6.1 section.

- 2. Construct the characterization W set and the state identification set Wi = {W0, W1... Wn-1} of S. Refer to 3.6.5 and 3.6.6 sections.

- 3. Construct the two sets P and R. Where P = Q.I, R = P/Q and I is the input list. Refer to 3.6.3 and 3.6.4 sections.

- 4. Generate the test suite one:  $\Pi 1 = Q$ . I (m-n). W. Refer to 3.6.7 section.

- 5. Generate the test suite two: Π2 = R. I (m-n) ⊕ {W0, W1... Wn-1}, where m >= n and m is the max number of states in IUT and n is the number of states in NFSM. That formula means that for each element in R set, find its corresponding reachable state from the initial state of NFSM by applying the same input sequences of R element. Then, calculate Wi for that reachable state. As a result of concatenating each element of R with its Wi, the test suite two is generated. Refer to 3.6.8 section.

- 6.  $\Pi = \Pi 1 \cup \Pi 2$ . That means the test suites is the union of the test suite one and the test suite two.

The first part checks that all the states defined by the specification are identifiable in the implementation. At the same time, the transitions leading from the initial state to these states are checked for the correct output and the state transfer. In this sense, this checking is a kind of the state verification.

The second part checks the implementation for all the transitions defined by the specification, which are not checked during the first part. It is a kind of the transition verification. Figure 21 illustrates NFSM for a system under test, which is completely specified [26].

Figure 21: NFSM under test

```

Q = \{\varepsilon, a, a.b\} \qquad P = Q.I = \{\varepsilon, a, b, c, a.a, a.b, a.c, a.b.a, a.b.b, a.b.c\}

R = P/Q = \{b, c, a.a, a.c, a.b.a, a.b.b, a.b.c\} W = \{b\}

W1 = \{b\} \qquad W2 = \{b\}

W3 = \{b\}

\Pi1 = Q.w = \{b, a.b, a.b.b\}

\Pi2 = R \oplus \{W0, ....Wn-1\} = b.W1 \cup c.W1 \cup a.a.(W1 \cup W2) \cup a.c.(W1 \cup W2) \cup a.b.a(W1 \cup W2 \cup W3) \cup a.b.b.(W1 \cup W3) \cup a.b.c.(W1 \cup W2) = \{b.b, c.b, a.a..b, a.c.b, a.b.a.b, a.b.b.a, a.b.c.a\}

\Pi = \{a.a.b, a.b.a.b, a.b.b.b, a.b.c.b, a.c.b, b.b, c.b\}

```

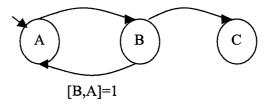

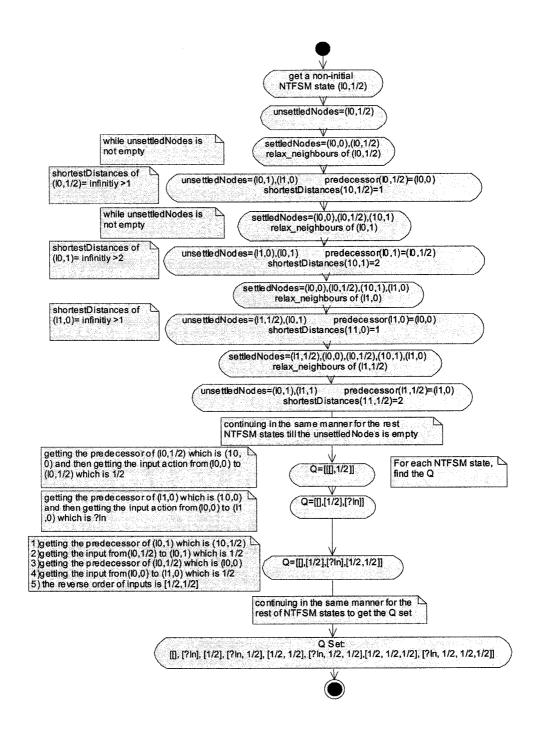

## 3.6.1 Q Process

By recalling its definition, a Q set is a state cover set of NFSM, if for every state Si; Q contains an input sequence that brings the M machine from the initial state S0 to Si. Therefore, we need a tree that is drawn from the initial state (the root of the tree) to the other states of NFSM. In other words, finding the Q is like finding the shortest distance from the initial state to the rest of NFSM states. Dijkstra's algorithm is applied to find the Q set. It finds the shortest path from a chosen source to a given

destination. To apply the algorithm on NFSM states, then we have to think of NFSM states as a graph, which has the states as vertices (or nodes) and the transitions as edges that link the states together. The transitions are directed and have an associated distance, sometimes called the weight or the cost. We have the assumption that each transition has a weight of 1. The distance between the states A and the state B is noted [A, B] and is always positive 1 [35].

Figure 22: Simple graph

Dijkstra's algorithm divides the states into two distinct sets, the set of *unsettled* states and the set of *settled* states. Initially all the states of NFSM are unsettled, and the algorithm ends once all the states are in the settled set. A state is considered settled, and moved from the unsettled set to the settled set, once its shortest distance from the initial state has been found.

With these definitions, the algorithm is the following:

- 1. Initializing the *shortestDistances* to infinity.

- 2. Initializing the predecessors and *unsettledNodes* to empty sets.

- 3. Adding the initial state of the NFSM s to unsettledNodes set.

- 4. Mapping the shortest distance of s to value of "0".

- 5. While not the end of unsettledNodes set.

- Getting the first element f of unsettledNodes set.

- Adding f to settledNodes set.

- Relaxing the neighbours of f.

How to relax its neighbours?

We go through each state "destination" adjacent to state f and see if the destination is not in the *settledNodes* and if the *shortestDistances* of "destination" is greater than the sum of the *shortestDistances* of f and f, destination (which is 1), then:

- 1. Mapping the *shortestDistances* of "destination" with value of (*shortestDistances* of "f" + 1).

- 2. Making f as a predecessor of "destination".

- 3. Adding "destination" to unsettledNodes set.

- 4. then repeating number 5.

For example, we shall run Dikjstra's shortest path algorithm on the following simple NFSM states [35] (without specifying the transitions' information and the clock values of the states), starting at the initial state a. Figure 23 shows the simple NFSM graph.

Figure 23:Dijkstra algorithm (1)

First, add the initial state a to unsettledNodes. Now unsettledNodes isn't empty, and the minimum is extracted, which is a again. a is added to settledNodes, then relaxing its neighbours. See Figure 24 to notice the relaxation of a.