# A TLM-RTL SYSTEMVERILOG-BASED Verification Framework For OCP Design

Shihua Zhang

A Thesis

In

**The Department**

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of Master of Applied Science at

**Concordia University**

Montr éal, Qu ébec, Canada

March 2011

© Shihua Zhang, 2011

#### CONCORDIA UNIVERSITY School of Graduate Studies

This is to certify that the thesis prepared

By: Shihua Zhang I.D. 6165443

Entitled: "A TLM-RTL SystemVerilog-Based Verification Framework For OCP

Design"

and submitted in partial fulfillment of the requirements for the degree of

#### **Master of Applied Science**

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|             | Dr.Dongyu Qiu               |

|-------------|-----------------------------|

|             | Dr.Amr Youssef              |

|             | Dr.Samar Abdi               |

|             | Dr.Otmane Ait Mohamed       |

| Approved by |                             |

|             | Chair of the ECE Department |

| 2011        |                             |

Dean of Engineer

#### ABSTRACT

## A TLM-RTL SystemVerilog-Based Verification Framework for OCP design Shihua Zhang

Open Core Protocol (OCP) establishes itself as the only non-proprietary, openly licensed, core-centric protocol that is used to support "plug-and-play" SoC (System-On-Chip) design practices. Designer can reuse OCP-compliance IP cores based on system integration and verification approach in multiple designs without reworking, reducing the development time and cutting down overall design costs.

In this thesis, we develop a reusable verification framework of OCP. Assertion-based verification was chosen in order to enforce the flow. An OCP SystemVerilog monitor which is developed in house is used to verify the OCP SystemC TL1 (Cycle-accurate Level) design. The monitor can also be reused for OCP designs described at different abstraction level and thus dramatically reduce the time needed for OCP functional verification. To increase the functional coverage of OCP models, Cell-based Genetic Algorithm (CGA) with random number generators based on different probability distribution functions is provided on OCP TL1 models for generating and evolving the OCP transactions. Furthermore, SystemC Verification Library (SCV) is employed as pure random number generator to compare with the proposed CGA. The experiments show that some probability distributions have more effect on the coverage than others. The best population of the CGA can be reused on OCP RTL models to reduce the verification time.

#### ACKNOWLEDGMENTS

First and foremost, I would like to send my deepest gratitude to my supervisor, Dr. Otmane Ait Mohamed, whose precious guidance, support and encouragement were pivotal in establishing my self-confidence in this endeavor.

To all my fellow researchers in the Hardware Verification Group (HVG) at Concordia University, thank you for help and encouragement. I especially appreciate Asif Iqbal Ahmed. This thesis would not have come into entirety without his constant and invaluable technical guidance. His contribution played a major role in finalizing this thesis.

Finally, I wish to express my gratitude to my family members for their love and support.

## TABLE OF CONTENTS

| LIST OF F | FIGURES                                       | vii  |

|-----------|-----------------------------------------------|------|

| LIST OF 7 | TABLES                                        | viii |

| LIST OF A | ACRONYMS                                      | ix   |

| Chapter   | 1                                             | 1    |

| Introduct | ion                                           | 1    |

| 1.1       | Motivation                                    | 1    |

| 1.2       | Functional Verification                       | 3    |

| 1.3       | Coverage Directed Test Generation             | 7    |

| 1.4       | Related Work                                  | 9    |

| 1.5       | OCP Verification Methodology                  |      |

| 1.6       | Thesis Contribution and Organization          |      |

| Chapter 2 | 2                                             | 17   |

| Prelimina | ary                                           | 17   |

| 2.1       | Open Core Protocol                            | 17   |

| 2.2       | Genetic Algorithm                             |      |

| 2.3       | SystemC Language                              | 24   |

|           | 2.3.1 SystemC Architecture                    |      |

|           | 2.3.2 Transaction Level Modeling in SystemC   |      |

|           | 2.3.3 SCV                                     |      |

| 2.4       | SystemVerilog                                 |      |

| 2.5       | Probability Distribution                      |      |

|           | 2.5.1 Uniform Distribution                    |      |

|           | 2.5.2 Normal Distribution                     |      |

|           | 2.5.3 Exponential Distribution                |      |

|           | 2.5.4 Beta Distribution                       |      |

|           | 2.5.5 Gamma Distribution                      |      |

|           | 2.5.6 Triangle Distribution                   |      |

| Chapter 2 | 3                                             |      |

| OCP Ver   | ification Methodologies                       |      |

| 3.1       | Reusable OCP TLM Verification Environment     |      |

|           | 3.1.1 OCP TL1 Channel                         |      |

|           | 3.1.2 OCP TL1 Generic Master Core             |      |

|           | 3.1.3 OCP TL1 Generic Slave Core              |      |

|           | 3.1.4 Reusable OCP Assertions                 | 41   |

|           | 3.1.5 OCP TLM-to-RTL Adapter                  | 45   |

| 3.2       | OCP Verification Framework with SCV Generator | 47   |

| 3.3       | Cell-based Genetic Algorithm on OCP           |      |

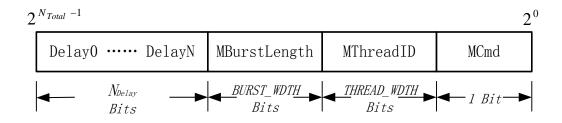

|           | 3.3.1 Solution Representation                 | 53   |

|           | 3.3.2 Random Number Generators                | 55   |

|           | 3.3.3 Initialization                          |      |

| 3.3.4 Selection and Elitism                                     | 57  |

|-----------------------------------------------------------------|-----|

| 3.3.5 Crossover                                                 | 58  |

| 3.3.6 Mutation                                                  | 59  |

| 3.3.7 Fitness Evaluation                                        | 59  |

| 3.3.8 Termination Criterion                                     | .61 |

| 3.3.9 OCP SystemC Functional Coverage Points                    | 61  |

| Chapter4                                                        | 63  |

| Implementation Result                                           | 63  |

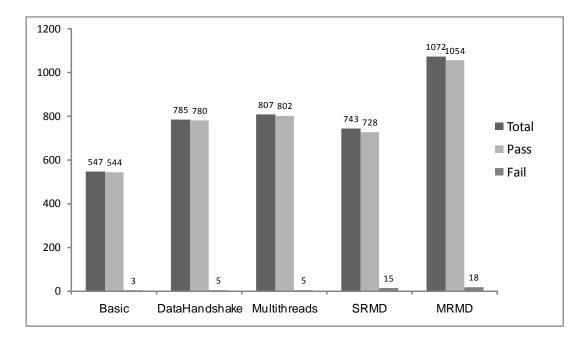

| 4.1 Directed Tests                                              | .63 |

| 4.1.1 Five OCP TL1 models                                       | .64 |

| 4.1.2 OCP TL1 generic master core and slave core configurations | 68  |

| 4.1.3 Experimental results                                      |     |

| 4.2 Random Tests                                                | 73  |

| 4.2.1 OCP Functional Coverage Points                            | .75 |

| 4.2.2 CGA Configuration                                         | .77 |

| 4.2.3 SCV representation                                        | .80 |

| 4.2.4 Experiment I                                              | .81 |

| 4.2.4 Experiment II                                             | .84 |

| 4.2.5 Experiment III                                            | 87  |

| 4.2.5 Discussion                                                | .90 |

| Chapter 5                                                       | 92  |

| Conclusion and Future Work                                      | 92  |

| 5.1 Conclusion                                                  | 92  |

| 5.2 Future Work                                                 | 94  |

| References                                                      | 96  |

## LIST OF FIGURES

| Figure 1.1 Design and Verification Gaps [45]                    | 2  |

|-----------------------------------------------------------------|----|

| Figure 1.2 Manual Coverage Directed Test Generation             | 8  |

| Figure 1.3 Proposed OCP Verification Methodology                | 13 |

| Figure 1.4 Design and Execution Flow of CGA                     | 14 |

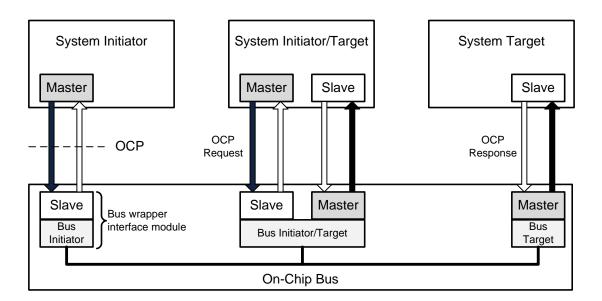

| Figure 2.1 Simple OCP System [16]                               | 18 |

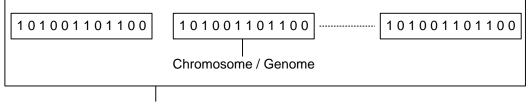

| Figure 2.2 GA Chromosome and Population                         | 21 |

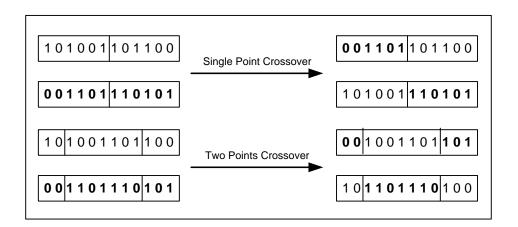

| Figure 2.3 Crossover Operators                                  | 23 |

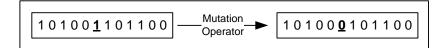

| Figure 2.4 Mutation Operator                                    | 23 |

| Figure 2.5 SystemC Architecture                                 | 25 |

| Figure 3.1 OCP Directed Verification Framework                  | 33 |

| Figure 3.2 OCP TL1 Generic Master Core                          | 36 |

| Figure 3.3 OCP TL1 Generic Slave Core                           | 40 |

| Figure 3.4 OCP TLM-to-RTL Adapter                               | 46 |

| Figure 3.5 OCP Verification Framework with SCV Random Generator | 48 |

| Figure 3.5 OCP CGA Verification Methodology                     | 49 |

| Figure 3.6 Flowchart of OCP CGA Verification Methodology        | 51 |

| Figure 3.7 Cells for Different Probability Distributions [25]   | 53 |

| Figure 3.8 CGA Random Initialization Schemes                    | 57 |

| Figure 4.1 Different OCP Configurations Assertions Hit Times    | 70 |

| Figure 4.2 Waveform of an Assertion Failure                     | 71 |

## LIST OF TABLES

| Table 3.1 OCP TL1 Generic Master Configuration Table          |    |

|---------------------------------------------------------------|----|

| Table 3.2 OCP TL1 Generic Slave Core Configuration Table      | 40 |

| Table 3.3 Pseudo-Code of OCP CGA Verification Methodology     | 52 |

| Table 4.1 Basic OCP Configuration                             | 65 |

| Table 4.2 OCP Data Handshake Configuration                    | 66 |

| Table 4.3 OCP Multi-thread Configuration                      | 66 |

| Table 4.4 OCP MRMD Configuration                              | 67 |

| Table 4.5 OCP SRMD Configuration                              | 68 |

| Table 4.6 OCP Generic Master Core Configuration               | 69 |

| Table 4.7 Pseudo-Code of getMCmdTrace Function                | 72 |

| Table 4.8 Pseudo-Code of Modified getMCmdTrace Function       | 73 |

| Table 4.9 CGA Configuration                                   | 79 |

| Table 4.10 Multiple Stage Strategy Parameters                 | 80 |

| Table 4.11 Coverage Strategy Result of Experiment I           | 82 |

| Table 4.12 Multiple Stage Strategy Result of Experiment I     | 83 |

| Table 4.13 SCV Result of Experiment I                         |    |

| Table 4.14 Coverage Strategy Result of Experiment II          |    |

| Table 4.15 Multiple Stage Strategy Result of Experiment II    |    |

| Table 4.16 SCV Result of Experiment II                        |    |

| Table 4.17 Coverage Strategy Result of Experiment Three       |    |

| Table 4.18 Multiple Stage Strategy Result of Experiment Three |    |

| Table 4.19 SCV Result of Experiment Three                     |    |

## LIST OF ACRONYMS

| AI   | Artificial Intelligence           |

|------|-----------------------------------|

| ANN  | Artificial Neural Network         |

| ABV  | Assertion-Based Verification      |

| AVE  | Advance Verification Environment  |

| BFS  | Breadth-First Search              |

| СА   | Cycle Accurate                    |

| CDF  | Cumulative Distribution Function  |

| CDG  | Coverage Directed-test Generation |

| CDV  | Coverage-Driven Verification      |

| CGA  | Cell-based Genetic Algorithm      |

| CRT  | Constraint-Random Test            |

| DFS  | Depth-First Search                |

| DUV  | Design Under Verification         |

| EA   | Evolutionary Algorithm            |

| GA   | Genetic Algorithm                 |

| IP   | Intellectual Property             |

| MDV  | Metric-Driven Verification        |

| MRMD | Multiple Request Multiple Data    |

| МТ   | Mersenne Twister                  |

| OCP  | Open Core Protocol                 |

|------|------------------------------------|

| OSCI | Open SystemC Initiative            |

| OVA  | OpenVera Assertion                 |

| PDF  | Probability Distribution Function  |

| PDG  | Priority Directed test Generation  |

| PRNG | Pseudo-Random Number Generator     |

| PSL  | Property Specification Language    |

| PV   | Programmer's View                  |

| PVT  | Programmer's View plus Timing      |

| RNG  | Random Number Generator            |

| RTL  | Register Transfer Level            |

| SCV  | SystemC Verification Standard      |

| SoC  | System-on-Chip                     |

| SRMD | Single Request Multiple Data       |

| SVA  | SystemVerilog Assertion            |

| SVWG | SystemC Verification Working Group |

| TLA  | Transaction Level Assertion        |

| TLM  | Transaction Level Modeling         |

| TTM  | Time-to-Market                     |

### **Chapter 1**

### Introduction

#### 1.1 Motivation

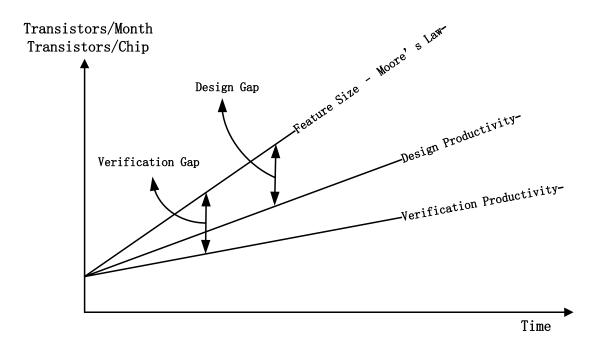

During the last decades, the semiconductor industry has grown rapidly and constantly. The silicon revolution has made ubiquitous electronics devices, such as computers, cell phones, wireless networks, and portable MP3 players, in a constant state of evolution. Providing more features in an electronics device need to add more logic gates in a single chip. Moore's law predicts that the number of transistors on a chip will double about every two years [17]. With the advent of high technology applications, System-on-Chip (SoC) technology has been widely applied in recent years. A SoC may contain on-chip memory, microprocessor, peripheral interface, I/O logic control and so on. The major impediment to developing a new chip is no longer the hardware design phase itself, but the verification of it [13]. It was noticed that verification takes around 60% to 80% of chip development effort in terms of time. Figure 1.1 shows the design and verification gaps.

Thousands of Intellectual Property (IP) cores and hundreds of hardware interconnects or buses have been involved SoC design. Tens even hundreds of IP cores can be integrated into a chip to provide various functions. For different SoC designs, IP cores have to be readapted to different interconnects. This makes SoC design an overwhelmingly complex amount of adaptation work. But the short Time-to-Market (TTM) cycle of electronic devices does not allow long schedule for SoC design. To satisfy the above requirement, OCP-IP association presents Open Core Protocol (OCP) [1] as a complete socket standard to enable true core plug-and-play and reuse. Using OCP, core designers can concentrate on core functionality and system integrators can concentrate on SoC timing, system bandwidth and latency requirement. Design time, design risk and manufacturing costs are reduced.

Figure 1.1 Design and Verification Gaps [45]

The high flexibility and configurability of OCP makes the IP core and system interconnection reusable. But the real challenge is to perform functional validation of an OCP model. Because of the wide usage of the OCP in SoC design, the reusable verification framework is necessary to be developed for reducing the verification efforts and shortening TTM. Since OCP is a core-specific, peer-to-peer protocol, OCP compliance IP cores can be verified independently with a universal OCP monitor with OCP compliance assertions attached to OCP interface. Additionally, OCP monitor should include OCP functional coverage points to measure verification progress. An OCP random generator is also needed for OCP verification. The generator should also be configurable to generate specific stimuli according to the configuration of the OCP model. In fact, to develop a reusable OCP verification framework, we have to integrate all possible aspects of features of the OCP protocol. The OCP model and all parts of the verification framework constraints by the OCP configuration.

#### **1.2 Functional Verification**

Functional verification is a process that ensures the implemented hardware design matches the intent of its specification prior to sending the device for manufacturing [39]. The implemented design refers to Design Under Verification (DUV). This is a complex task that spends the majority of time and effort in most large electronic system designs. Not only main features of DUV, but also functions in uncommon combinations of parameters ("corner cases") should be verified. Either directed test scheme or random test scheme can be utilized in functional verification.

There are several functional verification techniques divide into formal verification and simulation-based verification.

Formal verification is the use of mathematical techniques to prove or disprove the correctness of designs. Formal verification can be applied at different levels designs, ranging from gate-level to Register Transfer Level (RTL). Main techniques of the formal verification method are Equivalence Checking, Model Checking and Theorem Proving [2]. Equivalence checking is a formal, static verification technology which uses mathematical techniques to determine if two versions of the same design that are designed by different abstraction levels are functionality equivalent. The two versions could be two RTL versions, an RTL description and a gate-level netlist and two gate-level netlists. Model checking is an automatic technique for verifying finite state concurrent systems, such as digital circuits and communication protocol. The procedure uses an exhaustive search of the state space of the system to find out whether some specification is true or not. The procedure can terminate with a yes/no answer with a given sufficient resources. Although the disadvantage of model checking is the restriction on finite state systems, it is used on several important types of systems such as hardware controller and many communication protocols. Additionally, in some cases bugs can be found by restricting unbounded data structure to specific finite state instances. Model checking is preferable to deductive verification because it can be performed automatically. But some critical applications are necessary to be verified completely by theorem proving. Theorem Proving (deductive verification) refers to the use of axioms and proof rules to prove the correctness of the systems. It is a time-consuming process that can be performed only by experts who are educated in logic reasoning and have considerable experience. It can spend days or months to prove a single protocol or circuit. So theorem proving is used rarely and applied primarily to highly sensitive systems such as security protocols. Some mathematical tasks cannot be performed by an algorithm. Because there cannot be an algorithm that decides whether an arbitrary computer program terminates, correct termination of programs cannot be verified automatically in general. Therefore, most proof system cannot be completely automated. The main high order logic provers are HOL [3] and PVS [4].

Simulation-Based Verification, also called dynamic verification, is widely used in hardware verification. A testbench is built to provide meaningful scenarios to verify the logic behavior of the hardware design. A testbench can provide random, directed and constrained random stimuli over the entire input space of the DUV. A testbench is typically composed of the several types of verification components. Data Item represents the input of the DUV. Examples include bus transactions, networking packets and CPU instructions. A Driver repeatedly receives a data item and drives it to the DUV by sampling and driver the DUV signals. A Sequencer is an advanced stimulus generator that controls the data items that are provided to the driver for execution. Constraints can be added in order to control the distribution of randomized value. A Monitor is a passive entity that samples DUV signals but does not drive them. Monitors collect coverage information and perform protocol and data checking. Sequencer, driver and monitor can be reused independently. An Agent works as an abstract container to encapsulate a driver, sequencer and monitor. The Environment is the top-level component of the testbench which contains one or more agents. Some reusable frameworks for verification components, such as VMM [5], AVM [6] and OVM [7], have been provided by different EDA companies.

There are different verification methodologies including Assertion-Based Verification (ABV), Coverage-Driven Verification (CDV) and Metric-Driven Verification (MDV).

In ABV, assertions are quite simply design checks embedded in the module or IP to capture specific design intent and verify that the design correctly implements that intent either through simulation or formal verification. There are two types of assertions: *Concurrent Assertions* and *Immediate Assertions* [8]. Concurrent assertions express behavior spans over time. They are evaluated only at the occurrence of a clock tick. Concurrent assertions can be used with both formal and simulation-based verification. Immediate assertions are based on event semantics. Unlike concurrent assertions, immediate assertions are not temporal in nature and are evaluated immediately. They are used only with dynamic simulation. Assertion statements are written by HDL or special assertion languages such as SystemVerilog Assertion (SVA) [9], OpenVera Assertion (OVA) [10] and Property Specification Language (PSL) [11].

Coverage-driven verification combines automatic test generation, self-checking testbench and coverage metrics to significantly reduce the time spent verifying a design [7]. The CDV starts by setting verification goal using an organized planning process. Then a smart testbench is created to generate and send stimuli to the DUV. A monitor is connected to measure coverage process and identify undesired DUV behavior. The verification is ended when the verification goal has been achieved. Coverage metrics includes code coverage, finite state machine coverage, structural coverage and functional coverage.

Metric-Driven Verification improves coverage-driven verification approach by making the verification plan in an executable format. The executable verification plan can be used directly to generate verification scenarios, measure verification progress and identify verification closure.

#### **1.3 Coverage Directed Test Generation**

The functional specification of DUV can be translated to functional coverage tasks in SoC verification. Two steps are employed to the functional coverage process: (1) Define the cover points; (2) Finding meaningful stimuli to cover those points [12]. This process which is called Coverage Directed-test Generation (CDG) is repeated until the exit criteria (verification goals) are met.

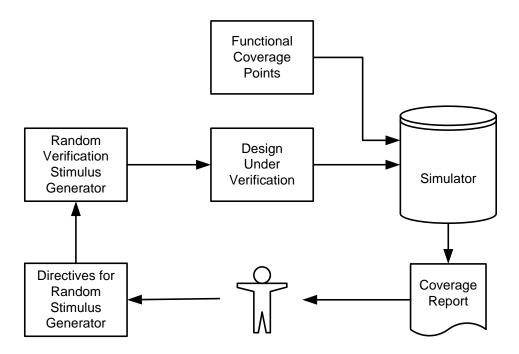

Figure 1.2 shows the manual CDG where verification engineers guide the random number generator by setting up directives and constraints. The manual effort of analyzing the coverage reports and translating them to directives for Random Number Generator (RNG) can constitute a bottleneck in the verification process. Therefore, it is worth to spend considerable effort on finding a method to automate this procedure and close the loop of coverage analysis and test generation. The automated CDG can dramatically reduce the manual effort in the verification process and increase its efficiency.

**Figure 1.2 Manual Coverage Directed Test Generation**

Artificial Intelligence (AI) techniques can be employed to automate the CDG. Several AI algorithms have been explored in the area of automatic CDG, such as Neural Network, Bayesian Network and Genetic Algorithms. Normally, random number generators, such as SCV [14] in SystemC and Randomization feature in SystemVerilog [15], use uniform probability distribution random number generator to create random stimuli to the DUV. Even though AI algorithms provide the constrained directives to RNGs, the time consumption for achieving the verification goal depends on the input of the DUV and its internal variable relationship. AI algorithms cannot reach the maximum coverage in a short time if the stimuli that achieve maximum coverage are not distributed uniformly across the input domain. Therefore, other probability distributions can be utilized by RNGs to enhance the coverage and shorten the time consumption. In this thesis, different probability distribution functions are employed to generate random numbers for AI algorithms.

#### **1.4 Related Work**

In this section, we present the related work in the area of assertion-based verification methodology for OCP TLM models. Then we give some methodologies for verifying the correctness of RTL refinement from TLM modeling. Then we will focus on functional coverage-based verification methodologies and algorithms such as Bayesian Network, Neural Network and Genetic Algorithm. Finally, we present a methodology of cell-based genetic algorithm with different probability distributions that is utilized to automate coverage directed test generation.

Many considerable efforts have been spent on OCP TLM verification in ABV. In [18], because the DUV is SystemC model, the authors developed a native assertion mechanism 'NSCa' in SystemC in order to employ their verification process. NSCa can construct a cycle level accuracy rule of the design as assertion expression form. The key variation in our approach is the formation of our assertion suite. Our scheme is based on off the shelf SVA which does not need any tailored SystemC based assertions. In addition, since SystemVerilog Assertions has a wider acceptance as an assertion language our approach stands elevated. Another work [19] focused on an assertion-based approach for system-level performance analysis applied to the single-channel OCP system. The system was described with SystemC TLM and in the analysis approach; performance primitives such as data rate and transaction latency were described using the Transaction Level Assertion (TLA). The prime difference between our research and the above mentioned research is in the method to construct of Re-Usable Assertions for design models created in various abstraction levels. Our assertion structure seamlessly integrates not only with models described at Transaction Level (TLM) but also with models written at Register Transfer Level (RTL). Therefore, our assertion suite minimizes the Design-Verification phase and enhances Time-to-Market factor.

Several attempts have been made to automate CDG. In [20], Bayesian Network is employed to model the relationship between coverage tasks space and the directives of a random test generator. This approach includes two phases: Learning phase and Evaluation phase. In the learning phase, a Bayesian network is constructed to represent the relationship between the coverage tasks and the test generation directives. Then a set of sample directives are used to run simulations and obtain a set of coverage results respectively. After that, a learning algorithm can be applied to estimate the parameters of the Bayesian network. In the evaluation phase, the trained Bayesian network can be used to generate directives for desired coverage tasks. The disadvantage of this approach is that the quality of certain sample directives has great influence on the ability of the Bayesian network to generate efficient test generation directives. In contrast, the CGA which is employed in this thesis starts with random number initiation and the quality of the initiation only affects the speed of evolution but not the quality of the generation. Artificial Neural Networks (ANNs) [44] are utilized to solve the Priority Directed test Generation (PDG) problems in the work of [21]. The DUV (OR1200 RISC CUP) was targeted by several directed test vectors.

The coverage result was represented by identified rate of predefined bugs for every test vector. Then the ANN was used to analyze the coverage results and determine the priority of each vector. Finally, the predefined test vectors with high priority can be reused for further verifications. This algorithm uses predefined test vectors with different priorities instead of random initialization in our CGA generator.

Genetic Algorithm has been employed to optimize the input test vectors in several functional verification methodologies. A simple genetic algorithm is introduced to guide random input sequences for improving coverage count of property checks in [22]. But this work can target only one property at a time. Moreover, it cannot describe sharp constrains on random inputs. In [23], a genetic algorithm is utilized to generate biased random instructions automatically for microprocessor architecture RTL model verification. The averages utilization statistics of specific buffers in PowerPC architecture are defined as coverage metrics. This approach is only for microprocessor verification. In contrast, our OCP verification framework is reusable for all OCP-compliance IP cores or bus interfaces. The work of [24] introduced genetic algorithm into a reusable verification environment. The environment adopts layered architecture and includes five layers: Signal layer, Command layer, Function layer, Scenario layer and Test layer. Only three chromosomes were initialized at the beginning of the simulation. In our framework, the initialization size of the CGA can be predefined and represent more complex solution.

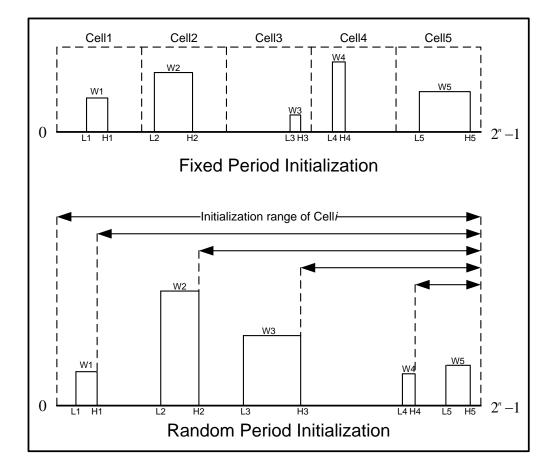

The work of [12] provided a Cell-based Genetic Algorithm (CGA) to automate

CDG. The CGA divided the input domain into sequences of inputs called *cells*. Each cell is represented by three parameters: upper limit, lower limit and weight. The number of cells and the range of the input domain are configured according to the DUV by the user. The process of the CGA begins from generating a certain number of cells randomly. Each cell targets the DUV and the coverage information of the cell is collected by the simulator. Then, the quality of each cell is evaluated by a predefined evaluation function which is called *fitness function*. Based on predefined criteria, the cells with good quality are preserved and forwarded to the next generation. The rest of the cells are modified by genetic operations for the new generation. Only uniform random generator is utilized in CGA. The work of [25] enhanced the CGA by adding several random number generators which are based on different probability distributions. The approach is applied to a SystemC 16×16 packet switch RTL model with several coverage points. The experiment results show that some RNGs based on specific probability distributions get greater fitness value within smaller number of generations than others. In this thesis, the CGA is employed to verify higher abstraction level TLM models instead of RTL models. The generation with the best coverage quality should be reused in RTL models.

#### **1.5 OCP Verification Methodology**

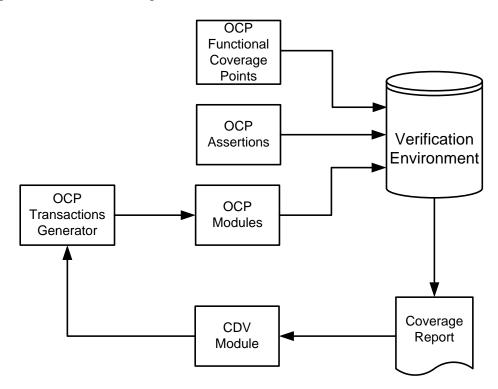

Figure 1.3 depicts our proposed OCP verification methodology. The DUV is an OCP model which normally includes different abstraction level of OCP master core,

slave core and OCP channel. Reusable OCP assertions are developed for protocol compliance checking. OCP functional coverage points are provided to measure the progress of the verification. The Advance Verification Environment (AVE) QuestaSim6.4 is selected as the simulator to provide coverage reports of OCP functional coverage points and assertions. The OCP transaction generator is used to generate OCP transaction randomly. Coverage-driven Verification (CDV) Module replaces the manual effort to analyze the coverage reports and modifying directives for OCP transaction generator for enhancing the functional coverage. In this thesis, the CGA [25] is chosen as our Coverage-driven Verification Module. In the CGA, random number generators based on six probability distributions such as Uniform, Normal (Gaussian), Exponential, Gamma, Beta and Triangle distributions are integrated into the CGA to generate OCP transactions.

Figure 1.3 Proposed OCP Verification Methodology

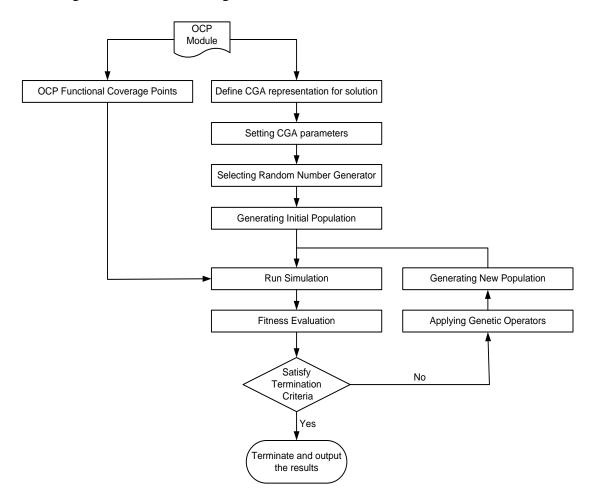

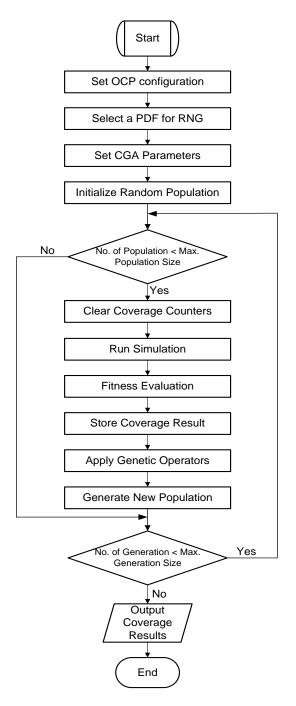

Figure 1.4 shows the design and execution flow of the CGA.

Figure 1.4 Design and Execution Flow of CGA

First of all, we define OCP functional coverage points and the representation of the specific OCP module for CGA process. Then we set the CGA parameters. After that, one kind of probability distribution with specific parameters is selected for Random Number Generator. Then an initial population is generated by the RNG based on the selected probability distribution functions. A fitness value is obtained based on OCP functional coverage points after running the simulation. Different definitions of fitness strategy can be used to evaluate how good the previous population is according to its functional coverage information. Normally, the fitness is calculated based on the percentage of the cover points being hit over the total number of coverage points in the DUV. The fitness evaluation guides the next generation of the process. Some of the elements with good quality in the population are forwarded or preserved to perform genetic operations such as crossover, mutation to the new population. The remaining part of the new population is filled by new random number generation. The whole evolution process is performed until the given termination criteria is reached.

#### **1.6 Thesis Contribution and Organization**

In light of the above related work review and discussions, we believe the contributions of this thesis are as follows:

- A set of OCP assertions in SystemVerilog Assertion (SVA) for protocol compliance checking have been defined.

- A reusable OCP verification framework for different abstraction levels (TLM and RTL) OCP models has been developed.

- A Cell-based Genetic Algorithm (CGA) using different probability distribution RNGs on different OCP TL1 channel models to enhance their functional coverage automatically has been implemented.

- A random generator has been defined in SCV and the results have been compared to the CGA approach.

The rest of the thesis is organized as following. Chapter 2 provides an introduction of Open Core Protocol. Then we present the basic principles and operators

of the genetic algorithms. We also provide overviews of SystemC and SystemVerilog language and formulas of different probability distributions. This chapter lays a foundation for the better understanding of the thesis. Chapter 3 presents our reusable OCP verification methodology. OCP TL1 channel models are selected as DUVs to be verified by directed tests and random tests. The proposed CGA based on different probability distribution RNGs is utilized to enhance the OCP functional coverage. To compare with the CGA, SCV random generators are employed to generate OCP random transactions as well. An OCP monitor with SVA assertions is attached to OCP channel for protocol checking. In Chapter 4, the implementation results of both directed tests and random tests are presented. We also describe functional coverage points which are defined in SystemC and SystemVerilog for SCV and CGA simulations respectively. After that, we discuss about the experiment results of CGA and SCV. Finally, we present our conclusion and some possible future works.

### **Chapter 2**

### Preliminary

This chapter describes briefly the preliminary components on which we are going to build our work in this thesis. They are Open Core Protocol, Genetic Algorithm, SystemC, SystemVerilog and probability distribution functions.

#### 2.1 Open Core Protocol

Open Core Protocol (OCP) [1] is a non-profit, open standard protocol that facilitates IP cores reuse and SoC integration. It defines a high performance, bus-independent interface between IP cores and it suits all hardware behaviors. Because of its high flexibility and configurability, OCP can be configured for high performance microprocessor, DMA blocks with out-of-order and outstanding transactions, simple peripheral core and on-chip communication subsystem. SoC designers can tailor the best OCP configuration socket with require features only for each IP core.

An OCP module is comprised of three parts: OCP Master Core, OCP Slave Core and OCP Channel (OCP interface). The OCP Channel is a points-to-point interface for two communication entities such as IP cores and bus interface modules. One of the entities is the OCP master core, and the other is the OCP slave core. The master core is an active device which sends requests to the OCP channel. The slave core responds to requests sent to him, either by accepting data from the master (write type commands), or presenting date to the interface (read type commands). Figure 2.1 presents a simple system consisting of a wrapped bus and three IP cores: one representing a system target, another one representing a system initiator, and an entity representing both. The characteristics of the IP core determine whether the core needs the master, the slave or both sides of the OCP. The bus interface modules must act as the complementary side of the OCP for each connected entity.

Figure 2.1 Simple OCP System [16]

The main features of OCP are summarized below:

• *Pipelining*: OCP supports pipelining of transfers. An OCP transfer consists of a complete request/response interaction. Multiple requests can be sent before the first response comes back. Requests and responses form a single

ordered thread and responses must be returned in the order of the requests.

- *Data handshake*: OCP master sends request and data separately with the data handshake signals instead of sending them together. To support data handshake feature, we can simply set OCP parameter *datahandshake* to 1.

- *Threads*: OCP interface can proceed to multiple transfers concurrently and out-of-order. OCP transfers in different threads have no ordering property and can be implemented independently in different control flows. To support multi threads feature, we set OCP parameter *threads* greater than 1.

- *Burst*: There are three kinds of burst in the OCP protocol: *MRMD* burst, *SRMD* burst and *Imprecise* burst.

- The MRMD (Multiple Request Multiple Data) burst is one kind of OCP precise burst. The length of the MRMD burst is constant. Each transfer of the burst has its own request phase.

- The SRMD (Single Request Multiple Data) burst is the other kind of precise burst. The length of the SRMD burst is constant but only one request phase presents in the first transfer of a SRMD burst.

- Imprecise burst: The length of an imprecise burst is unknown and changed. Each MBurstLength indicates the number of transfers left for the current burst.

#### 2.2 Genetic Algorithm

Genetic Algorithms (GAs) [26] are adaptive heuristic search techniques which were first invented by John Holland in the 1960s. As a particular class of evolutionary algorithm (EA), it follows Charles Darwin's principals of survival of the fittest to simulate process in nature evolution and generate high quality solutions to search and optimize problems. A genetic algorithm is an iterative procedure implemented in a computer simulation. During the simulation, a population of an abstract artificial representation is initialized and evaluated at first. Then some part of the solution with good quality will be kept and forwarded to the next population. This evolution process will run continuously until a satisfactory solution is found. Genetic algorithms cannot guarantee a unique best solution, but it finds optimal solutions more efficiently than traditional search techniques (linear programming [27], depth-first search (DFS) [28], breadth-first search (BFS) [29], etc.) in optimizing search problems with large space. Therefore, genetic algorithms have been studied, experimented and applied in many fields of science and engineering.

A typical GA needs a genetic representation and a fitness function. Genetic representation is used to represent solutions/individuals of the problems. Individuals of the problem are represented in binary arrays or other encoding methods (trees, hashes, etc.). As shown in Figure 2.2, the individual is called chromosome or genome. Potential individuals make up a population. The size of the population rests on the complexity of the search problem and the size of the search space. In generally, the size of the population is fixed, but some specific applications use dynamic population size [30]. Fitness function is provided to evaluate the optimality or satisfactoriness of an individual so that optimal individuals can be selected and used to generating a more optimal population.

Population

#### **Figure 2.2 GA Chromosome and Population**

To obtain the optimum solutions in simulation, GA provides three main genetic operators: *selection*, *crossover* and *mutation*.

Selection operator equates to survival of the fittest. During the evolution process, a proportion of individuals in the existing populations are selected for recombination. The selection methods include *Roulette Wheel* selection, *Tournament* selection, *Ranking* selection, *Top Percent* selection, *Best* selection and *Random* selection. The most popular methods are Roulette Wheel selection and Tournament selection [26].

Roulette Wheel selection is also called as *fitness proportionate* selection. In the selection, the fitness function assigns the fitness value for each individual. This fitness value is considered as the chromosome's quality and is used to decide the probability of selection with each individual. A chromosome with better quality will be more likely to be selected than the one with bad quality.

In tournament selection method, a "tournament size" of individuals is chosen from a population randomly. Then, the best one in the chosen individuals will be selected for the new offspring. It is easy to adjust the selection pressure by changing the tournament size. Weak individuals have a small chance to be selected in a large size tournament. But the problem of the tournament selection method is that the best individual may have no chance to be kept for the next generation if it is not in the tournament. *Elitism* addresses this problem by copy the best individual to the elitism set. Individuals in the elitism set are preserved for the evolution process and are never changed by genetic operators.

After applying selection operator, the selected individuals can be kept and forwarded to the next population directly or through crossover and/or mutation operators.

Crossover operator is employed between two selected individuals by exchanging parts of their genome to create new individuals. It is useful to preserve and forwards good features of exist individuals to the next generation. There are many different kinds of crossover methods, the most common types are one-point crossover and two-point crossover. Figure 2.3 illustrates them respectively. Crossover is performed with a set probability. If no crossover occurs, the selected individuals are copied to the new generation directly.

**Figure 2.3 Crossover Operators**

After selection and crossover, mutation operator is performed to change an arbitrary bit or bit-string in current individual as Figure 2.4 illustrates. The bits are chosen randomly. The purpose of mutation operator in GA is to avoid slowing evolution by preventing individuals from becoming too similar to each other.

**Figure 2.4 Mutation Operator**

Normally, a GA evolution process includes the following steps:

- Initialize a population (n) randomly

- Calculate the fitness of the population (n).

- Repeat until termination:

- Select a proportion of existing population (n) to produce the new population (n+1)

- Perform crossover and mutation operators to generate the new

population (n+1)

- $\blacksquare$  Calculate the fitness of the population (n+1)

- Terminate due to obtain a satisfactory solution or a maximum number of generations have been reached

First of all, the GA process starts by initializing a random population. Traditionally, the initial population is produced randomly, but it can be generated using some optimal algorithms that are easy to be found. After the initialization, the quality (fitness value) of the population is calculated by the fitness function. Then the population is evolved by three GA operators: *selection, crossover* and *mutation* to generate new populations repeatedly until a satisfactory solution has been obtained or the maximum number of generation have been reached.

### 2.3 SystemC Language

SystemC [31] is an open-source language based on C++. It is both a system level and hardware description language [32]. It is a hardware description language because SystemC allows register transfer level (RTL) modeling. It is a system level specification language because it supports high abstraction level (TLM or System Level) modeling. SystemC does not add new syntax to C++ programming language. Actually, SystemC is a new C++class library which provides powerful new mechanism to model system architecture with hardware timing, concurrency and reactive behavior.

#### 2.3.1 SystemC Architecture

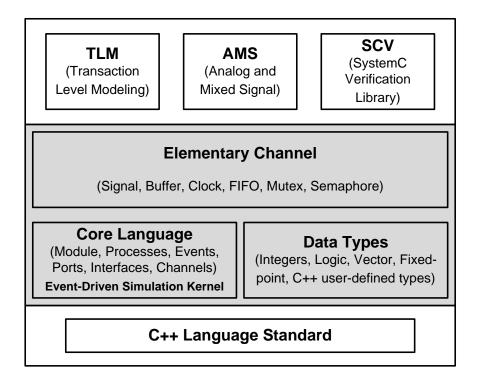

SystemC uses a layered approach that allows for the flexibility of introducing new, high-level constructors that share an efficient simulation engine [33]. The architecture of SystemC is shown in Figure 2.5.

Figure 2.5 SystemC Architecture

The bottom layer of the architecture presents that SystemC is built on standard C++ language. The second shaded gray layer is the main part of the SystemC. The *core language* includes some abstract elements and event-driven simulation kernel. *Modules* and *ports* are used to present structure information. *Interfaces* and *channels* are an abstraction for the communication. The *simulation kernel* works with *processes*

and *events* during the simulation. It does not know what the events actually represent or what the processes do. It only operates on events and switches between processes. On the right side of the core language, a set of *data types* can be used to model hardware and program software. The *elementary channel* layer is immediately above the core language. The elementary channels such as *signals*, *buffers and FIFOs* are widely used in hardware modeling. On the top of the architecture, the layers of extend design and methodology libraries are considered separate from the SystemC standard. Some of the extend libraries, such as SCV, AMS and TLM, are widely used in hardware design and verification. Over time, new libraries may be added and conceivably be incorporated into the standard language.

#### 2.3.2 Transaction Level Modeling in SystemC

Transaction Level Modeling (TLM) is a design and verification abstraction above RTL. It provides an early platform for software development so that software can be designed very early in the design flow. TLM abstracts hardware implementation details and uses function calls to model the communication between blocks in the system, and therefore it is much faster than RTL modeling. Additionally, designers can modify and replace the IP cores and buses more easily than RTL in system level design exploration and verification. TLM increases the productivity of software engineer, architects, implementation engineers and verification engineers.

Open SystemC Initiative (OSCI) released standard SystemC TLM library [35]. It provides a valuable set of templates and implementation rules for standardizing TLM methodology. In fact, transaction level does not denote a single level of description. Rather, it refers to a group of three abstraction levels. Programmer's View (PV) level is the highest level which is widely used by programmers. There is no hardware timing information in PV level. Programmer's View plus Timing (PVT) level enriches PV level with approximately timing information. It can be used for preliminary performance analysis. The lowest level is the Cycle Accurate (CA) level which adds the hardware design notion of clock and describes what happens at each clock cycle. Although CA level is cycle accurate, it is still faster RTL.

### 2.3.3 SCV

The SystemC standard can only be used to perform basic verification of a design. The SystemC Verification Working Group (SVWG) has identified the applicable verification requirements, discussed proposals from various members and provided the SystemC Verification Standard (SCV) as a set of features to be incorporated into the SystemC Standard [14]. SCV improves the capability of SystemC by adding APIs for transaction-based verification, constraint and weighted randomization, exception handling and other verification tasks. The main items within the SCV are as following:

- transaction-based verification

- data introspection

- constraint and weighted randomization

- transaction monitoring and recording

# 2.4 SystemVerilog

IEEE-1800, SystemVerilog [34] extends Verilog-2001 by adding important new features for design, synthesis and verification. The extensions include simple enhancements to existing constructs, extensions of data types and operators, a new constructs of Object-Oriented mechanism, assertion mechanism for verifying design intent and so forth.

As the integral part of SystemVerilog, SystemVerilog Assertions (SVA) is used for the temporal aspects of specification, modeling and verification. It can embed sophisticated assertions and functional checks in HDL code. It can also allow simple boolean expressions into complex definitions of design behavior.

## 2.5 Probability Distribution

In probability theory and statistics, a probability distribution describes probabilities that a random variable can take within all possible values. There are two types of probability distribution functions: continuous probability distribution functions and distribution probability distribution functions. A discrete probability distribution function gives a discrete number of values and their certain probabilities of occurrence at random events. The common discrete distributions are Binomial distribution, Geometric distribution, Logarithmic distribution and Poisson distribution [36]. Unlike discrete probability distributions, a continuous probability density function (PDF) measure the probability of an infinite number of values over continuous interval and the probability of each single value is always zero in continuous PDF. The main PDFs include Uniform distribution, Normal distribution, Beta distribution, Gamma distribution, Exponential distribution, Rice distribution, Triangular distribution, Lognormal distribution and Weibull distribution [36]. In this thesis, six continuous probability distributions are selected for generating random number in CGA, their probability density functions are presented as follows.

### 2.5.1 Uniform Distribution

Uniform distribution is defined by two parameters: a (lower limit) and b (upper limit). The probability of any value between a and b is equal. The PDF of uniform distribution of variable x is defined as:

$$f(x) = \begin{cases} \frac{1}{b-a} & \text{for } a \le x \le b \\ 0 & \text{for } x < a \text{ or } x > b \end{cases}$$

(2.1)

### **2.5.2 Normal Distribution**

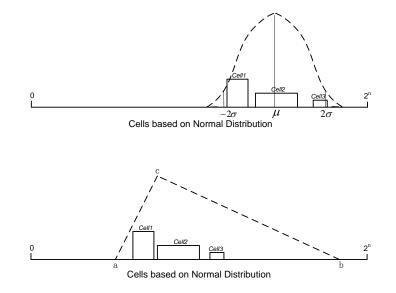

Normal distribution or Gaussian distribution is a continuous distribution that is defined by two parameters: *mean* ( $\mu$ ) and *standard deviation* ( $\sigma$ ). The PDF is defined as:

$$P(x) = \frac{1}{\sigma\sqrt{2\pi}}e^{-(x-\mu)^2/(2\sigma^2)}$$

*Where:* x = variable  $\mu = mean (average)$   $\sigma^2 = variance$

# 2.5.3 Exponential Distribution

The PDF of Exponential distribution is defined as:

$$f(x;\lambda) = \begin{cases} \lambda e^{-\lambda x}, \ x > 0 \\ 0, \ x < 0 \end{cases}$$

$$Where: \ \lambda > 0 \ and \ x \in (1,\infty) \end{cases}$$

(2.3)

# 2.5.4 Beta Distribution

Beta distribution is another continuous distribution that is defined by two parameters:  $\alpha$  and  $\beta$ . The PDF is defined as:

$$f(x; \alpha, \beta) \frac{x^{\alpha - 1} (1 - x)^{\beta - 1}}{\int_0^1 u^{\alpha - 1} (1 - u)^{\beta - 1} du} = \frac{x^{\alpha - 1} (1 - x)^{\beta - 1}}{B(\alpha, \beta)}$$

(2.4)

Where:  $0 < x < 1 \ \alpha \text{ and } \beta > 0$

# 2.5.5 Gamma Distribution

Gamma distribution is a non-symmetric continuous probability distribution that has two parameters: *scale factor*  $\theta$  and *shape factor* k. The PDF is defined as:

$$f(x; k, \theta) = x^{k-1} \frac{e^{-x/\theta}}{\theta^k \Gamma(k)}$$

(2.5)

Where: k and  $\theta > 0$

# 2.5.6 Triangle Distribution

Triangle distribution is defined by three parameters: low limit, mode, and upper limit. The PDF is given in the equation.

$$f(x; a, b, c) \begin{cases} \frac{2(x-a)}{(b-a)(c-a)} & \text{for } a \le x \le c \\ \frac{2(b-x)}{(b-a)(b-c)} & \text{for } c \le x \le b \\ 0 & \text{for any other cases} \end{cases}$$

(2.6)

# **Chapter 3**

# **OCP Verification Methodologies**

In this chapter, we provide both directed test scheme and random test scheme to verify OCP modules. In directed test scheme, a reusable OCP verification framework is developed to verify both TLM and RTL OCP models. After that, we employ SCV as a pure random number generator to generate OCP transactions to OCP TLM modules. Finally, we present the proposed methodology that utilizing Cell-based Genetic Algorithm with multiple probability distribution random number generators to generate OCP transactions and enhance the functional coverage of the OCP TLM models.

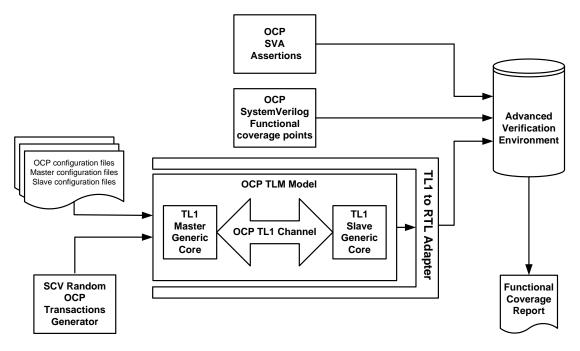

### 3.1 Reusable OCP TLM Verification Environment

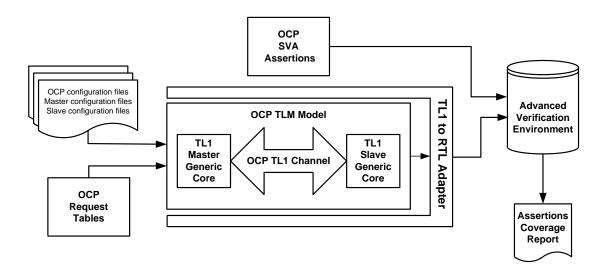

Figure 3.1 depicts the proposed verification methodology. The DUV (Design Under Verification) includes OCP generic master core, OCP generic slave core and OCP TLM (Cycle-Accurate Level) channel. The master and the slave cores are attached to one side of the OCP TL1 channel respectively. They communicate with each other by the channel. During the simulation, the master gets OCP requests from directed request tables and then sends the requests to the slave. The slave receives the requests and returns the corresponding responses to the master. An implementing adapter was developed for different abstract level modules communication. Reusable OCP SVA assertions were also developed to verify OCP protocol compliance checks in the OCP monitor. External OCP configuration files which stored in text files are used to configure both the OCP TL1 channel and the OCP monitor. Another two external configuration files are used for configuring OCP master and slave cores respectively. Using QuestaSim6.4 AVE (Advanced Verification Environment) [37] as our simulator, we can get the result of SVA assertions pass or failure from the AVE during the simulation.

**Figure 3.1 OCP Directed Verification Framework**

### 3.1.1 OCP TL1 Channel

OCP-IP [1] released OCP2.2 SystemC TLM Channels including Transaction Layer One (TL1), Transaction Layer Two (TL2) and Transaction Layer Three (TL3) [38]. The TL3 (or PV) channel is built on OSCI TLM package [35]. It is untimed and event-driven. The TL2 (or PVT) channel is designed for architecture evaluation and modeling. It is approximately-timed. The TL1 (or CA) channel is cycle-accurate but faster than RTL. Even though TL3 and TL2 channels are much more efficient than TL1, they cannot be our DUV because they hide the protocol details. To develop a reusable verification framework for both TLM and RTL modules, timing information is necessary and cannot be ignored. The TL1 channel is the transfer layer channel which is designed for simulations that are close to the hardware level. We choose the TL1 channel as our DUV because it supports all OCP transfer phases, timing and configuration parameters of OCP hardware specification. The SVA assertions that are developed for TL1 channel use to verify OCP protocol and configuration compliance can be reused for RTL OCP models.

The OCP SystemC TL1 channel uses "request/update" methods for delta cycle updates of the channel state. It implements the OCP API commands that process request, data handshake and response OCP transfers. The OCP master and slave interfaces in the TL1 channel provide port access to all OCP API commands. Moreover, the TL1 channel implements the monitor interface so that the monitor can be connected for protocol checking, performance analysis and trace dumping.

The TL1 channel is configured by a C++ STL (Standard Template Library) MAP object that contains all of the OCP parameter settings. The MAP is constructed by the key string being the name of the parameter and the value string being the value of the parameter. An example is shown below:

#### threads i:8

The left side (the key side) of the pair is the OCP parameter name. "*threads*" indicates that how many threads are in the OCP channel. The right side (the value side) are formatted as *type\_char:value*, where *type\_char* can be "i" for an integer or Boolean, "f" for a floating point value and "s" for a string. A value followed a colon (:) indicates the value of the OCP parameter. Accordingly, the example means the OCP TL1 model is configured as an eight-thread OCP channel.

During the elaboration, the OCP TL1 channel loads the OCP parameters from an external configuration file to build the configuration MAP and sends the corresponding settings to the OCP generic master core and the OCP generic slave core.

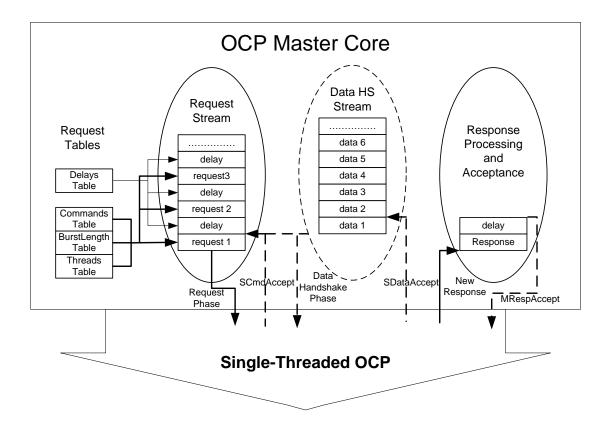

### 3.1.2 OCP TL1 Generic Master Core

An OCP TL1 generic master core is connected to one side of the OCP TL1 channel. It can generate OCP transfer requests to mimic an initiator core. The master core implements three SystemC thread processes: request thread process, optional data handshake thread process and response thread process. The request thread process handles the sending of OCP requests for the master core. The data handshake thread process handles sending the corresponding data for the master core. The response thread process handles the receiving of responses for the master core. Figure 3.2 shows a diagram of single thread OCP master core.

Figure 3.2 OCP TL1 Generic Master Core

As a directed test generator, the master core generates OCP transactions from few requests tables. The request tables contain OCP commands. The burstlength table has the lengths for each OCP transaction. The threads table indicates which thread is used for the corresponding OCP transfer request. The delays between the sending out of each request are also set in a delays table. An example of request tables is shown as follows. There are nine predefined OCP transactions in this example. For each table entry, the master sends the corresponding requests to the corresponding thread then waits the corresponding time before moving on to the next table entry. At the beginning of the simulation, the master core gets OCP commands from the first row of the command table. In this example, there are two OCP simple write commands in the first transaction. The first element in the thread table indicates that these two commands should be sent to OCP thread 0. Similarly, the first element of the burst table gives the burst length of the first transaction according to the number of the valid OCP commands in the command table. After that, the first entry of the delay table gives 100 cycles delay for the first command and 3 cycles delay for the second one. When the first transaction is finished, the master will get the next one according to the second entry of request tables. During the simulation, the master gets transactions from request tables in an infinite loop.

// OCP command table

OCPMCmdType Commands[9][4] = {

{OCP\_MCMD\_WR,OCP\_MCMD\_WR, OCP\_MCMD\_IDLE,OCP\_MCMD\_IDLE}, {OCP\_MCMD\_WR, OCP\_MCMD\_WR, OCP\_MCMD\_WR, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD,OCP\_MCMD\_IDLE,OCP\_MCMD\_IDLEOCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_N, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_IDLE, OCP\_MCMD\_IDLE}, {OCP\_MCMD\_RD, OCP\_MCMD\_RD, OCP\_MCMD\_WR, OCP\_MCMD\_IDLE}, };

37

//Thread table

unsigned int TestThread[] = {0, 1, 2, 3, 4, 5, 6, 7, 8};

//Burstlength table

*int* NumTr[] = {2, 3, 1, 3, 3, 4, 2, 3, 4};

// Delay table

int NumWait[NUM\_TESTS][4] = {

{100, 3, 0xF, 0xF},

{7, 1, 3, 0xF, 0xF},

{6, 0xF, 0xF, 0xF},

{10, 2, 1, 0xF},

{7, 1, 3, 0xF},

{6, 1, 1, 1},

{7, 2, 0xF, 0xF},

{8, 2, 1, 0xF},

{7, 2, 2, 2}

};

The master core is generic for different OCP configuration settings. Dashed parts are optional and can be enabled and disabled by OCP configuration settings. For example, if the OCP parameter "*datahandshake*" is set to 1, the master will involve the

optional data handshake thread process and send request phase and data handshake phase separately. Otherwise, it sends OCP transfer request with the data in the request thread process only.

The master core has its own parameters as well. Table 3.1 gives the parameters for the master core.

| Parameter              | Description                                                            |

|------------------------|------------------------------------------------------------------------|

| mrespaccept_delay      | The number of cycles to delay before accepting a response from the     |

|                        | slave.                                                                 |

| mrespaccept_fixeddelay | MRespAccept Delay Style. If the parameter is true (1), the master      |

|                        | always waits for "mrespaccept_delay" cycles before accepting a         |

|                        | response. If the parameter is false (0), the master waits for a random |

|                        | number of cycles before accepting the response. This random number     |

|                        | of cycles will vary uniformly from 0 to mrespaccept_delay.             |

Table 3.1 OCP TL1 Generic Master Configuration Table

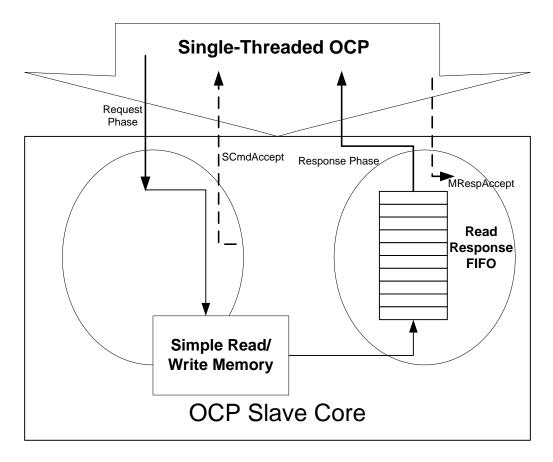

### 3.1.3 OCP TL1 Generic Slave Core

A generic OCP slave core that reacts like a target memory core is connected to the other side of the OCP TL1 channel. The slave core implements two SystemC thread processes: request thread process and response thread process. The request thread process handles the receiving of OCP requests for the slave core. The request thread also combines request and data if data handshake phase is the part of the OCP channel. The response thread process handles the sending of responses for the slave core. Figure 3.3 is a diagram of single thread OCP slave core.

Figure 3.3 OCP TL1 Generic Slave Core

Similarly to the OCP master core, the OCP generic slave core can not only deal with different OCP parameter settings, but also has its own parameters. The following table gives the parameters for the slave core.

| Parameter    | Description                                                          |

|--------------|----------------------------------------------------------------------|

| latencyX     | This is the response latency for thread number X. there is a latency |

|              | parameter for each thread in the channel. This parameter sets the    |

|              | minimum number of cycles between receiving the request and issuing   |

|              | the response.                                                        |

| limitreq_max | The outstanding requests per thread are limited to limitreq_max.     |

Table 3.2 OCP TL1 Generic Slave Core Configuration Table

### **3.1.4 Reusable OCP Assertions**

OCP-IP provides OCP2.2 compliance checks in the specification [16]. For a core to be considered OCP compliant, it must satisfy all the compliance checks. The compliance checks include protocol compliance checks and configuration compliance checks. The compliance checks includes dataflow signals checks, dataflow phase checks, dataflow burst checks, dataflow transfer checks, sideband checks and so on. SVA language is chosen to design OCP SVA assertions according to these compliance checks. All these assertions presented are embedded to a reusable OCP monitors. The monitor contains a full set of OCP parameters, all OCP signals. During the simulation, the OCP assertions can be activated or inactivated by the corresponding OCP parameters. In order to illustrate the approach to verify OCP protocol compliance, some SVA assertions are present as following.

#### Dataflow phase check 1.1.2: signal\_valid\_MCmd\_when\_reset\_inactive [16]

The signal MCmd should never have an X or Z value on the rising edge of the OCP clock.

property p\_signal\_valid\_MCmd\_when\_reset\_inactive; @(posedge ocpif.sv\_clk) disable iff (!ocpif.MReset\_n) !\$isunknown(ocpif.MCmd); endproperty

#### Dataflow phase check 1.2.3: request\_hold\_MCmd [16]

Once a request phase has begun, the signal MCmd may not change their value until the OCP Slave has accepted the request. This check is active only if the OCP parameter *cmdaccept*, *is* set to 1. The request phase begins when the master drives MCmd to a value other than Idle and ends when SCmdAccept is sampled asserted (true) by the rising edge of the OCP clock. The SVA assertion for this check shows below:

property p\_request\_hold\_MCmd;

@(posedge ocpif.sv\_clk) disable iff(!ocpif.MReset\_n//!ocpif.SReset\_n)

first\_match (ocpif.MCmd!=OCP\_MCMD\_IDLE&&

!ocpif.SCmdAccept && ocpif.ocpParams.cmdaccept)

/=>\$stable(ocpif.MCmd) throughout

(##[0:\$]\$rose(ocpif.SCmdAccept));

endproperty

#### Dataflow burst check 1.3.7: burst\_sequence\_MAddr\_INCR [16]

Within an INCR burst, the address increases for each new master request by the OCP word size. Because an INCR burst can be a precise burst or an imprecise burst. Obviously, we cannot translate this check into one SVA assertion. We have to separate the check into individual SVA assertions for all possible bursts.

There are two types of OCP precise burst, MRMD burst and SRMD burst. For SRMD burst, only the first request will be sent out, so this check makes nonsense for SRMD burst. For MRMD burst, although the burst length is constant, different MRMD bursts can have different lengths. However, SVA repetition operator must have a fixed value as the number of times the expression should match, so it's impossible to design one assertion for different MRMD bursts with different lengths. This problem was solved by defining a macro, putting the macro inside the repetition operator of the SVA assertion as a constant. Even though the assertion can only check fixed length MRMD burst in one simulation, different length bursts can be checked in different simulations by changing the macro value then rebuilding the monitor module before running another simulation. The SVA code shows below:

property p\_burst\_sequence\_MAddr\_INCR\_precise; logic[2:0] old\_cmd; @(posedge ocpif.sv\_clk) disable iff(!ocpif.MReset\_n) if(ocpif.ocpParams.burstlength&& ocpif.ocpParams.addr && ocpif.ocpParams.burstseq\_incr\_enable&& ocpif.ocpParams.burstseq) (first\_match(ocpif.MCmd!=OCP\_MCMD\_IDLE&& ocpif.MBurstLength==`BURST\_LENGTH && ocpif.MBurstSeq==OCP\_MBURSTSEQ\_INCR && ((ocpif.MBurstPrecise&&ocpif.ocpParams.burstprecise) // !ocpif.ocpParams.burstprecise)&& ((!ocpif.MBurstSingleReq&&ocpif.ocpParams.burstsinglereq) // !ocpif.ocpParams.burstsinglereq)), old\_cmd = ocpif.MCmd)

/=>(((ocpif.MAddr-\$past(ocpif.MAddr))==ocpif.ocpParams.data\_wdt

h/8) && ocpif.MCmd==old\_cmd) [->`BURST\_LENGTH-1];

endproperty

For imprecise burst, the way to decide the beginning and the end of a burst are different from precise burst. The beginning of an imprecise burst is the first request phase with MBurstLength greater than 1. The end of an imprecise burst is the request phase with MBurstLength equal to 1. So the SVA code shows below:

property p\_burst\_sequence\_MAddr\_INCR\_imprecise; logic[2:0] old\_cmd; @(posedge ocpif.sv\_clk) disable iff(!ocpif.MReset\_n) if(ocpif.ocpParams.burstprecise && ocpif.ocpParams.burstlength && ocpif.ocpParams.addr && ocpif.ocpParams.burstseq\_incr\_enable && ocpif.ocpParams.burstseq) first\_match(ocpif.MCmd!=OCP\_MCMD\_IDLE&& ocpif.MBurstLength>1 && ocpif.MBurstLength>1 && ocpif.MBurstSeq==OCP\_MBURSTSEQ\_INCR && !ocpif.MBurstPrecise), old\_cmd = ocpif.MCmd /=> ((ocpif.MAddr-\$past(ocpif.MAddr)==ocpif.ocpParams.data\_wdth/8) &&ocpif.MCmd==old\_cmd&&ocpif.MBurstLength>1)[->0:\$] ##[1:\$] (ocpif.MAddr-\$past(ocpif.MAddr)==ocpif.ocpParams.data\_wdth/8) &&

ocpif.MCmd==old\_cmd && ocpif.MBurstLength==1;

endproperty

The monitor includes not only the protocol compliance checks as above, but also the configuration compliance checks which involve enable relationships of OCP parameters. These configuration checks "param1\_enable\_param2" implies that param1 is somehow enabled by param2.

#### Request group check 2.1.7: req\_cfg\_sdata\_enable\_resp [16]

The parameter "sdata" can only be enabled if "resp" is enabled.

property P\_req\_cfg\_sdata\_enable\_resp;

*sdata*==1 /-> *resp*==1;

endproperty

The OCP reusable monitor can load OCP parameters from the configuration text files before the simulation just like the OCP TL1 channel does. All the SVA assertions are activated only when the corresponding OCP parameters are enabled.

### 3.1.5 OCP TLM-to-RTL Adapter

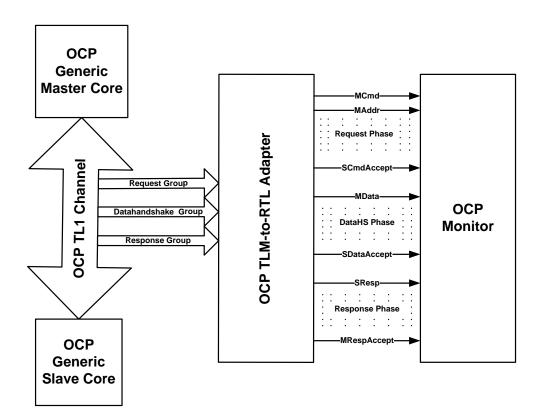

Even though OCP TL1 channel is cycle accurate, it is still high level abstract model without OCP signals in the Channel. The master and slave communicated by functional calls. On the other hand, our reusable OCP SVA assertions are developed based on OCP protocol compliance checks. All these checks are represented by OCP signals. The OCP monitor that contains the reusable SVA assertions should be pin accurate RTL models. Therefore, an OCP TLM-to-RTL implementing adapter is required to connect the cycle-accurate OCP TLM model to the pin-accurate OCP RTL monitor.

The OCP TL1 channel provides the monitor interface to access and sample the channel states. Because the OCP signals are abstracted to request group, data handshake group and response group, the TL1 monitor interface can only sample these groups. The implementing adapter divides those groups into OCP signals and sends them to the monitor by pin accurate port connections. Figure 3.4 shows the function of the implementing adapter.

Figure 3.4 OCP TLM-to-RTL Adapter

First of all, the implementing adapter samples OCP TL1 request group, OCP TL1 data handshake group and OCP TL1 response group by the positive edge of each clock cycle. Then those groups are divided into OCP signals. After that, a set of SystemC ports (*sc\_out*) for each OCP signal were defined for communication with the monitor. Finally, the powerful QuestaSim6.4 AVE was employed to connect the SystemC model (OCP TL1 channel) and the SystemVerilog model (OCP SVA monitor) because it supports mix-language design and verification simulation. Following the QuestaSim user's manual guidelines [37], the SystemC DUV can be instantiated in the SystemVerilog monitor and communication with the monitor.

### **3.2 OCP Verification Framework with SCV Generator**

The previous OCP verification framework utilized directed test scheme because the generic OCP master core gets test scenarios from request tables. As SoC designs grow larger, it becomes more difficult to generate a complete set of directed stimuli to cover their full functionality. A solution to overcome the weakness of directed test is using automatic constraint-random test (CRT). In this these, we employ SystemC verification library (SCV) as a traditional pure random number generator to produce random OCP transactions for our OCP models.

Figure 3.5 depicts the verification methodology. Instead of using directed OCP request tables, a SCV random OCP transaction generator is developed to target our OCP models. Because OCP has the high configurability and flexibility, the SCV

generator should have some configurable primitive directives to generate specific OCP transactions for each given OCP models. For instance, if the OCP channel has four-bit *thread\_wdth*, random thread numbers of OCP transactions which are generated by the SCV generator should be in the range of 0 to 15. Similar to the OCP TL1 channel, the SCV generator gets OCP configuration from the external file before the simulation. The OCP generic master core receives random OCP transactions from the SCV generator and sends them to the OCP channel.

Figure 3.5 OCP Verification Framework with SCV Random Generator

When using random test scheme, a verification coverage plan is necessary to measure and direct the verification progress. In this thesis, we develope several configurable OCP functional coverage points in our reusable monitor. These functional coverage points are developed in SystemVerilog because our verification framework is designed in SystemVerilog. The verification goal is that all functional coverage points should hit the least times. If the all coverage points reached the least times, the simulation will be terminated.

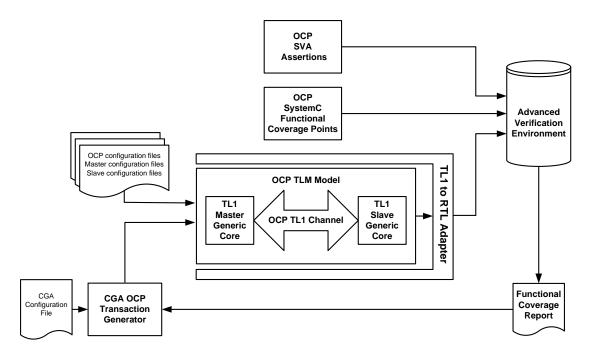

## 3.3 Cell-based Genetic Algorithm on OCP

Instead using of pure random SCV generator, Cell-based Genetic Algorithm with multiple probability distribution generators is provided as automatic CDV module to generate and evolve test vector for enhancing the functional coverage of OCP models. Figure 3.5 shows the proposed methodology.

Figure 3.5 OCP CGA Verification Methodology

First of all, one of the probability distributions and its parameters is selected to generate random numbers. In this thesis, six distributions are selected, which are Uniform distribution, Normal (Gaussian) distribution, Exponential distribution, Gamma distribution, Beta distribution and Triangle distribution. Normal, Exponential and Uniform distributions are chosen because they are well-known and have been widely employed in hardware design and verification tools. Gamma and Beta distributions are employed because the different probability curves can be easily obtained by controlling different value of their parameters. Triangle distribution is selected because it can define the range of random value according the input domain of the DUV. Then the maximum coverage rate can be achieved by adjusted one height parameter only. Additionally, Uniform distribution is also used for generate random values for the CGA to apply genetic operators. After that, OCP SystemC coverage points should be defined according to the antecedents of the OCP SVA assertions so that the OCP SystemC coverage points can reflect the coverage of the OCP SVA assertions. Finally, we repeat simulations for different probability distributions with different parameters and compare the coverage results of all the simulations for obtaining the best coverage solution.

The flowchart of the proposed CGA is presented in Figure 3.6. First, a probability distribution with its particular parameters is chosen to generate random numbers. For instance, if Exponential distribution is chosen then the value of the rate parameter  $\lambda$  is also set to predefined value. Then CGA parameters are loaded from an external file. The parameters are maximum number of generations, maximum population size, number of cells, number of OCP transactions, tournament size,

Figure 3.6 Flowchart of OCP CGA Verification Methodology

probability values for crossover, mutation and elitism, selection type, fitness definition, fitness evaluation formula and so on. After the CGA configuration, the initial population is generated by the random number generator which we selected from the first step. The process will not finish until the maximum number of generations is reached. In each generation, "maximum population size" of populations is generated for simulation. The coverage counters which count hit times of each coverage point are cleared before the simulation of each population starts. After each simulation, the coverage result is evaluated by a fitness function and stored in a text file for further analysis. Additionally, the applied genetic operators such as selection, elitism, crossover and mutation are used on the current population for evolving and producing the new one.

The pseudo-code of the CGA is present as follow:

| Pseudo-code of the OCP CGA Methodology:                                          |  |  |

|----------------------------------------------------------------------------------|--|--|

| Input : OCP Model (DUV)                                                          |  |  |

| Input : OCP configuration settings                                               |  |  |

| Input : CGA parameters                                                           |  |  |

| Input : Selected random distribution for RNG                                     |  |  |

| Output : Best fitness values with their population numbers for each generations. |  |  |

|                                                                                  |  |  |

| 1. $Population_Num = 0$                                                          |  |  |

| 2. $Generation_Num = 0$                                                          |  |  |

| 3. WHILE Generation_Num < GenerationSize DO                                      |  |  |