Parallelism in Graphics and its Representation in Data-flow Language and Architecture

Abel Ferreira

A Thesis

in

the Department

of

Computer Science

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Computer Science at Concordia University

Montréal, Québec, Canada

March 1985

c Abel Ferreira, 1985

## ABSTRACT

Parallelism in Graphics and its Repesentation in Data-flow Languages and Architectures

Abel Ferreira

This thesis is a theoretical study of parallelism in graphics and the possibility of using data-flow architecture to support this parallelism. It starts with surveys of graphic systems, data-flow architectures and languages. It demonstrates that graphic parallelism can in effect be supported by data-flow concepts. A data-flow graphic architecture is presented as a result of this integration.

# ACKNOWLEDGEMENTS

I received much help during the preparation of this thesis. I wish to thank Matrox Inc. for providing equipment and resources. To D. Lovegrove for her contribution to the illustrations of this document. To my co-workers for their encouragement and fruitful discussions about the ideas presented here. To my wife a word of appreciation for her support and patience, without which this work was not possible. My deepest recognition, however, is to professor fancott, who patiently allowed my research to proceed in new directions, but guided me with his comments. This document owes much to him.

## Contents

| 1 '                | Introduction                            | 1 .          |

|--------------------|-----------------------------------------|--------------|

| 2                  | Graphic Systems Model                   | . <b>5</b> , |

| 3-                 | Data-flow Architecture                  | 18           |

| 3.1                | Data-flow Concept                       | 19           |

| 3.2                | Data-flow Programs                      | 21           |

| 3.3                | Data-flow Computers                     | 24           |

| .,3.3.1            | M.I.T. Data-flow Computer               | 25           |

| 3.3.2              | DDM1 Utah Data-driven Machine           | 27           |

| 3.3.3              | Irvine Data-flow Machine                | 28           |

| 3.3.4              | Other Data-flow Computers               | 29<br>J      |

| 4                  | Bata-flow Programming Languages         | 34           |

| 4.1                | The VAL Programming Language            | 35           |

| 4.2                | Data-flow Machine Language              | 44           |

| 5                  | Graphic Systems and Data-flow Computers | 5 <b>2</b>   |

| 5.1                | Picture Representation                  | <b>52</b>    |

| 5.2                | Parallelism in Graphics                 | 5 <b>6</b>   |

| 5 <sup>1</sup> . 3 | Picture Description with VAL            | 64           |

| 5.4                | Data-flow Architecture for Graphics     | 75           |

\*

ļ.,

| Lordon .        | , ø .     |                                       | ;    |

|-----------------|-----------|---------------------------------------|------|

|                 | •         |                                       | 7    |

|                 | . ,       |                                       |      |

|                 |           |                                       |      |

|                 | 6         | Data-flow Graphics Computer           | 78   |

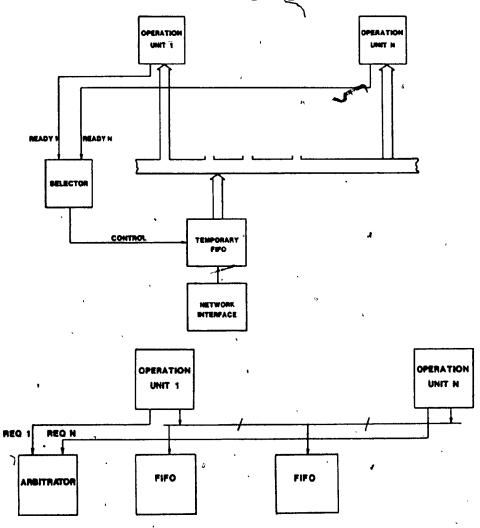

| •               | 6.1       | The Operation Units                   | 79   |

|                 | 6.1.1     | Vector Generator                      | 79   |

| , .             | 6.1.2     | Raster Operators                      | 83   |

| $\mathcal{A}$ . | 6.1.3     | Normaliser                            | 87   |

| <i>)</i> }      | 6.1.4     | Transformer                           | 91   |

|                 | 6.1.5     | Projection Units                      | 93   |

|                 | 6.1.6     | Complex Picture Generator             | 94   |

|                 | 6.1.7     | Clipper                               | 95   |

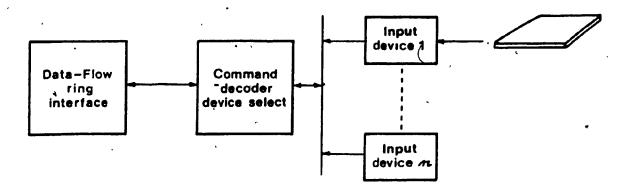

|                 | 6.1.8     | Input Devices                         | 97   |

|                 | A.1.9     | ALU                                   | 98 . |

|                 | 6.2       | Bit Map Interface                     | 100  |

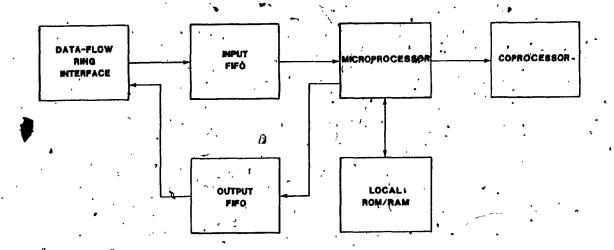

| _               | 6.3       | Data-flow Ring Interface              | 105  |

|                 | 6.4       | Data-flow Ring Architecture           | 107  |

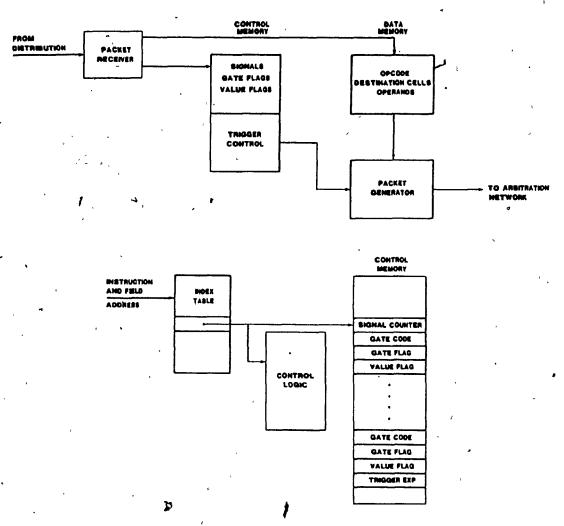

|                 | 6.4.1     | Instruction Cells                     | 107  |

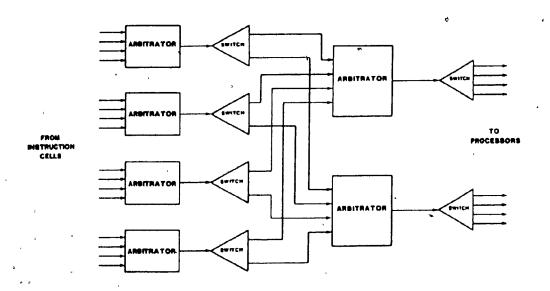

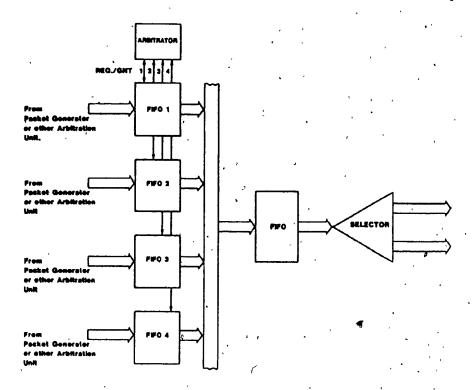

|                 | 6.4.2     | Arbitration and Distribution Networks | 110  |

|                 | 6.5       | Structure Storage and Processing      | 115  |

|                 |           |                                       |      |

|                 | 7         | Conclusion                            | 119  |

| •               |           |                                       |      |

|                 | Reference | as '                                  | 121  |

| , .             | Appendix  | I                                     | 132  |

| •               | Appendix  | II .                                  | 135  |

|                 | Appendix  | ıtı                                   | 138  |

|                 | Annendix  | TV                                    | 147  |

(,

d d

# Figures

| 2.1  | General System Model           | 7    |

|------|--------------------------------|------|

| 2.2  | General Graphic System Model   | 10   |

| 2.3  | IDS Block                      | 12   |

| 2.4  | DPU Block Diagram              | 15   |

|      | . /                            |      |

| 3.1  | (a+b)/(c+d) Graph              | 22   |

| 3.2  | Gate Operators                 | 23   |

| 3.3  | M.I.T. Data=flow Computer      | . 26 |

| 3.4  | uPD7281                        | 30   |

| 3.5. | M.I.T. with Structure Support  | ų    |

|      | •                              | •    |

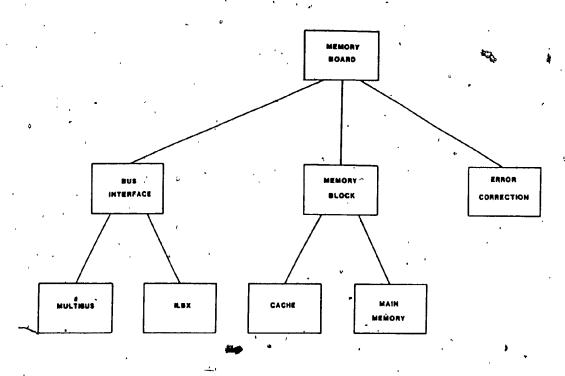

| 5.1  | Hierarchical Circuit Design    | . 58 |

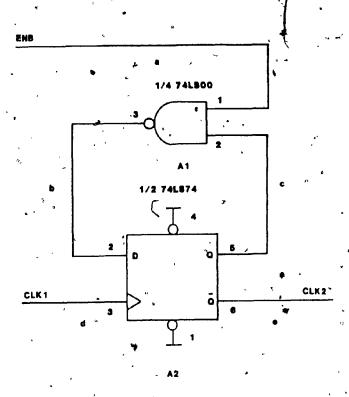

| 5.2  | Schematic Block                | 60   |

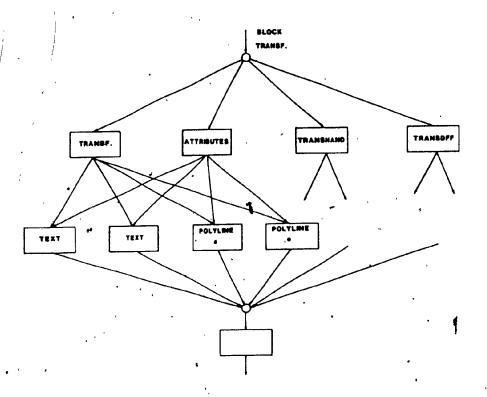

| 5.3  | Graph of Circuit Block         | 65   |

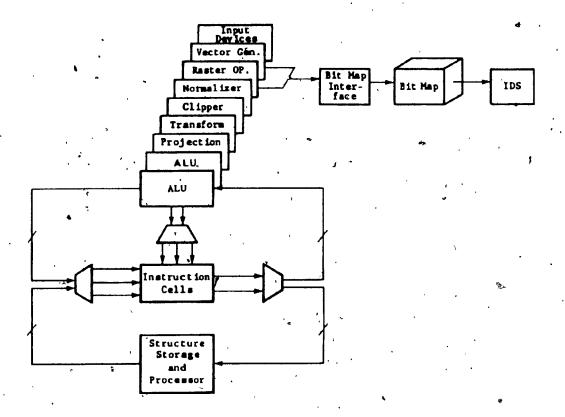

| 5.4  | Data-flow Graphics Computer    | 77   |

|      |                                | •    |

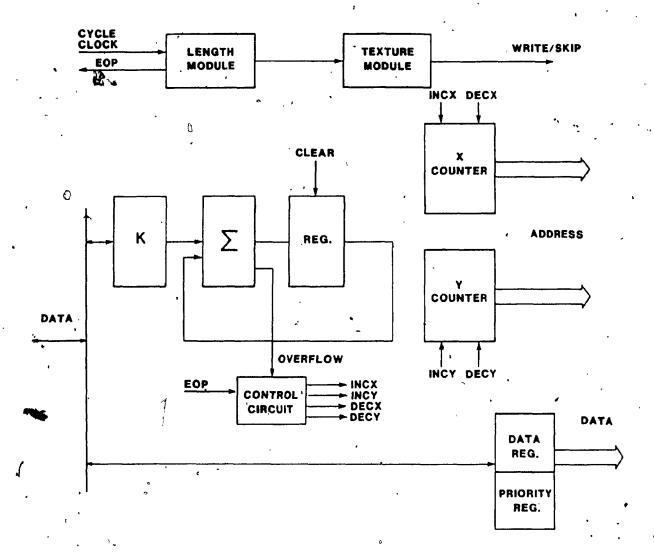

| 6.1  | Vector Generator Block Diagram | 81   |

| 6.2  | Working Areas                  | 84   |

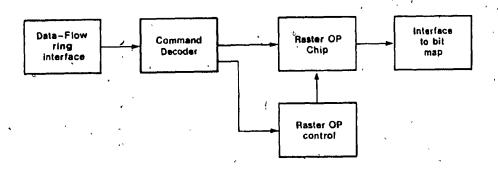

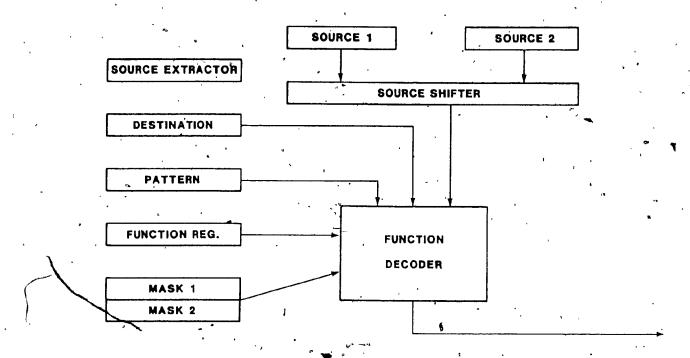

| 6.3  | Raster Operator Module         | 85   |

| 6.4  | Raster Operator Block Diagram  | 86   |

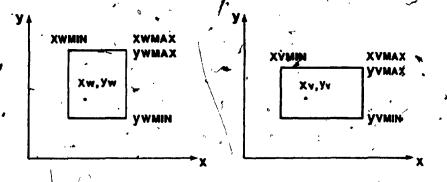

| 6.5  | Window and Viewport            | 88   |

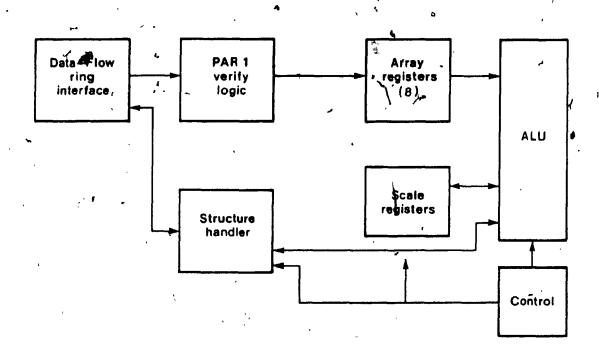

| 6.6  | Normaliser Block Diagram       | 90   |

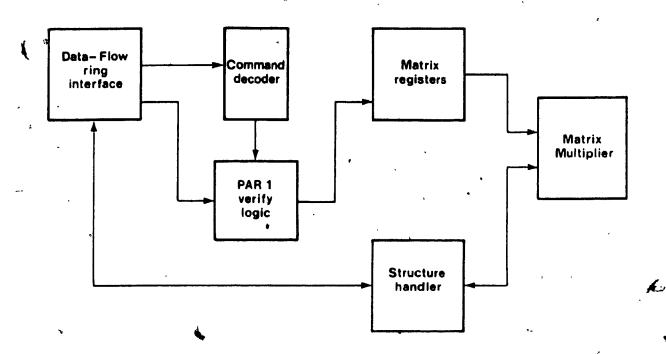

| 6.7          | Transformer Block Diagram | 92  |

|--------------|---------------------------|-----|

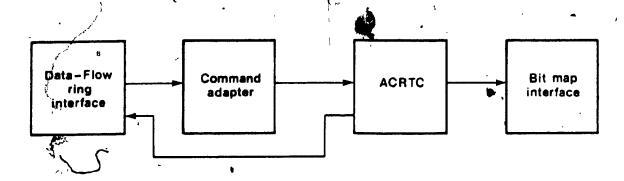

| 6.8          | ACRTC Block Diagram       | 95  |

| 6.9          | Window Clipping           | 98  |

| 6.10         | Input Module              | 98  |

| 6.11         | ALU Module                | 100 |

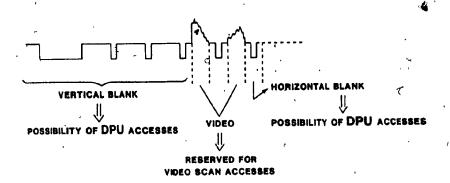

| 6.12         | Video Signal              | 101 |

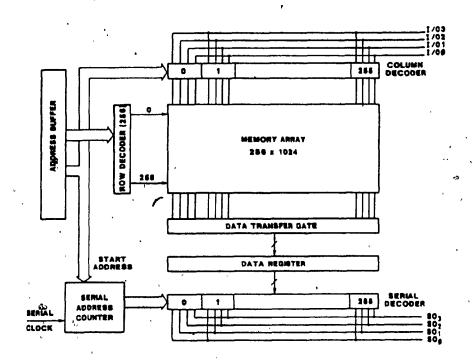

| 6.13         | Nemory Chip Block         | 102 |

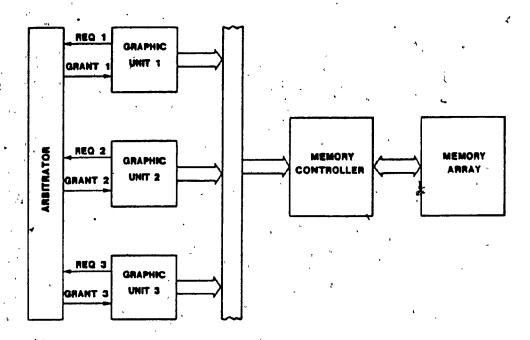

| 6.14         | Bit Map Interface         | 103 |

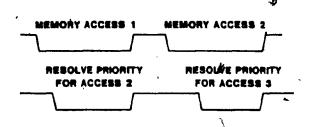

| 6.15         | Arbitration Timing        | 104 |

| <b>6</b> .16 | Data-flow Interface       | 106 |

| 8.17         | Instruction Cells Module  | 109 |

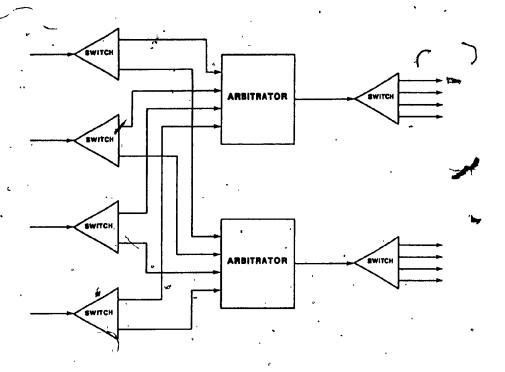

| 6.18         | Arbitration Network       | 111 |

| 6.19         | Arbitration Module        | 113 |

| 6.20         | Distribution Network .    | 115 |

## Introduction

Graphic systems are a mandatory component for almost any type of application. If for some, simple graphic routines are enough (business and education), for others a sufficiently high performance graphic system does yet not exist (CAD/CAM, image processing, mapping and animation). The search for such a machine is presently concentrated in the increase of graphics 'intelligence', i.e. the optimisation of the speed of devices and the integration of more functions in silicon. Very little has been done, however, in the study of new architectures that could explore other ways of increasing the performance of graphic systems. From our past experience we have realized that the inherent parallelism of graphics operations was not fully exploited. The search for an architecture that best supports this parallelism is the origin of this work.

On our initial literature search we realized the potential of data-flow architectures to support parallelism (their characteristics, the availability of high-level languages, the existence of several prototype machines and the announcement of a data-flow VLSI device dedicated to

image processing). Further research confirmed this possibility and defined the scope of this work: a theoretical study of graphic systems, data-flow computers, data-flow languages and the integration of the two domains in a basic data-flow architecture for graphic systems.

This document starts with a survey of raster scan displays, their evolution and characteristics. Because of the extent of the subject, the analysis was concentrated on details of current graphic architectures to investigate their limitation at handling parallelism in graphics.

Chapter three is another survey, in this case of dataflow architectures and computers. First, the concept of

data-flow is explained and compared in its performance to

handle parallelism with control-flow architectures. The

document continues with the description of data-flow graphs

and how they are used to represent data-flow programs.

Details of a small graph language are given. This chapter

finishes with the operational description of a data-flow

computer and an overview of the different types of dataflow architectures.

High-level languages for data-flow architectures is the subject of chapter four. It is a description of VAL, the the characteristics of the language, the syntax and semantics of the most representative commands, and the data types and structures. To terminate the overview of this high-level language we discuss the format of data-flow instructions and give an example of a data-flow machine language program derived from a VAL program sample.

Chapter five brings together this information in an analysis of the integration of graphics and data-flow architectures. It starts with a description of different methods of picture representation and an overview of graphic standards. Parallelism in graphics is the next topic. It is analysed from the application down to the implementation level. An example is used to show the inefficiency of expression of this parallelism in conventional languages. The same example is then described in a VAL program which is analysed in order to illustrate the support it is capable of providing for graphics parallelism. Other issues that refer to the quality of the representation are also studied. The example is also a vehicle to explain VAL instructions, how graphic functions are integrated, and the GKS language binding. Finally the chapter concludes with the presentation of a basic dataflow graphics processor based on the M.I.T. type of dataflow architecture.

The final chapter of this work is a detailed description of the basic architecture presented in the previous chapter. Each section of the computer is described, its function analysed and in most of the cases a

block diagram illustrates a possible implementation. Each operation unit is also presented with a subset of an instruction set whenever possible.

The conclusion of this document refers to areas of further research and analyses the results of this work.

## Graphic Systems Model

A

In this chapter an analysis of graphic systems is performed. Because of the considerable extent of the subject the analysis is directed towards the more recent raster scan systems.

The first part is a small historical overview of graphic systems which is followed by a list of the operations usually performed by such systems. Afterwards a description of current graphic systems at the concept level is given with examples of possible implementations. Finally we will show the limitations of these architectures and specify the aspects that can not be improved without major changes in the architecture.

Early graphic systems used display technologies other than raster scan such as storage tubes and stroke writing refresh tubes. The development of high resolution video screens and the decrease in price of solid state memories have made the raster scan display an increasingly attractive alternative to the storage tube display. The new technology brought improvements in graphic capabilities as well as new implementation problems. In the first category,

an example is selective erasing (in storage tubes the whole picture had to be erased and a new one reconstructed every time a part of the picture had to be changed), in the second the aliasing of the picture (oblique lines have a stairway aspect) and the need for solid state memories with very fast access times.

A further aspect in the evolution in graphics systems was triggered by the availability of microprocessors and cost effective dynamic rams. When solid state memory and cpu's where expensive it was the responsibility of the main and, most of the time, only CPU to execute the operating system, control the peripheral devices, perform all graphic transformations and finally convert the image expressed in vectors to a bit map representation that was sent to the screen via specialized hardware.

Cost effective RAM's made it practical to separate the main memory from the video memory (the one that contains the bit map representation of the image). Consequently the main memory was free from the raster scanner accesses that slowed down its throughput due to the frequency of the accesses. The video memory added was a dual ported memory that gave access both to the main CPU and the video scanner. With the availability of denser and less expensive RAM's the video memory was increased both in size (resolution of the screen) and in depth (number of bits per

pixel).

made it possible to use a dedicated CPU for the graphics operations. Therefore the video system was composed not only of the scanner and the video memory but also of a CPU (simple microprocessor, a bit-slice, custom designed VLSI or a pipeline of processors). The availability of this additional processing power reduced the number of tasks to be executed by the main CPU. In fact all the graphic transformations were transferred to the local CPU (the one in the video section), for example the picture bit mapping, rotations, translations, window clipping and others.

Further improvements are possible as we will show later on, but in the following we will describe and analyse the general model of a graphic system [Fole82,Free79].

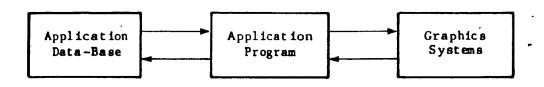

Fig. 2.1: General System Model

The application data-base provides the model and data

structures of the problem to be handled by the system. With the application program the model represented by the database can be viewed and operated by the user through the graphic system interface.

The application program has to describe to the graphic system in geometric terms that portion of the model from which the user wants a picture. In the other direction the graphic system provides geometric information to the application program as a result of user interaction. This information is interpreted by the application program in order to modify or add new elements to the data-structured model.

The form, type and amount of information passed between the graphic system and the application program is different from system to system. The analysis of this link can reveal the characteristics of the graphic system.

In earlier systems the information about the contents in the window (the part of the world or model that the user wishes to see) was provided by graphic output primitives such as points, lines, polygons or graphic strings. The coordinates of these primitives had already been transformed to the view-port (the portion of the screen where the window is to be mapped) and device coordinates.

Subsequent systems improved the set of graphic primitives with the addition of new primitives and

1,6

attributes, a more comprehensive set of input devices and pick support, more flexibility in the specification of coordinate values and the possibility to call segments of the picture definition. This last feature is equivalent to a CPU subroutine jump/return mechanism and it is a very efficient way to represent a display that has repetitive elements.

Another important advancement was made when the coordinates of the display list (the geometric information passed between the application program and the graphic system) were changed from the device space to the world or model space and support to modeling/viewing transformations was provided. Structured display file capability for traversing an object hierarchy and composing instance transformations were therefore necessary. For 3D systems perspective and projection operations were added to the set of available graphic commands.

The elements mentioned above are integrated in the following block diagram of a general graphic systems model [Fole82].

Fig. 2.2: General Graphic System Model

AM (the application model)-Contains a graphical and non-graphical description of an object in a format determined by the application program.

SDF (the structured display file)-Contains a hierarchic description of the graphical representation of the object in integer or floating point world coordinates.

BM (the bit map)-A buffer which holds the scanconverted image.

The logical processors in the system are;

DFC (the display file compiler)-The part of the application program ocontaining the model traverser and calls to the graphics package to map the AM to the SDF.

DPU (the display processing unit)-This unit maps the SDF to the BM.

IDS (image display system)-Reads the bit map and does any color table mapping before generating display monitor signals.

Since most graphic systems approach this model, it is

desirable to have a standard for the display file. Unfortunately a consensus does not yet exist among the different standards available, which makes porting application programs to different graphic systems difficult. Nevertheless there are some manufacturers that use one of the standards available (Core, GKS, GSX and others) with or without modifications. In this work we choose GKS as an example but the work is applicable to any of the other standards.

A visible characteristic of the graphic system model is the pipelining of its elements. To achieve some parallelism and increase throughput this pipelining is used in the physical implementation of the highest performance systems. There are nevertheless certain problems with this type of implementation of a graphic system. The first one is the fact that the pipeline also exists in the reverse direction using the same physical path. The second is that execution times in each element of the pipe as well as in the same element can differ for different operations. Finally, the pipeline does not work with a continuous and constant flow of load. These characteristics do not allow an efficient use of the pipe. For comparison with our architecture presented later, we provide a block diagram of the DPU and IDS of the highest performance systems available today [Door84].

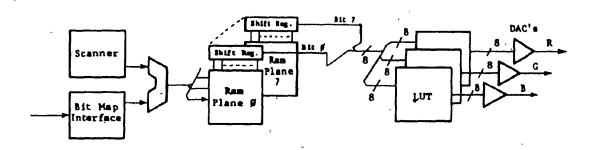

The main function of the IDS is to transfer the image represented in the bit map to the display. The simplest way to do this transfer is to organise the bit map as a one to one representation of the screen and let the IDS scan it in synchronisation with the video rate. Because the memory devices of the bit map cannot match the fast pixel rates of contemporary systems, these are normally accessed in parallel to provide more than one pixel/access. The pixel information is then serialized via shift registers. To add flexibility to the color manipulation, a look up table (LUT) is added between the shift registers and the digital to analog converters. With a LUT it is possible to have multiple planes with dynamic assignment of priority and limited animation [Levo77, Shou79].

Fig. 2.3: IBS Block Diagram

Another possibility for the IDS is to provide image transformation from the bit map to the screen. Presently

the type of transformation available is scaling and translation. With these features the bit map is normally 'bigger' than the screen and it can contain more than one image. The IDS will scan each of the images to different parts of the screen (called view-surfaces). Each one of the view-surfaces can sometimes be zoomed (by pixel replication) and pan/scrolled independently. A more difficult transformation is rotation which is not available in current systems.

The last function for the IDS is the mixing of video images. This can be done at the DAC level or at the LUT level. The last one is more powerful becaused the displays can be overlyed (mixed) in almost any possible combination depending on how the LUT is programmed.

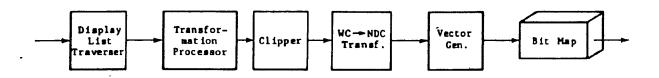

The DPU in the most complex systems has to perform the following functions:

a-Traverse a hierarchical display list that contains the graphical information about the model represented by the application data-base. This information is provided in master coordinates (the coordinates used in the definition of each object) and normally in floating point format.

b-Perform modelling and instance transformations to construct the world coordinate model.

c-Perform viewing transformations which is a world coordinate to a viewer coordinate transformation.

- d-Clip to the window limits in the viewer system.

- e-Perform projection transformations.

- f-Transform the previous result into a normalized device coordinate space by executing window to view-port transformations with hidden line elimination.

g-Translate the final graphic information into the bit map memory.

In an interactive system the DPU has to give to the application program the objects that are pointed by an input device or just a coordinate when building a new object. In the first case the DPU has to traverse the display list and find out the objects that are intersected by a small window centered around the coordinate given by the input device, after being transformed from device coordinates into world coordinates.

There are several possible implementations of machines that execute all these functions. Depending on cost, technology and other factors the implementations are following a trend where each step of the process is executed by a separate processor. This device is no longer a general purpose CPU but an operation unit dedicated to a specific function, for example, a floating point unit adapted to the graphic resolutions and to perform matrix operations. Another is a unit dedicated to do clipping and in the last stage, the most prolific one, vector

generators, pixel operators and so on. On the other end a dedicated display list traverser can substitute for the \$\forall general CPU used in the front end for the same function.

A DPU can then be represented by the following block diagram:

Fig. 2.4: DPU Block Diagram

It has been found that the graphic systems have pertinent characteristics that can be used to improve performance. One is the use of dedicated hardware for specific functions as it was shown in the previous paragraph. Another is the mapping of each step of the pipeline onto a physical component (normally a CPU or dedicated processor) of a particular implementation [Fole82, Door84].

Most of these issues are tied to the evolution of graphic systems and are therefore limited by the way this evolution took place. For example, the pipeline aspect of the graphic systems was emphasized over other aspects like the inherent parallelism of the display list interpretation and image drawing on a screen. The principal reason for this emphasis was the fact that the first system had only one CPU which had to execute all the phases of the pipeline, each one represented by a separate sub-program. When CPU's and other logic devices become available at lower cost and with more functionality the natural approach was to implement the existant sub-programs in different processors.

In this work what we are proposing to do is to look more deeply into the computer graphic process. The most striking aspect is that many operations in this process can be done in parallel, from the simple case of the vectors representing an object that can be drawn simultaneously, to the case of an hierarchical display list where each object can be transformed and drawn in parallel. Of course this is only possible if we are not restricted to a single processor. With multiprocessors the question becomes how should they be organized?

We have shown the first approach which is a pipeline of processors that achieve parallelism whenever there is a stream of data that requires a fixed sequence of graphic operations which is not always the case. Another approach is a parallel architecture. With this architecture will be

possible to support a single operation applied to multiple data which is the case, for example, of a graphics transformation applied to each object of a display list. The problems associated with this architecture are: The expression of a structured display file in a form suitable to the architecture, the support of sequential operations and the routing of the information flow between the different operation units.

A data-flow architecture is able to support both sequential and parallel operations due to the flexibility of its principle. The flow of information is inherent to the architecture and therefore directly supported by its implementation and finally there are high-level languages that can be used to express a structured display file. The characteristics of a data-flow architecture are presented in general terms in the next sections.

## Data-flow Architectures

The principles of computer architectures based on the von Neumann organization are the following:

- a) a single computing element that includes processor, memory and communications;

- b) memory organized in fixed size cells, with linear addressing;

- c) control of computation is sequential and centralized.

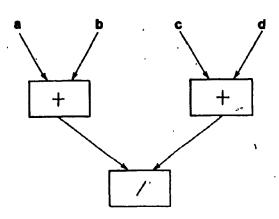

These principles are reflected in the operation of such architectures. For example the evaluation of an expression such as (a+b)/(c+d) is done by specifying to the machine a sequence of operations that are executed one after the other (Addition, Addition and Division). The operands of each one are available from a specified memory cell and the result is also stored in a memory cell. By giving to the machine the operations to be executed and the correct memory cell where the operands are stored the program is able to calculate the value of the expression. Other consequences of the von Neumann principles are the passive nature of the memory, the cells that store data or

operands are indistinguishable from the cells that store the instructions or operators and parallelism is reduced to the switching of a processor among separate processes or programmer specified decomposition of a program into parallel instruction streams to be executed by separate processors.

## 3.1 Data-flow Concept

The need to increase the throughput of computers by using the inherent parallelism of some applications has promoted the research of new architectures that have a more natural support for parallel computation. The resulting computers can be broadly classified in two fields: dataflow and demand-driven. The main characteristic of these two types of architectures is the way of controlling their operation. It is no longer a program counter that selects the next operation to be executed but the availability of all operands of an instruction in the first case and the need of a result in the second case. To clarify the two concepts let us consider the evaluation of the expression given above. In a data-flow computer the availability of the four values (a,b,c and d) will trigger the execution of the two additions. Only when the results of these are

available is the division then executed, because only at this time are the operands of this operation available. In a demand-driven computer the need of a result from the expression will trigger the execution of the division, but this one needs the results of the two additions in order to proceed. Finally these can be executed because the results they need are the values of a,b,c and d.

The possibility of executing instructions in parallel and without explicit information from the programmer is one of the main benefits of these architectures and also the main reason for extensive research in the implementation and application of the two new types of architectures.

Before making a more detailed examination of data-flow computers, we will give a brief comparison of the three architectures: control-flow or von Neumann, data-flow and demand-driven [Tre182].

With a control-flow there is a complete control over the sequence of executions but with the disadvantage of having to impose a programming discipline to avoid run-time errors (like the execution of data as a program).

A high degree of implicit parallelism resulting from the execution of instructions as soon as their operands are available is the advantage of data-driven computers. Their disadvantage is the possibility that instructions may waste time waiting for unneeded arguments like for example an ifthen-else which will only use two of its three arguments.

The advantage of demand-driven organizations is the fact that only the instructions whose result is needed are executed and the mechanism of procedure-calling is built in. On the other hand, the disadvantage of such architectures is the wasted effort of propagating demands for the evaluation of expressions such as arithmetic where every instruction always contributes to the final result.

Finally a common advantage of both data-flow and demand-driven programs is that they are free from side effects, making them suitable for distributed implementation.

#### 3.2 Data-flow Programs

In the previous paragraphs we presented the concept of data-flow with a small expression. Now we will expand the concept to more general problems and at the same time introduce the subject of data-flow languages.

The most natural way of representing a data-flow program is using a graph [Denn72]. In it, nodes represent operators and the arcs that connect these nodes represent the operands that flow from one operation to another. The expression given above can be represented by the following

graph:

Fig. 3.1: (a+b)/(c+d) Graph

The rules used to write and execute a graph are the following:

- a) In an operator node there are as many arcs, coming in as operands.

- b) The result of the operation is provided at the arc leaving the operator node.

- c) Data links are nodes that have only one incoming arc and multiple outgoing arcs.

- d) An arc is said to be active when it contains an operand or token of information.

- e) An operator node is ready for execution when all its input arcs are active and its output arc is empty.

These rules are enough to construct simple data-flow programs. In order to support more complex problems, the operator set has to be expanded with operators able to

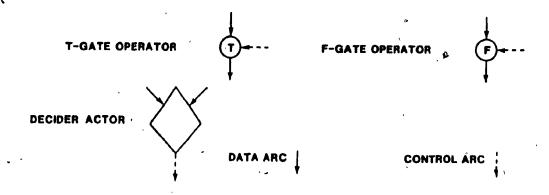

perform decisions. They are the gate operators defined below [Myer81].

Fig. 3.2: Gate Operators

With these operators we introduce another type of token: the control token as opposed to data tokens for arithmetic operators. The new operators are enabled when their data arcs follow the condition e) above and there is a token on their control arc. Their operation is the following:

- a) The decider actor provides a control token (a boolean value) depending on the result of the comparison performed on the two inputs. Examples are <, >, <=, >= or

- b) The T-gate passes the input token to its output when there is a token on the control arc with the value true. Otherwise no output is produced and both input tokens are 'consumed'.

c) The F-gate acts like the previous actor but with a false value instead.

With this language or similar ones it is possible to represent a problem in a data-flow program [Denn79,Denn80, Myer81] and have a machine that is able to execute it. The construction of such machines is the subject of the next section subject. The problem of expressing data-flow programs in a more workable language will be discussed in chapter four.

## 3.3 Data-flow Computers

Having described the characteristics of data-flow architectures and how they execute programs, we will present some of the implementations. These are the ones which have resulted from the initial research on data-flow in the Universities that are involved in this field.

The description given here is just a brief overview of the organization of those computers, how they work and what their main features are [Tre182].

# 3.3.1 M.I.T. Data-flow Computer

The research in the data-flow field done at the M.I.T. has been significant and has formed the basis for other research projects. Their computer is therefore the most representative of the machines of its type [Denn72, Denn79a].

The program organisation follows the data-flow rules expressed above, which do not allow more than one token in each arc. The architecture thus provides for acknowledge signals from the destination operators to the originators. The computer has five modules:

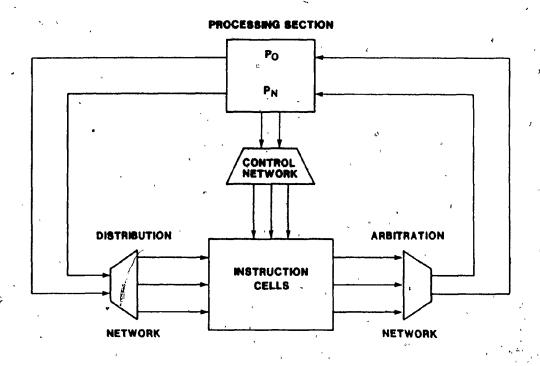

Fig. 3.3: M.I.T. Data-flow Computer

The processing section contains the operation units responsible for the execution of the instructions received from the arbitration network. This network passes information packets, containing instruction codes and operands, from the memory section to the processing section. Two types of results are available from the processing units: data tokens that are directed to the destination instruction cells via the distribution network and control tokens that are sent to the instruction cells through the control network. The first tokens contain input data for the destination cells and the second boolean

values. These only contribute to the triggering of destination instructions and are the result of boolean operators or signals used between instructions to inform of the availability of data arcs. Finally the memory section contains the instruction cells and the logic necessary to detect when an instruction is ready for execution.

#### 3.3.2 DDM1 Utah Data-driven Machine

This computer differs markedly from the previous one with its recursive architecture. It is composed of computing elements (processor memory pairs) where each element is logically recursive and contains other inferior elements. Physically the elements are organized in a tree structure with each element connected to a superior element and up to eight inferior elements [Davi78].

Other characteristics of this computer are: there are no control tokens, as the data tokens provide all communication between instructions, the arcs are viewed as first-in/first-out queues directly supported by the hardware, and finally it is able to recognize locality of reference and therefore reduce the critical problem of system wide communication. This latter aspect is considered important for distributed systems exploiting VLSI.

## 3.3.3 Irvine Data-flow Machine (Id)

This machine was intended to exploit the potential of VLSI and provide a highly concurrent program organization. The first feature of this architecture is its sophisticated token identification [Arvi77, Arvi81a]. A token identifier consists of the following information: a code block name identifying a particular procedure or Toop; a statement number within the code block; an initiation number for the loop; and a context name identifying the activity invoking this procedure or loop. The second feature is the support of data structures, such as arrays, by the inclusion of I structures [Arvi81b]. These structures are sets of components, with each component having an unique identifier and being either a value or an unknown if the component is not yet available.

The Id machine consists of N processing elements and a NxN communication network for routing the result of a processing element to the destination elements. In order to reduce the overhead in communication, the matching unit for tokens for a particular instruction is in the same processing element as is the storage of that instruction and there is a path from each processing element into itself

to route tokens that are destined to the same element that generated it [Arvi80].

# 3.3.4 Other Data-flow Computers

The previous computers are the most representative of the research being done in this field and all of them have running prototypes. There are, nevertheless, other dataflow computers such as the Manchester data-flow computer [Tre182], the Toulouse LAU system [Plas76], the Newcastle data-control flow computer [Tre178], the Texas Instrument distributed data processor [Corn79] and finally the uPD7281D (ImPP) from NEC Inc. [NECE84], the first commercially available VLSI chip supporting data-flow concepts. The architecture of this IC is a very simple data-flow ring with an addition of input and output controllers used to connect these devices in a chain for complex systems and also to interface with the other devices.

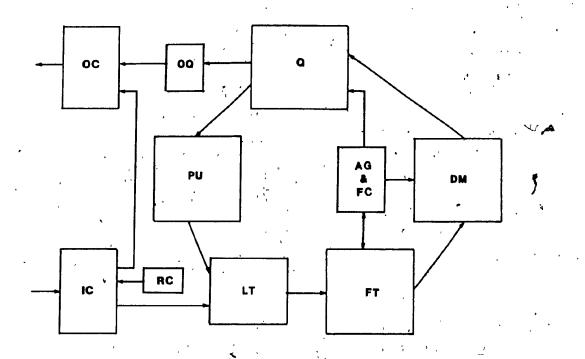

The components of this VLSI data-flow computer are shown in the /following illustration [NECE84].

Fig. 3.4: uPD7281 (ImPP) Block Diagram

IC :Input controller. Controls input data tokens and determines whether or not an input data token should be sent to the data-flow ring.

OC :Output controller. Controls output data tokens.

LT :Link table (128 words x 16 bits). Stores instruction parameters.

FT : Function table (64 words x 40 bits). Stores instruction parameters.

DM :Data memory (512 words x 18 bits). Stores constants or temporary data.

Q :Queue (48 words x 60 bits). FIFO queue. Data

queue: 32 words x 60 bits; Generator queue: 16 words x 60 bits.

PU : Processing unit. Executes logical, arithmetic and bit operations.

00 :Output queue (8 words x 32 bits). FIFO queue for the output tokens.  $\ensuremath{^{\circ}}$

AG&FC:Address generator and flow controller. Generates addresses for DM and controls the flow of tokens.

RC :Refresh controller. Generates refresh tokens for internal DRAMs.

This VLSI uses a token-based data-flow architecture. a token entered through the Input Controller (IC) is passed on to LT to be processed around the ring as many times as needed. When the processing of a token is finished, it is queued into the Output Queue (OQ) and then outputted via the Output Controller (OC). Before any processing occurs, the host processor down loads the object code into LT and FT of the ImPP by using specially formatted input tokens. At this time, constants may also be sent to DM to be stored. The contents of LT and FT are closely related to a computational data-flow graph. The arcs represent the entries in LT and the nodes represent the entries in FT, where the operation code is logged along with the identification information about the outgoing arc [NECE84].

To finalize this chapter we will introduce an addition

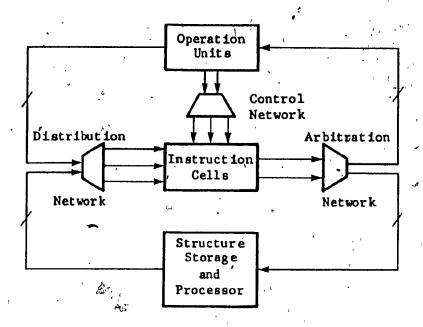

to the M.I.T. data-flow architecture to support structures [Myer81].

Fig. 3.5: M.I.T. Data-flow with Structure Support

In the architecture shown above the structure storage and processing can be considered in itself another dataflow ring with its own memory cells (holding the structures), processing units to perform operations in the structures such as create, add ..., and the distribution and arbitration networks that will route the tokens between these elements and also between this module and the distribution and arbitration networks of the computer. This

issue and the problems associated with it are analysed in chapter six that proposes a data-flow architecture for graphic systems. In the next chapter we will address the question of data-flow languages and their application to graphics.

## Data-flow Programming Languages

It is a fact that the usefulness of computers is related to the availability of high-level programming languages, and the same principle applies to data-flow computers. Since the early stages of data-flow research, therefore, equal effort has been put into the development of high-level programming languages for data-flow architectures. The intention of this work was to provide a tool to program and test the new concepts under development and verify the application of data-flow to practical problems.

Two approaches are possible: use available high-level languages and adapt them to the new concepts, or design new languages based on these concepts. The first approach has the advantage of being relatively easy to implement and can profit from a large base of application programs. The second approach lacks this advantage, but on the other hand allows the implementation of the concepts more directly and eliminates most of the problems that are present in standard high-level languages. It is in this domain where research on the new languages has concentrated [Acke79,

Back78, MacL82].

Almost all of the research groups designed their own programming language. Of these many different endeavors the programming language VAL is presently at a more advanced stage, and is used by other research groups in the analysis of language related issues.

### 4.1 The VAL Programming Language

The design goals for VAL (value-oriented algorithmic language) were: to provide implicit concurrency which is to identify concurrency in algorithms and to map as much concurrency as possible into the data-flow graphs; and to provide the constructions that enable programmers to write correct programs.

The principal feature of VAL is its value orientation reflected in the inexistence of assignment constructions, which are replaced by the concept of expressions [Denn79b, McGr82]. A program in VAL is an expression in the mathematical meaning of the word. Parallelism is implicit and is imposed by the fact that if two operations do not depend on the outcome of each other, then they can execute simultaneously. Another result of the expression orientation of the language is noninterference: once the

values of all inputs are known, execution can not influence the results of any other operations ready to execute. Therefore the features of von Neumann languages, such as the concept of modifying variables and aliasing are eliminated. The principles used in this new language have also been applied in other languages such as LISP, and therefore are not unfamiliar to computer professionals.

In the following paragraphs we provide a brief description of the language in order to support the examples given in this work. More detailed information about the language constructions is available from [Acke79a, Denn79b, McGr82].

The data types of the language are integer, real, boolean, character-string, arrays and record structures. The usual operators can be applied to the types integer, real, boolean and character-string. For arrays the following function invocations are available:

array-adjust shifts the origin

array-addh, array-addl adds elements to either end

array-remh, array-reml deletes elements at either end

array-join merges two arrays

array-seth, array-setl sets array bounds

array-limh, array-liml tests array bounds

and the infix operator || to catenate two arrays. Arrays are created in VAL with expressions that assign an index to

each element. For example,

[1:elem1;2:elem2]

is an expression that creates an array with two elements. The values bound to the two identifiers become the values for the 'corresponding array locations. In this case there is no concurrency in the construction of the array because the elements are simple values, but in most of the applications they are expressions that can be calculated in parallel. With the functions given above is then possible to add or delete elements to the array.

Record constructions are similar to the arrays in the way they are created. For example,

record[xw-min:xlow;xw-max:xmax;

yw-min:ylow;yw-max:ymax]

builds a record with four fields (xw-min, xw-max, yw-min, yw-max). Each field name is followed by an expression representing the value to be entered in the record. As with arrays the expressions on each field can be calculated simultaneously.

VAL is a value oriented language, therefore names used in the language do not refer to memory locations that can be modified as a result of assignments, but are simple binders to a value that are valid for a defined context of the program. This is commonly referred as single-assignment rule: once an identifier is bound to a value, that binding

remains in force for the entire scope of access to that identifier. This rule matches the data-flow concept represented by tokens in the arcs of a graph. Once a token is put on an arc, the same value must be transmitted to all receiving operators.

The language does not contain statements. It is completely based on expressions and functional operators. Besides the standard arithmetic expressions, and the IF-THEN-ELSE there is another basic expression particular to VAL, the LET-IN-ENDLET expression. The language through its compiler is able to recognise the implicit parallelism of such expressions. Two operations can be performed in parallel if none of them depends on the outcome of the other. The LET-IN-ENDLET expression is used to introduce names for expressions because they are common subexpressions of larger expressions. The syntax of this construction is the following:

```

LET

{ <type declaration> := <exp>; }

IN <exp>

ENDLET

```

The names in type declarations of a LET block are local names meaningful only within the block; these names

must be distinct from each other and may appear free in the expressions.

In quite a number of programs it is possible to carry operations in parallel, for example in the construction of an array. To support this type of calculation with an explicit parallelism, VAL uses the FORALL block.

<construction>::= CONSTRUCT <exp>

1

With this expression it is possible to calculate in parallel all the expressions in (1) for all values of (name) in the interval [(exp).(exp)] and produce a final value or an array. The first is obtained with the EVAL that allows the calculation of a value from the results of all elements of the interval, and the second with the construct that creates a new array and assigns to each index the result of its expression (there is a one to one correspondence between the indexes of the final array and the elements of the interval).

When it is necessary to impose a sequence in the evaluation of expressions, VAL provides a loop construction that follows the value orientation of the language. In this expression values can be transmitted from one pass through the loop to the next. This transmission can only occur by defining loop parameters and then binding new values to them just prior to the beginning of the next pass.

The loop is initialized by binding names to the values of the expressions defined between FOR and DO. These values are used in the calculation of the expressions in the DO body. Inside this block a conditional clause will decide if the loop terminates or continues. If the result arm selected by the conditional contains an expression, then the loop terminates yielding that expression as its result. Otherwise, the result arm must be an iter-block that initiates another loop pass.

Val functions are similar to functions in other languages with some exceptions: It is possible to generate more than one result from a function and in the function definition the formal parameters name and type all values to be passed on each call. The body of the function is one or more expressions which produces the result or results. These expressions can only access the formal parameters and locally defined names. Because of the single-assignment rule, the body of the function can not rebind the values bound to the formal parameters, therefore there are no side effects. Concurrency is exploited, both in the evaluation of the expressions in the body of the function and in the calculation of the formal parameters values.

These are the major constructions of VAL. A subset of

the language syntax is provided in appendix I.

The following example is a small program that uses some of the VAL constructions. The program does not produce any meaningful result. It is just an example. It takes an array multiplies each element with a scale factor and sums them. The scale factors are different for positive and negative numbers.

PROGRAM test

FUNCTION calculate (input:ARRAY[REAL] RETURNS REAL )

LET

scale1: REAL :=XWMAX-XWMIN;

scale2: REAL :=YWWAX-YWMIN

IN

FORALL I IN [1..3]

EVAL PLUS

IF input[i]<0</pre>

THEN scale1 \* input[i]

ELSE scale2 \* in [i]

ENDALL

ENDLET.

ENDFUN

calculate ([1:-1;2:3;3:-4])

END

In this program the final result is:

-scale1 + 3\*scale2 + (-4)\*scale1 where scale1=XWMAX-XWMIN and scale2=YWMAX-YWMIN (these names identify constants). The size of the array was fixed to three to reduce the complexity of the program representation in machine language, given in the next section. To make it realistic, the first statement of the FORALL expression should be:

FORALL i IN [ARRAY-LIML(input) . ARRAY-LIMH(input)]

To finalize this overview of a data-flow high-level language there are two issues that we want to refer to. The first is the handling of errors or exceptions. In VAL all the data types define error values and the corresponding operators recognize and are able to operate with such values (basically when an operator is not able to perform the task it was assigned it returns the appropriate error value. The second is the list of the language limitations. Bypassing the problems related to implementation the biggest limitations of the language are the lack of recursion, of functional operators (operations that produce functions as their result) and the omission of general input/output facilities [McGr82].

# 4.2 Data-flow Machine Language

The graph used to explain the operation of a data-flow computer is very close to what we call the machine language of a computer. Each instruction code includes a field where the destination cell addresses are stored (In conventional machines the destination field always points to a memory location where the result is stored). The other fields of the instruction are intimately related to the architecture they support. The ones given here are suitable for any

M.I.T. data-flow type computer. They are adapted from examples given in [Myer81].

### 4.2.1 The Instruction Cell

The contents of the instruction are grouped in two sets: the header and the operand ports.

| HEADER  | Operation code | 1 ,1   | gig         | Dest.  | addr. |

|---------|----------------|--------|-------------|--------|-------|

| d.      |                |        |             | ~~~~~  |       |

| OPERAND | Gating code    | Gate   | flag Valu   | e flag | Value |

| PORT a  |                |        |             |        |       |

| OPERAND | Gating code    | Gate : | flag   Valu | e flag | Value |

| PORT b  |                |        | ·<br>       |        |       |

|         | ,              |        |             |        |       |

These fields are optional

### HEADER.

Operation code-The operation code defines the type of operation to be performed with or upon the values in the value fields. Examples of operations are: ADD, MULTIPLY...

The field next to the operation code gives the number of signals that the cell has to receive before it can be

triggered. These signals are generated by other instruction cells and are used to avoid deadlocks as well as to provide synchronization of different paths in a calculation loop.

SIG-This field indicates that after the execution of the operation a signal is sent to the instruction cell specified by the address in the field.

Dest. addr.-This field gives the location of the instruction cells to where the result of the current instruction has to be sent. Besides the instruction cell address it is also given the location of the operand in the cell.

For special operation codes that can provide more than one result the instruction has more than one group of destination addresses. An example of such instructions are device dependent operations like input which can provide a value and a status.

#### OPERAND PORTS.

For each operand the following fields are necessary:

Gating code-This field provides a code that defines how and when a value received is going to be used to trigger the instruction cell. The four possible gating codes are:

N-no gating is performed. Any result directed here is placed in the value field (provided that the value

field is empty ).

T-a value directed here will be accepted if a true control value (gate flag) has been previously received, or when a true gate flag arrives; otherwise the value is discarded if and when a false gate flag arrives.

F-a value directed here will be accepted if a false control gate has been previously received, or when a false flag arrives; otherwise the value is discarded when a true flag arrives.

C-the value is a constant and is not erased when the instruction is executed.

Gate flag-The gate flag arrives from the control network. There are three possible values

OFF no control packet (gate flag) has been received.

T a true control packet has been received.

F a false control packet has been received.

Gate flags are generated by boolean instructions such as EQUAL, LESS THAN..

"Value flag-This field indicates whether a value currently exists in this operand port:

Value-The value field is received, from the distribution network.

To complete the description of this machine language we present below the example of the previous section

expressed in operation codes that can be executed by the machine: A full set of these opcodes is given in chapter six. It should be noted that they are rather more 'high level' than the actual opcodes one could expect in a particular machine. They are, however, sufficient to illustrate the concepts analysed in this work.

The design process of any high-level language is not finished until a compiler is available to translate its constructions into a particular machine language. VAL has already compilers for the M.I.T. data-flow computer and other research machines, therefore it is reasonable to assume that the following machine program can be obtained from example 4.1 through a compilation process. The problems of compiler design and optimisation are outside of the scope of this work.

To reduce the size of this example we will use a condensed version of the instruction cell:

#N opcode | SIG | Destination addresses gate code \*\*\*\* | gate code \*\*\*\* |

The fields that are only used during execution are not shown (gate flag and value flag) and the operands are put together in the same line instead of using a line for each operand port. The \*\*\* field contains the value of the

operand if it is a constant or \*# which indicates the instruction cells that can provide a value for this operand. N refers to the instruction cell address.

CREATE ARRAY | 3 | SIG | 4a,8a,12a #1 C 3 | C -1 | C 3 | C -4 | #2 SUBTRACT | 3 | SIG | 6a, 10a, 14a C XWMAX | C XWMIN | SUBTRACT | 3 | SIG | 7a, 11a, 15a #3 C YWMAX | C YWMIN | ARRAY[] | 3 | SIG 1 | 5a,6b,7b N 1 | C 1 | C 1 | LESS THAN | 2 | SIG 4 | 6b,7b → N ^4 | C O | #6 MULTIPLY | 1 | SIG 2,4,5 | 16a N ^2 | T ^5, ^4 | #7 MULTIPLY | 1 | SIG 3,4,5 | 16a N ^3 | F ^5, ^4 | #8 ARRAY[] | 3 | SIG 1 | 9a, 10b, 11b. N 1 | 6 2 | C 1 | #9 LESS THAN | 2 | SIG 8 | 10b, 11b N 18 | CO |

MULTIPLY | 1 | SIG 2,8,9 | 16b

N ^2 | T' ^9, ^8 |

#11 MULTIPLY | 1 | SIG 3,8,9 | 16b

N ^3 | F ^9, ^8 |

#12 ARRAY[] | 3 | SIG 1 | 13a,14b,15b

N ^1 | C 3 | C 1 |

#13 LESS THAN | 2 | SIG 12 | 14b,15b

N ^12 | C 0 |

#14 MULTIPLY | 1 | SIG 2,12,13 | 17b

N ^2 | T ^13,^12 |

#15 MULTIPLY | 1 | SIG 3,12,13 | 17bN ^3 | F ^13,^12 |

#16 ADD | 1 | SIG 6,7,10,11 | 17a

N ^6,^7 | N ^10,^11 |

#17 ADD | | SIG 16 |

N ^16 | N ^14,^15 |

### Example 4.2

# Explanatory notes for this example:

The instruction CREATE ARRAY creates an array in the structure storage unit. The operands for this instruction are: the first one gives the number of elements in the array, and the remaining the elements of the array in increasing order of the index.

The instruction ARRAY[] retrieves from the structure storage the array element that corresponds to the index

value available from the second operand port. The first operand specifies the array and the third specifies, in this case, that only one element is to be retrieved.

The instruction LESS THAN performs the following comparison Operand1 < Operand2. The result is sent to the gate flag field of the destination instructions.

Taking instruction #6 as an example we can say that it performs a multiplication, has to receive one signal (from instruction cell 16 informing that operand port a is ready to receive a value), generates three signals one for each of the instructions that provide an operand (they are 2,4 and 5), the result is sent to instruction 16 operand port a, the first operand is not gated and it is received from instruction 2 and finally the second operand is gated (has to receive a true flag from instruction 5) and the value is received from instruction 4. When in a value field there are more than one originator it can be one of the two cases:

- a) The operand is gated and the first originator refers to the instruction originating the gate flag.

- b) The originators come from two mutually exclusive branchs of a conditional instruction, which is the case of instructions 16 and 17.

### Graphic Systems and Data-flow Computers

In the first chapter we described the evolution of graphic systems and the general model for such machines. In the second and third we presented data-flow architectures and languages. In this chapter we will show how graphic systems and data-flow architectures can be matched: First we describe the different methods of picture representation in a graphic system; A graph approach for such representations is then proposed and analysed; Finally, based on the graphic system model and the conclusions about picture representation, we propose a data-flow architecture for graphic systems.

#### 5.1 Picture Representation

4

Since graphic devices were first integrated into computers it has been necessary to address the problem of picture generation [Berg78,Free79]. One technique was to simply integrate in a program the instructions to the graphic device to draw the picture the programmer wants.

Let's assume, for example, that we have a system consisting of a general purpose CPU and a graphics device only able to write and read a pixel (these actions are given to the graphics hardware via command registers located in the I/O space of the CPU) and we want a routine to draw a line given the start and end points. The program presented in appendix II achieves this using the Bresenham algorithm. With more powerful graphic systems, programs like these are no longer necessary because they are directly performed in the graphic system. Nevertheless, the programs designed to use those systems are quite similar in nature: routines that execute in the main CPU (the host CPU) and utilize the commands. These routines are themselves graphic incorporated in application programs. In summary, a picture is generated via a program that runs on the host CPU and sends commands to the graphic system.

This approach is suitable for systems that do not support all or almost all of the graphic operations (projections, transformation, clipping...) because to generate the desired final picture the host CPU has to be used intensively. In graphic systems that support the above operations it is possible to make a deeper separation between the application and the graphical representation of the model, as is shown in figure 2.2. In order to obtain a picture it is not necessary to embed graphic commands in a

host program but simply provide a list of commands (display list) to the graphic system. The application program in the host builds display lists (normally in main memory) and instructs the graphic system which lists to use and what kind of transformations to apply [Matr84].

The advantage of display lists reside in the reduction of interaction between the host CPU and the graphic system (allowing for more parallelism) and the possibility of having the display lists organized in a data base and easily available to be incorporated in more complex pictures (these display lists are normally referred as segments). It is easier to work with these lists incorporated in the application program than to use a set of routines that not only have to be retrieved from storage but executed by the host CPU (this is in some way equivalent to overlay techniques).

Another advantage of display lists is that they can be considered as functions or routines to be executed by the graphic system. With this extension in the use of the display list some graphic systems are able to support 'instructions' very similar to instructions of general purpose CPUs. For example, 'GOTO' a particular location in the display list and continue interpretation from there, 'CALL' a display list or perform conditional jumps. These instructions give more flexibility to the process of

creating a display list (a picture that contains repetitive elements can include CALLs to a display list that represents that element, instead of repeating the same list for every occurrence).

In both ways of passing information to a graphic system there is a need for standardization. The designers of application packages want their programs to be independent of the particularities of the hardware. There are presently several graphics standard available: the CORE system, GKS, GSX and others. The first two are the most popular. CORE is a set of subroutine calls to be incorporated in FORTRAN programs. An application program only has to link these routines without concern of most of the characteristics of the graphic system. This standard was the first one to be widely used. It was design for vector displays but has since been expanded for raster scan systems [Fole79]. CORE supports three dimensional graphics but does not support segments. GKS is a more recent standard and therefore incorporates new concepts such as workstations, segments and a multitude of input devices and input modes [GKS84, Hopg83, Inter81]. Unfortunately it does not support 3D, however the expansion to include three dimensional coordinates is not difficult and a proposal for such extension already exists. GKS is also a set of routines that can be bound to any programming language. The

support of display lists that are called metafiles in GKS are still under discussion. In this work we will use GKS nomenclature for our examples, but the use of this standard does not preclude the use of the ideas presented here with other standards. A list of GKS 'commands' with a short description is given in appendix III.

# 5.2 Parallelism in Graphics

Most applications that use a graphic interface for both output and input use a structured approach to 'build' the pictures that support the application program. This approach is used in order to improve the system capabilities and throughput.

For example, a package to automate PCB design will have a data-base that contains all the electronic components supported [Inter84]. For each component, the data-base must have logical information (logic operation for simulation, type of input and output...), electrical information (propagation delays, voltage and current levels for each input/output...), mechanical information (body dimensions, clearance area...), and graphic information (schematic symbol, pad layout...). A final PCB design will include a components list, a connections list, a schematic

diagram, components placement, connections routing, simulation vectors and others. Let's consider the schematic diagram which is basically graphic information.

In large circuits, the design is partitioned in logical blocks to improve the design phase (each block can be done by different people at the same time), the verification phase (the compliance with the product specification is easier to verify), and the simulation phase. The layout and artwork design is facilitated and blocks of the design can be used in other circuits. A design structure like the following is therefore quite common.

Fig. 5.1: Hierarchical Circuit Design

The schematic of this circuit, has the same structure.

Let's consider now how the graphic information for the schematic is organized. It is assumed that all logic symbols are already available, that they can be referenced by the device number, and that they have their coordinates defined relative to the origin (for completeness, the position of the origin relative to the symbol is the position of the bottom left corner of a hypothetical rectangle that encircles the symbol. The same principle applies for block references). The graphic information for each block of the schematic is: a transformation matrix

that gives the position in world coordinates, the scaling factor and angle of rotation (very unlikely); a viewport array that defines the portion of the world space that should be displayed; the viewport to window transformation; the viewport priority level (used during a pick operation when the pick device points to an area of the screen with overlapped viewports); the blocks or devices that belong to it; a list of vectors that interconnect the different components and a list of strings that represent the labels in the schematic.

For illustration purposes let the following circuit be a block of a more complex circuit:

Fig. 5.2: Schematic Block

The lower case letters besides the connection are there just for reference.

The graphic information of this block will contain:

- a) A transformation matrix to be applied to all components of the block and the priority of the segment.

- b) A window and viewport coordinates.

- c) Five polylines (see appendix III), one for each of the connections (a to e).

- b) Seven strings, one for each of the labels.

- c) Two symbol references. Each one with its own ('local') transformation matrix to position it in the block

space.

Each of the symbols in this picture are represented respectively by:

The NAND gate.

- a) One polyline for the symbol body.

- b) One circle for the output pin (use the GKS generalized output primitive).

- c) Three strings, each of them a single number for the pin numbers.

The D FLIP-FLOP.

- a) Two polylines. One for the square body and the other for the small clock input triangle.

- b) Two other polylines to draw the +5V connections to the set and reset pins:

- c) Two circles, for the set and reset inputs.

- d) Nine strings, for the three letters and six numbers of the symbol.

This description can be put more formally in the following 'pseudo' FORTRAN program (no restrictions are followed for variable names, variable declarations are not given, and instead of CALL POLYLINE we just write POLYLINE)

OPEN SEGMENT (clock block)

defines the subsequent calls as part of a block.

## SET SEGMENT TRANS (clock block, block matrix)

sets the transformation matrix to be used on all outputs included in this block.

SET .

SET

calls to set all the parameters window, viewport and text attributes.

EVALUATE (..., nand) evaluates the transformation matrix for the NAND gate.

EVALUATE (..., dff) evaluates the transformation matrix for the D FLIP-FLOP.

SET SEGMENT TRANS (74LS00, nand)

draws the NAND gate after transformation. The segment for the NANd gate is already defined.

SET SEGMENT TRANS (74LS74, dff)

same as above for the D flipflop.

POLYLINE (4, XDa, YDa) draws line a. XDa and YDa are arrays with respectively the X and Y coordinates for line a.

POLYLINE (4, XDb, YDb) line b

POLYLINE (4, XDc, YDc) line c

POLYLINE (2, XDd, YDd) line d

POLYLINE (2, XDe, YDe) line e

TEXT (X1, Y1, 'ENB') writes string 'ENB' starting at

the X1, Y1 position.

TEXT (X2,Y2,'1/4 74LSOO')

TEXT (X3,Y3,'A1')

TEXT (X4,Y4,'1/2 74LS74')

TEXT (X5,Y5,'CLK1')

TEXT (X6,Y6,'CLK2')

TEXT (X7,Y7,'A2')

When executing this program the host CPU will invoke the GKS subroutines which will pass the appropriate commands to the graphic system. The order in which the picture will appear in the screen is the order given here for GKS calls. First the NAND symbol is drawn followed by the D FLIP-FLOP, the connection lines, and finally the schematic labels. It is not difficult to realise that there is no reason for this particular order (all the output calls in the previous program can be interchanged in their position). This is merely the result of the inherent parallelism of those calls. All the graphic outputs or all the components of the picture could be drawn simultaneously without affecting the final picture. The only restriction to delay their execution is the availability of the transformation matrices and other attributes. In other words, these values

are the inputs for the graphic functions that can be executed as soon as their inputs are available. If we refer back to previous chapters this is no more than the triggering condition for instruction cells in data-flow computers. Therefore, a data-flow computer can be used in the display processing unit of a graphic system. Before describing such an architecture, we shall show how a high-level data-flow language can be used to describe a picture and utilise at the same time the implicit parallelism in the picture generation process.

## 5.3 Picture Description with VAL

We have just shown that the data-flow concept can be applied to graphic routines or primitives. If so, they can be represented with a graph, as we can see in the following figure.

Fig. 5.3: Graph of Circuit Block

The next step is to demonstrate that the program of a graphic system can be done with a high level data-flow language (VAL).

The first issue to be resolved is the support of input/output. One of the reasons why VAL does not support such constructions resides in their lack of conformity with the mathematical definition of a function (the basis for an applicative language). An output does not produce a result, it modifies some global environment, which can be considered a side effect. Both input and output can be invoked simultaneously by independent branches of a graph,

making it impossible to ensure the proper sequencing of output data as well as a coherent sequence of input data.

These considerations are not, however, valid in the case of a graphic display program. First, the proper sequencing of output is irrelevant because of the parallelism in the operations of building a picture. The elements of a picture can be drawn independently as well as the more primitive components of each element. There is, however, an exception to this rule. It is possible to have two pictures that are considered independent but whose bit map images overlap and therefore it is necessary to ensure a deterministic result. This problem can be solved in two ways: a) if the hardware supports segment priority, it is only necessary to have contingent pictures with different priorities, a necessity is picking is supported. The hardware will take care of using the priorities to decide which of the pictures overlaps the other; b) with the graphic functions defined in VAL for graphic representation it is possible to impose a sequence in the graphic outputs. This is discussed in the next paragraphs. Second, the inputs in graphic systems are used to interact with the operator. The characteristics of this type of input are different from input to general programs. It is serial and very slow compared with CPU speeds. It is therefore not necessary to support it with more than one

input function in the graphics program. The problem of inconsequent input data is therefore not a problem in this particular application. Finally, although output functions produce side effects, in our particular case these are outside the program context and can not influence the 'behavior' of any of the programs in the graphic system. The only 'global environment' affected is the operator but this is the purpose of a graphic system.

In order to conform to an existing standard we shall use GKS primitives, but because of VAL's nature certain modifications are necessary.

The SET commands of GKS can be eliminated for the simple reason that they are not functions. They were designed to set a value in a specific memory location or register and all the graphic commands following them will use that value for their operation. For example, SET POLYLINE INDEX (N) sets the polyline color and texture to a certain value and all POLYLINE commands executed after this statement will use that color and texture, until it is modified by another SET POLYLINE INDEX command. Instead of using the SET commands to define values that are then implicitly used by graphic functions we will pass those values directly to the function. This follows the principles used in VAL design, and at the same time makes it easier to write, verify and understand a graphics

program. We will know what the attributes of a graphic function are because they are explicit in the function parameters, instead of being defined somewhere else in the program and being implicitly defined when the function is called.

In terms of the VAL language, a function has to produce an output in order to be usable in the program expressions. If we restrict the graphic functions only to produce graphic outputs, we could not use them in a VAL program without major changes in the language principles. To eliminate this problem, every graphic function will return a boolean value to the program environment. With this value graphic functions can be included in boolean expressions and conditional expressions. Still to be defined is the meaning of the two possible values of the output. Simply expressed, a TRUE value implies that the function was executed successfully, otherwise it was not executed or an error occurred. In summary a picture description is an expression that produces a boolean result with the implications given above.

Ø

As an example of a GKS function in VAL, let's consider the polyline function.

POLYLINE (window, view, transf, polyindex, coordinates, trigger)

where

window: is an array defining the window rectangle (two X and Y world coordinates).

view: is another array specifying the normalized coordinates of the viewing rectangle.

transf: is a matrix that defines the scaling, translation and rotation to be applied to the line.

polyindex: defines the color and texture of the line.

coordinates: is a structure with n elements, each one of them specifying the coordinates of a vertex. The order in which they are in the structure defines the polyline to be drawn (V1, V2, V3... implies a line from V1 to V2, a line from V2 to V3 and so on until Vn).

trigger: this is a boolean value. If TRUE the function is executed when all the other inputs are available and provides after execution a boolean value as specified above. If FALSE the function does not provide any graphic output and provides a FALSE value to the other VAL expressions. As with other inputs the function is not executed until this input is received. The main reason for this input is to facilitate the sequencing of graphic functions when this is necessary.

The definition of this and other GKS functions in VAL syntax can be found in appendix IV.

Using the previous constructions we can express the

small schematic of figure 5.2 in a VAL program.

FUNCTION clock block (window, view, transf: ARRAY [REAL]; trigger: BOOLEAN RETURNS BOOLEAN)

{The OPEN and CLOSE statements are replaced by a function definition. The parameters define what are the window and viewport for clipping and normalization plus the transformation to apply to the all block. The input trigger has the same function of the input of the same name in POLYLINE given above.}

LET

polyindex:INTEGER:=xxx ;

{this name identifies the color }

transfnand:ARRAY [REAL] := ACCUMULATE

(transf, [1:xx;2:xx....]);

{transfinance identifies the transformation to apply to the NAND symbol. It is the result of the multiplication of two matrices, the transf matrix of the clock block and the matrix defining the position of the symbol in the block.}

${\tt transfdff:ARRAY\ [REAL]:=\ ACCUMULATE}$

(transf, [1:xx;2:xx....]);

{the same for the D FLIP-FLOP}

connecta: 2DLINE := [4,1,x1,y1;x2,y2;x3,y3;x4,y4];{defines the vertices for connection a. The structure 2DLINE is explained at the end of the example. {repeat the same for the other connections} textpath: INTEGER: =xxx; {defines text path for strings} {provide all the other attributes for text} labels:BOOLEAN:=TEXT(textpath,...,xt1,yt1, 'ENB', TRUE) AND TEXT(..., xt2, yt2, '1/4 74LS00', TRUE) AND TEXT(..., xt7, yt7, 'A2', TRUE); {labels are output to the screen and when completed the identifier label will have a TRUE value bound to it. The TEXT function draws the string specified at the given The initial values passed are positions. parameters to specify character features. A TRUE value is given to the trigger input a11 these functions because dependent on other graphic functions.} connections: BOOLEAN: =POLYLINE(window, view, transf, polyindex, connecta, TRUE)