MÓS

## METAL OXIDE SEMICONDUCTORS

Constantin D. Adamopoulos

A MAJOR TECHNICAL REPORT

In the

Faculty of Engineering

Presented in partial fulfilment of the requirements for the Degree of Master of Engineering at

Concordia University

Montreal Canada

October 1974

# METAL OXIDE SEMICONDUCTORS ABSTRACT

Interest in the semiconductor memories has grown, rapidly the past few years. The main reason for this interest is the increasing number of applications. It is now generally agreed that semiconductor memories will comprise a growing fraction of the computer memory.

Computer memory is the most obvious area of application for semiconductor memories. However, many other applications become apparent as low-cost semiconductor memories become available. Growing areas of application are desk and pocket calculators, minicomputers, peripheral controllers for computer sustems, manufacturing control equipment, communication systems and electronic watches.

The pace of development has been sutch that many potential users have difficulty anticipating the direction and rate of future progress. Systems designers must anticipate the characteristics of components well in advance in order to arrive at competitive new designs.

C. D. ADAMOPOULOS

## ACKNOWLEDGEMENTS

I wish to express my gratitude to Dr. B.A. Lombos for his useful suggestions on the content and presentation of this technical report.

## TABLE OF CONTENTS

|                                          | PAGE ·              |

|------------------------------------------|---------------------|

| ABSTRACT                                 | III                 |

| ACKNOWLEGEMENTS                          | IV                  |

| LIST OF FIGURES                          | VII                 |

| LIST OF TABLES                           | X                   |

| INTRODUCTION                             | 1                   |

| 1. GENERAL MOS                           | 2.                  |

|                                          |                     |

| 2. FIELD EFFECT TRANSISTORS              | 5 ~                 |

| 2.1 Generat                              | 5                   |

| ,2.2 The FET Principle                   | )'.; <sub>°</sub> 5 |

| 2.3 The Depletion MOSFET                 | 8                   |

| 2.4 Comments                             | 10                  |

| 3. OPERATING CHARACTERISTICS AND CIRCUIT | 12                  |

| SYMBOLS                                  | •                   |

| 3.1 Enhancement MOSFET.                  | 12                  |

| 3.2 Depletion MOSFET                     | 14                  |

| 3.3 Symbols                              | 16                  |

| 4. FABRICATION                           | 19                  |

| 4.1 General                              | 19 `                |

| 4.2 Bipolar Fabrication                  | 19                  |

| 4.3 MOS Fabrication                      | 25 .                |

| 5.       | MOS RESISTOR                       | ., 3-0.            |

|----------|------------------------------------|--------------------|

| •        | 5.1 Load Resistor                  | 30                 |

| 6.       | MQS CAPACITANCE                    | 33                 |

|          | 6.1 General                        | 33                 |

| ,        | 6.2 Intrinsic Capacitance          | 33                 |

|          | 6.3 Small Signal Gate Capacitance  | 36                 |

|          | 6.4 Parasitic Capacitance          | 38                 |

| 7.       | COMPARISON OF MOS PROCESSES        | 39 -               |

| · • .    | 7.1 P and N Channel MOS            | 39                 |

|          | 7.2 Complementary MOS              | 40                 |

| •        | 7.3 Some Application               | 43                 |

| •        | 7.4 New Technologies               | 44                 |

| 8.       | ADVANTAGES OF MOS DEVICES          | 48                 |

| <u> </u> | 8.1 General                        | .48                |

|          | 8.2 Economic Factors               | ·•4 <sup>*</sup> 8 |

|          | 8.3 Performance Factors            | · 52 ,             |

|          | 8.4 Problems and Limitations       | 54                 |

| •        | 8.4.1 Performance, Limitations     | 56                 |

|          | 8.4.2 Business-Management Problems | 57                 |

| C        | ONCLUS ION                         | 59                 |

| R        | EFERENCES                          | 61                 |

## LIST OF FIGURES

| ·               |                                            |                                         | PAG          |

|-----------------|--------------------------------------------|-----------------------------------------|--------------|

| 2-1             | Cross section of a p-channel MOSFET        | . :                                     | • •          |

| ••••            | before channel formation.                  | . ,                                     | , <b>7</b> , |

| 2-2             | Enhancement in a p-type MOSFET.            |                                         | · 7          |

| 2-3             | A p-channel depletion type MOSFET.         |                                         | 9            |

| 2-4.            | Channel depletion with the application     |                                         | _            |

|                 | of positive gate voltage.                  | , ·                                     | ·· 9         |

| 3-1a            | The volt-ampere drain characteristics o    | £ ,                                     | البي         |

|                 | a p-channel enhancement type MOSFET.       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 13           |

| 3-1b            | The transfer curve of a p-channel enhance  | cement                                  | ,            |

| e. <sup>-</sup> | type MOSFET.                               |                                         | 13           |

| 3-2             | Turn-on voltage as a function of thickness |                                         | • ,          |

|                 | of the SiO2 layer to various Si substra    | ate .                                   |              |

|                 | dopings.                                   |                                         | 15           |

| 3-3             | MOS device represented by two diodes and   | đa'                                     |              |

|                 | control plate in the OFF state.            | ٠,                                      | . 17         |

| 3-4             | Electrical symbols, output characterist    | ics                                     | •            |

| ,               | and transfer characteristics of the four   | r. l                                    | ~            |

|                 | types of MOSFET.                           |                                         | 18           |

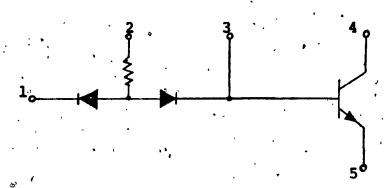

| 4-1a   | A circuit containing a resistor two diodes    | ,            |

|--------|-----------------------------------------------|--------------|

|        | and a transistor.                             | 20           |

| 4-1b   | Cross sectional view of a circuit containing  | •            |

| . ;    | a resistor, two diodes and a transistor in    |              |

| :      | integrated form for bipolar I.C.              | 20           |

| 4-2    | The steps involved in fabricating a monoli-   |              |

|        | thic circuit for bipolar I.C.                 | 22,2         |

| 4-3,4  | -4 The process steps in MOS fabrication       | 27,2         |

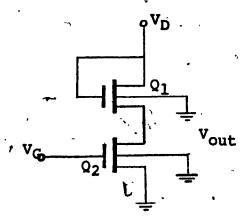

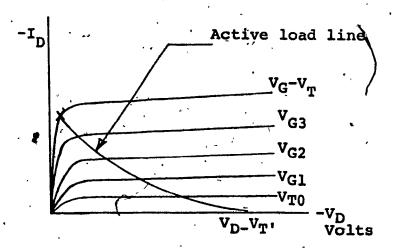

| 5-1    | An inverter circuit with a MOS transistor Q   | / <b>4</b> , |

| •      | operated as a load résistor.                  | 31.          |

| 5-2    | Transistor and resistor characteristics of    |              |

|        | the circuit FIG. 5-1 combined.                | 31           |

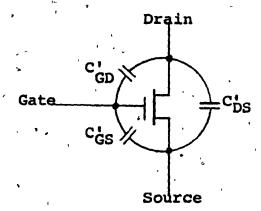

| 6-la   | Schematic representation of intrinsic         | • .          |

|        | capacitance.                                  | 34.          |

| 6-1b   | Location of the intrinsic capacitance         | 34           |

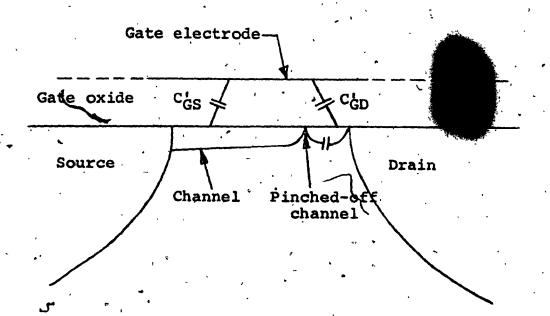

| 6-2    | Small signal capacitance of MOS structure     | <b>\$</b>    |

| ·<br>• | as a function of gate voltage.                | 37           |

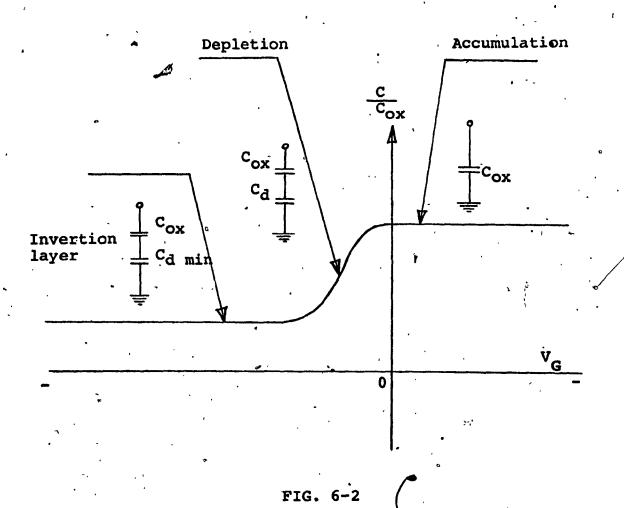

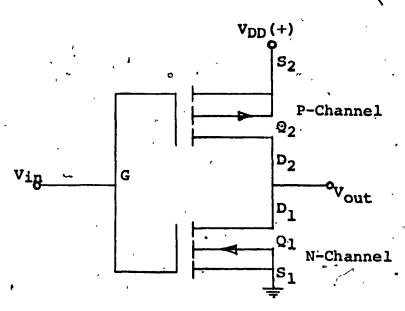

| 7-1a   | Typical complementary inverter.               | 42           |

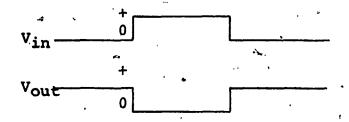

| '7-1b  | Input voltage, output voltage and output cur- | 4            |

| . •    | rent waveforms of the complimentary inverter. | . 42°        |

| •      |                                               | -     |

|--------|-----------------------------------------------|-------|

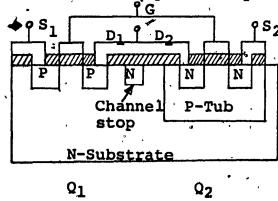

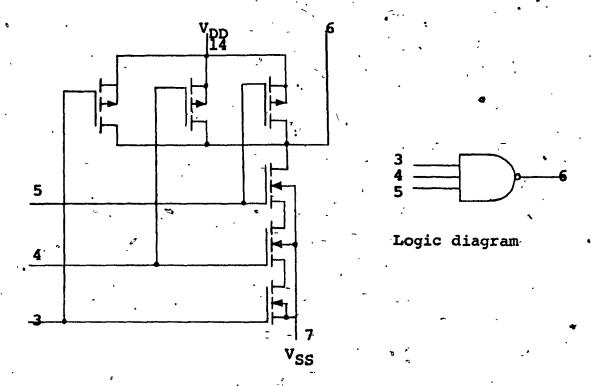

| , 7-2a | Complementary MOS circuit schematic and logic | • •   |

| ,:     | diagram of a 3-input'NAND' gate.              | · 45  |

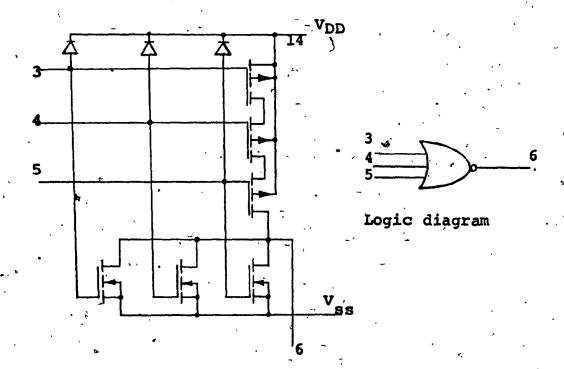

| 7-2b   | CMOS circuit schematic and logic diagram of   |       |

| * - ** | a 3-input 'NOR' gate.                         | 4,5   |

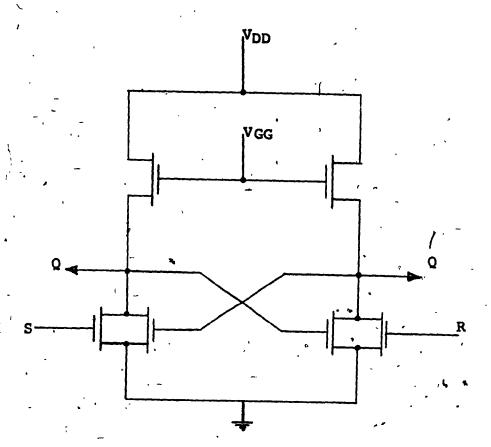

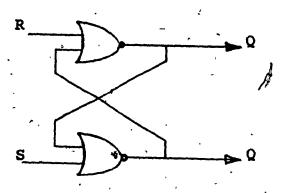

| -7-3   | The cross-coupled latch (PS flip-flop), MOS   | * , * |

|        | device using NOR gates.                       | 46    |

## LIST OF TABLES

|    |                                              | PAGI |

|----|----------------------------------------------|------|

| -1 | Summary of capacitance values                | 3    |

|    |                                              |      |

| -1 | Comparison of Metal Gate MOS and Double-Dif- |      |

| -  | fused Epitaxial Bipolar Fabrication process. | 5    |

|    |                                              | i    |

| •  |                                              | r    |

|    |                                              |      |

|    |                                              | 3    |

| -  |                                              | -    |

## SYMBOLS AND ABREVIATIONS

MQS : Metal Oxide Semidohductors

PMOS : P-channel MOS

NMOS : N-channel MOS

CMOS : Complimentary MOS

ROM : Read Only Memory

RAM : Rantom Access Memory

FET : Field Effect transistor

IGFET : Insulated Gate Field Effect Transistor

MOSFET : Metal Oxide Semiconductor FET

IÇ : Integrated Ciycuït

/LSI : Large Scale Integration

TTL: Transistor Transistor Logic

DTL : Diode Transistor Logic

CPU . : Central Processing Unit

SOS : Silicon On Sapphire

Class 100: When we have 100 particles of size less than

lµ per cubic foot.

V<sub>C</sub>' : Gate Woltage

V<sub>D</sub> : Drain Voltage

I<sub>D</sub> : Drain Current

V<sub>DS</sub> Drain to Source Voltage

V<sub>GS</sub> :: Gate to Source Voltage

$V_{_{\mathbf{T}}}$  : Threshold Voltage

$C_{OX}$ : Capacitance per unit area of the oxide

$T_{QX}$  : . Width of the inversion layer

C<sub>O</sub> : Permitivity of free space

$C_{OX}$  . Permitivity of the oxide

K<sub>OX</sub> Dielectric constant of the oxide

GD: : Gate to drain capacitance

C<sub>CS</sub> : Gate to source capacitance

C<sub>DS</sub>: Drain to source capacitance

: Depletion layer capacitance

: Gate capacitance

#### INTRODUCTION

As late as 1960 transistors were packaged in individual containers varying in size upward from 0.2 inches.

To construct a complete electronic circuit, individual transistors had to be linked together with other components, such as resistors, capacitors, diodes and other transistors.

About 1960 methods were developed to combine most of the components of a circuit on a single crystal wafer of silicon to form an integrated circuit.

The highest component densities on integrated circuits are achieved by the fabrication bechnology called MOS, which stands for metal oxide semiconductors. The MOS technology produces transistors of the unipolar type in contrast to earlier double junction transistors which are bipolar. Unipolar transistors use majority carriers only, either electrons or holes but not both to

The objective of this technical report is to describe the MOS devices, clarify their principle of operation, produce an up to date evaluation of the existing devices and discuss their advantages and limitations.

#### 1 GENERAL MOS

Although MOS technology is considered relatively new in the semiconductor world, the basic concepts of the IGFET (Insulated-Gate Field Effect Transistors), commonly called MOS or MOSFET type transistors, predate the bipolar transistor. Only through the comparatively recent development of stable predictable and high yield manufacturing process has MOS become reality in LSI (Large Scale Integration) form. Prior to this development, poor control and lack of complete understanding of solid state surface conditions resulted in low yields and unstable electrical characteristics. The technology and application of IGFET have been reviewed recently by J.T. Wallmark and H. Johnson<sup>1</sup>

Initial attempts to realize active solid state transistors that operate on the field effect principle, were made by J.E. Lilienfield and O. Heil in the early 1930<sup>2</sup>. The first working model of the principle was developed at Bell Telephone Laboratories in 1948 by J. Bardeen and W.H. Brattain<sup>3</sup>. They observed the field effect principle during a series of experiments in which they attempted to modulate current through point contact and bipolar junction transistors. Attention was then focused on these two types of bipolar transistors and the development of the field effect transistor was halted. In 1952 W.B. Shockley published the theory of the field effect transistor and a practical form of the device was built by G.C.Dacey and I.M. Ross in 1953<sup>5</sup>

This device used an electric field to control conduction in a germanium semiconductor structure. Early attempts to fabricate MOSFETs were unsuccessful due to lack of controlable and stable surfaces.

During the 1950's silicon began to supplant germanium as the preferred material because of its stability over a greater range of temperatures, its higher voltage breakdown, and because of promised better manufacturing control and hence better yield and lower cost. A body of knowledge about the surface properties of silicon was developed rapidly, along with fabricating techniques for highly stables structures in which the interface properties between silicon and silicon dioxide were better understood. The IGFET has also been made on various semiconductors such as Ge<sup>6</sup>,Si<sup>7</sup>, and GaAs<sup>8</sup>, using various insulators such as Sio<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and Al<sub>2</sub>O<sub>3</sub>.

A major breakthrough in semiconductor process occured in the early 1960 with the development of the silicon planar process. The planar process depends upon the fact that a layer of silicon oxide on the surface of a semiconductor slice will prevent the diffusion of certain dopant elements into the semiconductor. Thus patterns of oxide can be used to control the locations of diffused regions. The name "planar" comes from the fact that all three regions-emiter, base and collector-come to the surface of the device, which makes possible large scale integration.

manufacturing until 1967. At that time the yield of MOS type circuits with stable performance characteristics was increased through refinements in the basic MOS process in conjunction with tightened process control and institution of strict, class 100 clean room environments at critical process steps. Since then, yields have continued to rise as a result of manufacturing experience and development of better production equipment, tools and row materials. The silicon suppliers have not only produced high quality silicon wafers, but have also produced the larger diameter wafers (2 to 3 inches) to reduce manufacturing costs. Better wafer fabrication equipment, such as that needed to provide high accurary required in the sequence of photomasking operations, has also become available.

In addition to the general upgrading of the quality and capability of the manufacturing materials and equipment, knowledge of semiconductor surface phenomena has increased greately, resulting in improvement at various critical process steps. Another factor that helped sustain the rise in yield was the development of circuit design techniques to take better advantage of the unique character of MOSFETs. These techniques generally, tented to reduce circuit and array size with no loss in performance. Then in the late 1960s, computers were to control the generation of artwork and photomasks thus providing more uniform tooling and usage of proven predesigned circuits.

#### 2. FIELD EFFECT TRNSISTORS (FET)

#### 2.1 General

rated circuit is the field effect transistor, which is based on the lateral conductance within a silicon crystal by an electric field applied at right angles to the surf ce of the silicon. The junction or bipolar transistor, on the other hand, consists of two junctions formed within the body of a single crystal of silicon. The two junctions separate three regions called the emmiter, the base and the collector. The flow of current from the emmiter to the collector is controlled by changes in the signal applied to the base.

#### 2.2 The FET Principle

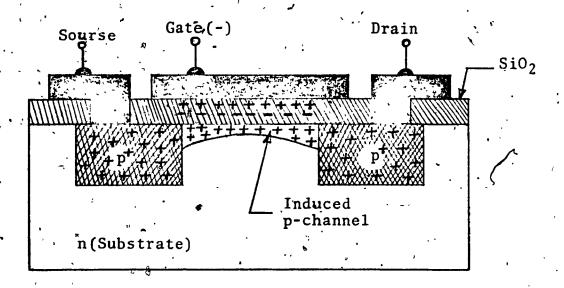

Since p-channel MOSFET is the most widely used of the basic MOS technologies, the p-channel MOSFET will be used to illustrate the FET principle. A cross section of MOS transistor is shown in Fig 2-1. It is made up as follows: A thin slice (8 to 10 mils) of lightly doped n-type silicon material, called a wafer, serves as the substrate or body of the MOS transistor. Two closely spaced (10 to 20 µm) p-type regions, the source and the drain, are formed within the substrate by selective diffusion using the planar technique. A thin (1000 to 2000 A<sup>0</sup>) layer of insulating silicon dioxide (SiO<sub>2</sub>) is grown over the surface of the structure, and holes are cut into the oxide layer, allowing contact with the source and the drain. Then a

thin layer of metal called the gate is overlaid covering the area between the source and the drain regions. Simultaneously metal contacts are made to the source and the drain through the holes cut into the oxide layer, Fig. 2-1. The area between the source and the drain is called the channel and the contact to the metal above the channel area is the gate terminal. The chip area of a MOSFET is 5 square mils or less, about 5 percent of that required by a bipolar junction transistor.

The gate of a MOSFET serves as the control element creating, when properly biased a conduction path or channel between the source and the drain regions as shown in Fig. 2-2. When a negative voltage is gradually applied at the gate, electrons are driven away from the interface of the oxide and silicon under the gate, and a positive charge is induced. With a sufficiently negative gate voltage, an inversion occurs that changes a very thin region of the silicon under the gate N-type (with electrons) to p-type (with holes), Fig. 2-2. The converted region is called p-channel and provides a conduction path for holes.

If a negative voltage is applied to the drain, current will flow from the source to the drain through the channel. The gate voltage controls the amount of the current. The higher the voltage (more negative) the higher the current. The minimum value of gate voltage just sufficient to cause channel formation is known as the gate threshold voltage and is given by the equation: 2-1

Fig. 2-1

P-Channel MOSFET before channel formation (cross section)

Fig. 2-2

Enhancement in a p-type MOSFET (cross section)

$V_T=2 \ \psi_0 + \frac{\sqrt{2 \, \mathcal{E}_S \, \mathcal{E} \, N_A \, 2 \, \psi_o}}{C \, \iota}$  where  $C_i=A \ \mathcal{E}(ox)$ . The threshold (where  $C_i$  dielectric constant,  $t_{ox}$  width of inversion layer) voltage is dependent upon the particular manufacturing, doping concentration, dielectric thickness and the crystal lattice orientation, of the silicon ingot from which the wafer is sliced. Above the conduction threshold (more negative) the gate voltage enhances the channel charge between the source and the drain thereby increasing the channel conduction. Such devices are called enhancement-type MOS devices.

If the drain voltage is increased (more negative) while the gate voltage remains constant, provided it is equal or more negative than the threshold voltage, the current from the source to grain increases. Eventually it reaches a point at which the current remains the same regardless of the increase of the drain voltage. This point is called pinch-off point.

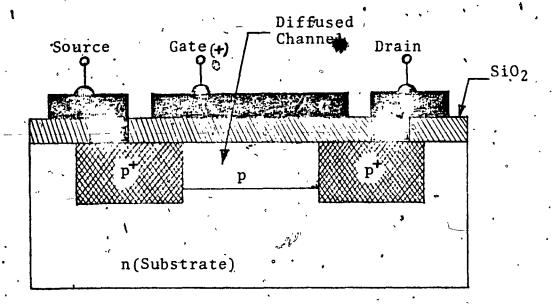

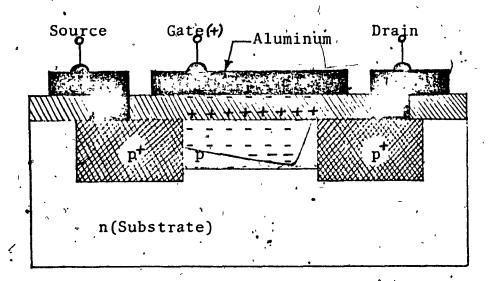

## 2.3 The Depletion MOSFET

which a channel of the same polarity as the source and the drain exists without a bias on the gate. This is done by diffusing a channel between the source and the drain, with the same type of impurity as ussed for the source and the drain. Such a structure is shown in Fig. 2-3.

Fig. 2-3

A p-channel depletion type MOSFET.

Fig. 2-4

Channel depletion with the application of positive gate voltage.

In this device an appreciable drain current Ipss flows for zero gate-to-source voltage  $V_{\rm GS}=0$ . This structure has been made with an p-type diffusion between the source and the drain regions. In this type of transistor, conduction decreases as positive gate voltage is applied. When the gate voltage is made positive, negative charges are induced in the channel, Fig. 2-4. Since the current in an FET is due to the majority carriers (holes for p-type material), the induced negative charges make the channel less conductive, and the drain current drops as  $V_{\rm GS}$  is made more negative. The redistribution of charge in the channel causes an effective depletion of majority carriers, thus the name Depletion MOSFET. Note that the region near the drain Fig. 2-4 is more depleted than near the source because of the voltage drop due to drain current 11.

#### 2.4 Comments

MOS integrated circuits are simpler than bipolar integrated circuits because bipolar circuits require at least two more masking steps plus a number of additional operations, such as oxide deposition, etching, alloying etc. as we shall see in chapter 4. It has been this basic simplicity, with the promise of very low cost, that has spurred work on MOS structures and processes. MOS transistors differ significantly from junction transistors in operating principles. MOS transistors can be used to advantage in many circuits because their properties are similar to those of vacuum tubes.

Their output response varies almost linearly with input and they have a high input impedance because of the layer of SiO<sub>2</sub> which results in an input resistance of 10<sup>10</sup> to 10<sup>15</sup> ohms. In contrast, bipolar transistors, which are current operated rather than field-effect devices, are quite non linear and have a much lower input impedance. The high impedance of MOS transistors makes it simpler to drive a large number of successive circuit stages and thereby to design more complex integrated circuits than with bipolar transistors.

#### 3. OPERATING CHARACTERISTICS AND CIRCUIT SYMBOLS

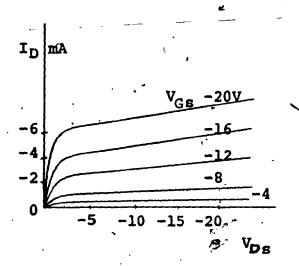

The operating characteristics of the Enhancement MOSFET will be considered first followed by the characteristics of the Depletion MOSFET.

#### 3.1 Enhandement MOSFET

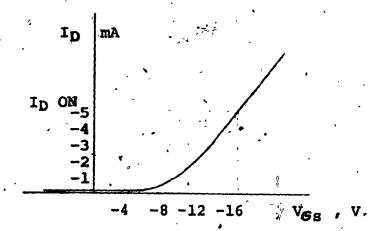

p-channel enhancent-mode MOSFET may be plotted using the gate voltage Ves as the control variable, Fig. 3-la. Its transfer curve is shown in Fig.3-lb. As it is shown from the transfer characteristic curve the current Ip (drain current) at Ves \(\geq 0\) is very small, of the order of few namount and the standard parameters. As Ves becomes more negative the current Ip increases slowly at first and then rapidly. The value of Ves at which Ip reaches some defined value say 10µA, is called Ver or threshold voltage. The value of Ver for the standard p-channel MOSFET is typically -4 volts, and it is common to use a -12 volts power supply for the drain. However this power supply voltage is incompatible with the 5V power supply used in bipolar integrated circuits. In general a low threshold voltage allows:

- a) The use of small power supply voltage.

- b) Campatible operation with bipolar devices.

- c) Smaller switching time due to the smaller voltage swing required during switching.

a) The volt-ampere drain characteristics of a p-channel enhancement type MOSFET

b) The transfer curve (V<sub>DS</sub>=10 V.) of a p-channel enhancement type MOSFET

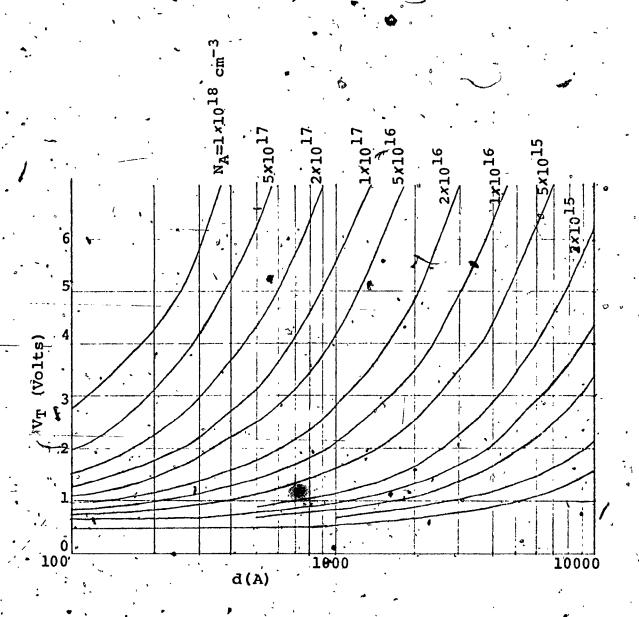

There are many methods used to lower the magnitute of threshold voltage Vr. The first method uses a silicon ( crystal lattice orientation in the (100) direction. It is found that in this orientation the VT is one-half that of (111) crystal lattice orientation. The second method is to use a layer of silicon nitride  $Si_3N_4$  and  $SiO_2$  instead of SiO, alone. In this structure the dielectric constant is about twice that of SiO, alone and reduces VT to about 2 volts. The third method is to use polycrystaline silicon doped with boron as the gate electrode instead of aluminum. This reduces the contact potentials between the gate electrode and the gate dielectric which in turn reduces VT. The device produced with such a method is called silicon gate As it can be seen from equation 2-1 and graph Fig. 3-2, V depends also on semiconductor doping density and insulator thickness. Fig. 3-2 shows a graphical presentation of the dependance of threshold voltage on the doping density and insulator thickness for a Si-SiO, system.

### 3.2 Depletion MOSFET

Depletion mode MOSFET. The depletion type MOSFET may also be operated in an enhancement mode. If we apply a positive gate voltage Fig. 2-3, negative charges are induced into the p-type channel. Since the current in an FET is due to the majority carriers (holes for an p-type material), the induced negative charges make the channel less conductive, and the drain current drops as Vps is made more positive.

Turn-on voltage as a function of thickness of the SiO<sub>2</sub> layer for various Si substrate dopings<sup>12</sup>

The redistribution of charge in the channel causes an effective depletion of majority carriers, which accounts for the designation depletion MOSFET.

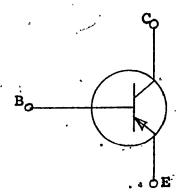

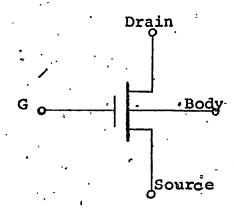

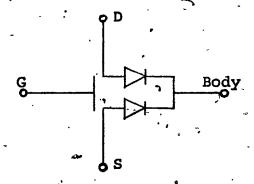

#### 3.3 Symbols

The MOS and bipolar transistor symbols are compared in Fig. 3-3. The MOS device may also be represented by two diodes and a control plate in the "OFF" state. The source is the reference terminal and by convention is positive with respect to the drain just as the emitter in the bipolar devices. The drain is the output terminal in the MOS device as it the collector in the bipolar device. The gate in the MOS device is the control terminal as is the base in the bipolar device. The gate is a metal plate isolated from the substrate by a thin oxide dielectric. The fourth terminal on the MOS device is the substrate often called the bulk or body.

In switching circuits it is desirable that the device is normally "OFF" therefore enhancement type MOS devices are mostly used. This means that a potential must be applied to the control element to cause conduction. The process has been described earlier.

Fig. 3-4 shows the electrical symbols, the transfer characteristics, and output characteristics of the four types of MOSFETs, p-enhancement, p-depletion, n-enhancement and n-depletion, for purposes of comparison<sup>2</sup>.

a) PNP Transistor

b) MOS Transistor

c) MOS device represented by two diodes and a control plate in the OFF state.

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          | <u> </u>               |                                          |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|------------------------------------------|

| TRANSFER<br>CHARACTERISTICS | To de la constant de |                          | - V60                  | TA VE OF TE                              |

| OUTPUT<br>CHARACTERISTICS   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | σ <sub>L</sub>           | Vo=0                   | Vy V |

| ELECTRICAL SYMBOL           | N G S A S A S A S A S A S A S A S A S A S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | die S                    | go os                  |                                          |

| E TYPE                      | n-čhannel<br>depletion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N-CHANNEL<br>ENJANCEMENT | P-CHANNEL<br>DEFLETION | P-CHANNEL.<br>ENHANCEMENT                |

Electrical symbols, output characteristics, and transfer characteristics of the four types of mosfets. 12

#### 4. FABRIÇATION

#### 4-1 General

It was stated earlier that MOS integrated circuits are simpler than bipolar integrated circuits. To appreciate this, and as a comparison of the two technologies, the fabrication of bipolar I.C.s is also discussed here. The bipolar I.C. fabrication will be discussed first and then the MOS fabrication will follow.

#### 4-2 Bipolar Fabrication

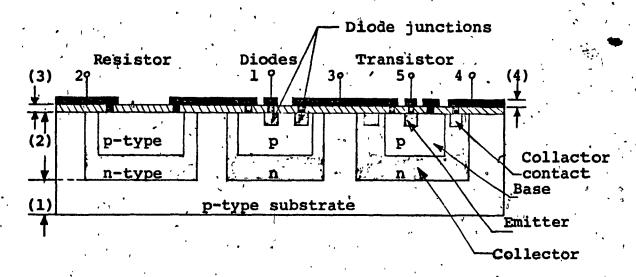

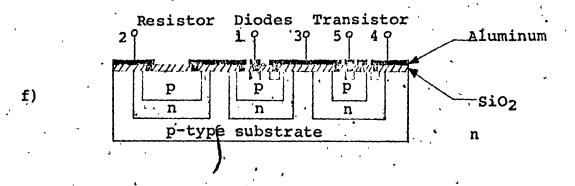

The basic structure of a bipolar integrated circuit comprised of one resistor, two diodes, and a transistor, is shown in Fig.4-1 and consists of four distinct layers of material. The bottom layer (1) (about 10 mils) is p-type silicon and serves as a substrate upon which the integrated circuit is built. The second layer (2) is thin  $(\frac{1}{2} \text{ mil})$ , (10 $\mu$ ) n-type material which is grown epitaxially as a single crystal extension of the substrate. All active and passive components are built within the n-type layer. A round silicon ingot with predetermined impurities, is sliced into wafers approximately 16 mils thick and each wafer is lapped and polished to eliminate surface imperfections. Once p-type silicon substrate is obtained, an n-type epitaxial layer, typically 10 µm thick, is grown on the substrate by Epitaxial Growth. The epitaxial process produces a thin film of single crystal silicon from the vapor phase upon an existing crystal wafer of the same material. The basic chemical

a) A circuit containing a resistor, two diodes, and a transistor.

b) Cross sectional view of the circuit above containing a resistor, two diodes and a transistor in integrated form.

Bipolar I.C.

reaction that describes the epitaxial growth of pure silicon is the hydrogen-reduction of silicon tetracloride.

Since it is required to produce epitaxial films of specific impurity concentrations, it is necessary to introduce impurities into the silicon tetrachloride-hydrogen gas stream. A thin layer of SiO<sub>2</sub> is formed then over the entire wafer, Fig.4-2a, by exposing the epitaxial layer to an-oxygen atmosphere while being heated to about 100° C<sup>11</sup>.

The second step in bipolar I.C fabrication is the Isolation Diffusion. But before that, it is required to selectively remove the SiO2, to form the openings through which impurities will be diffused. This is done by photolithographic-etching process. First the wafer is uniformly coated with photoresist. Then the mask with the desired patern of openings is placed over the photoresist. posing the photoresist to ultraviolet light through the mask, the photoresist becomes polymerized under the transparent regions of the mask. The mask is removed and the wafer is developed by a chemical that dissolves the unexposed portions of photoresist, Fig.4-2b. It is then immersed in an etching solution of hydrofluric acid, which removes the oxide from the areas of the windows uncovered by the photoresist openings through which dopants are to be The portions of Sio, that are protected by the photoresist are not affected by the acid. The photoresist is then removed and it is ready for the isolation diffusion

,

FIG. 4-2

The steps involved in fabricating a monolithic circuit.

- a) Epitaxial growth; b) masking operation;

- c) isolation diffusion; d) base diffusion.

Bipolar I.C.

FIG.4-2

The steps involved in fabricating a monolithic circuit.

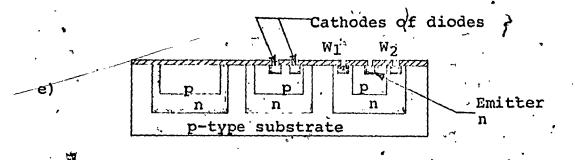

e) Emitter diffusion; f) aluminum metalization.

Bipolar I.C.

of acceptor impurities. The isolation diffusion lasts long enough to permit the p-type impurities to penetrate through the epitaxial layer and reach the p-type substrate; Fig. 4-2c.

Base Diffusion. A new layer of oxide is formed. The photolithographic process is used again to create the pattern shown in Fig.4-2d. The p-type impurities are diffused through the openings of this pattern and are shown in Fig. 4-2d. In this way the transistor base regions, the resistors, anode diodes and junction capacitors are formed.

emitter Diffusion. A new oxide layer is formed over the entire surface. The masking and etching operations are repeated to open windows in the p-type regions as shown in Fig. 4-2e. Through the openings n-type impurities are diffused for the formation of transistor emitters, and the cathode regions of diodes. Additional windows (w<sub>1</sub> and w<sub>2</sub>) are often made into the n regions to which a lead is to be connected, Fig. 4-2e, for the lower resistance collector contacts.

Aluminum Metalization. To interconnect the various components of the integrated circuit a fourth set of windows is opened into a newly formed SiO<sub>2</sub> layer at the points where contact is to be made. After the windows are opened by photolithographic process, the interconnections are made using vacuum deposition of a thin even film of aluminum over the entire wafer. The photoresist technique is then applied again to etch away all undesired aluminum areas, leaving the desired pattern of interconnections only 11, Fig. 4-2f.

The package leads are connected, after alloying the aluminium into the slicon, to the integrated circuit by stitch bonding of a 1 mil aluminum or gold wire from the terminal pad on the circuit to the package lead.

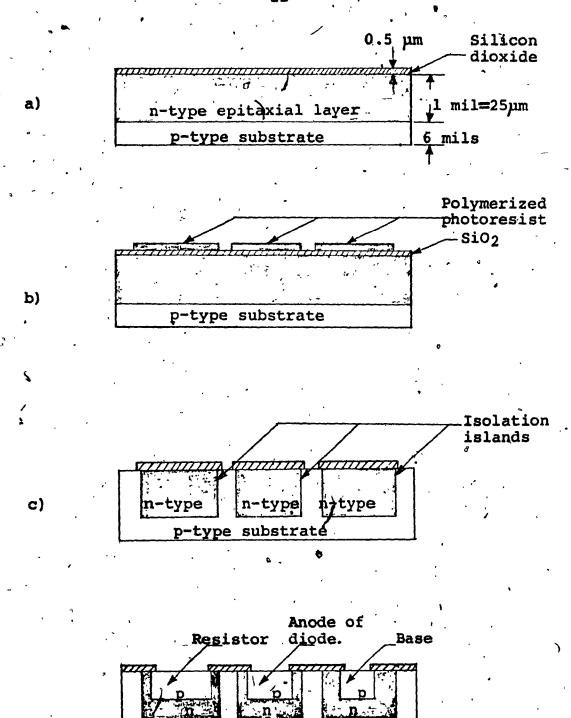

4-3 MOS Fabrication.

Since p-channel MOSFET is what we have been using in our discussion, the p-channel fabrication process will be described. The starting material for the p-channel processing is polished n-type lightly doped wafers in a resistivity range of 3 to 6 ohm cm, with (111) crystal orientation. After the wafer is thoroughly cleaned, a masking (0.6 µm) oxide is grown over its entire surface to serve as a mask against subsequent diffusion, Fig. 4-3a. The growing of the oxide by thermal oxidation is similar to the one already discussed in the bipolar fabrication.

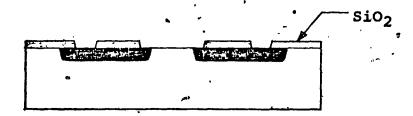

After the oxidation we proceed with the first masking step which defines the source and the drain regions,

Fig.4-3b. The kodak hoto Resist (KPR) KTFR, or KMER considered, is of the negative type and therefore it is soluble in certain liquid developers (i.e tricloroethylene) unless polymerized by exposure to ultraviolet light. The whole photolithographic-etching process for defining the source and the drain is identical to the one described for the bipolar device. After the photoresist is removed the wafer is ready for boron predeposition, Fig. 4-3c. The diffusion of dopants is usually accomplished by a two step process<sup>12</sup>.

The first step called "predeposition", is used to introduce

dopant impurities to only a shallow depth in the oxide layer codeposited with the dopant on the silicon, Fig. 4-3d. The second step called "drive-in diffusion", diffuses the dopant impurities deeper into the silicon to the desired depth, in oxydizing atm. Fig. 4-3e. Predeposition is performed in a diffusion furnace typically in the temperature range of 1000° to 1000°c. Volative compounds of boron, such as diborane (B2H6) and boron thrichloride (BCl3) or liquid compounds, such as boron tribromide (BBr3), are commonly used sources of boron predeposition.

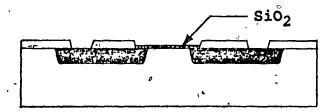

The wafer is now ready for drive-in diffusion. The drive-in diffusion serves not only to diffuse the dopant impurities further into the silicon, but also to form a protective layer of oxide over the sensitive p-doped silicon, Fig. 4-3e.

The oxide layer is completely removed over the gate only and subsequently regrown to the final gate oxide thickness, 1000 A maximum. The masking and etching operations are similar to the previous masking step, except that the alignment of the gate mask must be very precise, since the gate oxide region must extend to both source and drain. The tolerance for misalignment depends on intentional gate overlap and the amount of lateral diffusion of the source and drain.

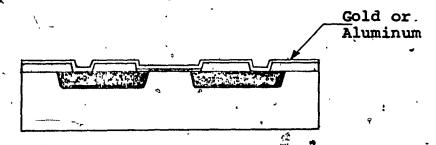

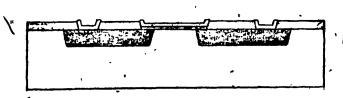

After the completion of the etch and photoresist removal the wafer appears as in Fig. 4-4a.

|          | ·SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •        | randa de la compania della compania |

| a)       | n-type substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •        | <u>.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -1       | Oxidized Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| •        | Photoresist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| `        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| , b)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>\</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| :        | Photoresist Developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | · • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| c).      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | Photoresist Removed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |