# CANADIAN THESES ON MICROFICHE

# THÈSES CANADIENNES SUR MICROFICHE

National Library of Canada Collections Development Branch

Canadian Theses on Microfiche Sérvice

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

# **NOTICE**

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously control materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

**AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de révue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

Canadä

Improved Power Supply Topologica for Fixed and Variable Frequency Operation

Eduardo P. Wiechmann

A Thesis

in

The Department

of

Electrical Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy at Concordia University Montréal, Québec, Canada

June 1985

© Eduardo P. Wiechmann, 1985

#### ABSTRACT

Improved Power Supply Topologies for Fixed and Variable Frequency Operation

Eduardo P. Wiechmann, Ph.D. Concordia University, 1985.

The theory of switching power converters is in a state of flux mainly for two reasons. First, because no comprehensive framework for the analysis of power converters has been established and second, because power semiconductor technology has been evolving continuously. These reasons have motivated this contribution to the development of a In particular, with unified theory for power converters. introduction of a transfer function for switch mode converters some basic principles can be stated, new relationships developed and the behaviour and characteristics of power converters studied. example, common mathematical expressions are introduced to analyze controlled rectifiers, voltage source inverters, and current source Altogether, these converters are by far the most important inverters. and frequently used in contemporary power applications. Further, time domain operations are proposed as an alternative to the more complex, slower, and less accurate frequency based operations. Finally, this unified approach is enhanced by a computer aided design (CAD) method for switch mode converters.

Moreover, while utilizing the technological advances in the field, this study contributes to them by introducing two power supply

topologies for fixed and variable frequency applications. supply topology first presented, intended primarily for fixed-frequency fixed-voltage applications (e.g. UPS systems), incorporates the regulation of the dc link to significantly increase the utilization of the system components. The performances of the two modes of operation of the system (PCU and CCU) are discussed and evaluated against the performance of a standard VSI-SPWM power supply system. fixed PWM pattern is also introduced to further boost the dc link utilization and reduce the operational switching frequency. The second power supply topology proposed, intended primarily for variable-voltage . variable-frequency applications (e.g. ac motor drives), utilizes a PWM controlled rectifier and a PWM current source inverter. The system has a number of intrinsic advantages which include: bilateral power flow reliability (current source), (regeneration), high input-output currents and voltages, reduced reactive components, improved input power factor and simpler current feedback sensors.

Finally, to facilitate the application of the CAD and the design of the proposed topologies, practical design examples are included, and selected predicted results are verified experimentally.

With love to my/wife Soledad

## ACKNOWLEDGEMENTS

I would like to express my gratitude to:

my supervisor, Dr. Phoivos D. Ziogas, for his friendship, guidance, and support throughout my graduate studies and in the development of this work. It has been a great honor to be a member of his research team;

my co-supervisor, Dr. Victor R. Stefanovic, for his support and for the valuable discussions, also, for his encouragment in initiating my interest in graduate studies;

my friends and research colleagues, Michael Boost and Donato Vincenti, for the interesting discussions we shared.

my friend, Dr. Carlos Martinez P., for the uncounted services made available to me in my homeland during my leave.

and finally, to Ms. Madeleine Klein for her reliable typing services and refreshing sense of humour.

# - TABLE OF CONTENTS

| LIST OF TABLES                                          | хi        |

|---------------------------------------------------------|-----------|

| LIST OF FIGURES                                         | xii       |

| LIST OF ACRONYMS                                        | xv        |

| LIST OF SYMBOLS                                         | xvi       |

|                                                         |           |

| 1. INTRODUCTION                                         | 1         |

| 1.1 General Introduction                                | 1         |

| 1.2 Functional Approach in Power Converter Analysis     | 2         |

| 1.3 Generalized Model for the ac/dc dc/ac Conversion    | •         |

| functions                                               | 5         |

| 1.4 Improved Voltage Source Inverter Design Method      | 7         |

| 1.5 Improved Power Supply for Fixed Frequency Operation | 8         |

| 1.6 Novel Power Supply for Variable Frequency Operation | 10        |

| 2. POWER CONVERTER ANALYSIS                             | .15       |

| 2.1 Introduction                                        | 15        |

| 2.1.1 Functional Analysis Approach                      | -16       |

| 2.1.2 The Transfer Function of Switch Mode              | ·         |

| Converters                                              | <b>18</b> |

| 2.2 Pulse Width Modulation of Converters                | 22        |

| 2.3 Voltage Source Inverter Transfer Function           | 25        |

| 2.3.1 VSI Voltage Transfer Function                     | 26        |

|          | .3.2 VSI Current Transfer Function                | 27           |

|----------|---------------------------------------------------|--------------|

| <b>~</b> | .3.3 VSI Steady State Input Current               | 29           |

| 2.4      | urrent Source Inverter Transfer Function          | 30           |

|          | .4.1 CSI Current Transfer Function                | 3 <b>.</b>   |

|          | .4.2 CSI Voltage Transfer Function                | 32           |

|          | .4.3 CSI Steady State Input Voltage               | `<br>33      |

| 2.5      | WM Controlled Rectifier Transfer Function         | 34           |

|          | .5.1 CR Current Transfer Function                 | 35           |

| 44'      | .5.2 CR Voltage Transfer Function                 | 36           |

|          | .5.3 CR Steady State Output Voltage               | 36           |

| 2.6      | Unified Model for VSI, CSI and CR                 | ` <b>3</b> 7 |

| •        | .6.1 Common Transfer Function                     | 37           |

|          | .6.2 The Functional Model                         | 38           |

|          | .6.3 Generalized Converter Input/Output waveforms | 42           |

|          | .6.4 Input/Output Converter Equivalent Circuits   | 51           |

|          | 2.6.4.1 VSI Equivalent Circuits                   | 52           |

|          | 2.6.4.2 CSI Equivalent Circuits                   | 53           |

|          | 2.6.4.3 CR Equivalent Circuits                    | 54           |

| 2.7      | ower Converter Analysis and Design                | 56           |

| •        | .7.1 Transient Converter Analysis                 | 56           |

|          | .7.2 Steady State Analysis                        | 58           |

| ,        | 2.7.2.1 Steady State Analysis in the Frequency    |              |

|          | Domain                                            | 60           |

| ,        | 2.7.2.2 Steady State Analysis in the Time         |              |

| ,        | Domain                                            | 61           |

|            | 2.7.3 Converter Switch Ratings                        | 65  |

|------------|-------------------------------------------------------|-----|

|            | 2.7.3.1 VSI Switch Ratings                            | 67  |

| •          | 2.7.3.2 CSI and CR Switch Rating                      | 68  |

| •          | 2.7.4 Converter Switching Frequencies                 | 71  |

|            | 2.7.5 Converter Filter Design Considerations          | 72  |

|            | 2.8 Conclusions                                       | 76  |

| 3 <b>.</b> | COMPUTER AIDED DESIGN FOR SWITCH MODE CONVERTERS      | 77  |

|            | 3.1 Introduction                                      | 7,7 |

|            | 3.2 Voltage Source Inverter Load Considerations       | 84  |

|            | -3.3 Voltage Source Current Analysis                  | 87  |

| ,          | 3.4 Generalized Design Curves                         | 92  |

| ,          | 3.5 A SPWM Voltage Source Inverter Design Example     | 97  |

|            | 3.6 Experimental Results                              | 99  |

|            | 3.7 Conclusions                                       | 104 |

| 4.         | IMPROVED POWER SUPPLY FOR FIXED FREQUENCY OPERATION   | 105 |

|            | 4.1 Introduction                                      | 105 |

|            | 4.2 The dc Link Voltage Boost Approach                | 113 |

|            | 4.2.1 The PCU Voltage Control Method                  | 113 |

|            | 4.2.2 The CCU Voltage Control Method                  | 117 |

|            | 4.3 UPS Inverter Input/Output Spectra                 | 124 |

| •          | 4.4 Experimental Results                              | 127 |

|            | 4.5 Discussion                                        | 129 |

|            | 4.6 Conclusions                                       | 131 |

| 5.         | NOVEL POWER SUPPLY FOR VARIABLE ERFOLIPTICY OPERATION | 132 |

1

|    | 5.1 | Introduction                                      | r 132 |

|----|-----|---------------------------------------------------|-------|

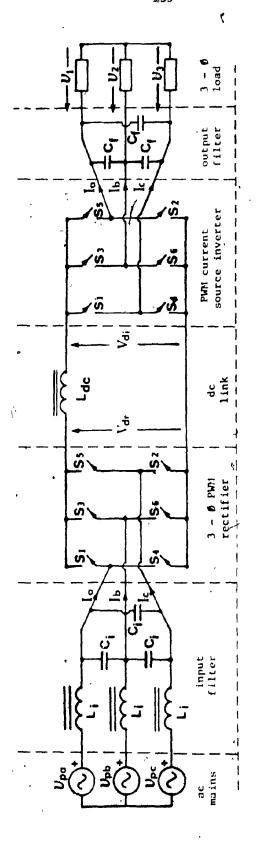

|    | 5.2 | Power Supply Configuration                        | 134   |

|    | 5.3 | PWM Rectifier-Inverter Transfer Function          | 138   |

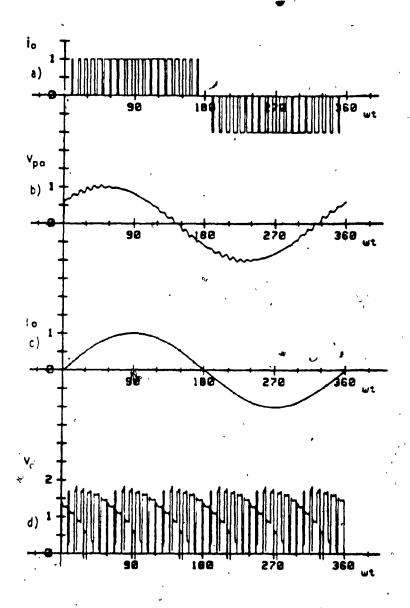

|    |     | 5.4.1 CSI Computer Simulation                     | 141   |

|    |     | 5.4.2 Semiconductor switch ratings                | 141   |

|    | 5.4 | Rectifier-Inverter Analysis and Design            | 145   |

| •  | 5.5 | Analysis and Design of Passive System Components  | 148   |

|    |     | 5.5.1 Load Filter Capacitors                      | 154   |

|    | •   | 5.5.2 Current Source Reactor                      | 157   |

|    | 5.6 | Multiple CSI Operation from Single Current Source | 158   |

|    | 5.7 | Experimental Results                              | 161   |

|    | 5.8 | Conclusions                                       |       |

|    |     |                                                   |       |

| 6. | CON | CLUSIONS                                          | 162   |

|    | 6.1 | Conclusions Summary                               | 162   |

| 4  | 6.2 | Suggestions for Further Work                      | 166   |

| 7. | REF | ERENCES                                           | 168   |

|    |     |                                                   |       |

| 8. | APP | ENDICES                                           | 173   |

|    |     | Appendix 1: PWM Techniques Subprograms            | 173   |

|    |     | Appendix 2: Transient Analysis Program            | 182   |

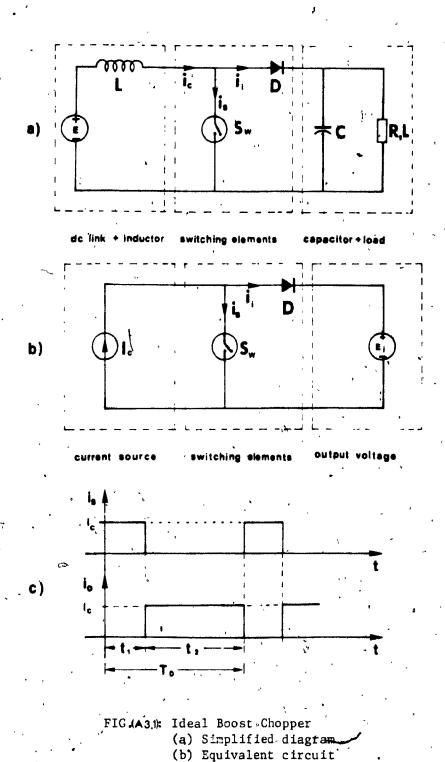

|    |     | Appendix 3: Boost Chopper Analysis                | 188   |

•

.

4

- x -

, .

0

\*

•

# LIST OF TABLES

| Table (2.1)   | Functional classification of power converters:      | 18            |

|---------------|-----------------------------------------------------|---------------|

| Table (2.2)   | Electrical variable classification for the ac/dc    | ;             |

| •             | functional family.                                  | 21            |

| Table (2,3)   | Per-unit system.                                    | . 39          |

| Table (2.4)   | Functional model for the ac/dc conversion function. | 40.           |

| Table (2.5)   | Steady-state block diagram of the functional model  | 41            |

| Table (2.6)   | Displacement angles for the steady-state waveforms  | ,             |

| ,             | of the ac/dc family of converters.                  | 50            |

| Table (2.7)   | State space formulation of converter equivalent     |               |

| •             | circuits,                                           | 59            |

| Table (2.8)   | Generalized converter switch ratings and switch     |               |

|               | utilization factors                                 | · <b>7</b> 0  |

| Table (2.9)   | Normalized switching frequencies                    | 72            |

| Table (2.10): | Input-output generalized spectra for VSI, CSI, and  | ,             |

|               | CR. SPWM and MSPWM control techniques M=1, Ø=0      | 75            |

| Table (4.1)   | Comparison of PWM schemes.                          | 123           |

| Table (4.2)   | Predicted input-output spectra.                     | , <b>12</b> 6 |

| Table (4.3)   | Relevant UPS performance data.                      | 130           |

| Table (5.1)   | Frequency spectra of PWM rectifier input            |               |

| . 3           | and CSI inverter line currents                      | 150           |

| Table (5.2)   | Frequency spectra of dc link (rectifier output      | 1             |

| •             | and CSI input) valtages                             | 151           |

# LIST OF FIGURES

| Fig. (2.1): SPWM* waveform and respective spects | rum                                     | 24         |

|--------------------------------------------------|-----------------------------------------|------------|

| Fig. (2.2): 30-VSI squematic diagram             |                                         | <b>2</b> 6 |

| Fig. (2.3): 3Ø-CSI squematic diagram             | • • • • • • • • • • • • • • • • • • • • | 31         |

| Fig. (2.4): 30-CR squematic diagram.             | •••••                                   | 34         |

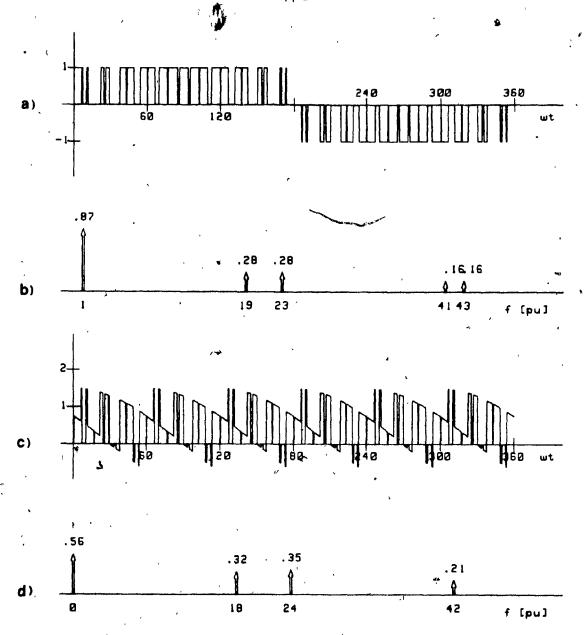

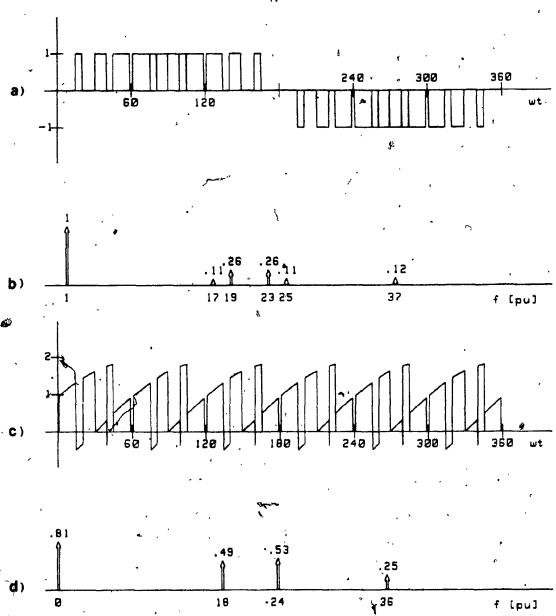

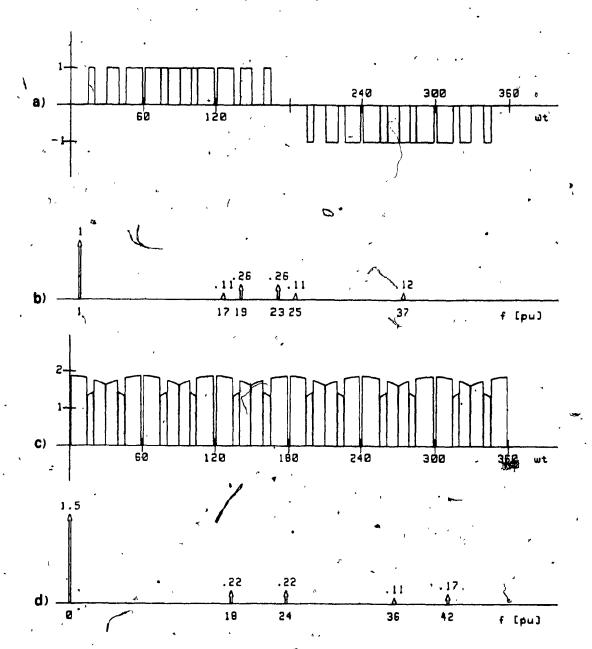

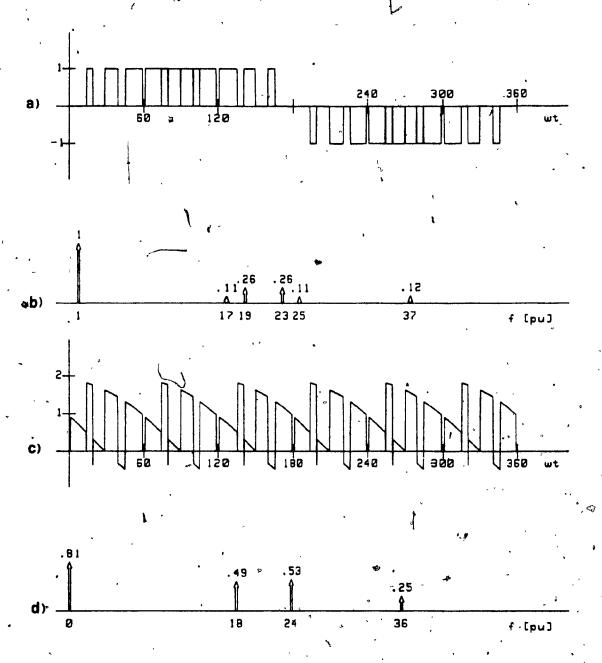

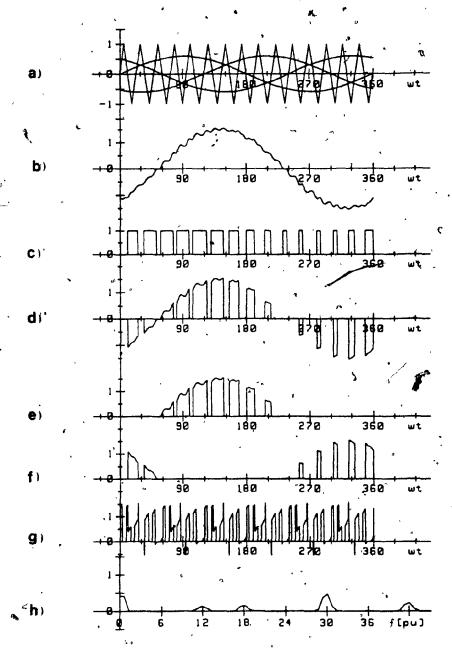

| Figs.(2.5): Generalized waveforms for the ac     | dc conversion                           |            |

| function. SkWM control technique.                | • • • • • • • • • • • • • •             | 44         |

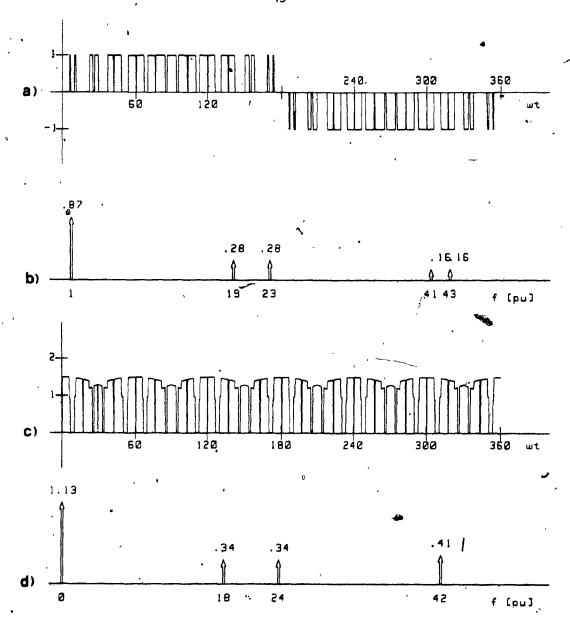

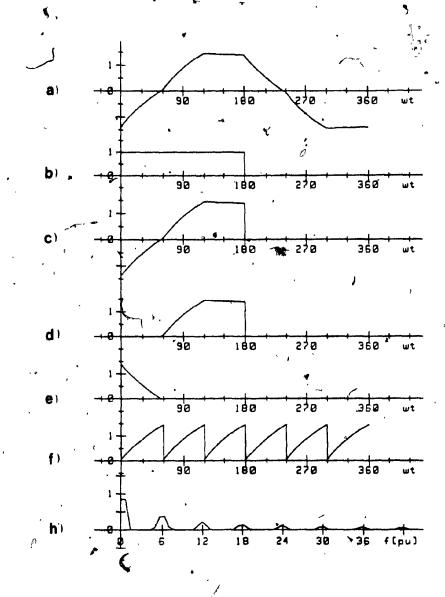

| Figs.(2.6): Generalized waveforms for the ac     | dc conversion                           |            |

| function. MSPWM control technique.               | *********                               | 47         |

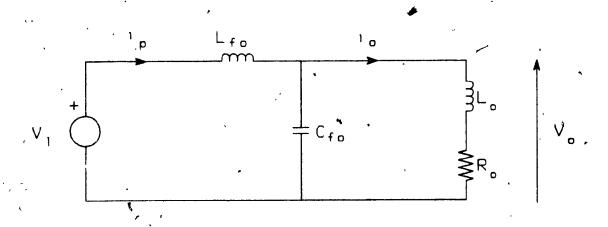

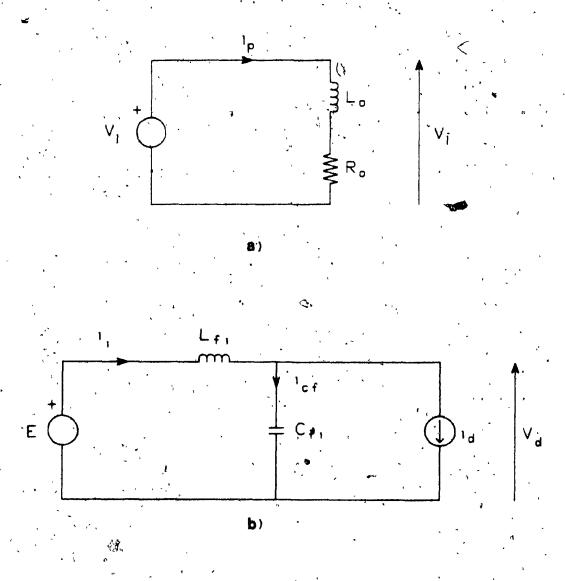

| Fig. (2.7): VSI output equivalent circuit.       | •••••                                   | 52         |

| Fig. (2.8): VSI input equivalent circuit.        | ,                                       | <b>5</b> 3 |

| Fig. (2.9): CSI output equivalent circuit.       | •••••                                   | 53         |

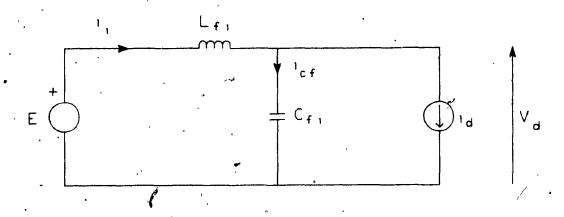

| Fig.(2.10): CSI input equivalent circuit.        | • • • • • • • • • • • • • • • • • • • • | 54         |

| Fig.(2.11): CR input equivalent circuit.         |                                         | 54         |

| Fig.(2.12): CR output equivalent circuit.        |                                         | 55         |

| Fig.(2.13): VSI transient response for a step    | of modulation                           | 57         |

| Fig.(2.14): Time domain operations to implemen   | t the transfer                          |            |

| function relationships using SPWM.               | 4                                       | 63         |

| Fig.(2.15): Generalized 30 bridge configuration  | n <sub>/7</sub>                         | 66         |

| Fig. (2.16): Definition of PWM parameters; norm  | alized carrier                          |            |

| frequency fcn, reference signals,                | 1                                       |            |

| factor.                                          |                                         | 71         |

| Fig. (3.1): Simplified VSI circuit-diagram.      | •••••••                                 | 78         |

| Fig. (2.2) . The circulated PUN control school   | ı                                       | ٥٨         |

| •              |                                                 |      |

|----------------|-------------------------------------------------|------|

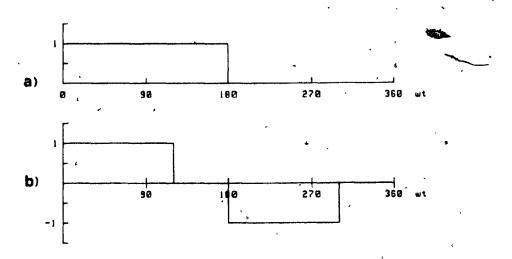

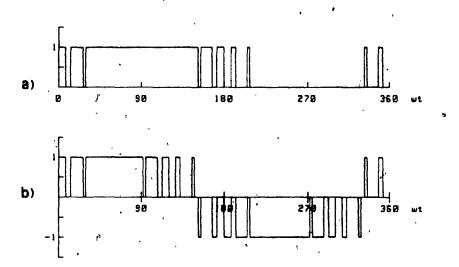

| Fig. (3.3):    | The six-step PWM scheme.                        | 81   |

| Fig. (3.4):    | A fixed PWM pattern scheme.                     | 81   |

| Fig. (3.5):    | VSI equivalent circuits.                        | 86   |

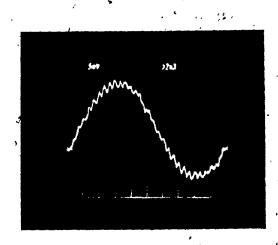

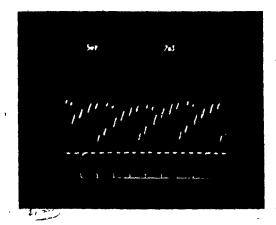

| Fig. (3.6):    | Inverter generated current waveforms with the   |      |

| J              | SPWM control scheme.                            | 89,  |

| Fig. $(3.7)$ : | Inverter generated current waveforms with the   |      |

| •              | six-step PWM scheme.                            | 90   |

| Fig. (3.8):    | Inverter generated current waveforms with a     |      |

|                | fixed PWM pattern (Fig. (3.4))                  | 91   |

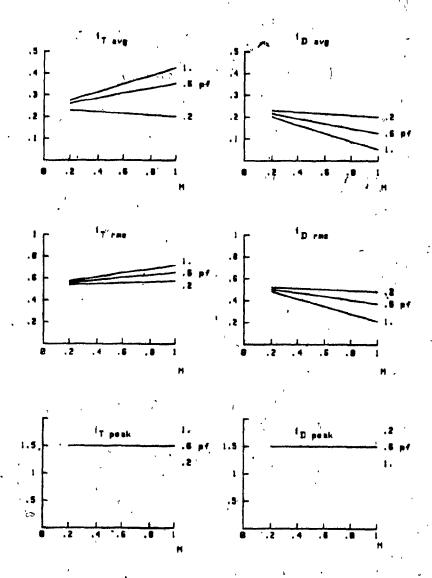

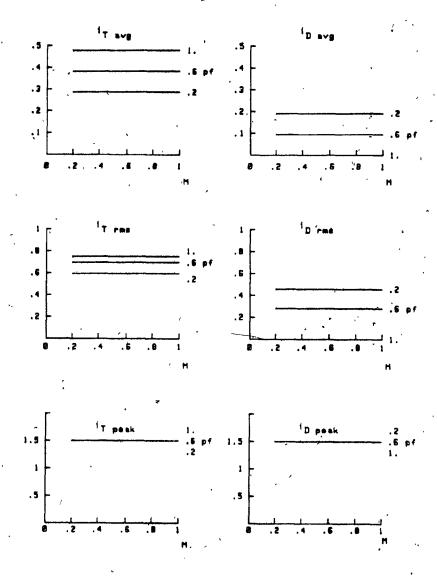

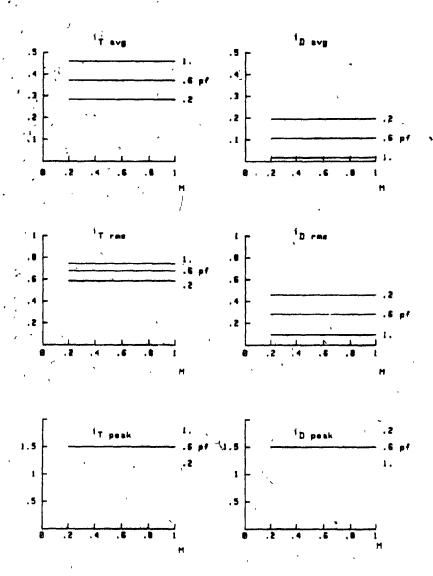

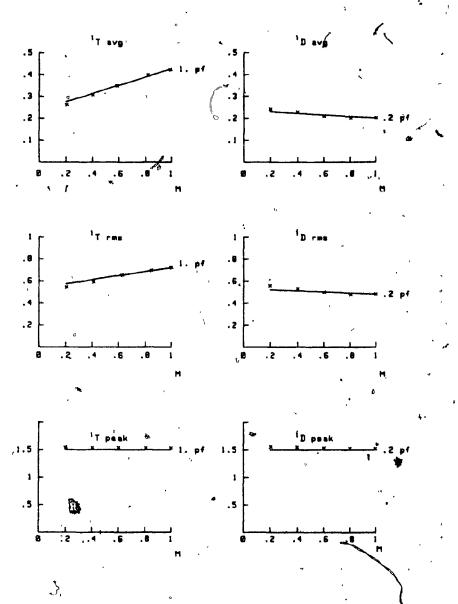

| Fig. (3.9)     | Normalized component ratings with the SPWM      |      |

| •              | control scheme.                                 | 94   |

| Fig.(3.10):    | Normalized component ratings with the six-step  | ,    |

| ,              | PWM scheme.                                     | 95   |

| Fig.(3.11):    | Normalized component ratings with the fixed PWM |      |

|                | pattern of Fig. (3.4)                           | . 96 |

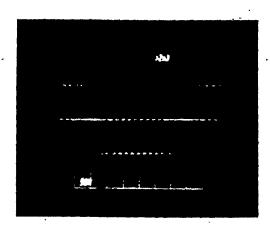

| Fig.(3.12):    | Experimental inverter voltage and ourrent       |      |

|                | waveforms with the SPWM control scheme          | 100  |

| Fig.(3.13):    | Worst case experimental and predicted inverter  |      |

| ;              | component ratings with the SPWM control scheme  | 103  |

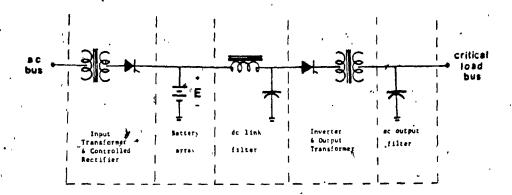

| Fig. (4.1):    | Simplified line diagram of a UPS system         | 107  |

| Fig. (4.2):    | Simplified circuit for the UPS inverter,        | •    |

|                | transformer, and filter components.             | 107  |

|                | Phase and line voltages using SPWM in a VSI     | 109  |

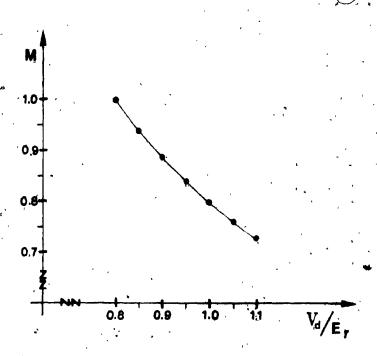

| Fig. (4.4):    | Required VSI modulation factor as a function of |      |

| ı              | the normalized dc link voltage.                 | 110  |

| Fig. | (4,5) | ; | Simplified line diagram of a UPS system with.          |   |

|------|-------|---|--------------------------------------------------------|---|

|      |       |   | a dc link voltage boost stage 114                      | ) |

| Fig. | (4.6) | : | Proposed PWM scheme for the UPS system (fixed          |   |

|      |       |   | pattern with fs=600 Hz) 119                            | ) |

| Fig. | (4.7) | : | Proposed PWM scheme for the UPS system (fixed          |   |

| •    |       |   | pattern with fs=1080 Hz) 120                           | ) |

| Fig. | (4.8) | : | Load-filter configuration. 125                         | , |

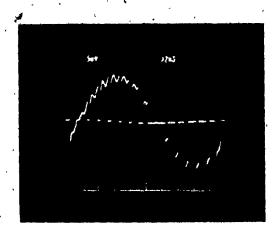

| Fig. | (4.9) | : | Experimental results with the proposed fixed PWM       |   |

|      |       |   | pattern. 128                                           | ţ |

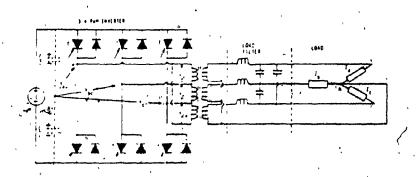

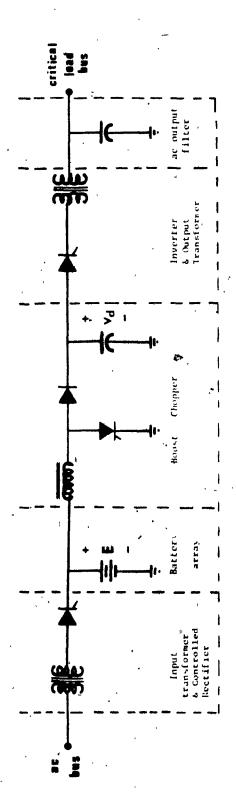

| Fig. | (5.1) | : | A simplified circuit diagram for the proposed          |   |

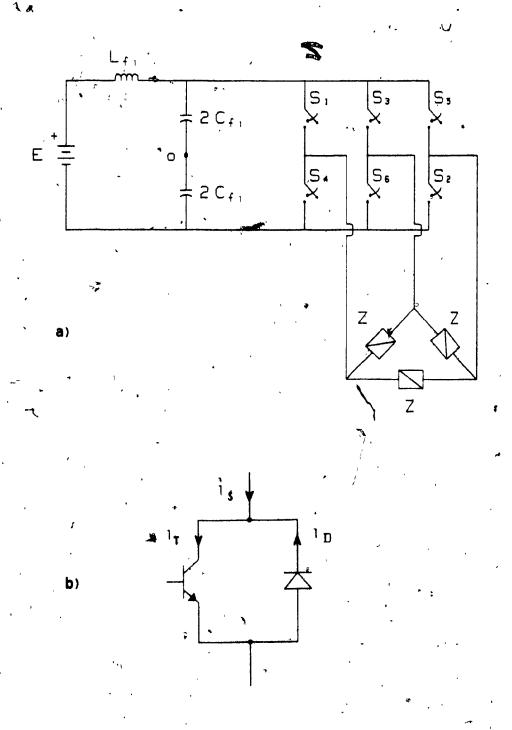

|      |       |   | PWM-CR-CSI power supply system 135                     | , |

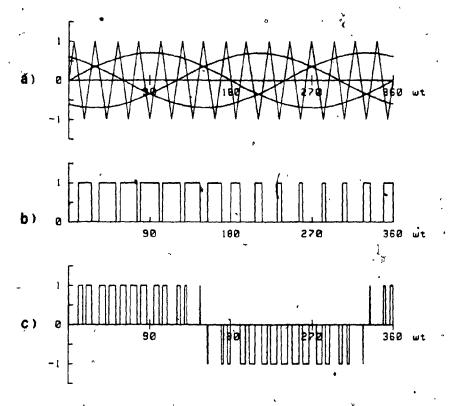

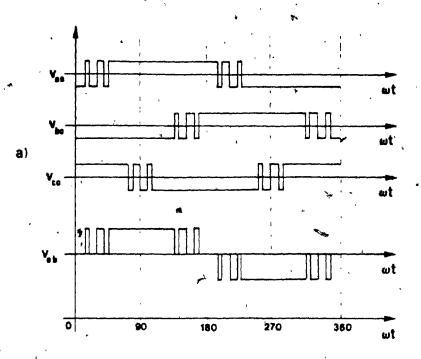

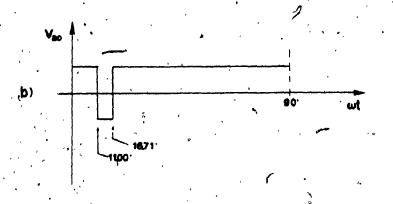

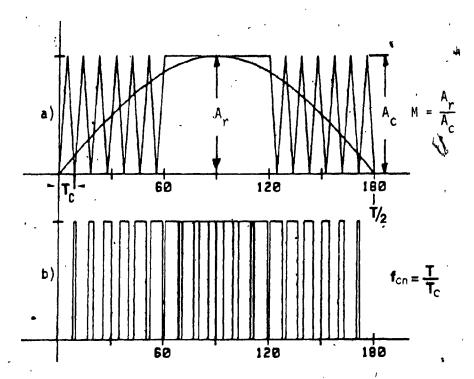

| Fig. | (5.2) | : | MSPWM control technique                                |   |

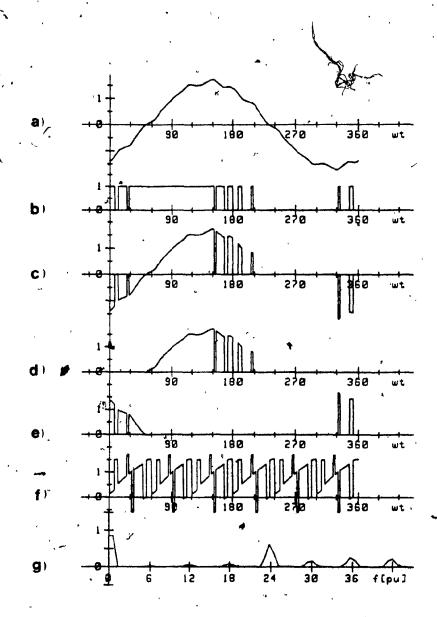

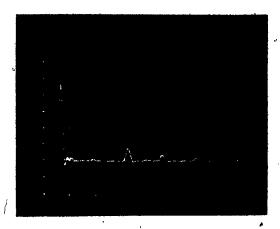

| Fig. | (5,3) | : | CSI voltage and current waveforms 143                  | , |

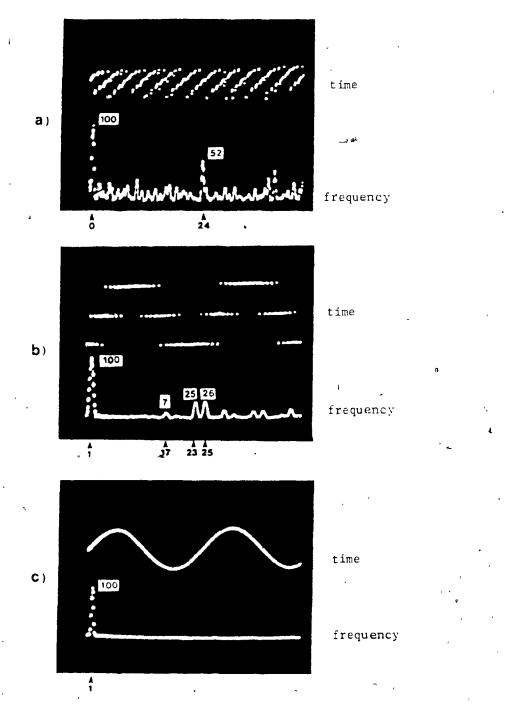

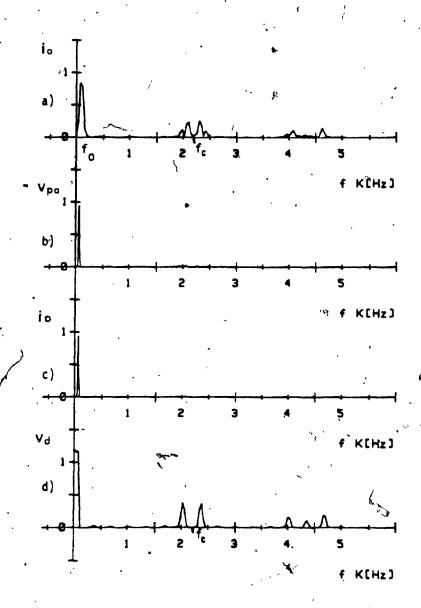

| Fig. | (5.4) | : | Frequency spectra of CSI waveforms Fig. (5.3) 144      |   |

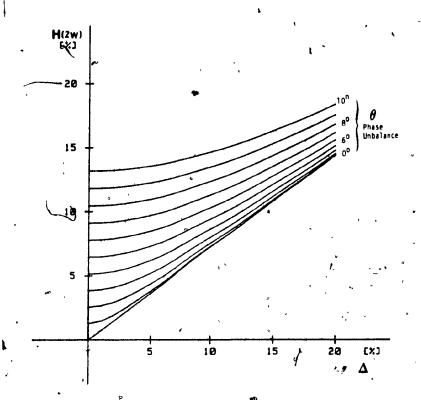

| Fig. | (5.5) | 1 | Amplitude of second harmonic of dc link voltage        |   |

|      |       |   | versus magnitude and phase unbalance of phase          |   |

|      |       |   | voltages 146                                           | ı |

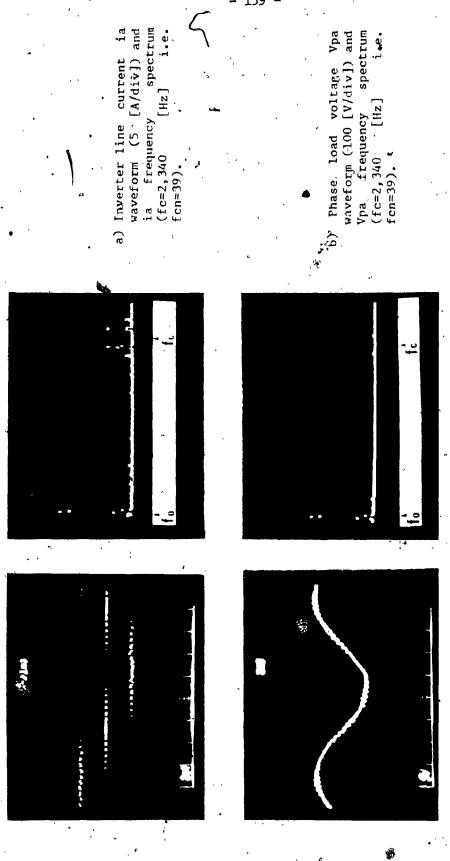

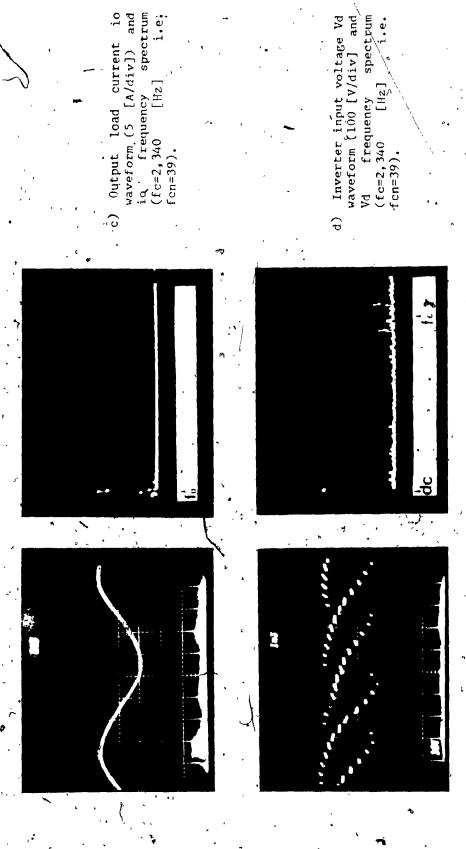

| Fig. | (5.6) |   | Evnerimental CSI waveforms (magnitude and enectra) 150 | , |

### LIST OF ACRONYMS

CR : Controlled Rectifier.

CSI : Current Source Inverter.

VSI : Voltage Source Inverter.

PWM: Pulse Width Modulation.

CAD: Computer Aided Design.

UPS : Uninterruptible Power Supply.

PCU: Partial Chopper Utilization.

CCU: Continuos Chopper Utilization.

DF : Distortion Factor.

THD : Total Harmonic Distortion.

CSR : Current Source Reactor.

### LIST OF SYMBOLS

### 1. General

- x(t) : Instantaneous values.

- X : Average (for dc) or rms (for ac) values.

- x(t) : Matrix of dimension 1X3 representing a 30 phase system (each component of the matrix is a function representing each phase).

- $\overline{x}_1(t)$ : Matrix representing line quantities.

- $x_a$ ,  $x_b$ ,  $x_c$ : Components of  $\overline{x}_1(t)$ :

- $\overline{x}_{o}(t)$ : Matrix representing phase quantities.

- $x_{po}, x_{pb}, x_{pc}$ : Components of  $x_p(t)$ .

- $\overline{x}_1(t)$ : Matrix of fundamental components (sinusoids at fundamental frequency, usually 60 or 50 Hz).

# 2. Voltages

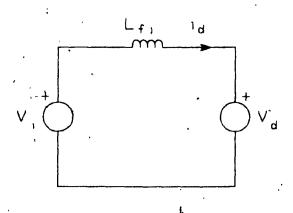

- v<sub>d</sub>, V<sub>d</sub> : Converter input dc voltage and respective average value (also called secondary dc link in Chapter 4).

- v : Output load voltage.

- v; : Input voltage with reference to Fig.(2.10).

- eq,eb,ec : Utility phase voltages

- .vc : Capacitor voltage.

- . E, Er : Primary dc link voltage and respective rated value.

### 3. Currents

- id : Converter dc input current.

- io . : Output load current.

- ice : Capacitor current.

- i | Utility line currents.

- is : Switch current.

- i, Controlled semiconductor current (Fig. 3.1b)).

- ip : Diode current.

# 4. Transfer Functions a

- $\overline{H}(t)$ : Bidirectional common transfer function for VSI, CSI, and CR.

- $\overline{S}$ ,  $\overline{C}$ ,  $\overline{R}$  : Bidirectional transfer functions for VSI, CSI and CR respectively.

- Sv,Cv,Rv : Voltage transfer functions for VSI, CSI and CR respectively.

- Si, Ci, Ri : Current transfer functions for VSI, CSI, and CR .

respectively.

- G : Boost Chopper Gain.

## 5. Electrical Components

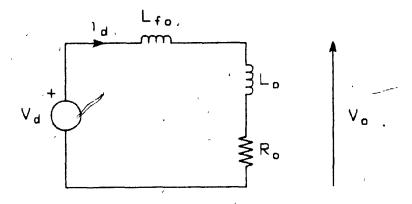

- Ro, Lo : Load resistor and load inductor.

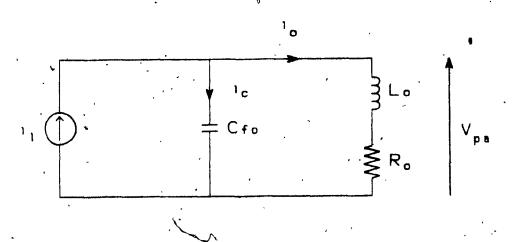

- Lfo, Cfo : Output inductor and output capacitor filter components.

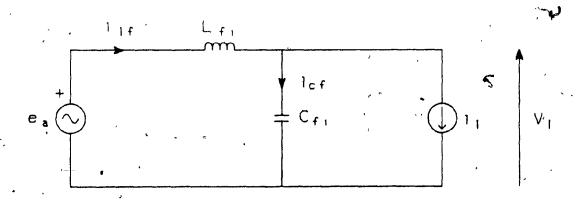

Lfi, Cfi : Input inductor and input capacitor filter components.

Cf : Capacitor filter (first order) for CSI in Chapter 5.

LCSR : Inductance value of the current source reactor.

6. Frequency and Time Variables

fo, : Fundamental frequencies (usually fo=60 or 50 Hz).

fc, fcn : Carrier and normalized carrier frequency.

: Break filter frequency.

: Switching frequency (conmutations per second).

: Time shift between voltage and current (i.e.  $T=\emptyset/\omega$ )

7. Impedances and Phase Displacement

Z(jw) : Load impedance at fundamental frequency (usually equal to one per-unit).

g : Phase displacement between voltage and current.

Xcd,Xc1 : Impedance of the filter capacitor/Cf (Chapter 5)

at the dominant and fundamental frequency

respectively.

8. Miscellaneous

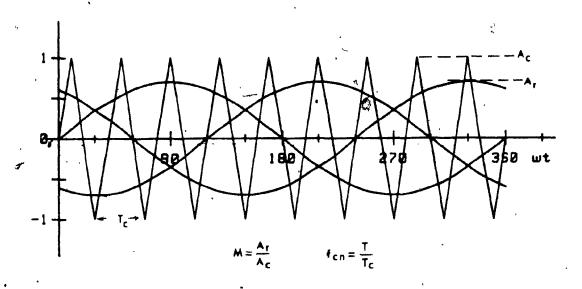

Modulation factor (Fig. (2.16)).

an : Magnitude of the nth harmonic component of a PWM waveform.

Ac : Magnitude of the carrier signal (Fig.(2.16)).

: Magnitude of the reference signal (Fig. (2.16)).

Por : Rated output power.

. Ns : Number of switches.

Suf Switch utilization factor (2.33)

Swuf : Switch components utilization factor (3.3).

pf : Power factor.

Pfe : Equivalent power fator seen by a VSI (4.8).

FUm : Utilization factor produced by the PWM technique.

FUv : Utilization factor produced by variations in the dc link.

FUo : Overall utilization factor.

order of the first significant harmonic (i.e. with a magnitude over 3% of the fundamental).

order of the dominant harmonic or equivalent dominant harmonic.

### CHAPTER 1

### INTRODUCTION

# 1.1 General Introduction

Progress in power semiconductors such as silicon rectifiers and thyristors has been a step-by-step evolutionary process, with gradual but steady improvements in operating characteristics, ratings and packaging concepts. Progress has been quite dramatic when viewed in relation to the modest early beginnings of these devices some twenty seven years ago.

emergence of several types of improved power semiconductors such as the Mosfet, Asymmetrical Thyristors, Gate Turn-off Thyristors and Bipolar Transistors. Some authors [1]...[8] have anticipated considerable improvements in the power converter area made possible by these new breakthroughs in semiconductor technology. These new power converters, implemented with gated turn-off semiconductors, are replacing the traditional power conversion topologies. Undoubtedly, the constant increase in the quality of performance and the drop in cost of these new semiconductor components makes affordable new goals for industrial processes; ensuring a growing field of applications for static converters.

This thesis takes advantage of these technological advances, and contributes to these new trends by focussing its objective on the improvement of power supply topologies for constant and variable

frequency applications. Moreover, in order to establish a common theme and facilitate the analysis of these new topologies, a common analytical framework is first established. Within this framework converters are classified and analysed according to their respective transfer characteristics instead of topologies. As a result new powerful analytical tools are established, eliminating old conceptual difficulties.

# 1.2 Functional Approach to Power Converter Analysis

The contemporary study, analysis and synthesis of power converters is classified, and therefore developed, according to converter circuit topologies, such as controlled rectifiers, choppers, current source inverters, voltage source inverters, dual converters, cycloconverters and frequency changers [9]...[14]. Moreover, the study of these different converter circuits has generated new subdivisions according to auxiliary circuitry employed by the main converter, such as commutation circuits and snubber networks. This somewhat disjointed analysis approach, although successful in describing the converter behaviour, does not establish important relationships among power converter circuits, which tends to prevent the generalized application of research advances.

Pioneering work in the general theory of switching power converters [15] has demonstrated that classifying power converters according to function (instead of circuit topology) permits better understanding of converter behaviour and relationships. Moreover, it

allows the development of analytical concepts applicable to families of converters rather than to individual converters.

Previous work on circuit configurations following a functional approach has been based on switching functions [15] [16] [17]. Basically, a switching function defines the on-off instants of switch conduction. However, current source converters and voltage source converters require completely different switching functions. Consequently, the analysis of voltage and current source converters has been treated separately.

This thesis presents a functional approach based on transfer functions rather than on switching functions [18] [19]. Following this approach current and voltage source converters can be analysed simultaneously (i.e. the transfer function does not depend on the nature of the analysis variables (current or voltage)). Therefore, the transfer function concept constitutes a more abstract but convenient method to relate the input-output variables of power converters.

This approach allows the reclassification of power converters into converter functional families (Table(2.1)), and the identification of significant commonalities among the converters. For example, a unique bidirectional transfer function is established for voltage source inverters (VSI's), current source inverters (CSI's) and controlled rectifiers (CR's). From a classical viewpoint this is a surprising result, although not unexpected in the context of the functional transfer function based analysis approach, because the three above mentioned converters perform the same ac/dc power conversion

function (considering bilateral power flow).

Also, it is noted that VSI, CSI and CR converters do not share switching functions (used extensively in the contemporary analysis of converters [15] [16] [17] [20]) in spite of sharing functional transfer function. This fact reveals the importance of the functional transfer function defined in this thesis (2.1).

Relevant practical relationships deduced for ac/dc converters sharing a common bidirectional transfer function can be summarized as follows:

- i) the same generalized circuit topology can be used by VSI,

CSI, and CR to perform their conversion functions,

- ii) identical pulse width modulation control techniques can be utilized by VSI's, CSI's and CR's, and

- iii) voltage source converters (VSI's) are the dual converters of current source converters (CR's, CSI's).

Converter duality implies that there is a one to one correspondance between reciprocal dependant variables for voltage source and current source converters. Specifically, Chapter 2 will demonstrate that the input current of a VSI, the input voltage of a CSI, and the output voltage of a CR have identical waveforms, and also that output voltages of a VSI, output currents of a CSI and input currents of a CR also have identical waveforms [19].

The converter duality between voltage and current source converters itself has important theoretical consequences. For example,

Chapter 5 will show that while VSI's can be connected parallel to a single dc supply, their dual CSI's can be connected in series to a single dc power supply [21].

A transfer function based functional approach also reveals a common converter filter (input-output) design approach and common PWM control techniques which are essential for the design of the overall power conversion system.

1.3 Generalized Model for the Controlled ac/dc dc/ac Conversion

Functions

Among the various power conversion functions performed by static power converters, the controlled ac/dc and dc/ac are by far the most significant and numerous in terms of applications.

Contemporary analyses of power converters performing these functions have been formulated using frequency domain expressions (Fourier Series) to obtain converter generated input-output waveforms. This analysis based approach provides exact input-output spectral content data [20] normally required for filter design and PWM technique optimization. However, the approach has some intrinsic disadvantages:

- i) it requires complex mathematical transformations and leads to infinite trigonometric series multiplications [15] [16] [20],

- ii) it requires frequency-to-time domain transformations which are intrinsically time consuming and inaccurate, thereby leading to inaccurate predicted time domain waveforms,

iii) it cannot provide good user-computer interaction, particularly in power converter simulation programs, and

iv) it cannot handle transient phenomena and non-linear loads.

These disadvantages have motivated research which focuses on the development of a generalized analysis approach which unifies the ac/dc and dc/ac conversion functions. As shown in this thesis, this approach yields a generalized converter model suitable for the unified analysis of VSI, CSI and CR converters, which is based on the extension of the concepts of switching functions [15] [16] and converter transfer function [18]. In addition according to the functional approach previously described, this study:

- i) presents a generalized converter model for the three phase VSI, CSI and CR families of converters.

- ii) provides state space analysis formulation capable of describing converter performance under transient and steady state conditions,

- iii) produces generalized converter design data for switch ratings, input-output filters and operating frequencies applicable to all aforementioned converter families.

To conclude, Chapter 2 will show that the proposed functional converter model:

- i) requires extremely simple and easily programmable mathematical operations,

- ii) facilitates, computer-aided design by reducing the computer

processing time required by the contemporary approach,

- iii) simplifies converter analysis and design by providing exact input-output predicted current and voltage time domain waveforms and respective spectra,

- iv) can be used to study transient converter performance, thus reducing considerably breadboarding costs and testing times.

## 1.4 Improved Voltage Source Inverter Design Method

The analytical concepts discussed in the previous sections are then employed to facilitate the analysis and design of some well known, static converters, as follows.

Today, the majority of power converter systems employing inverters use voltage source inverters. Therefore, since this thesis is concerned with the improvement of some important families of static power supplies, a critical examination of the contemporary VSI design method has been performed. Chapter 3 will show that a basic VSI design assumption, introduced by the contemporary approach, is responsible for a severe under-utilization of the VSI components. Specifically, the problem with the contemporary approach stems from the assumption that the VSI switch component ratings are identical to VSI switch ratings [11] [14].

By computing the exact VSI component ratings it will be shown that a substantial improvement in component utilization can be accomplished. Also, by using this design approach, the contemporary task of optimizing a VSI design evolves into a precise design method

[22] from an empirical (trial and error) approach.

Together with the generalized description of the analysis and synthesis method, Chapter 3 will present specific normalized design data applicable to fixed and variable output frequency VSI based systems. Moreover, to account for a wide variety of applications, wide ranges of inverter modulation and load power factors will be considered. Finally, for comparison purposes, the design data provided include three different PWM control schemes, namely, sinusoidal PWM [23], six-step PWM [22] and a optimized fixed PWM pattern proposed in Chapter 4 [24].

A comparative design example is used to illustrate the design method, as well as to produce a quantitative measure of the improvements accomplished in a specific case. The example shows a 64 % improvement in the semiconductor utilization factor.

To check the validity of the proposed design method, selected theoretical results will be verified with an experimental 2 KVA unit. Those experimental results, including pictures of actual VSI waveforms will be presented.

To conclude, the proposed design approach of Chapter 4 can be used to substantially increase the processed power per-unit of converter mass (and volume), and to significantly reduce the cost of a VSI based power supply.

# 1.5 Improved Power Supply for Fixed Frequency Operation

Continuing with the application of the analytical concepts

developed in Chapter 2 of this thesis, Chapter 4 focuses on the improvement of power supplies for fixed frequency operation. From this large family of applications, UPS systems are of primary importance and quite representative of this family. A study on UPS systems is justified by the increasing demand for more light, economical, reliable UPS systems [25]. A UPS system is normally operated at a constant output frequency (usually 50 or 60 Hz) to ensure good quality power for computers, hospitals, telephone switching systems, military installations, and in general, for any critical load that cannot tolerate disturbances associated with normal utility power such as; dips and surges, frequency variations and momentary or sustained losses of power. Previous work on UPS systems have incorporated sinusoidal PWM for the UPS-VSI [26]. Further progress has been made by utilizing improved PWM techniques [27] and optimal filtering [28]. A system employing a variable voltage input (VVI) six-step VSI, with the idea of a boost regulator in the dc link was presented in [29]. However, prior to the appearance of publication, the author of this thesis had already presented this concept in his Doctoral Seminar (Concordia University, Fall 1982). Furthermore, a more sophisticated overall system which incorporates an optimized fixed PWM pattern for the VSI inverter, together with the dc link boost chopper regulator, is presented in Chapter 4 [24]. optimization of the control pattern is based on a weighted harmonic optimizing criterion. Chapter 4 also presents an important evaluation of the traditional power conversion method for UPS, identifying some

important sources of component system under-utilization. Finally, several solutions to enhance system design are proposed and experimentally tested to verify predicted results.

For the purposes of completeness, a complementary study on UPS systems based in current source inverters has been performed on [30]. However, VSI based systems are finally recommended (instead of CSI) because in general, a UPS cannot be subjected to the restriction of load linearity and balance required for an efficient CSI system design (a study on effects of unbalanced loads on CSI is performed in Chapter 5 [21]).

As a result of the study and review of this UPS-VSI power conversion process, it is concluded that at least 65 % extra power handling capability can be added to the system without compromising cost or system performance. Furthermore, the improved results obtained for this power supply, are in addition to the improvements of VSI based systems obtained in Chapter 3. Therefore, further improvements of the UPS-VSI system components utilization can be obtained, if the design approach of Chapter 3 is followed to design the UPS topologies proposed in Chapter 4.

Finally, experimental results that demonstrate the feasibility of the proposed UPS-VSI system are obtained using a laboratory unit of 2 KVA.

1.6 Novel Power Supply for Variable Erequency Operation

Chapter 5 of this thesis deals with the improvement of power

supplies for variable frequency operation usually required in variable speed ac drives. A major research effort in that area is justified because, in spite of the many advantages ac machines have over do machines, the cost, control complexity, and poor perfomance and reliability of their respective power converters have prevented the widespread application of ac drive systems. However, with the continously falling prices of power semiconductors, relatively fixed prices of motors, and development of complex control strategies in low priced VLSI circuits, the differences in cost and complexity between ac have been slowly disappearing [2] [3] [31]. drives Consequently, by taking advantage of these developments, today's research and development efforts are focused on improving the converter and overall drive performance. These efforts have created three complementary research fronts. The first deals with control techniques that further improve the dynamic torque speed ac drive characteristics [32]...[35]. The second is engaged in induction motor design for switch mode operation and the development of new motors, such as the permanent magnet (PM) motor [36] [37]. Finally, the third research area is engaged in searching for power converter topologies, that further improve the overall power conversion process such as the one developed in Chapter 5 [38]...[44].

Previous work on these types of power supplies for ac drives can be classified according to three existing power converter families. The first based on diode rectifier PWM-VSI systems for general purpose drives, a scheme not regenerative unless a second front end converter

is added to operate in the inversion mode. Otherwise, dynamic braking can be accomplished only by using a contactor resistor combination across the dc link. So far, and because of its relative simplicity, the most popular technique for the PWM control of the VSI has been the sinusoidal PWM technique [23]. However technological advances, particularly in VLSI circuits, have made possible the consideration of improved modulation schemes for higher drive performance. Other converter types based in VSI will not be considered because they are in clear disadvantage when compared to the PWM-VSI [40].

The second scheme is based on the current control of the VSI, offering substantial advantages in the elimination of stator dynamics in high performance ac drives, compared to their voltage controlled counterparts. However, this scheme is also non-regenerative and has some inherent limitations. It requires three ac current feedback sensors, and sophisticated current controllers which can be expected to produce adverse interactions between phases if the load has no-neutral connection [41].

The last scheme is based on CSI. The six-step CSI is preferred in medium to high, power industrial drives, particularly in traction applications [31]. To improve the CSI performance and reduce low order current harmonics, fixed modulation patterns have been successfully introduced [44].

The simultaneous PWM control of the front end controlled rectifier and the CSI stages will be introduced and discussed in Chapter 5 [21]. Basically, this power conversion system consists of a

PWM-CR interconnected with a PWM-CSI. The generalized ac/dc power conversion function studied in Chapter 2 is used twice in this power supply, for the PWM-CR and for the PWM-CSI.

When compared with a diode rectifier PWM-VSI, a PWM CR-CSI system possesses a number of intrinsic advantages based primarily on its natural current shoot-through protection and reverse power flow capability. However, severe restrictions on the type of load to be used, have to be imposed in order to realize an efficient design of the converter. In fact, a three phase balanced load is required for a good design. This type of load, though restrictive, is encountered in a large family of applications which include ac drives.

Another system design requirement is to utilize improved PWM techniques such as the modified sinusoidal PWM [21] [46] at a chopping frequency over 1 KHz. Specifically, a chopping frequency of 1.38 KHz (well within the range of available gate turn-off devices), ensures:

- i) low order harmonics free dc link operation, thus reducing considerably the size of the bulky dc link reactor employed by six-step CSI's,

- ii) sinusoidal output currents, thus improving the ac motor performance, and

- iii) sinusoidal input currents, thus improving the input power factor and reducing the EMI.

Furthermore, any fault in the inverter side can be cleared by rectifier gate control. Linear operation and controlled regeneration

become natural for the PWM-CR supplying the continous current demanded by the CSI. Finally, the PWM-CR can control load variations by the means of a single dc link feedback. This feature cannot be accomplished using PWM-VSI due to the presence of flywheel diodes.

The subject of the power' supply concept, together with its analysis, design, operating characteristics, and experimental results are presented in Chapter 5 [21].

#### CHAPTER 2

#### POWER CONVERTER ANALYSIS

### 2.1 Introduction

Cost effective switch mode power supplies must be compact, lightweight, and capable of processing a large amount of power per unit volume. Yet power supplies have to be reliable and operable for long intervals without maintenance. Therefore, to specify design and evaluate cost for effective power supply topologies, exhaustive analysis taking into consideration respective performance criteria is required.

The objective of this Chapter is the development of a functional mathematical model suitable for the analysis and evaluation of improved power supply topologies presented in subsequent Chapters. The proposed model covers and unifies the ac/dc and dc/ac power conversion functions required throughout this thesis. However, the concepts developed are general, and therefore, not restricted to these functions alone. The proposed model is obtained following a functional approach (see subsection 2.1.1). Moreover, the model is based on the definition of a transfer function for switch mode converters. This concept can be regarded as the generalized extension of the optimum gain function developed in [18] (the scope of this switch mode converter transfer function is given in subsection 2.1.2). Specifically, the converter model developed in this chapter can be used to study the behaviour of

voltage and current source inverters (dc/ac), and controlled rectifiers (ac/dc) simultaneously.

In addition to the converter model, this chapter includes respective generalized input-output converter waveforms and respective generalized spectra. This information is essential in the design of converters and respective input-output converter filters. This chapter also includes generalized design data for switch ratings and filters.

The transfer function of switch mode converters introduced in this chapter, enables:

- i) the study of the duality between voltage and current converters and their waveform reciprocity,

- ii) the generalized comparison of PWM control schemes,

- iii) the analysis of converters in groups according to function instead of the analysis of individual converters,

- iv) the modular study of systems with multiple switch mode converters,

- v) a more systematic design approach for switch mode converter systems.

### 2.1.1 Functional Analysis Approach

The functional analysis approach tfeats power converters according their specific power conversion function. This function can be defined regardless of the specific application and/or circuit configuration. Table (2.1) shows a functional classification of some

important power converters.

As shown next, the ac/dc power conversion group of converters includes the controlled rectifiers and both voltage and current source inverters. Rectifiers are used to convert ac power into 🛊 power while inverters are intended to do precisely the reverse, that is, the conversion of dc power into ac power. Therefore, they appear to perform different functions. However, when these converters operate under regeneration (reverse power flow) they also perform their reverse function. For example, rectifiers under regeneration convert dc into ac, while, inverters under regeneration convert ac into dc.  $^{\mathcal{V}}$ Therefore, rectifiers can be also viewed and analysed as inverters and inverters as rectifiers. This point of view has been incorporated in the subject analysis approach. As a result, three major (and previously considered independent) classical converter (controlled rectifiers, current source inverters and voltage asource inverters) have been classified as one converter family that performs a common ac/dc or dc/ac function (Table (2.1)). The fact that these three converter types share identical transfer functions and thereby, can have identical input output waveforms is also to be shown. Moreover, a perfect electrical duality is found for current and voltage source converters. In fact, current and voltage variables in current source converters, have a one-to-one correspondance, with voltage and current variables in voltage source converters respectively.

| FUNCTION | CONVERTER TYPE                                                            |

|----------|---------------------------------------------------------------------------|

| ac/dc    | controlled rectifiers  current source inverters  voltage source inverters |

| dc/dc    | choppers                                                                  |

| ac/ac.   | frequency changers voltage controllers                                    |

Table (2.1): Functional classification of power converters.

## 2.1.2 The Transfer Function of Switch Mode Converters

The transfer function is widely used in Electrical Engineering in connection with the input-output transfer characteristics of linear systems, and for the investigation of their respective static and dynamic behaviours. Typically, transfer functions are used with linear, stationary (constant parameter) systems. Also, since a transfer function provides an input-output description of a system, it does not include any information concerning the internal structure of

function of linear systems is not applicable to the study of the highly nonlinear switch mode converters. However, the idea of describing the input-output behaviour of a system, regardless of its internal structure, is exploited in this chapter in order to define transfer functions for switch mode converters. This description of the converter behaviour is of tremendous relevance in power electronics. In particular, input-output converter waveforms are required:

- i) for the design of input-output filters,

- ii) to predict load waveforms,

- iii) to predict system input currents,

- iv) to estimate the degree of utilization of system components

(utilization factors),

- v) and to study systems with multiple stages of power conversion.

Furthermore, the idea of a suitable transfer function which is independent of the converter's internal structure allows the designer to decompose the synthesis of a power converter system into three major steps:

- i) the derivation of the converter transfer function from the task to be performed by the converter,

- ii) the synthesis of topologies to realize the required transfer function,

- iii) the determination of the gating strategy required to produce the transfer function i) with the topology derived in ii).

The converter transfer function can be used to compute a dependent variable in terms of its respective independent converter variable. For example, the input current of a voltage source inverter (dependent input) depends on the converter transfer function and the converter output line currents (independent output). Dependent switch mode converter variables [16] depend on two factors:on the method by which the converter switches are controlled (i.e. gating signals), and also on the independent power sources (e.g. input utility voltages of a rectifier) or ideal sink sources (e.g. continuous do output load current on a rectifier).

A summary of converter independent and dependent variables is presented in Table (2.2). This Table considers the port connected to the source of power (e.g. utility, batteries) as the input converter port, and the port connected to the load as output port.

Consequently, with the description of dependent variables, the transfer function of a switch mode converter is for convenience defined here as,

converter dependent variable

converter transfer function =

converter independent variable

converter independent variable

To fully specify the power conversion process in a switch mode converter (power=[voltage][current]), it is required to compute both current and voltage at the input and output ports. By applying (2.1)

to Table(2.2), it is concluded that a transfer function for voltage and a transfer function for current is defined for every converter type. The fact that a unique (valid for voltage and current) transfer function can be found for the group of converters that perform the ac/dc conversion function is yet to be shown.

| <del></del>    | <del></del> |                          | <u> </u>               |

|----------------|-------------|--------------------------|------------------------|

| CONVERTER      | PORT        | ° CURRENT                | VOLTAGE                |

| TYPE           |             | VARIABLE,                | VARIABLE               |

| controlled     | input       | dependent                | independent            |

| rectifier      | output      | independent              | dependent              |

| current source | input       | independent              | dependent              |

| inverter       | output      | dependent                | independent            |

| voltage source | input       | dependent                | independent            |

| inverter       | output      | independent <sup>*</sup> | dependent <sup>*</sup> |

Table (2.2): Electrical variable classification for the ac/dc functional family.

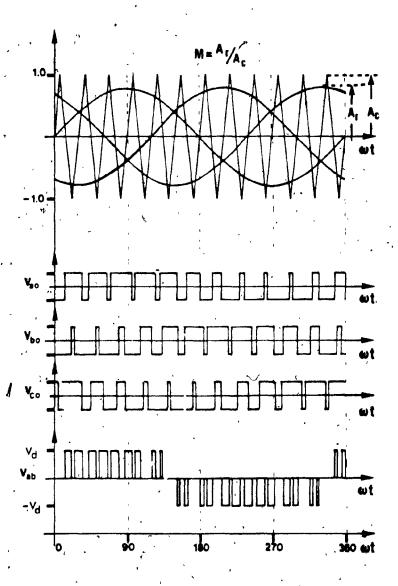

#### 2.2 Pulse Width Modulation of Converters

The practical realization of a switch mode converter transfer function is accomplished using pulse width modulation PWM [23] [27] [46] [47]. PWM in power converters refers to the synthesis of a desired voltage/current waveform by pulses of variable width in such a way that the average value of the modulated waveform has the same shape as a given reference waveform. Consequently, a sinusoidal reference will produce a modulated waveform which has a sinusoidal "average" waveform (and also some inherent but undesirable harmonics).

As stated in section (2.1), for a specific power conversion task the relationship between dependent and independent variables is given by the transfer function. The waveform subjected to modulation is the independent variable (e.g. input voltage in a voltage source inverter). The modulated waveform is the dependent variable (e.g. the output voltage of a voltage source inverter). Therefore, considering the definition of transfer function (2.1), it can be seen that a full analytical description of the modulation process is provided in the transfer function. Therefore, from the transfer function standpoint, power converters can be regarded as modulators.

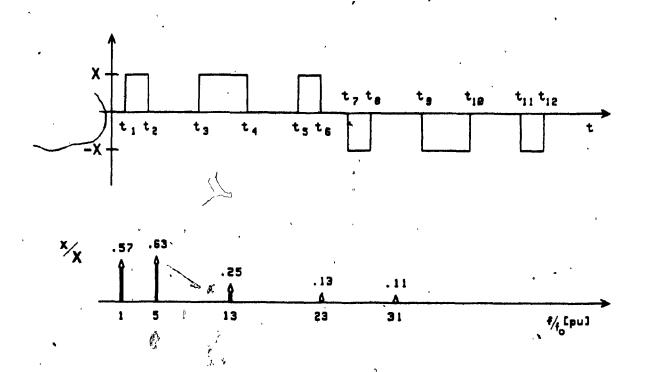

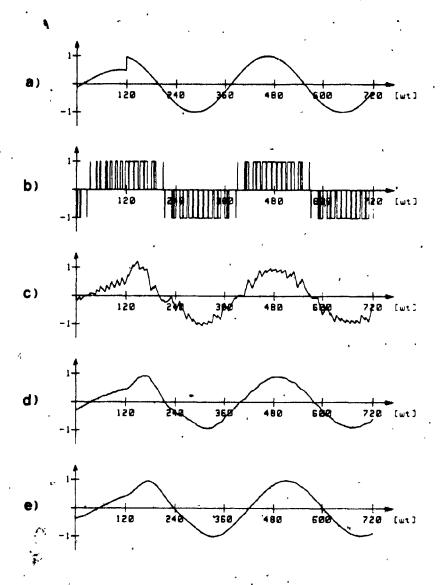

An explicit mathematical representation of the transfer function (or modulator action) requires an explicit representation of the modulated (dependent) waveform and the unmodulated (independent) waveform. Fig.(2.1a) and Fig.(2.1b) show a typical pulse width modulated waveform and its associated harmonic spectrum. The specific modulation technique employed to determine the waveform of Fig.(2.1a),

x(t), is called sine PWM [23]. This thesis examines various modulation techniques and provides the criteria for selecting them depending on specific applications.

Fig.(2.1) suggests two possible mathematical representations for x(t) (modulated or dependent waveform). The first based in Fig.(2.1a) as follows:

$$x(t) = X \sum_{k=1}^{12} (-1)^{k+r} u(t-t_k);$$

$1 \le k \le 6, r=1$   $7 \le k \le 12, r=0$  (2.2)

This approach of specifying x(t) is convenient for time domain analysis and therefore can be used with the converter model whenever transient analysis is required. The second mathematical expression derived from Fig. (2.1b) as the Fourier series expansion of x(t) as follows:

$$x(t) = X \sum_{n=1}^{\infty} a_n \cos(n\omega t)$$

(2.3)

The Fourier series expansion of x(t) is useful in frequency domain type of analysis and has been extensively used to predict steady state onverter behaviour [15] [16] [18] [20]. Whether (2.2) or (2.3) is used, it is clear that a mathematical representation of the converter transfer function can be defined on the basis of (2.1) as:

$$F(t) = \frac{x(t)}{X}$$

(2.4)

Fig. (2.1): SPWM waveform (a) and respective spectrum (b).

Sections (2.3), (2.4) and (2.5) develop specific relationships in order to define the VSI, CSI and CR common transfer function. Moreover, the subject transfer function is utilized to obtain explicit steady state common input-output waveforms encountered in the ac/dc group of converters. Moreover, Appendix 1 provides computer subprograms for the time and requency domain solutions of two PWM techniques, namely, SPWM [23] and modified SPWM [46].

### 2.3 Voltage Source Inverter Transfer Function

Considering (2.1) and Table (2.2) it can be concluded that each converter type (VSI, CSI, CR) can have at least two expressions for its respective transfer function. One for voltage and the other for current variables. Moreover, different transfer function expressions result by either choosing line currents instead of phase currents to define the current transfer function or by choosing phase voltages instead of line voltages to define the voltage transfer function. However, by choosing the independent and dependent variables in a particular way (i.e. phase currents and line voltages in a VSI) it is possible to find a common transfer function for both currents and voltages, thus simplifying the analysis.

For VSI's the voltage transfer function relates input dc voltage with output ac voltage. Also, the current transfer function relates output phase current with respective input dc link current. As stated,

a common transfer function expression valid for current and voltage can be found. This transfer function will be called bidirectional in the sense that relates input to output (voltages) and output to input (currents).

## 2,3.1 VSI Voltage Transfer Function

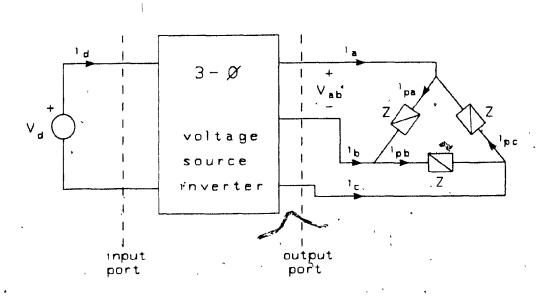

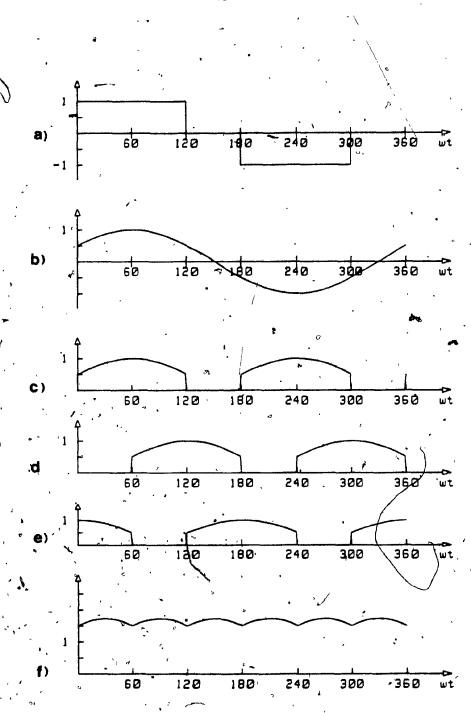

From Table (2.2) the VSI voltage transfer function can be defined by the ratio between the PWM output voltage (dependent variable) and the input voltage (independent variable). Fig.(2.2) shows a  $3\phi$ -VSI schematic diagram and respective input-output variables. The input dc source is represented by an ideal dc source.

Fig.(2.2): 3Ø-VSI schematic diagram.

By choosing the output line voltages as the VSI output dependent

variables (Fig.(2.la)) the voltage transfer function of a VSI becomes:

$$\bar{s}_{v} = \frac{\bar{v}_{\ell}}{v_{d}} = \frac{\left[v_{ab}, v_{bc}, v_{ca}\right]}{v_{d}}$$

(2.5)

Specific steady state assumptions are next considered. These assumptions are required to compute typical input-output waveforms. Since, modern PWM VSI should have a dc voltage ripple with a total harmonic distortion (THD) eqn.(2.6) figure smaller than 5%:

THD =

$$\frac{100}{a_1} \left( \sum_{i=2}^{\infty} (a_i)^2 \right)^{1/2} [\chi]$$

it is reasonable to assume that a small amount of dc ripple (THD 5%) will have a negligible influence on the output dependent variables. Consequently, the input inverter voltage (independent variable) is assumed to be constant for steady state analysis in this chapter. The validity of this assumption used in converter simulation has been cross checked against experimental results [21] [22] [24] [30].

$$v_{d} = E \tag{2.7a}$$

and

$$[v_{ab}, v_{bc}, v_{ca}] = E \cdot \vec{S}_{v}$$

### 2.3.2 VSI Current Transfer Function

From Table (2.2) the VSI output currents are independent

variables and the VSI input current  $(i_{\bf d})$  is a dependent variable. Therefore, by applying (2.1) (and choosing the output phase currents as independent variables) the current transfer function becomes:

$$i_{d} = \overline{s}_{i} \cdot \overline{i}_{p}$$

(2.8a)

or by components:

$$i_d = [s_{ia}, s_{ib}, s_{ic}] \cdot [i_{pa}, i_{pb}, i_{pc}]^T$$

(2.8b)

Furthermore, assuming a converter without losses, the input instantaneous power is equal to the output instantaneous power.

Therefore,

$$\mathbf{v}_{\mathbf{d}} \cdot \mathbf{i}_{\mathbf{d}} = \mathbf{\bar{v}}_{\mathbf{k}} \cdot \mathbf{\bar{i}}_{\mathbf{p}}^{\mathsf{T}} \tag{2.9}$$

replacing (2.8a),(2.5) into (2.9),

$$v_d \cdot \tilde{s}_i \cdot \tilde{i}_p^T = v_d \cdot \tilde{s}_v \cdot \tilde{i}_p^T$$

(2.10)

An inspection of (2.10) reveals that  $\overline{S}_{\bullet}$  (2.8a) is identical to  $\overline{S}_{\bullet}$  (2.7a). Therefore, there is a bidirectional transfer function  $\overline{S}$  that can be applied to compute both dependent variables (current and voltage) in VSI's.

$$\bar{s} + \bar{s}_i - \bar{s}_v \tag{2.11}$$

and using (2.11) and (2.5) the bidirectional transfer function  $\bar{S}$  can

be defined as,

$$\bar{S} = \frac{\bar{v}_{\ell}}{v_{d}} \tag{2.12}$$

$\bar{S}$  is bidirectional in the sense that it relates input to output  $(\bar{S}_{_{\bm{v}}})$  and output to input  $(\bar{S}_{_{\bm{v}}})$ .

### 2.3.3. VSI Steady State Input Current

The input current is determined using (2.8) and the output phase currents (Fig.(2.2)). This expression (2.8) can be used for transient and steady state analysis Consider steady state conditions for the establishment of typical generalized input current waveforms for a Steady state waveforms are relevant because they provide the basic information for PWM technique evaluation, filter design data, and converter ratings. A powerful simplifying assumption, for steady-state analysis would consider the independent VSI output current  $(\overline{i}_{\,m p})$  to be This assumption is valid sinusoidal, that is, perfectly filtered. because the high order harmonics present in the VSI PWM output voltages are attenuated to meet standard THD specifications (THD 5%). THD figure guarantees that the ripple in the output phase current will have a negligible effect on the input dc current [24] and therefore can be neglected when computing the steady-state VSI input current. sinusoidal phase current (fundamental of the output phase current) can be obtained with reference to Fig.(2.2) and (2.12) as follows:

$$\vec{\mathbf{I}}_{\mathbf{p},1} = \frac{\vec{\mathbf{v}}_{\ell,1}}{Z(\omega_0)} \tag{2.13a}$$

or

$$i_{p,1} = \frac{\bar{s}_1}{E \cdot 2(\omega_0)} \tag{2.13b}$$

and the input current (2.8a) becomes:

$$\mathbf{1}_{d} = \frac{\vec{S} \cdot \vec{S}_{1}^{\mathsf{T}}}{\mathbf{E} \cdot \mathbf{Z}(\omega_{0})} \tag{2.14}$$

#### 2.4 Current Source Inverter Transfer Function

The method of the previous section can be used to determine the current and voltage transfer functions for the CSI type of converters.

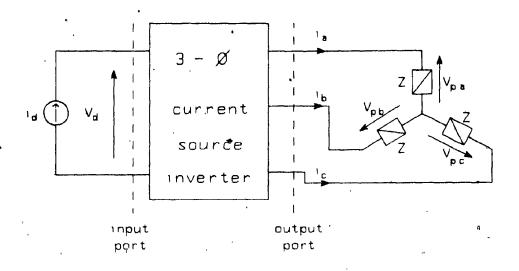

### 2.4.1.CSI Current Transfer Function

From Table (2.2) the CSI current transfer function can be defined by the ratio between the PWM output current (dependent variable) and the input current (independent variable). Fig.(2.3) shows a  $3\emptyset$ -CSI schematic diagram and respective input-output variables. The input current is represented by an ideal current source of magnitude  $i_d$ .

Fig.(2.3):  $3\emptyset$ -CSI schematic diagram.

The output line currents of the CSI shown in Fig.(2.3) are PWM waveforms such as the one depicted by Fig.(2.1a). The CSI current transfer function can be defined by choosing the output line currents (as dependent variables) and the input current (as independent variable) as in (2.1),

$$\tilde{c}_{i} = \frac{\tilde{i}_{g}}{i_{d}} = \frac{\left[i_{a}, i_{b}, i_{c}\right]}{i_{d}}$$

(2.15)

To obtain typical CSI line currents under steady state the dc input current is assumed constant. Basically, the same assumption is used for VSI under steady state in the previous section (i.e. constant dc

input voltage) ·

$$i_{d} = I \qquad (2.16a)$$

and therefore,

$$[\mathbf{i_a}, \mathbf{i_b}, \mathbf{i_c}] = \mathbf{I} \cdot \mathbf{\bar{c}_i}$$

(2.16b)

2.4.2 CSI Voltage Transfer Function

Applying the transfer function definition (2.1) and Table (2.2) (choosing phase voltages as dependent variables) the voltage transfer function  $\tilde{C}_{\nu}$  becomes:

$$\mathbf{v}_{\mathbf{d}} = \mathbf{\bar{C}}_{\mathbf{v}} \cdot \mathbf{\bar{v}}_{\mathbf{v}}^{\mathsf{T}} \tag{2.17a}$$

$$\mathbf{v}_{d} = \left[ \mathbf{c}_{\mathbf{va}}, \mathbf{c}_{\mathbf{vb}}, \mathbf{c}_{\mathbf{vc}} \right] \cdot \left[ \mathbf{v}_{\mathbf{pa}}, \mathbf{v}_{\mathbf{pb}}, \mathbf{v}_{\mathbf{pc}} \right]$$

(2.17b) -

Furthermore, by equating input and output power the CSI voltage transfer function  $\overline{C}_{v}$  can be related to the CSI current transfer function  $\overline{C}_{i}$ . Assuming a converter without losses, the input instantaneous power is equal to the output instantaneous power. Therefore,

$$\mathbf{i}_{\mathbf{d}} \cdot \mathbf{v}_{\mathbf{d}} = \mathbf{i}_{\mathbf{k}} \cdot \mathbf{\bar{v}}_{\mathbf{p}}^{\mathsf{T}} \tag{2.18}$$

replacing (2.17a) and (2.15) into (2.18),

$$\mathbf{i}_{\mathbf{d}} \cdot \mathbf{\bar{c}}_{\mathbf{v}} \cdot \mathbf{\bar{v}}_{\mathbf{p}}^{\mathsf{T}} = \mathbf{i}_{\mathbf{d}} \cdot \mathbf{\bar{c}}_{\mathbf{i}} \cdot \mathbf{\bar{v}}_{\mathbf{p}}^{\mathsf{T}} \tag{2.19}$$

by inspection of (2.19) it can be concluded that the  $\bar{c}_{\nu}$  (2.17a) is

identical to the  $\bar{C}_i$  (2.15). Therefore, there is a bidirectional transfer function  $\bar{C}$  that can be applied to compute both types of dependent variables (i.e. current and voltage) in VSI.

$$\overline{C} = \overline{C}_{y} = \overline{C}_{1} \tag{2.20}$$

Using (2.20) and (2.15) the bidirectional transfer function  $\bar{C}$  is defined as:

$$\bar{C} = \frac{\bar{i}_{\ell}}{i_{\ell}}$$

(2.21)

## 2.4.3 CSI Steady State Input Voltage

The input voltage can be determined using (2.17a) and the output phase voltages. Reasoning similar to the one that allows the assumption of sinusoidal waveforms for the steady-state output phase currents in a VSI (when computing the input carrent) can be also applied in CSI analysis. For the CSI case the output phase voltages can be assumed purely sinusoidal [21] [30] when computing the CSI steady state input voltage. Therefore, considering only the fundamental of i, and the circuit of Fig.(2.3),

$$\bar{v}_{p,1} = \bar{i}_{\ell,1} \cdot Z(\omega_0)$$

(2.22a)

$$\bar{\mathbf{v}}_{\mathbf{p},1} = \frac{\bar{\mathbf{c}}_1}{1} \cdot \mathbf{z}(\omega_0) \tag{2.22b}$$

and the steady state input voltage (2.17a) becomes,

$$v_{d} = \overline{c} \cdot \overline{c}_{1}^{\mathsf{T}} \left( \frac{z(\omega_{o})}{\overline{I}} \right)$$

(2.23)

## 2.5. PWM Controlled Rectifier Transfer Function

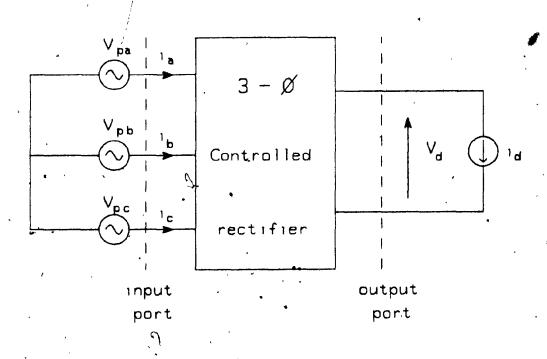

# .2.5.1 CR Current Transfer Function

From Tables (2.2) and (2.1) the CR current transfer function can be defined by the ratio between the PWM input current (dependent variable) and the dc output current (independent variable).

Fig.(2.4) shows a 30-CR schematic diagram and respective input output variables. The CR output current is represented in Fig.(2.4) by an ideal current source of magnitude i.

Fig. (2.4): 30-CR schematic diagram.

In this case the current transfer function becomes,

$$\bar{R}_{i} = \frac{\bar{i}_{\ell}}{i_{d}} = \frac{\left[i_{a}, i_{b}, i_{c}\right]}{i_{d}}$$

(2.24)

Also, in the analysis of VSI and CSI converters it has been assumed (for steady state) that the independent variable of the dc side of the converter is ripple free. Correspondingly, in PWM.CR steady state analysis the dc output current can be assumed constant (ripple free dc). This assumption is valid because when using PWM in CR the task of filtering becomes quite simple, with the output being typically a smooth (almost ripple free) dc current. Moreover, this assumption is routinely used even in the analysis of six step CR where current filtering becomes more critical [10] [11] [14]. Therefore for steady state,

$$[i_a,i_b,i_c] = I \cdot \bar{R}_i$$

(2.25b)

# 2.5.2 CR Voltage Transfer Function

By applying the transfer function definition (2.1) and Table (2.2) the voltage transfer function  $\bar{R}_{\mu}$  can be defined as,

$$v_{d} = \bar{R}_{v} \cdot \bar{v}_{p}^{T}$$

(2.26a)

$$v_{d} = [R_{va}, R_{vb}, R_{vc}] \cdot [v_{pa}, v_{pb}, v_{pc}]^{T}$$

(2.26b)

Also, assuming a converter without losses, the input instantaneous

power is equal to the output instantaneous power. Therefore,

$$\mathbf{i}_{\mathbf{d}} \cdot \mathbf{v}_{\mathbf{d}} = \overline{\mathbf{i}}_{\mathcal{L}} \cdot \overline{\mathbf{v}}_{\mathbf{p}}^{\mathsf{T}} \tag{2.27}$$

replacing (2.26a) and (2.24) into (2.27),

$$\mathbf{i}_{d} \cdot \overline{\mathbf{R}}_{v} \cdot \overline{\mathbf{v}}_{p}^{\mathsf{T}} = \mathbf{i}_{d} \cdot \overline{\mathbf{R}}_{1} \cdot \overline{\mathbf{v}}_{p}^{\mathsf{T}}$$

(2.28)

An inspection of (2.28) will reveal that  $\overline{R}_{V}$  (2.26a) is identical to  $\overline{R}_{V}$  (2.24). Therefore, there is a bidirectional transfer function  $\overline{R}_{V}$  that can be applied to compute both types of dependent variables (i.e. voltage and current) in CR's.

$$R = \overline{R}_{v} = \overline{R}_{i} \tag{2.29}$$

and using (2.29) and (2.24) the bidirectional transfer function for CR becomes:

$$\bar{R} = \frac{\bar{i}_{2a}}{i_d} \tag{2.30}$$

# 2.5.3 CR Output Voltage

The output voltage of a CR can be determined using (2.26a) and the input phase voltages (normally the utility).

## 2.6 A UNIFIED FUNCTIONAL MODEL FOR VSI; CSI AND CR.

The functional commonality between VSI, CSI and CR together with the set of input output relations developed throughout sections (2.3), (2.4) and (2.5), are used in this section to show that a single model exists which can be used to describe the behaviour of this family of ac/dc converters.

#### 2.6.1 Common Transfer Function.

The objective of this subsection is to show that the transfer functions derived earlier for each one of the VSI, CSI and CR converters ((2.12),(2.21),(2.30)) have been deliberately chosen to be identical. The advantage of such choice is that for analysis purposes all three types of converters merge into one, thus simplifying their analyses and designs.

To establish that the defined transfer functions are realizable the following (intuitively true) axiom is introduced "For any given transfer function whose resulting dependent current/voltage waveforms do not violate respective Kirchhof's laws, it is always possible to find a converter topology to implement the subject transfer function". Therefore, for each converter type under consideration (i.e. CR, CSI and VSI) there is at least one converter topology that can be used to realize a valid (i.e. respecting Kirchhof's laws) transfer function.

For a given modulation technique (e.g. sine PWM) the transfer functions defined by eqns.(2.12), (2.21) and (2.30), as the ratio of the dependent line PWM variable and the input dc independent variable,

are the normalized line PWM patterns of the given modulation, and thereby, the subject transfer functions are identical for such modulation. Therefore, for a valid line PWM pattern,

$$\overline{H} = \overline{S} = \overline{C} = \overline{R}$$

(2.31)

Any valid line to line pattern (i.e. one where the instantaneous sum of the line variables is equal to zero) will define a realizable transfer function  $\bar{H}$ . Therefore applying the axiom, it will be always possible to find a topology for a CR, a CSI or a VSI which implements  $\bar{H}$ . It is worth noting that  $\bar{H}$  can be used for both—steady state—and transient converter analysis.

From a classical viewpoint a common transfer function applicable to the analysis of VSI, CSI and CR is an unexpected result. However, this result is consistant with the functional classification of power converters (Table(2.2)). Moreover, from a practical viewpoint, and as mentioned earlier, a common transfer function enables the simultaneous analysis, design, and comparison of these converter types with the aid of a single functional—model.

#### 2.6.2 The Functional Model.

With a common transfer function H the expressions developed in sections (2.3), (2.4) and (2.5) relating dependent and independent variables constitute the basis of the common converter model. An additional step is to define a per-unit system (Table (2.3)) which allows the computation of per-unit generalized input-output waveforms.

As a result of this per-unit choice and the common transfer function (2.31), the one-to-one correspondence for all dependent and independent variables becomes more apparent.

```

E = 1 pu , VSI input voltage I = 1 \text{ pu} \qquad , \text{ CSI input and CR output current} Z(w_o) = 1 \text{ [}\emptyset \text{ pu} \qquad , \text{ fundamental load impedance (Fig.(2.2) and (2.3))} V_p = a_1 \sqrt{3} \qquad , \text{ magnitude of mains phase voltage} a_1(\text{SPWM}, \text{M=1}) = \sqrt{3}/2 \text{ , Appendix 1} a_1(\text{MSPWM}, \text{M=1}) = 1 \text{ , Appendix 1}

```

Table (2.3): Per-Unit System

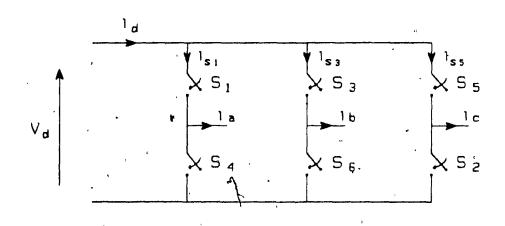

Table (2.4) shows the common ac/dc normalized (in per-unit) functional model. This table presents general relations suitable for transient analysis (rows a and b) and simplified expressions valid for steady state conditions (rows c,d and e). To further illustrate the relevance of the simplified steady state relationships (and respective typical waveforms) a block diagram of the functional model valid for steady state is presented in Table (2.5).

The functional model of Table (2.4) has been developed by also assuming:

- i) ideal semiconductors,

- ii) negligible stray circuit resistance, inductance, and

| $\overline{\mathbf{v}}_{g}(\mathbf{t}) = \overline{\mathbf{H}}(\mathbf{t})$ $\overline{\mathbf{i}}_{g}(\mathbf{t}) = \overline{\mathbf{H}}(\mathbf{t} - \mathbf{t})$ $\overline{\mathbf{v}}_{p}(\mathbf{t}) = \overline{\mathbf{H}}_{1}(\mathbf{t} + \mathbf{t})$  | $(2.8)^{\circ} \stackrel{\cdot}{v_{p}} (t)$ $v_{d}(t) = i (t) \cdot \stackrel{\cdot}{v_{p}} (t)$ $(2.8)$ $(2.17)$ | $(2.5)  i_{\hat{y}} = \overline{\Pi}(t) \cdot 1_{\hat{d}}(t) $ (2.15)<br>(2.15)<br>(2.24) G                       | CSI CR                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\bar{\mathbf{v}}_{g}(\mathbf{t}) = \bar{\mathbf{H}}(\mathbf{t})$ $\bar{\mathbf{i}}_{p}(\mathbf{t}) = \bar{\mathbf{H}}_{1}(\mathbf{t} - \mathbf{\tau})$ $\mathbf{i}_{d}(\mathbf{t}) = \bar{\mathbf{H}} \cdot \bar{\mathbf{H}}_{1}^{T}(\mathbf{t} - \mathbf{\tau})$ |                                                                                                                   | $i_d(\vec{z}) = \vec{H}(t) \cdot \vec{i}_p^T(t)$ $v_d(t) = \vec{H}(t) \cdot \vec{v}_p^T(t)$ $v_d(t) = \vec{H}(t)$ | $\overline{i}_{\ell_p} = \overline{\mathbb{H}}(t) \cdot i_{d}(t) \qquad \qquad$ |

$\tau = \frac{\phi}{\omega_0}$   $\phi$ : displacement angle introduced by the load impedance.

TABLE 2.4: Functional model for the ac/dc conversion function.

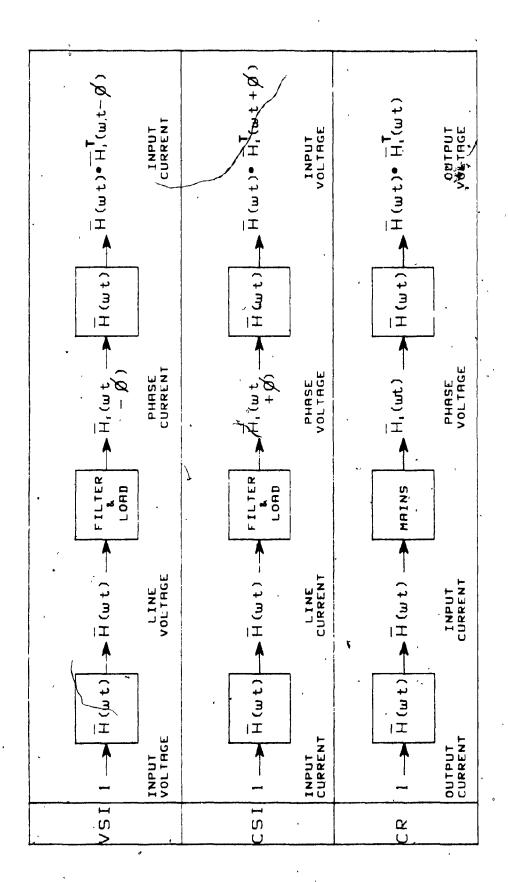

Table (2.5): Steady state block diagram of the functional model presented in Table (2.4).

なる 一日本語 日本語 日本日本語の

capacitance,

- iii) ideal operation of the converter control circuitry (perfect implementation of PWM techniques),

- iv) balanced (amplitude and phase) sinusoidal ac input voltages.

Furthermore, the explicit expressions for VSI and CSI input dependent variables ( $i_d$  and  $v_d$ ) are valid only under steady state ((2.14) and (2.23)). From a practical standpoint, the above set of assumptions doesn't constitute a severe restraint. In fact, in most of the situations the model describes the converter behaviour (and associated typical input-output waveforms) with a good degree of precision [21].

## 2.6.3 Generalized Converter Input-Output Waveforms

As stated in section (2.3.3) steady state waveforms provide the basic information to describe the converter behaviour, evaluate PWM techniques, design the input-output filter, and to specify the converter switch ratings.