Acquisitions and Bibliographic Services Branch

395 Weilington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votre reterence

Our file. Notice references

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

# **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle. de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Design of a Fast Adder Accumulator

Hala Tabl

A Thesis

in

The Department

oſ

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements for the Degree of Master of Engineering at Concordia University

Montréal, Québec, Canada

July 1990

© Hala Tabl, 1990

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votre reference

Our life. Notre reférence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive à Bibliothèque permettant la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-80986-8

#### ABSTRACT

# DESIGN OF A FAST ADDER ACCUMULATOR

The design of a pipelined adder accumulator is given. Pipelining is achieved both at the macro and micro level. The method is applied in the design of a 24-bit adder accumulator capable of adding 64K 8 bit words. The circuit is used as a threshold generator in a multi-processor image processing system. The adder is implemented in a new non standard domino logic, namely, MULTIPLE OUTPUT DOMINO LOGIC, with mixed dynamic and static logic.

Furthermore the overall circuit is modified to achieve a degree of fault tolerance. Fault tolerance is achieved through hardware redundancy. In our fault tolerance approach, new designs are introduced through duplication to achieve error correction, without resorting to traditional Triple Module Redundancy (TMR).

## **ACKNOWLEDGMENTS**

My deepest thanks and gratitude goes to my supervisor Dr. A. J. AlKhalili, for his support, encouragement, and guidance, throughout the whole work. His helpful suggestions and discussions made the realization of this work possible.

My thanks also goes to Mr. D. Hargreaves and Mr. G. Patel, of the VLSI Design Lab., for providing the environment that helped in the completion of this work.

# TABLE OF CONTENTS

| LIST OF FIGURES                                | vii |

|------------------------------------------------|-----|

| CHAPTER 1: INTRODUCTION                        | 1   |

| CHAPTER 2: DESIGN OF A 24BIT ADDER ACCUMULATOR | 4   |

| 2.1 Introduction                               | 4   |

| 2.2 Threshold Generator                        | 4   |

| 2.3 Adder Accumulator Design                   | 5   |

| 2.4 Adder Accumulator Functionality            | 9   |

| CHAPTER 3: ADDERS DESIGN                       | 14  |

| 3.1 Introduction                               | 14  |

| 3.2 Multiple Output Domino Logic               | 15  |

| 3.3 A 4-Blt MODL Adder                         | 16  |

| 3.4 A Full 4-Bit MODL Adder                    | 18  |

| 3.5 Comparison                                 | 26  |

| 3.8 Simulating the Adder Accumulator           | 40  |

| CHAPTER 4: FAULT ANALYSIS                      | 47  |

| 4.1 Introduction                               | 47  |

| 4.2 Fault Characterization                     | 47  |

| 4.3 Fault Model                                | 48  |

| 4.4 Fault Models for 4-Bit Partial Adder       | 48  |

| 4.5 Fault Models for Full 4-Bit Adder          | 51  |

| CHAPTER 5: FAULT TOLERANT ADDERS' DESIGN       | 55  |

| 5.1 Introduction                               | 55  |

| 5.2 Fault Tolerance Techniques                  | <b>5</b> 5 |

|-------------------------------------------------|------------|

| 5.3 Design of a Fault Tolerant 4-Bit Adder      | 57         |

| 5.4 Design of a Fault Tolerant Full 4-Bit Adder | 92         |

| CHAPTER 6: CONCLUSION                           | 124        |

| REFERENCES                                      | 125        |

| APPENDIX A                                      | 128        |

| APPENDIX B                                      | 139        |

| APPENDIX C                                      | 141        |

# LIST OF FIGURES

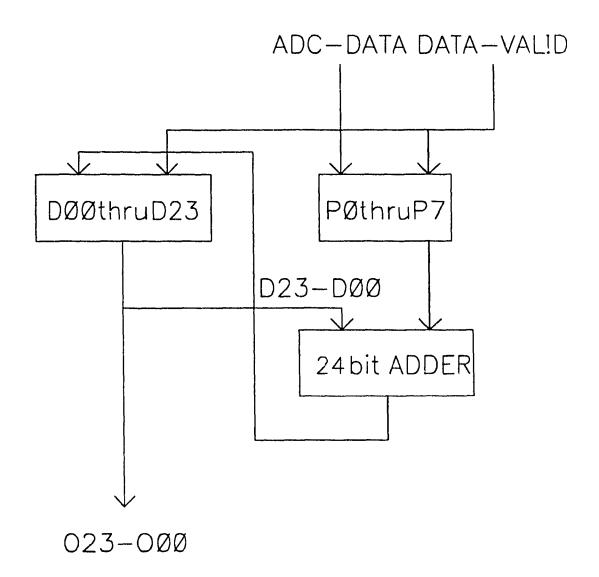

| Fig.2.1   | Single stage adder accumulator              | 6  |

|-----------|---------------------------------------------|----|

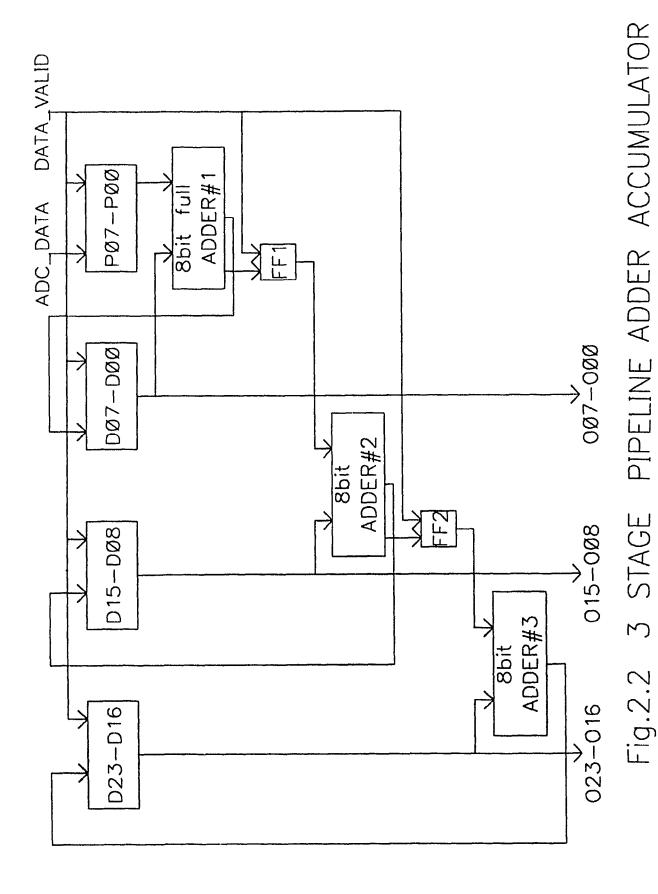

| Fig.2.2   | 3 Stage pipeline adder accumulator          | 7  |

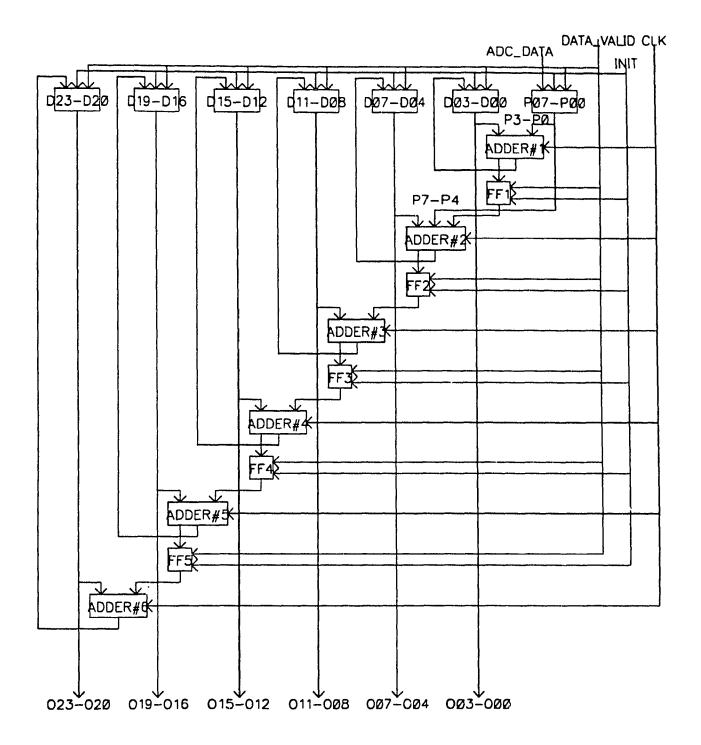

| Flg.2.3   | 6 Stage pipeline adder accumulator          | 8  |

| Flg.2.4   | Results propagation through pipeline        | 11 |

| Fig.2.5   | Computation steps in adder accumulator      | 13 |

| Flg.3.1   | 4-Bit partial MODL adder                    | 17 |

| Fig.3.2   | Simulation results of 4-bit MODL adder      | 19 |

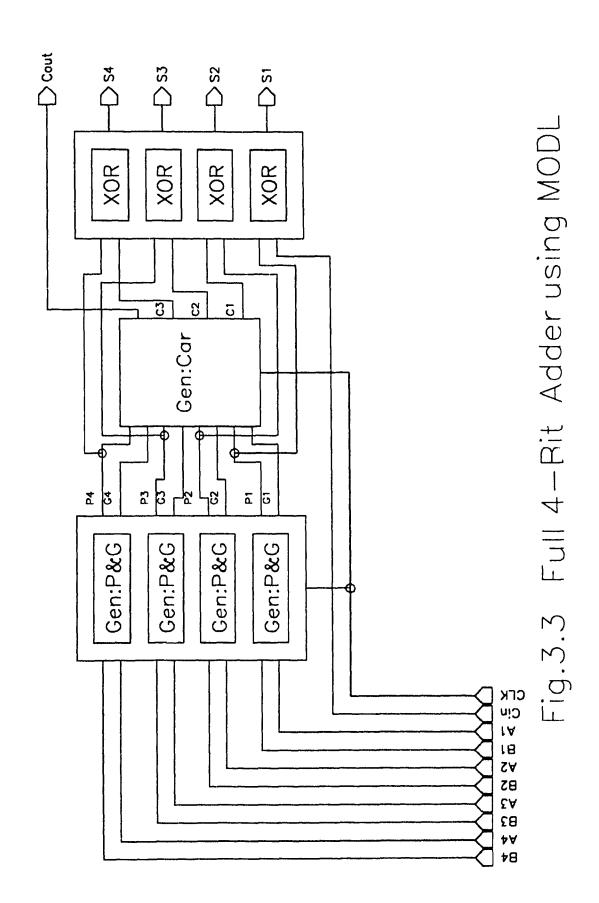

| Flg.3.3   | Overall design of full 4-bit MODL adder     | 22 |

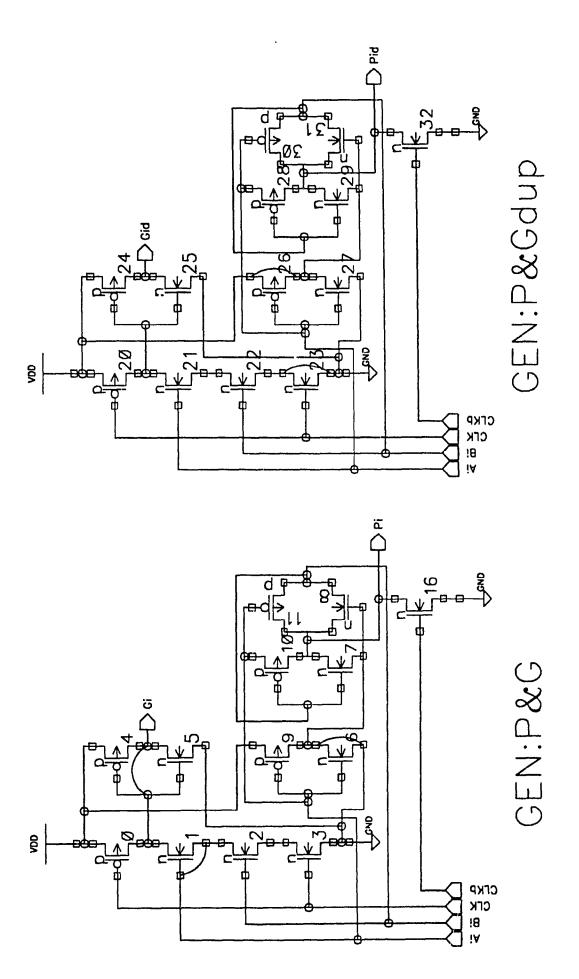

| Flg.3.4   | P&G generation unit                         | 24 |

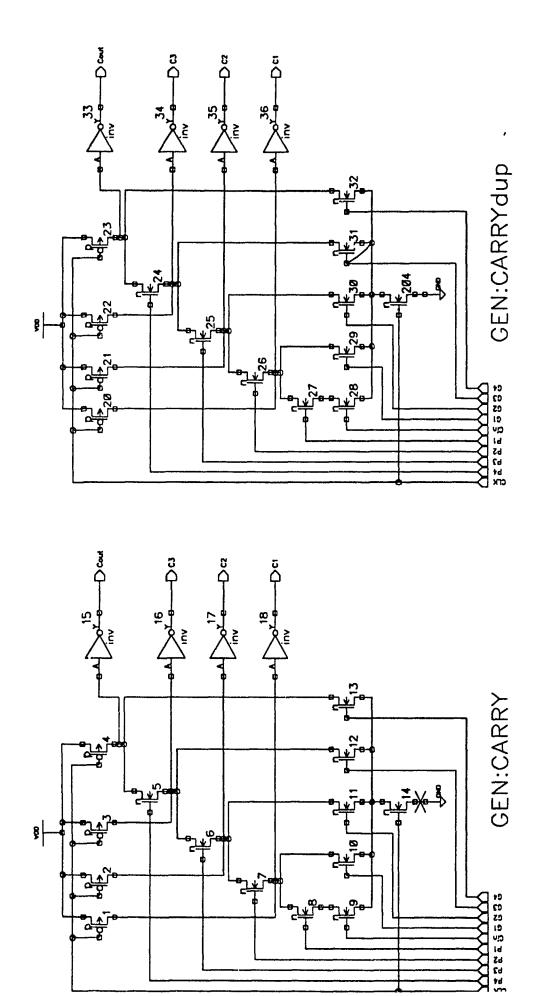

| Flg.3.5   | Carry generation unit                       | 25 |

| Fig.3.6   | Statle XOR                                  | 27 |

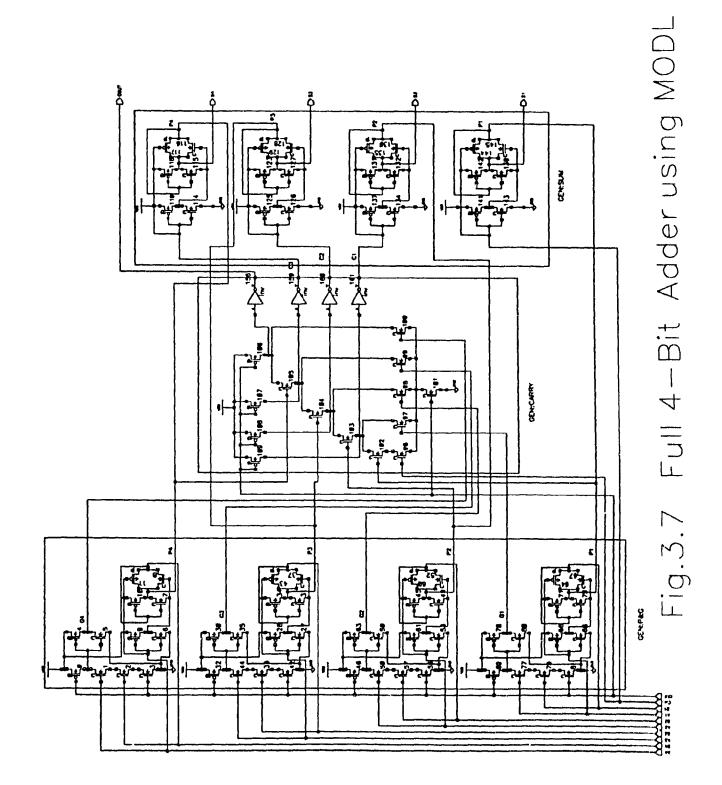

| Flg.3.7   | Full 4-bit MODL adder                       | 28 |

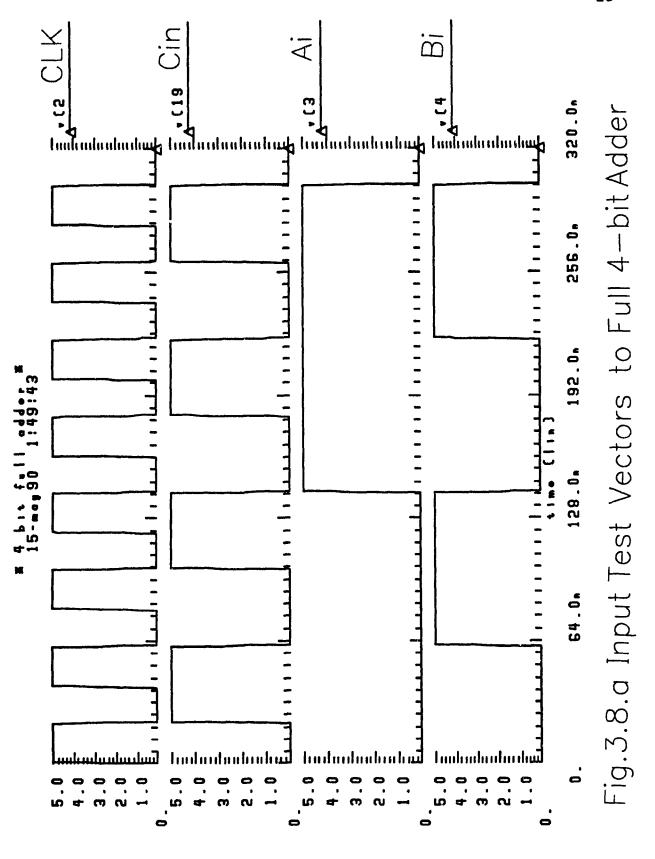

| Flg.3.8   | Simulation results of full 4-bit MODL adder | 28 |

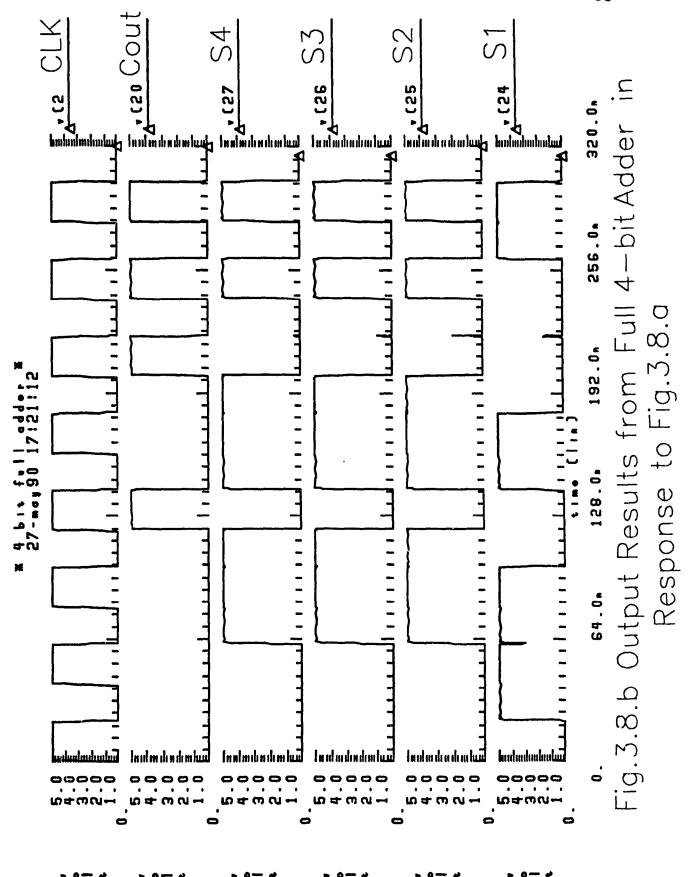

| Flg.3.9.a | Static CLA adder                            | 33 |

| Fig.3.9.b | Simulation results of static CLA adder      | 34 |

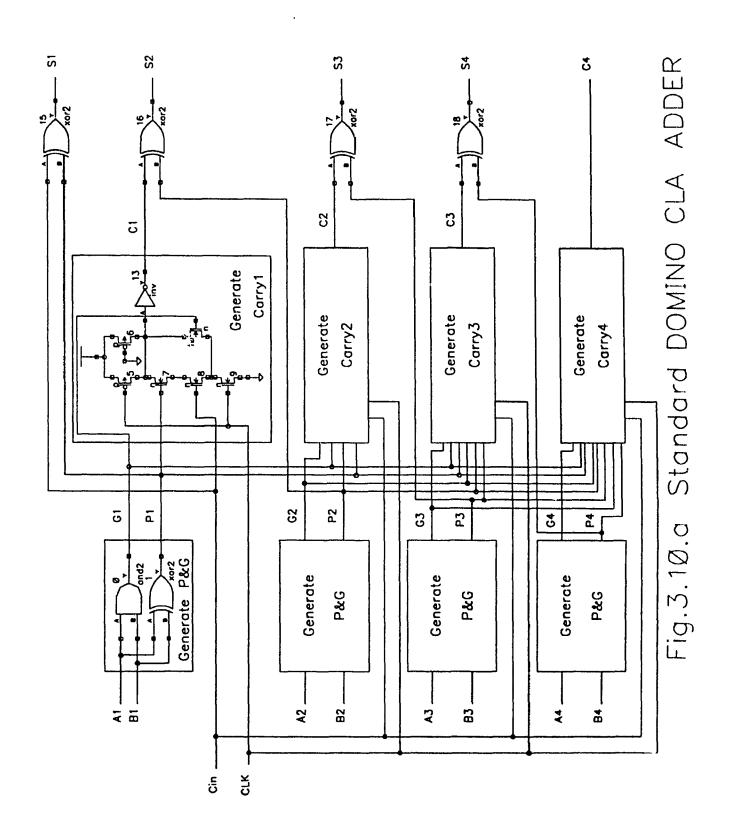

| Flg.3.10. | a Standard domino CLA adder                 | 36 |

| Flg.3.10. | b Simulation results of domino CLA adc      | 37 |

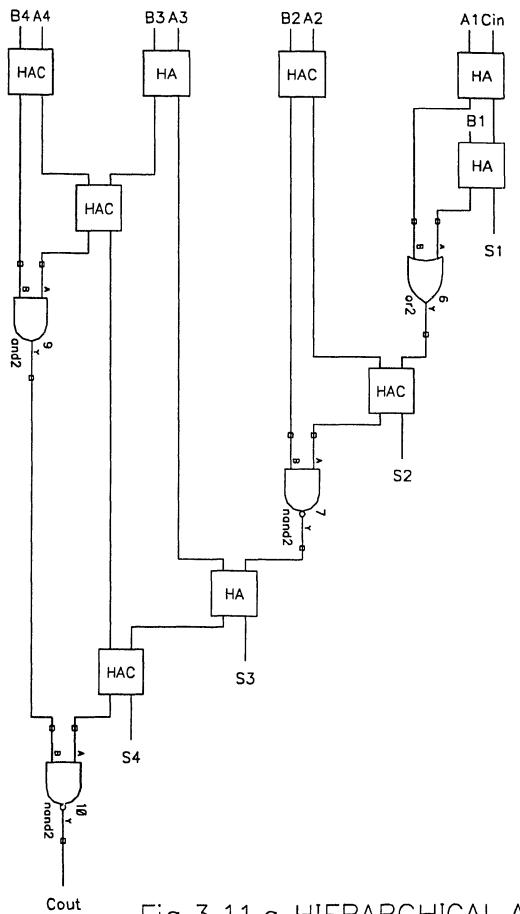

| Flg.3.11. | a Hierarchical adder                        | 38 |

| Flg.3.11. | b Simulation results of hierarchical adder  | 38 |

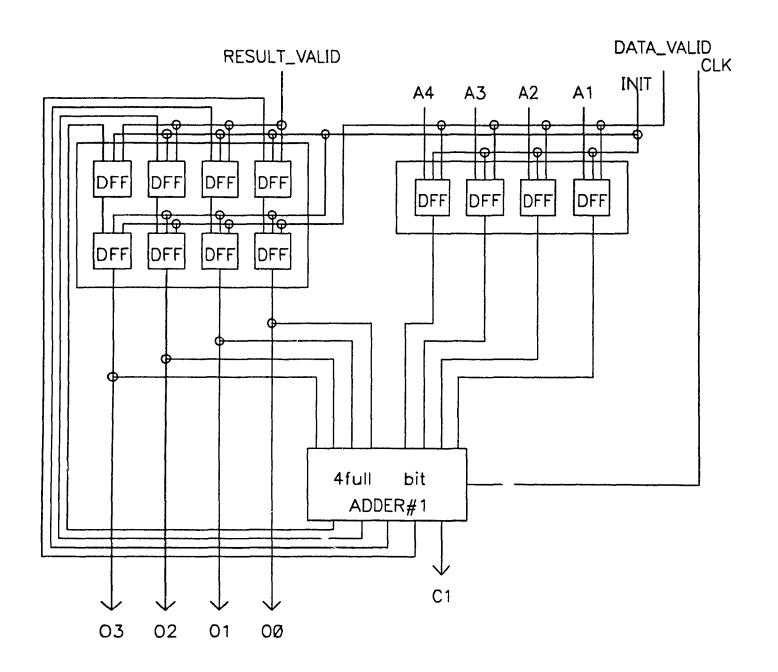

| Fig.3.12  | A stage of adder accumulator                | 41 |

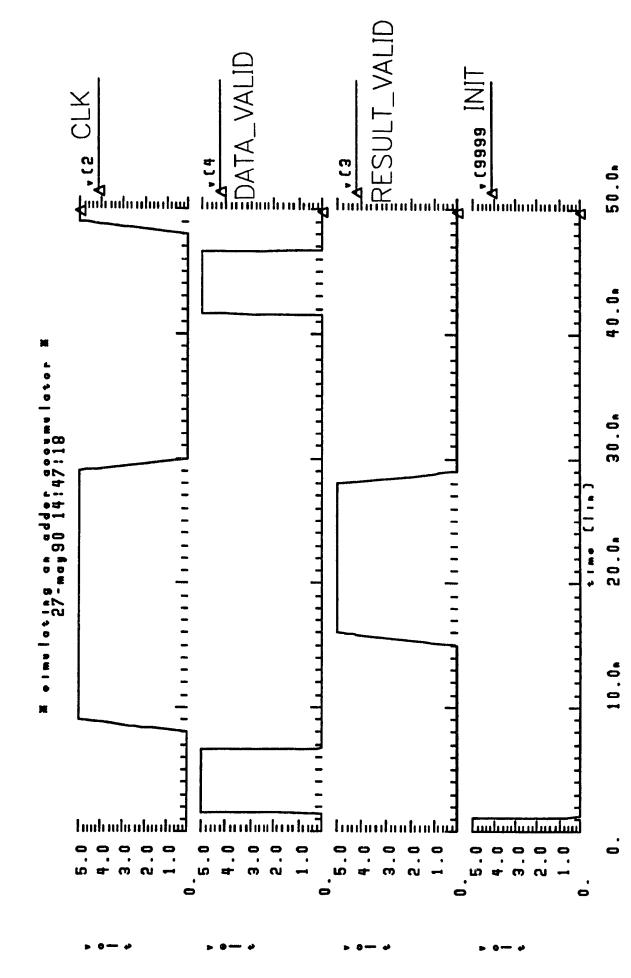

| Flg.3.13  | Timing diagram of control signals           | 42 |

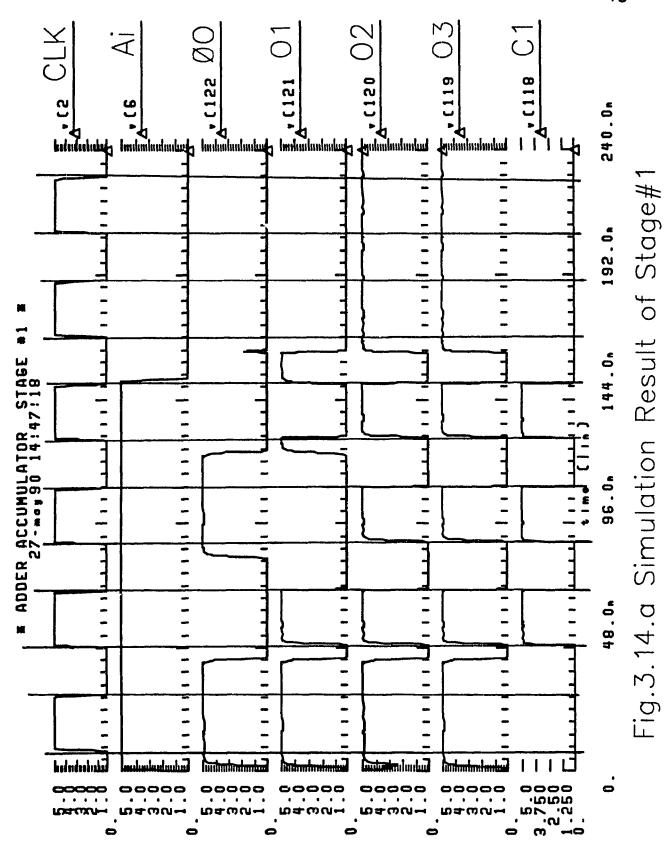

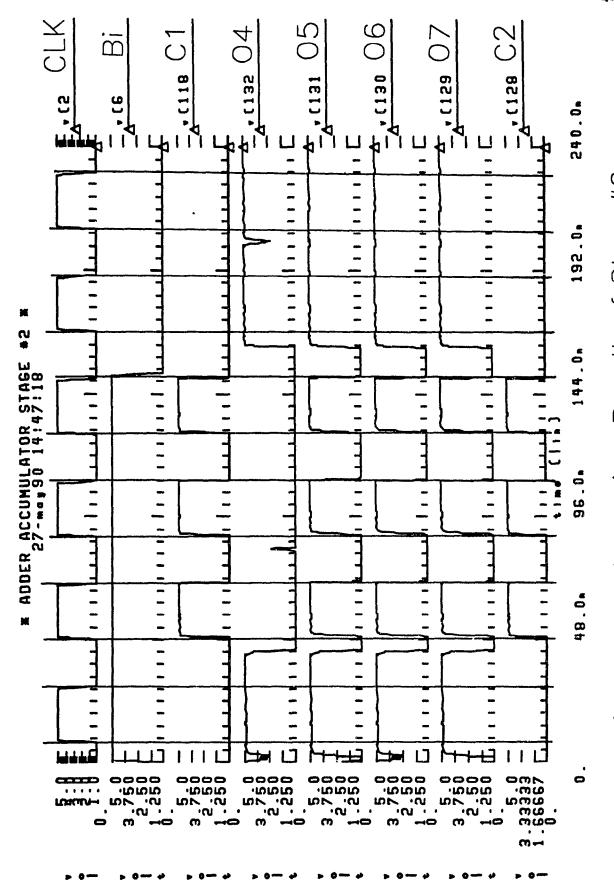

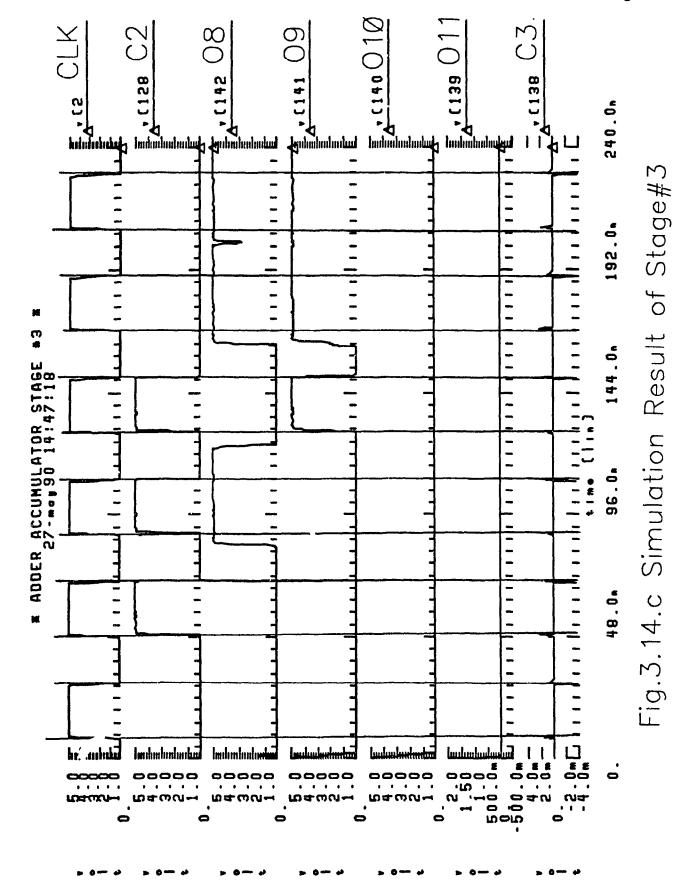

| Flg.3.14  | Simulation results of adder accumulator     | 43 |

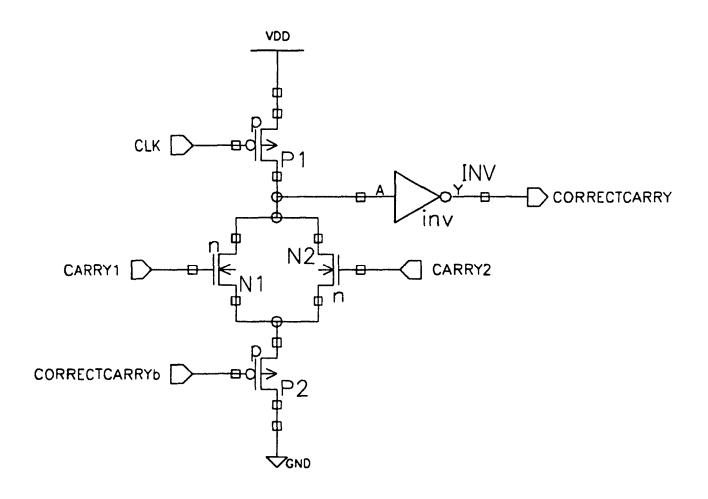

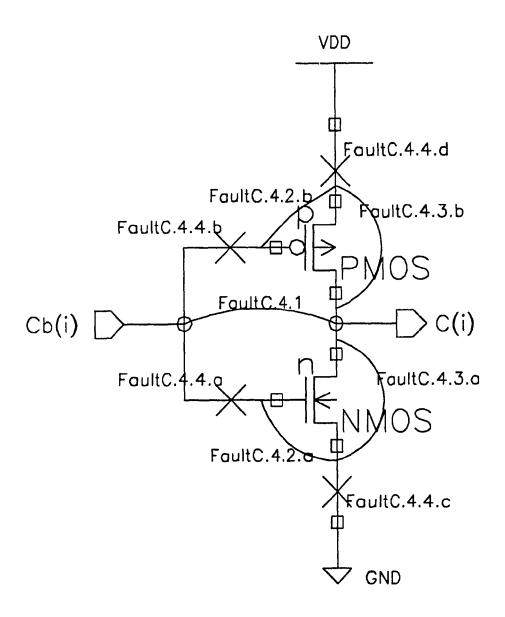

| Flg.5.1  | Carryb correction circuit                               | 80         |

|----------|---------------------------------------------------------|------------|

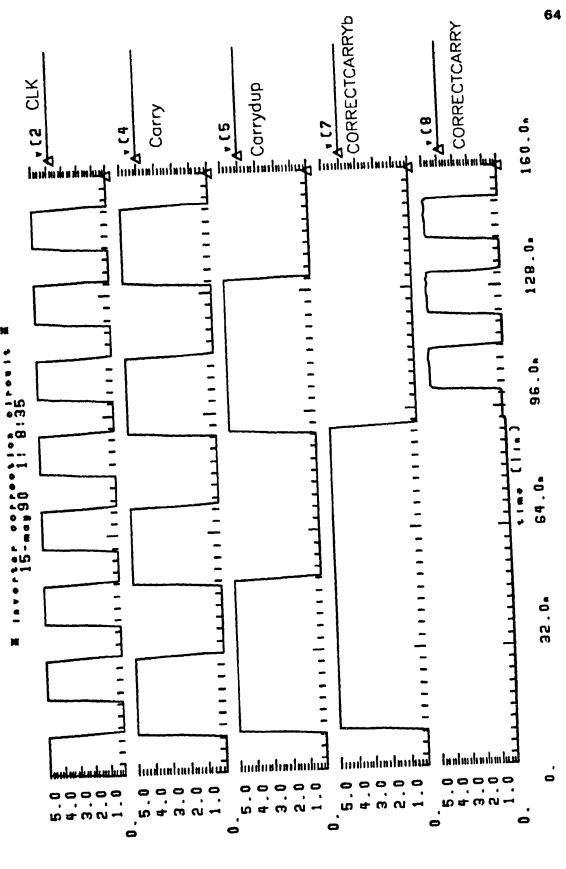

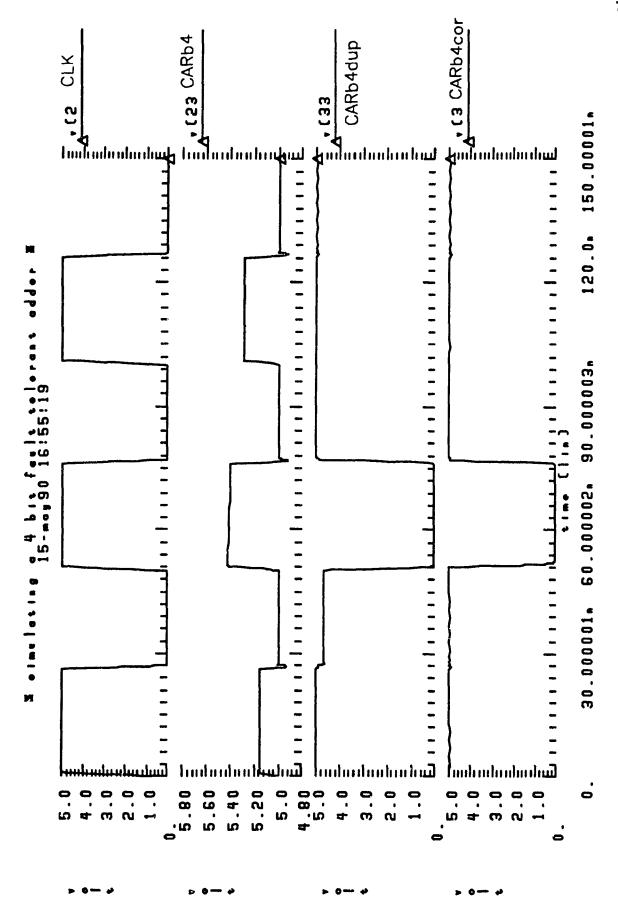

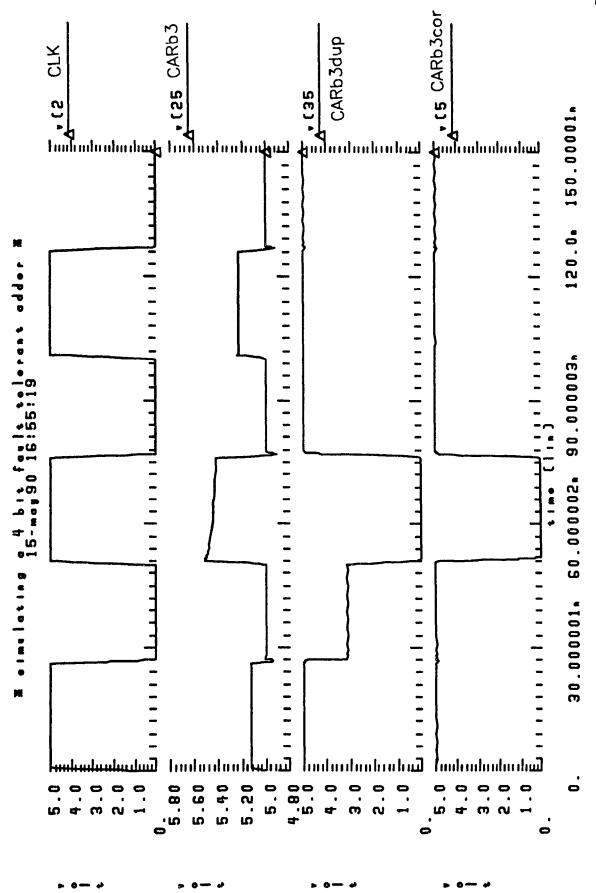

| Flg.5.2  | Simulation results of carryb correction cct.            | 62         |

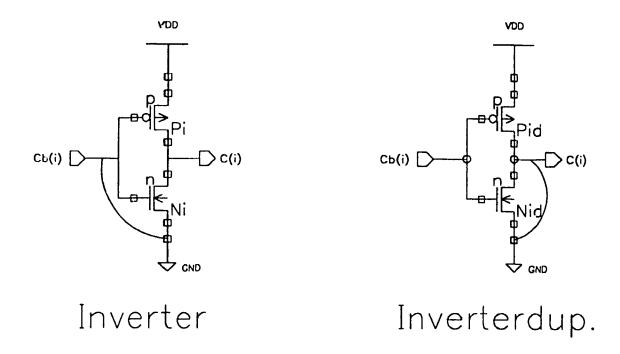

| Flg.5.3  | Inverter correction circuit                             | 63         |

| Flg.5.4  | Simulation results of inverter correction cct           | 64         |

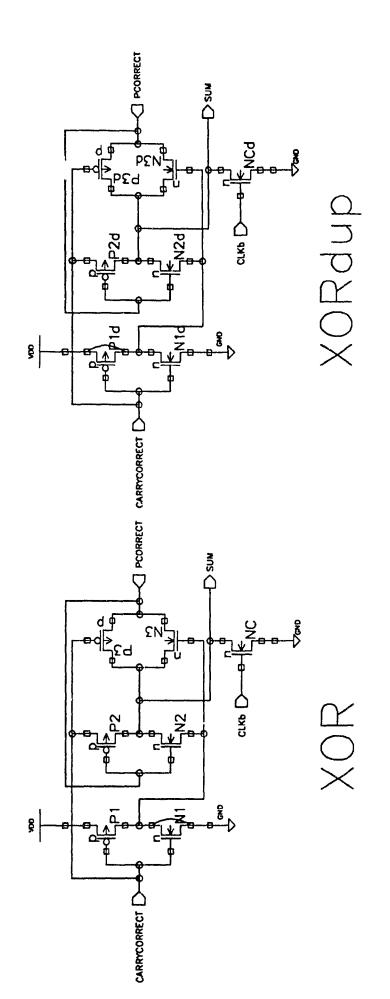

| Flg.5.5  | Modified static XOR                                     | 86         |

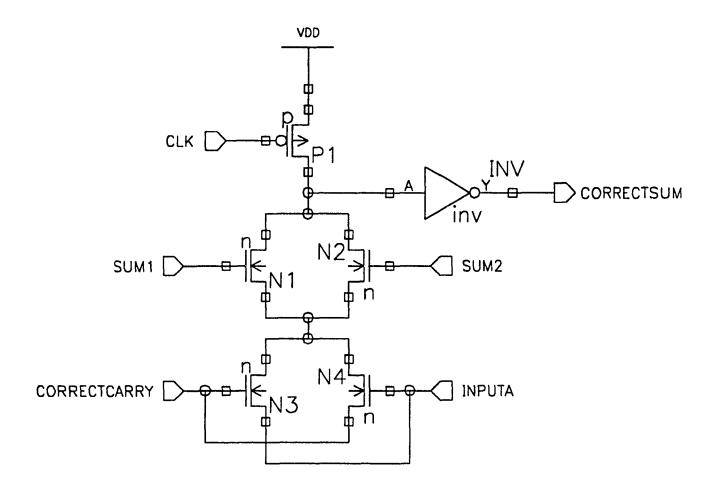

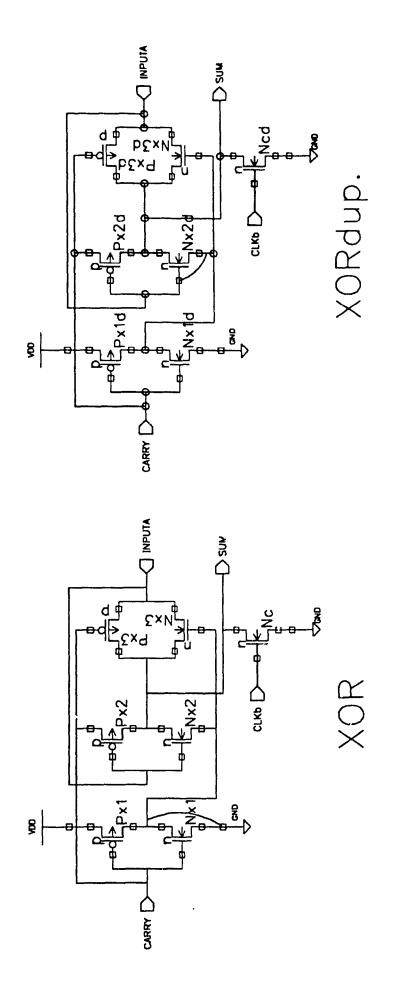

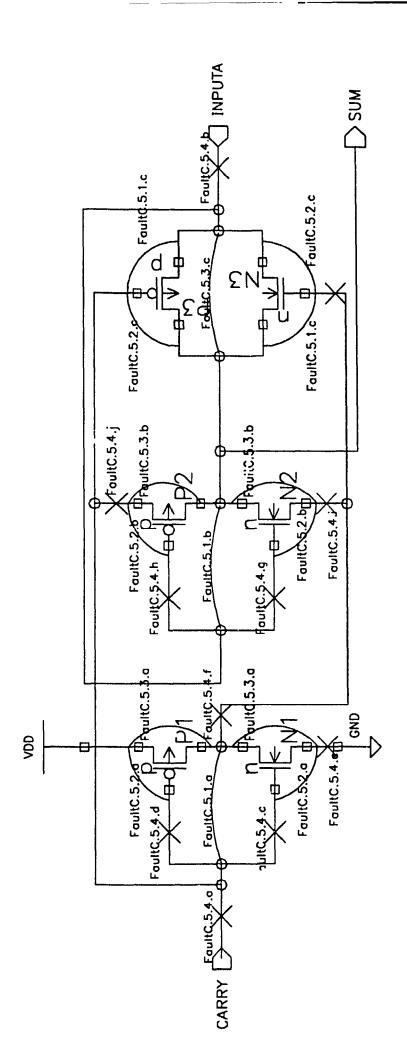

| Fig.5.6  | XOR correction circuit                                  | 67         |

| Fig.5.7  | Simulation results of XOR correction cct                | 68         |

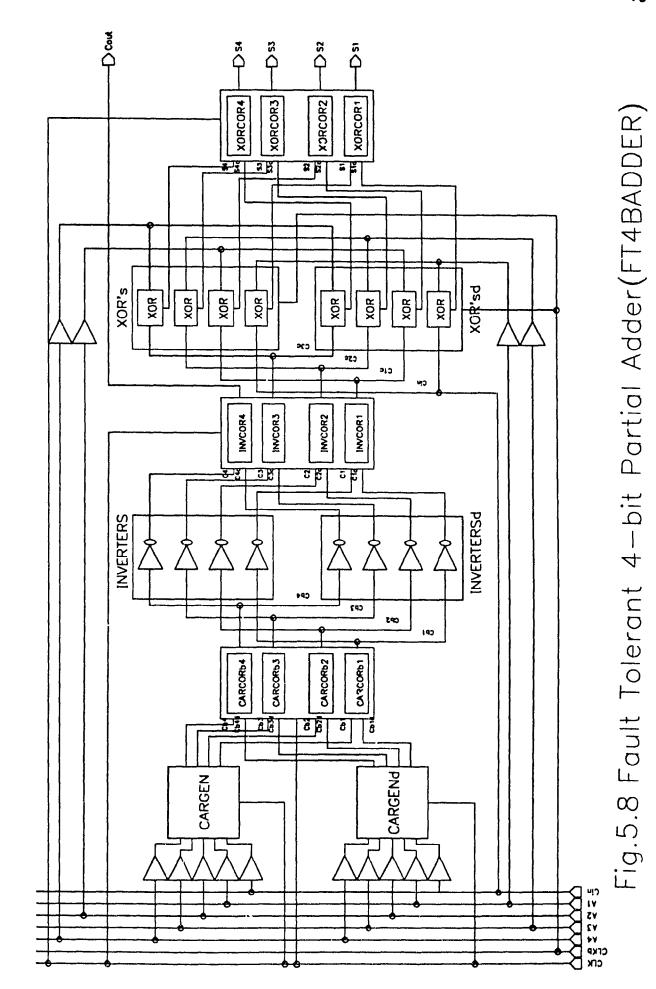

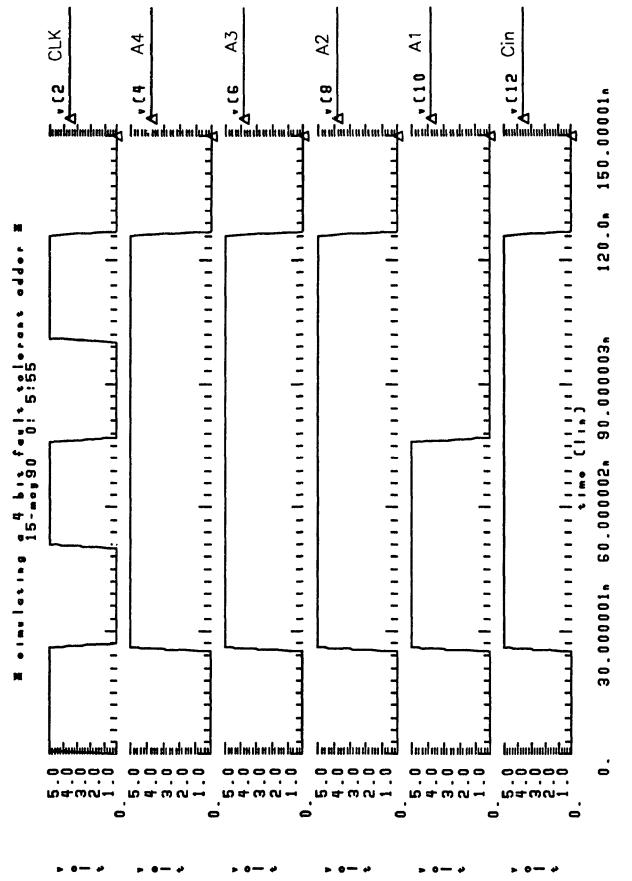

| Fig.5.8  | Fault tolerant 4-bit adder                              | 70         |

| Fig.5.9  | Simulation results of fault tolerant 4-bit adder        | 71         |

| Flg.5.10 | Simulated faults in carryb generation block             | 74         |

| Flg.5.11 | Simulated faults in inverter block                      | <b>7</b> 5 |

| Flg.5.12 | Simulated faults in XOR block                           | 76         |

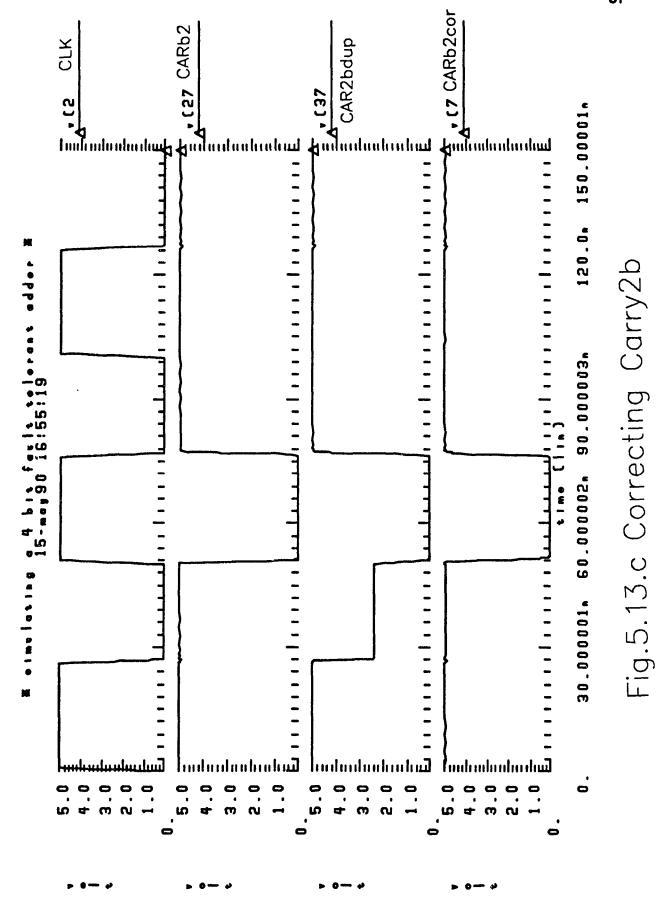

| Fig.5.13 | Simulation results of correcting carryb block's outputs | 79         |

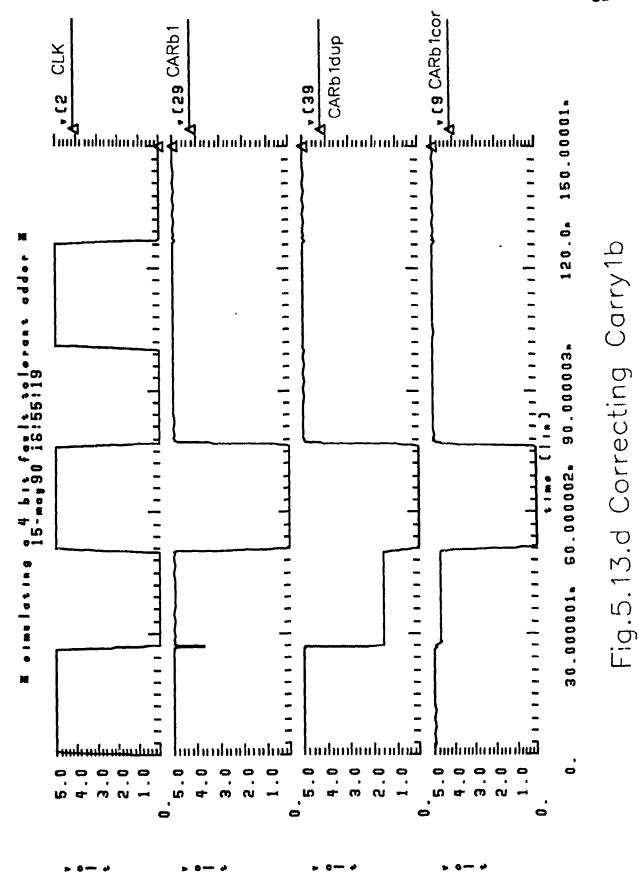

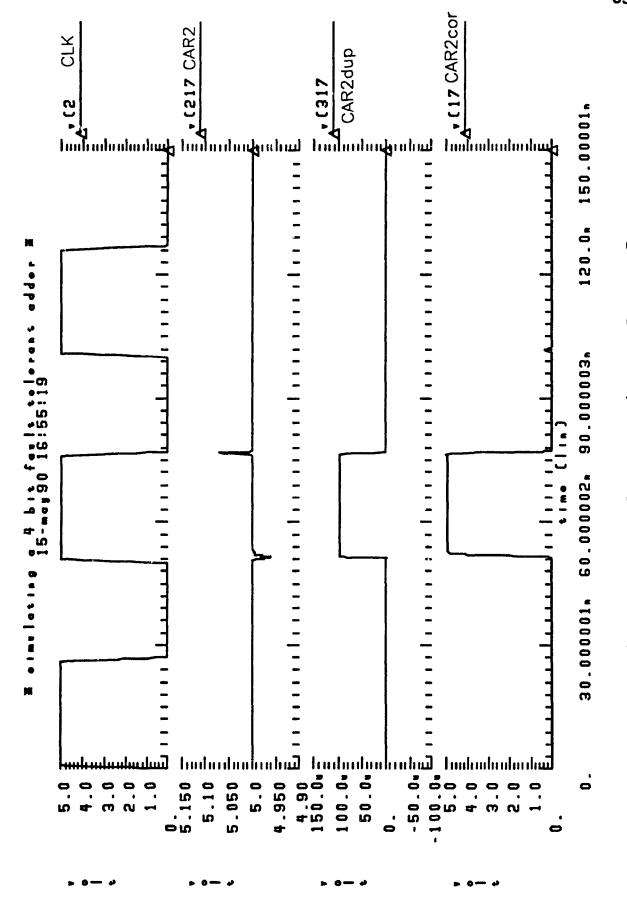

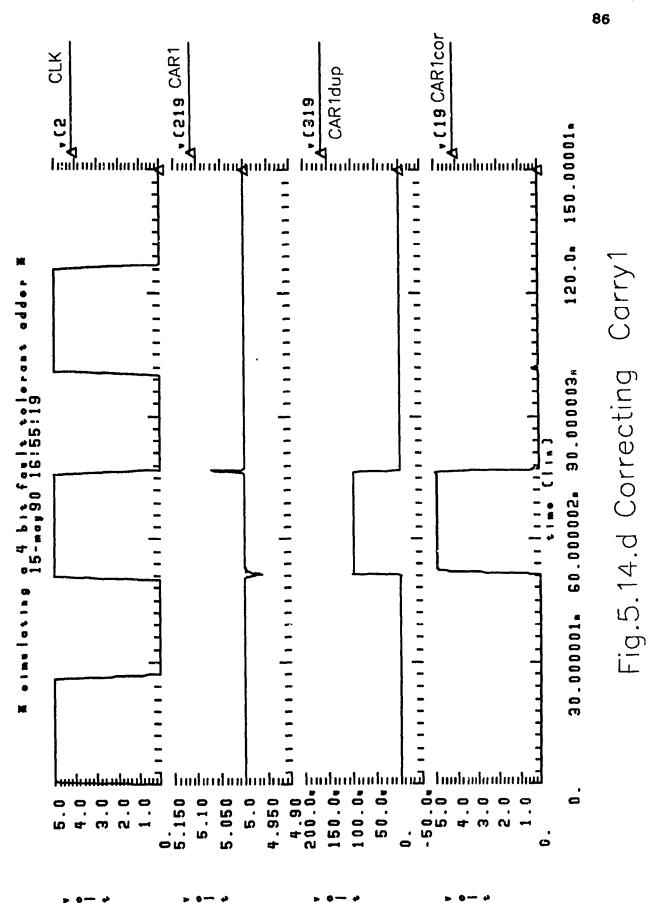

| Flg.5.14 | Simulation results of correcting inverters' outputs     | 83         |

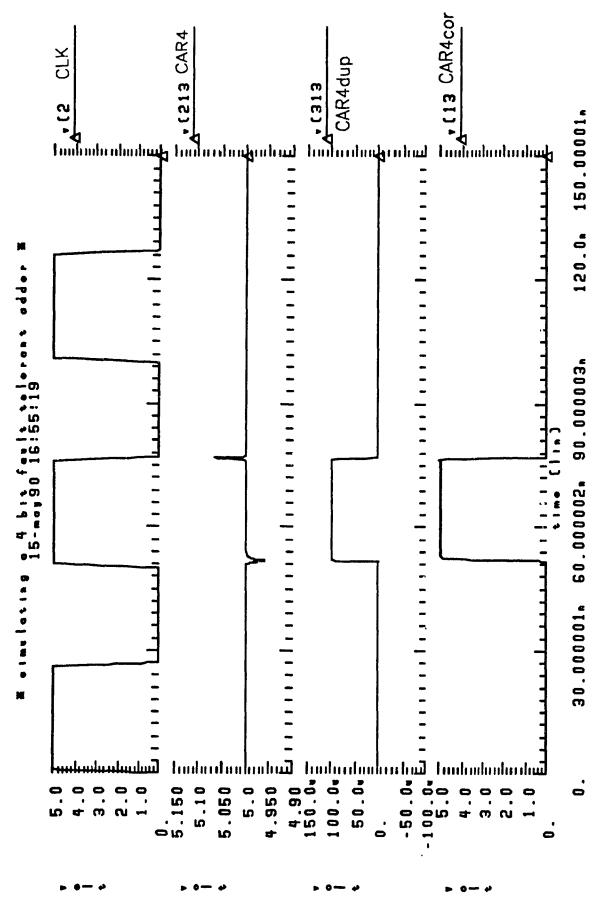

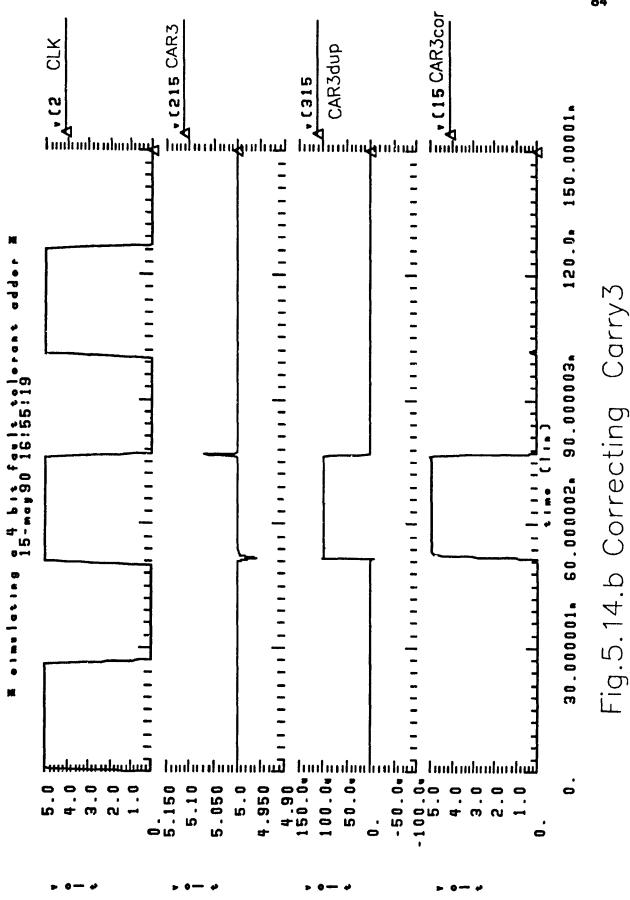

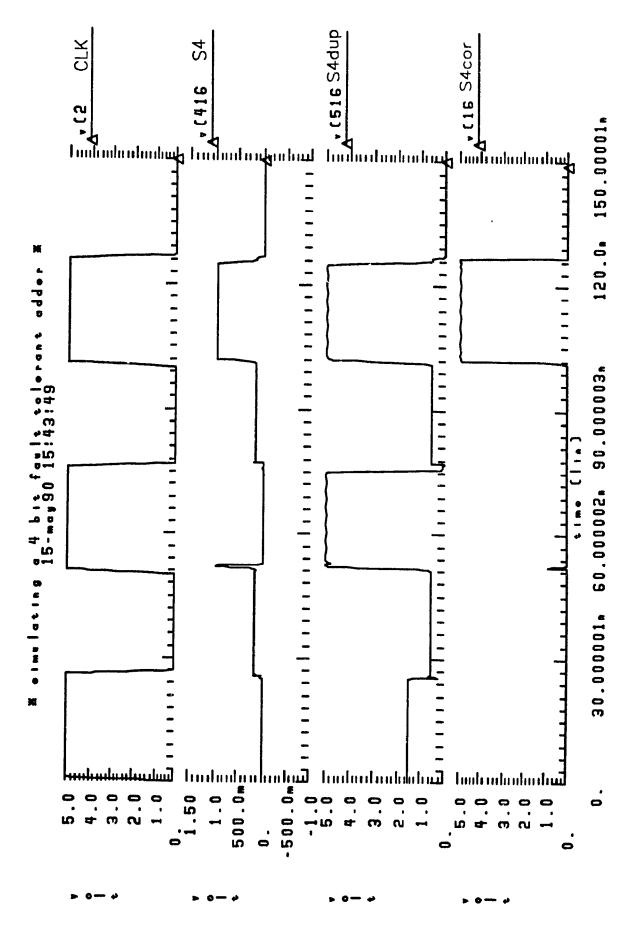

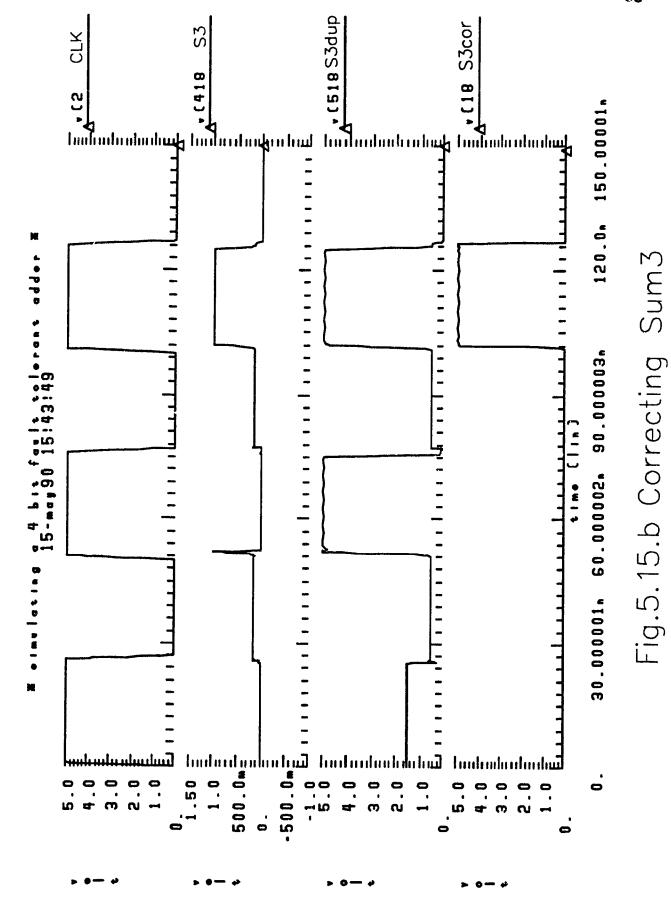

| Flg.5.15 | Simulation results of correcting XORs' outputs          | 87         |

| Flg.5.16 | Overall results of correcting faults in 4-bit adder     | 91         |

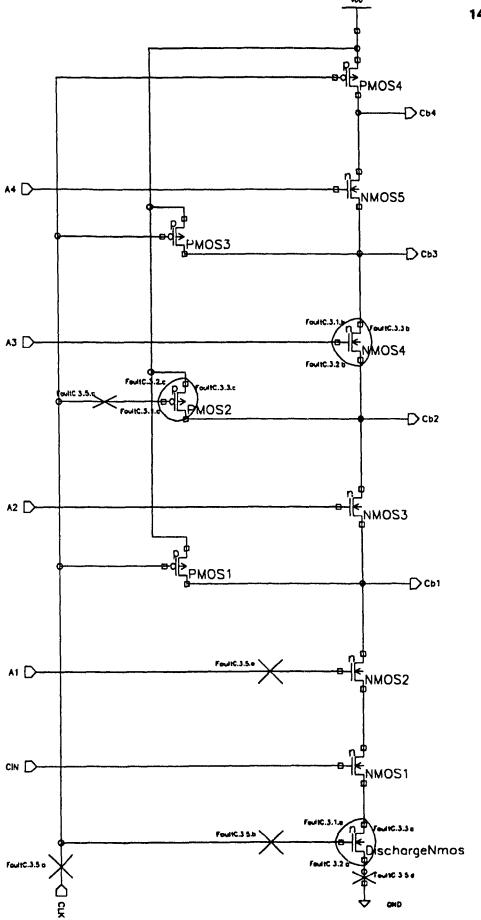

| Flg.5.17 | Gen:P&G correction circuit                              | 94         |

| Flg.5.18 | Simulation results of Gen:P&G correction cct            | 96         |

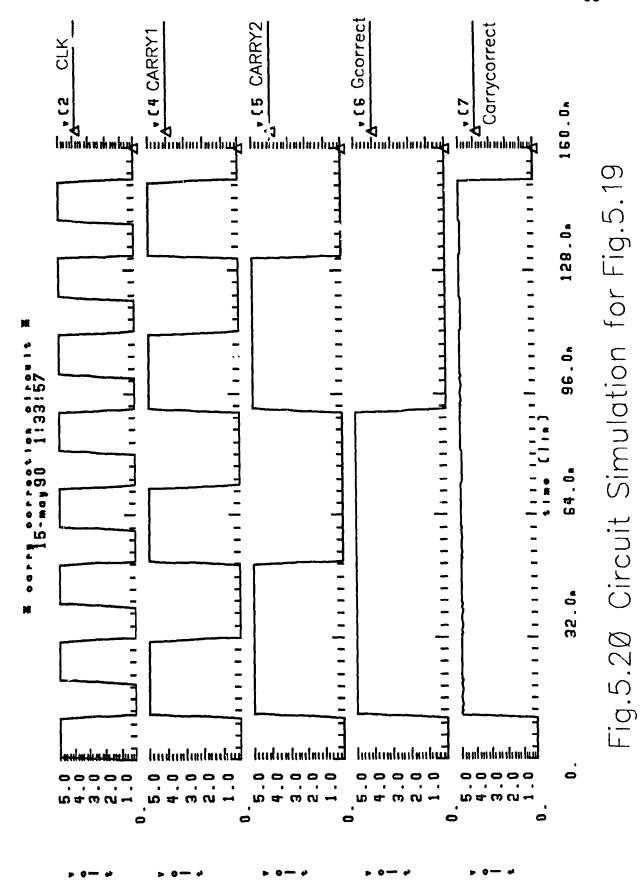

| Fig.5.19 | Gen:Car correction circuit                              | 98         |

| F1g.5.20 | Simulation results of Gen:Car correction ect.           | 86         |

| Fig.5.21 | Fault tolerant full 4-bit adder                         | 101        |

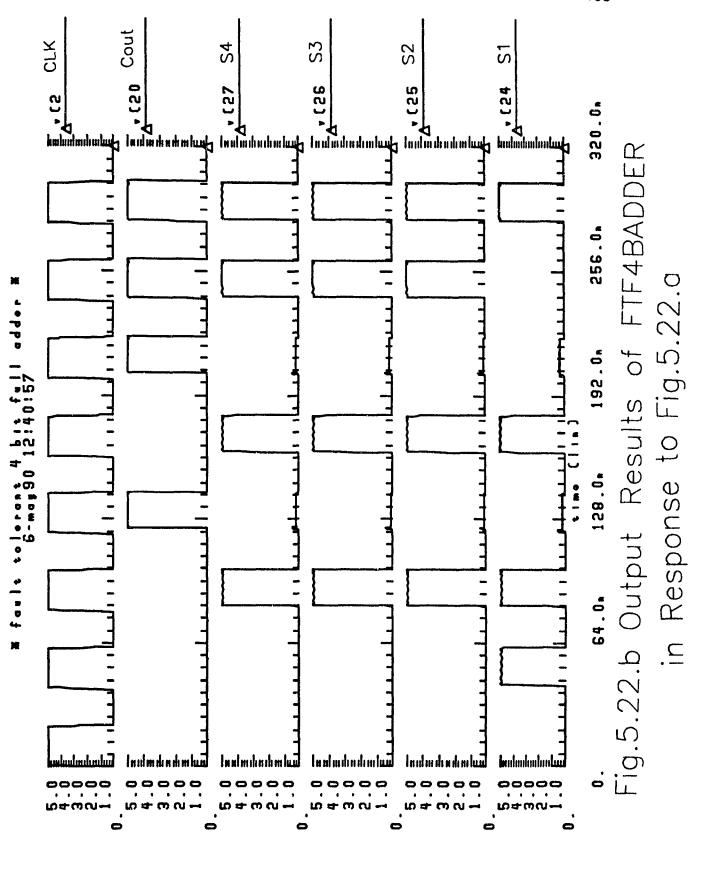

| Flg.5.22 | Simulation results of fault tolerant full 4-bit adder   | 102        |

| F1g.5.23 | Faults in Gen:P&G block                                 | 105        |

| F1g.5.24 | Faults in Gen:Car block                                 | 106        |

| Flg.5.25 | Faults in XOR block                                      | 107 |

|----------|----------------------------------------------------------|-----|

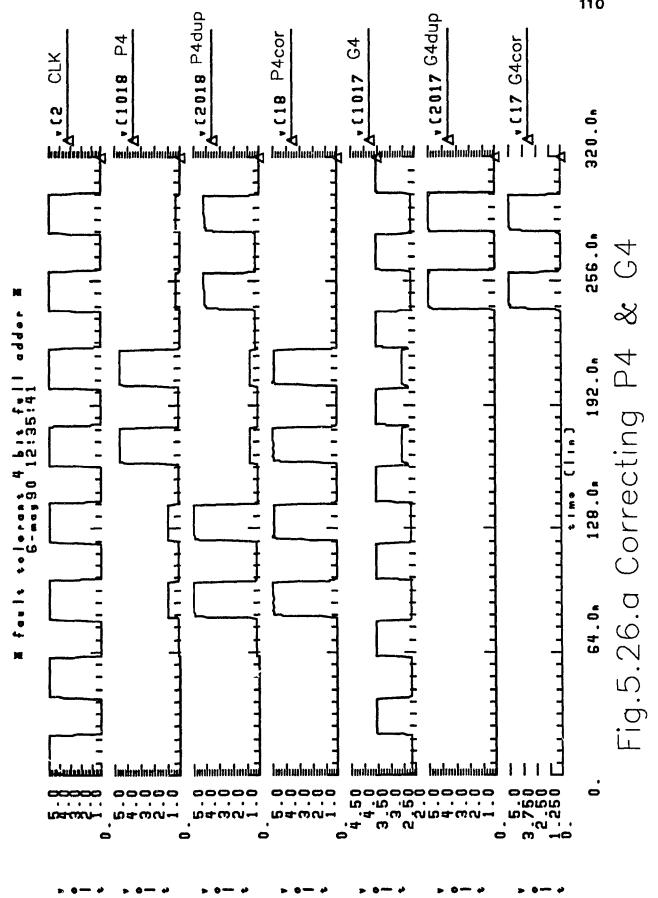

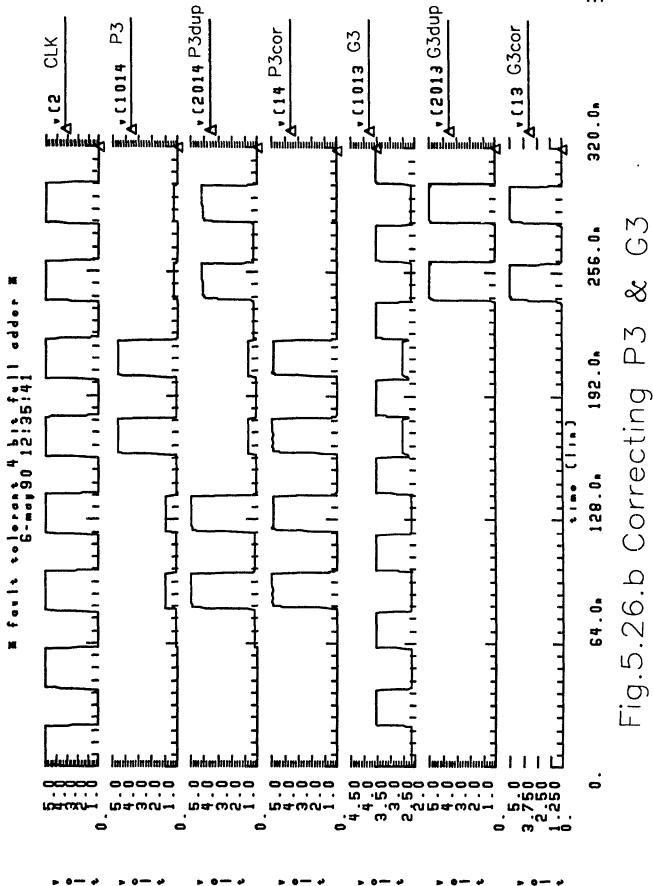

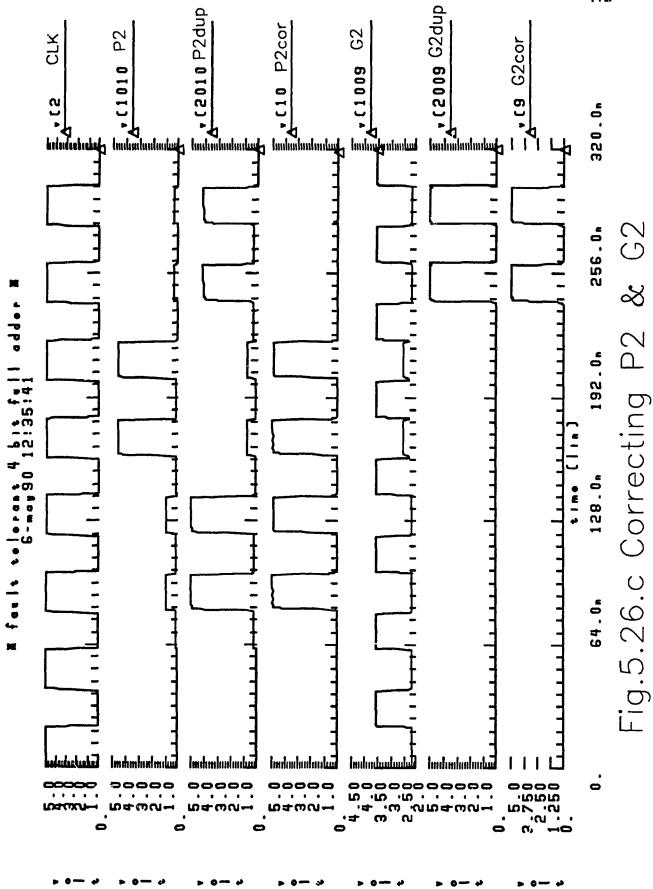

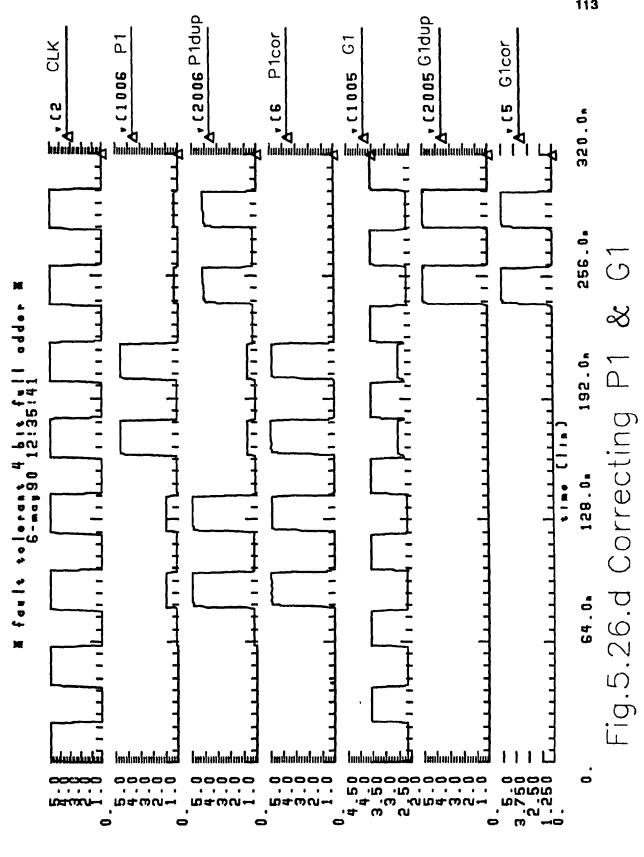

| F1g.5.26 | Simulation results of correcting Gen:P&G blocks' outputs | 110 |

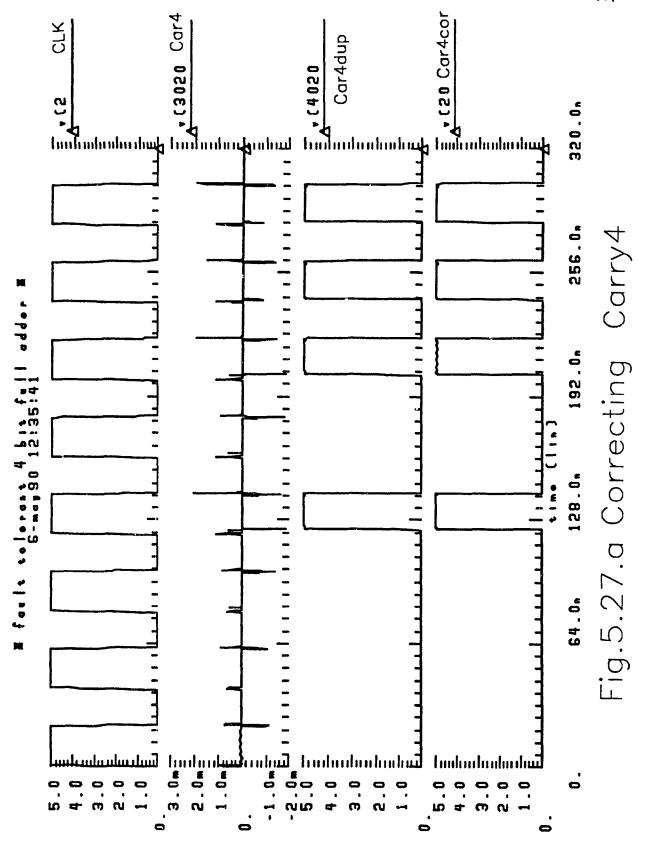

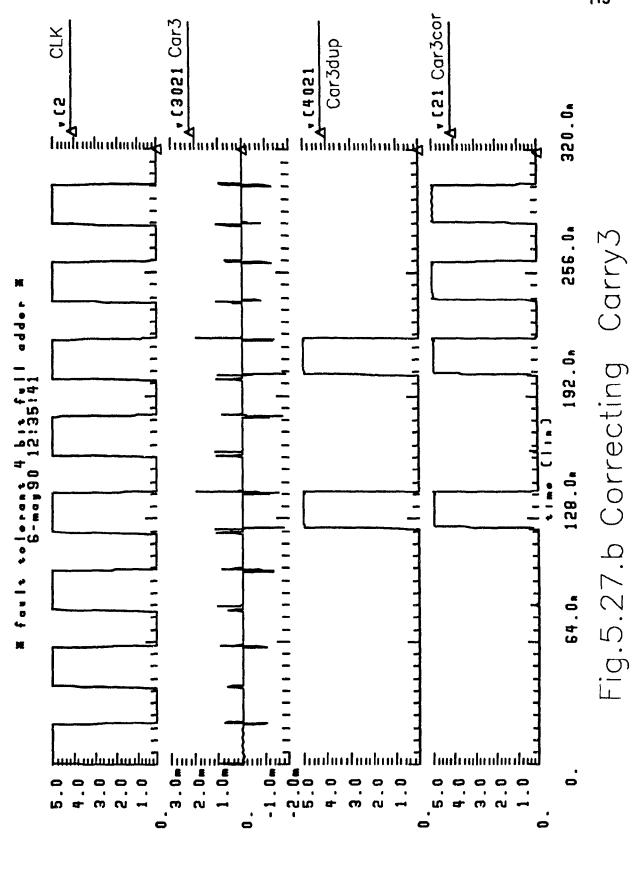

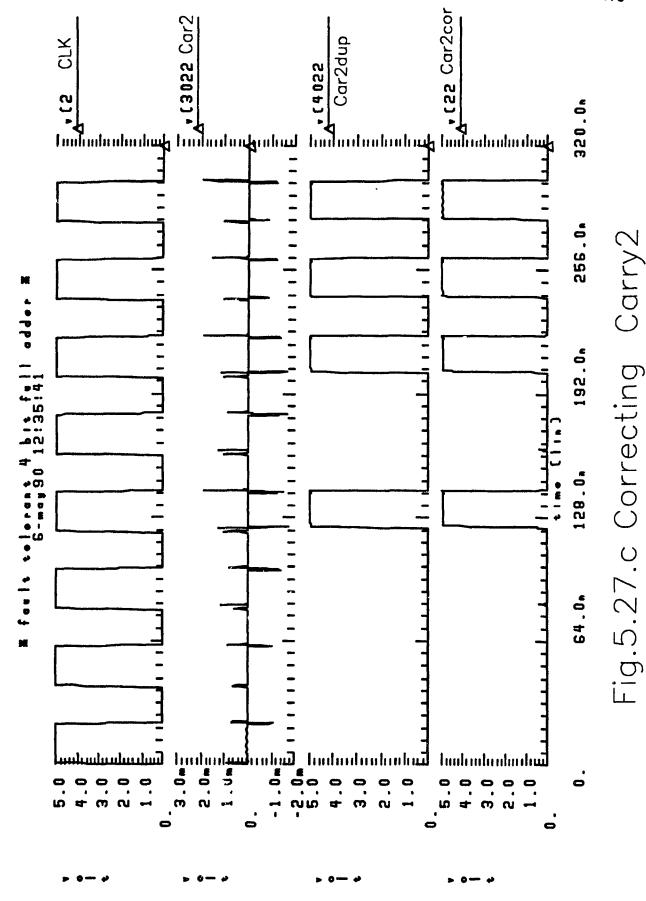

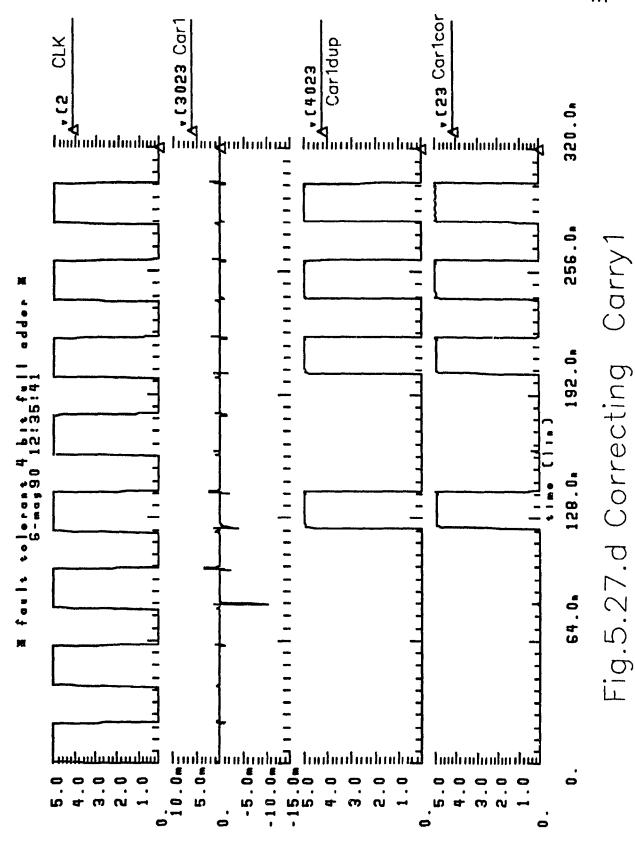

| Flg.5.27 | Simulation results of correcting Gen:Car block's outputs | 114 |

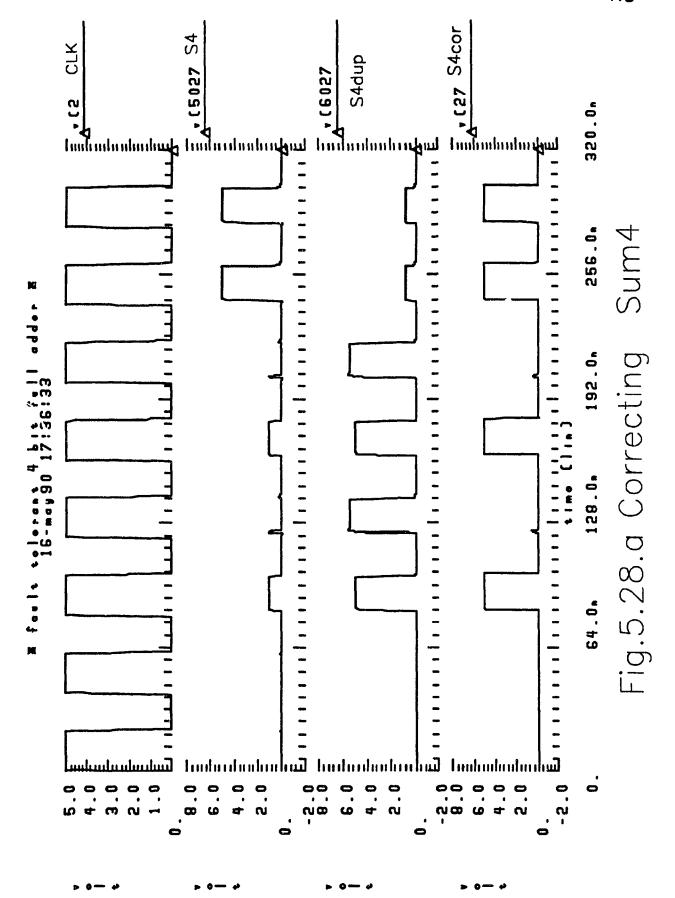

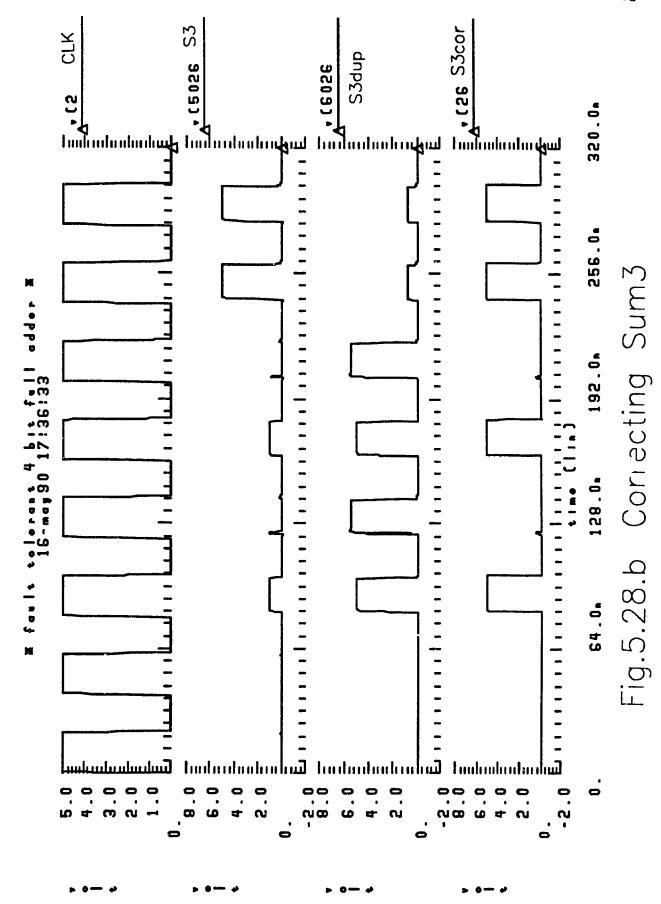

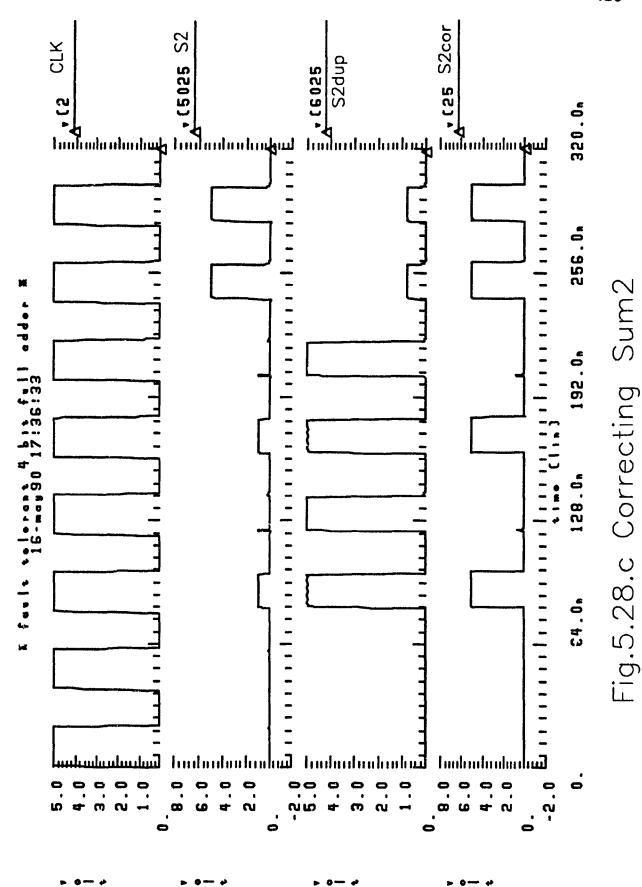

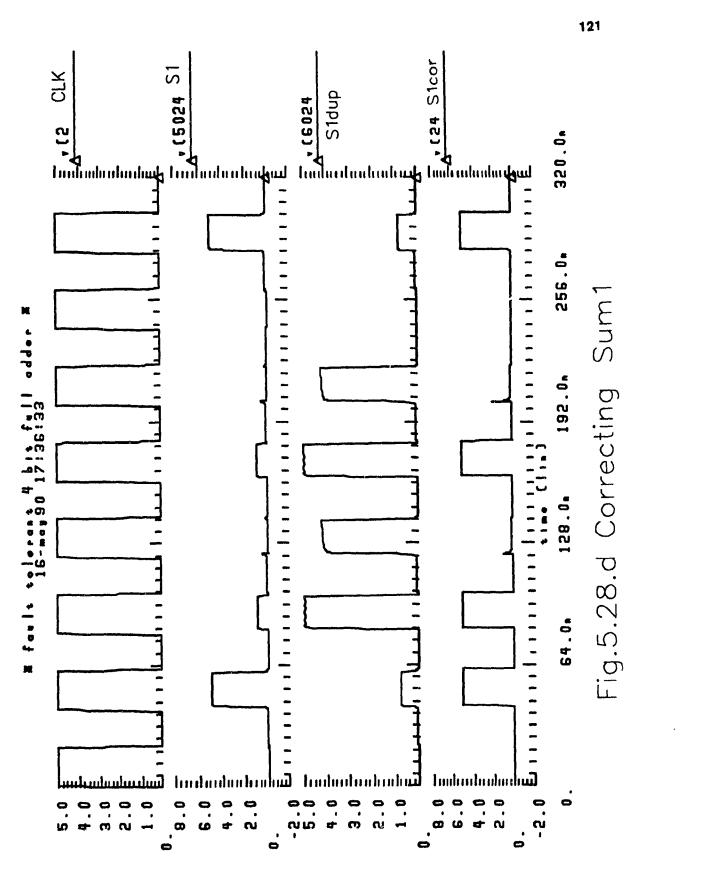

| Fig.5.28 | Simulation results of correcting XORs' outputs           | 118 |

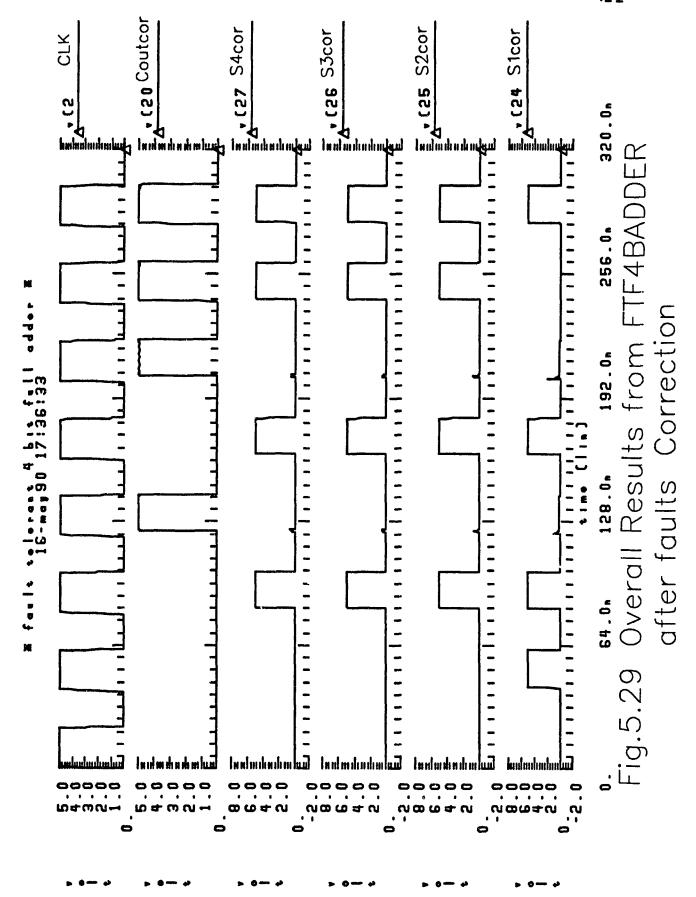

| Flg.5.29 | Overall results of correcting faults in full 4-bit adder | 122 |

| Fig.C.1  | Faults in carryb generation block                        | 143 |

| Fig.C.2  | Faults in inverter block                                 | 152 |

| Fig.C.3  | Faults in static XOR block                               | 157 |

| Flg.C.4  | Faults in P&G generation block                           | 172 |

| Fig.C.5  | Faults in carry generation block                         | 178 |

#### CHAPTER 1: INTRODUCTION

Addition circuitry is an important part of any computer architecture, since it is the major component of an ALU, floating point processors, or special purpose chips[1].

Various types of adders were introduced in the literature such as carry-look-ahead, ripple carry, hierarchical, transmission gate, manchester carry, combinational, ...etc.[1]. The implementation of the circuit could be in either static logic such as CMOS complementary or Pseudo-nMOS, or dynamic (complementary or non-complementary) logic such as dynamic CMOS, clocked CMOS, domino, cascade voltage switch, ...etc.[2].

In VLSI, design area complexity and time/delay performance are important factors that affect the performance of a design. The decision to implement a certain type of logic to a certain type of adder is based on speed and area considerations needed for the required application. In our design, the carry-look-ahead adder implemented with the new Multiple Output Domino Logic, was used for its advantages of speed, and smaller area.

Adder Accumulator circuits find their uses in a variety of digital signal processing systems. In our work, the addition circuitry is used as a threshold generator, which is part of a multi-processor image processing system. The adder accumulator (threshold generator) is used to calculate the threshold of a frame as soon as the frame pixels are generated from the A/D converter. The speed of the adder accumulator has to match the speed at which the pixels are generated. In our application, this is 18MHz.

The adder accumulator is built upon two types of carry-look-ahead adders.

A full 4-bit adder which is used to add 8 bit pixels, and a 4-bit partial adder

which is used to accumulate the generated carry's. In addition to implementing the adders in the adder accumulator, they can also be used in the convolver which is used in convolution calculation (one of the most frequent operations in image processing). They can also be implemented in the edge detector, and any other module that requires fast addition circuitry.

With the increasing demand for reliable components, and with the advent of VLSI, many fault tolerance techniques were made available. As the designed adders could be implemented in different modules, and the reliability of these modules is of importance, thus the need to redesign the adders as fault tolerant ones.

To design a fault tolerant component, first a fault model is built covering the various faults that the fault tolerant module would be able to tolerate. In our fault analysis, classical stuck-at-faults, non-classical stuck-open faults, and physical shorts (short between gate and source, gate and drain, drain and source) are studied.

The second step in designing a fault tolerant module is to decide between various fault tolerance techniques, i.e. to select the most suitable technique for the application, in terms of time, area, and fault coverage.

#### In this thesis:

Chapter 2 covers the theory and design of the adder accumulator.

Chapter 3 involves the design of the 4-bit partial adder and full 4-bit adder, a comparison between our adders and other adders involving either different types of logic (classical domino, static) or different types of adders (hierarchical); then an implementation and simulation of the adder accumulator follows.

Chapter 4 covers the fault analysis for the 4-bits and full 4-bits adders.

Chapter 5 presents the analysis and design of the fault tolerant 4-bits and full 4-bits adders.

Finally Chapter 6 concludes the work.

## CHAPTER 2: DESIGN OF A 24 bit ADDER ACCUMULATOR

#### 2.1 INTRODUCTION

In this chapter we present the design of an adder accumulator using pipelining techniques. Although the method is general to any length of bits, we will consider the design of a 24 bit adder accumulator that will be used in a multiprocessor image processing system. The adder accumulator is part of the threshold generator that is used as a slave accelerator for the overall image processing multiprocessor being developed[3]. The images produced by the camera are digitised[4] to provide a digital image with a resolution of 256 by 256 pixels. Each pixel is converted to an eight-bit word, thus, it will represent a grey level[5] of 256 grey levels. In our system, pixels are produced by the A/D converter at a rate of 18 MHz. During each cycle the accumulated value of the previous pixels is retrieved from the storage flip flops, the value of the newly generated pixel is added to that previous sum, and finally the new sum is stored again.

#### 2.2. THRESHOLD GENERATOR

The threshold generator is used to calculate the threshold value of all the pixels in a given frame, as that frame is sent by the camera. Thus we need to monitor the data bus of the system and capture the value of each of the 64K pixels, in order to calculate their threshold value, and have it available to the system.

The threshold value is defined as the mean value of the pixels within a frame, and is calculated using:

$$T = \frac{\sum_{i=1}^{256} \sum_{j=1}^{266} P_{ij}}{256 \times 256}$$

Where  $P_{ij}$  is the pixel value represented by 8 bits.

#### 2.3 ADDER ACCUMULATOR DESIGN

As was seen in the previous section that calculating the threshold value for a frame involves the addition of 64K words of eight bits. This addition will produce a maximum sum of 24 bits. A simple solution would have been adding a 24 bit accumulator to 8 bits from A/D converter using a 24-bit adder. Fig.2.1 shows that simple configuration. However that structure would be slow.

However, introducing pipelining, makes that structure plausible, since the 24-bit adder required will be divided into multiple stages. Fig.2.2 shows the pipeline structure using 8-bit partial adders, and full 8-bit adder.

Implementing the same principle but with using 4-bit partial adders and full 4-bit adders will result in our adder accumulator shown in Fig.2.3.

In deciding on the adders size, we had the choice of either having 8-bit, 4-bit, 2-bit, or 1-bit (partial and full) adders. The 8-bit size was discarded as it would have been slow, since in the carry generation unit (of the partial or full adder) a path of 10 serial nmos transistors will have a slowing impact on the speed by which the carry's are generated, thus slowing down the adder, in addition to having a low noise margin due to the length of the nmos chain. Implementing the adders in 2-bit (or 1-bit) size would have resulted in an increased number of transistors. Considering the case of the full adder (and the same argument holds true for the partial adder), with 2-bit (or 1-bit) we would have 4 (or 8) discharge nmos for carry generation unit as opposed to 2 in the case of using 4-bit, in addition to 4 (or 8) nmos which are to be used to add carrys generated by other carry generation units, as opposed to 2 in the case of 4-bit. As to the impact of having 2-bit (or 1-bit) adders on the adder accumulator, an increase in the number of stages will result, which in turn, would increase the flushing time

ADC-DATA is from A/D converter

D23-D00 is data accumulated

023-000 is final result

Fig. 2.1 SINGLE STAGE ADDER ACCUMULATOR

ADDERS 1,2 full 4-bit adders

ADDERS 3,4,5,6 4-bit partial adders

Fig.2.3 6 STAGE PIPELINE ADDER ACCUMULATOR

of the pipeline, in addition to having extra flip flops to store the resulting carry of each stage.

#### 2.4. ADDER ACCUMULATOR FUNCTIONALITY

Each 8 bit word that comes in, is first latched by the valid data signal. The first adder sees a stable value from the input latch (4 bits from the input word), and another input from Do3 - Do0 of the accumulator, thus the adder produces a stable sum that is passed back to the Do3 - Do0 of the accumulator, while the generated carry is passed to a flip-flop, to be used with the second stage of the pipeline during the next data valid signal. At the same time the second adder sees the remaining input 4 bits, another 4 bits from the accumulator (Do7 - Do4) and a carry bit from the flip-flop (initially 0). Again the second adder produces a sum that is passed back to the accumulator (Do7 - Do4), while the generated carry is again stored in another flip-flop, to be used with the third stage of the pipeline during the next data valid signal. When the next data valid signal arrives, the first carry will be added to the sum stored in bits 4 through 7 of the accumulator, in addition to the 4 bits of the input word. Also, the second carry will be added to the sum in bits 8 through 11 of the accumulator using a 4-bit adder.

The structure shown in Fig.2.3 implements the following functions:

$$\begin{array}{l} D \ G3_{i} \rightarrow D \ O0_{i} \ = \ D \ O3_{i-1} \rightarrow D \ O0_{i-1} + P \ O3_{i} \rightarrow P \ O0_{i} \\ \\ FF \ 1_{i} \ = \ carry \left( \ D \ O3_{i-1} \rightarrow D \ O0_{i-1} + P \ O3_{i} \rightarrow P \ O0_{i} \ \right) \\ \\ D \ O7_{i} \rightarrow D \ O4_{i} \ = \ D \ O7_{i-1} \rightarrow D \ O4_{i-1} + P \ O7_{i} \rightarrow P \ O4_{i} + FF \ 1_{i-1} \\ \\ FF \ 2_{i} \ = \ carry \left( \ D \ O7_{i-1} \rightarrow D \ O4_{i-1} + P \ O7_{i} \rightarrow P \ O4_{i} + FF \ 1_{i-1} \right) \end{array}$$

$$\begin{array}{l} D\ 11_{i} \to D\ 08_{i} = D\ 11_{i-1} \to D\ 08_{i-1} + FF\ 2_{i-1} \\ \\ FF\ 3_{i} = carry\ (\ D\ 11_{i-1} \to D\ 08_{i-1} + FF\ 2_{i-1}\ ) \\ \\ D\ 15_{i} \to D\ 12_{i} = D\ 15_{i-1} \to D\ 12_{i-1} + FF\ 3_{i-1} \\ \\ FF\ 4_{i} = carry\ (\ D\ 15_{i-1} \to D\ 11_{i-1} + FF\ 3_{i-1}\ ) \\ \\ D\ 19_{i} \to D\ 16_{i} = D\ 19_{i-1} \to D\ 16_{i-1} + FF\ 4_{i-1} \\ \\ FF\ 5_{i} = carry\ (\ D\ 19_{i-1} \to D\ 16_{i-1} + FF\ 4_{i-1}\ ) \\ \\ D\ 23_{i} \to D\ 20_{i} = D\ 23_{i-1} \to D\ 20_{i-1} + FF\ 5_{i-1} \\ \\ O\ 03_{i} \to O\ 00_{i} = D\ 03_{i} \to D\ 00_{i} \\ \\ O\ 07_{i+1} \to O\ 04_{i+1} = D\ 07_{i} \to D\ 04_{i} + P\ 07_{i+1} \to P\ 04_{i+1} + FF\ 1_{i} \\ \\ O\ 11_{i+2} \to O\ 08_{i+2} = D\ 11_{i+1} \to D\ 08_{i+1} + FF\ 2_{i+1} \\ \\ O\ 15_{i+3} \to O\ 12_{i+3} = D\ 15_{i+2} \to D\ 12_{i+2} + FF\ 3_{i+2} \\ \\ O\ 19_{i+4} \to O\ 16_{i+4} = D\ 19_{i+3} \to D\ 16_{i+3} + FF\ 4_{i+3} \\ \\ O\ 23_{i+5} \to O\ 20_{i+5} = D\ 23_{i+4} \to D\ 16_{i+4} + FF\ 5_{i+4} \\ \end{array}$$

Where Dxx is data in accumulator, Pxx is input pixel bits, and Oxx is resulting output, I stands for clock instant.

Fig.2.4 shows how temporary results propagate through the pipeline. It can be seen that a carry bit generated by a data word only propagates to the last bit of the accumulator five clock cycles later, i.e. with this design we have a flushing time of 5 cycles.

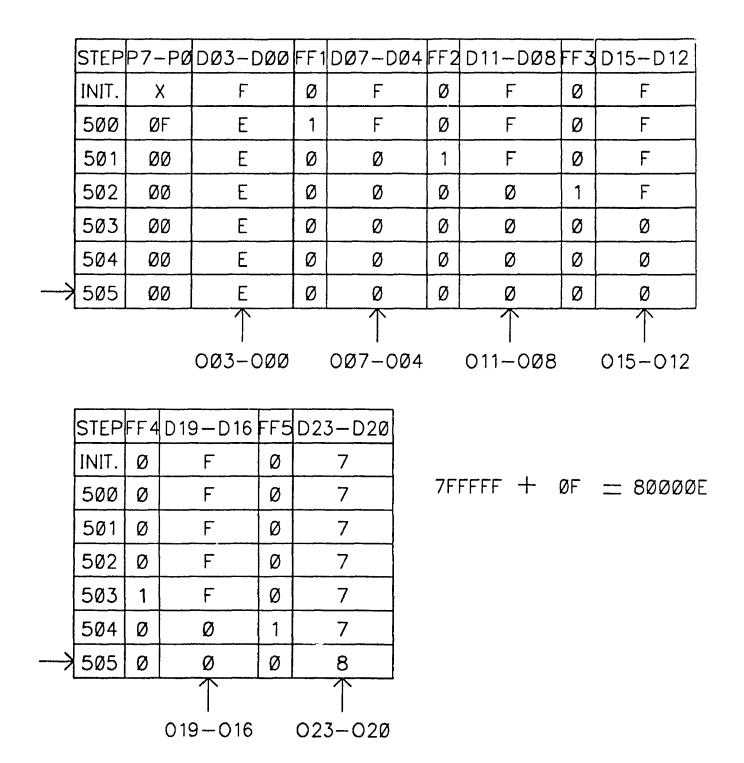

To explain this we give an example, and assume that at step 500 hex the

| STEP    | P7-PØ | DØ3-DØØ | FF1 | DØ7-DØ4 | FF2 | D11-DØ8 | FF3 | ე15−D12 |   |

|---------|-------|---------|-----|---------|-----|---------|-----|---------|---|

| INIT.   | Ø     | Ø       | Ø   | Ø       | Ø   | Ø       | Ø   | Ø       |   |

| 1       | FF    | F       | Ø   | F       | Ø   | Ø       | Ø   | Ø       |   |

| 2       | FF    | Ε       | 1   | Е       | 1   | Ø       | Ø   | Ø       |   |

| 3       | FF    | D       | 1   | Ε       | 1   | 1       | Ø   | Ø       |   |

| 4       | FF    | С       | 1   | E       | 1   | 2       | Ø   | Ø       | · |

| 5       | FF    | В       | 1   | E       | 1   | 3       | Ø   | Ø       |   |

| STEPS   |       |         |     |         |     |         |     |         |   |

| IN HEX. |       |         |     |         |     |         |     |         |   |

| 11      | FF    | F       | Ø   | E       | 1   | F       | Ø   | Ø       |   |

| 12      | FF    | E       | 1   | D       | 1   | Ø       | 1   | Ø       |   |

|         |       |         |     |         |     |         |     |         |   |

Fig.2.4 Results Propagation through Pipeline

accumulator contained 7FFFFF hex. That is the lower part contains F hex, and so does the following four parts, and the upper part contains 7 hex. Suppose also that all the carry flip-flops contained zero's. Also for the sake of clarity we'll assume that after this step the input word is 00 hex.

Now, referring to Fig.2.5, if our input word was 0F hex, say at step 500 hex, the lower part of the accumulator will be added to an F hex thus producing E hex and a 1 carry, meanwhile the second part of the accumulator will be added to 0 hex and a 0 carry (from the previous step), producing an F hex and a zero carry. In the next step (501 hex) the carry in FF1 will be added to the second part of the accumulator thus producing 0 hex and a 1 carry. In step 502 hex, the carry in FF2 will be added to the third part of the accumulator producing a 0 hex and a 1 carry. In step 503 hex, the carry in FF3 will be added to the fourth part of the accumulator producing a 0 hex and a 1 carry. In step 504 hex, the carry in FF4 will be added to the fifth part of the accumulator producing a 0 hex and a 1 carry. Finally in step 505 hex, the carry in FF5 will be added to the upper part of the accumulator producing 8 hex and a 0 carry, and at that point the resulting value of the addition can be read from the accumulator which is 80000E hex. Fig.2.5 shows the computation steps.

Thus it can be seen that it takes five clock cycles after the last data word has arrived to get the final result of the threshold computation.

In the following chapter, the design of the adders used, and the simulation of the adder accumulator will be given.

Fig.2.5 Computation Steps

# **CHAPTER 3: ADDERS DESIGN**

#### 3.1. INTRODUCTION

With the increasing demand for higher performance of CMOS VLSI processors with increased sophistication, there is a greater need to improve the performance, area efficiency, and functionality of the arithmetic unit within them.

As mentioned in chapter 1, various adders were introduced in the literature. Ripple carry adders provided circuits with small area but with large propagation delays[2]. Carry skip adders, implementing Manchester carry chain[3] or basic ripple adders[7], improved on the performance of ripple carry adders by making early signals more available by trading available time for extra hardware[6]. Carry select adders, on the other hand, expended area in favor of speed by duplicating two ripple carry adders, then selecting the appropriate sum[2]. Carry-look-ahead provided circuits with small propagation delay, however the complexity involved in the circuits implementing this principle remained.

Various CMOS logic styles were introduced exploiting noncomplementary structure with dynamic operations, in order to improve area efficiency, and speed of CMOS logic. Among these logic styles, NORA [8] provided high speed circultry, high logic flexibility, and compact chip area, however, charge redistribution and leakage of storage nodes problems were disadvantages to that CMOS logic style. Domino logic [9] provided speed and area advantages, in addition to being valuable for circuits involving complex gates with high fan-in and fan-out, but still shared with NORA the charge redistribution problems. Zipper CMOS [10] incorporated the advantages of NORA and Domino in terms of structural simplicity and performance, and at the same time had a better immunity to instability and charge redistribution problems.

In the following section we will discuss the new dynamic CMOS logic style, namely Multiple Output Domino Logic (MODL), that is going to be used for the implementation of our circuits.

#### 3.2. MULTIPLE OUTPUT DOMINO LOGIC

MODL is a new dynamic CMOS logic style introduced by Hwang and Fisher[11], that allows a single gate to produce multiple outputs. In conventional domino logic and other noncomplementary MOS logic, only one output is available from a certain gate. Thus if a certain subfunction is needed, as a separate output, it will have to be implemented with additional gates, hence, resulting in added circuitry.

The basic principle behind MODL is the use of intermediate functions that are available within the logic tree, thereby, saving the need to replicate circuitry, and hence, reducing the complexity of the design. These intermediate functions are obtained by precharging the corresponding intermediate nodes and adding inverters to obtain required outputs.

This logic design is particularly favorable as it reduces device number in a given circuit, in addition to inherent higher circuit stability as compared to standard domino and other dynamic circuits. Also MODL circuits are less susceptible to charge sharing problems, due to the precharging of the internal nodes. Due to the reduced device number, an improved performance results since load capacitance is reduced correspondingly.

The decision to implement the carry generation part of our circuits in MODL with carry-look-ahead principle stems from the overall advantage of using MODL in reducing the area and increasing the circuit performance plus allowing speed efficient designs.

As discussed previously two types of adders are used in our Adder Accumulator design. A partial bit adder which adds only a single bit to a full number, and a full adder. This distinction is based on the principle of saving area and enhancing speed.

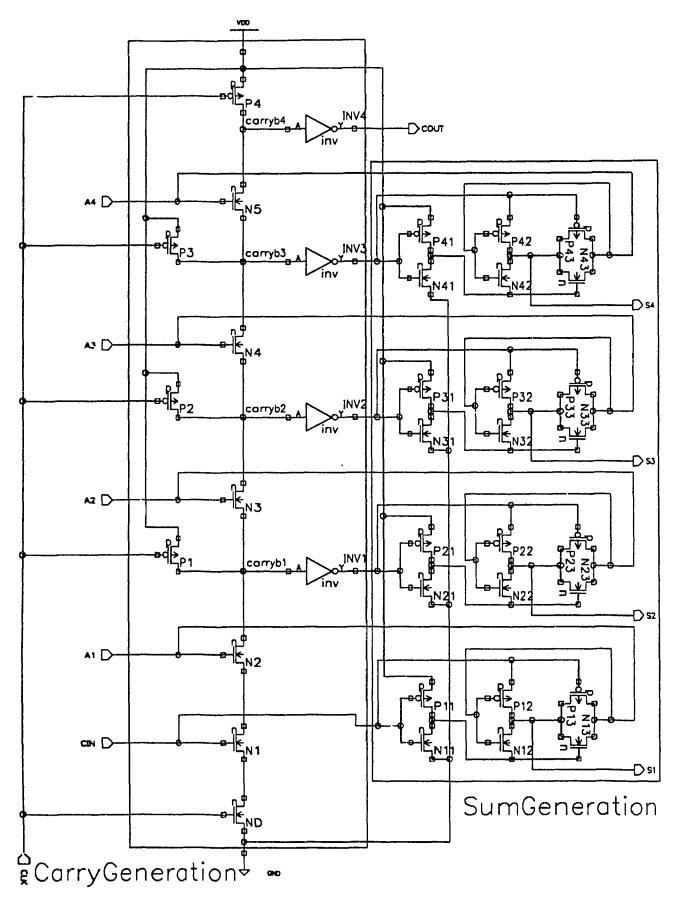

# 3.3. A 4-BIT MODL ADDER

A 4-bit partial adder with a carry-look-ahead organization is shown in Fig.3.1. The adder consists of two main units. A carry generation unit which generates the intermediate carry terms and the output carry, applying the formula:

$$C_i = A_i \bullet C_{i-1}$$

As it can be seen from Fig.3.1, the series connection of N1, N2, ..., N5 gives the ANDing function at each output node.

The second unit calculates the sum product, using a static XOR, using:

$$S_i = A_i \oplus C_{i-1}$$

The circuit consisted of 20 pmos and 22 nmos, with an overall gate area of  $175.68 \text{ pm}^2$ . The carry-look-ahead devices' widths were sized in multiples of the minimum design feature (L) following the "pyramid" FET scaling technique[12]. By scaling the nmos's using this technique, better speed was achieved as opposed to having all the serial nmos's in one size. It could also be seen here that had we implemented the adder in 8-bits, the increase in the size of nmos's, specially the bottom ones, would have an increasing effect on the area, in addition to a slowing effect on speed. Also with a 2-bit or a 1-bit implementation, that technique would not have an obvious effect on speed, thus we would have only achieved an overhead in the number of extra devices, and therefore area, without achieving

Fig.3.1 4—Bit Partial Adder using MODL

any gain in speed.

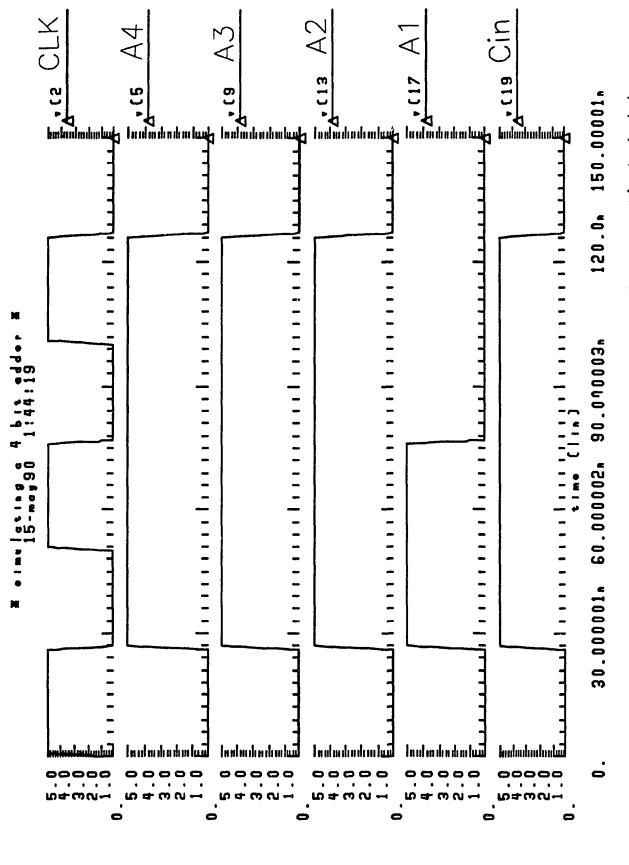

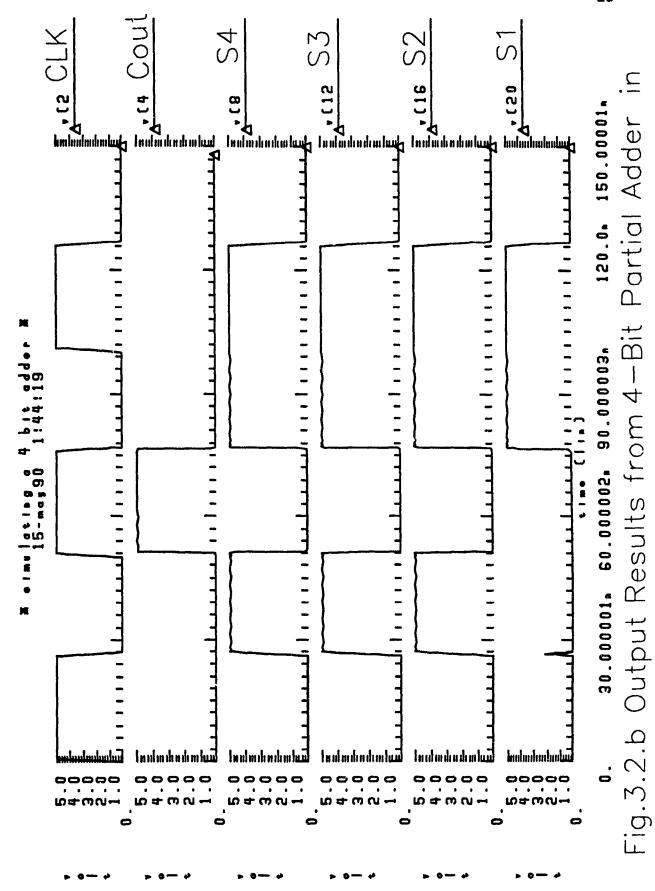

#### 3.3.1. SIMULATION

Simulation was carried out using HSPICE, with CMOS 1.2u, at worst case conditions, i.e. at input test vector  $A_i$  1111 and carry in  $C_{in} = 1$ , with Vdd= 5v, and at 25° C. The worst case condition resulted in a delay, from the clock to S1, of 0.78nsec. This comes from a worst case delay of 0.57ns in the carry generation block from clock to Carry3, in addition to 0.21ns delay in the XOR in order to get S4. Fig.3.2(a, b, and c) is the input test vector and the simulation results for the 4-bit partial adder circuit.

#### 3.4. A FULL 4-BIT MODL ADDER

The full 4-bit adder is designed using the carry-look-ahead principle in addition to MODL logic style. Fig.3.3 shows the overall design of the adder. The adder is split up to three units. The first unit generates the generate and propagate terms. The second unit generates the carry signals, and the third unit generates the sum products.

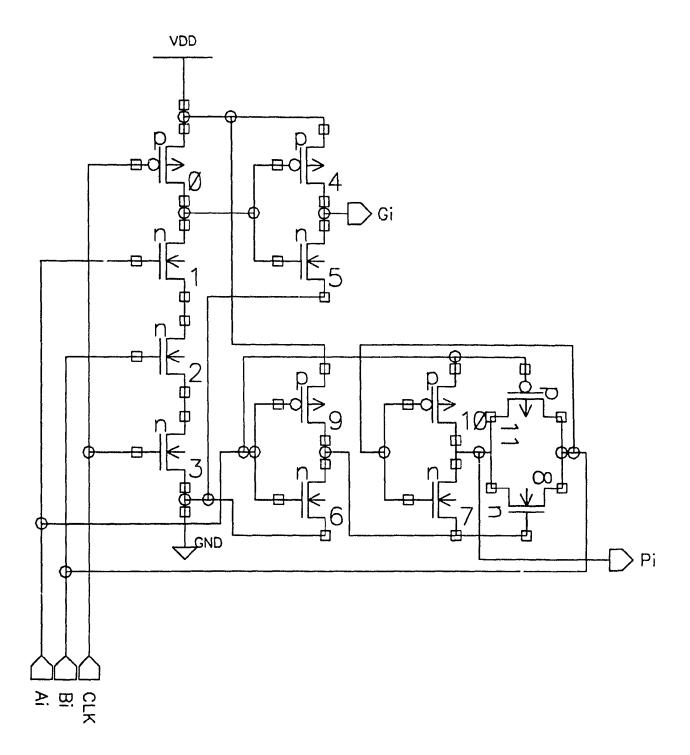

# 3.4.1. GENERATE AND PROPAGATE GENERATION UNIT (GEN:P&G)

This unit mainly calculates whether a carry should be generated, or simply the previous carry should be propagated. A carry is generated whenever both Al and Bl (the bits to be added) are 1's, while the carry from the previous addition will be propagated whenever either Al or Bl is 1. Thus the generate signal is calculated as:

$$G_i = A_i \bullet B_i$$

While the propagate signal is calculated as:

Fig.3.2.a Input Test Vectors to4—Bit Partial Adder

Response to Fig. 3.2.a

```

*PROPAGATION DELAY BETWEEN CLK AND COUT*

delay1 = 6.1315E-10 targ= 5.1113E-08 trig= 5.0500E-08

*PROPAGATION DELAY BETWEEN CLK AND SUM4*

delay2 = 7.8332E-10 targ= 5.1283E-08 trig= 5.0500E-08

*PROPAGATION DELAY BETWEEN CLK AND SUM3*

delay3 = 6.7383E-10 targ= 5.1174E-08 trig= 5.0500E-08

*PROPAGATION DELAY BETWEEN CLK AND SUM2*

delay4 = 6.2051E-10 targ= 5.1121E-08 trig= 5.0500E-08

*Propagation delay between CLK and SUM1 is not measured as both Cin and Al are calculated during low CLK, thereby SUM1 has an already steady

```

Fig.3.2.c Summary of Simulation Result

state value by the time the CLK becomes high.

$$P_i = A_i \oplus B_i$$

The propagate signal is calculated using the exclusive OR function instead of an OR function (which is commonly found in literature) in order to avoid the case of having both the P signal and the G signal to be simultaneously equal to 1 (case when both Ai and Bi are equal to 1), as this would cause a charge redistribution problem. As the P signal is calculated during low clock, while the G signal is calculated during high clock, with P equal to 1 the nmos it controls will be turned on, now, if during high clock G also goes high a charge redistribution will occur, which might cause erroneous results.

Fig.3.4 shows the design of the Gen:P&G unit.

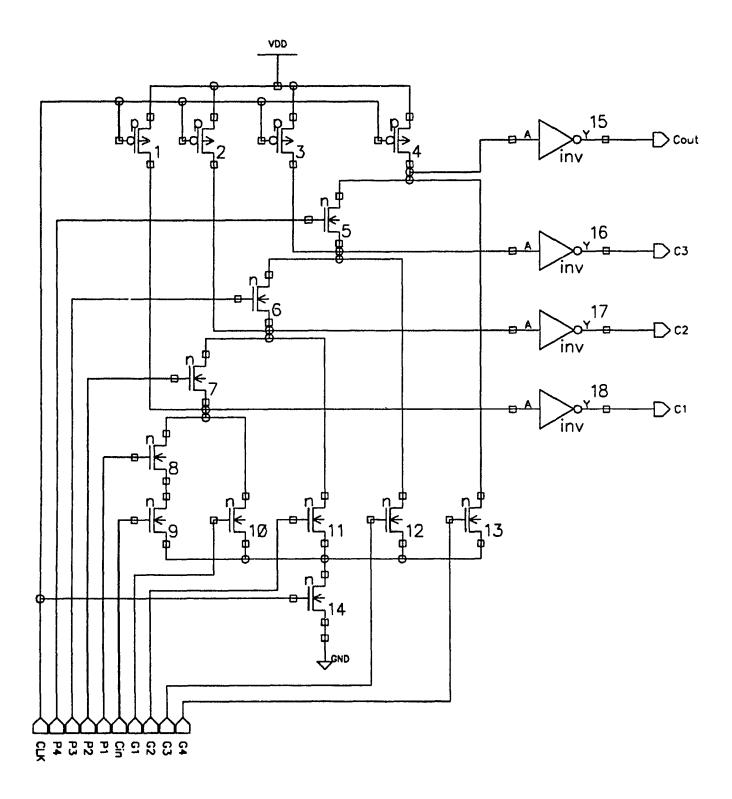

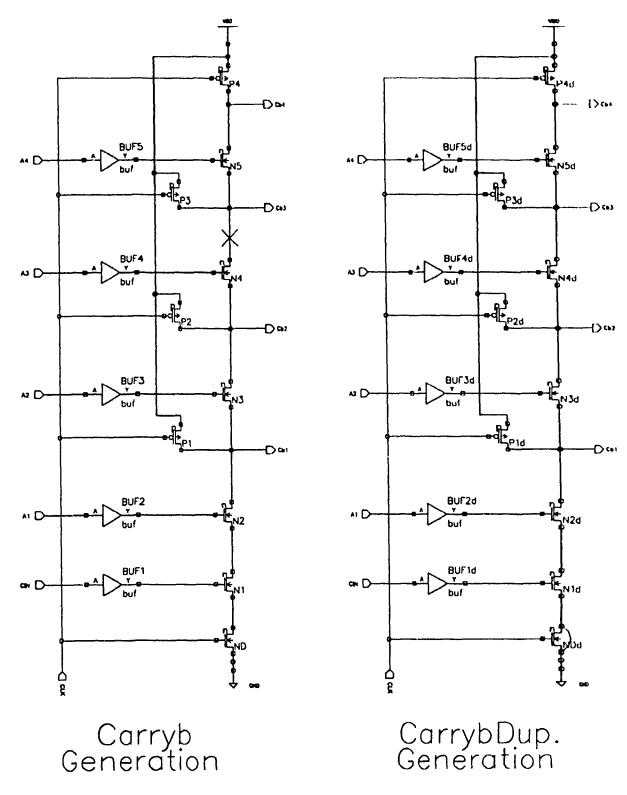

# 3.4.2. CARRY GENERATION UNIT (GEN:CAR)

The Gen: Car unit is 4-bit MODL carry generator that collects the resulting 8 generate and propagate signals, from the previous unit, together with the input carry (Cin). It then calculates the intermediate carrys (C1, C2, and C3), together with the output carry (Cout). The carry calculation is carried as follows:

$$C_i = G_i + (P_i \bullet C_{i-1})$$

Fig.3.5 shows the design of the Gen:Car unit.

## 3.4.3. SUM CALCULATION UNIT (XOR)

Now with both the carrys and the propagate signals available from the previous stages, the sum products are calculated through a static XOR using the formula:

$$S_i = P_i \oplus C_{i-1}$$

Fig.3.4 Generate & Propagate Circuit (GEN:P&G)

Fig. 3.5 Carry Generation Circuit (GEN:CAR)

Fig.3.6 shows the static XOR used. While Fig.3.7 shows the full 4-bit adder in transistor level.

As in the previous adder design, the devices' widths were sized in multiples of the minimum design feature (L), with "pyramid" FET scaling technique [12]. The circuit contains 40 pmos and 54 nmos with overall gate area of 368.64  $pm^2$ .

#### 3.4.4. SIMULATION

Simulation was carried out again using HSPICE, with CMOS 1.2u, with a set of test vectors, Vdd=5v, and at 25° C. The worst case condition resulted in a delay, from clock to S4, of 0.92nsec. In the Gen:P&G block, with the worst case condition simulation, all G's were set to 0. The resulting P's from the XOR were calculated during low clock, therefore, they represented no delay during the following evaluation clock. In the Gen:Car unit, the worst case delay between clock and Carry3 was 0.7ns, that in addition to 0.22ns delay in XOR generating the sum, resulted in the 1ns overall worst case delay of the complete adder. Fig.3.8(a, b, c, and d) shows the simulation results for the full 4-bit adder circuit.

#### 3.5. COMPARISON

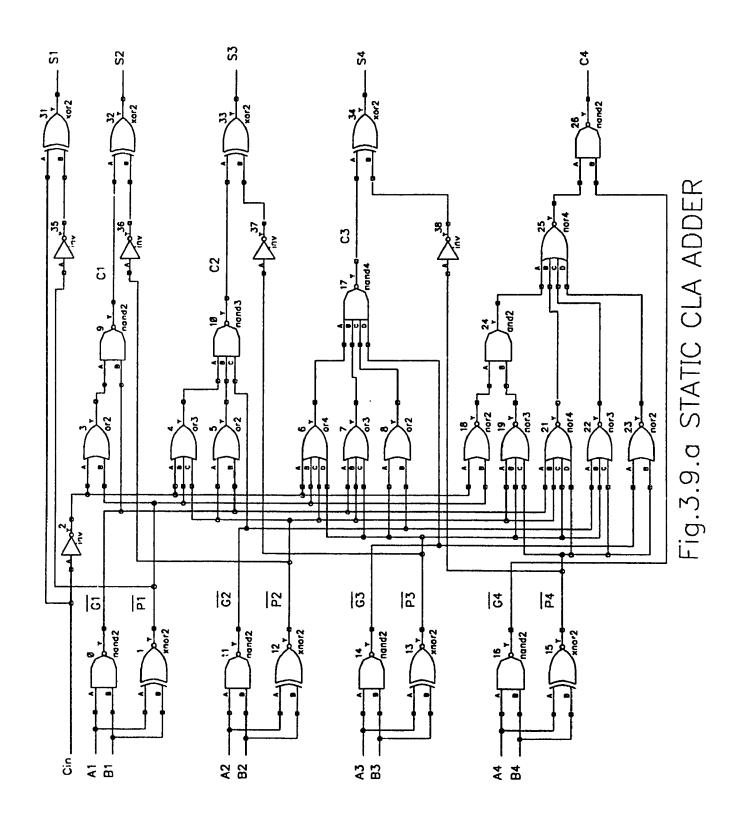

In this section we present the results of various simulations carried on three other full 4-bit adders so as to compare between these adders' performance in term of area and gate count, and speed to our full 4-bit adder. Fig.3.9.a shows a static carry-look-ahead adder[2], while Fig.3.9.b shows the simulation results (the same test vectors were used as in the case of the full 4-bit adder). From the simulation the adder gave a worst case propagation delay of 2.29ns (input A4 to S4), and the overall transistor area was 410.112 pm<sup>2</sup>, with a total transistor count of 190 mosfets.

Fig.3.6 Exclusive OR Circuit

--- ر بـ-- ر

```

*PROPAGATION DELAY BETWEEN CLK AND COUT*

delayl

= 7.0488E-10  targ=

1.2120E-07

trig=

1.2050E-07

delay2

7.0252E-10

targ=

2.0120E-07

trig=

2.0050E-07

delay3

5.2661E-10

targ=

2.4103E-07

trig=

2.4050E-07

= 5.1726E-10 targ=

delay4

2.8102E-07

trig=

2.8050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM4*

= 9.1651E-10 targ=

delay5

1.2142E-07

trig=

1.2050E-07

= 9.1828E-10

delay6

targ=

2.0142E-07

trig=

2.0050E-07

= 7.9400E-10

delay7

targ=

2.4129E-07

trig=

2.4050E-07

delay8

= 7.7795E-10

targ=

2.8128E-07

trig=

2.8050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM3*

delay9

7.1115E-10 targ= 1.2121E-07

trig=

1.2050E-07

delay10

7.1331E-10

2.0121E-07

2.0050E-07

targ=

trig=

= 7.9210E-10

delay11

targ=

2.4129E-07

trig=

2.4050E-07

delay12

= 7.7383E-10

targ = 2.8127E - 07

trig=

2.8050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM2*

targ=

delay13

= 6.5226E-10

1.2115E-07

trig=

1.2050E-07

= 6.4978E-10

delay14

targ=

2.0115E-07

trig=

2.0050E-07

delay15

7.9230E-10

targ=

2.4129E-07

trig=

2.4050E-07

delay16

= 7.7252E-10

targ=

2.8127E-07

trig=

2.8050E-07

```

Fig. 3.8.c Summary of Simulation Result

\*Propagation delay between CLK and SUM1 is not measured as both Cin and P1 are calculated during low CLK, thereby SUM1 has an already

steady state value by the time the CLK becomes high.

- \* PROPAGATION DELAY is 9.1828E-10 sec. \*

- \* RISE TIME is 5.3262E-10 sec. \*

- \* FALL TIME is 3.1559E-10 sec. \*

- \* AVERAGE POWER DISSIPATION is 2.6450E-04 watt \*

- \* MINIMUM POWER DISSIPATION is 6.0400E-09 watt \*

- \* MAXIMUM POWER DISSIPATION is 1.9132E-02 watt \*

- \* MAXIMUM Idd = 2.3869E-4 amp\*

- \* TEMP = 25 C \*

- \* Vdd = 5 volts \*

- \* CAPCITIVE LOAD ON EACH OUTPUT (assuming a buffer) is 5.5801E-14 farad \*

Fig.3.8.d Specification of Full 4-Bit Adder

```

*PROPAGATION DELAY BETWEEN I/P AND COUT*

= 1.7790E-09

1.0283E-07

delay9

targ=

trig=

1.0105E-07

= 2.1115E-09

delay14

targ=

1.4316E-07

trig=

1.4105E-07

delay19

1.7652E-09

targ=

1.8282E-07

trig=

1.8105E-07

= 2.0686E-10 targ=

delay28

3.0136E-07

trig=

3.0115E-07

*PROPAGATION DELAY BETWEEN I/P AND SUM4*

delay4

= 7.4525E-10

targ=

6.1795E-08

trig=

6.1050E-08

= 1.7139E-09

delay8

targ=

1.0276E-07

trig=

1.0105E-07

delay13

= 2.2905E-09

trig=

targ=

1.4334E-07

1.4105E-07

= 1.7160E-09 targ=

1.8277E-07

delay18

tria=

1.8105E-07

= 9.6583E-10 targ=

2.2202E-07

delay22

trig=

2.2105E-07

= 6.0324E-10

delay27

3.0175E-07

targ=

trig=

3.0115E-07

*PROPAGATION DELAY BETWEEN I/P AND SUM3*

= 8.4915E-10

targ= 6.1899E-08

delay3

trig=

6.1050E-08

= 1.4280E-09

delay7

targ=

1.0248E-07

trig=

1.0105E-07

= 1.9063E-09 targ=

delay12

1.4296E-07

trig=

1.4105E-07

= 1.4191E-09 targ=

delay17

1.8247E-07

trig=

1.8105E-07

= 1.1141E-09 targ=

delay21

2.2216E-07

trig=

2.2105E-07

delay26

= 5.5220E-10

targ=

3.0170E-07

trig= 3.0115E-07

*PROPAGATION DELAY BETWEEN I/P AND SUM2*

= 8.9622E-10

delay2

targ= 6.1946E-08

trig=

6.1050E-08

delay6

= 1.1643E-09

1.0221E-07

trig=

1.0105E-07

targ=

= 1.5297E-09 targ=

trig=

delay11

1.4258E-07

1.4105E-07

= 1.1644E-09 targ=

1.8221E-07

trig=

1.8105E-07

delay16

= 1.2782E-09

trig=

2.2105E-07

delay20

targ=

2.2233E-07

delay25

= 5.6864E-10

targ=

3.0172E-07

trig=

3.0115E-07

*PROPAGATION DELAY BETWEEN I/P AND SUM1*

= 1.4397E-10 targ=

= 2.1000E-10 targ=

= 2.6148E-10 targ=

2.1194E-08

trig=

2.1050E-08

delay1

1.0126E-07

trig=

1.0105E-07

delay5

1.4131E-07

trig=

delay10

1.4105E-07

= 2.1000E-10 targ=

1.8126E-07

delay15

trig=

1.8105E-07

= 1.4184E-10

2.6119E-07

2.6105E-07

delay23

targ=

trig=

= 1.0709E-10

delay24

targ = 3.0126E - 07

trig=

3.0115E-07

```

Fig. 3.9.b Summary of Simulation Result

The second adder we used for comparison was a standard domino carry-look-ahead adder[2] (shown in Fig.3.10.a). From the simulation (Fig.3.10.b) the adder gave a worst case propagation delay of 1.54ns (CLK to S4), and the overall transistor area was 665.136  $pm^2$ , with a total transistor count of 116 mosfets.

Our last simulation was carried on a static hierarchical adder (shown in Fig.3.11.a) so as to compare our adder with an adder with a different type. Simulation results (Fig.3.11.b) showed a propagation delay of 3.02ns (input B4 to S4), and with a transistor area of 327.6 pm<sup>2</sup>, and a total transistor count of 136 mosfets.

The following table summarizes the simulation results and the percentage of speed, area, and gate count between the MODL adder and the other adders.

| Adder           | Prop.del. (ns) | %<br>speed | Area<br>(pm) | %<br>Inc.<br>area | no.of<br>gates | %<br>Inc.<br>gate |

|-----------------|----------------|------------|--------------|-------------------|----------------|-------------------|

| MODL            | 0.92           | 100        | 368.64       | 0                 | 94             | 0                 |

| Static CLA      | 2.29           | 40.17      | 410.112      | 111.25            | 190            | 202               |

| Std. Domino CLA | 1.54           | 59.7       | 665.136      | 180.4             | 116            | 123.4             |

| Hierarchical    | 3.02           | 30.48      | 327.6        | 88.9              | 136            | 144.7             |

Table 3.1 Comparison Between Various Adders

From the simulation results it could be seen that in terms of speed the MODL adder is the fastest, followed by the standard Domino CLA adder (with only 60 % of the MODL speed). In terms of area MODL compares favorably with standard Domino, and static CLA adder, and even though it is slightly larger than the hierarchical adder (due to the pyramid sizing in the carry-look-ahead block, which is not required in the hierarchical), it still compares favorably to all the adders in term of gate count.

```

*PROPAGATION DELAY BETWEEN CLK AND COUT*

= 1.2071E-09 targ= 1.2171E-07 trig= 1.2050E-07

= 1.2071E-09 targ= 2.0171E-07 trig= 2.0050E-07

= 3.0608E-10 targ= 2.4081E-07 trig= 2.4050E-07

delay4

delay8

delay12

delay16

= 3.2386E-10 targ= 2.8082E-07

trig=

2.8050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM4*

= 1.5360E-09 targ=

1.2204E-07

delay3

trig=

1.2050E-07

= 1.5360E-09 targ= 2.0204E-07

= 7.8898E-10 targ= 2.4129E-07

trig=

2.0050E-07

delay7

2.0204E-07

trig=

delay11

2.4050E-07

= 8.1950E-10 targ= 2.8132E-07 trig=

2.8050E-07

delay15

*PROPAGATION DELAY BETWEEN CLK AND SUM3*

= 1.1681E-09 targ=

1.2167E-07

trig=

1.2050E-07

= 1.1683E-09 targ= 2.0167E-07 trig=

delay6

2.0050E-07

2.4129E-07

= 7.8934E-10 targ=

delay10

trig=

2.4050E-07

= 8.1857E-10

2.8132E-07 trig=

targ=

2.8050E-07

delay14

*PROPAGATION DELAY BETWEEN CLK AND SUM2*

= 9.3269E-10 targ= 1.2143E-07

trig=

delay1

1.2050E-07

= 9.3272E-10  targ= 2.0143E-07

trig=

2.0050E-07

delay5

= 7.9733E-10 targ= 2.4130E-07

delay9

trig=

2.4050E-07

delay13

= 8.2783E-10 targ= 2.8133E-07 trig= 2.8050E-07

```

Fig. 3. 10.b Summary of Simulation Result

Fig.3.11.a HIERARCHICAL ADDER

```

*PROPAGATION DELAY BETWEEN I/P AND COUT*

1.0402E-07

trig=

delay9

2.9736E-09

targ=

1.0105E-07

2.7272E-09

targ=

1.4378E-07

trig=

1.4105E-07

delay14

2.4102E-09

targ=

1.8346E-07

trig=

1.8105E-07

delay19

= 5.6742E-10

3.0172E-07

trig=

3.0115E-07

delay28

targ=

*PROPAGATION DELAY BETWEEN I/P AND SUM4*

=

1.3697E-09

6.2420E-08

trig=

6.1050E-08

targ=

delay4

trig=

3.0177E-09

1.0407E-07

1.0105E-07

delay8

targ=

= 2.8698E-09

targ=

1.4392E-07

trig=

1.4105E-07

delay13

1.8105E-07

= 2.4424E-09

1.8349E-07

trig=

targ=

delay18

targ=

2.2258E-07

2.2105E-07

1.5263E-09

trig=

delay22

trig=

3.0115E-07

3.0253E-07

1.3780E-09

targ≕

delay27

*PROPAGATION DELAY BETWEEN I/P AND SUM3*

6.1050E-08

triq=

=

targ=

6.1872E-08

delay3

8.2208E-10

2.4870E-09

targ=

1.0354E-07

triq=

1.0105E-07

delay7

targ=

1.4105E-07

= 2.3677E-09

1.4342E-07

trig=

delay12

targ=

1.8105E-07

= 1.8859E-09

1.8294E-07

trig=

delay17

trig=

2.2105E-07

delay21

1.0305E-09

targ=

2.2208E-07

7.2975E-10

3.0188E-07

3.0115E-07

delay26

targ=

trig=

*PROPAGATION DELAY BETWEEN I/P AND SUM2*

6.1805E-08

tria=

6.1050E-08

delay2

7.5472E-10

targ=

targ=

1.0301E-07

trig=

1.0105E-07

1.9635E-09

delay6

trig=

delay11

1.8164E-09

targ=

1.4287E-07

1.4105E-07

.4206E-09

targ=

1.8247E-07

trig=

1.8105E-07

delay16

=

.9427E-09

targ=

2.2299E-07

trig=

2.2105E-07

delay20

3.0115E-07

1.1525E-09

targ=

3.0230E-07

trig=

delay25

*PROPAGATION DELAY BETWEEN I/P AND SUM1*

9.5003E-10

targ=

2.2000E-08

trig=

2.1050E-08

delayl

1.0607E-09

targ=

1.0211E-07

trig=

1.0105E-07

delay5

1.1313E-09

targ=

1.4218E-07

triq=

1.4105E-07

delay10

= 1.0082E-09

targ=

1.8206E-07

trig=

1.8105E-07

delay15

= 1.0481E-09

targ=

trig=

2.6105E-07

delay23

2.6210E-07

targ=

3.0202E-07

delay24

= 8.7432E-10

trig=

3.0115E-07

```

Fig.3.11.b Summary of Simulation Result

### 3.8. SIMULATING THE ADDER ACCUMULATOR

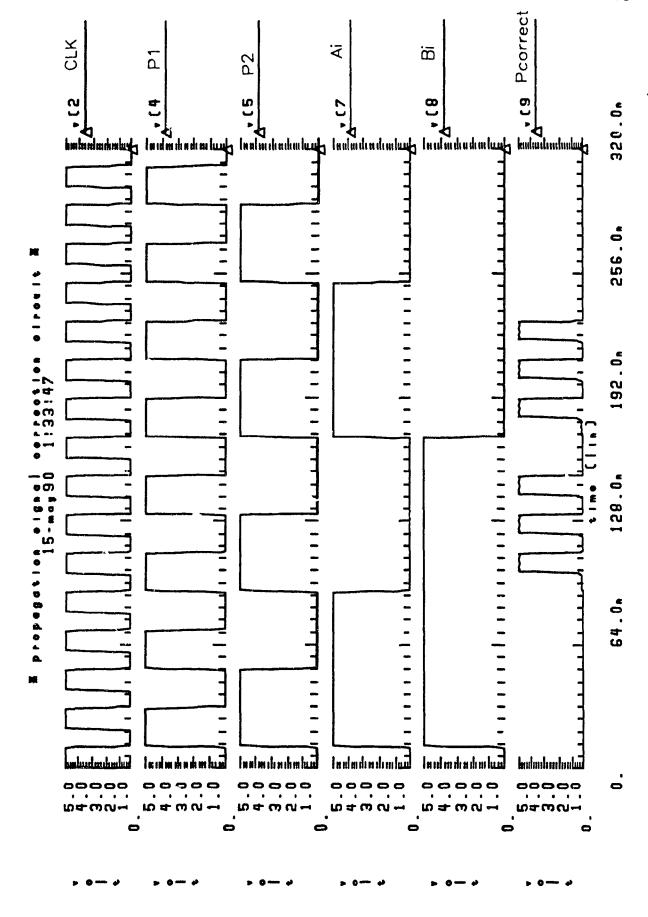

With both the 4-bit partial adder and the full 4-bit adders, designed, the following step is the simulation of the adder accumulator, discussed in the previous chapter.

Due to the dynamic nature of the adders, the output of the adders will be stored during high clock after the outputs have reached a steady state by using a result valid signal (result valid signal goes high 6ns after the clock is high, and it remains high for 12ns, then goes low his before the clock goes low and the results are no longer valid). On the other hand, data from the registers are to be presented to the adders during the low clock using a data valid signal (data valid signal goes high during low clock 6.5ns before the clock goes high, remains high for 5ns, then goes low 2.3ns before clock goes high). Fig.3.12 shows a segment of the adder accumulator with various control signals. As D flip-flops are used for storage, it was taken in consideration that the duration of the control signals be long enough to ensure stable results. Fig.3.13 shows the timing diagram of the control signals. The INIT signal is used to clear the registers at the beginning of every new frame(INIT signal, again, goes high during low clock, remains high for 1 ns and meanwhile a 0 input is presented to the flip flops to initialize them, then signal goes low before the data valid signal goes high by 0.3ns).

The adder accumulator is simulated with 0 initial conditions, followed by FF words for 4 clock cycles, followed by 00 words to clear the pipeline and propagate the generated carry's down the pipe. Fig.3.14 shows the simulation results.

The delay in every stage of the adder accumulator is proportional to the adder's delay in that stage, and as explained in the previous chapter, the final result of the addition, will be available after 5 clock cycles from the last word arrival.

Fig. 3.12 ADDER ACCUMULATOR

Fig. 3.13 Timing Diagram of Control Signals

of Stage#2 Fig. 3.14.b Simulation Result

It is interesting to note two points in favor of this design. One is that: as the number of bits increase, because of the pipeline nature of the design, the clock rate remains constant depending solely on the speed of the full 4-bit adder, therefore, the performance is independent of the bit size apart from the flushing requirements at the end of the calculation. The second point is in regard to the area: apart from the first word size adder, which is a full adder, the rest of the adders are all partial bit adders, thus saving on area tremendously as the bit size increases.

Appendix A gives the spice decks for the 4-bit partial adder, the full 4-bit adder, and the adder accumulator.

### **CHAPTER 4: FAULT ANALYSIS**

### 4.1. INTRODUCTION

In this chapter results of a complete analysis is given for the faults that might occur in both the 4-bit partial adder, and the full 4-bit adder, and which will be used as the base for designing the fault tolerant adders. Due to the bulk of the work, results of simulation runs are presented in Appendix C, with only the overall conclusion of the analysis presented in this chapter. We begin by discussing the various types of fault models, this will be followed by the analysis of the faults and the effect of these faults on the circuits' behaviour.

### 4.2. FAULT CHARACTERIZATION

Appendix B gives why and where physical faults occur. These physical faults are translated to stuck-at faults. Stuck-at fault model had been widely accepted in the past since it was adequate for the earlier fabrication technologies[13]. However, Wadsack[14] discovered that digital circuits implemented in CMOS technology could display fault models other that stuck-at faults. Wadsack[14] introduced the non-classical stuck-open fault. This condition is defined as the open or high state impedance. Stuck-open faults are the result of missing connections to gate, source, or drain of FET. Non-classical faults cause combinational circuits to behave in a sequential way. However, Wunderlich and Rosenstiel[15] proved that for dynamic circuits these type of faults will not cause sequential behaviour.

Relation of physical faults to fault models and their classification is given in Appendix B. In our analysis the following faults will be studied:

a. Short between gate and drain.

- b. Short between gate and source.

- c. Short between drain and source.

- d. Open gate.

- e. Open drain.

- f. Open source.

- g. Inputs stuck-at.

- h. Outputs stuck-at.

Appendix C gives detailed analysis of the above mentioned faults, their manlifestation in the adders' circuits, and the test vectors to detect them. The work

is comprehensive and have been put in the appendix to focus this chapter only on

the conclusion of the analysis work.

### 4.3. FAULT MODEL

As mentioned in the previous section, the faults that we are going to cover include shorts (between gate and drain, gate and source, and drain and source), opens (in gate, drain, and source), and stuck at faults. Based on the fault analysis supplied in Appendix C, faults manifest one of three states. The first manifestation gives the effect of the unit's output being stuck-at-1, the second gives a stuck-at-0 effect, and the third gives intermediate values (such as soft 1's, or soft 0's). A summary of these manifestations follows for various units of the 4-bit partial adder and the full 4-bit adder. For more understanding of how these conclusions were drawn, please refer to Appendix C.

# 4.4. FAULT MODELS FOR 4-BIT PARTIAL ADDER

In the following sections the fault model of each module of the adder is given.

### 4.4.a. CARRYB GENERATION

The effect of various faults is grouped into:

### A. Faults that give the effect of output being stuck-at-1:

- 1. Inputs s-a-0.

- 2. Outputs s-a-1.

- 3. Short between gate and source in any of the nmos (this would cause the carryb's above the faulty nmos to become s-a-1, while those below will behave normally, meanwhile the carryb connected to the source of the faulty nmos, will vary between 1 and 0 depending on the value of the input).

- 4. Short between drain and source in the charging pmos would cause the carryb connected to the faulty pmos drain to be s-a-1, while those below it might have intermediate values depending on the inputs.

- 5. Open in ground connection of the discharge nmos.

- 6. Open in gate connection of the discharge nmos.

- 7. Open in input connection to any of the nmos's gate.

- 8. Open in source connection of any nmos.

### B. Faults that give the effect of output being stuck-at-0:

- 1. Inputs s-a-1.

- 2. Outputs s-a-0.

- 3. Short between drain and source in any of the nmos (again here the carryb's above the faulty nmos will be affected depending on the input values, while those below it will be unaffected).

- 4. Open in drain connection of any pmos.

# C. Faults that give outputs with intermediate values:

1. Short between drain and gate of any nmos.

- 2. Short between gate and source of input nmos (this would affect the carryb that is connected to the source of the faulty nmos and those below it whenever the input to that faulty nmos is 1).

- 3. During low clock with a short between source and drain of the discharge nmos. This, however, will have no effect on the circuit behaviour during evaluation phase, but it can be seen that the domino concept is no longer applicable.

- 4. Short between drain and source in charging pmos (this will affect the carryb's below the faulty pmos).

- 5. Open in drain connection of any nmos would cause the carryb connected to the faulty nmos to be floating, while the carryb's above it would be kept at 1.

- 6. Open in gate connection of any the charging pmos.

### 4.4.b. INVERTER

In the inverter the manifestation of faults is grouped into:

- A. Faults that give the effect of outputs stuck-at-1:

- 1. Input s-a-0.

- 2. Output s-a-1.

- 3. Short between gate and source of nmos.

- 4. Short between drain and source of pmos.

- 5. Open in ground connection of nmos.

- 6. Open in nmos gate connection.

- B. Faults that give the effect of output being stuck-at-0:

- 1. Input s-a-1.

- 2. Output s-a-0.

- 3. Short between gate and source of pmos.

- 4. Short between drain and source of nmos.

- 5. Open in Vdd connection of pmos.

C. Faults that give intermediate values for the output. This basically includes an open in the pmos gate connection.

In addition to these three groups, the inverter manifests a fourth type of error, which is the its falling to invert the input. This happens whenever a short between gate and drain occurs in either the pmos or the nmos of the inverter.

#### 4.4.c. XOR

Due to the nature of the static XOR, even though the faults manifest the same three values of output, they cannot be grouped since they depend on the different combination of inputs and the same fault could give different manifestations with different combinations of input.

#### 4.5. FAULT MODELS FOR FULL 4-BIT ADDER

In the following sections a summary of the manifestations of various faults in the adder's different units, and the units' fault models are presented. The effect of faults is grouped into: output stuck-at-1 effect, output-stuck-at-O effect, and output having intermediate values.

#### 4.5.a. GEN:P&G

The effect of various faults on the Gen:P&G block (this does not include the XOR faults' effect as they are the same as the previous XOR given in the fault tolerant 4-bit partial adder) is grouped into:

A. Faults that give the effect of output being stuck-at-1:

- 1. Inputs s-a-1.

- 2. Output s-a-1.

- 3. Output of small totem pole (or input to inverter) s-a-0.

- 4. Short between gate and source in inverter nmos.

- 5. Short between drain and source in any of the totem pole nmos's.

- 6. Short between drain and source of inverter pmos.

- 7. Short between gate and drain in any of the totem pole nmos's (whenever the input to that faulty nmos is 0).

- 8. Open drain connection of charging pmos.

- 9. Open in GND connection of inverter nmos.

- 10. Open in the gate connection of the inverter nmos

- B. Faults that give the effect of output being stuck-at-0:

- 1. Inputs s-a-0.

- 2. Output s-a-1.

- 3. Output of small totem pole (or input to inverter) s-a-1.

- 4. Short between gate and source in any of the totem pole nmos's.

- 5. Short between gate and source of inverter pmos.

- 6. Short between drain and source of charging pmos.

- 7. Short between drain and source of inverter nmos.

- 8. Short between gate and drain in any of the totem pole nmos's (whenever the input is 11).

- 9. Open in GND connection of discharge nmos.

- 10. Open in the gate connection of any of the totem pole nmos's (including the discharge nmos).

- 11. Open in the source connection of any of the totem pole nmos's.

- 12. Open in the VDD connection of the inverter pmos.

### C. Faults that give outputs with intermediate values:

- 1. Short between drain and source in discharge nmos (seen during low clock only).

- 2. Short between gate and drain in inverter nmos or pmos.

- 3. Open in gate connection of inverter pmos.

- 4. Open in gate connection of charging pmos.

### 4.5.b. **GEN:CAR**

The effect of various faults is grouped into:

- A. Faults that give the effect of output being stuck-at-1:

- 1. Inputs s-a-1.

- 2. Outputs s-a-1.

- 3. Outputs of totem pole (or inputs to inverters) s-a-0.

- 4. Short between gate and source in inverter nmos.

- 5. Short between drain and source in any of the totem pole nmos's.

- 6. Short between drain and source of inverter pmos.

- 7. Open in drain connection of any of the charging pmos.

- 8. Open in GND connection of inverter nmos.

- 9. Open in gate connection of inverter nmos.

- B. Faults that give the effect of output being stuck-at-0:

- 1. Inputs s-a-0.

- 2. Outputs s-a-1.

- 3. Outputs of totem pole (or inputs to inverters) s-a-1.

- 4. Short between gate and source in any of the totem pole nmos's.

- 5. Short between gate and source of inverter pmos.

- 6. Short between drain and source of any charging pmos (for the

carry's above the faulty pmos, and the carry connected to the faulty pmos drain).

- 7. Short between drain and source of inverter nmos.

- 8. Open in GND connection of discharge nmos.

- 9. Open in gate connection of discharge nmos.

- 10. Open in source connection of any of the totem pole nmos's.

- 11. Open in VDD connection of inverter pmos.

- 12. Open in gate connection of any of the totem pole nmos's.

### C. Faults that give outputs with intermediate values:

- 1. Short between drain and source in discharge nmos (seen during low clock only).

- 2. Short between gate and drain in inverter amos or pmos.

- 3. Short between gate and drain of any of the totem pole nmos's.

- 4. Short between drain and source of any of the charging pmos (for the carry's below the faulty pmos).

- 5. Open in gate connection of inverter pmos.

- 6. Open in gate connection of charging pmos.

- 7. Open in drain connection of any of the totem pole nmos's.

### 4.5.c XOR

The faults manifestation for the XOR was already given before, in the fault analysis of the 4-bit partial adder.

In the following chapter, the design of the fault tolerant adders will be given, based on the fault models that were given in this chapter.

### CHAPTER 5: FAULT TOLERANT ADDERS DESIGN

## **5.1 INTRODUCTION**

In this chapter the design and analysis of two fault tolerant adders (based on the previous design of the 4-bit partial adder and full 4-bit adder and the previous fault models) is presented. A study of the available fault tolerance techniques is first given, followed by the design and the simulation results of the two adders.

# 5.2. FAULT TOLERANCE TECHNIQUES

Achieving increased reliability could be done through one of two approaches: fault avoidance (fault intolerance) and fault tolerance[21]. In this section, fault tolerance techniques will be presented, as our goal is to design a fault tolerant system.

Ever since the idea of introducing redundancy to improve the reliability of systems originated in the 1950's, redundancy has been recognized as a realistic means for constructing reliable systems[22]. In fault tolerant designs redundancy is used to provide information necessary to negate the effect of the failures.

Redundancy is manifested in two ways: extra time, or extra components[21]. Time redundancy involves the repetition of computations in ways that allow errors to be detected, thus it attempts to reduce the amount of extra hardware at the expense of using extra time[23]. Component redundancy, on the other hand, involves the use of extra gates, functional modules, and the like to supply the extra information needed to guard against the effect of failures[21].

The fundamental concept of time redundancy is to perform the same computation two or more times and compare the results to determine if a discrepancy

exists. If an error is detected, the computations are repeated to see if the error still exists. This approach is seen to be useful for detecting errors resulting from translent faults.

On the other hand, alternating logic[24], recomputing with shifted operands (RESO)[25], recomputing with swapped operands (RESWO), and recomputing using duplication with comparison (REDWC)[23], have the ability to detect permanent faults. However, most of the time redundant techniques require a considerable amount of extra circuitry (100% increase in alternating logic technique to make a circuit self dual, added circuitry such as shifters and registers in order to implement RESO, RESWO), besides, being able to only detect faults and not correct them.

The time redundant approach, however, can be used for error correction, if the computation is repeated three or more times, then the results are compared, and the error is corrected using a majority voter[26]. Another method for error correction was given in[27], where the computation is carried twice to detect any discrepancy (based on RESO method), and once an error was detected, a third rotation and a third computation is carried out.

Hardware redundancy has become more practical as the semiconductor components have become smaller and less expensive. There are three basic forms of hardware redundancy[21,26].

Passive techniques, which involves masking the faults in order to hide the occurrence of faults and prevent the faults from giving erroneous results, include N modular redundancy and voting (NMR), error correcting codes, and masking logic.

Active techniques, or dynamic redundancy, achieves fault tolerance through detecting the existence of faults, and performing some action to remove the faulty hardware from the system. These techniques include reconfigurable

duplication, reconfigurable NMR, backup sparing, and graceful degradation.

Hybrid techniques combines both the passive and active approaches. Fault masking is used to prevent the faults from generating erroneous results, while fault detection, location, and recovery, are used to improve the fault tolerance by removing faulty hardware and replacing it with spares.

## 5.3. DESIGN OF A FAULT TOLERANT 4-BIT ADDER

In the following sections the design of a fault tolerant 4-bit partial adder is given, based on the previous design of our 4-bit partial adder. We begin by introducing the fault tolerance approach that will be implemented. The design of the various adder circuitry (used to achieve fault tolerance) is given, together with the complete design of the fault tolerant adder. Finally, simulation is carried out to see the adder's behaviour in the presence of various faults, followed by a comparison with Triple Modular Redundancy.

#### 5.3.1. FAULT TOLERANCE APPROACH

In order to achieve fault tolerance, hardware redundancy, as opposed to time redundancy, was chosen to correct faults effects, as the area of the circuit is fairly small, besides, opting for speed.

With duplication, we can only detect the occurrence of a fault in either modules. Our approach was to add to the error detection module additional circultry that would enable the choice of the correct value from the two available results of the two modules whenever possible.

In the design, each part of the circuit (carryb generation, inverters, and XOR's) is duplicated, then the results are compared and corrected if necessary. This approach does not allow a fault that happens in one module to propagate to the following modules thus making the correction circuits more simple, and the

percentage of fault tolerance even higher.

To decide which of the two available values is correct, we are going to use two different approaches. The first one is to make use of the fault analysis that was done, in order to determine on a statistical basis, which are the most likely faults to occur and their manifestation in the circuit, so that to choose the right value. It can be seen that this approach will not achieve a 100% fault tolerance, but, it will achieve a percentage of fault tolerance proportional to the number of most likely faults to occur, beside, being simple and easy to implement. The second one, is based on the fact that knowing the correct value, we can simply pick the correct value. This approach offers a very high percentage of fault tolerance, as the correcting circuit will be able to select the correct value of the two available results, as long as the two results do not have the same faulty value, regardless of the type of fault that caused the erroneous result, but, it can be implemented only with small circuits, as otherwise with large circuits, the involved circuitry will be too complicated.

In the design of our fault tolerant adder, the first approach was used to achieve fault tolerance in the carryb generation unit, while the second approach will be used for both the inverters set, and the XOR's set.

We assume that no faults will occur that will affect the clock signal, i.e. faults such as short between gate and source or between gate and drain of any of the charging pmos's or the discharge nmos will be considered not to occur. The second assumption is that, for the carryb generation unit, inverters and the XOR's, no two modules fail at the same time such that the values of the two outputs are erroneously identical. This assumption does not imply single fault assumption (as will be seen later, the fault tolerant addrers will be able to tolerate multiple faults), it simply assumes that if faults occur in any two modules the manifestation of the faults will not be identical (for example one

module might manifest a stuck-at-1 value, while the other might give an intermediate value, as opposed to both modules simultaneously giving a stuck-at-1, or stuck-at-0 ... etc.). The third assumption is that correcting circuitry are assumed to be fault free. One last thing is that all global input signals are buffered, so that a fault in one module (e.g. short or open to that input signal line) will not affect another module that uses the same signal.

#### 5.3.2. FAULT CORRECTING CIRCUITS

In this section, the design for each fault correcting circuit will be given together with the various faults that it will cover.

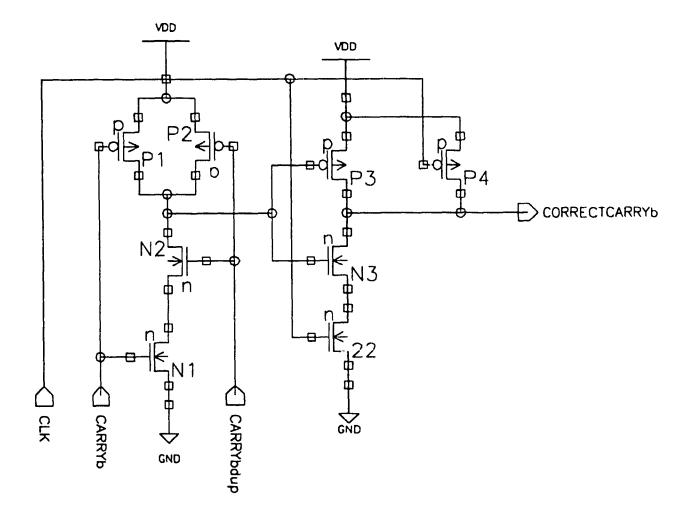

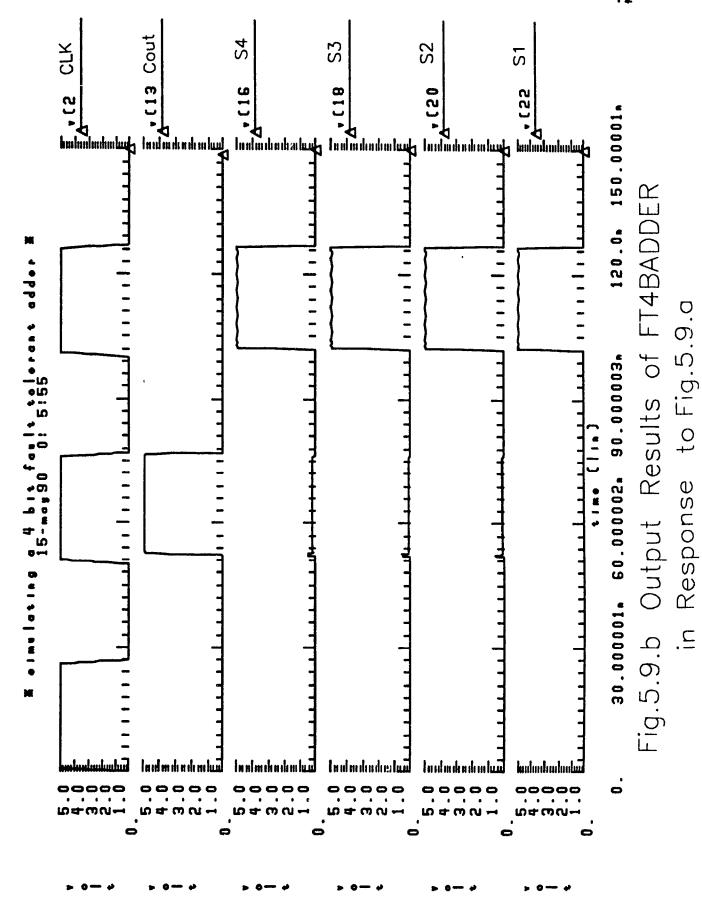

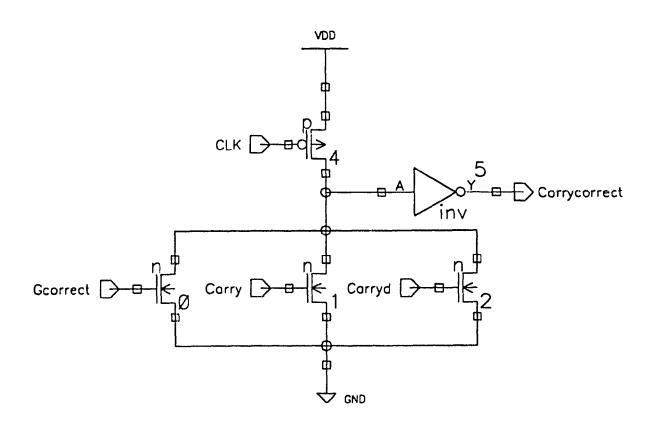

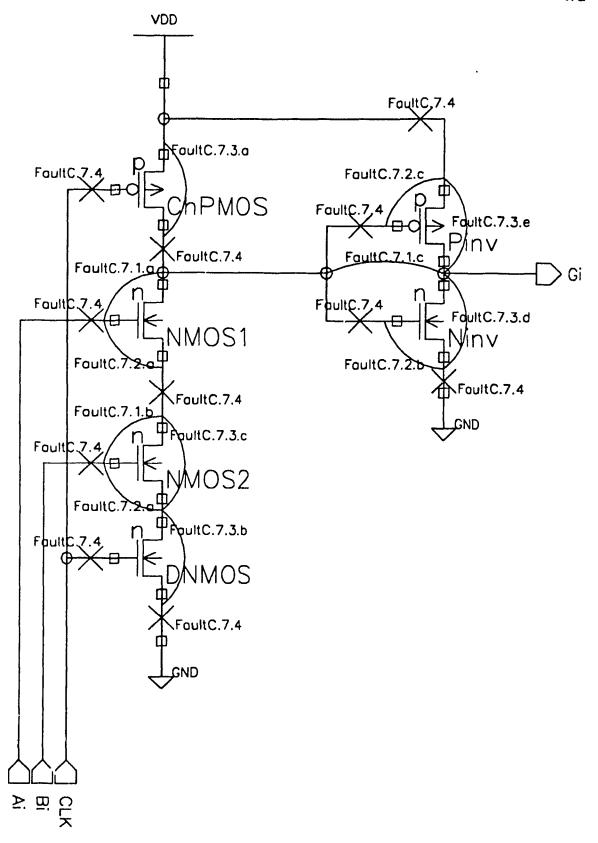

### 5.3.2.a. CARRYB GENERATION CORRECTION CIRCUIT

The circuit shown in Fig.5.1, shows a simple AND circuit that would choose a 0 whenever one or both outputs from the two carryb generation circuit is 0, and 1 with both outputs equal to 1.

In this circuit we introduced an additional pmos at the output, for the sake of controlling it in such a way that it will always be charged to 1 during low CLK signal, regardless of what the values of the carryb's being compared are, so that the output does not affect the following circuits or cause discharge problems, also this will cover the problem of having a short between drain and source of discharge nmos which invalidates the domino principle. Also, an extra nmos was introduced in series with the inverter nmos, and is controlled with CLK signal, in order to avoid a direct dc path to gnd that might occur in case either carryb or carrybdup or both of them become 0's during low CLK.

The faults that will be covered by this circuit include any fault that might cause the carryb to be erroneously stuck-at-1, and faults that result in an intermediate value where the correct value is 0.

Fig. 5.1 Carryb Correction Circuit (CARCORb)

Fig. 5.2 shows the result of the circuit simulation.

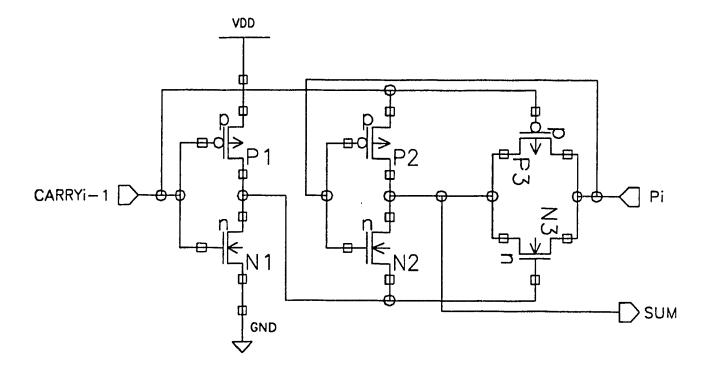

#### 5.3.2.b. INVERTER CORRECTION CIRCUIT

The second circuit to be discussed is the circuit used to correct the output of the inverter. As mentioned before, the design depends on the fact that knowing what the right value of the output should be, the circuit should be able to pick the correct value from the available outputs. The circuit implements the following function:

$$Correct carry = \overline{Correct carry b} (Carry 1 + Carry 2)$$

Where correct carryb is the correct carryb generated by the totem pole and corrected by the carryb correct circuit. Carry1, and carry2 are two outputs from two inverters inverting simultaneously correct carryb.

Fig. 5.3 shows the inverter correction circuit.

The circuit would be able to correct any fault occurring in either inverter, so long as both inverters do not fall simultaneously with a failure that makes them both result in the same erroneous value. However, this circuit is weak due to the presence of an inverter in its serial path, which in a way defeats what we are trying to do.

Fig. 5.4 shows the simulation results of the circuit. It should be noted that the test vectors given are for the sake of fully testing the circuit under all possible combinations, but in actuality, Correctcarryb will always be 1 during low CLK (it was taken care of that issue in the carryb correction circuit), thus avoiding a direct dc path to gnd when both carry and carydup are equal to 1 during low CLK.

Fig.5.3 Inverter Correcting Circuit (INVCOR)

Fig.5.4 Circuit Simulation for Fig.5.3

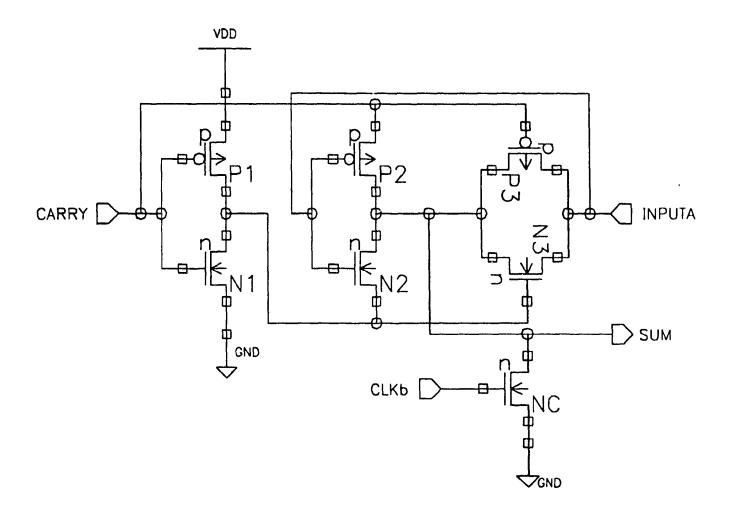

## 5.3.2.c. XOR CORRECTION CIRCUIT

Fig. 5.5 shows a slightly modified circuit for the static XOR that was used in the original adder circuit. An extra nmos (that is controlled by CLKb) is added at the output. The reason for that modification is to maintain the XOR output at 0 during low CLK so that no discharging problem would occur in the following XOR correction circuit.

As in the case of the inverter correction circuit, we again use the fact that knowing both inputs to the XOR, the correct resulting value could be known. With the outputs from two identical XOR's available, the XOR correction circuit implements the function:

Correctsum, =

$$(A_i \oplus C_{i-1})$$

(Sum 1 + Sum 2)

Where C is the correct carry resulting from the previous stage, sum1 and sum2 are the two outputs of two duplicate XOR's that are to be compared.

Fig. 5.6 shows the XOR correction circuit.

It could be seen that N3 and N4 implement the exclusive or part of the function, while N1 and N2 implement the oring part of it. Again the XOR correction circuit is able to cover any type of faults occurring in either XOR, even if different faults occur simultaneously in both XOR, so long as both XOR's do not result in identical erroneous results.

Fig. 5.7 shows the simulation results for the circuit. Again, it should be noted here that the test vectors given are for the sake of fully testing the circuit under all possible combinations, but in actuality, Sum1 and Sum2 will always be 0 during low CLK (it was taken care of that by adding extra nmos in XOR circuit as mentioned before), thus avoiding any discharge during low CLK.

Fig.5.5 Modified Exclusive Or Circuit

Fig.5.6 XOR Correcting Circuit(XORCOR)

Fig.5.7 Circuit Simulation for Fig.5.6

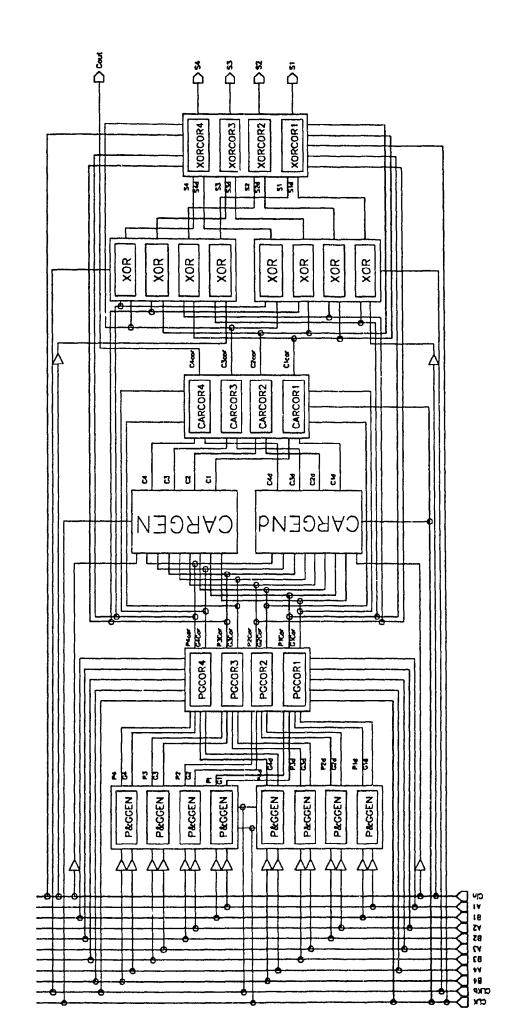

# 5.3.2.d. FAULT TOLERANT 4-BIT PARTIAL ADDER

Fig. 5.8 shows the complete adder, while Fig. 5.9.a shows a set of worst case test vectors. Results of simulation are shown in Fig. 5.9.b. From the simulation results, the complete adder gives a worst case propagation delay of 1.8ns. Worst case delay is considered to be for the carry signal to be produced correctly (that is from CLK to Carry4). This comes from 1.2ns delay to get the Carry4b correctly, plus 0.8ns delay to get the correct result from the inverter correcting circuit. The reason we did not take the CLK to Sum4 propagation delay as the worst case delay, is that, of the added circuitry, the output of XOR is kept low during low CLK, also, the carry signal being fed to the XOR is kept at 0 during low clock. So even though input A4 might reach the XOR during low clock, the output will be kept at 0 during that duration, therefore, abolishing the need to discharge the XOR output during evaluation period which was the case with our non-fault tolerant adder.

# 5.3.3. FAULT SIMULATION

Next, a set of faults were introduced to the circuit. These faults are:

- 1. An open fault in the drain connection of nmos N4, in carryb generation circuit (Fig.5.10).

- 2. A short between drain and source in discharge nmos NDd, in duplicate carryb generation circuit (Fig.5.10).

- 3. A short between gate and source of nmos Nil, in inverter circuit (Fig. 5.11).

- 4. A short between drain and source of nmos Nild, in duplicate inverter circuit (Fig.5.11).

- 5. A short between drain and source of nmos Nx1 in xor circuit (Fig.5.12).

- 6. A short between gate and source of nmos Nx2d in duplicate xor circuit (Fig.5.12).

Fig.5.9.a Input Test Vectors for FT4BADDER

```

* PROPAGATION DELAY BETWEEN CLK AND COUT*

delay1 = 1.8013E-09 targ= 5.2301E-08 trig= 5.0500E-08

*PROPAGATION DELAY BETWEEN CLK AND SUM4*

delay2 = 1.5870E-09 targ= 1.0209E-07 trig= 1.0050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM3*

delay3 = 1.5870E-09 targ= 1.0209E-07 trig= 1.0050E-07

*PROPAGATION DELAY BETWEEN CLK AND SUM2*

delay4 = 1.5870E-09 targ= 1.0209E-07 trig= 1.0050E-07

* PROPAGATION DELAY BETWEEN CLK AND SUM1*

delay5 = 1.5625E-09 targ= 1.0206E-07 trig= 1.0050E-07

```

Fig.5.9.c Summary of Simulation Result

Fig.5.10 Simulated Faults in Carryb Generation Block

Fig.5.11 Simulated Faults in Inverter Block

XOR Block Fig.5.12 Simulated Faults in

The effect of these faults could be seen as following:

#### A. For carryb generation circuit:

- 1. Due to the open drain connection in the first circuit carryb4 and carryb3, will always have a value of 1, which should have been 0 with test vector 11111. However, carryb2 and carryb1 will not be affected by that fault.

- 2. Due to the short between drain and source of discharge nmos in the duplicate circuit, the carryb's will never charge up during low clock.

### B. For inverter circuit:

- 1. Due to short between gate and source of nmos in first inverter, the output will be always stuck-at-1.

- 2. Due to short between drain and source of nmos in duplicate inverter, the output will be always stuck-at-0.

It should be noted that for the sake of simulation it is assumed that the faults in both inverter and duplicate inverter are repeated for the set of 4 inverters generating the carry's.

#### C. For exclusive or circuit:

- 1. Due to short between drain and source of nmos in the first inverter of the xor, the output of this inverter is always kept at 0, thus disabling the transmission gate nmos and causing the output to be a soft 0 (1v) to result with a 10 input to the xor.

- 2. Due to the short between gate and source of nmos in the second inverter of duplicate xor, with a 11 input to the xor, the transmission gate nmos will be turned on thus passing a faulty 1 to the output.

From the simulation results it could be seen that the carryb correction circuit was able to correct the faults that occurred in the carryb generation circuit and the duplicate one, thus passing a fault free set of carryb's to the inverter

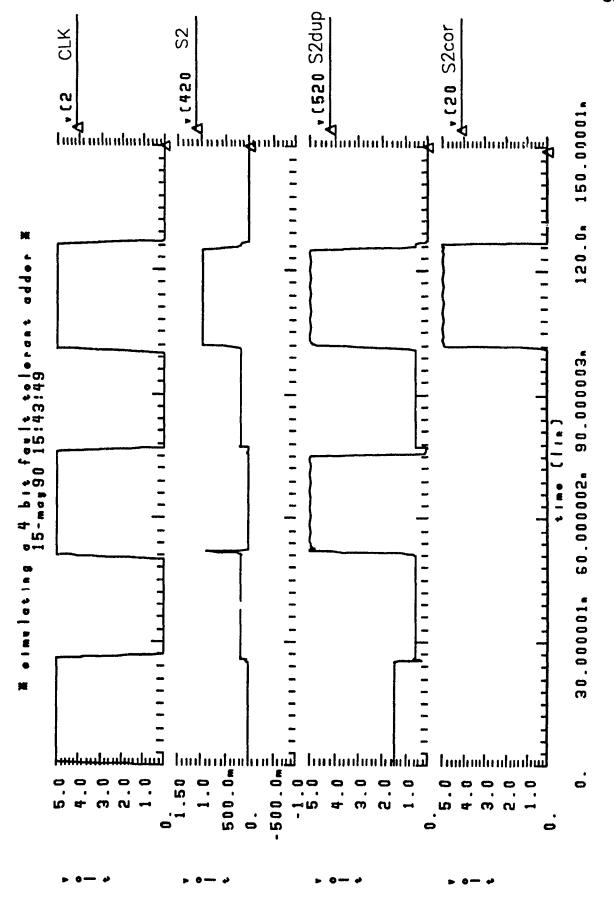

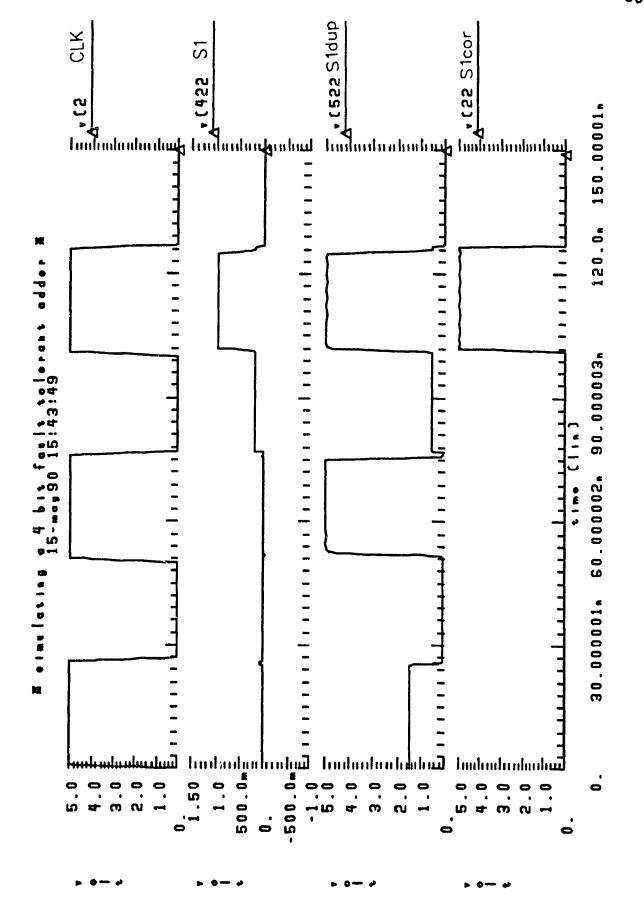

sets. Fig.5.13.a, 5.13.b, 5.13.c, and 5.13.d show the simulation results.

In the inverter stage, even though both inverters were giving stuck-at output values, however, the inverter correction circuit was able to correct these faults, and passed a set of correct carry's to the exclusive or stage. Fig.5.14.a, 5.14.b, 5.14.c, and 5.14.d show the simulation results.

In the third and final stage of the adder, the xor correction circuit corrected the faults occurring in both xor and duplicate xor, by depending on the fact that we have both inputs to the xor fault free and comparing the two available outputs to determine the correct sum values. Fig.5.15.a, 5.15.b, 5.15.c, and 5.15.d show the simulation results.

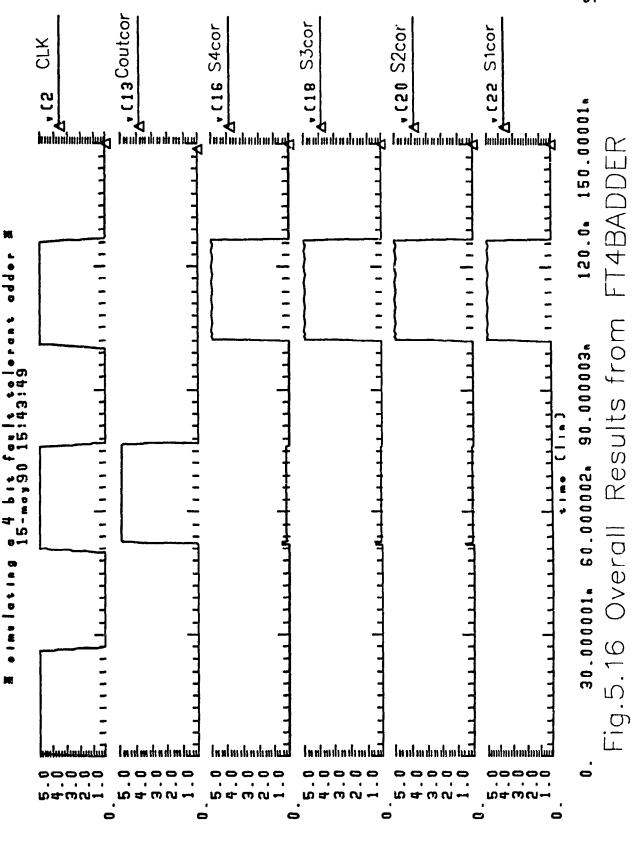

Fig.5.16, shows the final results of the simulation of the complete circuit (with faults), and it could be seen that all outputs are correct and match the fault free circuit results, in term of values and propagation delays.

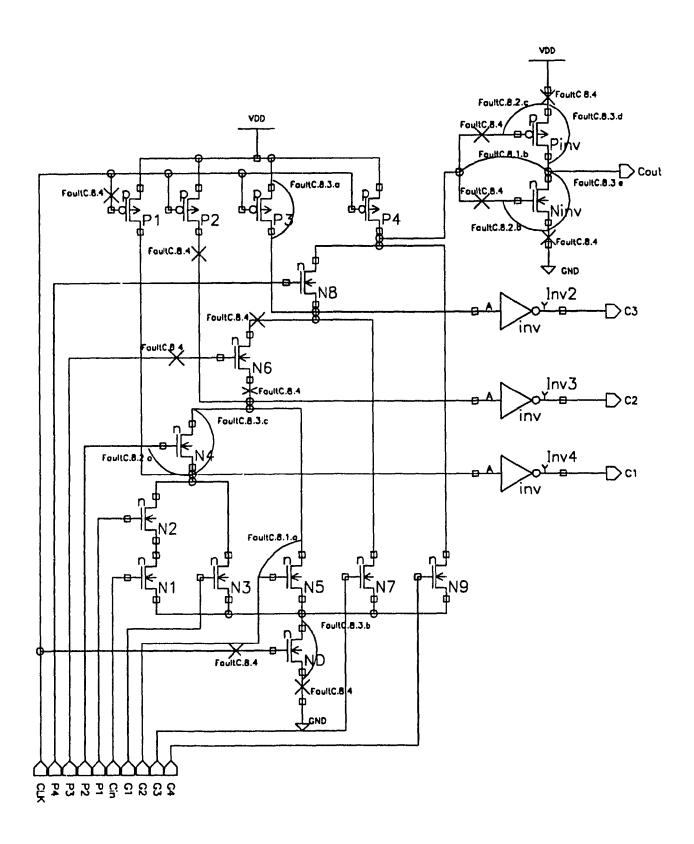

## 5.3.4. COMPARISON

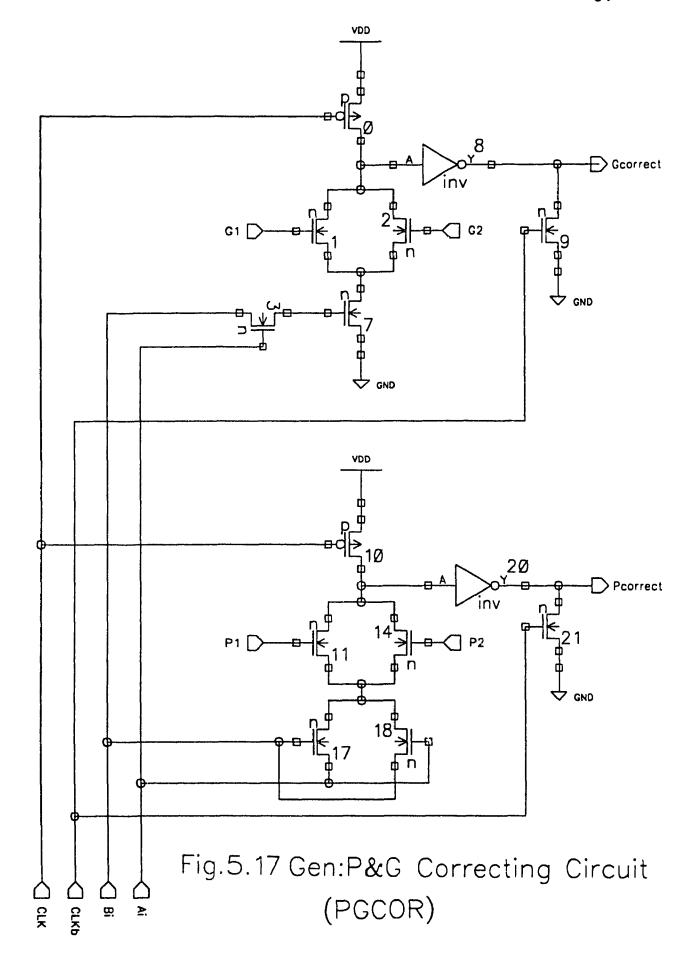

It could be seen that in dividing the original adder into three parts, the design of fault correction circuits became less complicated, and the fault coverage inadvertently increased.