# Compile-Time Scheduling of Digital Signal Processing Data Flow Graphs onto Homogeneous Multiprocessor Systems

#### Ali Shatnawi

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy at

Concordia University

Montréal, Québec, Canada

April 1996

© Ali Shatnawi, 1996

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliotheque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive Bibliothèque permettant à la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition thèse à la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-18441-2

#### ABSTRACT

Compile-Time Scheduling of Digital Signal Processing Data Flow Graphs onto Homogeneous Multiprocessor Systems

Ali Shatnawi, Ph.D. Conacordia Unviersity, 1996

The data flow graph (DFG) has proven to be an efficient model for the class of problems not involving data-dependent decision-making operations, such as those in most digital signal processing (DSP) applications. It has the inherent property of exposing the parallelism in the algorithms as it does not impose unnecessary constraints other than those imposed by the data precedency among the operations.

This thesis is concerned with finding a compile-time (static) schedule for DFGs representing DSP algorithms onto multiprocessor systems. It concentrates mainly on producing a rate-optimal schedule that achieves the minimum iteration period known as the iteration period bound. The problem of optimizing the I/O delay is also considered. Regardless of the optimality criteria used, minimizing the number of processors is one of the main concerns.

The problem of scheduling consists of two phases: (1) the time scheduling phase where the tasks of the DFG are scheduled in the time domain such that the precedency constraints are satisfied and the iteration period bound achieved assuming an infinite number of resources, and (2) the processor assignment phase where the time schedule is mapped onto a matrix in the time-processor discrete space.

A combinatorial theory is developed to produce a rate- and delay-optimal time schedule for a fully specified DFG. A rate-optimal time schedule is obtained analytically by a cyclic to acyclic transformation through a sequence of critical-circuit contractions. It is also shown that it is always possible to achieve both the rate and the delay optimality simultaneously, and a technique to ensure it is presented. An algorithm is then presented to map the time-schedule to a processor assignment. Further, a technique is proposed to reduce the number of processors, which often results in achieving the processor bound. Several examples are considered to illustrate the efficiency of the technique proposed. Finally, it is shown that the overall order of time complexity is lower than those of the existing techniques for most applications.

To My Late Mother

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude and heartfelt thanks to my thesis supervisors Drs. M. O. Ahmad and M. N. S. Swamy for their interest, guidance and constructive criticism throughout this work. Their advice, encouragement and close support have been invaluable.

I gratefully acknowledge the support of Jordan University of Science and Technology through a scholarship. This work was also supported in part by NSERC and FCAR through grants awarded to my thesis supervisors.

It is my great pleasure to thank my friends and colleagues at the Centre for Signal Processing and Communications for the many fruitful discussions which we have had during the course of this work.

Special thanks go to my family for their constant support and prayers, without which this work would not be possible. I owe special thanks to my wife, Faten, for her patience, encouragement and love. Her great effort in taking care (the lion share) of our daughter, Inas, has contributed a lot in giving me the peace of mind to complete this work.

# « وَمَا أُوتِيتُم مِّنَ العِلْمِ إِلَّا قَلِيلًا » الإِسرَاء آية م

"... of knowledge it is only a little that is communicated to you. (O men!)"

Holy Quran, Chapter 17. Verse 85.

"... And say, "O my Lord! advance me in knowledge."

Holy Quran, Chapter 20, Verse 114.

#### TABLE OF CONTENTS

| LI | ST O | F FIGURES                                      | `   |

|----|------|------------------------------------------------|-----|

| LI | ST O | F TABLES                                       | i   |

| 1  | Intr | roduction                                      | 1   |

|    | 1.1  | Programming Models                             | 3   |

|    | 1.2  | Graph Theory Background                        | S   |

|    | 1.3  | Thesis Objective                               | į)  |

| 2  | Rat  | e-Optimal Time Scheduling 2                    | 1   |

|    | 2.1  | The Scheduling Problem                         | 1   |

|    | 2.2  | Rate Optimality                                | 6   |

|    | 2.3  | Previous Work                                  | 8   |

|    | 2.4  | Time Scheduling Theory                         | .1  |

|    | 2.5  | The Critical Path Method                       | 7   |

|    | 2.6  | Examples                                       | 9   |

|    | 2.7  | Summary 6                                      | 7   |

| 3  | Del  | ay Optimal Schedule 6                          | 9   |

|    | 3.1  | Rate- and Delay-Optimal Schedule               | 0   |

|    | 3.2  | Obtaining Delay Optimality                     | 3   |

|    | 3.3  | Effect of Delay-Optimality on Node Flexibility | 7   |

|    | 3.4  | Example                                        | 8   |

|    | 3 5  | Summary                                        | (٠) |

| 4 | Pro        | cessor Assignment                               | 84  |

|---|------------|-------------------------------------------------|-----|

|   | 4.1        | Processor Optimality                            | 85  |

|   | 4.2        | Processor Assignment Algorithm                  | 88  |

|   | 4.3        | The Clustering Technique                        | 92  |

|   | 4.4        | Examples                                        | 96  |

|   | 4.5        | Summary                                         | 104 |

| 5 | Per        | formance Evaluation of the Scheduling Technique | 106 |

|   |            |                                                 |     |

|   | 5.1        | Time Complexity                                 | 107 |

|   |            | Time Complexity                                 |     |

|   | 5.2        |                                                 | 116 |

| 6 | 5.2<br>5.3 | Comparison with Previous Work                   | 116 |

### LIST OF FIGURES

| 1.1  | A synchronous actor with one input edge and one output edge                        | 7  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Asynchronous actors (a) select and (b) switch                                      | 7  |

| 1.3  | An asynchronous DFG showing a conditional example                                  | 9  |

| 1.4  | An asynchronous DFG showing a loop example                                         | 10 |

| 1.5  | An inconsistent SDF graph                                                          | 12 |

| 1.6  | A consistent SDF graph                                                             | 13 |

| 1.7  | (a)A non-homogeneous SDF graph, and (b) its corresponding homoge-                  |    |

|      | neous SDF graph                                                                    | 15 |

| 1.8  | A graph showing an edge with an ideal delay of $n_\epsilon$ and its two end nodes. | 17 |

| 2.1  | A critical circuit                                                                 | 35 |

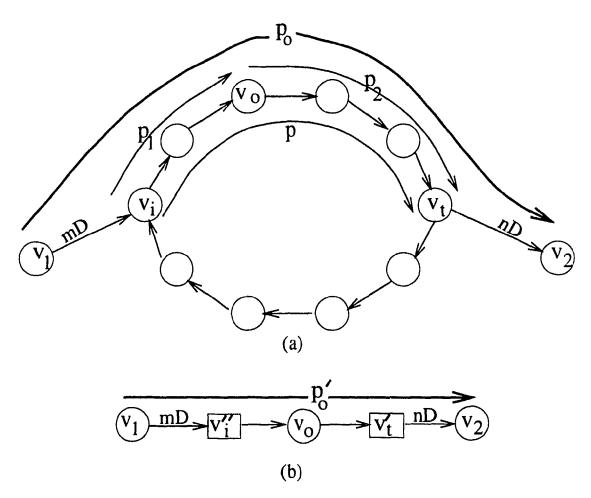

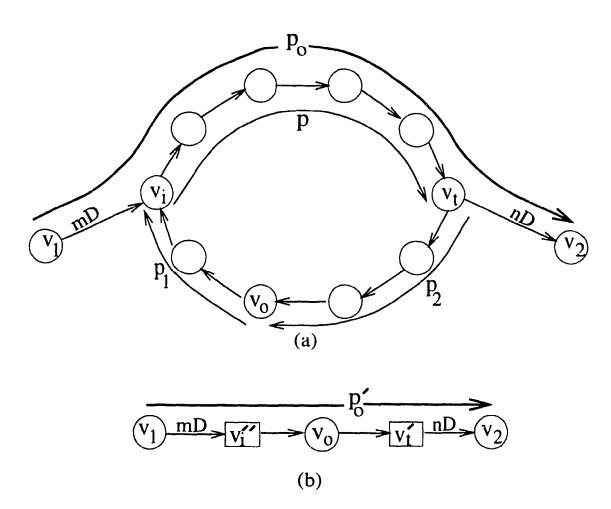

| 2.2  | (a) A subgraph before and (b) after the contraction of the shown circuit           | 41 |

| 2.3  | (a) A subgraph before and (b) after the contraction of the shown circuit           | 41 |

| 2.4  | (a) A subgraph before and (b) after the contraction of the shown circuit           | 45 |

| 2.5  | An illustration of the definitions used in the proof of Theorem 4                  | 48 |

| 2.6  | (a) A DFG segment after some circuit contractions, and (b) the corre-              |    |

|      | sponding time schedule                                                             | 56 |

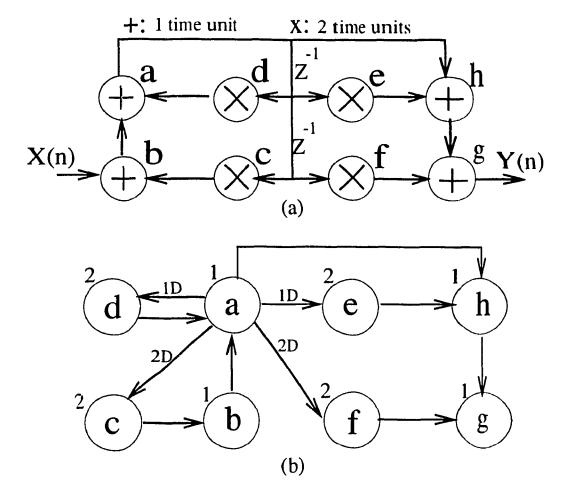

| 2.7  | (a) A second-order IIR filter, and (b) its DFG representation                      | 59 |

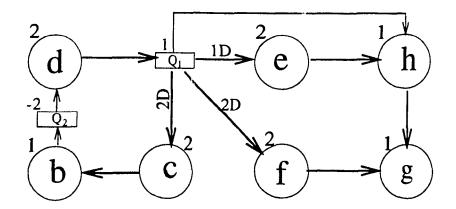

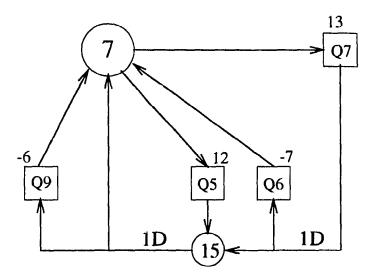

| 2.8  | The graph after contracting the circuit a-d-a to node d                            | 60 |

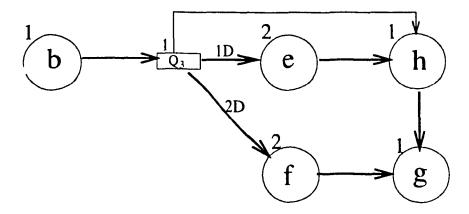

| 2.9  | The graph after contracting the circuit c-b-Q2-d-Q1-c (a-c-b-a in the orig-        |    |

|      | inal DFG) to node b                                                                | 61 |

| 2.10 | A time schedule for the second-order IIR filter                                    | 62 |

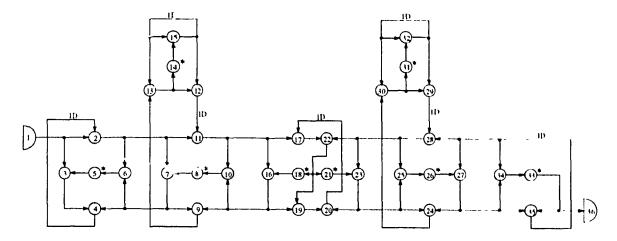

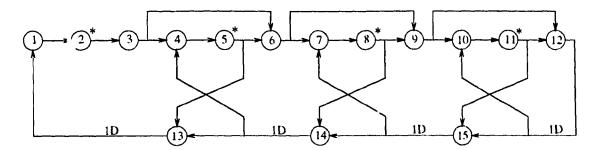

| 2.11 | A DFG of the fifth-order elliptic filter considered in Example 2                   | 63 |

| 2.12 | The DFG of the wave filter after contracting the circuit $C_1, \ldots, \ldots$  | 64 |

|------|---------------------------------------------------------------------------------|----|

| 2.13 | The DFG of the wave filter after contracting the circuit $C_2,\ldots\ldots$     | 64 |

| 2.14 | The DFG of the wave filter after contracting the circuit $C_3$                  | 65 |

| 2.15 | The DFG of the wave filter after contracting the circuit $C_4,\ldots$           | 66 |

| 2.16 | The DFG of the wave filter after contracting the circuit $C_5, \ldots, \ldots$  | 66 |

| 2.17 | A time schedule for the wave filter (T=16)                                      | 67 |

| 3.1  | An illustration used in the proof of Theorem 7                                  | 72 |

| 3.2  | A DFG in which the nodes of the non-critical circuit are all contained in       |    |

|      | a critical path                                                                 | 78 |

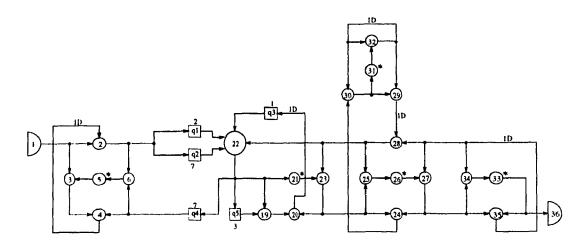

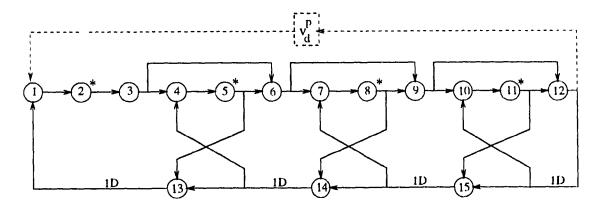

| 3.3  | A DFG of a fourth-order all-pole lattice filter considered in Example 2         | 79 |

| 3.4  | The DFG of a fourth-order all-pole lattice filter after introducing the delay-  |    |

|      | optimality path                                                                 | 79 |

| 3.5  | The DFG of the lattice filter after contracting the delay-optimality critical   |    |

|      | circuit                                                                         | 80 |

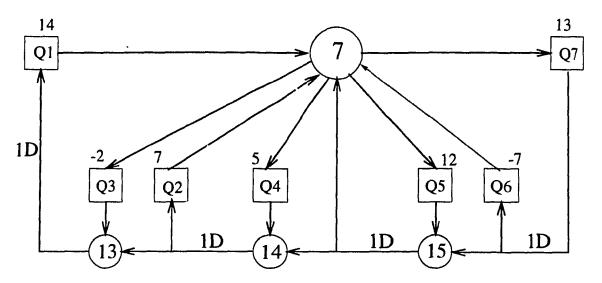

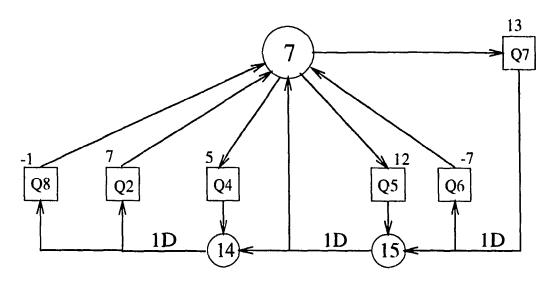

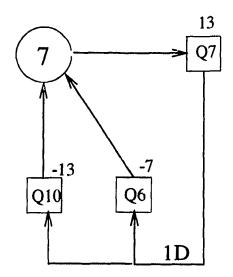

| 3.6  | The DFG of the lattice filter after contracting the circuit $7, Q_3, 13, Q_1$   |    |

|      | corresponding to the circuit 1,2,3,4,5,13 in the original DFG                   | 81 |

| 3.7  | The DFG of the lattice filter after contracting the circuit $7, Q_4, 14, Q_2$   |    |

|      | corresponding to the circuit 4,5,6,7,8,14 in the original DFG                   | 81 |

| 3.8  | The DFG of the lattice filter after contracting the circuit $6, Q_5, 15$ corre- |    |

|      | sponding to the circuit 7, 8, 9, 10, 11, 15 in the original DFG                 | 82 |

| 3.9  | A time schedule for the lattice filter DFG                                      | 82 |

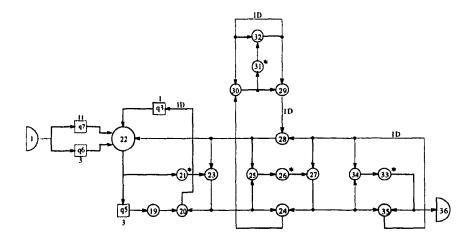

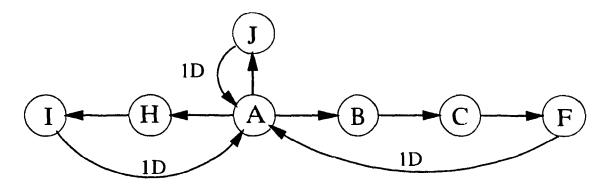

| 4.1  | A time schedule for the second-order IIR filter                                 | 96 |

| 4 9  | A processor assignment for the second-order IIR filter                          | 98 |

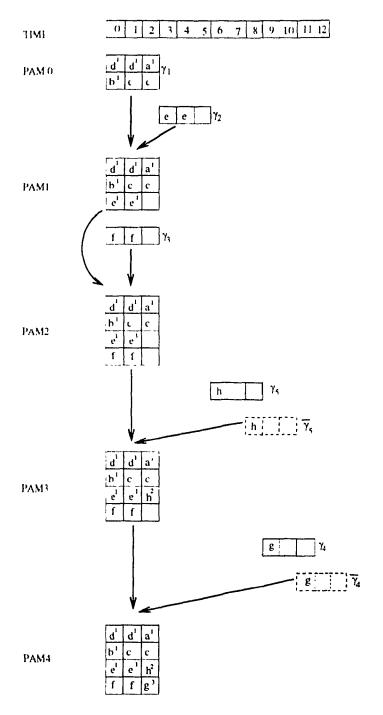

| 4.3  | The steps of applying the Clustering Algorithm to the DFG of the second-     |

|------|------------------------------------------------------------------------------|

|      | order IIR filter                                                             |

| 4.4  | An optimal processor assignment for the second-order IIR filter 100          |

| 4.5  | A processor assignment for the wave filter (T=16) 101                        |

| 4.6  | A time schedule for the wave filter (T=17),                                  |

| 4.7  | A processor assignment for the wave filter (T=17)                            |

| 4.8  | An optimal processor assignment for the wave filter (T=17) 103               |

| 4.9  | A processor assignment for the lattice filter DFG                            |

| 4.10 | A processor-optimal but not delay-optimal processor assignment for the       |

|      | lattice filter DFG                                                           |

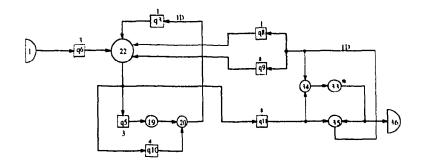

| 5.1  | A DFG which may not be scheduled processor-optimally by the critical         |

|      | path method                                                                  |

| 5.2  | A processor assignment for the DFG in Figure 5.1 as produced by the          |

|      | critical path method                                                         |

| 5.3  | A time schedule for the DFG in Figure 5.1 as produced by the Scheduling      |

|      | Algorithm                                                                    |

| 5.4  | An optimal processor assignment for the DFG in Figure 5.1 as produced        |

|      | by the Processor Assignment Algorithm                                        |

| 5.5  | A DFG which may not be scheduled processor-optimally by the range-chart      |

|      | technique                                                                    |

| 5.6  | The equivalent classes produced by the range-chart technique 12:             |

| 5.7  | The time schedule as produced by the Scheduling Algorithm 12:                |

| 5.8  | The processor schedule as produced by the Processor Assignment Algorithm 12: |

## LIST OF TABLES

| 2.1 | The scheduling times of the nodes of the IIR filter 62                   |

|-----|--------------------------------------------------------------------------|

| 2.2 | Distribution of shimming delays for the wave filter DFG (T=16) 65        |

| 2.3 | The contracted circuits in the DFG of the wave filter and their versions |

|     | prior to contraction                                                     |

| 1.1 | Distribution of shimming delays for the wave filter DFG (T=17) 102       |

| 5.1 | Comparison of several scheduling algorithms for cyclic DFGs [68]         |

# Chapter 1

# Introduction

For real-time applications which are computationally intensive, parallel processing solution is unavoidable, since physical constraints will eventually place a limitation on the performance of a single processor. Furthermore, due to the rapid advances in VLSI design and technology, and consequent decrease in the chip cost and size. parallel processing is becoming more attractive. Parallel processing and pipelining as two approaches utilizing concurrency benefit from the advancement in VLSI technology; however, they lead to more complicated programs. Increased parallelism in architectures means that algorithm designers have to be more concerned with vectorizing, pipelining, or finding systolic implementations for their algorithms. Hence, in order to utilize these sophisticated hardware resources, efficient software tools are required. As a matter of fact, the capabilities of the existing software are much lower than those of the available hardware. In other words, parallel processing systems which are already designed are under-utilized by the available software. This underutilization may be attributed to the following two reasons. First, researchers have been focusing their attention on designing general purpose architectures by either optimizing for the worst case conditions, or for the most frequent conditions: neither of these methods necessarily leads to optimizing an entire program for a given task. Second, the models used to represent the algorithms lack the feature of exposing their inherent parallelism. Adapting algorithms to parallel implementations is traditionally performed on a case-by-case basis [1]-[5]. Automated techniques for finding parallelism in algorithms have not made significant progress. Despite the fact that parallel processing affords an opportunity to improve computational performance, it requires more implementation effort.

The primary goal of parallel machines such as multiprocessors, vector machines, array processors, etc, is to exploit parallelism of algorithms. Along with introducing these machines, compilers have been developed to extract parallelism from programs written in conventional languages. Moreover, some languages such as Parallel C and Concurrent Pascal have been developed to deal with parallel systems. Researchers have realized the need for a radical departure from the conventional programming methodologies in order to utilize parallel resources efficiently. The most successful compilers either address only the modes of parallelism in pipelined and superscalar machines or restrict themselves to domain-specific areas such as signal processing.

A conventional way of representing concurrent tasks of an algorithm is accomplished by breaking down the algorithm into subtasks, and this technique is well known since the invention of the computer. This is achieved by breaking a program into subroutines; but, this technique is not very suitable for parallel processing implementations in view of the fact that such programs are written with sequential execution in mind. However, if the breakdown of the tasks of a program is done as a consequence of the programming model, we could expect more efficient utilization of concurrent resources.

## 1.1 Programming Models

A programming model is a set of program abstractions which provides the user a transparent view of the computer hardware/software system. Parallel programming models are those models which deal with programming of multiprocessors or multicomputers [6].

#### 1.1.1 Parallel programming models

In general, parallel programming models can be categorized into the following five groups [6]:

- 1. Shared-variable model: This model is mainly used in tightly coupled multiprocessors. It involves handling the issues of cache coherency, memory consistency, atomicity of memory operations, memory access protection, etc.

- 2. Message passing model: This model is used in a multicomputer system with interconnection network where messages between processing nodes are rooted. In this programming model, the program is distributed or duplicated over the processing nodes.

- 3. Data-parallel model: This model is suitable for single instruction multiple data (SIMD) computers, where one program is executed on several data sets. It could also be used in synchronized multiple instruction multiple data (MIMD) computers, where all processors execute the same program on different data.

- 4. Object oriented model: In this model, concurrency is exploited between objects which use message passing as inter-object communication. Objects, which are dynamically created and manipulated, are program modules that contain the working data along with the executable code.

5. Logic and functional programming models: Logic programming are models suitable for knowledge processing and artificial intelligence.

The programming model of our interest is the functional programming model. Functional programming is a model that describes a program by a set of functions. each having a set of inputs and outputs. Executing a function may not produce "side effects"; therefore, there is no notion of storage, assignment and branching. "Side effect" refers to the case where a program module writes to a memory location which may be used by other modules. In other words, a model is free of side effects if the modules of any program can only communicate through a priori specified communication paths. By having no side effects, functional programming models give a better chance for exploiting parallelism. Furthermore, parallelism is enhanced by the fact that regardless of the order of producing its operands, a function produces the same results. Data flow and single assignment languages are examples of functional languages.

#### 1.1.2 The data flow model

The basic premise behind data flow is that a node representing a task can be executed whenever its inputs are available. Data flow was originally thought of as a new architectural paradigm rather than a programming model for multiprocessors [7, 8]. Such architectures contain specialized hardware that execute their functions upon the arrival of operands on their inputs. In data flow architectures, data driven semantics is obviously implemented at a low level, namely the machine level. In contrast, data flow as a programming model permits to describe algorithms in such a way that implementations on a general purpose multiprocessor or a pipelined architecture becomes relatively simple.

The principal strength of data flow graphs is that they do not over-specify an algorithm by imposing unnecessary sequencing constraints between operators. Instead, they specify a partial order, where sequencing constraints are imposed only by data precedences. Since the representation does not over-constrain the order of operations, a scheduler has the freedom it needs to adequately exploit deep pipelines, to maximize the re-use of limited hardware resources, or to exploit parallel processing units.

A data flow language as a functional language is a model describing a set of functions performing some tasks with inter-relations represented by the flow of operands. This model of programming is suitable for representation by graphs. A graph which describes the data flow model is called a data flow graph (DFG). A DFG is a directed graph represented by the pair (V,E), where V is a set of nodes representing operations and E a set of edges representing communication paths.

Representing the data flow model by a graph stems from the following two reasons:

- 1. The concept of data flow is that the availability of operands enables the execution of a node; therefore, references to operands can be thought of as edges, which when loaded, fire the corresponding node.

- 2. Data flow graphs can be easily composed into larger ones. This can be accomplished by merging the output edges of one graph with the input edges of another according to the governing program.

The data items which are assumed to flow among the nodes through the specified directed edges are called tokens. An edge may be thought of as a FIFO (first in first out) queue which stores incoming operands and feeds them in sequence to the corresponding node every time it fires. A scalar node is one that has no input edges

and provides the same output value every time it is requested by another node. In this thesis, we will assume that the data flow model has no scalar nodes, instead we consider the scalar operands as a parameter embedded in the operation of a node itself. An input node is a queue that stores an input stream, while an output node is one which stores an output stream. The input and output nodes do not have the notion of firing, but they store the operands on arrival.

The data flow model has been used for many years [9]-[30] and has proved to be successful in exhibiting the parallelism of the algorithms. It does not impose unnecessary constraints other than those imposed by the data precedency among operations of an algorithm; consequently, the maximum concurrency is theoretically achievable. Moreover, the data flow model provides the user an opportunity to break down a program into tasks so that utilizing the resources becomes more feasible. Another appealing characteristic of the DFG model is that it permits several permissible firing sequences, that is, all firing orders of the actors of a given graph produces the same result as long as the data precedency is preserved.

#### General data flow graphs

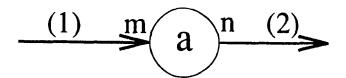

General DFGs are those which can represent any application on a general purpose computer system. Before giving details, we define the following terms. A synchronous actor is one, which upon firing, consumes a fixed amount (number) of data items from each of its input lines, and produces a fixed amount of data items on each of its output lines. A typical synchronous actor is depicted in Figure 1.1 where m and n are, respectively, the number of consumed and produced tokens upon the firing of the actor a.

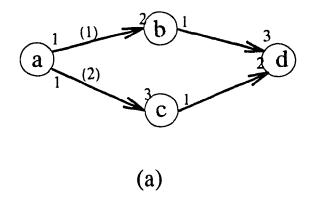

Figure 1.1: A synchronous actor with one input edge and one output edge.

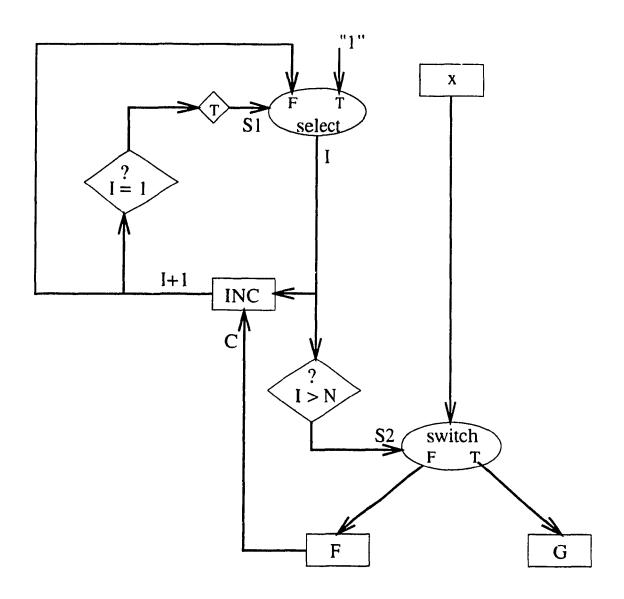

Figure 1.2: Asynchronous actors (a) select and (b) switch.

In contrast, an asynchronous actor consumes and/or produces a variable number of data items on at least one of its input or output lines based on some data-dependent control. Asynchronous actors are also called data-dependent decision making operators, because the behavior of the actor is based on a decision affected by some input data. Several models of actors have been adopted in the literature to represent data dependent flow. For the purpose of demonstration we will use the model adopted in [31]. This model consists of only two asynchronous actors namely switch and select. The select actor shown in Figure 1.2(a) consumes one input from either  $x_1$  or  $x_2$ , based on the consumed input from line C, and outputs it on line y. In other words, (a) it consumes C and (b) if C is true, then it consumes  $x_1$  and sets  $y = x_1$ ; otherwise it consumes  $x_2$  and sets  $y = x_2$ . The second asynchronous

actor, switch, shown in Figure 1.2(b) consumes x and outputs it to either  $y_1$  or  $y_2$  depending on the boolean value consumed at C, that is,  $y_1 = x$  if C is true; otherwise  $y_2 = x$ .

To illustrate how to use these actors to represent data-dependent flow, we give the following two examples written in C-like code.

```

Example 1. (Conditional) Input x; y1=A(x,c) If (c) y2=G(y1); else y2=H(y1); y=y2;

```

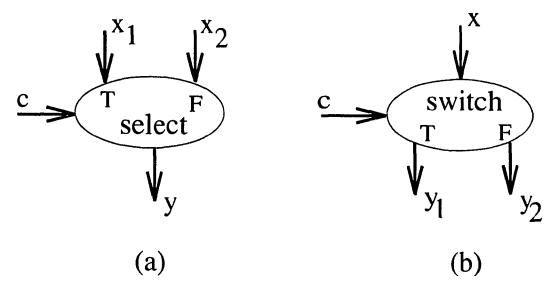

The conditional example is depicted in Figure 1.3 using data flow representation. The boolean output C of actor A controls the flow of  $y_1$  which is consumed by either actor H or actor G. S1, and S2 are, respectively, the control lines of the *switch* and the *select* actors. Both S1 and S2 will get the same boolean value as C; therefore, the select actor will select the output of the function (G or H) corresponding to the input  $y_1$  of the same instance.

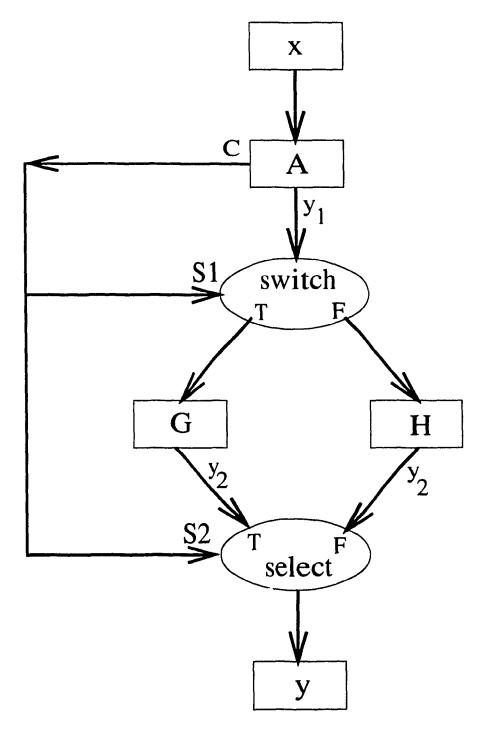

The data flow representation of the loop example is shown in Figure 1.4. The small diamond node is an initial condition on the edge: it is marked with T to denote a boolean input initialized by a token of value *true*. The large diamond

Figure 1.3: An asynchronous DFG showing a conditional example.

Figure 1.4: An asynchronous DFG showing a loop example.

actors are comparison actors which output boolean tokens depending on the input value relative to the indicated condition. Initially the select actor will select the value 1 for I because the consumed control on S1 has the value tree. As long as I is less than or equal to N, S2 will get a false value, and hence function F will consume the input x and execute. Executing function F, a dummy output is transferred as a control to the INC actor which then fires. The (I = 1) comparator will always generate a false value, that is, after the select actor consumes the value 1 for I, it will keep selecting the updated value of I. Once S2 gets a true token as I exceeds N, the switch will direct the input x to function G which then executes. Since F does not execute, no dummy control will reach INC and hence the loop action will halt.

General data flow graphs having data-dependent decision-making operations may not be scheduled at compile time, since the behavior of the actors is dependent upon some input data which may not be known at compile time. In this thesis, we are concerned with the problem of compile time scheduling, and hence, this type of graph will not be considered.

#### Synchronous data flow graphs

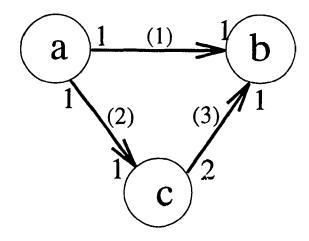

A graph whose nodes are all synchronous is called a synchronous data flow (SDF) graph. In other words, the amount of consumed tokens from each input and produced token on each output are known at compile time for a node in a SDF graph. A SDF graph is said to be consistent if in the long run the number of tokens consumed from an edge matches that produced on the same edge. An inconsistent SDF graph may require infinite resources to execute. Consider the inconsistent data flow graph shown in Figure 1.5. Upon the firing of actor a, one token will be produced

Figure 1.5: An inconsistent SDF graph.

on each of the edges (1) and (2). Hence, actor c will execute because it requires only one operand and as a result it will produce two tokens on edge (3). One of them along with the token on edge (1) will be consumed as actor b fine and one token will remain on edge(3). Consequently, for every sequence of firing actors a, b and c, one token will stack on edge (3) which means that the graph can not execute with finite memory on edge (3). This kind of a graph is inconsistent.

For large graphs, a systematic way of determining the consistency is required. Lee et al. have proved in [32] that the problem of checking the consistency of a SDF graph can be reduced to a problem of finding the rank of a matrix, called the topology matrix, denoted by  $\zeta$ . In this matrix the rows represent edges while the columns represent nodes. The matrix entry  $\zeta(i,j)$  represents the number of tokens produced on edge i when node j fires. The entry  $\zeta(i,j)$  is assigned a negative value if the tokens are consumed by node j. It has been proved in [32] that if the rank of the matrix  $\zeta$  is equal to (N-1), where N is the number of nodes, then the SDF graph corresponding to the topology matrix  $\zeta$  is consistent, otherwise it is inconsistent. As an example, consider the SDF graph shown in Figure 1.6. The topology matrix  $\zeta$

Figure 1.6: A consistent SDF graph.

for this graph is

$$\zeta = \begin{pmatrix} 1 & -4 & 0 & 0 & 0 & 0 \\ 1 & -4 & 0 & 0 & 0 & 0 \\ 1 & 0 & -1 & 0 & 0 & 0 \\ 0 & 4 & 0 & -2 & 0 & 0 \\ 0 & 4 & 0 & 0 & -1 & 0 \\ 0 & 0 & 2 & -4 & 0 & 0 \\ 0 & 0 & 2 & 0 & -2 & 0 \\ 0 & 0 & 0 & 1 & 0 & -1 \\ 0 & 0 & 0 & 0 & 1 & -2 \end{pmatrix} \begin{array}{c} edge \ 7 \\ edge \ 8 \\ \end{array}$$

The rank of  $\zeta$  is five which is equal to (N-1); therefore, the graph corresponding to  $\zeta$  is consistent.

In addition to using the topology matrix to determine the consistency, it can be used to determine the relative firing frequency of the nodes. Let q be an N-dimensional vector representing the relative firing frequency of the nodes in the SDF graph, then q can be obtained by solving the linear system  $\zeta q = 0$ . If  $\zeta$  is of rank N, then a nontrivial q does not exist. For the example of Figure 1.6, the smallest integer solution for q is  $q = [4 \ 1 \ 4 \ 2 \ 4 \ 2]'$  which means that if node q executes 4 times, the other nodes q and q will, respectively, execute once,

4 times, twice, 4 times and twice. The graph will return to its initial state after each iteration specified by the above frequencies

#### Homogeneous data flow graphs

A special case of SDF graphs is the homogeneous SDF graph in which every node consumes one token from each of its input edges and produces one token on each of its outputs edges. In this thesis, we are interested in this type of graph. A schedule of a homogeneous SDF graph contains one instance for each node, that is, q is a vector of ones. Unlike a general SDF graph, a homogeneous SDF can be scheduled for different optimality criteria. The reason behind the difficulty of optimal scheduling of a general SDF graph is that the instances of a node, with frequency other than unity, may need to be scheduled non-sequentially and on different processors to achieve the optimality criteria.

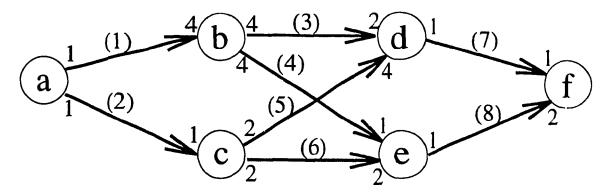

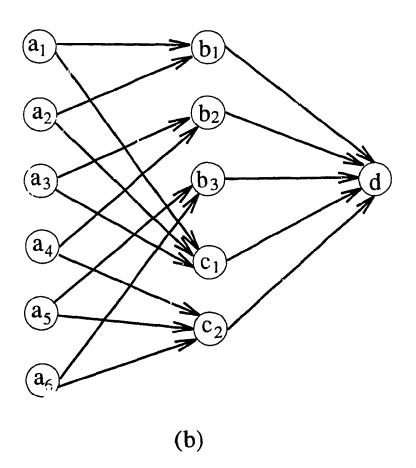

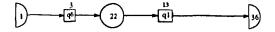

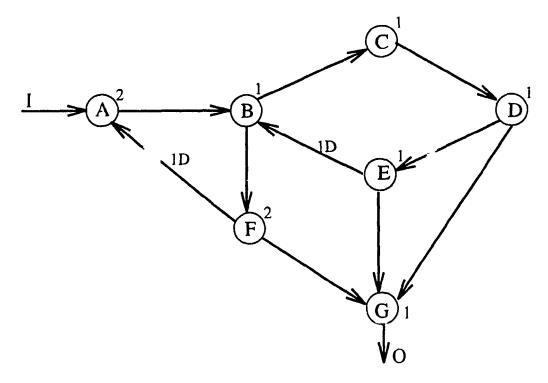

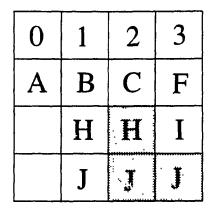

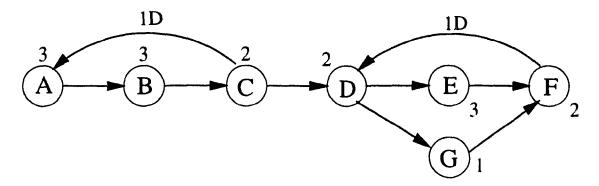

Fortunately, any consistent SDF graph can be transformed into a homogeneous SDF graph by replacing each node by  $q_t$  nodes and establishing the edge set based on the flow of operands among the different instances of each node [33]. We explain this transformation by an example. Consider the SDF graph shown in Figure 1.7(a). If the nodes are ordered as a, b, c and d, then  $q = [6 \ 3 \ 2 \ 1]$ . Since actor b requires two tokens from edge (1), while actor a produces only one token on edge (1), an instance of b requires the outputs of two instances of a. Using the same reasoning for the rest of the instances of each node, the resultant homogeneous SDF graph will be as shown in Figure 1.7(b). In the rest of this thesis we will only consider homogeneous SDF graphs, and refer to them, for simplicity, as DFGs.

Figure 1.7: (a)A non-homogeneous SDF graph, and (b) its corresponding homogeneous SDF graph.

#### DFGs representing DSP applications

Regardless of the model used to represent the algorithms, designing a general purpose parallel architecture that efficiently exploits their inherent parallelism is still a dream. If the domain of applications is not very wide, then utilizing the concurrency, reducing the hardware cost, and producing efficient software tools will all become relatively simple. In this thesis, we are interested in the class of digital signal processing (DSP) applications (filtering, adaptive filtering, decimation and interpolation, computation of autocorrelation, power spectrum estimation, transformations, etc.) that are computationally intensive, periodic, and involves no data-dependent decision-making. These characteristics are, as a matter of fact, very common in DSP algorithms, and hence it is possible to apply deterministic scheduling techniques at compile time for such applications. A program is said to be periodic if it is applied to an infinite input stream(s) producing an infinite output stream(s). The periodic nature of the applications gives another degree of parallelism: parallelism between iterations (an iteration is defined as the execution of the entire program to consume one input from each input line and produce one output on each output line), where operations between successive iterations can be overlapped. When the program involves no data-dependent decision-making operations, runtime overhead can be avoided, which means that scheduling can be completely accomplished at compile time. As a result of this automation, the hardware cost is substantially reduced and the performance improved.

Representing DSP programs by block diagrams is more natural than representing them by Fortran, although familiarity with Fortran may lead some to oppose this. The data flow graph, which belongs to the class of block representation languages, has proven to be an efficient model [32]-[41] for the representation of DSP

Figure 1.8: A graph showing an edge with an ideal delay of  $n_e$  and its two end nodes.

applications described above. In this model, a node has an associated positive integer number that represents the computational delay of its corresponding operation. The complexity of the operations is referred to as the granularity level. Operations might be atomic or compound. Atomic (indivisible) operations represent the basic machine operations like the addition and the multiplication. Compound or non-atomic operations might be macros, code segments, functions, iterations, FFT units, digital filters, etc. If all the operations in a data flow model are atomic then it is a fine grain model; otherwise, it is course grain model.

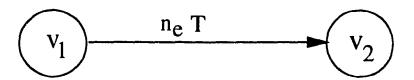

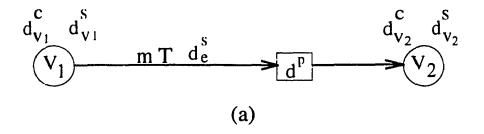

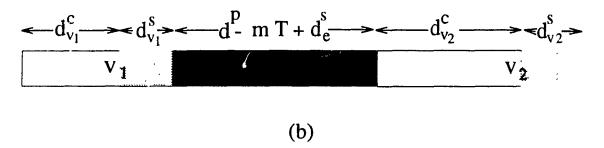

An edge has an associated nonnegative integer that represents its ideal delay. An edge with no ideal delay appearing in the graph is assumed to be of zero delay. If  $v_1$  and  $v_2$  are, respectively, the initial and terminal nodes of an edge with  $n_i$  ideal delays (see Figure 1.8), then the firing of node  $v_2$  at iteration i is dependent upon the availability of the output of  $v_1$  at iteration  $(i - n_e)$ .

The DFG considered in this thesis is assumed to be a proper graph, that is, there is a path to every node in the graph from an input node, and there is a path from every node in the graph to an output node. Throughout the thesis, without loss of generality, we assume that a DFG has one input node and one output node, since it can be easily transformed to become so even if the given graph has more than one input node or output node. For a graph having more than one input node, an artificial input with zero computational delay is added to the node set of the graph and a zero-ideal-delay edge is added from this node to each input node in the given

graph. In a similar manner, a graph having more than one output node is altered. We further assume that the edges in the DFG model have no communication delays as though all the nodes are assigned to a single processor. This assumption may sound too restrictive, but is really not so since the communication delays may be encapsulated with the computational delays of the nodes.

## 1.2 Graph Theory Background

In this section certain definitions from graph theory that are needed are now given [42].

A directed graph G=(V,E) is uniquely represented by its node set V(G) and its edge set E(G). An edge  $\epsilon=(v_I,v_T)$  is said to be incident out of its initial node  $v_I$ , and incident into its terminal node  $v_T$ . The initial and terminal nodes of an edge are said to be its end nodes. An edge is also said to be incident on its end nodes. Every node has an in-degree and an out-degree. The in-degree of a node is the number of directed edges incident into it while its out-degree is the number of directed edges incident out of it. Consider a subgraph G'=(V',E') where  $V'\subset V$ . Then G' is said to be a node-induced subgraph onto the node set V' if  $E'\subset E$  such that edge  $(v_i,v_j)\in E'\iff v_1,v_j\in V'$ . Let us use the operator  $\oplus$  to denote any set operation. The operation  $G_1\oplus G_2$  is assumed to be equivalent to the two operations:  $V(G_1)\oplus V(G_2)$ , and  $E(G_1)\oplus E(G_2)$ . Hence, the equation  $G_1\oplus G_2=G_3$  implies that  $V(G_1)\oplus V(G_2)=V(G_3)$ , and  $E(G_1)\oplus E(G_2)=E(G_3)$ .

A path p is a finite alternative sequence of distinct nodes and distinct edges beginning and ending with nodes. The path length, len[p], of the path  $p = v_1 \rightarrow v_2$ is defined as the minimum elapsed time between consuming the input operand(s) at its initial node  $v_1$  and producing an output at its terminal node  $v_2$  [43], that is,

$$len[p] = \sum_{\text{node } \nu_i \in V(p)} d_{\nu_i}^c - T \sum_{\text{edge } e_i \in E(p)} n_{e_i}, \tag{1.1}$$

where  $d_{v_t}^c$  is the computational delay of node  $v_t$ ,  $n_{e_t}$  the number of ideal delays of edge  $e_t$ , and T the iteration period. If in an iteration, the firing of the terminal node of a path p does not depend on the output of its initial node, then len[p] may be negative. We define len[p[, len]p] and len[p[ as the path lengths of the path p when the computational delays of its terminal node, initial node, and end nodes, respectively, are excluded. An elementary path whose initial and terminal nodes are identical is called a circuit. A DFG which contains at least one circuit is said to be a cyclic graph, otherwise it is acyclic.

## 1.3 Thesis Objective

The primary objective of this thesis is to seek a compile-time static schedule for completely specified data flow graphs on a parallel system. Since completely specified programs are very common in DSP applications, the scheduling technique is mainly concerned with DSP algorithms. The theory developed in this thesis (see also [44, 45, 46]) is amenable to a general DFG as long as the computational delays of all the nodes are known and there are no data-dependent decision-making operations.

The thesis is concerned with three different optimality criteria: rate-optimality, delay-optimality, and processor-optimality. These optimality criteria will be discussed thoroughly in the next three chapters. In Chapter 2, we first define the rate-optimality criterion, and review related work. Then, a theory for finding a

rate-optimal time schedule, without consideration to processor allocation, is presented. In Chapter 3, we present a theory and techniques necessary to modify the schedule developed in Chapter 2 so that delay-optimality is achieved. Chapter 4 deals with the mapping of the time schedule to a processor assignment with an objective to minimize the number of processors needed. In Chapter 5, performance analyses of the different algorithms presented in the preceding chapters are carried out, and a comparison with some related work presented. Chapter 6 concludes the thesis by highlighting the contributions of this study and making some suggestions for possible further work.

# Chapter 2

# Rate-Optimal Time Scheduling

The scheduling problem can be described by the 4-tuple (PS, TS, PQ, FQ), where PS is the set of processors, TS the set of tasks constituting a given program, PQ the sequence of processors to which the tasks are to be assigned, and FQ is the sequence of firing times of the tasks. Further, let  $TQ[P_k]$  be the ordered sequence of tasks which are allocated to processor  $P_k$ , that is, if the task  $s_t$  precedes  $s_t$  in  $TQ[P_k]$ , then processor  $P_k$  will execute the task  $s_t$  before executing  $s_t$ . For example, let  $PS = \{P_1, P_2\}$ ,  $TS = \{s_1, s_2, s_3, s_4, s_5, s_6, s_7\}$ ,  $PQ = \{P_1, P_1, P_2, P_1, P_2, P_2, P_2\}$  and  $FQ = \{t_1, t_2, t_3, t_4, t_5, t_6, t_7\}$ . This implies that the tasks  $s_1$ ,  $s_2$  and  $s_4$  are allocated to the processor  $P_1$ , and the tasks  $s_3$ ,  $s_5$ ,  $s_6$  and  $s_7$  to the processor  $P_2$ . Further, the task  $s_1$  fires at the time instant  $t_1$ ,  $s_2$  at  $t_2$ , an so on. If  $t_1 < t_2 < t_4$ ,  $TQ[P_1] = \{s_1, s_2, s_4\}$ ; and if  $t_3 < t_5 < t_6 < t_7$ , then  $TQ[P_2] = \{s_3, s_5, s_6, s_7\}$ . Hence, scheduling can be defined as the process of assigning tasks to processors, ordering their execution and specifying the times when they start execution. Whether PQ, FQ or TQ are determined at compile time or at run time, scheduling can be classified into the following categories [47, 34].

- Fully dynamic: An operation is assigned to a free processor at run time when all its operands are ready, that is, both PQ and FQ are determined at run time.

- 2. Static Assignment: Operations are assigned to processors at compile time. The availability of operands determines which operations to fire. That is, only PQ is determined at compile time.

- 3. Self timed: The tasks are assigned to the processor at compile time and their order of firing is also known before hand. The availability of operands determine whether to proceed with execution or to pause. That is PQ and TQ are determined at compile time but not FQ.

- 4. Fully static: The allocation of tasks to processors and the exact times of their execution are specified at compile time. That is, both PQ and FQ are determined at compile time.

For a periodic algorithm, the scheduling parameters are determined for one iteration and the complete schedule is constructed by a periodic repetition of a single iteration schedule. It is to be recalled that a periodic algorithm is applied to a stream of inputs to produce a stream of outputs by repeating the tasks of the algorithm on each and every input. In addition to the above scheduling schemes, periodic programs can be scheduled in a cyclo-static manner. Cyclo-static scheduling is similar to the fully static one except that in the former the tasks are periodic in the processor space. That is, a task may be allocated to different processors in different iterations according to some periodic vector that determines the processor displacement from iteration to iteration for each task [43, 48, 49, 50].

In general, for problems where scheduling at compile time is unattainable, many solutions have been proposed to solve the problem of data dependency at run time. Not surprisingly, most systems that execute operations in parallel have datadriven semantic models. As an example, a general purpose super-scalar pipeline processor uses the reservation-station technique to resolve data dependency among instructions. A pre-specified number of instructions are decoded without checking their data dependency and sent to reservation stations. Each instruction in a reservation station waits for its operands to be ready. An instruction having its operands ready waits for the appropriate functional unit to be free. The data dependency among the instructions waiting in the reservation stations is resolved by register renaming and/or scoreboarding techniques. More details about these techniques can be found in [6] and [51]. Obviously, an algorithm which has to be scheduled during run time (fully or partially) requires more hardware and/or software to dynamically resolve the issue of data dependency to ensure its correct execution. However, the overhead due to such dynamic behavior may be avoided for some algorithms if the scheduling can be completely accomplished at compile time. An algorithm can be fully scheduled at compile time if it has the following properties.

- 1. It has no loop for which the number of repetitions is not known before hand.

- 2. It has no branch instruction whose behavior (branch/proceed) depends on some value to be determined at run time.

- 3. It is a pure code, that is, it may not modify itself during run time.

- 4. Each operator in the algorithm has a fixed number of operands, that is, in an iteration, the number of consumed inputs as well as the number of produced outputs are fixed and known at compile time.

In a fully static schedule, also known as a completely specified static schedule, a task has two parameters which are specified at compile time: the firing time of its execution and the processor which will execute it. In this chapter, we focus on the first parameter, while the second is dealt with in Chapter 4. It is noted that the terms algorithm and DFG are used interchangeably. A schedule that gives the firing time instances of the tasks of a given algorithm without information about processor allocation is referred to as a time schedule. Hence, the principal objective of this chapter is to obtain a valid time schedule for an algorithm represented by a DFG.

The data dependency in algorithms represented by DFGs is inherently exposed by the programming model. Therefore, our task is not to extract the data dependency between actors but instead to schedule them in a way that achieves some optimality criteria without sacrificing the integrity of precedency among tasks.

In this chapter, we will first define the scheduling problem of a DFG on a multiprocessor and explain the implications of the different scheduling parameters. Also, more specifications about the DFGs of interest will be given. In Section 2.2, the rate optimality criterion will be discussed. The theory developed in this work to time schedule DFGs on multiprocessors will be the subject of Section 2.4.

# 2.1 The Scheduling Problem

A poor schedule for any system in general, and for a parallel one in particular, may violate the timing requirements or lead to an inefficient utilization of the resources. In the scheduling problem, therefore, we seek a schedule that respects the time requirements and at the same time utilizes, optimally or near-optimally, the resources of a given system. The problem of allocating tasks to processors and specifying at

compile time their firing times has been proved to be NP hard, that is, a problem that is not solvable by deterministic algorithms in a polynomial time [52, 53]. For such a problem, a heuristic solution is necessary.

The scheduling problem consists of a fully specified DFG representing a periodic algorithm, a set of identical processors and some optimality criteria. In the literature, a node in a fully specified DFG is assumed to have a single atomic operation. In this thesis, we relax the definition of a fully specified DFG by allowing nodes of multiple operations as long as the total computational delay of each such node is known for the underlying architecture. For the solution time to be possible at compile, the flow graph which describes the problem has to be deterministic and fully specified. For example, conditionals or decision nodes (nodes whose outcomes affect the flow of control) leading to non-deterministic problems may not be solved until execution time, thus precluding compile-time solutions. The processors are assumed to be identical to give flexibility for the tasks to run on any processor as long as their precedence requirements are satisfied. A schedule may be preemptive or non-preemptive. It is preemptive if the interruption of the tasks is permitted before being completed; otherwise it is non-preemptive. In general, a preemptive schedule is more efficient than a non-preemptive one unless the task switching cost (in terms of switching time and memory space) is relatively high [52]. In cases where task switching is costly, preempting is usually avoided.

The scheduling problem can be considered to consist of two phases, time scheduling and processor assignment. Time scheduling is concerned with specifying the firing time of each node in a single iteration assuming an infinite number of processors, while processor assignment is a mapping procedure of the nodes in the time schedule to a processor-time space. In this chapter, we present a new theory

along with an algorithm for finding a rate-optimal time schedule for a completely specified DFG.

# 2.2 Rate Optimality

In most real-time applications, the throughput is very critical to be maximized. It is to be recalled that the throughput, a performance measure, refers to the number of outputs per time unit. A schedule for a given algorithm is said to be  $rat\epsilon$ -optimal if and only if it achieves the maximum throughput, equivalently, minimizes the time between producing successive outputs. The time between successive outputs is referred to as the iteration period. Hence, a rate-optimal schedule should achieve the minimum iteration period, which is usually referred to as the iteration bound. For an acyclic DFG, the iteration bound is determined by the computational delay of the longest operation. This is so because, if enough computational resources are available, a pipeline with a number of stages equal to the number of operations can definitely achieve an iteration period equal to the computational delay of the longest operation. The minimum iteration period, however, could be less than the computational delay of the longest operation if more than one processor can share the execution of that operation.

For a cyclic DFG, the iteration bound is not only constrained by the hardware resources, but also by the topology of the graph. If the hardware resources are unlimited, the iteration period bound as constrained by the topology of the given graph is given by

$$T_0 = \max_{C \in ctrcuits} \left[ \frac{D_C}{N_C} \right], \tag{2.1}$$

where

$$D_C = \sum_{v_j \in V(C)} d_{v_j}^c,$$

and  $N_C$  is the total number of delays in the circuit C [54], which is given by

$$N_C = \sum_{e_i \in E(C)} n_{e_i}.$$

Although this bound has been given in the literature as an axiom, we like to provide the reader with some reasoning for this formula. Let A be a node in a circuit C. Obviously, the output token of node A at iteration i ( $A_i$ ) will propagate through the nodes of C (changes as per the functions of these nodes) and come back to A as an input needed for the computation of the  $(i + N_C)th$  iteration. The minimum time required for node A to provide its output at the  $(i + N_C)th$  iteration since outputting  $A_i$  is  $D_C$ . Therefore, at most  $N_C$  outputs can be produced by node A in  $D_C$  time units, and hence the above formula.

When there are some unbreakable operations with computational delays greater than the iteration period, the rate-optimal schedule is not achievable using fully-static scheduling. This is due to the fact that in fully static scheduling, an operation is assigned to a single processor and hence, has to be executed within the time limit determined by the iteration period. In this case, rate-optimality can be achieved using cyclo-static scheduling or scheduling via unfolding. Consequently, if the schedule is required to be fully static, the iteration bound has to be modified as

$$T_0' = \max\left(T_0, \max_{v_i \in V(G)} d_{v_i}^c\right). \tag{2.2}$$

A circuit C is called *critical* if its loop bound  $(D_C/N_C)$  is equal to the iteration period bound. A non-critical circuit has a spare-time called the *slack time*. The slack time of a circuit can be thought of as the total time during which none of the circuit operations is executed within one iteration period  $T_0$ , and is given by

$$ST(C) = T_0 N_C - D_C. (2.3)$$

It is clear from (2.3) and (1.1) that

$$ST(C) = -len[C]. (2.4)$$

If  $T_0$  is a non-integer, then unfolding is necessary to achieve the bound. A DFG is said to be k-unfolded if it has been unfolded k times, and k is called the unfolding factor. The k-unfolded DFG has an iteration period equal to  $(kT_0)$ , where  $T_0$  is the iteration period of the original DFG [55]. The unfolding factor can be expressed as

$$k = \frac{N_C}{GCD(N_C, D_C)}.$$

where GCD denotes the greatest common divisor, and  $N_C$  and  $D_C$  are, respectively, the ideal and the computational delays of any critical circuit [56]. For the fully-static schedule to exist, the iteration bound is given by (2.2), where  $T_0$  is replaced by  $kT_0$ .

## 2.3 Previous Work

In the literature different techniques have been developed to employ parallelism in the implementation of algorithms represented by DFGs [54].

1. Parallelism in a single iteration (intra-iteration parallelism): In these methods [57], a given cyclic DFG is first converted to an acyclic one which corresponds to the precedence graph of a single iteration. This conversion can be carried out by replacing each delay element by an input and an output node. Scheduling acyclic data flow graphs has been well studied in the literature [58, 59]. In general, techniques that first convert the cyclic graph to an

acyclic one prior to scheduling generate non-overlapped schedules, where the schedule for one iteration is periodically repeated. Since these methods do not utilize inter-iteration parallelism, they are, in general, incapable of producing schedulers with maximum throughput or optimal number of processors. Hence, these methods are not suitable for iterative algorithms in real time applications in which the throughput is a critical issue.

The parallelism in the resultant acyclic graph can then be exploited to minimize the schedule length by any of the following scheduling methods [54]:

- (a) Precedence graph method [60].

- (b) Precedence matrix method [61].

- (c) Critical path method [59, 62].

- (d) The method of Nouta and Simula based on the petri nets [63, 64].

The repetitive nature of the DSP algorithms is totally ignored (not utilized), if this technique is used for their scheduling.

2. Parallelism within a block of iterations [65, 66]: Before converting the given graph to an acyclic one, it is unfolded by some factor n. This kind of transformation helps capture more parallelism as concurrency can be utilized among the operations of n iterations. Although these methods do better job than those from the preceding category, they do not, in general, produce rate-optimal schedules for high sampling rate in reai-time applications.

This technique is known for implementations of DSP algorithms. Fore example, high speed filtering can be accomplished by processing sequences of input samples instead of one sample. In [67], high speed implementation for finite

convolution is done using Fourier transform. This method is efficient only if the transform is applied to filters with high orders. Hence blocking is necessary for filters with low order.

Blocking will definitely improve the utilization of inter-iteration parallelism. However, the maximum utilization may not be achieved as the blocking factor is finite. Hence a virtual infinite unfolding of the graph is required for the maximum utilization of this kind of parallelism.

- 3. Popelining the feed-forward part of the DFG: Pipelining is efficient when the program consists of repeated processes. The basic principle behind pipelining is that the computation for the iteration of a given task can be started before the computations of earlier iterations have been completed. Pipelining can be viewed as additional delays inserted into the DFG; as a consequence, the I/O delay increases. These delays can be added to the feed-forward part of the network, but obviously may not be added to the circuits of the graph since they may alter the data dependency between iterations. However, pipelining the tasks of a circuit in a graph is possible for certain values of iteration period. This is because a task is not only pipelined with tasks from the same iteration but also with some tasks from other iterations.

- 4. Periodic parallelism (inter-iteration parallelism): This parallelism is a result of utilizing the parallelism between successive iterations in an infinite or a sufficiently long schedule [68, 43, 55, 69]. Schedulers that utilize this parallelism, which can be either fully-static or cyclo-static, generate overlapped schedules, where operations from different iterations are overlapped. When maximum parallelism is utilized, the resulting schedule will be rate optimal for which the

iteration period T is equal to the iteration bound  $T_0$ . Some of the important rate-optimal scheduling techniques existing in the literature will be discussed later in this section.

As a matter of fact, the maximum inter-iteration parallelism can be accomplished by using the technique of direct blocking. It has been shown in [55] that the blocking-factor can be chosen so that the unfolded graph is a perfect-rate one, which can always be scheduled rate-optimally. Each circuit in a perfect-rate graph has only one ideal delay unit, say associated with edge  $\epsilon$ . Hence, the nodes of a circuit can be sequentially scheduled by starting from the terminal node until reaching the initial node of the edge  $\epsilon$ . Scheduling the acyclic version of the resulting perfect-rate graph will hence produce a rate-optimal schedule.

In the following paragraphs, we will discuss some schedulers that produce rate-optimal schedules. A simple technique to produce a rate- and delay-optimal schedule for an acyclic graph is the critical path method. In this method, the longest distance is computed between the input node of the graph and every other node. If the input node is scheduled at time 0, the distance between the input node and any other node represents its scheduling time. For the longest distance calculations, the weight assigned to a node is its computational delay, and the weight assigned to an edge is the negative of the product of its ideal delay and the iteration period. The basic problem of this technique is the fact that it does not utilize the inherent flexibility of the nodes to minimize the number of required processors.

The maximum spanning tree (MST) technique proposed in [54] and [70] is concerned with producing rate-optimal schedules for IIR filter networks. In this technique, the graph is transformed into an equivalent one by removing the ideal

delays from the branches of the MST and inserting non-negative shimming delays such that the resulting delay associated with each link is equal to the total delay of the corresponding fundamental loop in the original DFG. In the resulting DFG, the integrity of time precedency is preserved among the nodes. Then, the MST is scheduled according to the precedency constraints represented by the edges, and the timing constraints represented by the computational and shimming delays. This algorithm produces a valid rate-optimal time schedule. However, other optimality criteria are not addressed as well as no processor optimization is taken into consideration, leading, in general, to solutions with non-optimal number of processors.

In [55], the DFG is first converted to a perfect-rate graph by unfolding it with an unfolding factor that is equal to the least common multiple of the ideal delays in all the circuits in the graph. Each circuit in the resulting graph will contain one unit of ideal delay. Since the computational delay of any circuit will be less than or equal to the iteration period, as will be shown later, the DFG can always be scheduled rate-optimally. It can be easily seen that this approach has a serious problem of increasing the size of a given program. As an example, a DFG for a 7th-order IIR filter may possibly need to be unfolded by a factor of 420 in order for it to be converted to a perfect-rate graph. Further, this method does not try to optimize the number of processors.

The cyclo-static method [43, 48, 49, 50] consists of a depth-first search of cyclostatic solutions by fixing both the iteration period and the number of processors. Unlike static solutions, cyclo-static solutions have the property that the tasks assigned to a processor vary from iteration to iteration. However, the allocation of the tasks on the processors is periodic. That is, the tasks allocated to a processor at iteration n will be the same as those allocated to it at iteration  $n + n_p$ , where  $n_p$  is the cyclo-scheduling period. The main strength of this method is that no unfolding is required even when there are some operations with computational delays greater than the iteration period. This is due to the fact that an operation may be assigned to more than one processor in consecutive iterations. The basic problem with this method is that it does not guarantee a schedule, since it is not always possible to obtain a solution when both the iteration period and the number of processors are fixed. An example of the cyclo-static solution is the scheduling heuristic proposed in [43]. This heuristic narrows the search for a solution by imposing all constraints on the required solution: maximum throughput, minimum delay, and minimum number of processors. The algorithm is expected to output a schedule matrix in the time-processor space, where columns represent time slots and rows represent processors. The resulting matrix not only specifies which tasks are allocated to each processor, but also gives the information as to which iteration the occurrence of each node belongs. Along with the scheduling matrix, the algorithm generates a cycling vector that determines the relative permutation of the processors in successive iterations; hence, the cyclo-static schedule is completely specified. In this heuristic, the flexibility of all the nodes are first computed by considering the slack times of the circuits and the delays of the I/O paths, and next the nodes are scheduled in the order of increasing flexibility.

The most efficient static scheduling technique developed thus far is the rangechart technique [68, 71]. In this technique, first, a node is chosen as the reference node, and the flexibility of every other node is calculated. The flexibility of the nodes in a DFG is represented in a range chart form, which indicates the range within which each node can be executed. The node with the minimum range or flexibility is first chosen to be scheduled, and the range chart updated. The process of choosing a node and updating the chart is repeated until all the nodes are scheduled.

It may be noted that the heuristics proposed in the literature handle scheduling as a single problem. In contrast, we divide the scheduling problem into two phases. The first phase, time scheduling, is solved analytically using combinatorial concepts. The second phase is the mapping of the time schedule to a processor assignment.

# 2.4 Time Scheduling Theory

The scheduling problem addressed in this thesis is concerned with finding a rate-optimal schedule for a cyclic DFG. In a cyclic DFG, the critical circuits determine the iteration period bound. If C is a critical circuit, it is clear from (2.4) that len[C]=0, since ST(C)=0 from (2.3) and (2.1).

We will first show that any cyclic, fully specified DFG can be converted through a sequence of transformations to an acyclic one. Then we will use one of the known algorithms to schedule the resulting acyclic graph as a starting step in scheduling the whole graph. The transformation is accomplished by contracting each circuit in the graph to a single node.

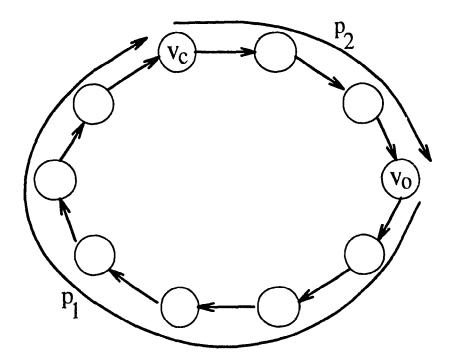

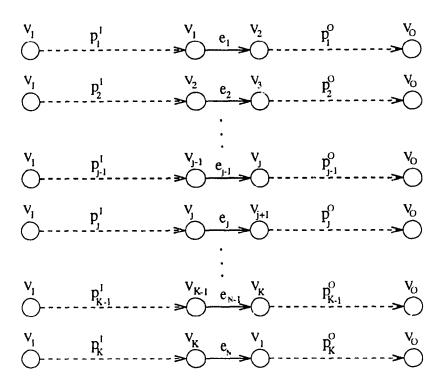

**Lemma 1** The time schedule of the nodes of a critical circuit is uniquely specified if and only if one of its nodes is time-scheduled.

#### **Proof:**

Necessity: Obvious.

**Sufficiency:** Assume that  $v_0 \in V(C)$  is a node in the critical circuit C with a fixed time schedule. For any node  $v_c \in V(C)$ , assume that its earliest firing time is  $EFT(v_c)$  and its latest firing time  $LFT(v_c)$ . Without loss of generality, assume that

Figure 2.1: A critical circuit.

$v_0$  is fired at time zero.

Assume  $p_1$  is the directed path  $(v_0 \to v_c) \subset C$  and  $p_2$  the directed path  $(v_c \to v_0) \subset C$  as shown in Figure 2.1. Since C is critical,

$$len[p_1[ +len[p_2[ = 0.$$

(2.5)

The precedence constraints require that

$$FT(v_0) + len[p_1] \le EFT(v_c) \tag{2.6}$$

and

$$LFT(v_c) + len[p_2] \le FT(v_0) \tag{2.7}$$

where  $FT(v_0) = 0$  is the firing time of  $v_0$ . Adding (2.6) to (2.7) gives

$$LFT(v_c) + len[p_1[ +len[p_2[ \leq EFT(v_c)$$

Using (2.5), this inequality reduces to

$$LFT(v_c) \leq EFT(v_c)$$

However,  $LFT(v_c) < EFT(v_c)$  is not feasible. Therefore,

$$LFT(v_c) = EFT(v_c),$$

and hence the proof.

**Lemma 2** Let  $v_x \notin V(C)$  and  $v_c \in V(C)$  be connected nodes. If the scheduling time of  $v_x$  is fixed relative to the scheduling time of  $v_c$ , then it is also fixed relative to all other nodes in C.

#### **Proof:**

Since the scheduling of  $v_x$  is fixed relative to the scheduling of  $v_c$ , we can establish that

$$FT[v_x] - FT[v_c] = B_1.$$

(2.8)

where  $B_1$  is a constant. Further, as per Lemma 1, the scheduling time of  $v_c$  is fixed relative to all other nodes in C; hence

$$FT[v_c] - FT[v_{cx}] = B_2.$$

(2.9)

where  $B_2$  is also a constant and  $v_{cr}$  is any node in C. Summing up (2.8) and (2.9), we get

$$FT[v_x] - F[v_{cx}] = B_1 + B_2 = Constant,$$

and hence the proof.

Theorem 1 In a DFG, any critical circuit can be contracted to one of its nodes without altering the scheduling problem.

#### Proof:

Assume that the critical circuit C is contracted into one of its nodes  $v_0$ . According to Lemma 1, the rest of the nodes in C have fixed scheduling times as long as  $v_0$  does; therefore, if the node  $v_0$  is scheduled correctly, the rest of the nodes in C will automatically get scheduled according to their displacement relative to  $v_0$ . Hence removing such nodes will not affect the scheduling problem as far the scheduling of the circuit nodes is concerned.

Let  $v_x$  be any other node not in C. If  $v_x$  is not connected to C, then it can be scheduled independently of  $v_0$ . If it is connected to some node in C, then according to Lemma 2, the scheduling time of  $v_x$  relative to this node can be represented by its scheduling time relative to  $v_0$ . Therefore, the circuit nodes other than  $v_0$  are not necessary to be present in the DFG as far as the scheduling of the rest of the nodes in the DFG is concerned, and hence the theorem.

So far, we have shown that a critical circuit can be replaced by a single node and yet the scheduling problem is not altered. This kind of a replacement will be referred to as critical circuit contraction, or simply circuit contraction. In order to contract a circuit to a single node, it is required to make up for the data dependency between the circuit nodes which will be removed due to the circuit contraction and the other graph nodes. According to Theorem 1 this is always possible. Let the circuit C be a critical circuit to be contracted to a node  $v_0$ . The data dependency between a node  $v_x$  not in C and any node  $v_c$  in C due to the existence of some path between  $v_x$  and  $v_c$ , can be compensated for by introducing a path to (form)  $v_x$  from (to)  $v_0$  having the same length. One way of introducing such path is by introducing pseudo nodes whose assigned delays compensate for the missing subpaths due to the circuit contraction. Using the above method of compensating for the missing

subpaths by introducing pseudo nodes, we now give an algorithm for the contraction of a critical circuit C in a given graph G to form a new graph G'. The single node to which the circuit C is contracted will be referred to as a "supernode".

## Contraction Algorithm:

- 1. Let G' be the node-induced subgraph on its node set  $V(G') = [V(G) V(C)] \cup \{v_0\}$ , where  $v_0 \in V(C)$  is the node to which the circuit C is to be contracted.

- 2. For each node  $v_c \in [V(C) \{v_0\}]$  with an out-degree greater than one, perform the following operations.

- (a) Create a pseudo node  $v'_c$  with a computational delay equal to len]p], where p is the directed path in C from node  $v_0$  to node  $v_c$ , i.e,  $p = (v_0 \rightarrow v_c) \subset C$ .

- (b) Set  $V(G') = V(G') \cup \{v'_c\}.$

- (c) Move the tail of each edge ε ∈ E(G), incident out of the node v<sub>c</sub> to some node not in C, to be incident out of the node v'<sub>c</sub>. (The terminal node of the edge and the ideal delay associated with it remain unchanged.) Set E(G') = E(G') ∪ {ε}.

- (d) Set  $E(G') = E(G') \cup \{(v_0, v'_c)\}$ , where  $(v_0, v'_c)$  is a delay-free edge.

- For each node v<sub>c</sub> ∈ [V(C) {v<sub>0</sub>}] with an in-degree greater than one, perform the following operations.

- (a) Create a pseudo node  $v''_c$  with a computational delay equal to len[p[, where p is the directed path in C from node  $v_c$  to node  $v_0$ , i.e,  $p = (v_c \rightarrow v_0) \subset C$ .

- (b) Set  $V(G') = V(G') \cup \{v_c''\}$ .

- (c) Move the head of each edge ε ∈ E(G), incident into v<sub>c</sub> from some node not in C, to be incident into {v<sub>c</sub>"}. (The initial node of the edge and the ideal delay associated with it remain unchanged.) Set E(G') = E(G') ∪ {c}.

- (d) Set  $E(G') = E(G') \cup \{(v''_c, v_0)\}$ , where  $(v''_c, v_0)$  is a delay-free edge.

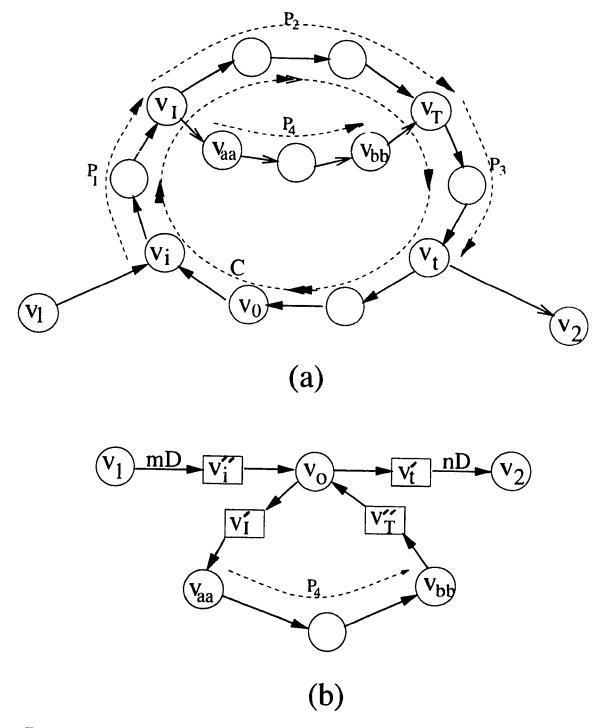

We will now study the effect of applying the Contraction Algorithm to contract a critical circuit on the slack times of other circuits and the lengths of the I/O paths. In fact, we are going to show that neither the slack time of a circuit, nor the length of an I/O path is effected by contracting a critical circuit to a single node using the Contraction Algorithm. Recall that, as per (2.4), the slack time of a circuit is nothing but the negative of its path length. Hence, to show that neither the slack time of a circuit nor the length of an I/O path is altered by the contraction of a critical circuit, it is enough to show that the length of any path in the graph does not change due to such contraction. It is to be noted that a path may change its node and edge sets due to a circuit contraction. Therefore, when we say that the length of the path does not change, we relate the original path with the corresponding path in the graph after contraction. Let G' be the graph that results after contracting a critical circuit C from G. For every path  $p \in G$  whose end nodes are not in C', there is a corresponding path  $p' \in G'$  such that len[p] = len[p']. As a matter of fact the path p' is not necessarily elementary, that is, it may contain a circuit as will be shown soon.

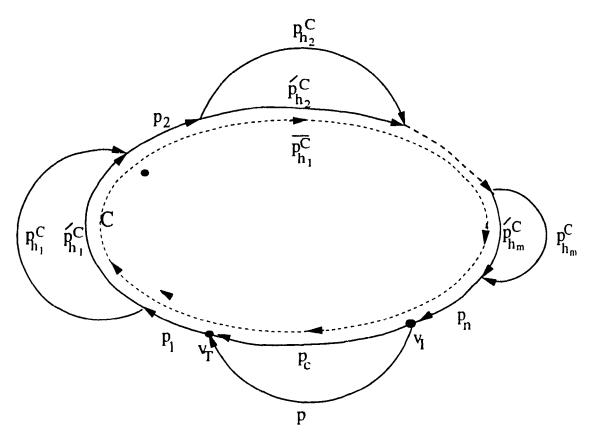

**Definition 1** A path  $p_h^C$  is said to be a hop-path with respect to a circuit C if and only if it has no common edges with C, and its node set is disjoint from the node set of C except for its initial and terminal nodes, that is,  $E(p_h^C) \cap E(C) = \Phi$ , and  $V(p_h^C) \cap V(C) = \{v_I, v_T\}$ , where  $v_I$  and  $v_T$  are the initial and terminal nodes of  $p_h^C$ .

**Lemma 3** Let G' be a graph resulting after contracting circuit C from a given graph G, and let  $p_h^C$  be a hop-path with respect to C. G' will contain a circuit of the form  $v_0, v_I', (p_h^C - \{v_I, v_T\}), v_T'', v_0$ , where  $v_I'$  and  $v_T''$  are the pseudo nodes generated by the Contraction Algorithm as the nodes  $v_I$  and  $v_T$  are removed, and  $v_0$  is the supernode to which the circuit C has been contracted. Further, this circuit is the path in G' corresponding to  $p_h^C$ .

#### **Proof:**

Let  $p_h^C$  be a hop-path with respect to a circuit C. As seen from Figure 2.2(a),  $p_h^C$  can be expressed as  $p_h^C = v_I, p_4, v_T$ . Contracting the circuit C (see Figure 2.2(b)) will result in the pseudo node  $v_I^c$  with a delay-free edge coming from  $v_0$  and an edge going to the initial node of  $p_4$ . It will also result in a pseudo node  $v_T^u$  and an edge incoming from the terminal node of  $p_4$  and an edge going to the node  $v_0$ .  $p_4$  along with these four edges constitute the circuit  $v_0, v_I^c$ ,  $(p_h^C - \{v_I, v_T\}), v_T^u$ ,  $v_0$ , and hence the first part of the lemma. The second part of the lemma is obvious as the node  $v_I$  is replaced by the pseudo node  $v_I^c$  and an incoming edge from  $v_0$ , and the node  $v_T^c$  by the pseudo node  $v_I^c$  and an outgoing edge to  $v_0$ .

**Theorem 2** Let G' be the graph resulting after contracting a circuit C from the given graph G, and p an elementary path in G. If  $p_h^C \subset p$ , where  $p_h^C$  is a hop-path with respect to C, then there would be no elementary path in G' corresponding to p.

#### **Proof:**

Let p' in G' be the path corresponding to the path p in G. Since  $p_h^C \subset p$ ,  $p_h^{C'} \subset p'$ , where  $p_h^{C'}$  is the path corresponding to  $p_h^C$  in G'. The path  $p_h^{C'}$ , by Lemma 3, is a circuit. Therefore, p' contains a circuit and hence the proof.

Figure 2.2: (a) A subgraph before and (b) after the contraction of the shown circuit.

Corollary 1 A circuit  $C_0$  that contains a hop-path with respect to a circuit C in G may not have a corresponding circuit in the graph G' resulting after contracting the circuit C.

The above theorem showed that some paths have no corresponding paths in the resulting graph after contracting a circuit. The following theorem, however, will show that a path which does not meet the criterion in the above theorem, will have a corresponding elementary path in the graph resulting after a circuit contraction with exactly the same path length.

**Theorem 3** Let  $v_1$  and  $v_2$  be any two nodes such that  $v_1, v_2 \in G - C$ , where G is the DFG before contracting the circuit C. Then for each path  $p_0 = (v_1 \to v_2) \subset G$ , such that  $p_0$  does not contain a hop-path with respect to C, there is a corresponding path  $p'_0 = (v_1 \to v_2) \subset G'$  with the same path length, that is,  $len[p_0] = len[p'_0]$ , where G' is the graph resulting after the contraction.

#### **Proof:**

Take any path  $p_0$  whose initial node is  $v_1$  and terminal node  $v_2$ . If  $p_0$  has no common subpath with C, then the proof is evident as  $p_0$  will remain unchanged in G'. Assume that  $p_0$  has some common subpaths with C. If there are multiple such disjoint paths, then the path  $p_0$  will contain at least one hop-path, and hence its corresponding path in G' is not elementary as stated by Theorem 2. If there is only one common subpath, say p, assume that its initial node is  $v_t$  and terminal node  $v_t$ . Without loss of generality, we may assume that  $v_1$  is an immediate precedent to  $v_t$  and  $v_2$  is ... immediate successor to  $v_t$ , that is,  $(v_1, v_t), (v_t, v_2) \in E(G)$ . It is enough to show that the length of the path  $p'_0 = v_1, (v_1, v''_1), v''_1, (v''_1, v_0), v_0, (v_0, v'_t), v'_t, (v'_t, v_2), v_2$  in the graph after contracting circuit C to node  $v_0$  is the same as the length of the

path  $p_0 = v_1, (v_1, v_i), p, (v_t, v_2), v_2$  is the graph before the contraction, where  $v_i''$  and  $v_t'$  are pseudo nodes resulting as per the Couraction Algorithm. The lengths len] $p_0$ [ and len] $p_0'$ [ are given by

$$len]p_0[=\overline{n}_{(v_1,v_2)} + len[p] + \overline{n}_{(v_1,v_2)},$$

and

$$l\epsilon n]p_0'[ = \overline{n}_{(v_1,v_1'')} + d_{v_1''}^c + \overline{n}_{(v_1'',v_0)} + d_{v_0}^c + \overline{n}_{(v_0,v_1')} + d_{v_1'}^c + \overline{n}_{(v_1',v_2)}.$$

where  $\overline{n}_{(v_1,v_i)} = -n_{(v_1,v_i)}T$ .

But  $\overline{n}_{(v_1,v_i'')} = \overline{n}_{(v_1,v_i)}$  and  $\overline{n}_{(v_i',v_2)} = \overline{n}_{(v_i,v_2)}$ . Moreover,  $\overline{n}_{(v_0,v_i')} = \overline{n}_{(v_i'',v_0)} = 0$ . Therefore,

$$len]p_0[=\overline{n}_{(v_1,v_1)}+d^c_{v''_1}+d^c_{v_0}+d^c_{v'_1}+\overline{n}_{(v_1,v_2)}.$$