INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

800-521-0600

UMI<sup>®</sup>

# ANALYSIS AND DESIGN OF AN AUXILIARY COMMUTATED FULL BRIDGE DC/DC CONVERTER FOR LOW VOLTAGE AND HIGH CURRENT APPLICATIONS

DHEERAJ K. JAIN

A Thesis

In

The Department

Of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Concordia University

Montreal, Quebec, Canada.

December 2001

©Dheeraj k. Jain, 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-68442-3

#### **ABSTRACT**

## ANALYSIS AND DESIGN OF AN AUXILIARY COMMUTATED FULL BRIDGE DC/DC CONVERTER FOR LOW VOLTAGE AND HIGH CURRENT APPLICATIONS

#### DHEERAJ K. JAIN

The analysis and design of an auxiliary commutated Full Bridge dc/dc converter topology including the effect of leakage inductance of the output transformer is presented in this thesis. In applications where the transformer has high turns-ratio between the primary and secondary windings, the value of leakage inductance is relatively high. This high value of leakage inductance, however, is not large enough to achieve the zero voltage switching (ZVS) of the converter over the entire range of operating load conditions, but can be effectively used in minimizing the circulating current of the auxiliary commutation circuit used for achieving ZVS. The operating principle of the circuit is demonstrated, and the steady state analysis is performed. Based on the analysis, a criterion for optimal design is given.

#### **ACKNOWLEDGEMENT**

I would like to express my sincere gratitude to Dr. Praveen K. Jain for his encouragement, support and guidance during the course of this study. His ideas and suggestions were a source of guidance to me and without his timely help this research project would have taken a far longer time to finish. His support and encouragement is highly appreciated.

I would also like to especially thank Mr. Haibo Zhang of Cistel Technology.

Ottawa for his invaluable help during the course of this work.

I want to thank all my friends and colleagues at the P. D. Ziogas Power Electronics Lab at Concordia University, for their friendship, their help, and for many valuable discussions and suggestions.

This work has been financially supported by the strategic grant from National Science and Engineering Research Council of Canada (NSERC).

Dedicated to my parents

#### **TABLE OF CONTENTS**

| List of Figures                                                      | x    |

|----------------------------------------------------------------------|------|

| List of Tables                                                       | xiii |

| List of Acronyms                                                     | xiv  |

| List of Principal Symbols                                            | xv   |

|                                                                      |      |

| Chapter 1 Introduction                                               |      |

| 1.1 Introduction                                                     | 1    |

| 1.2 Review of Existing ZVS Full Bridge Topologies                    | 2    |

| 1.2.1 Conventional ZVS full bridge topologies                        | 2    |

| 1.2.2 ZVS full bridge topology with auxiliary circuit                | 6    |

| 1.2.3 ZVS full bridge converter with Current Doubler and Synchronous |      |

| Rectifiers                                                           | 7    |

| 1.3 Objective and scope of the study                                 | l l  |

| 1.4 Thesis Outline                                                   | 12   |

|                                                                      |      |

| Chapter 2 Full bridge Converter with Synchronous Rectification       |      |

| 2.1 Introduction                                                     | 13   |

| 2.2 Circuit description                                              | 14   |

| 2.3 Brief operation of the proposed converter                        | 16   |

| 2.3.1 Model                                                          | 16   |

| 2.3.2 Mode2                                                          | 20   |

| 2.4 Synchronous Rectification                                        | 23 |

|----------------------------------------------------------------------|----|

| 2.4.1 Self-driven technique                                          | 25 |

| 2.4.2 External driven or control-driven technique                    | 27 |

| 2.4.3 Comparison of synchronous rectifier topologies                 | 28 |

| 2.5 Conclusions                                                      | 29 |

|                                                                      |    |

| Chapter 3 Steady state analysis                                      |    |

| 3.1 Introduction                                                     | 30 |

| 3.2 Steady state analysis                                            | 30 |

| 3.2.1 Assumption and some constants for the analysis                 | 31 |

| 3.2.2 Steady state analysis of each interval in Mode 1               | 35 |

| 3.2.3 Steady state analysis of each interval in Mode 2               | 41 |

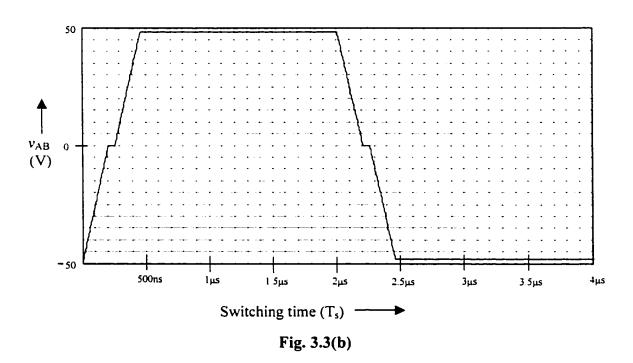

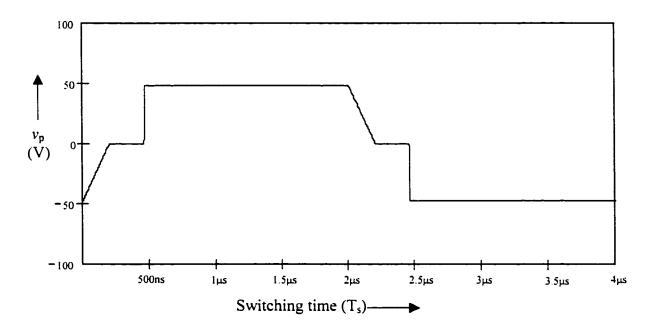

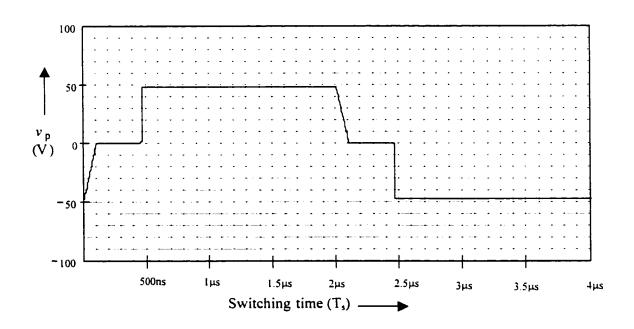

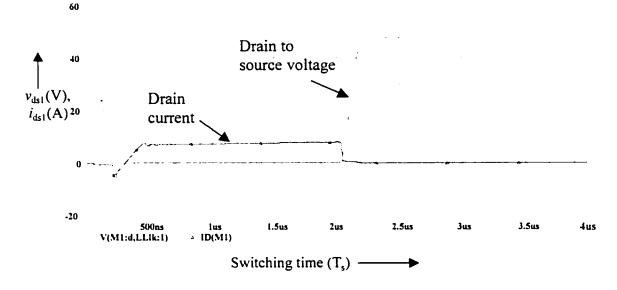

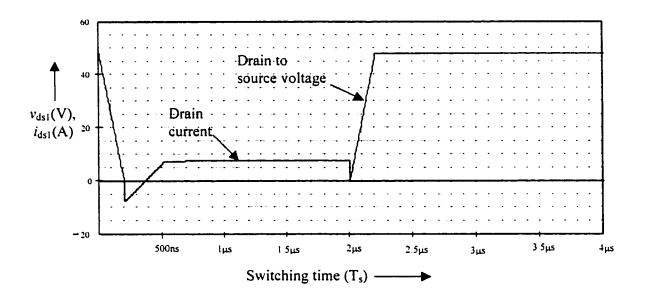

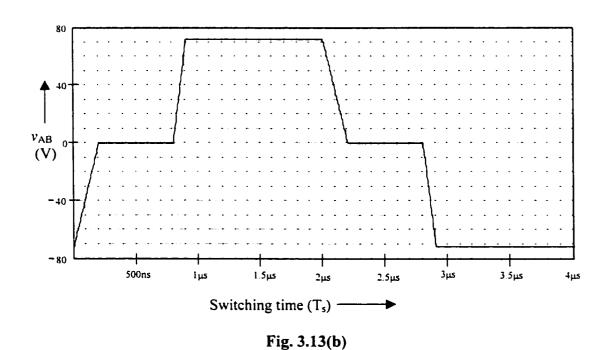

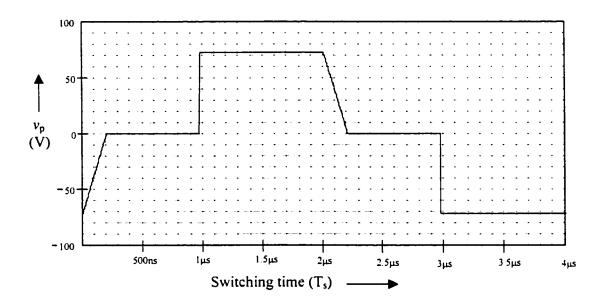

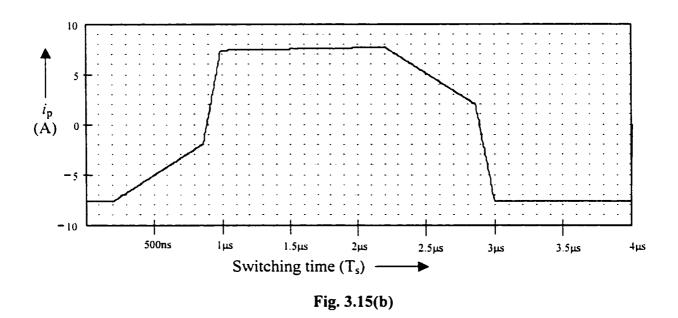

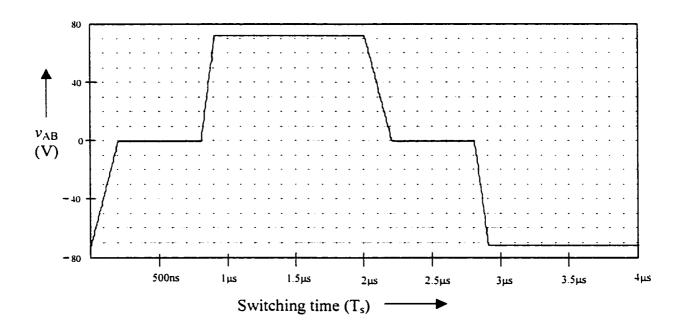

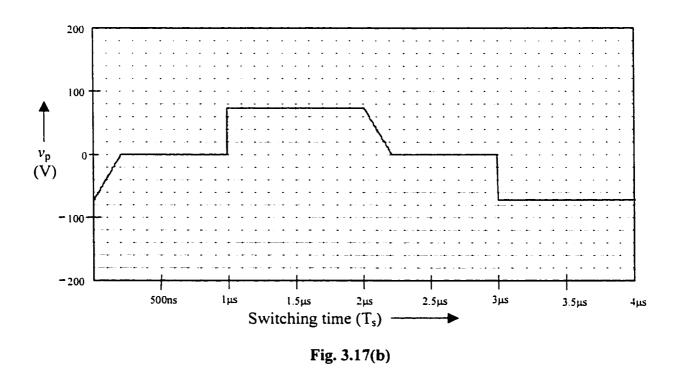

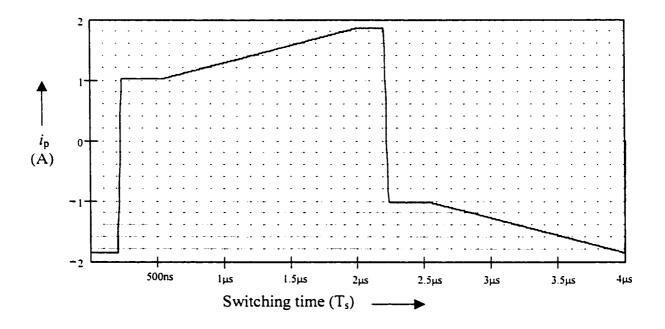

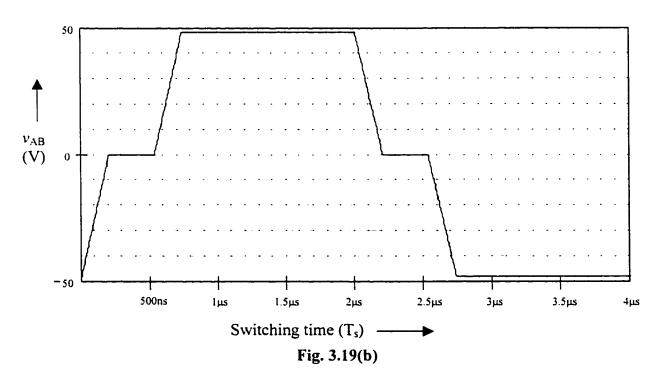

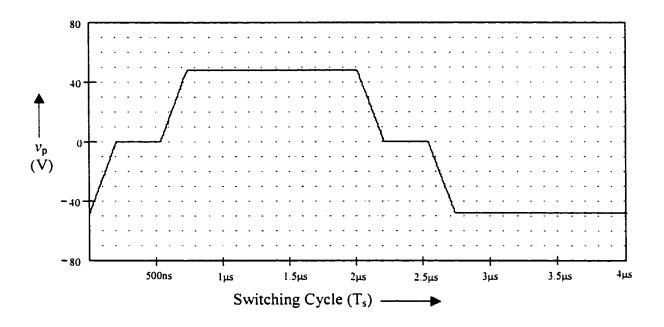

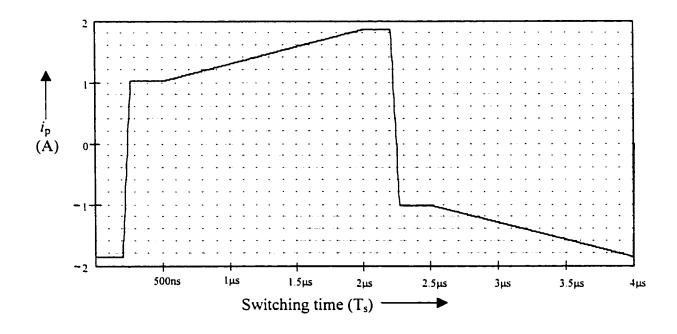

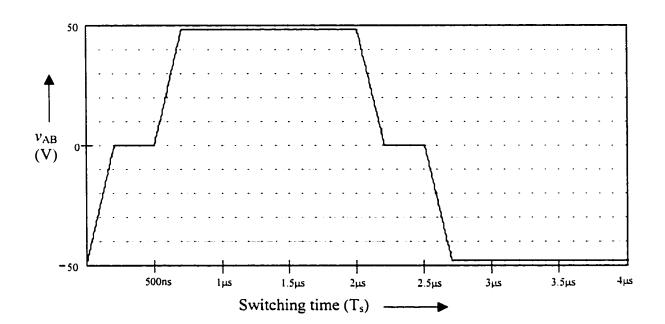

| 3.3 Analytical and simulated waveforms of the proposed converter     | 48 |

| 3.4 Conclusions.                                                     | 72 |

|                                                                      |    |

| Chapter 4 Characteristics curves                                     |    |

| 4.1 Introduction                                                     | 73 |

| 4.2 Choice of switching frequency, leakage inductance and duty cycle |    |

| 4.3 Zero Voltage Switching range                                     |    |

| 4.4 Conclusions                                                      |    |

#### **Design Procedure** Chapter 5 5.1 Introduction..... 85 5.2 Design Procedure..... 85 5.3 Design Example.... 87 5.3.1 Specifications..... 87 5.3.2 Transformer design ..... 88 5.3.3 Selection of $C_{r,t}$ and $C_{r,t}$ , the capacitor type voltage divider ...... 89 5.3.4 Selection of $L_1, L_2 \& C_n$ , the output filter..... 89 5.3.5 Selection of Primary switches $S_1, S_2, S_3$ and $S_4$ ..... 90 5.3.6 Selection of Synchronous Rectifiers $S_{RI}$ and $S_{R2}$ ...... 91 5.3.7 Selection of $L_{mx}$ , $L_{I/k}$ , $C_{,b1}$ , $C_{,b}$ , $C_{,b}$ , & $C_{,b4}$ ...... 92 5.3.8 Design summary ..... 92 5.4 Performance demonstration ..... 93 5.5 Conclusions..... 96 Chapter 6 **Summary and Conclusion** 6.1 Summary ...... 97 6.2 Conclusions 98 6.3 Contributions..... 99

99

6.4 Suggestion for Future Work.....

| References | 101 |

|------------|-----|

| Appendix1  | 104 |

| Appendix2  | 108 |

#### LIST OF FIGURES

| Fig. 1-1 Conventional ZVS full bridge converter topologies                                | 3  |

|-------------------------------------------------------------------------------------------|----|

| Fig. 1-2 ZVS full bridge topology using auxiliary devices                                 | 6  |

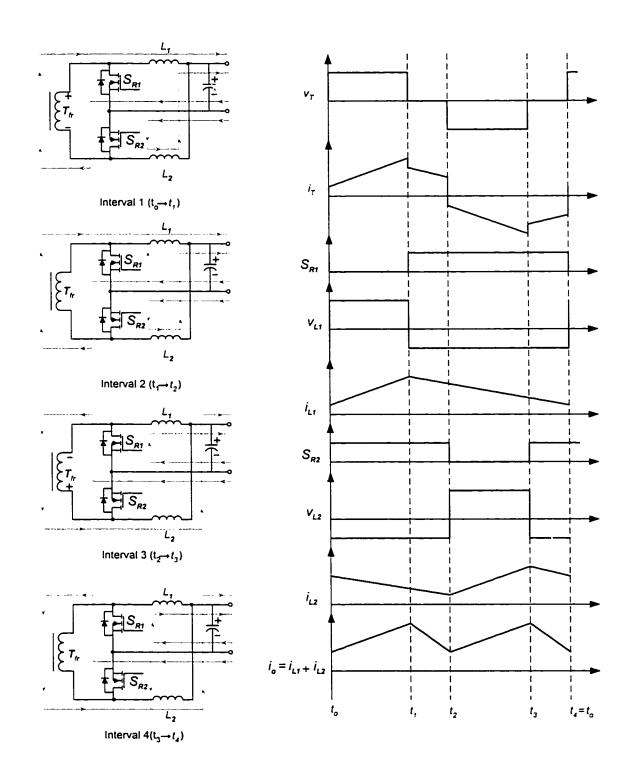

| Fig. 1-3 Circuit diagram of current doubler rectifier                                     | 8  |

| Fig. 1-4 Operation of the current doubler rectifier                                       | 10 |

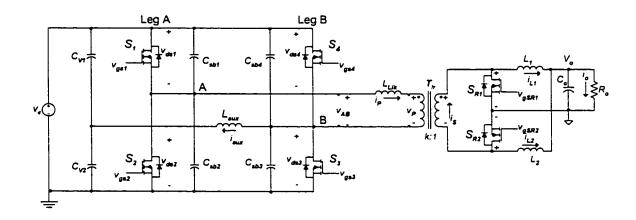

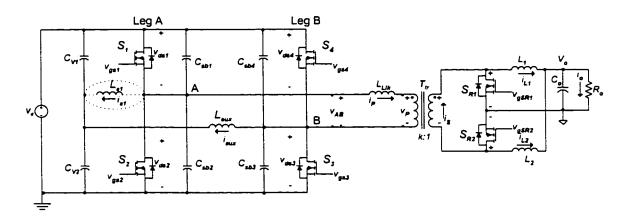

| Fig. 2-1 The proposed ZVS full bridge converter topology                                  | 15 |

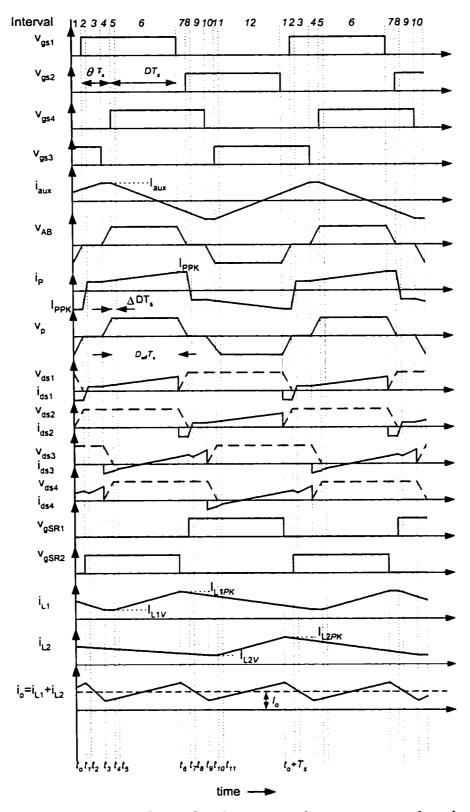

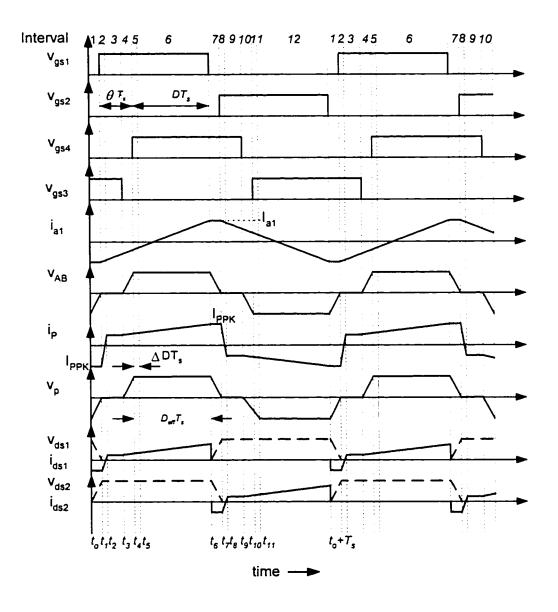

| Fig. 2-2 Key waveforms for the proposed converter topology in Model                       | 17 |

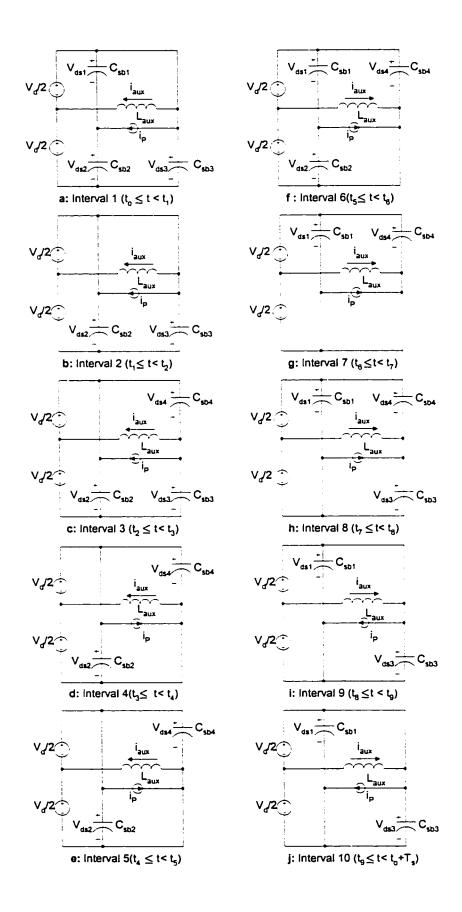

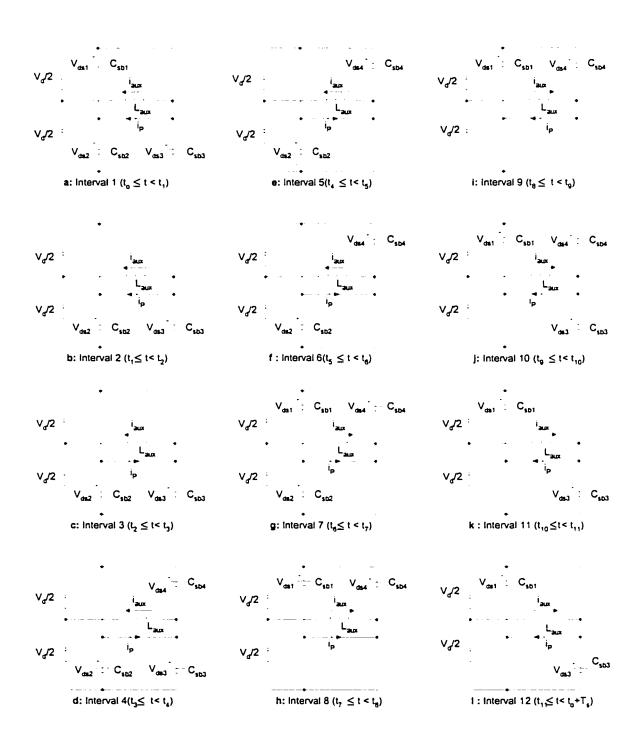

| Fig. 2-3 Equivalent circuit in different intervals in Mode1                               | 18 |

| Fig. 2-4 Key waveforms for the proposed converter topology in Mode2                       | 21 |

| Fig. 2-5 Equivalent circuit in different intervals in Mode2                               | 22 |

| Fig. 2-6 MOSFET used as a synchronous rectifier                                           | 24 |

| Fig. 2-7 MOSFET used as a synchronous rectifier using self-driven technique               | 26 |

| Fig. 2-8 MOSFET used as a synchronous rectifier using external-driven technique           | 28 |

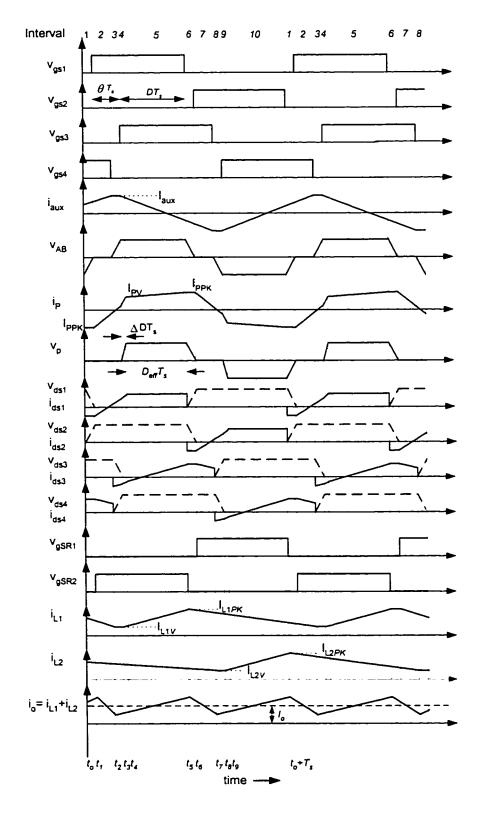

| Fig. 3-1 The proposed ZVS full bridge converter topology                                  | 31 |

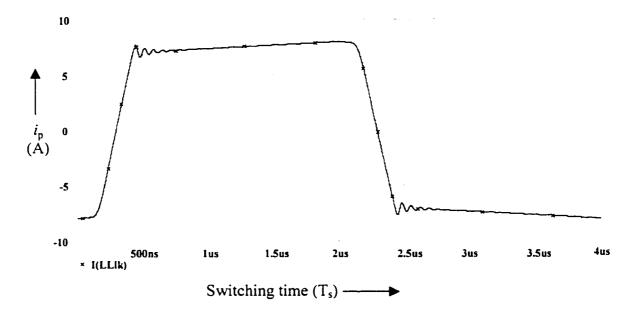

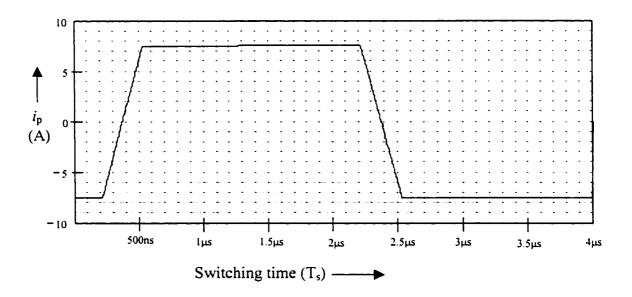

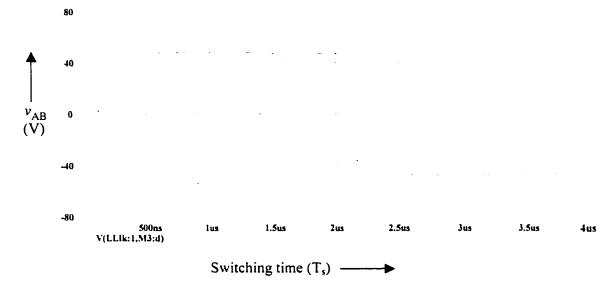

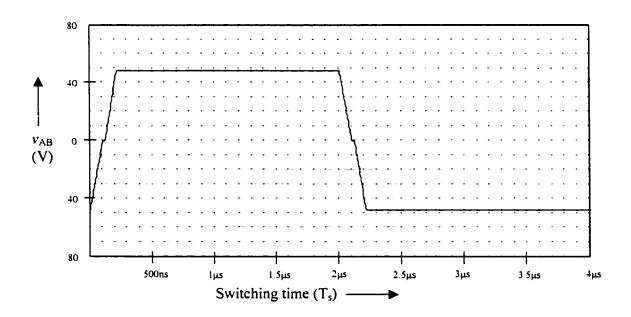

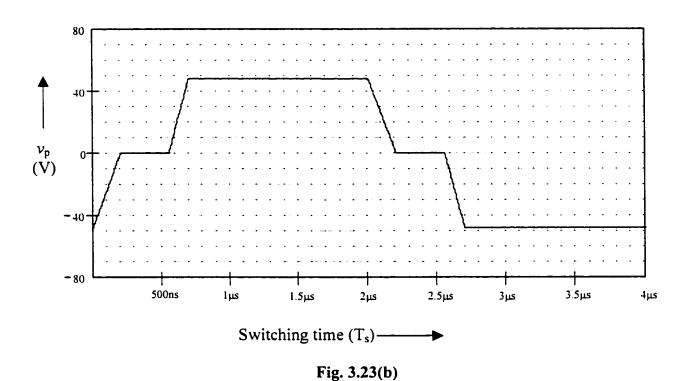

| Fig. 3-2 through Fig. 3-23 Simulation and analytical results at different line and load   |    |

| conditions                                                                                | 50 |

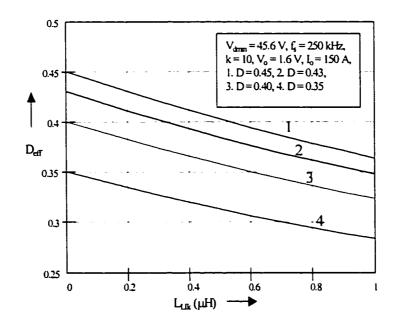

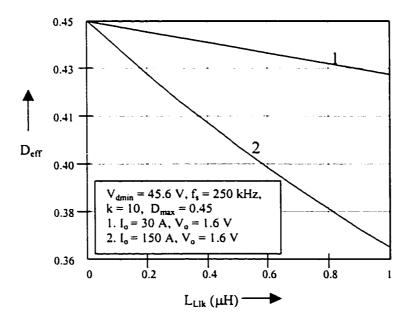

| Fig. 4-1 Effective duty cycle versus leakage inductance at full load                      | 76 |

| Fig. 4-2 Effective duty cycle versus leakage inductance                                   | 76 |

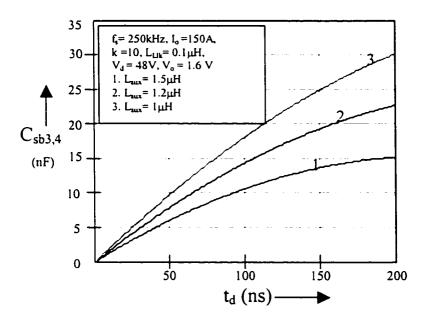

| Fig. 4-3 Snubber capacitor $(C_{sb3,4})$ versus dead time $(t_d)$ with leakage inductance |    |

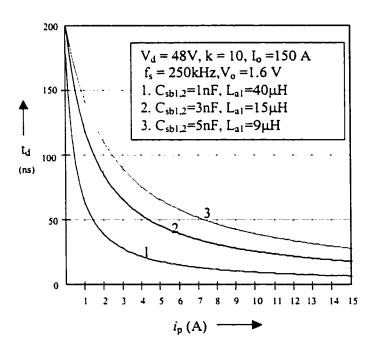

| $(L_{l,lk} = 0.1 \mu\text{H})$ for leg B                                                  | 79 |

| Fig. 4-4 Snubber capacitor $(C_{vb3,t})$ versus dead time $(t_d)$ with leakage inductance |    |

| $(L_{I.lk} = 0.5 \mu \text{H}) \text{ for leg B}$                                                                      | 79  |

|------------------------------------------------------------------------------------------------------------------------|-----|

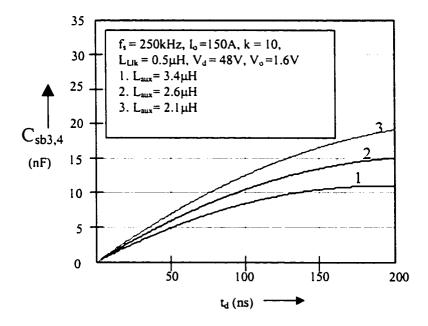

| Fig. 4-5 Snubber capacitor ( $C_{sb3,4}$ ) versus dead time ( $t_d$ ) with leakage inductance                          |     |

| $(L_{l,lk}=l \mu H)$ for leg B                                                                                         | 80  |

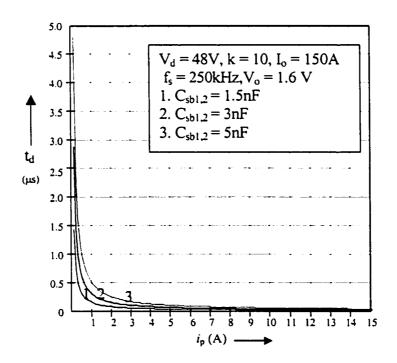

| Fig. 4-6 Dead time $(t_d)$ versus primary current $(i_p)$ for leg A                                                    | 80  |

| Fig. 4-7 Shows the additional auxiliary inductor ( $L_{ul}$ ) used in leg A for the proposed                           |     |

| converter to achieve ZVS from no load to full load                                                                     | 81  |

| Fig. 4-8 Gating pattern and key waveforms for leg A at no-load                                                         | 82  |

| Fig. 4-9 Dead time $(t_d)$ versus primary current $(i_p)$ for leg A                                                    | 83  |

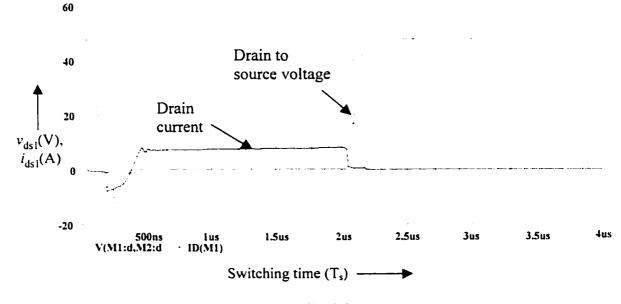

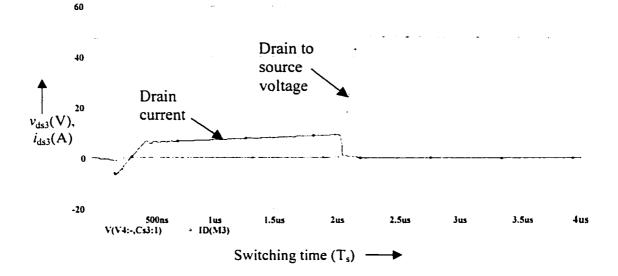

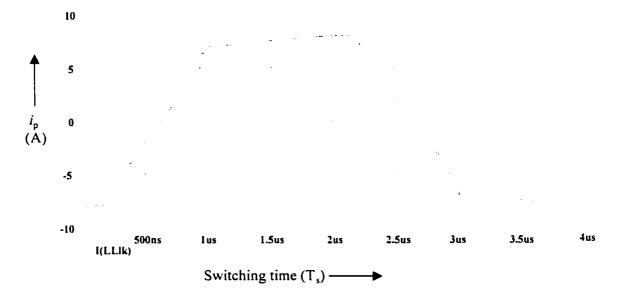

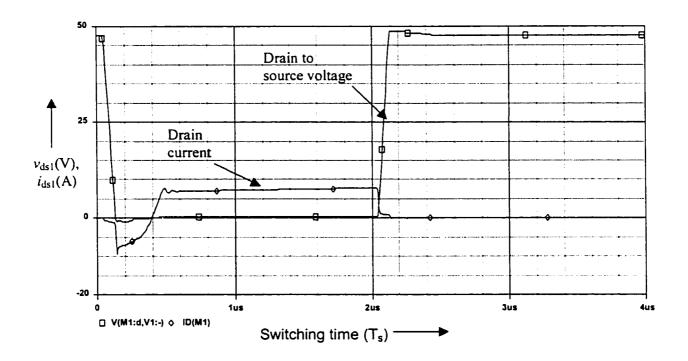

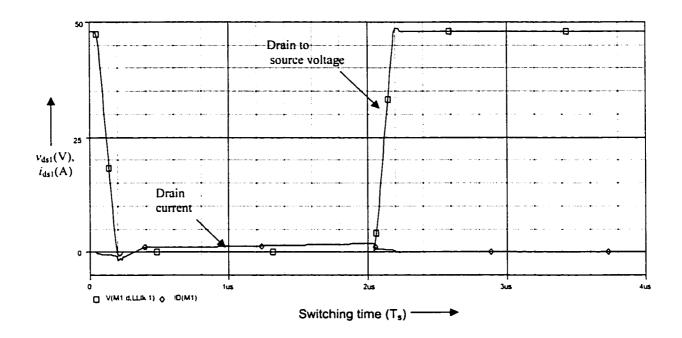

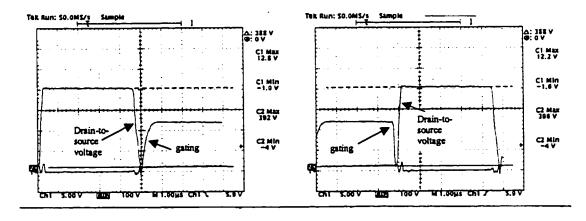

| Fig. 5-1 Simulation result for leg A at $L_{L/k} = 0.5 \mu H$ , $L_{disc} = 2.6 \mu H$ with $C_{sbL,2} = 3 \text{nF}$  |     |

| at full load                                                                                                           | 94  |

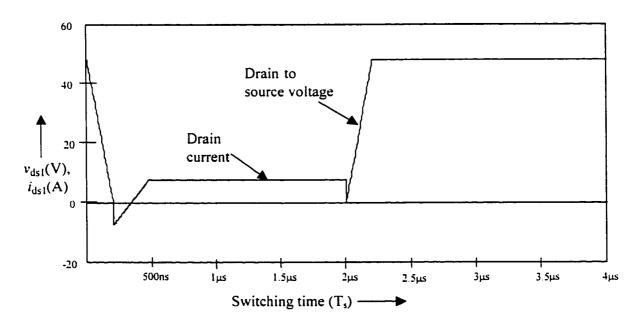

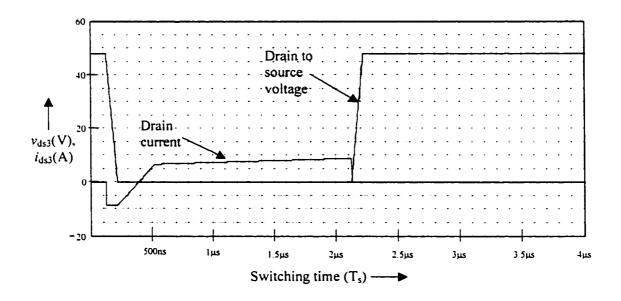

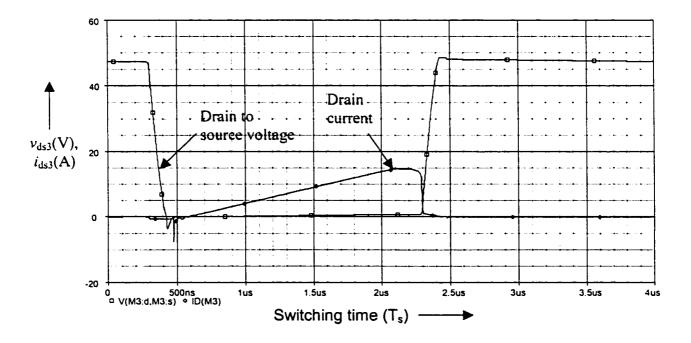

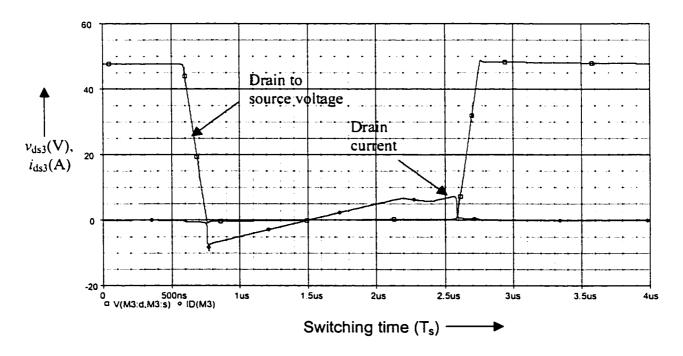

| Fig. 5-2 Simulation result for leg B at $L_{L/k} = 0.5 \mu H$ , $L_{cour} = 2.6 \mu H$ with $C_{sh3,d} = 15 \text{nF}$ |     |

| at full load                                                                                                           | 94  |

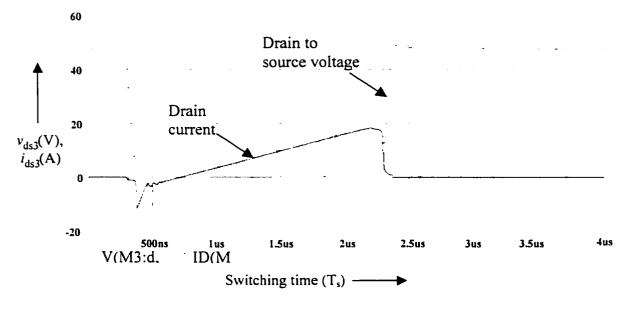

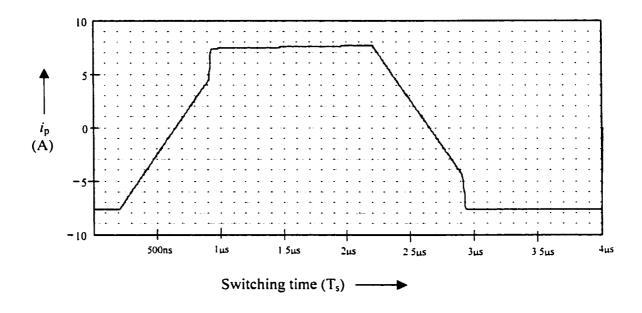

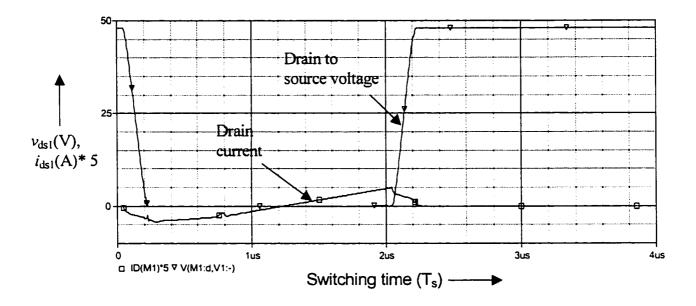

| Fig. 5-3 Simulation result for leg A at $L_{IJk}$ =0.5 $\mu$ H, $L_{aux}$ =2.6 $\mu$ H with $C_{shL2}$ =3nF            |     |

| at 20% load                                                                                                            | 95  |

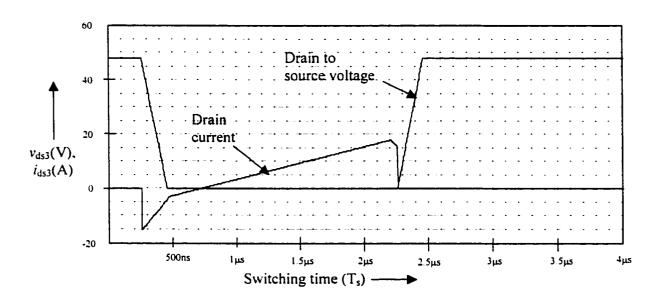

| Fig. 5-4 Simulation result for leg B at $L_{L/k} = 0.5 \mu H$ . $L_{aux} = 2.6 \mu H$ with $C_{sb3.4} = 15 nF$         |     |

| at 20% load                                                                                                            | 95  |

| Fig. 5-5 Simulation result for leg A at $L_{t,lk}$ =0.5 $\mu$ H, $L_{ul}$ =40 $\mu$ H with $C_{vbl,2}$ =1nF at 1%      |     |

| load                                                                                                                   | 96  |

| Fig. A.1 Shows the circuit reported in [1]                                                                             | 104 |

| Fig. A.2 Shows the proposed circuit                                                                                    | 105 |

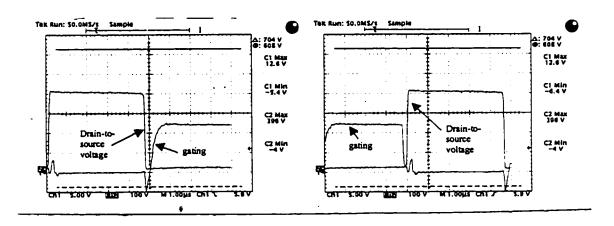

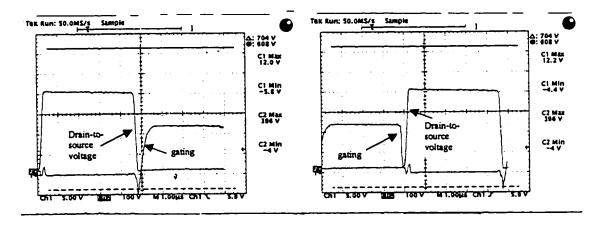

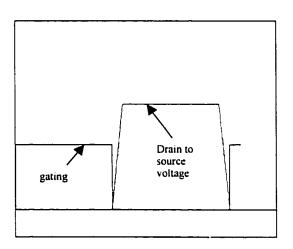

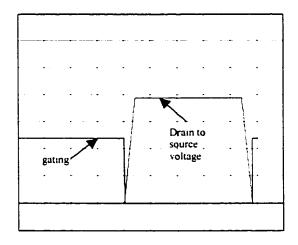

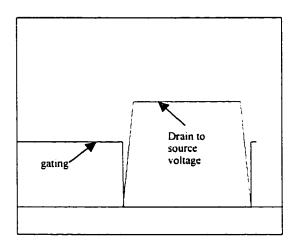

| Fig. A.3 Experimental results showing gating and drain-to-source waveforms of the |     |

|-----------------------------------------------------------------------------------|-----|

| switches under full load                                                          | 108 |

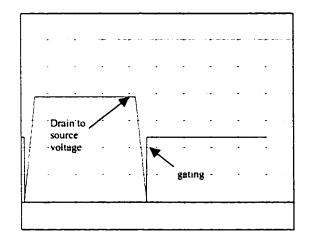

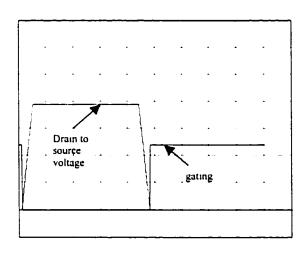

| Fig. A.4 Experimental results showing gating and drain-to-source waveforms of the |     |

| switches under light load                                                         | 109 |

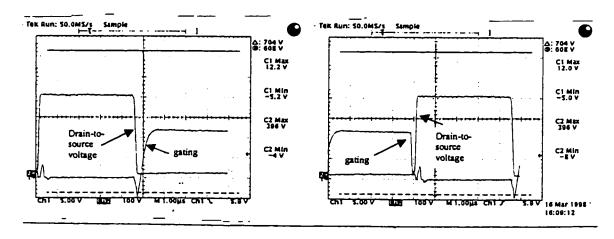

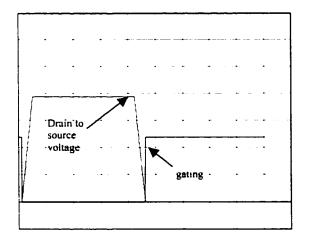

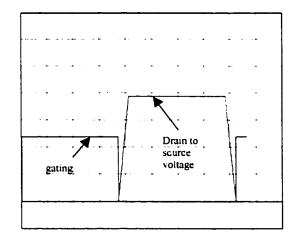

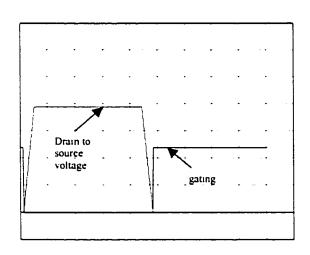

| Fig. A.5 Analytical results showing gating and drain-to-source waveforms of the   |     |

| switches under full load                                                          | 111 |

| Fig. A.6 Analytical results showing gating and drain-to-source waveforms of the   |     |

| switches under light load                                                         | 112 |

#### LIST OF TABLES

| Table 3-1 Principal parameters of the simulation circuit           | 72  |

|--------------------------------------------------------------------|-----|

| Table 5-1 Example circuit                                          | 93  |

| Table A.1 Comparison for high-voltage and low-current applications | 106 |

| Table A.2 Comparison for low-voltage and high-current applications | 107 |

| Table A.3 Principal parameters of the simulation circuit           | 110 |

#### LIST OF ACRONYMS

AC Alternative Current

DC Direct Current

CCM Continuous Conduction Mode

DCM Discontinuous Conduction Mode

EMI Electromagnetic Interference

ESL Equivalent Series Inductor

ESR Equivalent Series Resistor

IGBT Isolated Gate Bipolar Transistor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PWM Pulse Width Modulation

rms. RMS Root Mean Square value

SR Synchronous Rectifier

ZCS Zero Current Switching

ZVS Zero Voltage Switching

EDT Externally Driven Technique

PSM Phase Shift Modulation

#### LIST OF PRINCIPAL SYMBOLS

$\theta$  phase angle expressed in fraction of a switching cycle period

$C_{VI}$  and  $C_{V2}$  auxiliary circuit input voltage splitter capacitors

C<sub>a</sub> output filter capacitor

$L_1$  and  $L_2$  output filter inductors

D duty ratio of main switches

$D_{eff}$  effective duty cycle

$\Delta D$  loss in duty cycle

$f_s$  switching frequency

$C_{ybl}$ ,  $C_{ybl}$ , and  $C_{ybl}$  snubber capacitors for each of the four switches, respectively

k transformer turns ratio

$L_{t,lk}$  leakage inductance of the transformer

$P_o$  output power of the converter

$S_1, S_2, S_3$ , and  $S_4$  four switches of the full bridge converter

$SR_1$  and  $SR_2$  two switches of the synchronous rectifiers

$R_o$  the converter load

$T_{fr}$  power transformer

$v_{ds1}, v_{ds2}, v_{ds3}$ , and  $v_{ds4}$  instantaneous drain to source voltage of the four switches,

respectively

| $V_o$                                     | nominal output voltage                                        |

|-------------------------------------------|---------------------------------------------------------------|

| $V_d$                                     | nominal input voltage                                         |

| $V_{d min}$ and $V_{d max}$               | input de voltage range                                        |

| <i>T</i> ,                                | switching cycle period                                        |

| $t_d$                                     | switching dead time                                           |

| t                                         | time variable                                                 |

| $I_{aux}$ and $I_{aI}$                    | peak value of the current through the two auxiliary inductors |

|                                           | $L_{aux}$ and $L_{af}$ , respectively                         |

| $I_{LIpk}$ and $I_{LIv}$                  | peak and valley values of the current through the output      |

|                                           | inductor $L_i$ , respectively                                 |

| $I_{L2pk}$ and $I_{L2v}$                  | peak and valley values of the current through the output      |

|                                           | inductor $L_2$ , respectively                                 |

| $I_{ppk}$ and $I_{pv}$                    | peak and valley values of the current in primary winding of   |

|                                           | transformer $T_{fr}$ , respectively                           |

| $I_o$                                     | nominal output current                                        |

| $i_{ds1}, i_{ds2}, i_{ds3}$ and $i_{ds4}$ | instantaneous primary current of the four switches.           |

|                                           | respectively                                                  |

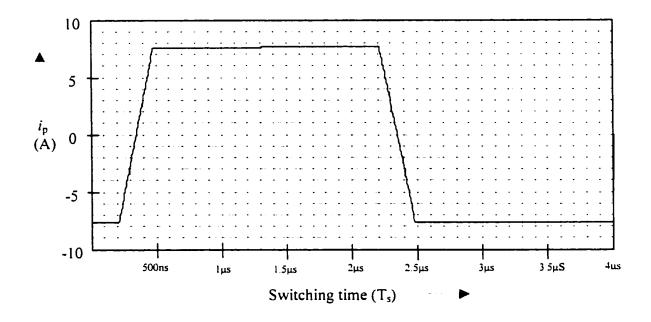

| $i_p$                                     | instantaneous primary current of the power transformer        |

| $\dot{t}_{aux}$                           | instantaneous auxiliary current through the auxiliary         |

inductor  $L_{aux}$

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

Full-bridge dc/dc converters are extensively used in medium to high power level applications. For most of these applications, particularly those of the computer and telecommunication systems, the most desirable features of the converter are high efficiency, high power density, high reliability and low EMI.

Unfortunately, the standard full bridge topology operates in hard switching, and the hard switching converter is unable to achieve high efficiency and high power density, because of the following reasons. In order to achieve high power density, the switching frequency is normally increased. At increased frequency, the converter can employ smaller sized power magnetics and capacitors. However, as the switching frequency increases, the switching losses associated with the turning on and off of switches will become excessive. These losses remarkably reduce the converter's overall efficiency, and high power density can hardly be achievable due to the resultant high cooling requirements.

To solve these problems, soft switching techniques are normally used. Basically there are two types of the soft switching techniques: zero voltage switching (ZVS) and zero current switching (ZCS). Either of the techniques can greatly reduce and even completely eliminate the switching losses in a converter, and then high efficiency will be

obtained. However, it has been well understood that ZVS is more advantageous for a MOSFET switch topology than is ZCS.

High power level full bridge converters usually use IGBT switches, due to IGBT's low conduction losses and high power capability. However, IGBT is not as fast as MOSFET, and its switching frequency is hardly above 100 kHz. Unlike IGBT, MOSFET is a resistive device when it is turned-on, and the conduction losses are higher as compared to IGBT. However, MOSFET is the fastest device and is able to be operated above 1 MHz.

As mentioned before, the approach to achieve high power density is to operate the converter at a higher switching frequency. Thus, for power levels below 3 kW, the full-bridge converters now employ MOSFET switches. In most of these converters, ZVS is used to boost the overall efficiency and alleviate the thermal problems. However, as to be reviewed in the following section, these converters lose ZVS under some operating conditions, causing potential thermal problems and risking the reliability of the converter.

#### 1.2 Review of Existing ZVS Full Bridge Topologies

#### 1.2.1 Conventional ZVS full bridge topologies

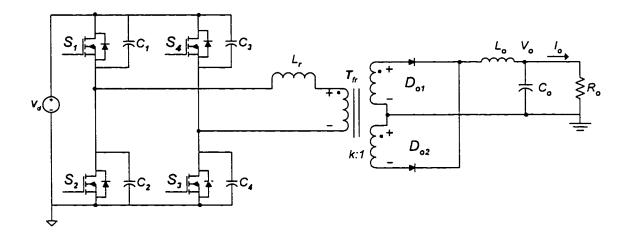

Fig. 1.1 shows two typical full bridge topologies those achieve ZVS. In Fig. 1.1a, ZVS is achieved by placing an inductor in series with the power transformer, while in Fig. 1.1b; it is achieved by placing an inductor in parallel with the power transformer. In both topologies, a snubber capacitor is placed across each switch. In a practical configuration, the series inductor may be the leakage inductor of the power transformer, the parallel inductor may be the magnetizing inductor of the power transformer, and the

snubber capacitor may be the inherent drain-to-source capacitor of the MOSFET switch.

All these make these topologies very simple.

a: ZVS topology with series inductor

b: ZVS topology with parallel inductor

Fig. 1. 1: Conventional ZVS full bridge converter topologies.

The basic operating principles to achieve ZVS in these two topologies are as follows.

- (i) ZVS turn-off is achieved by holding the drain-to-source voltage at zero or very low during the turn-off. This is accomplished by the snubber capacitor. At turn-off, the snubber capacitor significantly slows down the rising of the drain to source voltage of the pertinent switch. In this way, the overlaps between the decreasing drain current and rising drain-to-source voltage of each switch is greatly reduced, or even completely eliminated, and so are the switching losses.

- (ii) ZVS turn-on is achieved by completely discharging the snubber capacitors of the switches before they are turned-on. During the dead time of the gating of the bridge switches, the residual current in the series inductor as in the former topology, or the parallel inductor as in the later topology fulfills the discharging of the snubber capacitors.

In comparison of these two topologies in Fig. 1.1, the one with the series inductor can achieve ZVS even when a short circuit (or over loading) occurs in the load, while the other one that has the parallel inductor maintains ZVS operation even when an open circuit (or no load) occurs in output terminals. Both topologies are simple. However, both of them suffer from their own shortcomings.

The drawbacks of the topology with series inductor (Fig. 1.1a) include the following.

(i) Loss of ZVS at no load or light-load. It is because the completely discharge of snubber capacitors depends on the stored energy in  $L_r$  that is proportional to the square of the peak value of the primary current. When the load is light, the

primary current is low, and consequently the stored inductor energy is too low to deplete the snubber capacitor during the dead time. Thus, ZVS turn-on will be lost.

(ii) Reduction of the effective duty ratio because of the voltage drop on the series inductor. This leads to increase the output filter inductor, because a smaller effective duty ratio relates to higher ripple component in the secondary voltage, which needs a larger output inductor to filter out.

The drawbacks of the topology with parallel inductor (Fig. 1.1b) include the following.

- (i) Loss of ZVS under over load or short-circuit conditions. It is because, when short circuit occurs in the output terminal, the large load current, when it is reflected into the primary side, will override the parallel inductor current and cancel its function to achieve ZVS.

- (ii) Increased conduction losses and reduced efficiency at light load. It is because the circulating current flowing along the parallel inductor, switch and the input dc line is almost independent of the load level. At light load, the conduction losses arisen from the circulating current becomes significant compared to the load current, and this remarkably increases the total conduction losses as compared to the standard full bridge converter and the ZVS topology with series inductor.

It is seen that, both topologies lose ZVS under certain operating conditions. The loss of ZVS results in the following problems: (i) increased size of heat sink due to switching losses, (ii) higher EMI due to high di/dt of the snubber discharging current when the switch is turned-on, and (iii) reduced reliability due to reverse recovery current

5

of the body diodes.

#### 1.2.2 ZVS full bridge topology with auxiliary circuit

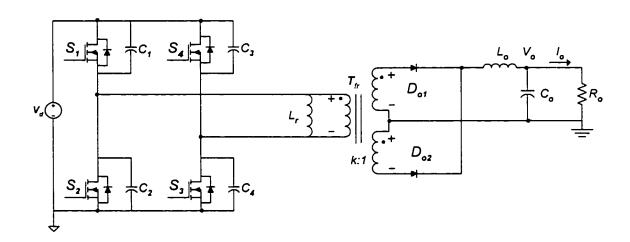

Fig. 1.2 shows a ZVS full bridge topology with passive components [1]. It employs two asymmetrical auxiliary circuits. At proper timing, the switches are turned-on and off such that the appropriate snubber capacitor of the switches is discharged immediately before the switch is turned-on. This active approach to achieve ZVS overcomes the aforementioned drawbacks existing in the topologies shown in Fig. 1.1. Specifically, it achieves ZVS even under both extreme operating conditions, namely no load and output short circuit conditions, and there is no reduction of the effective duty ratio.

Fig. 1. 2: ZVS full bridge converter topology using auxiliary devices.

However, the topology in Fig. 1.2 is originally developed for low to medium power full-bridge converters using MOSFET's with low output current. For the same power with very high output current applications and increased switching frequency, the circuit topology should be further optimized to reduce the conduction losses caused by the auxiliary circuits. Also, at the same time efficient and synchronous rectification technique should be included in the output stage. Following section discusses a current doubler for the output rectifier circuit.

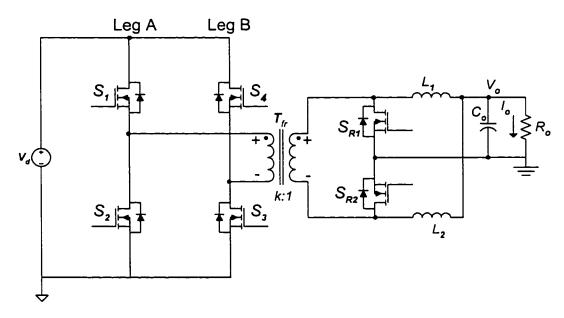

#### 1.2.3 ZVS full bridge converter with current doubler synchronous rectifiers

Fig. 1.3 shows the operation of a ZVS full bridge topology with current doubler, synchronous rectifiers [3]. The current doubler offers an alternative rectification method for the bridge converters where bipolar voltages are utilized at the secondary side of the isolation transformer. It is well suited for low voltage and high current applications. The current doubler has following advantages [5]:

- there is no need for center-tapping

- transformer structure is simpler

- ripple currents cancel on output capacitor.

- each filter inductor carries only half of the dc output current.

- finer steps in turns ratio are possible

- transformer carries approximately half of the output current.

- operation on the primary side, including duty-cycle is unchanged.

synchronous rectifier and output capacitor stresses are identical to the full-wave technique.

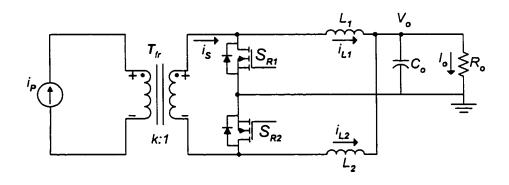

Fig. 1.3: Circuit diagram of current doubler rectifier.

Advancement in high density, low  $r_{ds(on)}$  MOSFET development makes synchronous rectification a feasible and competitive rectification technique for low voltage, high current dc/dc converters. Synchronous MOSFET switches are used in the design to achieve higher efficiency [5], [16], [17]. The proper timing for the gates of the MOSFET rectifiers have an important role in determining the ultimate efficiency of the circuit. Early termination of the conduction interval will force the current into the body diode of the transistors leading to reverse recovery problems and switching losses in the devices. Conversely, any delay at the turn-off of the synchronous switches will result in a shoot through situation on the secondary side of the isolation transformer lowering the efficiency of the circuit.

Phase shift PWM technique is used as the control technique to regulate the

output voltage. Since the conventional phase-shift full-bridge converters have been extensively addressed in the literature, only the operation of the secondary side of the current doubler is discussed. The operation of the current doubler with synchronous rectification is highlighted in Fig. 1.4. In accordance with the primary side, the switching interval is divided into four intervals.

#### A. Interval $1 (t_o \le t < t_p)$

At  $t_o$ , voltage across transformer ( $v_T$ ) becomes positive at the end of last interval. During Interval 1,  $S_{R1}$  is off and  $S_{R2}$  is on. Current flows in positive direction in both filter inductors  $L_I$  and  $L_2$ . The sum of  $i_{LI}$  and  $i_{L2}$  supplies the load current. The load current is equally shared between  $L_I$  and  $L_2$ . The current  $i_{LI}$  flows through  $S_{R2}$  and the transformer secondary. The voltage across  $L_I$  is equal to  $v_T - v_o$ . This positive voltage causes  $i_{LI}$  to increase. At the same time,  $L_2$  freewheels through  $S_{R2}$  and  $i_{L2}$  decreases by the rate of  $\frac{v_o}{L_2}$ . The current through the secondary ( $i_T$ ) is equal to  $i_{LI}$  and its accounts for half of the total load current.

#### B. Interval 2 $(t_1 \le t < t_2)$

In this interval,  $v_T$  becomes zero and both  $S_{R1}$  and  $S_{R2}$  are on. The voltage across  $L_I$  becomes  $-v_o$ , producing a negative slope in  $i_{LI}$ , which now flows through  $S_{RI}$ . The conditions for  $L_2$  do not change and both inductors are in freewheeling mode.

Fig. 1.4: Operation of the current doubler rectifier.

#### C. Interval 1 $(t_2 \le t < t_3)$

In this Interval,  $v_T$  becomes negative.  $S_{R1}$  is on and  $S_{R2}$  is off. A positive voltage  $v_T - v_o$  appears across  $L_2$  and  $i_L$ , starts to increase. In this state,  $i_T$  equals  $i_L$ , flows in the secondary again.  $L_I$  freewheels through  $S_{RI}$  and  $i_{LI}$  decreases by the rate of  $-\frac{v_o}{L_I}$ .

#### D. Interval 4 $(t_3 \le t < t_d)$

The full operating cycle is completed by another freewheeling period. The voltage  $v_T$  becomes zero and  $S_{R1}$  and  $S_{R2}$  are on.  $-v_o$  appears across  $L_2$  causing its current to decrease and freewheel through  $S_{R2}$  while  $L_1$  continues to freewheel as in Interval 3.

After Interval 4, the other switching cycle will start and the same operation is repeated again.

#### 1.3 Objectives and scope of the study

The objectives of the study are as follows:

- (i) presenting an optimized ZVS full bridge topology for low-voltage and highcurrent applications,

- (ii) characterizing the proposed topology for industrial applications,

- (iii) generating the design procedure.

The scope of this thesis is limited within the following frame:

- (i) steady state analysis,

- (ii) concept verification through ORCAD simulations and experimental results.

#### 1.4 Thesis outline

The thesis follows the following structure.

In Chapter 2, the proposed topology is presented. Circuit description, operation and comparison and description for different gate driving techniques used for the control of synchronous rectification.

In Chapter 3, the steady state analysis is performed to understand its steady states characteristics and properties.

In Chapter 4, the performance and characteristics curves for the proposed topology has been proposed.

In Chapter 5, a design example is given for industrial application and for the proof of concept.

Conclusions of the thesis work are drawn in Chapter 6, followed by the suggestions for the future work.

#### **CHAPTER 2**

### FULL BRIDGE CONVERTER WITH SYNCHRONOUS RECTIFICATION

#### 2.1 Introduction

The improved line and load independent ZVS full bridge converter topology is presented in this chapter. This topology is simply a combination of a conventional full bridge converter and an auxiliary circuit that consists of few passive components. The effect of leakage inductance has also been taken into account. However, the advantages of the topology are remarkable: (i) it achieve ZVS independent of line and load conditions, and the power circuit is just that of the conventional full bridge converter, (ii) ZVS independent of line and load conditions results in smaller heat sinks for the switches and also the capability of operating the converter at high frequency, (iii) the design of the converter can follow well understood and well developed procedure to facilitate industrial application.

To extend the soft-switching capability of the phase shifted full bridge converter to supply low voltage, high current loads in distributed power systems, the current doubler offers an alternative rectification method, where bipolar voltages are utilized at the secondary side of the isolation transformer. Synchronous MOSFET switches are used in the design to achieve higher efficiency and zero voltage transitions from zero to full load [5], [16], [17].

In order to understand the operating principle and performance characteristics of

the proposed topology, and to provide reference in design procedure in Chapter 4, the steady state analysis is performed in the chapter 3.

In this chapter, the proposed topology is presented in Section 2.2. The working of the proposed topology is explained in Section 2.3. At the end of this chapter, some conclusions are drawn.

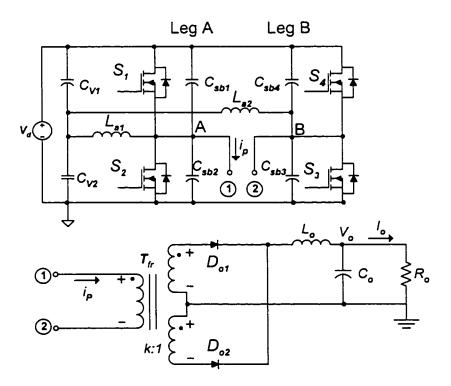

#### 2.2 Circuit description

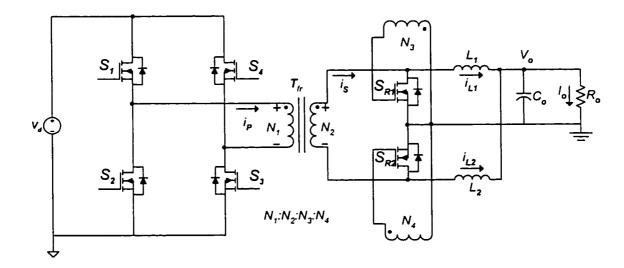

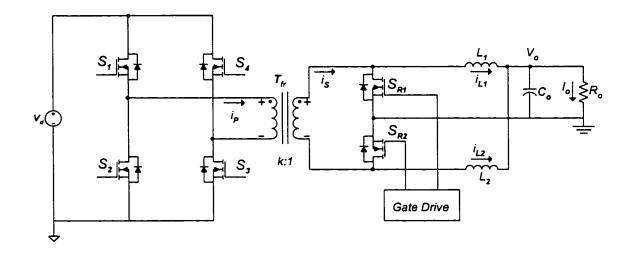

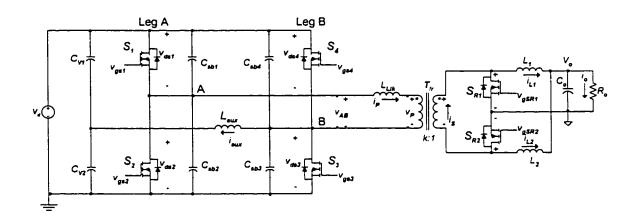

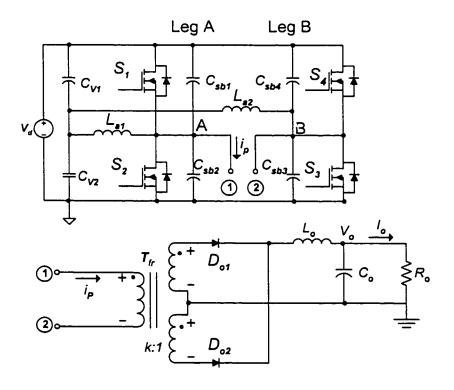

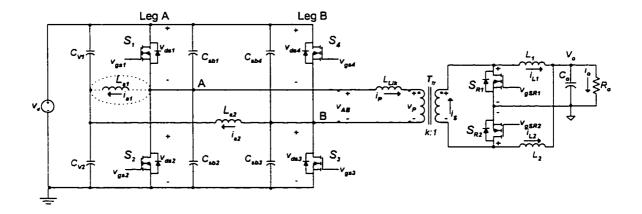

Fig. 2.1 shows the auxiliary commutated ZVS full bridge converter topology. It consists two functional sub-circuits. One sub-circuit is a PSM conventional full bridge converter, which is referred to as the power circuit hereafter. The other is an auxiliary network shown inside the dotted area in Fig. 2.1.

The power circuit employs the following devices: (i)  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ , four MOSFET switches, (ii)  $T_{fr}$ , the power transformer with a turns ratio of k, (iii)  $S_{R1}$  and  $S_{R2}$ , two synchronous rectifying MOSFET's, (iv)  $L_1$  &  $L_2$  and  $C_0$ , the output filter, and (v)  $R_0$ , the load.

The auxiliary circuit is comprised by seven passive devices, i.e., (i)  $C_{sb1}$ ,  $C_{sb2}$ ,  $C_{sb3}$ , and  $C_{sb4}$ , four drain-to-source snubber capacitors, each connected across one switch, (ii)  $C_{V1}$  and  $C_{V2}$ , a capacitor voltage divider, (iii)  $L_{aux}$ , a auxiliary inductor.

Phase shift pulse width modulation is used as the control technique for output regulation in the proposed converter topology. When conventional PWM converters are operated at higher frequencies, the circuit parasitics are shown to have detrimental effects on the converter performance. Switching losses are specially pronounced in high frequency operations. Snubbers are normally required, thus adding significant losses in

high frequency operation. This topology enables designers to advantageously employ transformer leakage inductance along with auxiliary inductance. It has a somewhat higher rms current than the conventional full-bridge PWM converter, but with the combination with auxiliary inductor, it has much lower rms currents than other converters. The auxiliary inductor hardly interferes with the power transfer from input to the output. However, the auxiliary circuit does have significant influence on the switching transients

Fig. 2.1 The proposed ZVS full bridge converter topology

of the switches: it simply removes the switching losses from all the switches during both turn-on and turn-off transients. Since the higher value of leakage inductance will reduce the effective duty cycle of the power circuit, eventually resulting in lower turns ratio. This increases the reflected output current value on the primary side and the voltage stress of the secondary side rectifier devices, both leading toward lower overall efficiency of the circuit. With the addition of the auxiliary inductor, the value of leakage inductance can be reduced and as a whole the power circuit efficiency can be increased with the expense of small conduction loss.

#### 2.3 Brief operation of the proposed converter

The gating signals are such that, instead of turning-on the diagonal opposite switches in the bridge simultaneously, a phase shift is introduced between the switches in the left leg and those in the right leg with a small delay between the switches of each leg. PSM is used as a control technique for the output voltage regulation and the externally driven technique (EDT) is used for the synchronous rectifier switches. Together, with the auxiliary circuit, the leakage inductance of the transformer, PSM control and EDT, zero voltage switching is achieved for all the switches of full-bridge converter as well as the synchronous rectifier.

The proposed converter has two modes of operation: Mode 1 and Mode 2. Mode 1 occurs at heavy loads and the converter has ten distinct operating intervals during a single switching cycle. The key waveforms and equivalent circuits are shown in Fig. 2.2 and Fig. 2.3. The other mode of operation occurs at light loads and the converter has twelve distinct operating intervals during one switching cycle. The key waveforms and equivalent circuits are shown in Fig. 2.4 and Fig. 2.5. The operation principle for Mode 1 and Mode 2 are explained in Section 2.3.1 and Section 2.3.2.

#### 2.3.1 Mode 1

It is well understood that power transfer from the primary side to the secondary side will be there when diagonal switches are conducting. The different intervals for Mode 1 are shown in Fig. 2.2 and the equivalent circuits are shown in Fig. 2.3. Mode 1 explains the behavior of the proposed converter.

Fig. 2.2 Key waveforms for the proposed converter topology in Mode 1. The dead time and switching transient are exaggerated.

Fig. 2.3 Equivalent circuit in different intervals in Mode 1.

In the last interval of previous cycle when both  $S_2$  and  $S_4$  were on, the primary current of  $T_{fr}$  saw a constant voltage,  $-V_d$ , and  $S_{RI}$  was on and  $S_{R2}$  was off. At the end of this interval the primary current reached at its peak value  $I_{ppk}$ . At the beginning of this interval when  $S_2$  is turned-off and no other switching action takes place. The current flowing through  $S_2$  is the primary peak current  $I_{ppk}$  which is flowing through  $leg\ A$ starts to charge  $C_{sb2}$  and discharge  $C_{sb1}$ . During this interval  $T_{fr}$  starts to see a zero voltage which is given by dead time  $(t_d)$ . During this interval none of the secondary rectifier switches  $S_{RJ}$  and  $S_{R2}$  are turned-on so the current is freewheeling in both inductors. As this interval is small the primary current  $(i_p)$  remains constant. Within this interval the voltage across switch  $S_I$ , which is given by  $v_{dsI}$  falls to zero volts and the voltage across switch  $S_2$ , which is given by  $v_{ds2}$  reaches to  $V_d$ . Now  $S_1$  has ZVS condition for turn-on. In the next interval,  $S_i$  is turned-on in ZVS condition. As both  $S_i$ and  $S_4$  are on, the primary winding of  $T_{fr}$  sees zero voltage. During this interval  $S_{R2}$  is turned-on. At the beginning of Interval 3,  $S_{\bullet}$  is turned-off, the auxiliary current flowing through  $L_{aux}$  reaches to its peak, which is given by  $I_{aux}$ . In this interval primary current is still flowing in the negative direction due to the energy stored in  $L_{Llk}$ . This primary current helps auxiliary current to charge the snubber capacitor  $C_{sb4}$  and discharging snubber capacitor  $C_{sb3}$ . The duration of this interval is given by dead time. At the beginning of next interval,  $S_3$  is turned-on under ZVS condition. During this interval  $i_{aux}$ starts to decrease linearly and the primary current starts to reverse the direction from negative to positive. At the beginning of interval 5, the primary side has positive current and both diagonal switches  $S_i$  and  $S_j$  are on. Thus the power transfer from primary side to secondary side is there and load current is equally shared between  $L_i$  and  $L_2$ . The rest five intervals are similar to first five intervals.

### 2.3.2 Mode 2

The different intervals for Mode 2 are shown in Fig. 2.4 and the equivalent circuits are shown in Fig. 2.5. Mode 2 explains the behavior of the proposed converter. This mode occurs at light loads and has twelve distinct operations. The working and operation is same as Mode 1 but due to light load it is going to have two more additional intervals per switching cycle.

In the last interval of previous cycle when both  $S_2$  and  $S_4$  were on, the primary current of  $T_{fr}$  saw a constant voltage,  $-V_d$ , and  $S_{RI}$  was on and  $S_{R2}$  was off. At the end of this interval the primary current reached at its peak value  $I_{ppk}$ . At the beginning of this interval when  $S_2$  is turned-off and no other switching action takes place. The current flowing through  $S_2$  is the primary peak current  $I_{ppk}$  which is flowing through  $leg\ A$  starts to charge  $C_{sb2}$  and discharge  $C_{sb1}$ . During this interval  $T_{fr}$  starts to see a zero voltage which is given by dead time  $(t_d)$ . During this interval none of the secondary rectifier switches  $S_{RI}$  and  $S_{R2}$  are turned-on so the current is freewheeling in both inductors. As this interval is small the primary current  $(i_p)$  remains constant. Within this interval the voltage across switch  $S_1$ , which is given by  $v_{ds2}$  reaches to  $V_d$ . Now  $S_1$  has ZVS

Fig. 2.4 Key waveforms for the proposed converter topology in Mode 2. The dead time and switching transient are exaggerated.

Fig. 2.5 Equivalent circuit in different intervals in Mode 2.

condition for turn-on. In the next interval,  $S_i$  is turned-on in ZVS condition. As both  $S_i$ and  $S_4$  are on, the primary winding of  $T_{fr}$  sees zero voltage. During this interval  $S_{R2}$  is turned-on. In this interval primary current discharge the leakage inductance (  $L_{\it Lik}$  ) very fast and changed the direction from negative to positive. During the beginning of next interval no switching action takes place and the primary current remains constant for the rest of interval. In the beginning of Interval 4,  $S_4$  is turned-off, the auxiliary current flowing through  $L_{aux}$  reaches to its peak, which is given by  $I_{aux}$ . During this interval, auxiliary current is enough to charge the snubber capacitor  $C_{sb4}$  and discharging snubber capacitor  $C_{sb3}$ . The duration of this interval is very small which is given by dead time. In this interval, the primary side of the transformer starts to see the positive voltage. At the beginning of next interval,  $S_3$  is turned-on under ZVS condition. During this interval  $i_{aux}$ starts to decrease linearly. The primary side has positive current and both diagonal switches  $S_i$  and  $S_3$  are on. Thus the power transfer from primary side to secondary side is there and load current is equally shared between  $L_1$  and  $L_2$ . At the beginning of interval 6, no switching action takes place so there will be no effect on the power transfer. The rest six intervals are similar to first six intervals.

### 2.4 Synchronous Rectification

The conduction loss of diode rectifier contributes significantly to the overall power loss in a power supply, especially in low output-voltage application. The rectifier conduction loss is proportional to the product of its forward voltage drop,  $V_F$  and the forward conduction current,  $I_F$ . On the other hand, operating the MOSFET in third

quadrant, it can be used as a synchronous rectifier, which presents a resistive *i-v* characteristic. Under certain current level, the forward voltage drop of a synchronous rectifier can be lower than that of a diode rectifier, and consequently reduces the rectification loss [17]. Due to the fact that the synchronous rectifiers are active devices, the design and utilization of synchronous rectification need to properly address.

Fig. 2.6: MOSFET used as a synchronous rectifier

With the advanced technology in MOSFET design, the on-resistance is very low (in the order of a few milliohms), thus the power losses are also very low. Since the MOSFET now acts as a diode and not as a switch, the role of the source and drain become reversed. Fig. 2.6 shows the synchronous rectifier, where the current of full bridge is modeled as a square wave current source on the primary side. When the power MOSFET is used for synchronous rectification, it is configured so that the current normally flows through the channel from source to drain (in the direction of body diode). This ensures reverse blocking capability by the body diode, when the transistor is off because there is no current path through the body diode. To guarantee that the two MOSFET's do not turn- on simultaneously and create a transformer short circuit, a dead

time is usually introduced between the two gate signals. Control of the synchronous switches now becomes the main issue. The synchronous rectifiers can either be self-driven or external driven. A few examples of gate driving techniques for synchronous rectifiers have been presented in Section 2.4.1 and 2.4.2. The advantages and disadvantages of these synchronous rectification techniques have been explained briefly in Section 2.4.3

### 2.4.1 Self-driven technique

Fig. 2.7 shows full bridge current doubler with synchronous rectification using self-driven gate driving technique has been shown. Transformer  $T_{fr}$  has four windings  $N_1:N_2:N_3:N_4$  as shown in Fig. 2.7. Since no driver or control circuit is used to provide the gate-drive signals, this implementation of synchronous rectification is the simplest possible. The driving voltage now controls the conduction of MOSFET's. As the driving voltage, in the case of phase shifted bridge converter, is a quasi-voltage, the synchronous MOSFET's are on only during the positive and negative intervals of the driving voltage waveform. This results in lesser utilization of the synchronous MOSFET switches and the rectifier losses can't be reduced significantly. As every MOSFET has turn-on and turn-off delay, the load current at first flows through the body diodes of  $S_{RI}$  and  $S_{R2}$ . Due to relatively high forward voltage drops of the body diodes of  $S_{RI}$  and  $S_{R_2}$ , the efficiency of synchronous rectification is reduced. The efficiency loss due to the body diode conduction depends on the duration of the dead time and the forward voltage drop of the body diodes. This loss can be minimized by connecting schottky diodes in parallel with  $S_{RI}$  and/ or  $S_{R2}$  or by minimizing the conduction times of body diodes of

$S_{RI}$  and  $S_{R2}$ .

Fig. 2.7: MOSFET used as a synchronous rectifier using self-driven technique

The conduction loss of the body diodes of  $S_{RI}$  and  $S_{R2}$  is also dependent on the commutation time. To minimize the commutation times, the total inductance of the secondary side should be minimized. Moreover, it is important to make the leakage inductance of the transformer small relative to the other circuit inductance to avoid a loss of gate drive voltage for SR's.

The conduction of the body diodes of SR's not only increase the conduction loss, but also introduces the power loss due to their reverse recovery. This loss becomes more significant at high frequency at full load and high line. The only method of eliminating this loss is to parallel the schottky diodes to  $S_{RI}$  and  $S_{R2}$ .

#### 2.4.2 External driven or control-driven technique

The problems of previous self-driven technique become more pronounced as the frequency is increased. Using external driven control circuits for the synchronous rectifier these drawbacks can be reduced. With this type of control, discrete IC's are used to drive the gate signal to achieve precise timing. The goal of whole exercise is to imitate the function of an ideal diode. When the drain-source voltage goes to zero, the MOSFET will turn-on and when the drain current goes to zero, the MOSFET will turn-off.

Fig. 2.8 shows the full bridge current doubler with synchronous rectification using external driven technique. The important issue, which justifies the use of synchronous rectifiers in place of diode rectifiers, is the timing. This is especially necessary as the operating frequencies are increased. The turn-on and turn-off of the switch has to be exactly on time, otherwise the inherent body diode will begin conducting resulting in increased conduction losses. In most cases, this could pose a problem since the external gate drive circuit will naturally have propagation delay. A brief overlapping of the gate-drive signals that turn-on both SR's simultaneously would short the secondary, causing an increased secondary current, and thus would lower efficiency or, in severe cases, would cause converter failure. To avoid simultaneous conduction of SR's in practical applications, a delay period is introduced. Since during the delay period no gate-drive signal is applied to the SR's the body diodes of the SR's are conducting. This not only increases conduction losses but also introduce reverse recovery loss. Therefore, the performance of control driven SR's is strongly dependent on the timing of the gate drive.

Fig. 2.8 MOSFET used as a synchronous rectifier using external-driven technique

## 2.4.3 Comparison of synchronous rectifier topologies

The different types of gate driving techniques for synchronous rectification have been examined. The advantages and disadvantages of the above driving techniques has been explained briefly:

# Self -driven technique

### Advantages:

- no external control or driver circuitry required

- simple design and requires few components

## Disadvantages:

- synchronous rectifier losses increases as frequency increases

- power losses due to reverse recovery of body diodes

### External driven or control driven

### Advantages:

- suitable for high frequency operation

- very good accuracy

- synchronous rectifier including power MOSFET and gate/driver circuitry can be packaged together on a single chip, thus reducing losses otherwise caused by discrete components

- overcome timing delay problem

#### Disadvantages:

- more complex design

- packaging of synchronous rectifier on a single chip is costly

#### 2.5 Conclusions

The operation of current doubler with synchronous rectification has been presented and it is clear by the description that the auxiliary circuit hardly interferes in the working of the proposed topology. The circuit is not complex and easy to understand. Also the different synchronous rectification techniques have been described briefly and some of conclusions based on the comparison of the different gate drive techniques used for synchronous rectification have been explained. As it is found from the comparison and description for the external and self- driven techniques for synchronous rectification that external driver is more suitable for high frequency operation.

# **CHAPTER 3**

# STEADY STATE ANALYSIS

#### 3.1 Introduction

The analysis of improved ZVS full bridge converter with synchronous rectification shown in Fig. 3.1 has been presented in this chapter. The working principle has been described in Chapter 2. In this Chapter the detailed analysis of the proposed converter has been given.

The converter has two Modes of operation- Mode 1 occurs at full load or higher load. However Mode 2 occurs at reduced load. The difference between Mode 1 and Mode 2 is the energy stored in the leakage inductance. The optimization of leakage inductance and auxiliary inductance has been analyzed.

To better understand the operating principle and performance characteristics of the proposed topology performed in Chapter 4, and to provide reference in optimal procedure in Chapter 5, a detailed steady state analysis is performed in this chapter.

The steady state analysis is done in Section 3.2 for both Mode 1 and 2. Comparison between simulation done by ORCAD and analysis performed by Math CAD software has been given in Section 3.3.

### 3.2 Steady state analysis

As explained, in Chapter 2, a phase-shift control method is used in operating the converter. As conventional phase shift full bridge converters have been extensively discussed in the literature, the analysis of its operation will not be addressed in detail.

Only the operation of the auxiliary circuit with leakage inductance is analyzed below.

The analysis will be performed with the assumptions made below. In the analysis, the time varying variables such as the current and voltage of the principal components and devices are determined. Based on these variables, the performance of the converter can be illustrated, and the quantities such as rms, average or peak current and voltage of these components can be obtained. These quantities are used in designing the converter as presented in Chapter 5.

Fig. 3.1 The proposed ZVS full bridge converter topology

In the analysis presented below, a closed form solution is obtained by solving a set of differential equations in each interval and by matching the boundary conditions at the boundary of the intervals.

### 3.2.1 Assumptions and some constants for the analysis

To perform the steady state analysis, the following assumptions are made:

- (i) The steady state conditions have been established and the converter is running in the continuous conduction mode at an input dc voltage  $V_d$ , producing the nominal output voltage  $V_o$  and delivering a power of  $P_o$  to a static load.

- (ii) The gating of switches on  $leg\ A$ , namely  $S_1$  and  $S_2$ , is leading the gating of switches on  $leg\ B$ , or  $S_3$  and  $S_4$ , by a phase shifted angle  $\theta$  which is required to regulate the output voltage,

- (iii) The switching frequency is  $f_s$ ,

- (iv) All components and devices have ideal properties and characteristics, i.e.,

- (1)  $T_{fr}$ : core works in a linear range and the transformer has a leakage inductance ( $L_{Lik}$ ),

- (2)  $L_1$ ,  $L_2$  and  $L_{aux}$ : all inductors are pure inductors and their losses are negligible, and their inductances are constant,

- (3)  $C_o$ ,  $C_{V1}$ ,  $C_{V2}$ ,  $C_{sb1}$ ,  $C_{sb2}$ ,  $C_{sb3}$ , and  $C_{sb4}$ : all capacitors are pure capacitors, their equivalent series resistance (ESR) and equivalent series inductance (ESL) are negligible,

- (4)  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ : all switches have negligible conduction losses, and the inherent capacitances are 0 F,

- (5)  $S_{R1}$  and  $S_{R2}$ : the forward voltage drop is 0 V, and the recovery time is 0 s.

- (6) The magnetizing inductance of the power transformer is so great that the magnetizing current is negligible.

- (v) There is a very short dead time,  $t_d$ , between the on states of the two switches on each leg of the bridge,

- (vi)  $C_{sb1}$  and  $C_{sb2}$  have equal capacitance value, and so do  $C_{sb3}$  and  $C_{sb4}$ ,

- (vii)  $C_{\nu_1}$  and  $C_{\nu_2}$  have equal capacitance value, and they are large enough to maintain constant and ripple free voltage during the steady state operation.

- (viii) Under these assumptions, the operating principle is illustrated. The proposed converter has two modes of operation: Mode 1 occurs at full load and Mode 2 occurs at reduced loads. The key waveforms for Mode 1 were shown in Fig. 2.2. Each switching cycle can be divided into ten distinct intervals. The equivalent circuit for each interval in Mode 1 has been shown in Fig 2.3. The key waveforms for Mode 2 have been shown in Fig. 2.4. Each switching cycle can be divided into twelve distinct intervals. The equivalent circuit for each interval in Mode 2 is shown in Fig 2.5.

For convenience, some constants are defined below.

In steady state, the effective duty ratio  $D_{\it eff}$  of each output rectifier is determined

by

$$D_{eff} = \frac{D}{\left[1 + \frac{L_{Llk} \cdot f_s}{k^2 \cdot R_o}\right]}$$

(3-1)

where,

$$k = \frac{V_d \cdot D_{eff}}{V_o}, \tag{3-2}$$

$$D = \frac{1}{2} - \frac{t_d}{T_s} - \theta \,, \tag{3-3}$$

and

$$D_{\text{max}} = \frac{1}{2} - \frac{t_d}{T_c}$$

(3-4)

where  $t_d$  is the switching dead time of the main switches,  $f_s$  the switching frequency, D is primary duty cycle,  $D_{eff}$  is change in duty cycle due to leakage inductance ( $L_{Llk}$ ) and  $\theta$  the phase shifted angle expressed in a fraction of one switching cycle.

It is not difficult to find that the current flowing through the output inductor has a waveform of saw-tooth biased by the output dc current  $I_o$ . Defining  $I_{LIpk}$  and  $I_{LIv}$  as the peak and valley values of this saw-tooth shaped current, respectively, then there are:

$$I_{L1pk} = \frac{1}{2} [I_o + \frac{V_o}{L_1} (1 - D_{eff}) T_s]$$

(3-5)

$$I_{L1v} = \frac{1}{2} [I_o - \frac{V_o}{L_1} (1 - D_{eff}) T_s]$$

(3-6)

For the auxiliary circuit,  $C_{v_1}$  and  $C_{v_1}$  act as a voltage divider, each holding half the input voltage  $V_d$ . For example, when  $S_3$  is on for the duration of half cycle minus  $t_d$ ,  $L_{aux}$  sees the positive voltage across  $C_{v_1}$  that is  $\frac{V_d}{2}$ , and when  $S_4$  is on, it sees the voltage across  $C_{v_2}$  in opposite polarity that is  $-\frac{V_d}{2}$ . Then the current through, the auxiliary inductor  $L_{aux}$  alternatively rises and falls in linear mode. The magnitude of the total variation of this fluctuating current is determined as,

$$\Delta I_{aux} = \frac{V_d}{2L_{aux}} \left(\frac{T_s}{2} - t_d\right) \tag{3-7}$$

In addition, because the capacitors  $C_{\nu_1}$  and  $C_{\nu_2}$  the steady state auxiliary inductor current have no dc component. Thus, the current have a triangular waveform that is symmetrical about zero. Defining  $I_{aux}$  as absolute peak values of the current through  $L_{aux}$ :

$$I_{aux} = \frac{V_d}{4L_{aux}} (\frac{T_s}{2} - t_d)$$

(3-8)

### 3.2.2 Steady state analysis of each interval in Mode 1

# A. Interval $1 (t_o \le t < t_p)$

In the last interval of previous cycle, both  $S_2$  and  $S_4$  were on while both  $S_1$  &  $S_3$  were off, the primary winding of  $T_{fr}$  saw a constant voltage,  $-V_d$ , and  $S_{R1}$  was forward biased and  $S_{R2}$  reverse biased. Thus, the output inductor current  $i_{L1}$  was reflected back into the primary side via  $S_{R1}$  and the coupling of  $T_{fr}$ . The drain current of  $S_2$  was given by primary current and it reached its peak value at the end of the last cycle. This peak value is given by

$$I_{ppk} = \frac{I_{L1pk}}{k} \tag{3-9}$$

At the beginning of this interval,  $S_2$  is turned-off, and no other switching action takes place during this interval. The equivalent circuit of this interval is shown in fig. (2.3), Interval 1.

As  $S_2$  is off,  $I_{ppk}$ , which is the total current flowing into  $leg\ A$ , starts to charge  $C_{sb2}$  and discharge  $C_{sb1}$ . Thus, the drain to source voltage of  $S_1(v_{ds1})$  is decreasing while the drain to source voltage of  $S_2(v_{ds2})$  is increasing. Also  $S_3$  remains off and  $S_4$  is on. Then  $T_{fr}$  starts to see a zero voltage during this interval. Thus,  $S_{R1}$  and  $S_{R2}$  are both off. Both the inductors are in freewheeling stage.  $i_S$  (secondary current) equals to  $I_{L2pk}$  is

reflected back into the primary side. Thus, the primary peak current ( $I_{ppk}$ ) is flowing into  $leg\ A$ .

As the interval is very small, the primary peak current ( $I_{ppk}$ ) can be considered as constant. The drain to source voltage of both switches in  $leg\ A$  are governed by,

$$-C_{sb1}\frac{dv_{ds1}(t)}{dt} + C_{sb2}\frac{dv_{ds2}(t)}{dt} = I_{ppk}$$

(3-10)

&

$$v_{ds1}(t) + v_{ds2}(t) = V_d$$

(3-11)

By taking initial conditions as  $v_{ds1}(t_o) = V_d$  and  $v_{ds2}(t_o) = 0$ , and by taking the values of  $C_{sb1} = C_{sb2}$ , the equations (3-10) & (3-11) can be solved as:

$$V_{dsl}(t) = V_d - \frac{I_{ppk}}{2C_{shl}}(t - t_o)$$

(3-12)

$$v_{ds2}(t) = \frac{I_{ppk}}{2C_{sh}}(t - t_o)$$

(3-13)

Within this interval,  $v_{ds,l}$  falls to zero volts and  $v_{ds,2}$  reaches  $V_d$ , then the body diode of  $S_1$  conducts to provide  $v_{ds,l}$  at zero in the rest of this interval. Now  $S_1$  has ZVS condition at turn-on.

After  $V_{ds1}$  reaches zero, the primary winding of  $T_{fr}$  will see a zero voltage as  $S_4$  is still on. During this interval both  $S_{R1}$  and  $S_{R2}$  are off. As required by the both output inductors, the output current  $I_o$  is equally shared. This mode is a freewheeling mode as in a conventional full bridge converter.

In the meantime, the current that flows through  $S_4$  only consist of  $i_{aux}$ , which is the current of the auxiliary inductor  $L_{aux}$ . It is found that

$$i_{aux}(t) = \frac{V_d}{2L_{aux}}(t - t_o - \theta \cdot T_s) + I_{aux}$$

(3-14)

The duration of this interval is the dead time  $t_d$ , i.e.,

$$t_1 - t_0 = t_d \tag{3-15}$$

# B. Interval 2 $(t_1 \le t < t_2)$

At the beginning of this interval,  $S_1$  is turned-on in ZVS condition. So,  $S_1$  will achieve zero turn-on losses. No other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.3, Interval 2.

As both  $S_1$  and  $S_4$  are on, the primary winding of  $T_{fr}$  still sees zero voltage. During this interval  $S_{R2}$  is turned-on and  $S_{R1}$  is still off. The primary current is still flowing through the primary winding. Hence,  $S_1$  consists of primary current which is governed by

$$I_{p}(t) = \frac{\frac{V_{d}}{L_{Llk}}(t_{3} - t_{4}) + I_{pv} + I_{ppk}}{(t_{3} - t_{1})} (t - t_{1}) - I_{ppk}$$

(3-16)

The current passing through  $S_4$  only has auxiliary current ( $i_{aux}$ ) flowing through it, which is given by

$$i_{aux}(t) = \frac{V_d}{2L_{aux}}(t - t_1 - \theta \cdot T_s) + I_{aux}$$

(3-17)

The duration of this interval is determined by the phase shift angle that is required to regulate the output voltage as well as by the dead time:

$$t_2 - t_1 = \theta \cdot T_s - t_d \tag{3-18}$$

# C. Interval 3 $(t_2 \le t < t_3)$

At the beginning of this interval,  $S_4$  is turned-off. No other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.3, Interval 3.

When  $S_4$  is off,  $i_{aux}$  reaches its positive peak value  $I_{aux}$  and remains constant during this interval. During this interval the primary current is still flowing and it helps in discharging and charging of snubber capacitors in  $leg\ B$ . It starts to charge  $C_{sb4}$  and discharge  $C_{sb3}$ . Owing to  $C_{sb4}$ ,  $V_{ds4}$  can only rise slowly, providing the ZVS condition for  $S_4$  to turn-off. Thus, a nearly loss less turn-off is achieved on  $S_4$ .

During this interval  $T_{fr}$  still see a zero voltage. During this interval  $S_{R2}$  is forward biased and  $S_{R1}$  is reverse biased. The load current is equally shared between  $L_1$  and  $L_2$ . The current  $I_{L1}$  flows through  $SR_2$  and the transformer secondary. The voltage across  $L_1$  is equal to  $V_P - V_o$ . Thus, the current flowing out of  $leg\ B$  is  $i_{dux}$  plus the reflected output inductor current during the charging/discharging interval.

As this interval is small,  $i_{aux}$  is almost constant at its peak value  $I_{aux}$  and the value of primary current which is decreasing during this interval can be defined as:

$$I_{p}(t) = \frac{\frac{V_{d}}{L_{Llk}}(t_{3} - t_{4}) + I_{pv} + I_{ppk}}{(t_{3} - t_{1})} (t - t_{1}) - I_{ppk}$$

(3-19)

Similar to Interval 1, it is found that

$$V_{ds3}(t) = V_d - \int_{t_1}^{t_3} \frac{I_{aux} - \frac{V_d}{L_{Llk}}(t_3 - t_4) + I_{pv} + I_{ppk}}{(t_3 - t_1)} dt$$

(3-20)

$$V_{ds4}(t) = \int_{t_1}^{t_3} \frac{I_{aux} - \frac{V_d}{L_{Llk}}(t_3 - t_4) + I_{pv} + I_{ppk}}{(t_3 - t_1)} dt$$

(3-21)

Within this interval,  $V_{ds3}$  falls to zero volts and  $V_{ds4}$  reaches  $V_d$ . The equation (3-20), (3-21) shows that the secondary current relieves switch  $S_3$  turn-on stress from  $i_{aux}$  by providing strength of  $i_{aux}$  in discharging the snubber capacitor ( $C_{sb3}$ ) of  $S_3$  but it will be increase the turn-off stress of  $S_4$ . During this Interval the primary of the transformer is till seeing zero voltage as negative current is still flowing through the primary due to the effect of leakage inductance in the primary side.

The duration of this interval is determined by the dead time:

$$t_3 - t_2 = t_d \tag{3-22}$$

# D. Interval 4 $(t_3 \le t < t_4)$

At the beginning of this interval,  $S_3$  is turned on under ZVS condition. Thus, a nearly loss-less turn-on is achieved for  $S_3$ . No other switching action takes place during this interval.

As  $S_3$  is on,  $L_{aux}$  sees a constant negative voltage established by  $C_{v2}$ .  $i_{aux}$  starts to decrease linearly, as given by

$$i_{aux}(t) = -\frac{V_d}{2L_{aux}}(t - t_3) + I_{aux}$$

(3-23)

During this interval, primary current  $I_p$  changes from the negative polarity to the positive polarity. It is found that,

$$I_{p}(t) = \frac{V_{d}}{L_{I/k}} (t - t_{4}) + I_{pv}$$

(3-24)

The duration of this interval is determined by the loss in duty ratio due to leakage inductor required to regulate the output voltage:

$$t_{4} - t_{3} = \Delta D \cdot T_{c} \tag{3-25}$$

where,  $\Delta D$  is the loss in Duty cycle due to leakage inductance and is given by:

$$\Delta D = \frac{I_o \cdot L_{Llk}}{k \cdot V_d \cdot T_s} \tag{3-26}$$

# E. Interval $5(t_4 \le t < t_5)$

At the beginning of this interval no switching action takes place and the primary side starts to build up the positive voltage equals to  $V_d$ . During this interval  $S_{R1}$  is off and  $S_{R2}$  is forward biased. Current is flowing in both filter inductors. The load current is equally shared between  $L_1$  and  $L_2$ . The value of  $L_{aux}$  is still decreasing which is governed by

$$i_{aux}(t) = -\frac{V_d}{2L_{aux}}(t - t_4) + I_{aux}$$

(3-27)

As the current becomes positive and diagonal switches  $S_1$  and  $S_3$  are on. The voltage across primary is  $V_d$ . The amount of current passing through primary is governed by

$$I_{p}(t) = \frac{I_{ppk} - I_{pv}}{(t_{5} - t_{4})}(t - t_{4}) + I_{pv}$$

(3-28)

The duration of this interval is determined by the effective duty ratio required to regulate the output voltage:

$$t_{5} - t_{4} = D_{eff} \cdot T_{s} = \frac{kV_{o}}{V_{d}}$$

(3-29)

### F. Interval 6 through 10

The analysis of the circuit in the last five intervals of this switching cycle is similar to the first five intervals. The process will not be repeated here. After Interval 10, another switching cycle begins and operation of the circuit repeats the process from Intervals 1 through 10.

### 3.2.3 Steady state analysis of each interval in Mode 2

When the load is reduced, the leakage inductor has a small stored energy. As a result primary current will change the direction. The time required to discharge and charge in the other direction is based on the value of leakage inductance. So there will be an increase of one more interval. So in Mode 2 it is going to have twelve intervals per switching cycle. The analysis, key waveforms and equivalent circuit for each interval are given in the following section. The key waveforms for Mode 2 are shown in Fig. 2.4. Each switching cycle can be divided into twelve distinct intervals. The equivalent circuit for Mode 2 for each interval is shown in Fig 2.5.

# A. Interval $1 (t_o \le t < t_p)$

In the last interval of previous cycle, both  $S_2$  and  $S_4$  were on while both  $S_1$  &  $S_3$

were off, the primary winding of  $T_{fr}$  saw a constant voltage,  $-V_d$ , and  $S_{R1}$  was forward biased and  $S_{R2}$  reverse biased. Thus, the output inductor current  $I_{L1}$  was reflected back into the primary side via  $S_{R1}$  and the coupling of  $T_{fr}$ . The drain current of  $S_2$  was given by primary current and it reached its peak value at the end of the last cycle. This peak value is given by

$$I_{ppk} = \frac{I_{LIpk}}{k} \tag{3-30}$$

At the beginning of this interval,  $S_2$  is turned-off, and no other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.5, Interval 1.

As  $S_2$  is off,  $I_{ppk}$ , which is the total current flowing into  $leg\ A$ , starts to charge  $C_{sb2}$  and discharge  $C_{sb1}$ . Thus, the drain to source voltage of  $S_1(V_{ds1})$  is decreasing while the drain to source voltage of  $S_2(V_{ds2})$  is increasing. Also  $S_3$  remains off and  $S_4$  on. Then  $T_{fr}$  starts to see a zero voltage during this interval. Thus,  $S_{R1}$  and  $S_{R2}$  are both off. Both the inductors are in freewheeling stage.  $I_S$  (secondary current) equals to  $I_{L2pk}$  is reflected back into the primary side. Thus, the primary peak current ( $I_{ppk}$ ) is flowing into  $leg\ A$ .

As the interval is very small, the primary peak current ( $I_{ppk}$ ) can be considered as constant. The drain to source voltage of both switches in  $leg\ A$  are governed by,

$$-C_{sb1}\frac{dV_{ds1}(t)}{dt} + C_{sb2}\frac{dV_{ds2}(t)}{dt} = I_{ppk}$$

(3-31)

&

$$V_{ds1}(t) + V_{ds2}(t) = V_d$$

(3-32)

By taking initial conditions as  $V_{ds1}(t_o) = V_d$  and  $V_{ds2}(t_o) = 0$ , and by taking the values of  $C_{sb1} = C_{sb2}$ , the equations (3-31) & (3-32) can be solved as:

$$V_{dsl}(t) = V_d - \frac{I_{ppk}}{2C_{chl}}(t - t_o)$$

(3-33)

$$V_{ds2}(t) = \frac{I_{ppk}}{2C_{sb2}}(t - t_o)$$

(3-34)

Within this interval,  $V_{ds1}$  falls to zero volts and  $V_{ds2}$  reaches  $V_d$ , then the body diode of  $S_1$  conducts to provide  $V_{ds1}$  at zero in the rest of this interval. Now  $S_1$  has ZVS condition at turn-on.

After  $V_{ds1}$  reaches zero, the primary winding of  $T_{fr}$  will see a zero voltage as  $S_4$  is still on. In this interval both  $S_{R1}$  and  $S_{R2}$  are off. As required by the both output inductors, the output current  $I_o$  is equally shared. This mode is a freewheeling mode as in a conventional full bridge converter.

In the meantime, the current that flows through  $S_4$  only consist of  $i_{aux}$ , which is the current of the auxiliary inductor  $L_{aux}$ . It is found that

$$i_{aux}(t) = \frac{V_d}{2L_{max}}(t - t_o - \theta \cdot T_s) + I_{aux}$$

(3-35)

The duration of this interval is the dead time  $t_d$ , i.e.,

$$t_1 - t_o = t_d \tag{3-36}$$

# B. Interval 2 $(t_1 \le t < t_2)$

At the beginning of this interval,  $S_1$  is turned-on in ZVS condition. So,  $S_1$  will achieve zero turn-on losses. No other switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.5, Interval 2.

As both  $S_1$  and  $S_4$  are on, the primary winding of  $T_{fr}$  still sees zero voltage. During this interval  $S_{R2}$  is turned-on and  $S_{R1}$  off. The primary current is still flowing through the primary winding but due to reduced load the charge stored in leakage inductor ( $L_{Llk}$ ) starts to decrease and change to the direction from negative to positive. Hence,  $S_1$  consists of primary current which is governed by

$$I_{P}(t) = \frac{V_{d}}{L_{Llk}}(t - t_{1}) - I_{ppk}$$

(3-37)

The current passing through  $S_4$  only has auxiliary current ( $i_{aux}$ ) flowing through it, which is given by

$$i_{aux}(t) = \frac{V_d}{2L_{aux}}(t_1 - t) + I_{aux}$$

(3-38)

The duration of this interval is determined by the phase shift angle that is required to regulate the output voltage as well as by the dead time:

$$t_2 - t_1 = \frac{I_o \cdot L_{Llk}}{k \cdot V_d} \tag{3-39}$$

# C. Interval 3 $(t_2 \le t < t_3)$

At the beginning of this interval, no other switching action takes place. The equivalent circuit of this interval is shown in Fig. 2.5, Interval 3.

During this interval  $T_{fr}$  still see a zero voltage. During this interval  $S_{R2}$  is forward biased and  $S_{R1}$  is reverse biased. During this interval the primary current reached to a constant value as no switching action takes place. During this interval the primary current can be given by:

$$I_{p}(t) = \frac{V_{d}}{L_{III}}(t_{2} - t_{1}) - I_{ppk}$$

(3-40)

The duration of this interval is determined by:

$$t_{s} - t_{2} = \theta \cdot T_{s} - t_{d} - t_{2} + t_{1} \tag{3-41}$$

# D. Interval 4 $(t_3 \le t < t_{\psi})$

At the beginning of this interval,  $S_4$  is turned-off and no other switching action takes place. The equivalent circuit of this interval is shown in Fig. 2.5, Interval 4.

When  $S_4$  is off,  $i_{aux}$  reaches to its positive peak value  $I_{aux}$ . Similar to Interval 1, this current starts to charge  $C_{sb4}$  and discharge  $C_{sb3}$ . The  $V_{ds4}$  starts to rise from zero while  $V_{ds3}$  decreases from  $V_d$ .

During this interval  $T_{fr}$  starts to see a positive voltage because  $S_1$  is already on. Therefore, the current flowing out of  $leg\ B$  is  $i_{aux}$  minus the reflected current from the load during the charging and discharging interval.

As this interval is very short,  $i_{aux}$  is almost constant at its peak value  $I_{aux}$ . The primary current starts to increase during this interval, which is given by:

$$I_{P}(t) = \frac{2I_{ppk} - \frac{V_{d}}{L_{Llk}} (t_{2} - t_{1})}{(t_{6} - t_{3})} (t - t_{3}) + \frac{V_{d}}{L_{Llk}} (t_{2} - t_{1}) - I_{ppk}$$

(3-42)

Similar to Interval 1, it is found that

$$V_{ds3}(t) = V_d - \int_{t_1}^{t_2} \frac{I_{aux} - I_p(t)}{2C_{sb3}} (t - t_3) dt$$

(3-43)

$$V_{ds4}(t) = \int_{t_1}^{t_2} \frac{I_{aux} - I_p(t)}{2C_{sb4}} (t - t_3) dt$$

(3-44)

Contrary to the switches on  $leg\ A$  as seen from (3-43) and (3-44), the load current relieves  $S_4$ 's turn-off current stress from  $i_{aux}$ , but it also reduces the strength of  $i_{aux}$  in discharging the snubber capacitor of  $S_3$ . In order to prepare the ZVS condition for  $S_3$  to turn-on,  $I_{aux}$  must be greater than the reflected load current. Otherwise ZVS turn-on would be lost in  $C_{sb3}$ .

The duration of this interval is determined dead time, which is given by:

$$t_{\lambda} - t_{\lambda} = t_{\lambda} \tag{3-45}$$

# F. Interval $5(t_1 \le t < t_2)$

At the beginning of this interval  $S_3$  is turned-on under ZVS condition. Thus nearly loss-less turn-on is achieved for  $S_3$ . No switching action takes place during this interval. The equivalent circuit of this interval is shown in Fig. 2.5, interval 4.

As  $S_3$  is on,  $L_{aux}$  sees a constant negative voltage established by  $C_{V2}$ .  $i_{aux}$  starts to decrease linearly, as is governed by

$$i_{aux}(t) = -\frac{V_d}{2L_{aux}}(t - t_4) + I_{aux}$$

(3-46)

As the current becomes positive and diagonal switches  $S_1$  and  $S_3$  are on. The voltage across primary is  $V_d$ . The amount of current passing through primary is governed by

$$I_{P}(t) = \frac{2I_{ppk} - \frac{V_{d}}{L_{Llk}}(t_{2} - t_{1})}{(t_{6} - t_{3})} (t - t_{3}) + \frac{V_{d}}{L_{Llk}}(t_{2} - t_{1}) - I_{ppk}$$

(3-47)

The duration of this interval is determined by the duty loss due to leakage inductance.

$$t_5 - t_4 = \Delta D \cdot T_s \tag{3-48}$$

# F. Interval $6(t_s \le t < t_6)$

At the beginning of this interval no switching action takes place and the primary side starts to build up the positive voltage equals to  $V_d$ . During this interval  $S_{R1}$  is off and  $S_{R2}$  is forward biased. Current is flowing in both filter inductors. The load current is equally shared between  $L_1$  and  $L_2$ . The value of  $L_{aux}$  is still decreasing which is governed by

$$i_{aux}(t) = -\frac{V_d}{2L_{aux}}(t - t_5) + I_{aux}$$

(3-49)

As the current becomes positive and diagonal switches  $S_1$  and  $S_3$  are on. The voltage across primary is  $V_d$ . After this interval the primary current reached the peak value of the primary current ( $I_{ppk}$ ). The amount of current passing through primary is governed by

$$I_{p}(t) = \frac{2I_{ppk} - \frac{V_{d}}{L_{Llk}}(t_{2} - t_{1})}{(t_{6} - t_{3})} (t - t_{3}) + \frac{V_{d}}{L_{Llk}}(t_{2} - t_{1}) - I_{ppk}$$

(3-50)

The duration of this interval is determined by the effective duty ratio required to regulate the output voltage: