#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# A ZERO VOLTAGE SWITCHING BOOST CONVERTER USING A SOFT SWITCHING AUXILIARY CIRCUIT WITH REDUCED CONDUCTION LOSSES

Nikhil Jain

A Thesis

In

The Department

Of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of Master of Applied Science at

Comcordia University

Montreal, Quebec, Canada.

December 2000

© Nikhil Jain, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-59306-1

#### **ABSTRACT**

### A ZERO VOLTAGE SWITCHING BOOST CONVERTER USING A SOFT SWITCHING AUXILIARY CIRCUIT WITH REDUCED CONDUCTION LOSSES.

#### NIKHIL JAIN

Modern AC-DC power supplies utilize power factor correction in order to minimize the harmonics in the input current drawn from the utility. The Boost topology is the most popular topology for power factor correction today but it has some disadvantages like very high EMI due to reverse recovery of the boost diode and high switching losses caused by hard switching of the boost switch.

Many variations of the original boost topology have been suggested to overcome these problems. The Zero Voltage Transition Boost converter is one such solution. In such a converter an auxiliary resonant circuit is employed which is activated only when the boost switch is turning on or off. This auxiliary circuit allows the boost switch to turn on and off under zero voltage conditions thus reducing the switching losses. However the auxiliary circuit might be very complex and conduction losses in it might offset the expected rise in efficiency.

In this thesis a soft-switching boost power converter is proposed and analyzed. This converter reduces the EMI and increases the efficiency because the auxiliary circuit is itself soft-switching and has low conduction losses due to creative placement of the resonant capacitors. Characteristic curves are generated for the proposed converter which not only give valuable insight on the behavior of the converter but also aid in designing the converter. The feasibility of the proposed converter is examined by means of results obtained from an experimental prototype.

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere gratitude to both my supervisors – Dr. Geza Joos and Dr. Praveen Jain, both of whom helped me tremendously during the course of this thesis. Their ideas and suggestions were a source of guidance to me and without their timely help this research project would have taken a far longer time to finish. Their support and encouragement are highly appreciated.

I would also like to especially thank Mr. Joe Woods of Power Electronics Laboratory, Concordia University and Mr. Haibo Zhang of Cistel Technology, Ottawa for their invaluable help during the construction and testing phase of the designed prototype. I want to thank all my friends and colleagues at the P.D. Ziogas Power Electronics Laboratory for their many useful discussions and suggestions.

Financial aid given in form of a tuition fee waiver and an FCAR grant is highly appreciated. Financial support provided by an NSERC strategic grant to conduct the research activity is also acknowledged.

Dedicated to my parents

#### **TABLE OF CONTENTS**

| List of figuresx                             |

|----------------------------------------------|

| List of Acronymsxiv                          |

| List of Main Symbolsxv                       |

|                                              |

| CHAPTER 1 1                                  |

| 1.1 General Introduction                     |

| 1.2 PWM BOOST CONVERTER FOR PFC APPLICATIONS |

| 1.3 Losses In Hard Switching                 |

| 1.3.1 RESONANT SOFT SWITCHING SCHEMES        |

| 1.3.2 ZERO VOLTAGE TRANSITION CONVERTERS     |

| 1.4 Thesis Objectives                        |

| 1.5 Thesis Outline                           |

|                                              |

| CHAPTER 214                                  |

| 2.1 Introduction                             |

| 2.2 FUNCTIONAL DESCRIPTION 15                |

| 2.3 Converter Features 18                    |

| 2.4 Steady State Analysis                    |

| 2.4.1 SIMPLIEVING ASSLIMPTIONS 19            |

| 2.4.2 DESCRIPTION AND ANALYSIS OF THE CONVERTER SWITCHING      |

|----------------------------------------------------------------|

| Intervals in Mode 1                                            |

| 2.4.3 DESCRIPTION AND ANALYSIS OF THE CONVERTER SWITCHING      |

| Intervals in Mode 2                                            |

| 2.5 ANALYTICAL AND SIMULATED WAVEFORMS OF THE PROPOSED         |

| CONVERTER35                                                    |

| 2.6 CONCLUSIONS                                                |

|                                                                |

| CHAPTER 3 42                                                   |

| 3.1 Introduction                                               |

| 3.2 DESCRIPTION OF PROGRAM                                     |

| 3.3 CHARACTERISTIC CURVES OF THE CONVERTER 44                  |

| 3.3.1 DEFINITION OF VARIABLES USED IN CHARACTERISTIC CURVES 44 |

| 3.3.2 SOFT-SWITCHING OF THE MAIN SWITCH IN MODE 147            |

| 3.3.3 Auxiliary Circuit Characteristic Curves when converter   |

| OPERATES IN MODE 1                                             |

| 3.3.3.1 PEAK VOLTAGE AND CURRENT GRAPH FOR THE CONVERTER       |

| SWITCHES IN MODE 1                                             |

| 3.3.3.2 GRAPHS OF RMS CURRENT FOR AUXILIALRY SWITCH AND        |

| AVERAGE CURRENT FOR AUXILIARY CIRCUIT DIODES IN MODE 161       |

| 3.3.3.3 BOUNDARY BETWEEN MODE 1 AND MODE 2 OPERATION OF THE    |

| CONNEDTED 65                                                   |

| 3.3.4 AUXILIARY CIRCUIT CHARACTERISTIC CURVES WHEN CONVER | TER  |

|-----------------------------------------------------------|------|

| OPERATES IN MODE 2                                        | . 67 |

| 3.3.4.1 PEAK VOLTAGE AND PEAK CURRENT GRAPH FOR           | THE  |

| CONVERTER SWITCHES IN MODE 2                              | 68   |

| 3.3.4.2 Graphs for RMS Current for Auxiliary Switch A     | AND  |

| AVERAGE CURRENT FOR AUXILIARY CIRCUIT DIODES IN MODE 2    | .72  |

| 3.3.5 SOFT SWITCHING OF THE MAIN SWITCH IN MODE 2         | . 74 |

| 3.4 Conclusions                                           | . 75 |

|                                                           |      |

| CHAPTER 4                                                 | .76  |

| 4.1 Introduction                                          | . 76 |

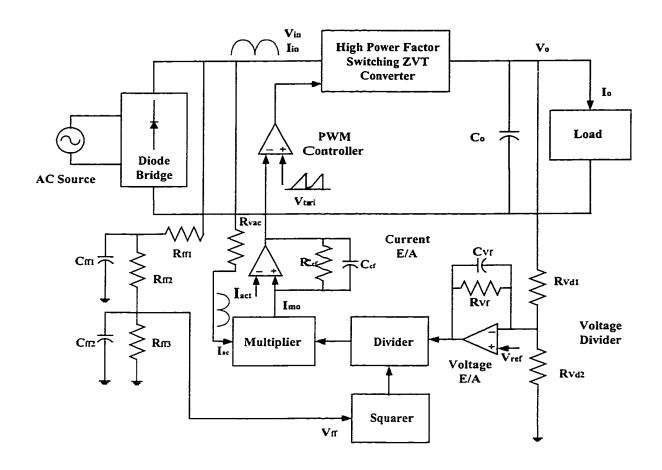

| 4.2 ACTIVE POWER FACTOR CORRECTION CONTROL CIRCUIT        | . 77 |

| 4.3 CONTROL LOOP DESIGN                                   | . 80 |

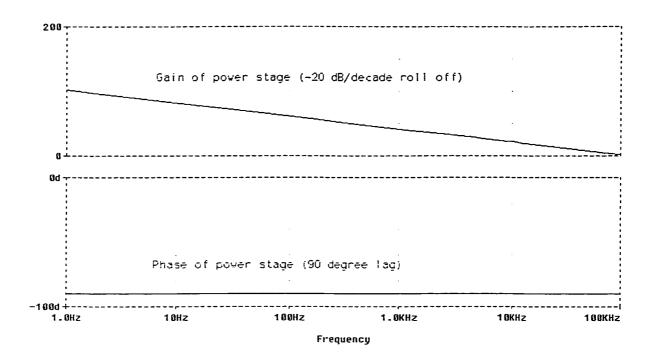

| 4.3.1 SMALL SIGNAL MODEL OF THE CONVERTER                 | . 80 |

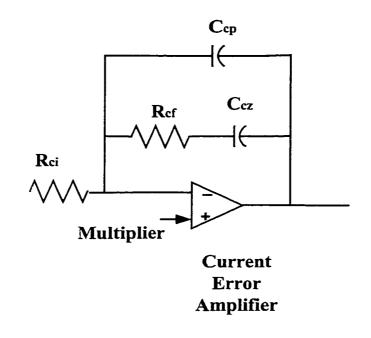

| 4.3.2 COMPENSATION OF THE CURRENT LOOP                    | . 81 |

| 4.3.3 COMPENSATION OF THE VOLTAGE LOOP                    | . 86 |

| 4.4 CONCLUSIONS                                           | . 91 |

|                                                           |      |

| CHAPTER 5                                                 | 92   |

| 5 1 Introduction                                          | . 92 |

| 5 2 DESIGN OF THE PROPOSED ZVT CONVERTER                  | . 93 |

| 5.2.1 Design Objectives and Specifications                | 93   |

|     | 5.2.2 DESIGN PROCEDURE AND EXAMPLE                             | . 94 |

|-----|----------------------------------------------------------------|------|

|     | 5.2.2.1 DESIGN OF THE POWER CIRCUIT                            | .94  |

|     | 5.2.2.2 DESIGN OF THE AUXILIARY CIRCUIT AND MAIN SWITCH        | 98   |

|     | 5 3 SIMULATED AND EXPERIMENTAL RESULTS OF THE PROPOSED CONVERT | ER   |

|     |                                                                | 104  |

|     | 5.4 Conclusions                                                | 114  |

|     |                                                                |      |

| CH. | APTER 6                                                        | 115  |

|     | 6.1 Summary                                                    | 115  |

|     | 6.2 Conclusions                                                | 116  |

|     | 6.3 Suggestions for future work                                | 117  |

|     |                                                                |      |

| REI | FERENCES                                                       | 18   |

#### **LIST OF FIGURES**

| Fig  | . 1.1 Conventional Two stage Rectifier                                                | 2   |

|------|---------------------------------------------------------------------------------------|-----|

| Fig  | 1.2 (a) Diode Bridge Rectifier (b) Input current Waveform of Diode Bridge             | 2   |

| Fig  | . 1.3 Common Power Factor Correction Topologies (a) Boost topology (b) Buck           |     |

|      | topology (c) Block Diagram of Single Stage topology.                                  | 3   |

| Fig. | . 1.4 Input current waveforms for different topologies (a) for Boost topology (b) for |     |

|      | Buck topology (c) Unfiltered input current for Single Stage topology operating in     |     |

|      | Discontinuous Mode.                                                                   | . 4 |

| Fig. | . 1.1.1 Generic Switching Waveforms a) Control Signal b) Switch Current and           |     |

|      | Voltage, c) Instantaneous Switch power loss                                           | . 7 |

| Fig. | 1.1 (a) ZCS turn-off using negative voltage (b) ZVS turn-on using negative curren     | t.  |

|      |                                                                                       | . 9 |

| Fig. | 2.1 The proposed ZVT PW M boost converter.                                            | 16  |

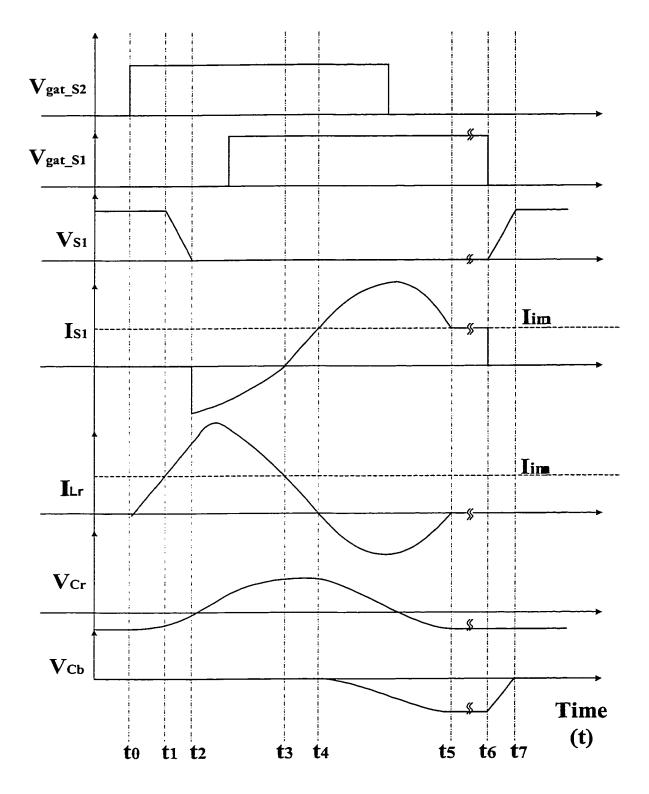

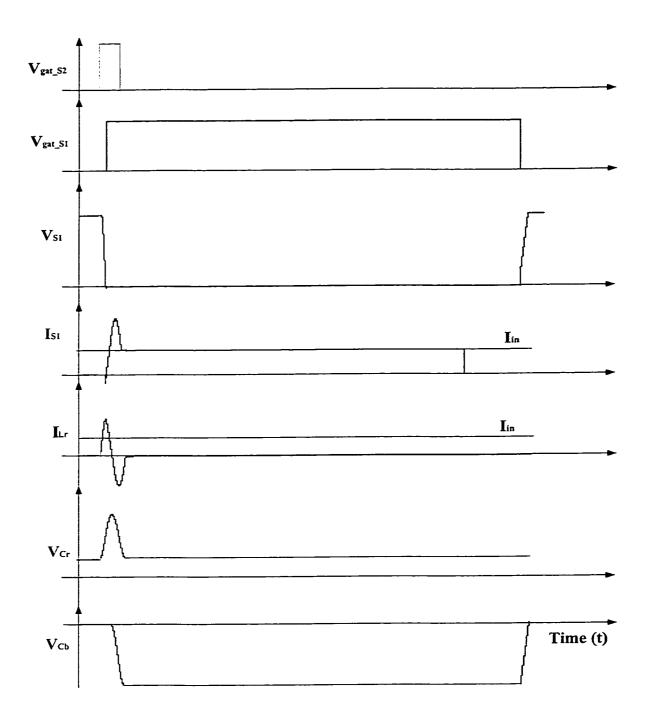

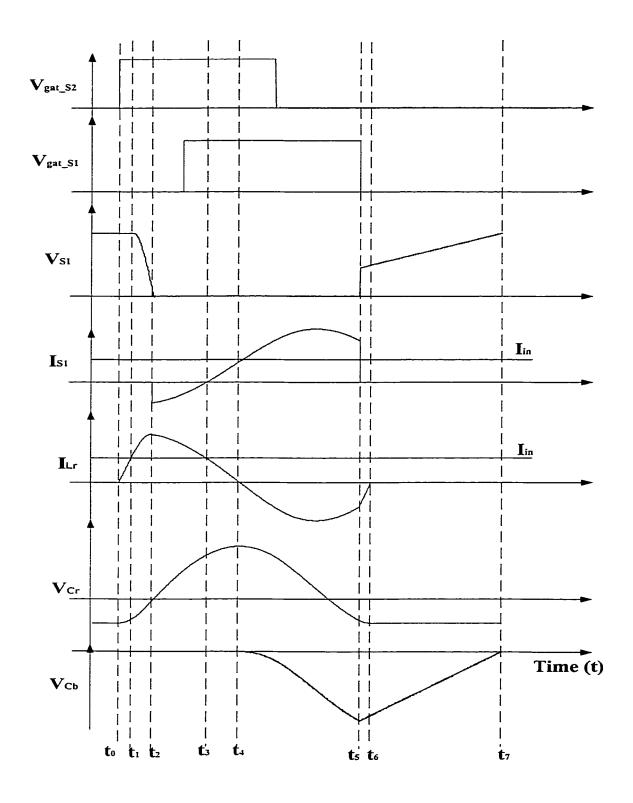

| Fig. | 2.1 Ideal Auxiliary circuit switching waveforms under Mode 1                          | 23  |

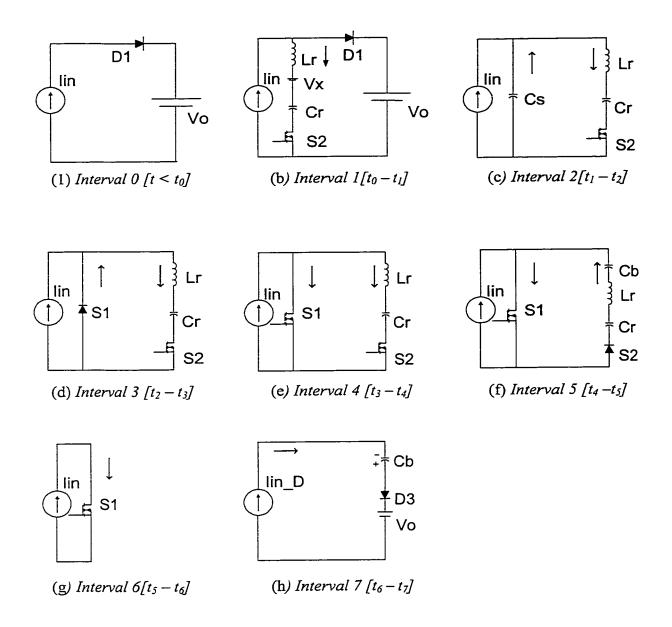

| Fig. | 2.2 Operating intervals for a single switching cycle of the proposed ZVT converter    |     |

|      | under Mode 1                                                                          | 24  |

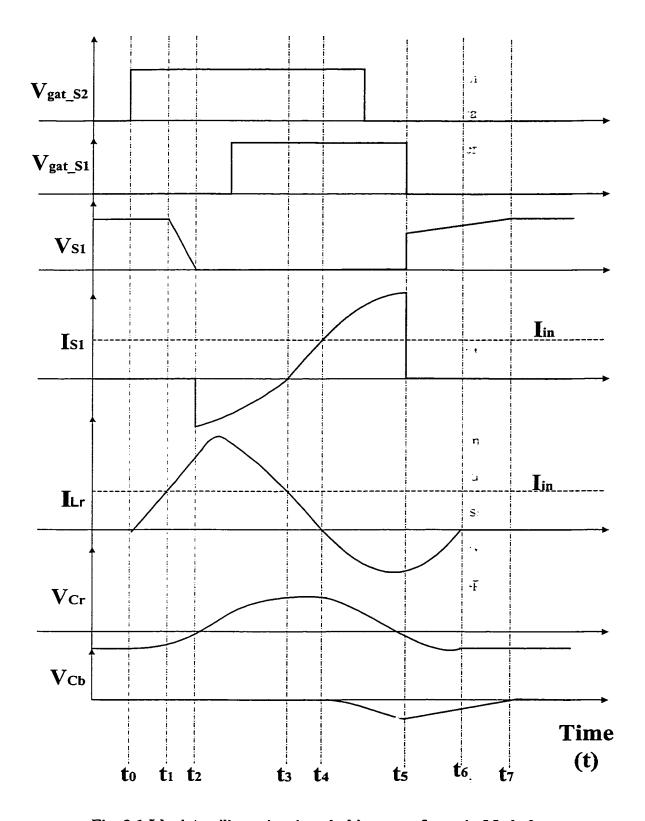

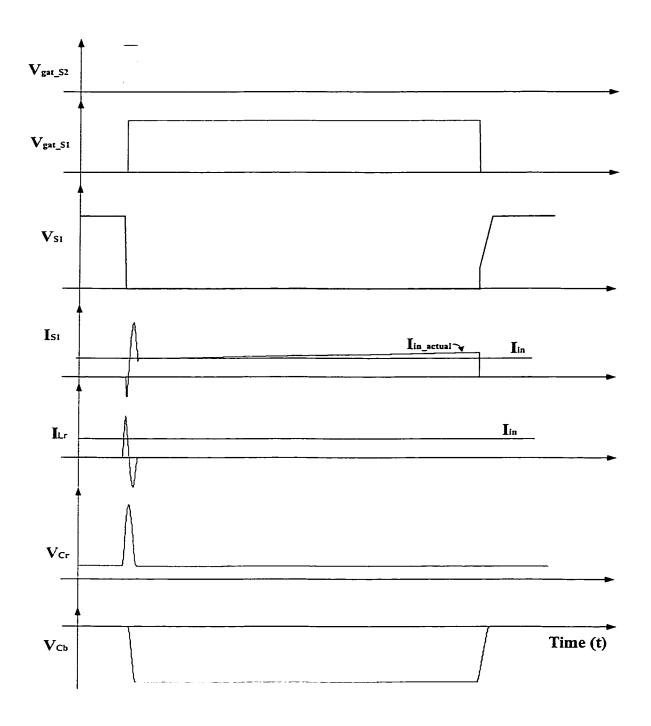

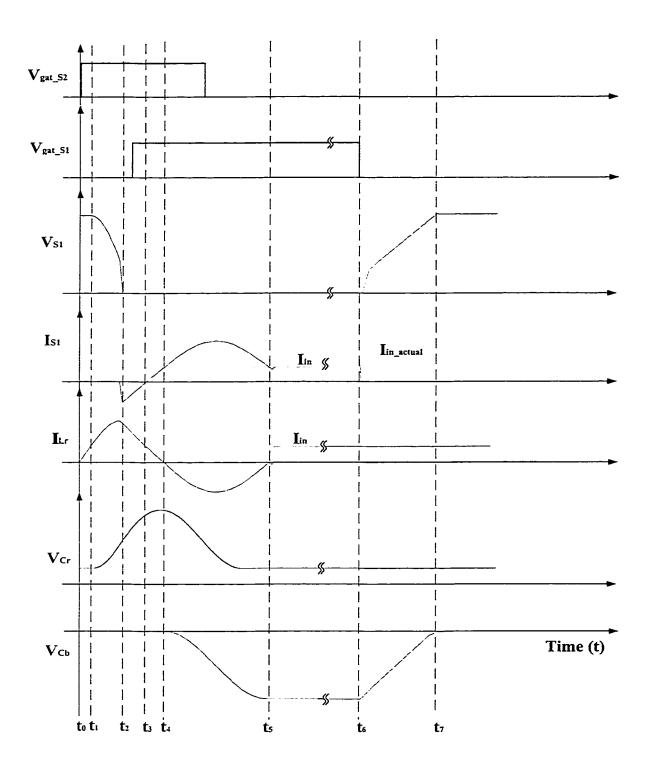

| Fig. | 2.1 Ideal Auxiliary circuit switching waveforms in Mode 2                             | 32  |

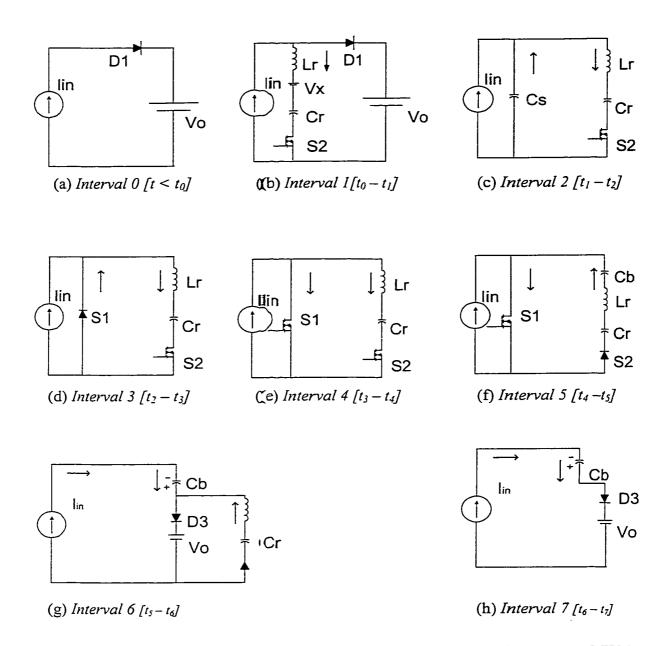

| Fig. | 2.2 Operating intervals for a single switching cycle of the proposed ZVT converter    |     |

|      | under Mode 2.                                                                         | 33  |

| Fig. | 2.1 Analytical waveforms of the Auxiliary circuit in Mode 1                           | 36  |

| Fig. | 2.2 Simulated waveforms of the auxiliary circuit in Mode 1.                           | 37  |

| Fig. | 2.3 Exploded Simulation waveforms of the auxiliary circuit in Mode 1 emphasizing                      |

|------|-------------------------------------------------------------------------------------------------------|

|      | the turn-on and turn-off periods of main switch.                                                      |

| Fig. | 2.4 Analytical waveforms of the Auxiliary circuit in Mode 2                                           |

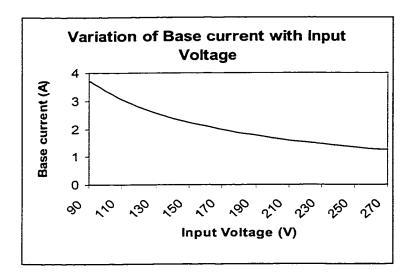

| Fig. | 3.1 Variation of Base Current as a function of Input Voltage for Output Power 250                     |

|      | Watt4                                                                                                 |

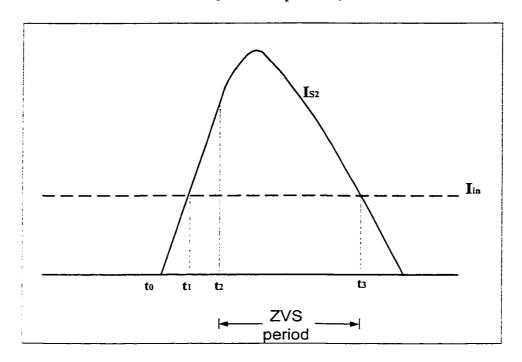

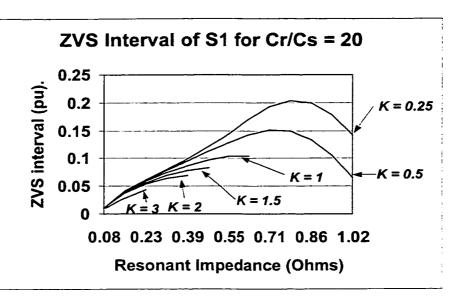

| Fig. | 3.1 ZVS Interval for Soft turn-on of S <sub>1</sub>                                                   |

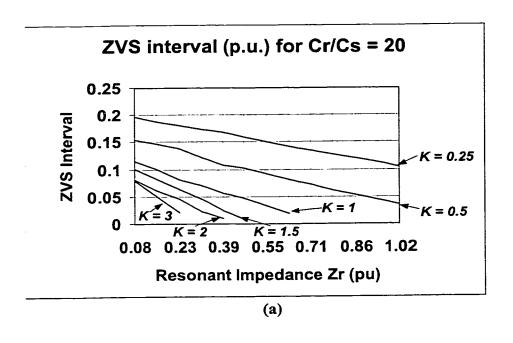

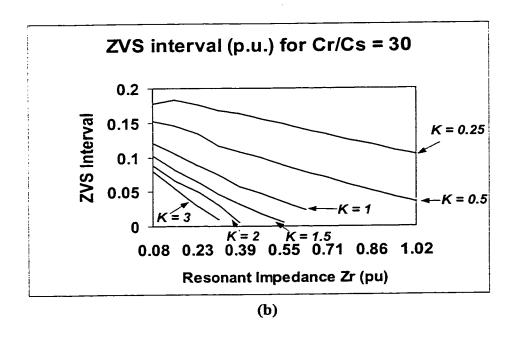

| Fig. | 3.2 ZVS Interval for $R_r = 1~\Omega$ and (a) $C_r/C_s = 20$ and (b) $C_r/C_s = 30$                   |

| Fig. | 3.3 Polarity of Voltage across resonant capacitor $C_r$ for (a) $K < 1$                               |

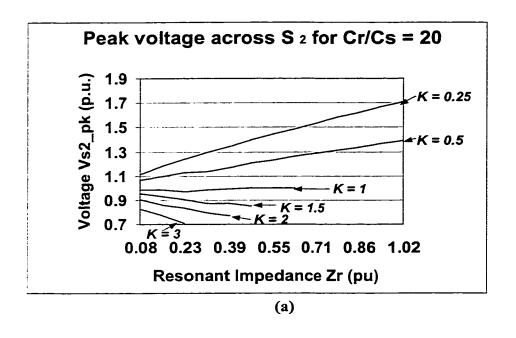

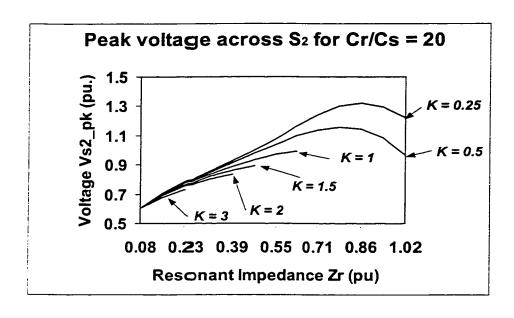

| Fig. | 3.1 Peak Voltage Across auxiliary switch $S_2$ vs. resonant impedance $Z_r$ for $R_r$ = 1 $\Omega$    |

|      | and (a) $C_r/C_s = 20$ and (b) $C_r/C_s = 30$                                                         |

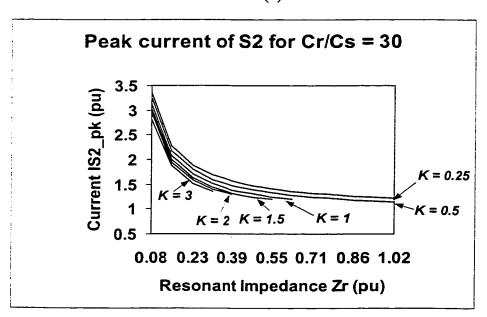

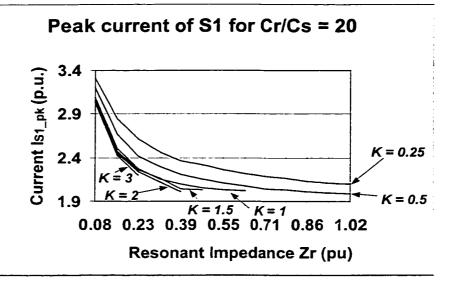

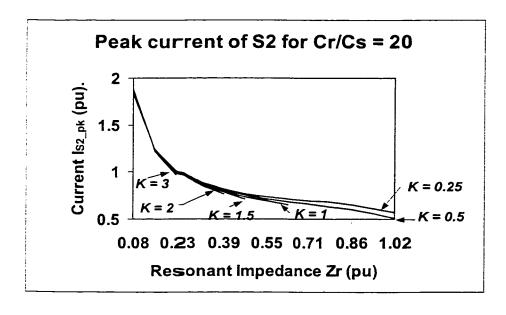

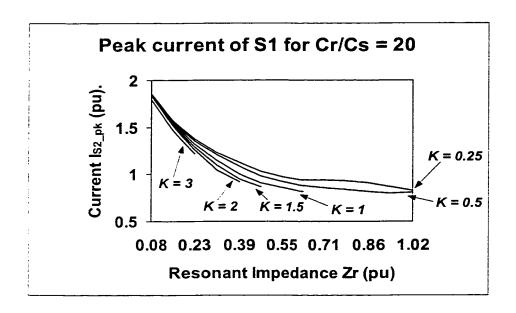

| Fig. | 3.2 Graph of Peak Current Of Auxiliary Switch for $R_r = 1 \Omega$ and                                |

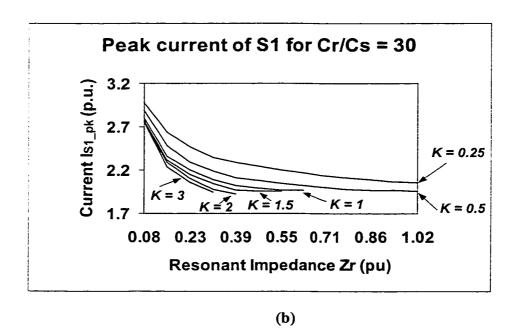

| Fig. | 3.3 Graph of Peak current of Main Switch for $R_r = 1 \Omega$ and                                     |

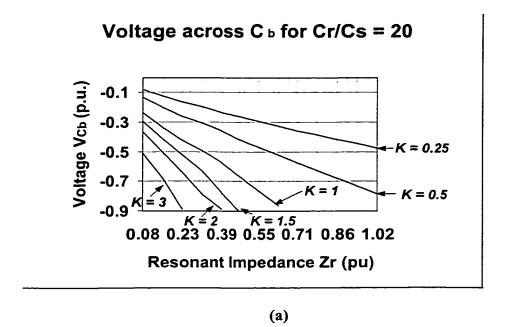

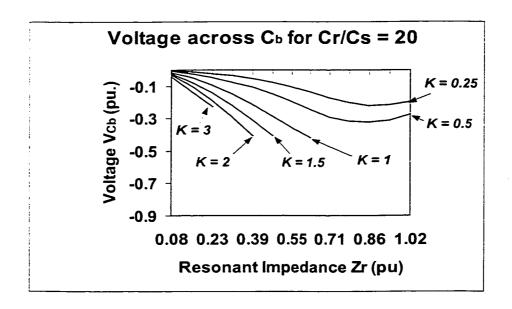

| Fig. | 3.4 Graph Showing Voltage $V_{Cb}$ across Capacitor $C_b$ for $R_r=1~\Omega$ and (a) $C_r/C_s=20$     |

|      | (b) $C_r/C_s = 30$                                                                                    |

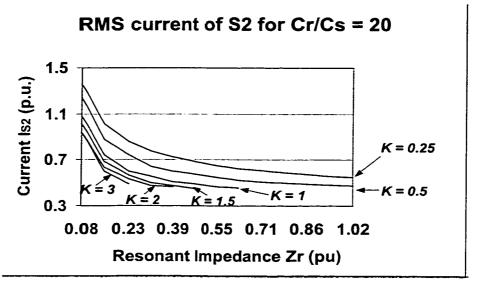

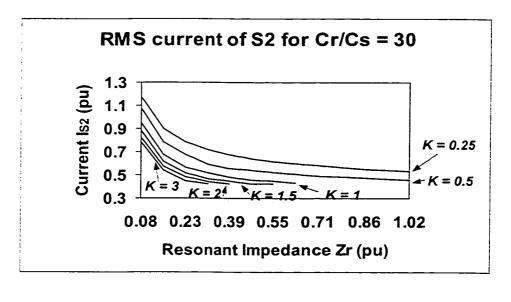

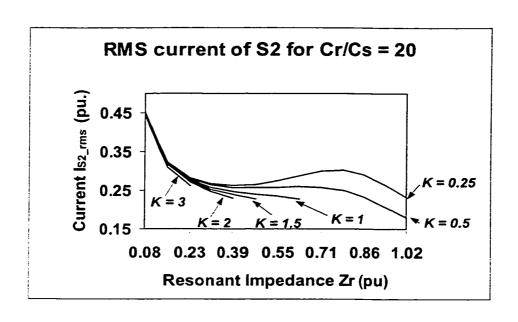

| Fig. | 3.1 Graph of RMS current of Auxiliary Switch $I_{S2\_rms}$ for $R_r = 1 \Omega$ and (a) for $C_r/C_s$ |

|      | = 20 and (b) for $C_r/C_s = 30$                                                                       |

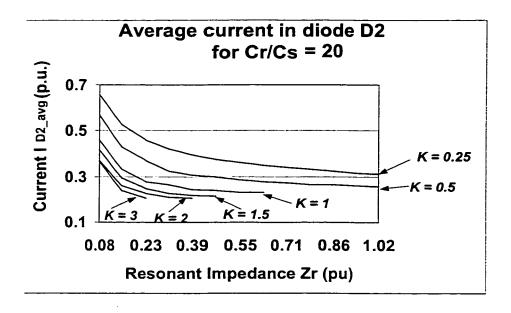

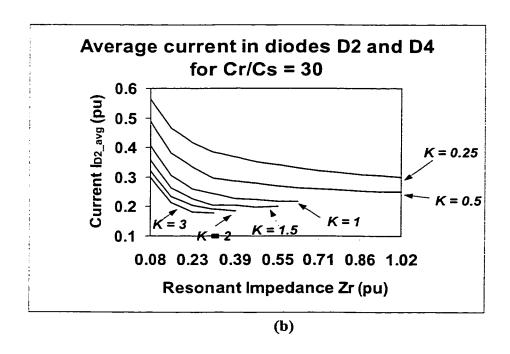

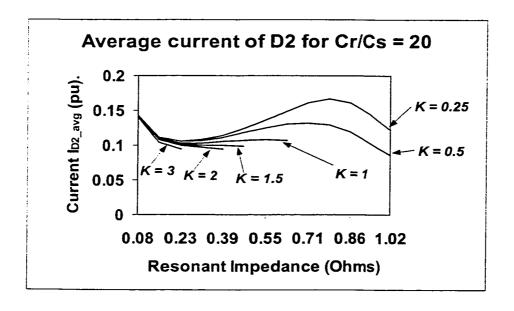

| Fig. | 3.2 Graph Of Average Current $I_{D2\_avg}$ of diode $D_2$ for $R_r = 1 \Omega$ and                    |

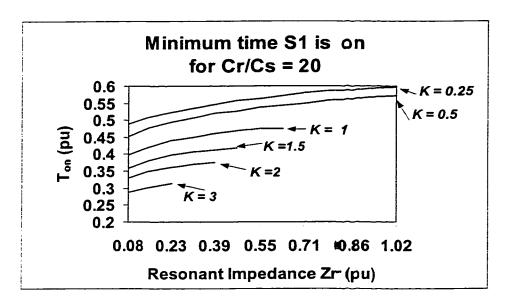

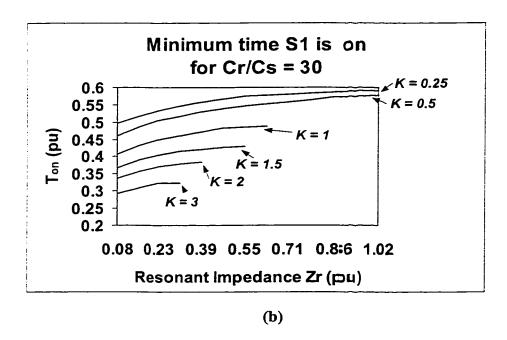

| Fig. | 3.1 Graph showing the Minimum Time that Switch S <sub>1</sub> has to remain on for the                |

|      | converter to operate under Mode 1, for (a) $C_r/C_s = 20$ and (b) $C_r/C_s = 30$                      |

| Fig. | 3.1 Graph of peak voltage across Switch S1 for $R_r = 1 \Omega$ when the converter operates           |

|      | in Mode 2                                                                                             |

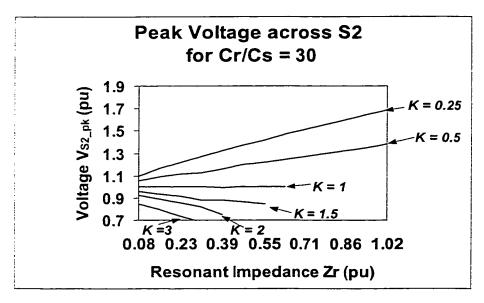

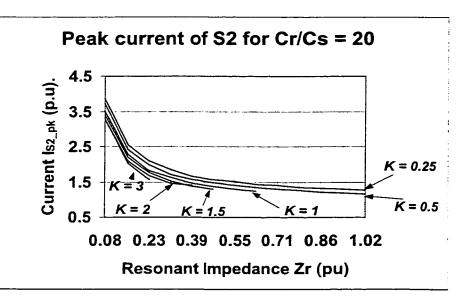

| Fig. | 3.2 Graph of peak current through switch S2 for $R_r = 1 \Omega$ when converter operates in           |

|      | Mode 2                                                                                                |

| Fig. 3.3 Graph of peak current through main switch S1 for $R_r = 1 \Omega$ when the converter                |

|--------------------------------------------------------------------------------------------------------------|

| operates in Mode 270                                                                                         |

| Fig. 3.4 Graph showing the Voltage $V_{Cb}$ across Capacitor $C_b$ for $R_r = 1 \Omega$ when $S_1$ turns     |

| Off in Mode 271                                                                                              |

| Fig. 3.1 Graph of rms current of Auxiliary Switch $S_2$ for $R_r = 1$ $\Omega$ when the converter is         |

| operating in Mode 2                                                                                          |

| Fig. 3.2 Graph of Average current in Series diode D2 for $R_r = 1 \Omega$ when the converter is              |

| operating in Mode 2                                                                                          |

| Fig. 3.1 Graph of the ZVS interval for $R_r = 1 \Omega$ when the converter operates in Mode 2.75             |

| Fig. 4.1 Design of Control loop for Power Factor Correction Applications                                     |

| Fig. 4.1 Gain characteristic and Phase characteristic of power stage                                         |

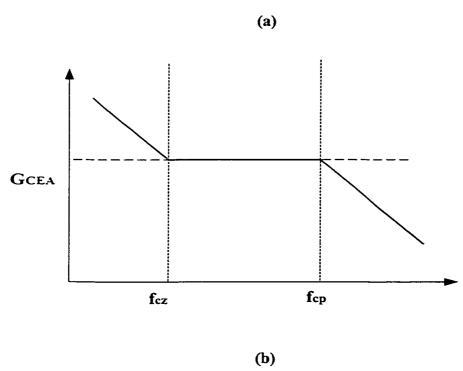

| Fig. 4.1 (a)Type 2 Current Error Amplifier (b) Ideal Gain characteristic of the Error                        |

| Amplifier                                                                                                    |

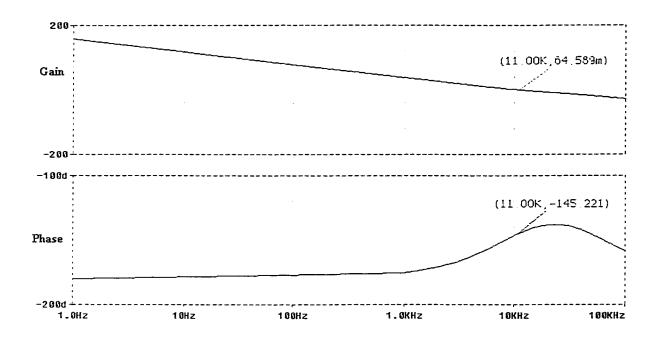

| Fig. 4.2 Gain and Phase characteristic of the Open Loop Current Regulator with Power                         |

| Stage                                                                                                        |

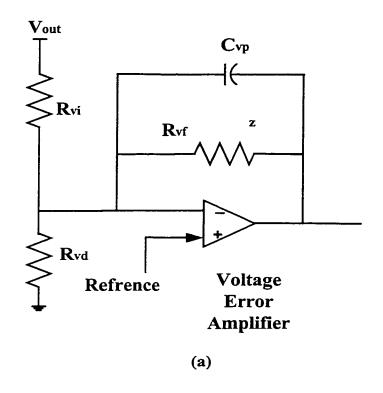

| Fig. 4.1 (a) Type-1 Voltage Error Amplifier (b) Ideal Characteristic Curve of given                          |

| Amplifier                                                                                                    |

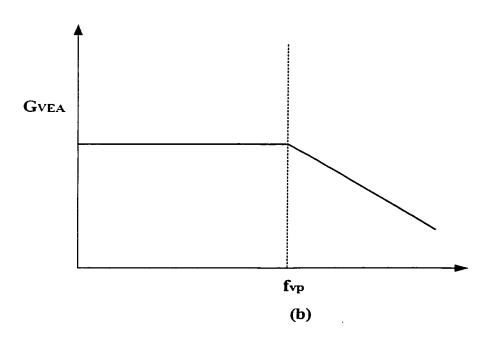

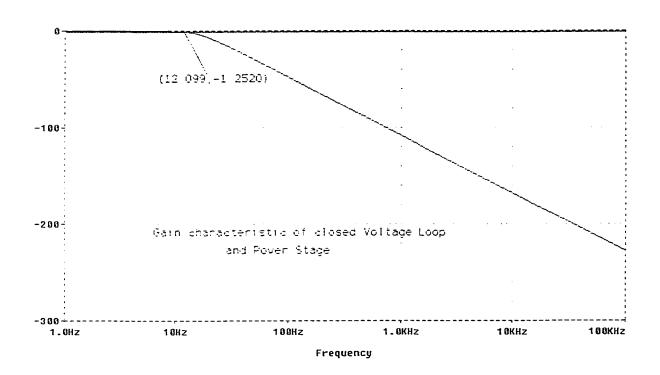

| Fig. 4.2 Gain Characteristic of Closed Voltage Loop and Power Stage                                          |

| Fig.5.1 Experimental Setup for obtaining the Switching Waveforms of the proposed                             |

| Converter                                                                                                    |

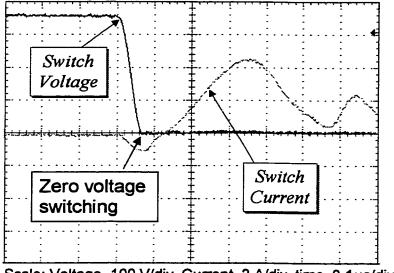

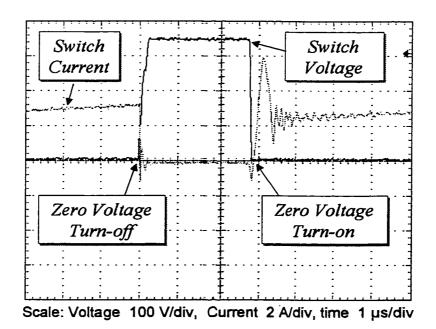

| Fig. 5.2 Switching waveforms of the main switch $S_1$ at turn-on for $V_{in}=128V$ ,                         |

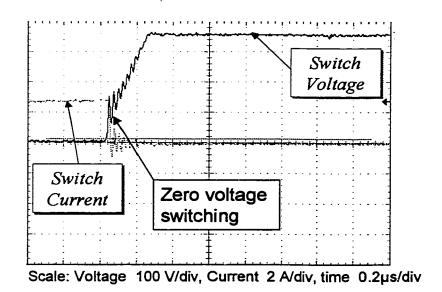

| Fig. 5.3 Switching waveforms of main switch S <sub>1</sub> at turn-off for V <sub>in</sub> =128V <sub></sub> |

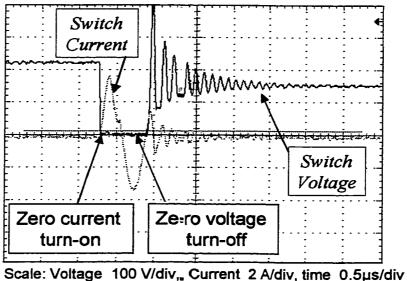

| Fig. 5.4 Auxiliary switch $S_2$ voltage and current waveforms at turn-on and turn-off for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| V <sub>in</sub> =128V, Vo =350 V, Po = 250 W, Fsw = 100kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109 |

| Fig. 5.5 Switching waveforms of main switch $S_1$ on a larger time scale for $V_{in}$ =128V, $V_$ | Vo  |

| =350 V, Po = 250 W, Fsw = 100kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

| Fig. 5.6 Switching waveforms of the main switch $S_1$ at turn-on for Output Power Po =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | :   |

| 200 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 110 |

| Fig. 5.7 Switching waveforms of the main switch $S_1$ at turn-off for Power Output Po =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 200 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 110 |

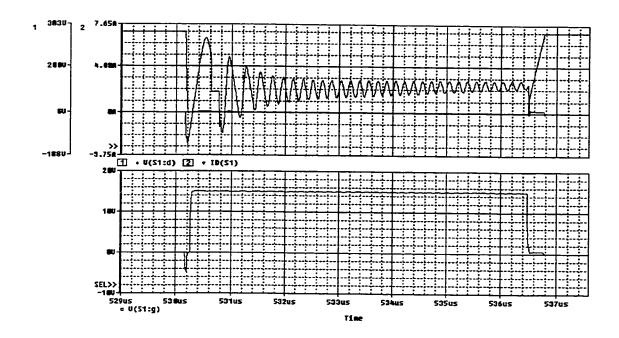

| Fig. 5.8 Simulated waveforms of the main switch $S_1$ showing switch current $I_{S1}$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| voltage $V_{S1}$ (upper waveform) and gating $V_{S1\_gat}$ for $V_{in}$ =128V, $V_{O}$ =350 V, $P_{O}$ =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 250 W, Fsw = 100kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111 |

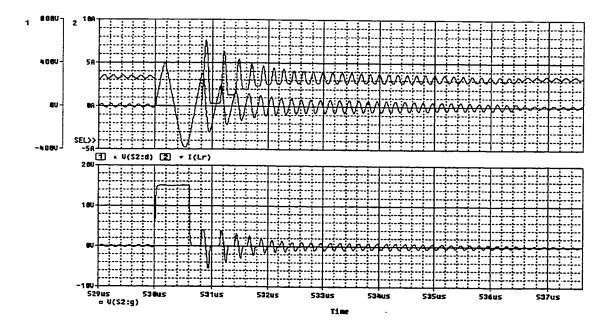

| Fig. 5.9 Simulated waveforms of the auxiliary switch S2 showing switch current $I_{S2}$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ıd  |

| voltage $V_{S2}$ (upper waveform) and gating $V_{S2\_gat}$ for $V_{in}$ =128V, $V_0$ =350 V, $P_0$ =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 250 W, Fsw = 100kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

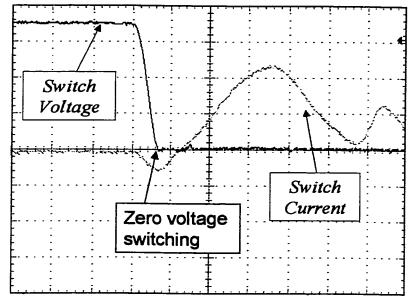

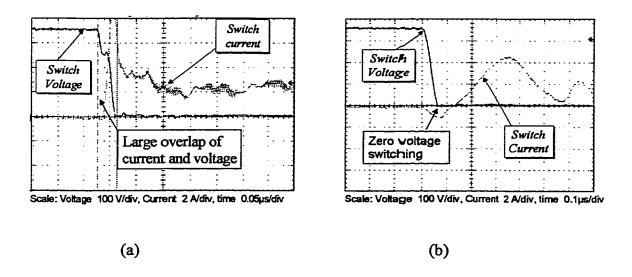

| Fig. 5.10 Turn-on of the main switch under (a) Hard switching (b) Soft switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112 |

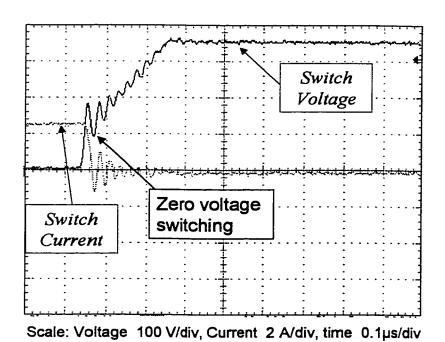

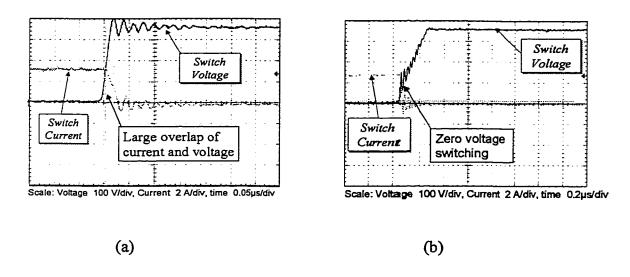

| Fig. 5.11 Turn-off of the main switch under (a) Hard switching (b) Soft switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 112 |

#### LIST OF ACRONYMS

EMI electro-magnetic interference

MOSFET metal—oxide semiconductor field—effect transistor.

PFC power factor correction

PWM pulse-width modulation

QRC quasi-resonant converter

rms root mean square

THD Total Harmonic Distortion

ZCS zero current switching

ZVS zero voltage switching

ZVT zero voltage transition

#### LIST OF MAIN SYMBOLS

Ccapacitor, capacitance  $C_o$ output capacitor  $C_b$ reverse charging capacitor of the auxiliary circuit  $C_p$ equivalent capacitance when boost switch capacitance is discharging  $C_r$ auxiliary circuit resonant capacitor  $C_{s}$ parasitic capacitance of main boost switch  $C_{nb}$ equivalent capacitance when auxiliary circuit current reverses  $D(\omega t)$ duty cycle as a time varying function  $D_{min}$ minimum duty cycle  $D_{min\ I}$ minimum duty cycle under Mode 1  $D_{pk}$ duty cycle when input current is maximum  $D_I$ boost diode  $D_2$ auxiliary circuit series blocking diode  $D_3$ auxiliary capacitor discharge diode  $D_{4}$ auxiliary circuit series blocking diode  $D_5$ auxiliary circuit anti-parallel diode  $F_{sw}$ switching frequency of converter ripple frequency which is 2<sup>nd</sup> harmonic of input line frequency  $f_r$  $I_b$ base current amplitude of 2<sup>nd</sup> harmonic current fed into the output capacitor  $I_{chg\_pk}$  $I_{Di\_avg}$ average current flowing through diode i

| $I_{Din\_avg}$         | average current flowing through an input diode                       |

|------------------------|----------------------------------------------------------------------|

| $I_{in}$               | Input current                                                        |

| $I_{in\_D}$            | Input current through boost inductor when duty cycle is $D$          |

| $I_{in\_Dmin}$         | Input current through boost inductor at minimum duty cycle $D_{min}$ |

| $I_{in\_pk}$           | peak input current                                                   |

| $I_{Lr}$               | current through auxiliary circuit resonant inductor                  |

| I <sub>rpk_max</sub>   | maximum input current with ripple in converter                       |

| $I_{Si\_pk}$           | peak current through switch S <sub>i</sub>                           |

| I <sub>Si_rms</sub>    | rms current of switch S <sub>i</sub>                                 |

| K                      | ratio of capacitor C <sub>r</sub> to C <sub>b</sub>                  |

| $L_{in}$               | input inductor                                                       |

| $L_r$                  | auxiliary circuit resonant inductor                                  |

| $P_o$                  | output power                                                         |

| $R_r$                  | on-state resistance of auxiliary switch                              |

| $S_I$                  | main boost switch                                                    |

| $S_2$                  | auxiliary switch                                                     |

| $t_0$                  | instant at which the auxiliary switch is turned om                   |

| $t_0$                  | instant at which the main switch is turned on with ZVS               |

| $t_2$                  | earliest instant at which the main switch can be turned on with ZVS  |

| <i>t</i> <sub>3</sub>  | latest instant at which the main switch can be turned on with ZVS    |

| $t_i$                  | the i <sup>th</sup> time instant                                     |

| t <sub>rr</sub>        | boost diode reverse recovery time                                    |

| $T_r$                  | length of the natural resonant cycle of the auxiliary circuit        |

| $V_b$                  | base voltage                                                         |

| $V_{\mathit{chg\_pk}}$ | output voltage peak ripple                                           |

$V_{Cb}$  voltage across reverse charging capacitor

$V_{Cr}$  voltage across the resonant capacitor

$V_{Cs}$  voltage across the capacitor  $C_s$

$V_{gat\_Si}$  gating signal of the i<sup>th</sup> switch

$V_{in}$  input rms. voltage

$V_{in\_max}$  maximum rms input voltage

$V_{in\_min}$  minimum input rms voltage

$V_{in\_pk}$  peak input voltage

Vo output voiltage

$V_{S2\_pk}$  peak voltæge across auxiliary switch

Z<sub>r</sub> auxiliary circuit resistance

$Z_{rb}$  base impedance

$\Delta I_{rpp}$  peak-to-peak input current ripple

η efficiency

ξ damping ∞onstant

$\omega$  angular frequency in radians

$\omega_o$  natural frequency of auxiliary circuit in radians

$\omega_{opb}$  natural frequency of auxiliary circuit when current is reversing

$\omega_r$  resonant Frequency

$\omega_{rpb}$  resonant frequency of auxiliary circuit when current is reversing

ψ phase angule during first operating interval of the switching cycle

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 GENERAL INTRODUCTION

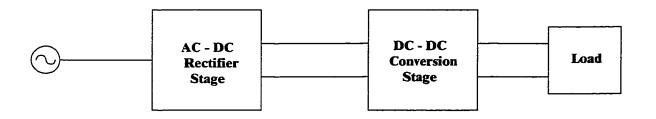

In modern power applications a reliable ac-dc power converter is required. For power applications above 250 W, a two stage process is usually used to provide an isolated and regulated dc output voltage. The first stage of such a converter is a rectifying stage that converts the ac voltage to dc and the second stage is an isolated dc-dc converter that converts the dc input voltage into a regulated dc voltage at the output as shown in Fig. 1.1. One of the most important functions of the rectifying stage is to provide Power Factor Correction (PFC) of the input current in order to minimise the harmonics in it.

Historically diode bridge rectifiers with a large capacitor at the dc bus have been used to convert the ac voltage to a dc voltage. But diode bridge rectifiers draw a very high peak current from the ac utility as shown in Fig. 1.2(b) which is rich in harmonics and thus gives a very poor power factor of about 0.6. International standards such IEC 61000 and IEEE 519–92 lay down the maximum amount of harmonics that can be tolerated in the system and diode bridge rectifiers cannot match these criteria.

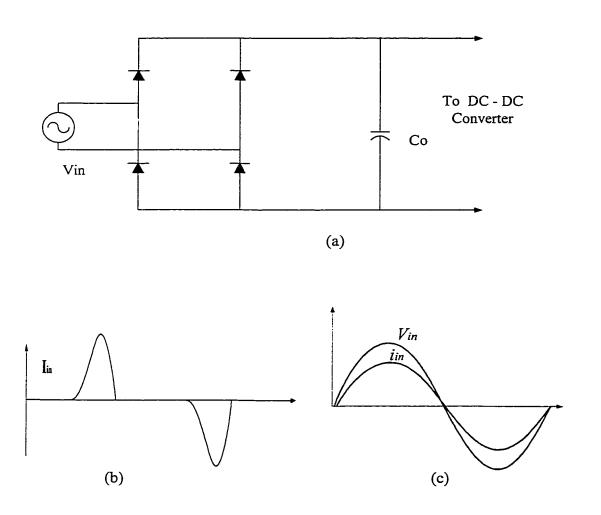

Many topologies such as Buck, Boost, Single Stage converters etc. can be used for PFC applications to overcome these problems. These topologies are shown in Fig. 1.3 and their input currents are shown in Fig. 1.4. The filtered input current in most of these topologies resembles Fig. 1.2 (c) closely giving a power factor close to unity.

Fig. 1.1 Conventional Two stage Rectifier

Fig. 1.2 (a) Diode Bridge Rectifier (b) Input current Waveform of Diode Bridge

(c) Desired input current.

Fig. 1.3 Common Power Factor Correction Topologies (a) Boost topology (b) Buck topology (c) Block Diagram of Single Stage topology.

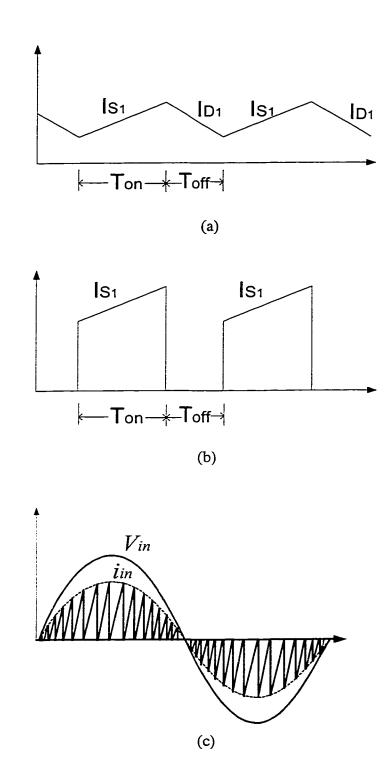

Fig. 1.4 Input current waveforms for different topologies (a) for Boost topology (b) for Buck topology (c) Unfiltered input current for Single Stage topology operating in Discontinuous Mode.

The most popular among these topologies is the Pulse-Width-Modulated (PWM) boost converter which is used in almost 85% of PFC applications today [1] - [5].

The reasons why boost topology is preferred as a PFC pre-regulator are:

- 1) The input current in the boost topology has the smallest current ripple as can be seen from Fig. 1.4(a). Thus the filtering requirements for this topology are the lowest resulting in a small filter.

- 2) Buck pre-regulators require a larger filter at the input since the input current is "chopped up." They also provide an output voltage that is always lower than the minimum input voltage and this causes problems at zero crossings of the input ac voltage. Although with some modifications buck pre-regulators can give an almost-unity power factor the solutions require a large output inductance for continuous conduction [6] [7]. This increases the size of the converter as well as cost. For same power level the boost topology gives same Total Harmonic Distortion (THD) with a much smaller inductance.

- 3) Single-stage converters improve efficiency over two-stage converters by processing power only once to give a regulated dc output voltage which also reduces the cost of the overall control circuit. However they require a larger high voltage dc bus capacitor than the two stage approach which increases cost of converter as the power level increases [8]. Also it is preferable to operate these converters in discontinuous conduction mode to keep the control simple but this increases both the input rms currents resulting in higher conduction losses as well as higher Electro Magnetic Interference (EMI). A large EMI filter has to be provided at input [9] to filter the input current shown in Fig. 1.4(c). Some of the converters rely on variable frequency

control making design of filter complex [10] so the power level of single-stage converters is limited to a maximum power of 150-250 W.

#### 1.2 PWM BOOST CONVERTER FOR PFC APPLICATIONS

The switch mode boost converter can perform power factor correction by shaping the input current to be sinusoidal and forcing it to follow the input voltage waveform. This achieves a power factor close to unity and the harmonics are also reduced. However boost converters suffer from their own set of disadvantages:

- 1) The output of a boost converter is always greater than the peak input voltage. So if a converter is designed for Universal Input Line Applications (90–265 Volt) the output dc bus voltage must be greater than the peak of the 265 Volt ac wave. Thus the output voltage of the boost must be kept at least 400 V and turning on the main switch of the converter at such a high voltage causes a lot of turn—on losses in the switch.

- 2) The boost switch has hard turn-on as well as hard turn-off and the boost diode has a hard turn-off and as can be seen from Fig. 1.4(a). This causes additional losses. During the reverse recovery of the boost diode the output capacitor is shorted to ground and this causes a very large and negative current spike to appear in the converter switching waveforms. This current spike causes a large amount of EMI in the circuit and can cause problems in telecommunication systems.

Thus a converter which can minimise these switching losses and reduce the EMI is required. The losses can be substantially reduced by using soft switching techniques

#### 1.3 Losses in Hard Switching

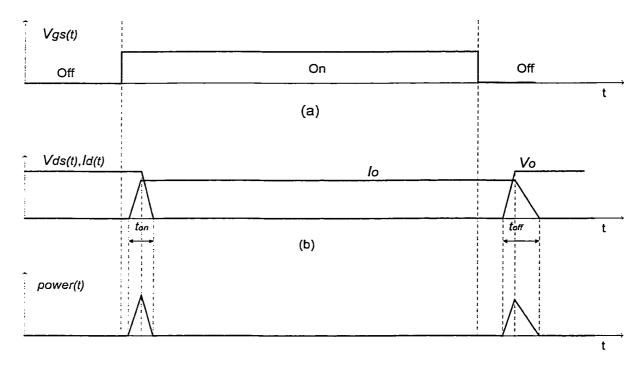

The reason why there are switching losses in any switch mode power converter is that when the switching element turns on or off, high voltage and current are present simultaneously in the switch. This leads to very high instantaneous power loss in the switch resulting in a low efficiency of the converter as shown in the following Fig.

Fig. 1.1.1 Generic Switching Waveforms a) Control Signal b) Switch Current and Voltage, c) Instantaneous Switch power loss.

As there are  $f_s$  such turn—on and turn—off transitions during each switching cycle then the switching loss in the switch as given in [1] shall be:

$$P_s = \frac{V_o \cdot I_o \cdot f_s}{2} \cdot (t_{on} + t_{off})$$

(1.1)

This equation shows that the switching loss in any semiconductor switch varies linearly with switching frequency  $f_s$  and the delay times. Such a switch mode converter is therefore unsuitable for operation at high frequencies above 20 kHz. Although switching stresses can be reduced by using simple dissipative snubbers across the switch the efficiency of the converter is not improved as the switching power loss shifts from the switch to the snubbers.

From equation (1-1) an important result can be deduced that switching losses can be reduced by two methods:

- (i) By reducing the turn-on and turn-off delay times. This is done by using faster and more efficient switches in the converter.

- (ii) By making the current or voltage across the switch zero before turning it on or off.

Soft switching resonant converters are based on this concept.

#### 1.3.1 RESONANT SOFT SWITCHING SCHEMES

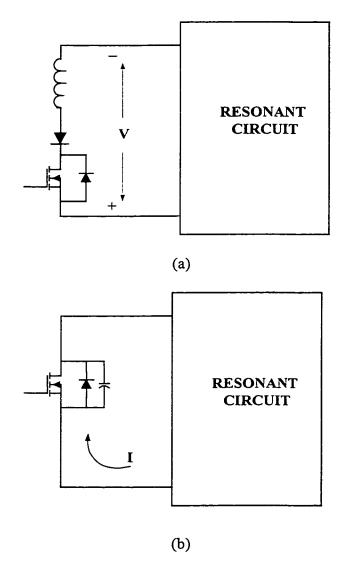

There are two types of resonant soft switching depending on whether the voltage across switch or the current through switch is made zero:

(i) Zero-Current Switching (ZCS): A switch that operates with ZCS has an inductor in series with it and a series blocking diode if the switch is bi-directional. The switch is turned on with ZCS as the series inductor slows down the rate of rise of current after voltage across switch goes to zero. If a negative voltage from a resonant circuit is made to appear across the switch-inductor combination, then the current through switch will naturally reduce to zero and switch is turned off with ZCS as shown in Fig. 1.1 (a).

(ii) Zero-Voltage Switching (ZVS): A switch that operates with ZVS has an anti-parallel diode and a capacitor across it. If negative current is forced to flow through the anti-parallel diode then voltage across switch reduces to zero and then the switch is turned on with ZVS. During turn-off the capacitor across switch reduces the rate of rise of voltage across device as current reduces to zero as in Fig. 1.1 (b).

Fig. 1.1 (a) ZCS turn-off using negative voltage (b) ZVS turn-on using negative current.

ZVS is preferred over ZCS because with ZVS the parasitic switch capacitance dissipates its energy into the load. If there were no ZVS this parasitic capacitance would dissipate as heat in the switch which lowers the efficiency of the system.

There are three main types of resonant converters – 1) Series resonant 2) Parallel resonant and 3) Series-parallel resonant converter. These converters have been discussed in [11] and operate with variable frequency control. They are suitable for the dc-dc converter stage only since it is difficult to implement power factor correction as well as output voltage regulation in the control circuit. Several modifications of the original topologies have been proposed which work under fixed switching frequency but almost all are suitable for use as dc-dc converters only.

For use as ac-dc converter, a new class of resonant converters utilising PWM techniques called Quasi-Resonant Converters (QRC) was developed in [12]-[13]. These converters have ZVS of the main switch but they suffer from parasitic oscillations between the resonant inductor and parasitic capacitance of the rectifying diode. These oscillations affect the stability of the system and damping them results in power loss in the converter. Multi-resonant converters solved this problem by using the various parasitics of the converter as a part of the resonant network [14]-[15]. But they suffer from increased complexity of converter leading to more cost. Also the size of the converters is not reduced much even though the switching frequency can be pushed to as high as 10 MHz.

Another approach to achieve high efficiency in ac-dc converters was to integrate the diode bridge with a resonant boost PFC pre-regulator by using controllable switches in the diode bridge [16]. This resulted in lesser conduction losses in the converter as the input current flowed through two switches only instead of three which was the case when the

diode bridge and boost stage were separate. But these did not result in high efficiency [16] because of hard switching or because the switches had ZCS and not ZVS which is more efficient [17]. The converter in [18] works with slightly higher efficiency but with variable frequency operation. Some of the converters were very complex [19] – [20] which have isolated sensing of voltage and current which makes converter expensive as well. The converter in [21] has many sub-circuit modes which makes converter design difficult.

#### 1.3.2 ZERO VOLTAGE TRANSITION CONVERTERS

Zero Voltage Transition (ZVT) converters were proposed in [22] and [23]. In ZVT converters there is an auxiliary resonant circuit across the main switch. The auxiliary circuit is activated only during the main switch transitions and so it is on for only a small time during the switching cycle. Therefore resonance occurs only during the switch transitions. This limits the auxiliary circuit losses. As the resonant inductor slows down the rate of fall of current through the boost diode, the EMI of the ZVT boost converter is also low.

Although highest efficiency of the rectifier is achieved using the ZVT boost converter, some common disadvantages of this class of converter are:

- 1) The circuit suffers from high stress in across the auxiliary switch as in [22] [26].

- 2) The converter in [27] suffers from higher conduction loss due to high rms currents in auxiliary circuit and the boost diode.

- 3) The converter in [28] suffers from parasitic resonance between the resonant inductor and parasitic capacitance of the auxiliary switch. The saturable inductor limits the switching frequency also.

- 4) Control of the converter in [29] is very complex.

- 5) The converter in [30] cannot be used for PFC applications as optimum design for ac input is difficult.

The converter proposed in [31] and [32] overcomes all the above problems at the cost of slightly greater voltage stress across the auxiliary switch. However it makes use of an auxiliary transformer to feed-forward some of the energy of the auxiliary circuit to the output. The design of this transformer is difficult as the leakage inductance of this transformer causes severe oscillations in the current through the main switch. Also there are conduction losses in the auxiliary circuit which limit the rise in efficiency. So it is desirable to have a feed-forward mechanism in the auxiliary circuit without using this transformer.

#### 1.4 THESIS OBJECTIVES

This thesis presents a ZVT converter with a soft switching auxiliary circuit which has reduced conduction losses, for PFC applications. The main objectives of the thesis are to:

- (i) Analyse the steady-state operation of the proposed converter under the worst case condition that is defined as the peak of the input ac voltage wave when input current is maximum and the ZVS interval is the least.

- (ii) Present design characteristics of the converter based on the steady state analysis, which help in understanding the internal working of the converter.

- (iii) Present the control scheme used to achieve power factor correction.

- (iv) Specify the design guidelines with a design example to assist in the design process.

(v) Verify with results from an experimental prototype the design procedure and feasibility of the proposed converter.

#### 1.5 THESIS OUTLINE

The contents of the thesis are as follows:

In Chapter 2 the proposed ZVT converter is described and its operation explained. The steady state analysis is performed during a single switching cycle of the main switch.

Analytical results are given at the end of the chapter.

In Chapter 3 characteristic curves of the converter are obtained based on the steady state analysis of Chapter 2. These curves help provide insights into the working of the converter.

In Chapter 4 control of the proposed converter for PFC applications is described.

In Chapter 5 a design example is given which makes use of the design curves of Chapter 3. Experimental results from a laboratory prototype are given which verify the design procedure and the usefulness of the topology.

In Chapter 6, a summary of the thesis is given. Conclusions and contributions of this thesis are discussed. Suggestions for future work in this area are also suggested.

#### **CHAPTER 2**

## A ZERO VOLTAGE SWITCHING BOOST CONVERTER USING A SOFT SWITCHING AUXILIARY CIRCUIT

#### 2.1 Introduction

In examining previous ZVT converters it is found that many [22]-[25] do not offer a lossless turn—on and turn—off of the auxiliary switch which results in lower efficiency in the converter. These converters also have to incorporate a capacitor as a snubber across the main switch in order to achieve its zero voltage turn—off. The addition of this capacitor results in higher rms current in the auxiliary switch that results in more conduction losses in the auxiliary circuit. Also it is seen from [31] that adding this capacitor also results in lesser ZVS turn-on interval of the main switch if other parameters in the auxiliary circuit are kept the same. All these points indicate that it is desirable to keep the value of this capacitor the least possible. As the switch always has some parasitic capacitance associated with it so this capacitance is the minimum which a converter should have across the main switch.

This chapter presents a new topology which overcomes the above mentioned drawbacks. Steady state analysis of the proposed converter during a switching cycle is presented from which design curves are obtained in Chapter 3 which are then used in Chapter 5 in designing the ZVT converter. Experimental results obtained from a prototype are shown and finally the main points of this chapter are summarised.

The outline of this chapter is as follows:

Section 2.2 gives a short functional description of the proposed converter.

The converter's features are presented in Section 2.3

The steady state analysis of the ZVT converter is presented in Section 2.4.

Section 2.5 presents analytical waveforms obtained from the steady-state analysis.

Section 2.6 summarises the key points of this chapter.

#### 2.2 Functional Description

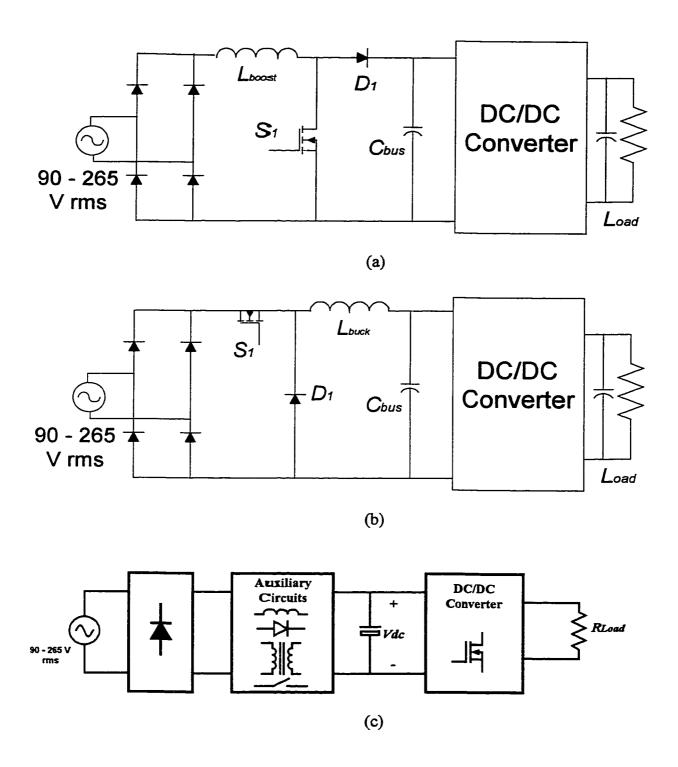

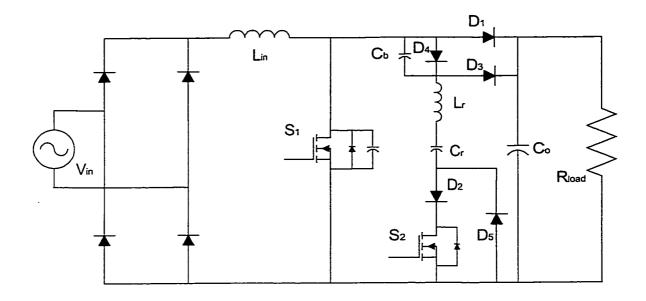

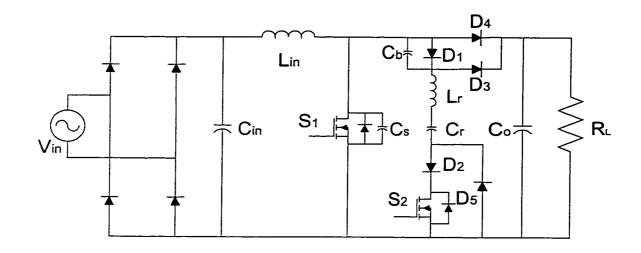

Fig. 2.1 shows the ZVT converter that is being presented and analysed in this thesis. The circuit can be assumed to be made up of two parts:

- 1). The main power circuit consisting of a diode bridge, main boost switch  $S_I$ , boost inductor  $L_{in}$  the boost diode  $D_I$ , and the output capacitor  $C_o$ .

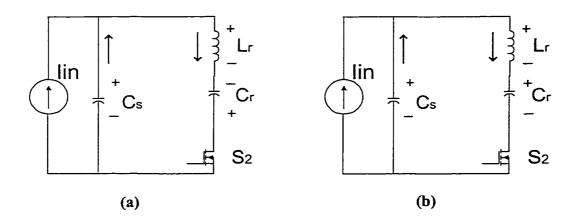

- 2). The auxiliary circuit consisting of the resonant inductor  $L_r$ , resonant capacitor  $C_r$  and another capacitor  $C_b$ , auxiliary switch  $S_2$  and diodes  $D_2$ ,  $D_3$ ,  $D_4$  and  $D_5$ .

The output load is represented by an output resistance  $R_{load}$ . The diode bridge rectifies the variable input AC source voltage at 60 Hz into an uncontrolled DC voltage. The boost inductor  $L_{in}$ , main switch  $S_I$  and boost diode  $D_I$  form a simple boost converter which converts the uncontrolled DC into a controlled DC bus voltage at the output capacitor  $C_o$ . Capacitor  $C_o$  filters the second harmonic current and prevents its appearing at the load. Switch  $S_2$  is turned on just before  $S_I$  and serves to achieve a zero current turnoff of the diode  $D_I$  and also discharges the parasitic capacitance across  $S_I$  to ensure ZVS of  $S_I$ . Auxiliary circuit resonant components  $C_r$  and  $L_r$  make possible the ZCS turnon

Fig. 2.1 The proposed ZVT PWM boost converter.

and ZVS turn-off in  $S_2$ .

Diode  $D_2$  is placed in series with  $S_2$  to prevent conduction of the body diode of the auxiliary switch which is a slow recovery diode. This will also prevent the parasitic capacitance of  $S_2$  from resonating with  $L_r$ . Diode  $D_5$  is a fast recovery diode which is placed across  $S_2$  and allows current to flow in direction opposite to switch  $S_2$  current.

Diode  $D_4$  forces this reverse current to flow through capacitor  $C_b$  which will store a part of the energy from the resonant capacitor  $C_r$  and will acquire a negative voltage. If capacitor  $C_b$  was not present then all the energy from the resonant circuit would have been dissipated in the main switch as conduction losses. But  $C_b$  is able to store some of this energy which is sent to the output load at the end of the switching cycle.

When the switch  $S_I$  is turned off it will do so with ZVS because the net voltage across  $S_I$  will not be the output voltage  $V_o$  but voltage  $V_o$  minus voltage across  $C_b$ . The

resonant peak current through the main switch is also reduced because capacitor Cb is able to store some of the energy of the resonant circuit which would have otherwise been wasted as conduction losses. Diode  $D_I$  is prevented from turning on by the negative voltage across  $C_b$  and so the current first discharges  $C_b$  into the load through diode  $D_3$  and only then does  $D_I$  conduct.

The brief description of the converter's principle of operation is: