#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

|  | · |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# Design and Evaluation of a

# **Data-Dependent Low-Power 8×8 DCT/IDCT**

Cheng-Yu Pai

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillments of the Requirement

for the Degree of Master of Applied Science (Electrical) at

Concordia University

Montreal, Quebec, Canada

December 2000

© Cheng-Yu Pai, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-59308-8

#### **ABSTRACT**

#### Design and Evaluation of a

### Data-Dependent Low-Power 8×8 DCT/IDCT

Cheng-Yu Pai<sup>1</sup>

Traditional fast *Discrete Cosine Transform* (DCT)/*Inverse DCT* (IDCT) algorithms have focused on reducing arithmetic complexity and have fixed run-time complexities regardless of the input. Recently, data-dependent signal processing has been applied to the DCT/IDCT. These algorithms have variable run-time complexities.

A new two-dimensional 8×8 low-power DCT/IDCT design is implemented using VHDL by applying the data-dependent signal-processing concept onto the traditional fixed-complexity fast DCT/IDCT algorithm. To reduce power, the design is based on Loeffler's fast algorithm, which uses a low number of multiplications. On top of that, zero bypassing, data segmentation, input truncation, and hardwired canonical sign-digit (CSD) multipliers are used to reduce the run-time computation, hence reduce the switching activities and the power.

When synthesized using Canadian Microelectronic Corporation 3-V 0.35  $\mu$ m CMOSP technology, this FDCT/IDCT design consumes 122.7/124.9 mW with clock frequency of 40MHz and processing rate of 320M sample/sec. With technology scaling to 0.35  $\mu$ m technology, the proposed design features lower switching capacitance per

<sup>&</sup>lt;sup>1</sup> This work is supported by National Sciences and Engineering Research Council of Canada (NSERC) post-graduate scholarship, and NSERC research grants

sample, i.e. more power-efficient, than other previously reported high-performance FDCT/IDCT designs.

**Keywords**: Data-dependent computation, discrete cosine transform (DCT), inverse discrete cosine transform (IDCT), low power, canonical sign-digit multiplier.

## Acknowledgements

I would like to express my deepest and most sincere gratitude toward my supervisors – Dr. Asim J. Al-Khalili and Dr. William E. Lynch. They have given me clear and helpful guidelines throughout my years as a master student. Above all, I wish to thank them for the great amount of time devoted to me and my work.

I wish to thank the scholarship offered by the National Sciences and Engineering Research Council of Canada (NSERC) Post-Graduate Scholarship (PGS-A), and NSERC research grants. Their financial support allows me concentrating my time and effort on my research.

I would also like to thank my fellow friends Wassim Tout, Wei Wang, and VLSI lab specialist Ted Obuchowicz for helping me throughout the technical problems with the simulation environments, and giving me their valuable opinions about the comparison strategy.

Finally, I would like to dedicate this work to my family for their love and support.

I thank you all for your patience and your sacrifices. This work is as much yours as it is mine.

# **Table of Contents**

| List of | f Fig   | ures                                             | ix |

|---------|---------|--------------------------------------------------|----|

| List of | f Tak   | oles                                             | X  |

| List o  | f Acr   | onyms                                            | xi |

|         |         |                                                  |    |

| 1 Int   | rodu    | lction                                           |    |

| 1.1.    |         | search Motivation                                |    |

| 1.2.    |         | ntribution of this Thesis                        |    |

| 1.3.    |         | wer Measurement Criteria                         |    |

| 1.4.    |         | esis Organization                                |    |

|         |         |                                                  |    |

| 2. Ba   | ckgr    | ound of FDCT/IDCT                                | 7  |

| 2.1.    | De      | finition of DCT and its Inverse                  | 7  |

| 2.2.    | Ch      | oices of Algorithms                              | 9  |

| 2.3     | 2.1.    | Chen's Algorithm Family                          | 9  |

| 2.:     | 2.2.    | Loeffler's FDCT/IDCT Algorithm                   | 11 |

| 2.:     | 2.3.    | Jeong's FDCT Algorithm                           | 13 |

| 2.      | 2.4.    | Summary and Comparison of Algorithm Complexities | 14 |

| 2.3.    | Pre     | ecision Requirements of IDCT                     | 15 |

| 2.4.    |         | apter Summary                                    |    |

| 1 D     | . • .   | Claire fourth a EDCT/IDCT                        | 17 |

|         | _       | Choices for the FDCT/IDCT                        |    |

| 3.1.    | Da      | ta-Dependent Loeffler's FDCT Algorithm           |    |

| 3.      | 1.1.    | Data-Dependent Bypassing Logic                   |    |

| 3.      | 1.2.    | Truncate Some Least-Significant Bits from Input  |    |

| 3.2.    | Da      | ta-Dependent Loeffler's IDCT Algorithm           |    |

| 2.3     | $T_{r}$ | anspose Memory Architecture                      | 25 |

| 3.4.               | Chapter Summary                                                  | 28 |

|--------------------|------------------------------------------------------------------|----|

| 4. Mu              | ltiplier Architectures                                           | 29 |

| 4.1.               | Survey of Constant Multiplication Schemes                        |    |

|                    | .1. Modified Booth Multiplier                                    |    |

| 4.1                | .2. Distributed Arithmetic (DA)                                  |    |

| 4.1                | .3. Hardwired Canonical-Sign-Digit (CSD) Wallace-Tree Multiplier |    |

| 4.1                | .4. Pattern-Based CSD Multiplier                                 |    |

| 4.2.               | CSD Multiplier Implementation Procedure                          | 35 |

| 4.3.               | Multiplier Synthesis Result                                      | 40 |

| 4.4.               | Chapter Summary                                                  | 42 |

| 5. Im <sub>1</sub> | olementation                                                     | 43 |

| 5.1.               | Hardwired CSD Multiplier Generator                               | 43 |

| 5.2.               | IEEE Standard 1180-1990 IDCT Compliant                           | 45 |

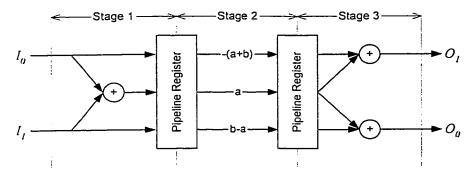

| 5.3.               | Pipelining Design                                                | 46 |

| 5.4.               | Chapter Summary                                                  | 47 |

| 6. Syn             | thesis Results                                                   | 49 |

| 6.1.               | Synthesis Results of the Proposed Design                         | 49 |

| 6.2.               | Comparison with past FDCT/IDCT VLSI implementations              | 50 |

| 6.3.               | Chapter Summary                                                  | 53 |

| 7. Coi             | aclusion                                                         | 54 |

| 7.1.               | Summary of Research.                                             | 54 |

| 7.2.               | Conclusion                                                       | 55 |

| 7.3.               | Possible Improvements for Future Research                        | 56 |

| Biblio             | graphy                                                           | 59 |

| Appendix A | Truncation Test Result                         | 65 |

|------------|------------------------------------------------|----|

| Appendix B | Sample Output of CSD Multiplier Generator      | 69 |

| Appendix C | Source Code of Constant Multiplier Generator   | 74 |

| Appendix D | IEEE Standard 1180-1990 Compliant Test Program | 95 |

# **List of Figures**

| Figure 1: General block diagram of video compression encoder                           | 2  |

|----------------------------------------------------------------------------------------|----|

| Figure 2: 2-D FDCT/IDCT using row-column (separable) method                            | )  |

| Figure 3: Loeffler's FDCT algorithm                                                    | 1  |

| Figure 4: Loeffler's IDCT algorithm                                                    | 2  |

| Figure 5: Jeong's fast FDCT algorithm                                                  | 3  |

| Figure 6: Setup for measuring the accuracy of a proposed 8x8 IDCT 1                    | 5  |

| Figure 7: Zero Bypassing Multiplier                                                    | 8  |

| Figure 8: Multiplication Segmentation                                                  | 9  |

| Figure 9: 2-D row-column FDCT with truncation                                          | 1  |

| Figure 10: Test model to measure the effect of truncation                              | 2  |

| Figure 11: Ping-pong transpose memory                                                  | .5 |

| Figure 12: On-the-fly 8×8 Transpose Memory                                             | .6 |

| Figure 13: States of the transpose matrix for different clock cycles                   | .7 |

| Figure 14: Converting binary number 0110010111 into CSD representation                 | 3  |

| Figure 15: Hardwired CSD multiplier for multiplying $cos(3\pi/16)$ with 8-bit unsigned | ed |

| integer3                                                                               | 8  |

| Figure 16: Hardwired CSD multiplier for multiplying $\cos(3\pi/16)$ with 8-bit signs   | èĊ |

| integer4                                                                               | ŧС |

| Figure 17: Pinelined ken block                                                         | 16 |

# **List of Tables**

| Table 1: Transfer function of Loeffler's FDCT building blocks                        | . 11 |

|--------------------------------------------------------------------------------------|------|

| Table 2: Transfer function of Loeffler's IDCT building blocks                        | . 12 |

| Table 3: Complexities of different FDCT algorithms                                   | . 14 |

| Table 4: IEEE Standard 1180-1900 IDCT Precision Requirement                          | . 16 |

| Table 5: Truncation errors against the number of truncated bits                      | . 23 |

| Table 6: Comparison of general-purpose multiplication against ROM based              |      |

| multiplication                                                                       | . 31 |

| Table 7: Canonical sign-digit representation of $\cos(n\pi/16)$                      | . 33 |

| Table 8: Truth-table of b+1                                                          | . 36 |

| Table 9: Truth table to simplify sign-extension                                      | . 39 |

| Table 10: Comparison of 32-bit CSD Wallace-tree multiplier with 4 different general- |      |

| purpose multipliers using Xilinx 4052XL-1 FPGA technology                            | . 41 |

| Table 11: IEEE Standard 1180-1990 Compliance for Proposed IDCT                       | . 46 |

| Table 12: Latencies for 1-D FDCT and 1-D IDCT                                        | . 47 |

| Table 13: Latencies for 2-D FDCT and 2-D IDCT                                        | . 47 |

| Table 14: Process and Specifications of the proposed FDCT/IDCT designs               | . 50 |

| Table 15: Summary of specifications of several FDCT/IDCT chips                       | . 51 |

| Table 16: Energy Efficiency (Switching Capacitances/Sample in 0.35μm technology).    | . 53 |

| Table 17: Truncation errors of test sequences: coke, salesman, and tennis            | . 68 |

### List of Acronyms

CCITT International Telegraph and Telephone Consultative Committee

CMC Canadian Microelectronic Corporation

CMG Constant Multiplier Generator

CPA Carry Propagate Adder

CSA Carry Save Adder

CSD Canonical Sign-Digit

DA Distributed Arithmetic

dB Decibel

DCT Discrete Cosine Transform

DFT Discrete Fourier Transform

FDCT Forward Discrete Cosine Transform

FPGA Field-Programmable Gate-Array

HDTV High-definition TV

IDCT Inverse Discrete Cosine Transform

IEEE Institute of Electrical and Electronic Engineers

JPEG Joint Photographic Experts Group

MC Motion Compensation

ME Motion Estimation

MHz Mega-Hertz

MOS Metal-Oxide Semiconductor

MPEG Moving Picture Experts Group

MUX Multiplexer

NMOS N-type MOS

PMOS P-type MOS

PSNR Peak Signal-to-Noise Ratio

ROM Read-Only Memory

SD Sign-Digit

SFG Signal Flow Graph

VLC Variable-Length Coding

VLSI Very Large-Scale Integration

# Chapter 1

### Introduction

#### 1.1. Research Motivation

Waveform compression has been an important research topic, and it has wide industry applications. The term waveform is a generic term that can be applied to speech signal, still image, or video signals. Generally speaking, these waveforms require large storage in physical devices, and require large communication bandwidth to transmit. For example, one-hour colored 704×480 frame-size video requires 704×480 (bytes/frame)  $\times$  1.5 (for color frames)  $\times$  30 (frame/sec)  $\times$  60 (sec./min.)  $\times$  60 (min/hour)  $\cong$  54.7 GB to store/transmit. That is an enormous amount of data. Due to the nature of these signals, redundancies can be removed by means of waveform compression. In practice, for the video signals, one can achieve from 40:1 (for high quality) up to 80:1 (for low quality) compression ratio. In other words, one-hour of digital video requires only about 1.37 GB to store or transmit.

The discrete cosine transform (DCT) has been widely used in waveform compression because it features good energy compaction and low computational complexity. It has become an integral part of many waveform compression standards, such as JPEG, MPEG-2, MPEG-4, CCITT Recommendation H. 261 and H. 263, and HDTV. [26]

The DCT, like the Discrete Fourier Transform (DFT), is used to transform the signal to the frequency domain. Unlike DFT that uses complex exponentials as basis functions, DCT uses cosines (real numbers) as basis functions. Since the human audiovisual system is less sensitive to high frequency harmonics, waveform compression standards use DCT to transform signal to frequency domain and perform compression on the DCT coefficients.

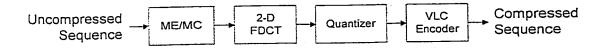

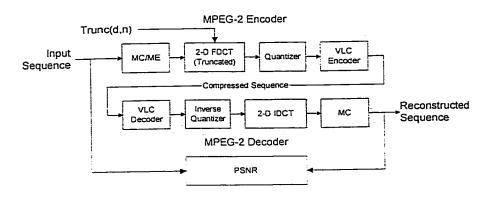

As an example, for video compression, both temporal and spatial redundancies are eliminated as shown in Figure 1. The motion estimation/motion compensation (ME/MC) block is used to reduce temporal redundancies due to high correlation among adjacent frames. The forward DCT (FDCT) together with the quantizer is used to reduce spatial redundancies. Finally, the variable-length coder (VLC) is used to reduce coding redundancies.

Figure 1: General block diagram of video compression encoder

With the advances in communication and VLSI technologies, it is expected that video telephony/conferencing on mobile devices will be more and more common in the future. Because mobile devices operate with battery power, in order to increase the battery life and recharging time, mobile devices always have stringent power specifications. Also, to save valuable communication bandwidth, video compression is always performed on these applications. As a result, the DCT chip is an integral part of video communication mobile devices, and the design of a low-power DCT chip is an

important problem. In this thesis, a low-power data-dependent DCT/IDCT design is presented to meet this need.

# 1.2. Contribution of this Thesis

Many earlier fast DCT algorithms are aimed at reducing the number of multiplications because general-purpose multipliers are assumed to be the basic hardware elements for computing the DCT. Later on, other design techniques, such as digital filtering and distributed arithmetic (DA), are also used to compute DCT [9]. In more recent works, data-dependent DCT algorithms have been introduced in [19]-[21][28]. Unlike traditional algorithms, which have fixed-computation complexity, data-dependent algorithms have variable run-time complexities that depend on the statistical properties of the input data. They may yield fewer or more computations in the run-time than the fixed complexity algorithms.

To reduce the power consumption, optimizations are performed at both the algorithmic level and the architectural level. The low-complexity Loeffler's [10] fast FDCT/IDCT algorithm is chosen to reduce the hardware requirement, which in turn reduces power.

The concept of data-dependent signal processing has also been applied to the fixed-complexity Loeffler's algorithm to reduce the switching activities. For both the FDCT and IDCT, zero-bypassing logic is inserted into the circuit to bypass redundant computations. The zero-bypassing logic takes advantages of high correlation among input data for the FDCT, and high proportion of zero inputs for the IDCT. Furthermore, the FDCT design also truncates bits from its input to reduce the amount of data to be

processed, consequently reducing power consumption. The error introduced by the truncation is also analyzed in the thesis.

Further architectural optimization is performed on multipliers. Since multiplication is a high complexity operation compared to addition, the FDCT/IDCT designs use hard-wired canonical sign-digit (CSD) Wallace-tree multipliers since it utilizes minimum amount of power over the multipliers surveyed.

To summarize, the main contributions made in this thesis are listed as following:

- Introduce new data-dependent FDCT/IDCT algorithm by merging the datadependent processing concept with fast FDCT/IDCT algorithm.

- Empirically study the effect of truncating some least significant bits of the FDCT input to save computation.

- Derive detailed design procedure for implementing low-power constantcoefficient multipliers.

- Develop a code generator written in C++ that generate VHDL code of constant multipliers for different specifications.

### 1.3. Power Measurement Criteria

In VLSI design, it is always difficult to compare one design with another due to different process technology (feature size), supply voltages, operating frequency, implementation approach (full-custom, semi-custom, etc.), optimization parameters, and design algorithm/architectures. Depending on the design goal, several comparison methods have been suggested and used, such as A, P, T, PT, AT,  $AT^2$ , etc., where A stands

for area, T stands for time (delay), and P stands for power. Unfortunately, these measurement criteria give rough measures, which do not take all process technology into account.

In this thesis, the proposed design is compared with other reported designs by comparing the *switching capacitance per sample*, which has been used in [19-21][28]. In VLSI design, power can be estimated from the well-known formula:

$$P \cong \left(\frac{1}{2}p_{t} \cdot C_{L}\right) \cdot f_{Clk} \cdot V_{DD}^{2} \qquad \dots (1)$$

where P is the power,  $p_i$  is the switching probability,  $C_L$  is the load capacitance of the DCT/IDCT in this case,  $f_{Clk}$  is the clock frequency, and  $V_{DD}$  is the supply voltage. From equation (1), the switching capacitance is defined as  $\frac{1}{2}p_i \cdot C_L$ , and the switching capacitance per sample can be obtained by dividing the switching capacitance by the number of input/output samples per clock cycle. Since switching capacitance is directly proportional to power, this measurement method leads to comparing relative energy efficiency rather than absolute values such as in AP, PT, etc. It indicates how much power (switching capacitance) is required to obtain one output.

The main advantage of this method is that it takes out the effect of different process technology by performing technology scaling. Thus to compare one design of one technology with another design of different technology, technology scaling is first performed on the measured power, then the effects of clock frequency and voltage supply are factored out to obtain the switching capacitance per sample.

# 1.4. Thesis Organization

The organization of this thesis is as follows: in Chapter 2, the definition of discrete cosine transform and its inverse and the algorithm used in the proposed design are described. Chapter 3 describes the data-dependent signal processing concept and how it is incorporated into the design. Chapter 4 summarizes the pros and cons of several multiplier architectures, and provides a detailed design procedure for the selected multiplier – hardwired canonical sign-digit (CSD) Wallace-tree multiplier. Chapter 5 describes the design automation effort made to facilitate the implementation of hardwired multipliers. The IDCT accuracy test result and pipelining design are also described. In Chapter 6, synthesis results of the new FDCT/IDCT designs are reported and compared against previously reported implementations.

### Chapter 2

### **Background of FDCT/IDCT**

Since there exist many DCT definitions [38], the forward DCT (FDCT) and its inverse (IDCT) are defined in Section 2.1 for clarification.

Numerous fast algorithms for both FDCT and IDCT have been reported in the literature. Most of them attempted to minimize the number of additions and multiplications ([1], [8]-[13], [17-18], [29], etc.). These algorithms usually take advantage of the symmetry in the cosine basis functions, and the computation complexity is fixed for all input data (data independent algorithm). Since multiplication requires more hardware and computation time than adders, fewer multiplications imply low power.

In Section 2.2, several existing fast FDCT/IDCT algorithms are studied and compared. The Loeffler's [10] algorithm is chosen to be the fundamental FDCT/IDCT algorithm of the proposed design.

Since the FDCT is always followed by a quantizer, its precision requirement is not high. On the contrary, the IDCT is used to perform inverse transformation at both the encoder and the decoder, which requires high precision. It needs to conform to IEEE Standard 1180-1990, which is described in 2.3.

### 2.1. Definition of DCT and its Inverse

The N-point 1-D forward DCT (FDCT) is defined in equation 2:

$$X(n) = \sqrt{\frac{2}{N}}C(n)\sum_{k=0}^{N-1} x(k)\cos\frac{(2k+1)n\pi}{2N}$$

(2)

The N-point 1-D inverse DCT (IDCT) is define in equation 3:

$$x(n) = \sum_{k=0}^{N-1} \sqrt{\frac{2}{N}} C(k) X(k) \cos \frac{(2n+1)k\pi}{2N}$$

(3)

where

$$C(n) = \begin{cases} 1/\sqrt{2} & n = 0\\ 1 & n = 1, 2, ..., N-1 \end{cases}$$

Similarly, the  $N \times N$  2-D FDCT is defined as follows: [4]

$$X(u,v) = \frac{2}{N}C(u)C(v)\sum_{i=0}^{N-1}\sum_{j=0}^{N-1}x(i,j)\cos\left(\frac{(2i+1)u\pi}{2N}\right)\cos\left(\frac{(2j+1)v\pi}{2N}\right)...(4)$$

and the  $N \times N$  2-D IDCT is defined as:

$$x(i,j) = \frac{2}{N} \sum_{u=0}^{N-1} \sum_{v=0}^{N-1} C(u)C(v)X(u,v) \cos\left(\frac{(2i+1)u\pi}{2N}\right) \cos\left(\frac{(2j+1)v\pi}{2N}\right) \dots (5)$$

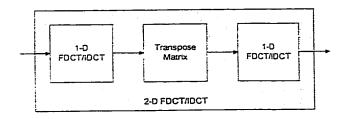

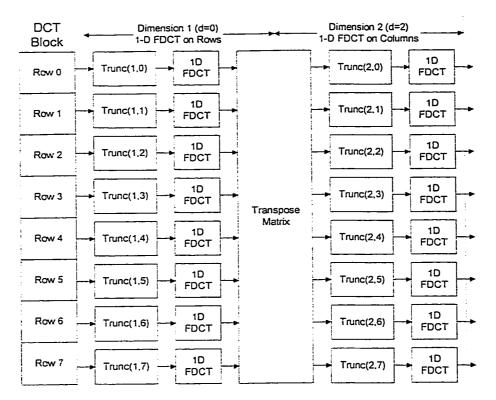

Notice that 2-D *N*×*N* FDCT/IDCT is a separable transformation, which means that it can be obtained by first performing 1-D *N*-point DCT/IDCT on the rows, then performing 1-D *N*-point DCT/IDCT on the columns, or the other way around. This method of computing 2-D DCT/IDCT is generally referred to as row-column method or indirect method. The general block diagram of this method is shown in Figure 2.

Figure 2: 2-D FDCT/IDCT using row-column (separable) method

The row-column method is the most popular method in VLSI implementations ([2]-[7], [9], [14]-[16], etc.). Also, since the 8×8 block size is used by MPEG and other standards, in this thesis, the FDCT/IDCT design presented uses 8×8 block size.

#### 2.2. Choices of Algorithms

Many fast DCT/IDCT algorithms have been reported in the literature. In this section, several fixed-complexity algorithms are reviewed and compared based on their arithmetic complexities. The comparison suggests that Loeffler's FDCT/IDCT algorithm is the most efficient and is used as the basis of the proposed design.

#### 2.2.1. Chen's Algorithm Family

Chen's fast algorithm [1] reported in 1977 is by far the most widely used DCT/IDCT algorithm. It has been used in [2]-[7] and many other papers. It is a fixed-complexity algorithm. The idea of Chen's algorithm is to exploit the symmetry in the DCT/IDCT transformation matrix. The 8x8 DCT can be written in matrix form:

$$\begin{bmatrix} X(0) \\ X(1) \\ X(2) \\ X(3) \\ X(4) \\ X(5) \\ X(6) \\ X(7) \end{bmatrix} = \begin{bmatrix} a & a & a & a & a & a & a & a & a \\ b & d & e & g & -g & -e & -d & -b \\ c & f & -f & -c & -c & -f & f & c \\ d & -g & -b & -e & e & b & g & -d \\ a & -a & -a & a & a & -a & -a & a \\ e & -b & g & d & -d & -g & b & -e \\ g & -e & d & -b & b & -d & e & -g \end{bmatrix} \begin{bmatrix} x(0) \\ x(1) \\ x(2) \\ x(2) \\ x(3) \\ x(4) \\ x(5) \\ x(6) \\ x(7) \end{bmatrix}$$

$$(6)$$

where

$$[a \ b \ c \ d \ e \ f \ g] = \frac{1}{2} \left[ \cos \frac{\pi}{4} \ \cos \frac{\pi}{16} \ \cos \frac{\pi}{8} \ \cos \frac{3\pi}{16} \ \cos \frac{5\pi}{16} \ \cos \frac{3\pi}{8} \ \cos \frac{7\pi}{16} \right]$$

Since the even rows of the transformation matrix are even symmetric and odd rows are odd-symmetric, by exploiting the symmetry and separating even and odd rows, equation (6) can be rewritten as follows:

$$\begin{bmatrix} X(0) \\ X(2) \\ X(4) \\ X(6) \end{bmatrix} = \begin{bmatrix} a & a & a & a \\ c & f & -f & -c \\ a & -a & -a & a \\ f & -c & c & -f \end{bmatrix} \times \begin{bmatrix} x(0) + x(7) \\ x(1) + x(6) \\ x(2) + x(5) \\ x(3) + x(4) \end{bmatrix}$$

$$\begin{bmatrix} X(1) \\ X(3) \\ X(5) \\ X(7) \end{bmatrix} = \begin{bmatrix} b & d & e & g \\ d & -g & -b & -e \\ e & -b & g & d \\ g & -e & d & -b \end{bmatrix} \times \begin{bmatrix} x(0) - x(7) \\ x(1) - x(6) \\ x(2) - x(5) \\ x(3) - x(4) \end{bmatrix}$$

$$(7)$$

Similarly, the 1-D IDCT can be rewritten as follows:

$$\begin{bmatrix} Y(0) \\ Y(1) \\ Y(2) \\ Y(3) \end{bmatrix} = \begin{bmatrix} a & c & a & f \\ a & f & -a & -c \\ a & -f & -a & c \\ a & -c & a & -f \end{bmatrix} \times \begin{bmatrix} X(0) \\ X(2) \\ X(4) \\ X(6) \end{bmatrix} + \begin{bmatrix} b & d & e & g \\ d & -g & -b & -e \\ e & -b & g & d \\ g & -e & d & -b \end{bmatrix} \times \begin{bmatrix} X(1) \\ X(3) \\ X(5) \\ X(7) \end{bmatrix} \tag{8}$$

$$\begin{bmatrix} Y(7) \\ Y(6) \\ Y(5) \\ Y(4) \end{bmatrix} = \begin{bmatrix} a & c & a & f \\ a & f & -a & -c \\ a & -f & -a & c \\ a & -c & a & -f \end{bmatrix} \times \begin{bmatrix} X(0) \\ X(2) \\ X(4) \\ X(6) \end{bmatrix} - \begin{bmatrix} b & d & e & g \\ d & -g & -b & -e \\ e & -b & g & d \\ g & -e & d & -b \end{bmatrix} \times \begin{bmatrix} X(1) \\ X(3) \\ X(5) \\ X(7) \end{bmatrix}$$

#### 2.2.2. Loeffler's FDCT/IDCT Algorithm

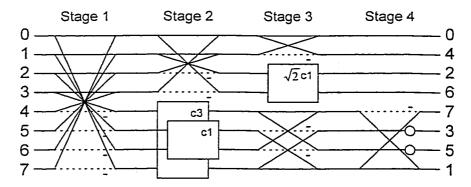

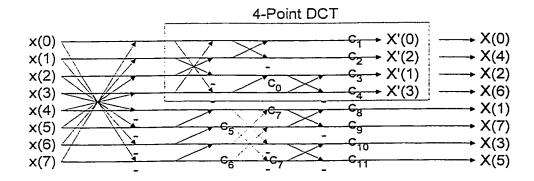

Loeffler's 1-D 8-point FDCT algorithm uses 11 multiplications and 29 additions only. The signal flow graph (SFG) of an 8-point 1-D DCT is shown in Figure 3, and the transfer functions of the building blocks are given in Table 1.

Figure 3: Loeffler's FDCT algorithm [10]

| Symbol                                   | Equation                                                                                                                                                                                     | Effort             |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                                          | $O_0 = I_0 + I_1$ $O_1 = I_0 - I_1$                                                                                                                                                          | 2 add              |

| $I_{ij} - kcn - O_{ij}$ $I_{i} - O_{ij}$ | $O_0 = I_0 \left( k \cos \frac{n\pi}{2N} \right) + I_1 \left( k \sin \frac{n\pi}{2N} \right)$ $O_1 = -I_0 \left( k \sin \frac{n\pi}{2N} \right) + I_1 \left( k \cos \frac{n\pi}{2N} \right)$ | 3 mult. +<br>3 add |

| I O                                      | $O = \sqrt{2}I$                                                                                                                                                                              | l mult.            |

Table 1: Transfer function of Loeffler's FDCT building blocks [10]

Notice that the second building block (*kcn*) requires only 3 multiplications and 3 additions instead of 4 multiplications and 2 additions when equation 9 is used.

$$\begin{cases}

O_0 = aI_0 + bI_1 = (b - a)I_1 + a(I_0 + I_1) \\

O_1 = -bI_0 + aI_1 = -(a + b)I_0 + a(I_0 + I_1)

\end{cases}, \text{ where } a = k \cos \frac{n\pi}{2N}, b = \sin \frac{n\pi}{2N} \tag{9}$$

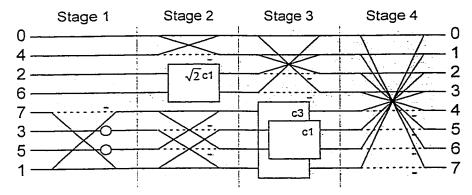

By reversing the transfer function of each building block shown in Table 1, and reversing the signal-flow direction, it is easy to show that the IDCT has SFG shown in Figure 4 with building block transfer function shown in Table 2. Notice that the Loeffler IDCT algorithm has the same arithmetic complexity as in the FDCT case (11 multiplications and 29 additions). Notice also that division by 2 is considered using no operation since it can be realized by ignoring the least-significant bit of the value to be divided.

Figure 4: Loeffler's IDCT algorithm

| Symbol                                                                                                             | Equation                                                                                                                                                                                                                            | Effort             |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                                                                                                                    | $O_0 = (I_0 + I_1)/2$<br>$O_1 = (I_0 - I_1)/2$                                                                                                                                                                                      | 2 add              |

| $\begin{bmatrix} I_0 & - & & & \\ I_1 & - & & & \\ \end{bmatrix} \begin{bmatrix} kcn & -O_0 \\ -O_1 \end{bmatrix}$ | $O_0 = I_0 \left( \frac{1}{k} \cos \frac{n\pi}{2N} \right) - I_1 \left( \frac{1}{k} \sin \frac{n\pi}{2N} \right)$ $O_1 = I_0 \left( \frac{1}{k} \sin \frac{n\pi}{2N} \right) + I_1 \left( \frac{1}{k} \cos \frac{n\pi}{2N} \right)$ | 3 mult. +<br>3 add |

| 1-0-0                                                                                                              | $O = I/\sqrt{2}$                                                                                                                                                                                                                    | 1 mult.            |

Table 2: Transfer function of Loeffler's IDCT building blocks

#### 2.2.3. Jeong's FDCT Algorithm

Jeong's [13] 8-point FDCT algorithm reported in 1998 uses 28 additions, 12 multiplications. This algorithm is special because it performs most multiplications at the final stage and requires fewer multiplication stages than other algorithms, so propagation errors occurring in the fixed-point computation can be reduced.

By separating even and odd points in the DCT, this algorithm uses trigonometric identities to reduce the number of multiplication needed to calculate DCT.

• Even points:

$$X(2l) = \sqrt{\frac{2}{N}}\alpha(n)\sum_{k=0}^{N/2-1} \left[x(k) + x(N-1-k)\right]\cos\frac{(2k+1)2l\pi}{2N}, \text{ where } l \in [0,3]$$

• Odd points:

$$X(2l+1) = \left(2\cos\frac{(2l+1)\pi}{2N}\right)^{-1}\sqrt{\frac{2}{N}}\alpha(n) \times \left[y(2m-1) + y(2m)\right]\cos\frac{(2l+1)2m\pi}{N} + \left[y(2m) + y(2m+1)\right]\cos\frac{(2l+1)(2m+1)\pi}{N}\right\}$$

where  $y(k) = x(k) - x(N-1-k)$  and  $y(-1) = 0$

The signal flow graph is shown in Figure 5.

Figure 5: Jeong's fast FDCT algorithm [13]

where

$$c_0 = 1/C_4^1$$

,  $c_1 = \sqrt{2}/4$ ,  $c_2 = C_4^1/2$ ,  $c_3 = C_4^1/C_8^1$ ,  $c_4 = C_4^1/4C_8^3$ ,  $c_5 = c_3$ ,  $c_6 = 1/C_8^1$ ,  $c_7 = C_8^3/C_8^1$ ,  $c_8 = C_8^1/4C_{16}^1$ ,  $c_9 = C_8^1/4C_{16}^7$ ,  $c_{10} = C_8^1/4C_{16}^3$ ,  $c_{11} = C_8^1/4C_{16}^5$ , and  $C_m^n \equiv \cos \pi n/m$

#### 2.2.4. Summary and Comparison of Algorithm Complexities

Since in VLSI implementation, each computation, i.e. addition and multiplication, requires hardware and consumes power, algorithms with fewer addition/multiplication lead to lower power. Also, since multiplication requires more power than addition, one algorithm is better than another if it requires fewer multiplications (for integer operations).

Table 3 summarizes the complexity of several fixed-complexity FDCT algorithms. In [34], Duhamel demonstrated that the theoretical lower bound of an 8-point DCT is 11 multiplications. Since the number of multiplication in Loeffler's [10] algorithm reaches the theoretical lower bound and the number of addition is not worse than other algorithms (except Jeong's), the Loeffler's algorithm is chosen.

| Algorithm      | Chen [1] | Wang<br>[31] | Lee<br>[11] | Vetterli<br>[32] | Suehiro<br>[33] | Hu<br>[12] | Loeffler [10] | Jeong<br>[13] |

|----------------|----------|--------------|-------------|------------------|-----------------|------------|---------------|---------------|

| Multiplication | 16       | 13           | 12          | 12               | 12              | 12         | 11            | 12            |

| Add            | 26       | 29           | 29          | 29               | 29              | 29         | -29           | 28            |

Table 3: Complexities of different FDCT algorithms (adapted column 1-7 from Table 1 in [10])

#### 2.3. Precision Requirements of IDCT

In video compression, the precision requirement of FDCT is not high because it is always followed by heavy quantization. On the contrary, since the IDCT is used for sequence reconstruction, it is important for IDCT to be computed with high precision.

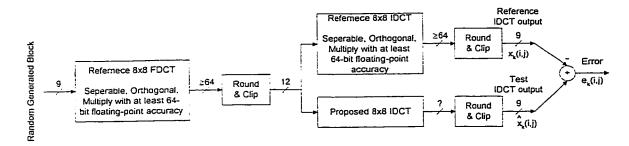

The IEEE Standard 1180-1990 [27] defines the specification for the implementations of IDCT. The step for measuring the accuracy of an 8x8 IDCT block is shown in Figure 6.

Figure 6: Setup for measuring the accuracy of a proposed 8x8 IDCT (figure 2 in [27])

The standard defines a random number generator that can generate numbers within lower and upper bounds (-L and H) inclusive. Based on these random numbers, 10000~8x8 blocks for (L=256, H=255), (L=H=5) and (L=H=300) are used as input for reference FDCT (see Figure 6), and passed through the diagram shown in Figure 6. The error,  $e_k(i,j)$ , is defined to be the difference between the "test" IDCT output and the "reference" IDCT output, i.e.:

$$e_k(i,j) = \hat{x}_k(i,j) - x_k(i,j)$$

The standard defines the following terms to measure the error (see Table 4).

| Term                                                                  | Definition                                                                                          | Maximum<br>Magnitude |  |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Peak error (ppe)                                                      | $Max( e_k(i.j) )$                                                                                   | 1                    |  |  |  |  |

| Mean square error for any pixel ( <i>pmse</i> )                       | $pmse(i,j) = \frac{\sum_{k=1}^{10000} e_k^2(i,j)}{10000}$                                           | 0.06                 |  |  |  |  |

| Overall mean square error (omse)                                      | omse(i, j) = $\frac{\sum_{i=0}^{7} \sum_{j=0}^{7} \sum_{k=1}^{10000} e_k^2(i, j)}{64 \times 10000}$ | 0.02                 |  |  |  |  |

| Mean error for any pixel (pme)                                        | $pme(i,j) = \frac{\sum_{k=1}^{10000} e_k(i,j)}{10000}$                                              | 0.015                |  |  |  |  |

| Overall mean error (ome)                                              | $ome(i,j) = \frac{\sum_{i=0}^{7} \sum_{j=0}^{7} \sum_{k=1}^{10000} e_k(i,j)}{64 \times 10000}$      | 0.0015               |  |  |  |  |

| For all-zero input, the proposed IDCT shall generate all-zero output. |                                                                                                     |                      |  |  |  |  |

Table 4: IEEE Standard 1180-1900 IDCT Precision Requirement

#### 2.4. Chapter Summary

In this chapter, the FDCT and IDCT are defined. Several fast fixed-complexity FDCT/IDCT algorithms are reviewed and their computational complexities are summarized in Table 3. Since low arithmetic complexity usually implies low power, the Loeffler's algorithm is used as the basis of the proposed design.

The IEEE 1180-1990 standard is also described in this chapter. The standard defines the precision requirements of IDCT, which the new IDCT design will conform to.

In the next chapter, detailed discussion/description is presented to show how the data-dependent concept is integrated into Loeffler's FDCT/IDCT algorithm to make it a data-dependent algorithm.

### Chapter 3

# **Design Choices for the FDCT/IDCT**

In this chapter, the data-dependent processing concept is applied to Loeffler's FDCT/IDCT algorithm. In Section 3.1 and 3.2, data-dependent bypassing logic is inserted into Loeffler's FDCT/IDCT algorithms to achieve more power reduction. To further reduce the computation complexity, the least significant bits of the FDCT inputs are truncated. The effect of truncation is studied in detail.

Since the row-column method is used to compute the 2-D FDCT/IDCT by using two 1-D FDCT/IDCT with a transpose memory in between (see Figure 2), Section 3.3 studies two transpose memory architectures. The on-the-fly transpose memory architecture is used in this work.

#### 3.1. Data-Dependent Loeffler's FDCT Algorithm

To have a power-efficient design, data-dependent algorithm and truncation techniques are adopted into Loeffler's FDCT algorithm.

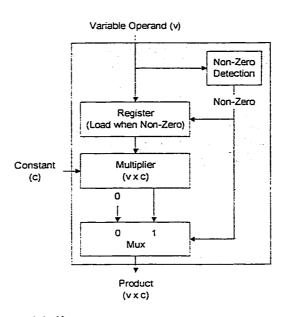

#### 3.1.1. Data-Dependent Bypassing Logic

Loeffler's FDCT algorithm performs several butterfly operations on the inputs (see Figure 3). In general, the inputs are well correlated for the FDCT. Thus, the subtractions used in the butterfly are very likely to produce zeros or small numbers. Since

most multiplications are performed in the *kcn* blocks, and the inputs of the *kcn* blocks are the results of subtractions, adding zero bypassing logic in front of each multiplication in the *kcn* blocks will reduce the number of multiplications. As shown in Figure 7, the zero bypassing logic only adds the non-zero-detection logic (AND gate), a register, and a multiplexer (MUX) to the circuit. The overhead, both the area and speed, introduced is small comparing to the multiplier itself.

Figure 7: Zero Bypassing Multiplier

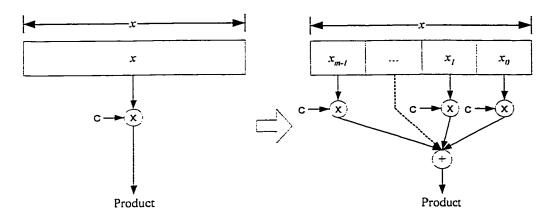

By segmenting the inputs of multipliers into several smaller chunks (data segmentation), further computational reduction can be achieved by taking advantage of the fact that the inputs of the kcn block are very likely to be small numbers because the inputs are obtained from butterflying highly correlated data. Thus, instead of multiplying x by c directly, the multiplication is done by breaking x into m segments, performing multiplication on each segment, and then adding the products together with proper offset if necessary (see Figure 8). The sum of the products is still  $x \times c$ . By inserting bypassing logic in front of each smaller multiplier, part of the small number inputs can be bypassed,

consequently reducing the switching activities and the power. For example, if  $x=00000111_b$  (7<sub>d</sub>), with two segments,  $x\times c$  is performed as  $(0000\times c)<<4+0110\times c$ . With zero-bypassing logic inserted,  $0000\times c$  is bypassed and uses no operation.

Figure 8: Multiplication Segmentation

The choice of segment size affects the probability of zero bypassing. One extreme is that there is only one segment, which is direct multiplication of  $x \times c$ . The other extreme is that each segment is one bit only, which is essentially performing shift-and-add operation. Theoretically, if we use segment of one bit only, one can achieve highest bypassing probability and uses lowest amount of multiplication. However, it requires the largest number of addition to add partial products to produce the final product. For n-segment, one would require to add n partial products together. Having more segments implies more complicated control logic and delay to produce the final result. Thus, having the trade-off between the probability of bypassing and the segmentation overhead in mind, we decide to use two segments for FDCT multiplications. It allows bypassing of small numbers while keeping the segmentation overhead small since there are only two partial products to be added.

### 3.1.2. Truncate Some Least-Significant Bits from Input

Since the IEEE standard [27] defines only the precision requirements for the IDCT, and since the FDCT is usually followed by quantization, in this thesis, some least-significant bits (LSBs) of the FDCT are truncated. Truncating input bits results in less computation, consequently, reduces power consumption and increases the speed. On the other hand, truncation introduces error at the output. Although some error introduced by the truncation will be compensated by the heavy quantization that follows the FDCT module, the error still exist. Thus, truncation allows trade-off between power and error. The goal is to find the *best* strategy to truncate input bits so that the error is in *acceptable* range depending on the application.

In 2-D 8x8 FDCT, there are eight 8-point 1-D FDCT in the first dimension (rows), and eight 8-point 1-D FDCT in the second dimension (columns). Let Trunc(d,n) denote the number of bits to be truncated from the n-th 1-D FDCT of dimension d, where d = 1 (row), 2 (column) and n = 0...7. The truncation for all eight inputs of any 1-D 8-point FDCT is the same. Figure 9 illustrates the detailed view of 2-D row-column FDCT with truncation.

Figure 9: 2-D row-column FDCT with truncation

If we allow truncating at most m bits from each 1-D FDCT, since there are 16 1-D FDCT blocks, there are a total of  $(m+1)^{16}$  possible combinations (including no truncation for m=0). Even when m is small, say m=1, there are still 65536 possibilities to be examined. Fortunately, not all combinations are valid from the distortion point of view.

In practice, since human eyes/ears are less sensitive to high frequency signal components, higher frequency FDCT coefficients (larger n) are quantized more heavily than the lower frequency coefficients. This fact suggests that the effect of truncation in higher frequency FDCT coefficients is less than the lower frequency coefficients. This argument leads to the following equation.

$$Trunc(d,n_1) \leq Trunc(d,n_2) \text{ if } n_1 < n_2 \ (10)$$

Further test cases reduction can be achieved due to the fact that the transpose matrix distributes all coefficients computed in each of the first-dimension FDCT modules

to all second-dimension FDCT modules. Thus, all first-dimension (d=1) FDCT modules are equally important, i.e.:

$$\forall n : Trunc(1, n) = k$$

, where k is a constant (11)

Since the truncation error introduced in the first stage affects entire second stage, to have a more accurate result, k=0 (no truncation at the first dimension FDCT blocks) is used in the design of FDCT.

Figure 10: Test model to measure the effect of truncation

To have a quantitative measure of the truncation effect, standard MPEG-2 encoder is modified as the test model (see Figure 10). By changing the Trunc(2,n), different PSNR values are measured. The PSNR values are then compared against the reference: PSNR of no truncation (Trunc(2,n)=0 for all n). Smaller PSNR difference indicates smaller distortion introduced due to truncation. The truncation error is defined as:

Since the goal is to save power, one combination is better than another if it truncates more bits, but has higher PSNR (smaller truncation error), i.e.

$$\sum_{n=0}^{7} Trunc_{\text{Case 1}}(2, n) > \sum_{n=0}^{7} Trunc_{\text{Case 2}}(2, n), \text{ and } PSNR_{\text{Case 1}} > PSNR_{\text{Case 2}}$$

(7)

Three test video sequences (coke, salesman, and tennis) are used to measure the truncation errors. Each sequence has 180 frames and is encoded using pure I-frames at 8 Mb/s. The FDCT is computed with fixed-point calculation with 11-bit precision after binary points.

To show the effect of truncation, all 165 possible combinations are using m=3 (truncate at most 3 bits) and Trunc(1,n)=0 (no truncation for first-dimension FDCT). The testing results (truncation errors) are shown in Appendix A.

Table 5 illustrates the best truncation patterns and its average truncation error compared to all other truncation patterns with the same total truncated bit. In this thesis, truncation pattern Trunc(1,n)=0 and  $Trunc(2,n)=\{1,1,1,1,1,1,1,1,1\}$  is used in the implementation of the FDCT because its truncation error is moderate (around 0.5 dB).

| Total<br>Truncated Bits | Trunc(7 n) | Truncation Error<br>(dB) | Total<br>Truncated Bits | Trunc(7 n) | Trun cation Error (dB) |

|-------------------------|------------|--------------------------|-------------------------|------------|------------------------|

| 0                       | 00000000   | 0.0000                   | 13                      | 11122222   | 1.5023                 |

| 1                       | 00000001   | 0.0621                   | 14                      | 11222222   | 1.6806                 |

| 2                       | 00000011   | 0.1237                   | 15                      | 1222222    | 1.8576                 |

| 3                       | 00000111   | 0.1831                   | 16                      | 2222222    | 2.0400                 |

| 4                       | 00001111   | 0.2398                   | 17                      | 2222223    | 2.6143                 |

| 5                       | 00011111   | 0.3064                   | 18                      | 2222233    | 3.1380                 |

| 6                       | 00111111   | 0.3721                   | 19                      | 22222333   | 3.5924                 |

| 7                       | 01111111   | 0.4403                   | 20                      | 22223333   | 3.9806                 |

| 8                       | 11111111   | 0.5136                   | 21                      | 22233333   | 4.3642                 |

| 9                       | 11111112   | 0.7327                   | 22                      | 22333333   | 4.7059                 |

| 10                      | 11111122   | 0.9497                   | 23                      | 23333333   | 5.0382                 |

| 11                      | 11111222   | 1.1406                   | 24                      | 33333333   | 5.3550                 |

| 12                      | 11112222   | 1.3161                   |                         |            |                        |

Table 5: Truncation errors against the number of truncated bits

### 3.2. Data-Dependent Loeffler's IDCT Algorithm

Like the FDCT, row-column method is used to compute the 2-D IDCT. Due to the heavy quantization of the encoder (for high compression), a high proportion of the coefficients are expected to be zero at the input of the first-dimension IDCT.

One problem with the Xanthopoulos's data-dependent IDCT designs in [19]-[21] is that they may result in more computation than the fixed-complexity fast algorithms. In the worst case, such as the input does not satisfy the assumed statistical property, the data-dependent design in [19]-[21] may yield as high as 1024 multiplications for 2D IDCT, i.e. degenerates to its base algorithm (direct IDCT computation).

In this work, like the FDCT, zero-bypassing logics are inserted into the IDCT circuit to reduce the number of computation. Since zero-bypassing logic does not increase the number of computation, even at the worst situation, the data-dependent design yields the same complexity as the fundamental Loeffler's algorithm. In other words, in the worst scenario (none of the bypassing logic active), data-dependent Loeffler's 2D IDCT algorithm uses 176 multiplications (2 dimensions x 8 rows (columns)/dimension x 11 multiplication/row (column)).

In real life, some zero-bypassing logics will be active, and the number of multiplications starts to depend on the distribution of input data. For instance, if there is one non-zero coefficients in the input of the 1-D IDCT, data-dependent Loeffler's IDCT algorithm requires 0, 2, 5 or 6 multiplications depending on the position of non-zero input. If the probability of the non-zero input position is the same for all 8 inputs, the algorithm requires only 3.25 multiplications in average. Thus, by applying zero-bypassing logic onto Loeffler's IDCT algorithm, the fixed-complexity algorithm is

transformed into a data-dependent algorithm. The new 2-D IDCT multiplication lower bound is the same as Xanthopoulos' (0), while the upper bound is significantly reduced from 1024 down to 176.

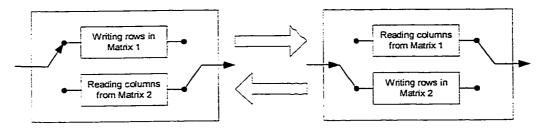

## 3.3. Transpose Memory Architecture

There are various ways to transpose 8×8 matrix in hardware. The trivial way is to have two matrices (as shown in Figure 11). They are used for read and write alternatively (ping-pong buffering). Two matrices are required since the data arrives row-by-row.

Figure 11: Ping-pong transpose memory

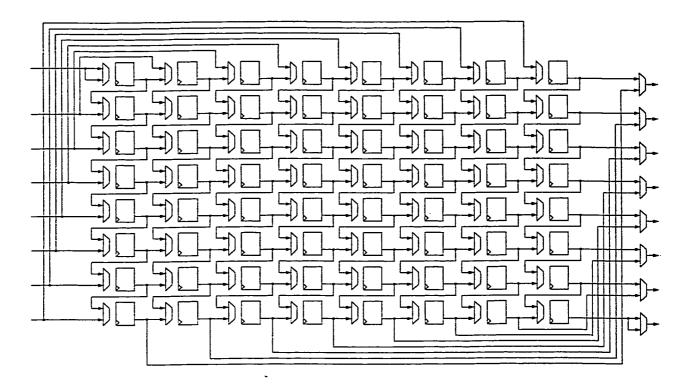

Another way to transpose a matrix is reported in [28]. As shown in Figure 12, only one matrix is required. Data is transposed on the fly by changing the shifting direction (top-to-bottom or left-to-right).

Figure 12: On-the-fly 8×8 Transpose Memory [28]

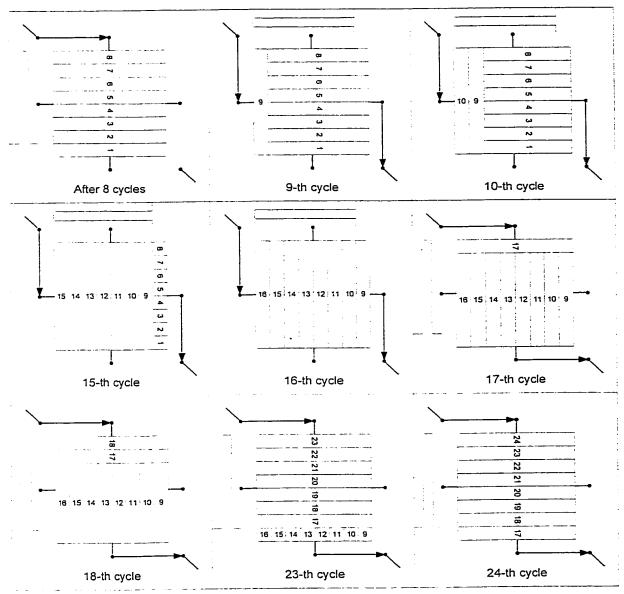

The state of the transposition matrix for clock cycles is illustrated in Figure 13. To fill up the matrix, from clock cycle 1 to 8, shifting direction is top-to-bottom. From clock cycle 9 to 16, the shifting direction is left-to-right. From clock cycle 17 to 24, the shifting direction is top-to-bottom. Clock cycle 25 is identical to clock cycle 9, and so on.

Figure 13: States of the transpose matrix for different clock cycles

Since n-bit element 8×8 matrix is built with 64n flip-flops, if n is large, the area consumption will also be large. In the proposed FDCT/IDCT design, the on-the-fly transposition architecture is used since it requires only 64n flip-flops instead of 128n flip-flops in the ping-pong case.

### 3.4. Chapter Summary

In this chapter, data-dependent Loeffler FDCT/IDCT algorithms are described. The zero-bypassing logic is inserted into fixed-complexity Loeffler's algorithm to convert it into a data-dependent algorithm, which the new design is based on. For FDCT, input truncation technique was also analyzed and applied to further reduce the amount of data to be processed, hence reduce the power consumption. Based on the simulation result, we decided to truncate one bit from the input of the second dimension FDCT.

The transpose memory architecture has also been studied. The on-the-fly transpose memory reported in [28] is chosen because it requires only half the amount of area comparing to the ping-pong architecture.

Since multiplier is the fundamental building block of FDCT/IDCT, in the next chapter, different multiplier architectures are analyzed based on low-power criteria.

## Chapter 4

## **Multiplier Architectures**

In VLSI implementation, floating-point multipliers are much larger, slower, and consume more power than fixed-point multipliers due to normalization of mantissa. For this reason, all FDCT/IDCT designs reviewed in this thesis used fixed-point multiplication instead of floating-point multiplication.

Since fixed-point or integer multipliers are larger, slower, and consume more power than adders, the choice of multiplier greatly affects the overall FDCT/IDCT performance and power consumption.

One special note about the multiplications performed in FDCT/IDCT is that they are all constant multiplications, i.e. one of the multiplicand is a constant. In Section 4.1, several constant multiplication schemes are studied, and the hardwired CSD multiplier is chosen for low-power design. Section 4.2 describes the design procedure of the hardwired CSD multipliers. In Section 4.3, synthesis is performed, and the result indicates that the CSD multipliers indeed consume less power than general-purpose multipliers.

## 4.1. Survey of Constant Multiplication Schemes

Following is a brief description of the characteristics of different constant multipliers. More detailed description can be found in the references.

#### 4.1.1. Modified Booth Multiplier

Modified Booth multiplier [35] is a popular general-purpose multiplier. Both of its multiplicands are variables that can be changed at run-time. However, in DCT/IDCT multiplications, only one of the multiplicand is variable, the other one is a constant  $(\cos(n\pi/16))$ . Having both operands of multiplier variable implies more hardware, consequently more power. Thus, general-purpose modified Booth multiplier is not a good choice for low-power DCT/IDCT design.

#### 4.1.2. Distributed Arithmetic (DA)

Distributed arithmetic (DA) is a bit-serial operation that performs shift-and-add operation to multiply two numbers (one of which is a constant). It replaces the multiplication with additions and a look up ROM table [14]. The input is used as index in the ROM, and the ROM contains the partial product of multiplying the address with the constant multiplicand, and the partial products are then added by using shift-and-add operations.

The main disadvantage of DA is that it is slow due to its bit-serial nature and parallel-serial/serial-parallel conversion. This implies that it needs higher internal clock frequency than parallel processing to do the same work. Moreover, shifting consumes much power because of the high switching activities. In [14] and [15], the authors evaluated the trade-off between the performance and the power for three multiplication schemes: general-purpose multiplier, pure ROM based, and mixed ROM based (DA).

|                | Mult          | iplier     | Pure          | ROM        | Mixed         | ROM        |

|----------------|---------------|------------|---------------|------------|---------------|------------|

| Voltage<br>(V) | Delay<br>(ns) | Power (mW) | Delay<br>(ns) | Power (mW) | Delay<br>(ns) | Power (mW) |

| 5              | 101.56        | 13.49      | 86.5          | 30.4       | 79.5          | 30.1       |

| 4              | 132.27        | 7.64       | 111.4         | 18.6       | 103.7         | 18.1       |

| 3.3            | 162.53        | 4.99       | 137.1         | 10.5       | 129.1         | 11.0       |

Table 6: Comparison of general-purpose multiplication against ROM based multiplication [14]

As shown in Table 6, the multiplier-based implementation is slower than the DA-based implementations. However, the power is about 30-50% less than the DA-implementations because about 85% of the entire DA chip runs at higher frequency due to its bit-serial nature. As the result, DA is not a good choice for low-power design.

# 4.1.3. Hardwired Canonical-Sign-Digit (CSD) Wallace-Tree Multiplier

Hardwired multipliers hard code the constant multiplicand by using only shift-and-add operations. Unlike DA, which performs shift-and-add operation at run-time, these shifts are hard-wired at design time and consume no power. In other words, hardwired multipliers are simply Wallace-tree carry-save adders. This results in a smaller and more power-efficient multiplier than general-purpose multiplier.

Further power reduction can be achieved on the fixed multiplicand by not using 2's complement representation, but using radix-2 canonical sign-digit (CSD) representation. By definition, the *canonical* sign-digit representation is a redundant number system that represents number with *no adjacent non-zero digits*. Every number has a unique CSD representation [30]. It represents numbers with fewer or equal non-zero digits [4] as the algebraic sum/subtraction of several power-of-two, i.e.:

$$c = \sum s_k 2^{-k}$$

, where  $s_k \in \{-1,0,1\}$

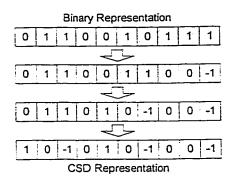

A procedure to transform a conventional binary number to CSD representation is described in [30]. We have also derived a more intuitive transformation algorithm:

Given a (n+1)-digit binary number  $\mathbf{B} = B_n B_{n-1} \dots B_l B_0$  with  $B_n = 0$  and  $B_i \in \{0,1\}$  for  $i \in [0,n-1]$ . The following procedure converts  $\mathbf{B}$  into the (n+1)-digit radix-2 canonical SD vector  $\mathbf{D} = D_n D_{n-1} \dots D_l D_0$  with  $D_n \in \{0,1\}$  and  $D_i \in \{0,1,-1\}$  for  $i \in [0,n-1]$  such that both vector  $\mathbf{D}$  and  $\mathbf{B}$  represent the same value:

$$\alpha = \sum_{i=0}^{n} B_{i} 2^{i} = \sum_{i=0}^{n} D_{i} 2^{i}$$

- 1. If there are consecutive 1's in **B**, continue to step 2. Otherwise, the resulting number **B** is in CSD representation (**D**). End the process.

- 2. Replace the rightmost (starting from the lowest order  $2^i$  end) occurrence of bit pattern 0  $\underbrace{1...1}_{(m-1)1's}$  1 with 1  $\underbrace{0...0}_{(m-1)0's}$  -1. This replacement is possible because

$$\sum_{i=m}^{n} 2^{i} = 2^{n+1} - 2^{m}, \text{ where } n > m$$

3. Go back to step 1.

Figure 14 shows a step-by-step example that converts a binary number  $0110010111_b$  ( $407_d$  in decimal) into CSD representation. The consecutive 1's to be replaced are shaded in the figure. The resulting CSD representation of  $407_d$  is  $10\overline{1}010\overline{1}00\overline{1}$ , where  $\overline{1}$  denotes -1. As expected,  $407 = 2^9 - 2^7 + 2^5 - 2^3 - 2^0$ . In this example, the CSD representation reduces the number of 1's from 6 down to 5.

Figure 14: Converting binary number 0110010111 into CSD representation

As another example, Table 7 shows the CSD representations of the constant operands  $(\cos(n\pi/16))$  used in FDCT/IDCT with 15-bit precision after binary point (total of 16 bits).

|   |                                  | cos(nπ/16) |                                  |             |        |  |  |

|---|----------------------------------|------------|----------------------------------|-------------|--------|--|--|

|   | Traditional Binary Represe       | entation   | Canonical Sign-digit Re          | presentatio | n      |  |  |

| n | Bit Pattern                      | # Non-     | Bit Pattern                      | # Non-      | % Bit  |  |  |

|   | $(2^{0},2^{-1},2^{-2},,2^{-15})$ | Zero Bits  | $(2^{0},2^{-1},2^{-2},,2^{-15})$ | Zero Bits   | Saving |  |  |

| I | 0111110110001010                 | 9          | 100000-10-10001010               | . 5         | 44%    |  |  |

| 2 | 0111011001000010                 | 7          | 1000-10-1001000010               | 5           | 29%    |  |  |

| 3 | 0110101001101110                 | 9          | 10-101010100-100-10              | 7           | 22%    |  |  |

| 4 | 0101101010000010                 | 6          | 10-10-101010000010               | 6           | 0%     |  |  |

| 5 | 0100011100011101                 | 8          | 0100100-100100-101               | 6           | 25%    |  |  |

| 6 | 0011000011111100                 | 8          | 010-1000100000-100               | 4           | 50%    |  |  |

| 7 | 0001100011111001                 | 8          | 0010-10010000-1001               | 5           | 38%    |  |  |

Table 7: Canonical sign-digit representation of  $cos(n\pi/16)$

As shown in Table 7, the CSD representation can reduce the number of non-zero bits up to 50% over traditional representation. In hardwired-multiplier, each non-zero digit (except the first 3 non-zero digits) in the constant multiplicand requires one extra carry-save adder stage.

Because canonical means no adjacent non-zero digits, any n-bit number can be represented with at most  $\lceil n/2 \rceil$  number of non-zero digits, which in turn reduces at least half of the carry-save adder stages comparing to general purpose array multiplier. It can also be shown that CSD generates an average of n/3 additions [40]. Since fewer non-zero

bits imply less computation, less switching activity, and less power consumption, the hardwired CSD multiplier is a good choice for low-power design.

#### 4.1.4. Pattern-Based CSD Multiplier

The CSD representation uses minimum shift-and-add (S&A) operations when multiplying constant k with variable x directly. However, direct multiplication of  $x \times k$  does not necessarily use minimum S&A operations to perform  $x \times k$ . In some situations, it is possible to find patterns inside the CSD representation, which can be reused to avoid repeated computation. Thus, instead multiplying x with k directly, x is multiplied with sub-expressions of k, then partial products are used to construct the final product. As an example, let  $k = 11100111 = 100\overline{10}100\overline{1}$  (231<sub>d</sub>). Using CSD representation without pattern searching, 231x requires 4 additions. However, with pattern-based algorithm, 231x can be represented by (7x << 5) + 7x, which requires 3 additions only. The Bernstein's algorithm [41], Lefèvre's algorithms [39-40], and Potkonjack algorithm [42] are pattern-based algorithms.

The pattern-based algorithms are very useful for multiplication with very large constants where the patterns can be reused frequently. For example, in encryption/decryption, the constant may have several hundreds or thousands of bits. In such situation, pattern-based algorithm can reduces the computation significantly. However, for the purpose of FDCT/IDCT and most DSP applications, the constants word lengths are usually small, and patterns (if any) are reused less frequently.

For pattern reuse, one must obtain the entire partial product, which requires using carry-save-adder (CSA) followed by carry-propagate adder (CPA). In general, in VLSI

implementation, CPA is slower, and consumes more power than CSA due to carry propagation. The slower pattern-based algorithm speed can be compensated by adding pipeline registers after each CSA used for partial product (pattern) computation. The extra power consumption due to the carry propagation in CPA can be reduced by using other types of adders such as carry-bypass adders or carry-select adders. However, given the patterns are not reused frequently, the overall power consumption of pattern-based multiplier is still larger than the one without using pattern. Since the design criterion of this thesis is power, only the CSD multiplication without using pattern is considered, and all multipliers used in FDC/IDCT are hardwired CSD multipliers.

Notice that the application of hardwired CSD Wallace-tree multiplier is not restricted to FDCT/IDCT only. It can be used in many other digital signal processing (DSP) applications, such as digital filters, where fixed-coefficient multiplication is required.

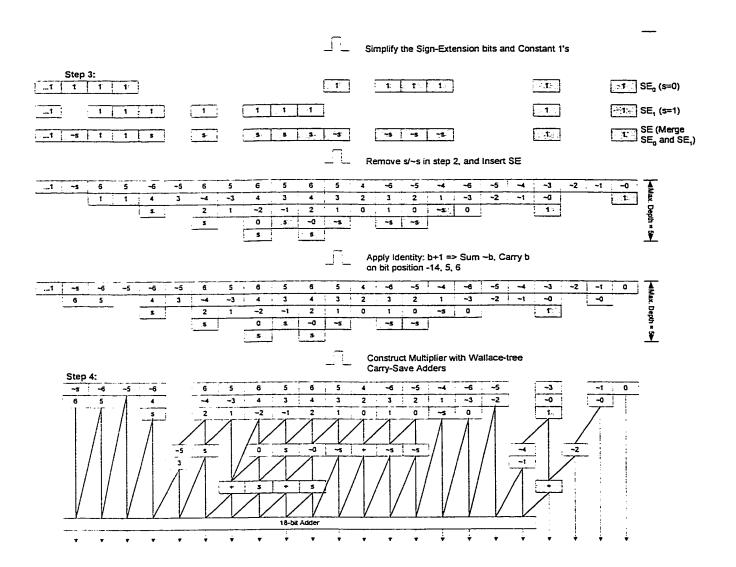

# 4.2. CSD Multiplier Implementation Procedure

To design a hardwired CSD multiplier for multiplying unsigned variable integer operand (v) with a constant operand, we derived the following steps:

- 1. Obtain the CSD representation of the constant operand by using the algorithm described in Section 4.1.3.

- 2. For each non-zero bit position p in constant operand:

- For each 1 in the constant operand, place the unsigned variable operand, i.e. performing  $v \times 2^{r}$ .

- For each -1 in the constant operand, negate the unsigned variable operand with a 1 placed at the least-significant bit (2's complement), and extend 1's to the left of the most-significant bit (sign extension) of the variable operand, i.e. performing  $(-v) \times 2^p$

- 3. Simplify the diagram by adding the constant 1's together to avoid redundant computation at run time. By studying the truth-table of addition, we found that further optimization can be achieved by using identity I.1:

Identity I.1: Variable bit b plus constant 1 results in sum  $\sim b$  and carry b, where  $\sim b$  denotes NOT operation

|             | b+1  |           |  |

|-------------|------|-----------|--|

| В           | Sum  | Carry     |  |

| 0           | 1    | 0         |  |

| 1           | 0 _  | <u> 1</u> |  |

| Sum=b, Carr | y=~b |           |  |

Table 8: Truth-table of b+1

This identity allows reduction of one operand to be added for position p by increasing the number of operands to be added for position p+1 by 1. Intelligent use of this identity can reduce the number of carry-save adder (CSA) stages (critical path delay) without introducing any extra hardware.

4. Combine the operands placed in step 2 and the simplified constant 1's (in step 3) with carry-save adders in Wallace-tree form. The result of the carry-propagate adder is the result of multiplying variable input operand with the constant operand.

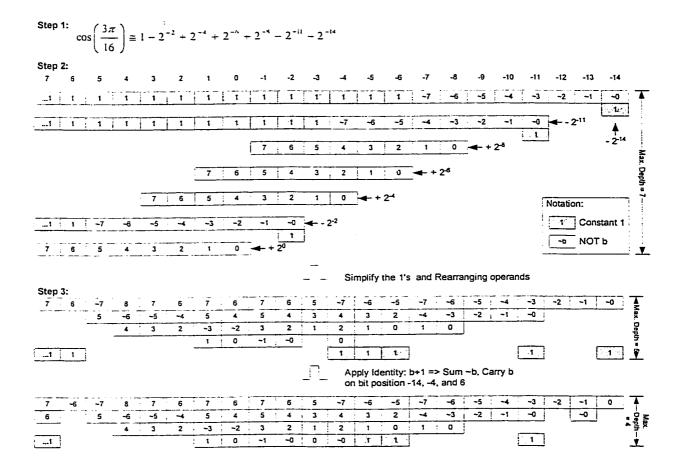

To illustrate the above algorithm, Figure 15 shows the procedure of constructing a CSD hardwired-multiplier of constant  $\cos(3\pi/16)$  multiplying with an 8-bit unsigned

integer. Constant  $\cos(3\pi/16)$  is chosen because it contains the most non-zero bits in the Table 7. As shown in Figure 15, in step 3, the application of identity I.1 reduces the depth of CSA tree from 7 down to 4. As the result, the multiplication of  $\cos(3\pi/16)$  with an 8-bit unsigned number has critical path of only 2 full-adder stages with a 19-bit CPA adder. Notice that despite the fact that the multiplier uses CSD representation for the constant operand, both the variable operand and the product are still in 2's complement representation.

Figure 15: Hardwired CSD multiplier for multiplying  $\cos(3\pi/16)$  with 8-bit unsigned integer

Similarly, to multiply a signed 2's complement variable operand (v) having a sign-bit (s) with a constant operand, the following procedure is derived:

- 1. Obtain the CSD representation of the constant operand.

- 2. For each non-zero bit position *p* in constant operand:

- For each 1 in the constant operand, place the signed variable operand, i.e. performing  $v \times 2^p$ . Sign-extend towards left.

- For each -1 in the constant operand, negate the signed variable operand v with a 1 placed at the least-significant bit (2's complement), and extend  $\sim s$  (negated sign-bit s) to the left of the most-significant bit (sign extension) of the variable operand, i.e. performing  $(-v) \times 2^p$

- 3. Simplify the sign extension bits and constant 1's in the diagram:

- Let s=0, replace all s with 0, and  $\sim s$  with 1, add all constant 1's together, and obtain a constant value  $SE_0$ .

- Le s=1, replace all s with 1, and  $\sim s$  with 0, add all constant 1's together, and obtain a constant value  $SE_{I}$ .

• For each bit at position p, merge  $SE_{\theta}$  and  $SE_{l}$  together to obtain another value SE using the following truth table:

| $SE_0$ (s=0) | $SE_{I}$ (s=1) | SE |

|--------------|----------------|----|

| 0            | 0              | 0  |

| 0            | 1              | S  |

| 1            | 0              | ~s |

| 1            | 1              | 1  |

Table 9: Truth table to simplify sign-extension

- Remove all sign extension bit (s or  $\sim$ s), insert SE into the diagram.

- Like the unsigned case, apply identity I.1 where suitable.

- 4. Combine the operands placed in step 2 and the simplified sign-extension bits and constant 1's (in step 3) with carry-save adders in Wallace tree form. The result of the carry-propagate adder is the result of multiplying variable signed 2's complement input operand with the constant operand.

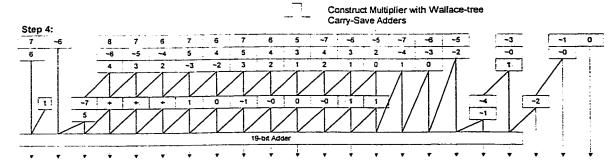

Like the unsigned case, step-by-step illustration of construction of a CSD hardwired-multiplier of constant operand  $\cos(3\pi/16)$  multiplying with an 8-bit signed 2's complement integer is shown in Figure 16.

Figure 16: Hardwired CSD multiplier for multiplying  $\cos(3\pi/16)$  with 8-bit signed integer

### 4.3. Multiplier Synthesis Result

To demonstrate that the hardwired CSD Wallace-tree constant multiplier consumes less power and area while offering comparable speed performance, its delay,

area, and power consumption figures are compared with the with other 32-bit popular general-purpose multipliers.

Since the hardwired CSD multiplier has one operand constant, several CSD multipliers are implemented with different constant operand used in FDCT/IDCT ( $\cos(n\pi/16)$ , and  $2^{\pm 1/2}$ ). All constants have 1-bit integer part and 31-bit fraction part to form a 32-bit fixed-point number. The constants are then multiplied with a 32-bit signed integer (variable operand). All multipliers are synthesized using Xilinx 4052XL-1 FPGA technology.

| 32-bit<br>Multipliers | Array<br>Multiplier | Modified<br>Booth<br>Multiplier | Wallace<br>Tree<br>Multiplier | Modified<br>Booth-<br>Wallace Tree<br>Multiplier | Proposed<br>Scheme |

|-----------------------|---------------------|---------------------------------|-------------------------------|--------------------------------------------------|--------------------|

| Area (CLB)            | 1165                | 1292                            | 1659                          | 1239                                             | 493                |

| Delay (ns)            | 187.87              | 139.41                          | 101.14                        | 101.43                                           | 106.21             |

| Power (mW)            | 16.651              | 23.14                           | 30.95                         | 30.86                                            | 7:67               |

Table 10: Comparison of 32-bit CSD Wallace-tree multiplier with 4 different general-purpose multipliers using Xilinx 4052XL-1 FPGA technology (Columns 1-5 adopted from Table 1 in [36])

As shown in Table 10, the CSD multiplier uses least amount of area and power (less than half of the power than the array multiplier) while offering comparable speed performance with the other multipliers (around 100 ns). This result agrees with the analysis – hardwired CSD is more power efficient then other general-purpose multipliers. Therefore, hardwired CSD Wallace-tree multipliers are used in the FDCT/IDCT designs presented in this thesis.

### 4.4. Chapter Summary

In this chapter, by analyzing different constant multiplication schemes, a new constant-coefficient multiplier design is presented. The multiplier is based on canonical sign-digit representation with Wallace-tree formation. As shown in the analysis and simulation, the CSD multiplier is both more power and area efficient than general-purpose multiplier while offering similar speed performance. Consequently, it is used in the FDCT/IDCT design presented in this work. Detailed design procedures for both unsigned and signed integer are also described.

In the next chapter, more implementation details, such as design automation and pipeline design, are presented.

# Chapter 5

### **Implementation**

Since the main efforts are concentrated on the arithmetic level (data-dependent algorithm) and implementation level (hardwired CSD multipliers), we decide to use VHDL to implement the FDCT/IDCT designs. No optimization on the circuit level or technology level is made.

To ensure error-free coding, some design automation effort is made. In Section 5.1, a C++ program that generates VHDL code of hardwired CSD Wallace-tree multiplier is developed. Similarly, to make the IDCT design compliant to IEEE Std. 1180-1990, in Section 5.2, a Java program is developed that calculates the error figures defined in IEEE standard [27] for different internal bandwidths. The pipeline designs for both the FDCT and IDCT are also described in this Chapter (Section 5.3).

### 5.1. Hardwired CSD Multiplier Generator

Since the FDCT/IDCT design uses hardwired CSD multiplier, for each constant operand and bandwidth of variable operand, different multipliers are required. To save the design time and avoid bugs in the coding, it is ideal to generate constant multipliers through a code generator.

Several constant multipliers generators [40][43-44] have been reported in the literature. All of them are optimized for Xilinx FPGA 4000 and Virtex technologies. To

have a technology-independent constant multiplier generator, a C++ program that generates VHDL code for hardwired CSD multiplier is developed. The program is called constant multiplier generator (CMG). The C++ source code of the generator is listed in Appendix C and in attached CD.

The CMG is capable of generating VHDL code that multiplies signed/unsigned variable operand with any positive integer constant multiplicand. The constant operand can have the size of long type in C++ language. The CMG takes the following information from the user:

- VHDL entity name.

- Integer value of the constant operand: For real number constant operand, use the integer value of the corresponding fixed-point representation. For Intel Pentium® processors running Microsoft Windows® 32, the limitation of the constant operand is from 0 to 2147483647.

- Variable operand: Number of bit of the signed/unsigned variable operand.

- Product Least-Significant-Bit Truncation: This feature is useful for real number (fixed-point) multiplications. In many situations, not all bits in the real part are required. Truncating some least-significant bits from the product results in a smaller, faster, and more power-efficient multiplier. The truncation error has been analyzed in [45].

The generator uses the algorithm described in Section 4.2 to generate VHDL code. At the end of the code generation, it also reports critical statistical information: number of carry-save adder stages, number of inverters, half adders, and full adders. This information is useful for power, area, speed, and pipelining analysis.

As an example, for constant operand  $\cos(3\pi/16)$  with 15-bit precision multiplied with 12-bit variable operand and no truncation, the CMG generates the VHDL code shown in Appendix B.

### 5.2. IEEE Standard 1180-1990 IDCT Compliant