Copyright by

Long Chen

2016

## The Dissertation Committee for Long Chen certifies that this is the approved version of the following dissertation:

# Design Techniques for Low-power SAR ADCs in Nano-scale CMOS Technologies

| Committee:          |  |

|---------------------|--|

|                     |  |

| Nan Sun, Supervisor |  |

| T. R. Viswanathan   |  |

| David Z. Pan        |  |

| Michael Orshansky   |  |

| Eric Soenen         |  |

# Design Techniques for Low-power SAR ADCs in Nano-scale CMOS Technologies

by

Long Chen, B.S.; M.S.E.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

May 2016

### Acknowledgments

First and most importantly, I would like to express my most sincere gratitude to my supervisor, Dr. Nan Sun. Without his insightful guidance and continuous support, I would have never accomplished my research work and thesis. I have been benefited a lot from his vision and perception. I would also like to thank my committee members, Dr. T. R. Viswanathan, Dr. David Z. Pan, Dr. Michael Orshansky, and Dr. Eric Soenen, for their valuable advice and discussions. I am truly grateful to Dr. Eric Soenen for providing me an opportunity to intern in TSMC Austin. It was a wonderful experience to work there in 2015. I have been honored and thankful to many excellent labmates in Sun research group: Kareem Ragab, Arindam Sanyal, Yeonam Yoon, Wenjuan Guo, Ji Ma, Peijun Wang, Matther Schueler, Xiyuan Tang, Sungjin Hong, Shaolan Li, Manzur Rahman, Miguel Gandara, Jeonggoo Song, and Haoyu Zhuang. Special thanks to Arindam Sanyal, Kareem Ragab, Xiyuan Tang, Ji Ma, Yeonam Yoon, Manzur Rahman and Matther Schueler for their collaboration in my research. Thanks to Wei-Gi Ho for his insightful technical discussions. I would also like to thank my friends in Austin for making my life more fun. I am greatly indebted to my parents for their selfless support and care. Last but not the least, I am truly fortunate to have my wife Pingshuai Cao in my life. There is no way I can reach this point without her support, faith and love.

**Design Techniques for Low-power SAR ADCs in Nano-scale**

**CMOS Technologies**

Long Chen, Ph.D.

The University of Texas at Austin, 2016

Supervisor: Nan Sun

This thesis presents low power design techniques for successive approxi-

mation register (SAR) analog-to-digital converters (ADCs) in nano-scale CMOS

technologies. Low power SAR ADCs face two major challenges especially at high

resolutions: (1) increased comparator power to suppress the noise, and (2) increased

DAC switching energy due to the large DAC size. To improve the comparator's

power efficiency, a statistical estimation based comparator noise reduction tech-

nique is presented. It allows a low power and noisy comparator to achieve high

signal-to-noise ratio (SNR) by estimating the conversion residue. A first prototype

ADC in 65nm CMOS has been developed to validate the proposed noise reduc-

tion technique. It achieves 4.5 fJ/conv-step Walden figure of merit and 64.5 dB

signal-to-noise and distortion ratio (SNDR). In addition, a bidirectional single-side

switching technique is developed to reduce the DAC switching power. It can reduce

the DAC switching power and the total number of unit capacitors by 86% and 75%,

respectively. A second prototype ADC with the proposed switching technique is

vi

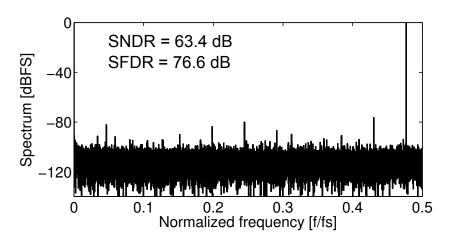

designed and fabricated in 180nm CMOS technology. It achieves an SNDR of 63.4 dB and consumes only 24  $\mu$ W at 1MS/s, leading to a Walden figure of merit of 19.9 fJ/conv-step.

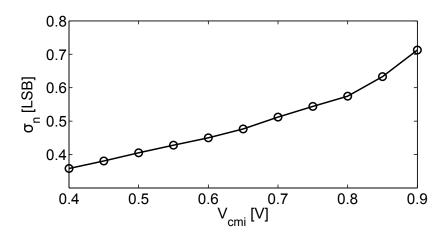

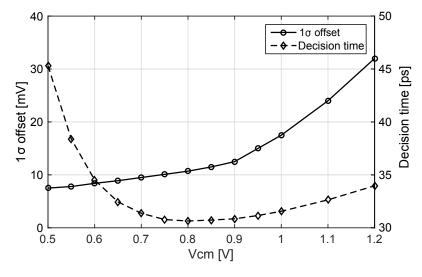

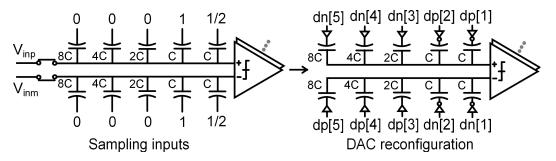

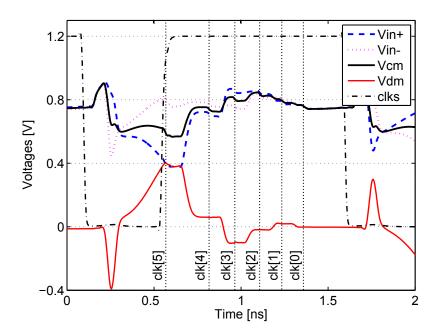

This thesis also presents an improved loop-unrolled SAR ADC, which works at high frequency with reduced SAR logic power and delay. It employs the bidirectional single-side switching technique to reduce the comparator common-mode voltage variation. In addition, it uses a  $V_{cm}$ -adaptive offset calibration technique which can accurately calibrate comparator's offset at its operating  $V_{cm}$ . A prototype ADC designed in 40nm CMOS achieves 35 dB at 700 MS/s sampling rate and consumes only 0.95 mW, leading to a Walden figure of merit of 30 fJ/conv-step.

## **Table of Contents**

| Acknov  | vledgn | nents                                                                                | V  |

|---------|--------|--------------------------------------------------------------------------------------|----|

| Abstrac | ct     |                                                                                      | vi |

| List of | Tables |                                                                                      | X  |

| List of | Figure | s                                                                                    | xi |

| Chapte  | r 1. I | ntroduction                                                                          | 1  |

| 1.1     | Mo     | tivation                                                                             | 1  |

| 1.2     | Org    | ganization                                                                           | 4  |

| Chapte  | r 2. S | Statistical Estimation Based Noise Reduction                                         | 6  |

| 2.1     | Inti   | roduction                                                                            | 7  |

| 2.2     |        | posed Statistical Estimation Based Noise Reduction Technique: sic Idea               | 12 |

| 2.3     |        | posed Statistical Estimation Based Noise Reduction Technique: thematical Formulation | 15 |

|         | 2.3.1  | Estimator based on averaging                                                         | 17 |

|         | 2.3.2  | Maximum likelihood estimator (MLE)                                                   | 18 |

|         | 2.3.3  | Bayes estimator                                                                      | 22 |

|         | 2.3.4  | Estimator performance comparison                                                     | 26 |

|         | 2.3.5  | Comparison to oversampling and analog scaling                                        | 29 |

| 2.4     | Pro    | totype ADC Design                                                                    | 31 |

|         | 2.4.1  | Detailed circuit schematics                                                          | 31 |

|         | 2.4.2  | Measurement Results                                                                  | 36 |

| Chapte  | r 3. Bi  | directional Single-side Switching Technique       | 43  |

|---------|----------|---------------------------------------------------|-----|

| 3.1     | Intro    | duction                                           | 44  |

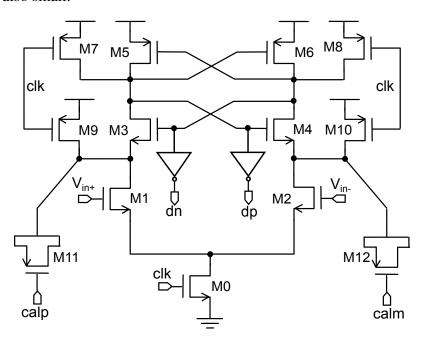

| 3.2     | Effec    | et of Comparator Common-Mode Variation            | 47  |

| 3.3     | Prop     | osed BSS switching technique                      | 54  |

|         | 3.3.1    | Comparator input common-mode variation reduction  | 54  |

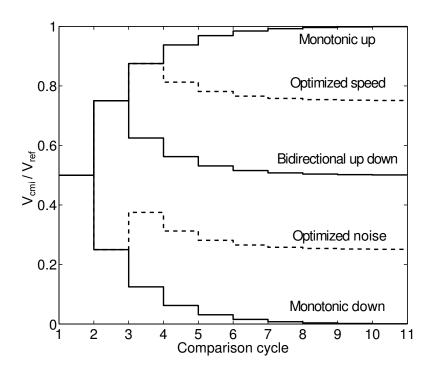

|         | 3.3.2    | Comparator input common-mode voltage optimization | 58  |

|         | 3.3.3    | Capacitance reduction                             | 60  |

|         | 3.3.4    | Reduced DAC reference energy                      | 60  |

| 3.4     | Proto    | otype ADC Design                                  | 62  |

|         | 3.4.1    | Detailed circuit schematics                       | 62  |

|         | 3.4.2    | Measurement Results                               | 66  |

| Chapte  | r 4. Lo  | w-power and High-speed Single-channel SAR ADC     | 73  |

| 4.1     | Intro    | duction                                           | 74  |

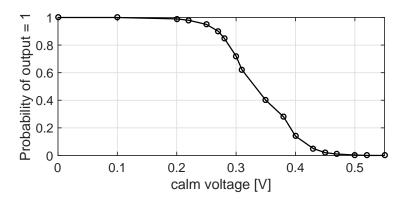

| 4.2     | Prop     | osed SAR ADC Architecture                         | 76  |

| 4.3     | Proto    | otype ADC Design                                  | 79  |

|         | 4.3.1    | Detailed circuit schematics                       | 79  |

|         | 4.3.2    | Measurement results                               | 85  |

| Chapte  | r 5. Co  | onclusion and Future Directions                   | 91  |

| 5.1     | Conc     | lusion                                            | 91  |

| 5.2     | Futui    | re Directions                                     | 92  |

| Append  | lix      |                                                   | 94  |

| Append  | lix 1. I | ist of publications                               | 95  |

| Bibliog | raphy    |                                                   | 97  |

| Vita    |          |                                                   | 104 |

## **List of Tables**

| 2.1 | Measured performance summary | 42 |

|-----|------------------------------|----|

|     | Measured performance summary |    |

| 3.2 | Performance comparison       | 72 |

| 4 1 | Performance comparison       | 90 |

## **List of Figures**

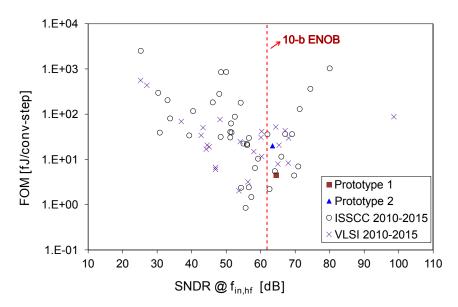

| 1.1  | FOM versus SNDR plot for recently published SAR ADCs in ISSCC and VLSI conferences                                                                                              | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

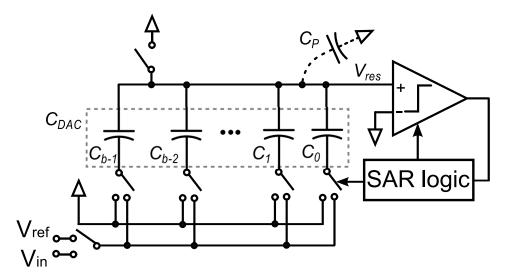

| 2.1  | Diagram for a <i>b</i> -bit SAR ADC                                                                                                                                             | 13 |

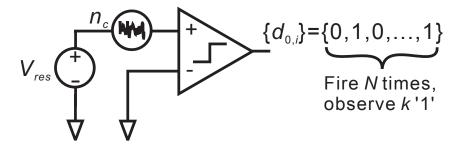

| 2.2  | Simplified SAR ADC model during the LSB comparison                                                                                                                              | 16 |

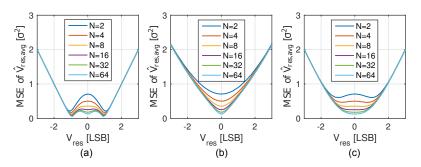

| 2.3  | MSE of $\hat{V}_{res,avg}$ for various $N$ and (a) $\sigma=0.5$ LSB, (b) $\sigma=2$ LSB, and (c) $\sigma=1$ LSB                                                                 | 17 |

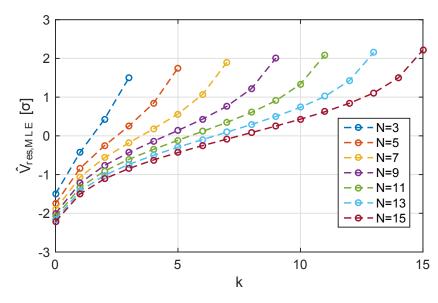

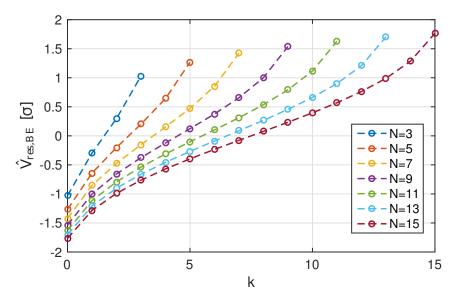

| 2.4  | Value of $\hat{V}_{res,MLE}$ as a function of $N$ and $k$                                                                                                                       | 22 |

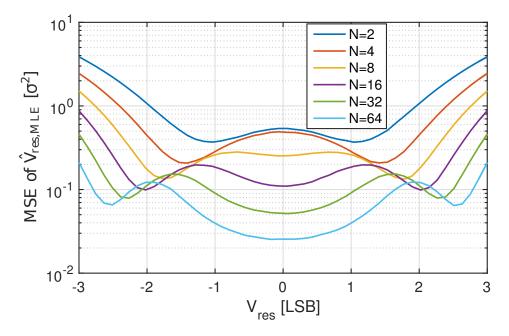

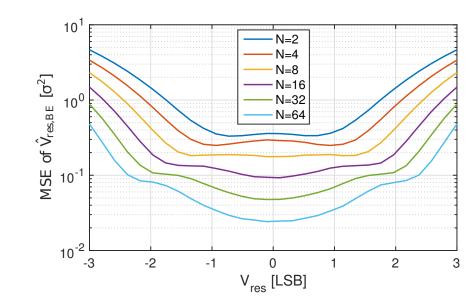

| 2.5  | MSE of $\hat{V}_{res,MLE}$ for different $V_{res}$                                                                                                                              | 23 |

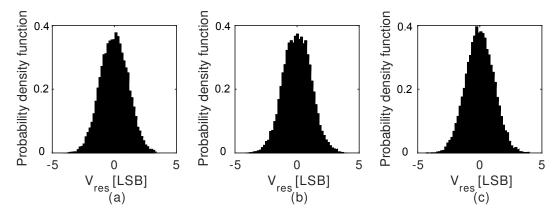

| 2.6  | Histogram of $V_{res}$ for (a) a $-6$ -dBFS sinusoidal input, (b) a $-20$ -dBFS sinusoidal input, and (c) a Gaussian random input with standard deviation of 10% ADC full range | 24 |

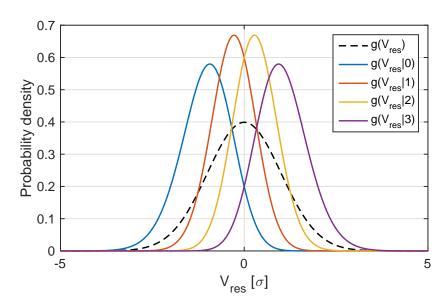

| 2.7  | Prior distribution $g(V_{res})$ and posterior distribution $g(V_{res} k)$ for $N=3.\ldots\ldots\ldots$                                                                          | 25 |

| 2.8  | $\hat{V}_{res,BE}$ as a function of $N$ and $k$                                                                                                                                 | 27 |

| 2.9  | MSE versus $x$ for $\hat{V}_{res,BE}$                                                                                                                                           | 27 |

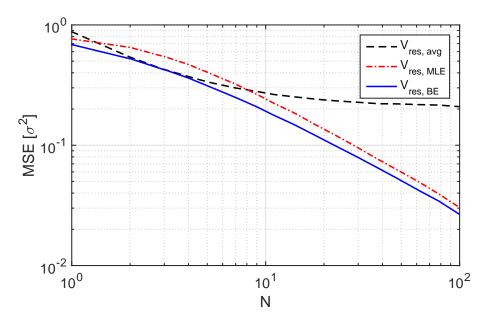

| 2.10 | MSE versus $N$ for a normal distributed $x$ with $\sigma=1$ LSB                                                                                                                 | 28 |

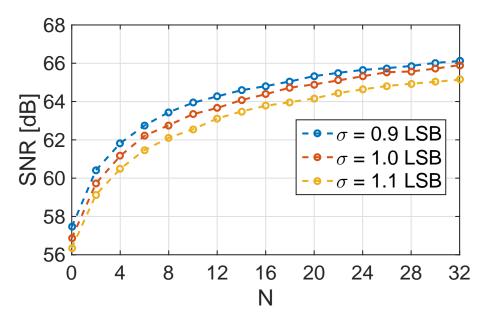

| 2.11 | Simulated SNR versus $N$ with $\pm 10\%$ variations in the comparator noise $\sigma$                                                                                            | 30 |

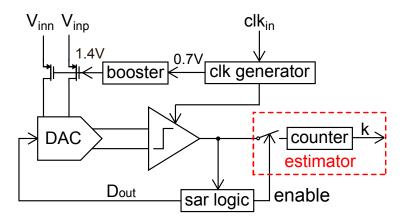

| 2.12 | Proposed SAR ADC architecture                                                                                                                                                   | 32 |

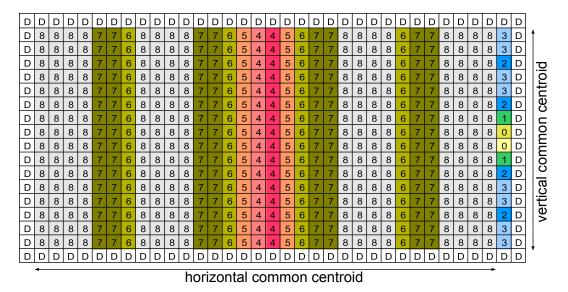

| 2.13 | DAC capacitor array floor plan                                                                                                                                                  | 33 |

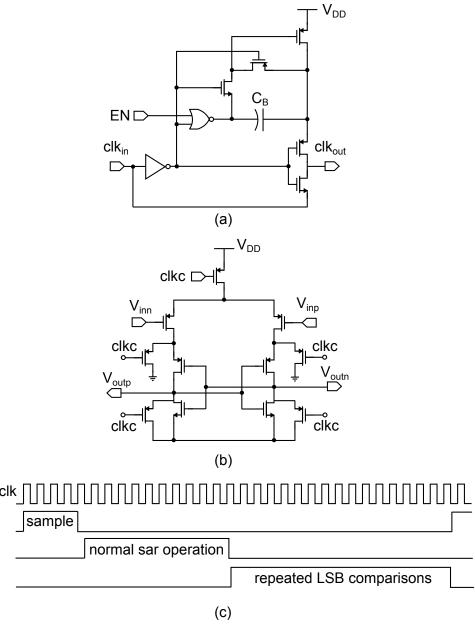

| 2.14 | Schematic of (a) the clock booster; (b) the comparator; and (c) the timing diagram                                                                                              | 34 |

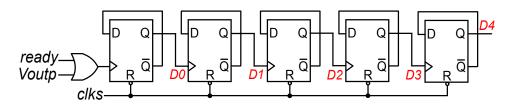

| 2.15 | 5-bit counter to count $k$                                                                                                                                                      | 35 |

| 2.16 | Die micrograph                                                                                                                                                                  | 36 |

| 2.17 | Measured DNL and INL                                                                                                                                                            | 37 |

| 2.18 | $D_{out}$ distribution with and w/o estimation at $V_{in}=0.$                                                                                                                   | 38 |

| 2.19 | Measured $2^{14}$ -point ADC output spectrum with 96-kHz input                                                                                                                  | 39 |

| 2.20 | Measured SNR versus input amplitudes                                                                                                                                            | 40 |

| 2.21 | Measured SNR improvement versus various comparator noise $\sigma$                                                                                                                       | 41 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.22 | FOM versus SNDR plot for this work and recently published ADCs in ISSCC and VLSI conferences                                                                                            | 42 |

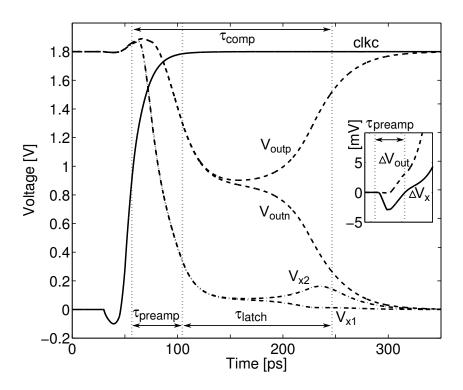

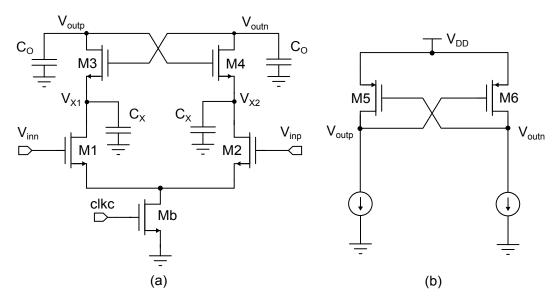

| 3.1  | Schematic of a strong-arm latch comparator                                                                                                                                              | 48 |

| 3.2  | Transient behavior of a strong-arm latch comparator                                                                                                                                     | 49 |

| 3.3  | Comparator schematic for (a) the pre-amplification phase and (b) the latch regeneration phase                                                                                           | 50 |

| 3.4  | Simulated comparator performance: (a) $G$ and $g_m/I_D$ ; (b) noise and offset; (c) linear fitting for noise and offset with $1/G^2$ ; (d) resolve time; (e) power and (f) $FOM_{comp}$ | 53 |

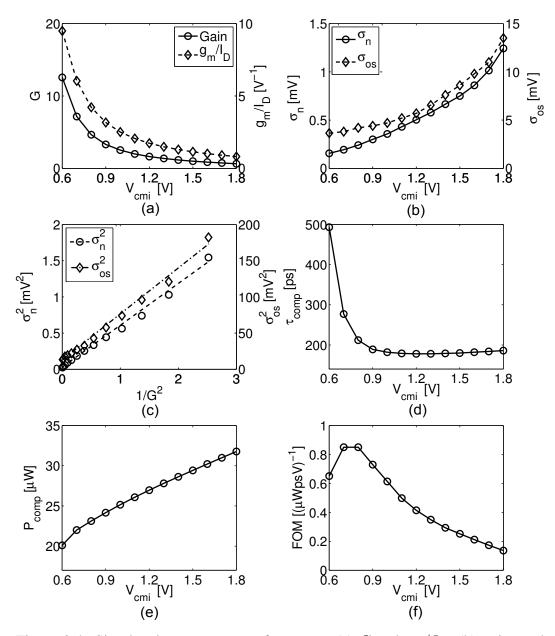

| 3.5  | Proposed bidirectional single-side switching technique                                                                                                                                  | 55 |

| 3.6  | Comparator input common-mode variation for different switching techniques                                                                                                               | 57 |

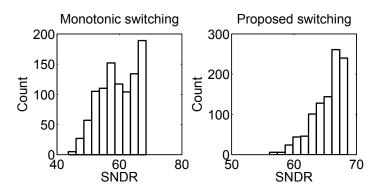

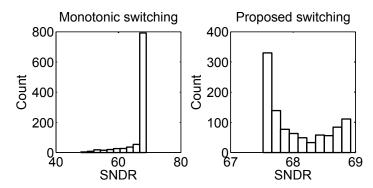

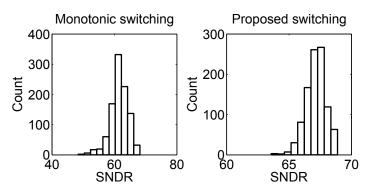

| 3.7  | Simulated SNDR with comparator offset variation                                                                                                                                         | 58 |

| 3.8  | Simulated SNDR with both comparator offset variation and a redundant capacitor after the 6th MSB capacitor                                                                              | 59 |

| 3.9  | Simulated SNDR with comparator offset variation, noise and a redundant capacitor after the 6th MSB capacitor                                                                            | 59 |

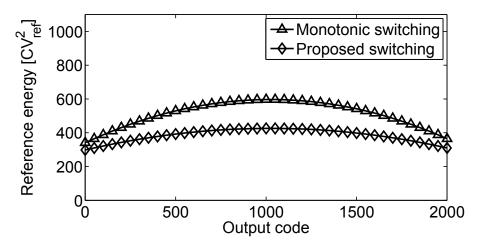

| 3.10 | DAC reference energy for an 11-bit SAR ADC with different output codes                                                                                                                  | 61 |

| 3.11 | Architecture of the 11-bit prototype SAR ADC                                                                                                                                            | 63 |

| 3.12 | DAC capacitor array floor plan                                                                                                                                                          | 65 |

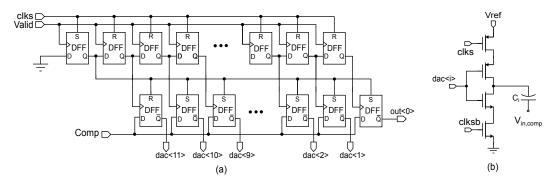

| 3.13 | Schematic for (a) the SAR logic and (b) the DAC switch                                                                                                                                  | 66 |

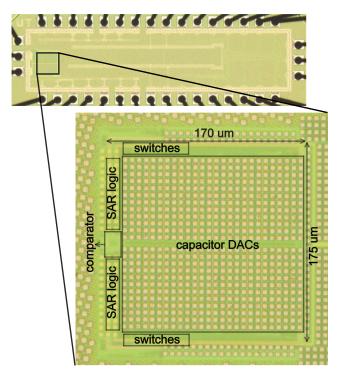

| 3.14 | Die micrograph and zoomed view                                                                                                                                                          | 67 |

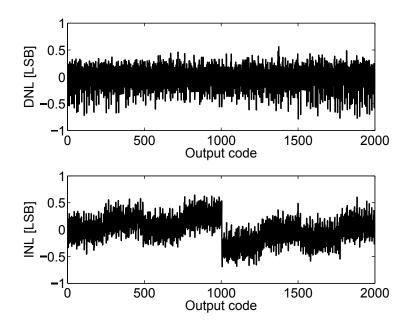

| 3.15 | Measured DNL and INL                                                                                                                                                                    | 68 |

| 3.16 | Measured 65536-point FFT spectrum with $V_{DD}$ = 1V                                                                                                                                    | 68 |

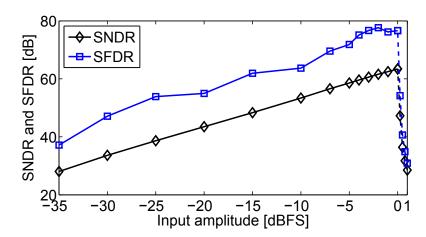

| 3.17 | Measured SNDR and SFDR versus input amplitudes                                                                                                                                          | 69 |

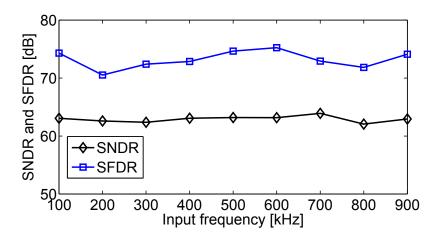

| 3.18 | Measured SNDR and SFDR versus input frequencies                                                                                                                                         | 69 |

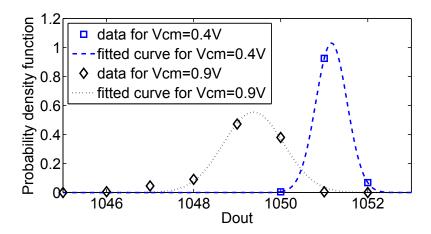

| 3.19 | Measured $D_{out}$ distribution with $V_{cmi}=0.4V$ and $V_{cmi}=0.9V$                                                                                                                  | 70 |

| 3.20 | Measured $D_{out}$ standard deviation with different $V_{cmi}$ at $V_{in}=0$ V                                                                                                          | 71 |

| 4.1  | (a) Architecture and (b) timing diagram of the proposed SAR ADC.                                                                                                                        | 76 |

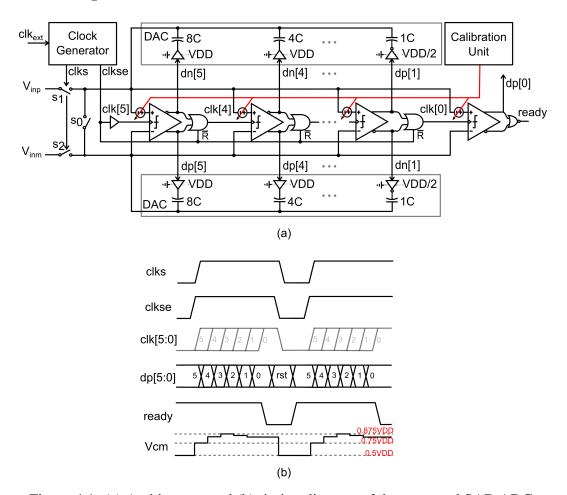

| 4.2  | Dynamic comparator with varactor loading                                                                                                                                                | 80 |

| 4.3  | Simulated comparator offset and decision time at different $V_{cm}$                                                                                                                     | 80 |

| 4.4  | BSS switching scheme                                                                                                                                                                                                                       | 82 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | Simulated time-domain waveforms for comparator inputs Vin+/Vin-, its common mode voltage $V_{cm}$ and its differential mode voltage $V_{dm}$ .                                                                                             | 83 |

| 4.6  | Probability of MSB comparator output being '1' versus its $calm$ with $calp$ fixed at 1.2V                                                                                                                                                 | 84 |

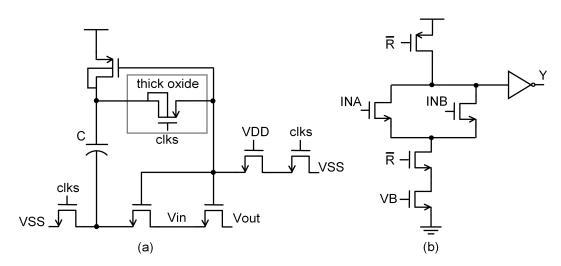

| 4.7  | Schematic of (a) bootstrapped sampling switch and (b) dynamic OR gate                                                                                                                                                                      | 85 |

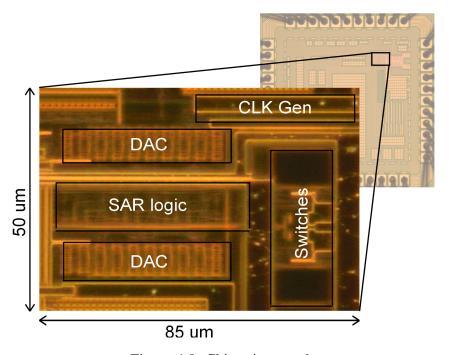

| 4.8  | Chip micrograph                                                                                                                                                                                                                            | 86 |

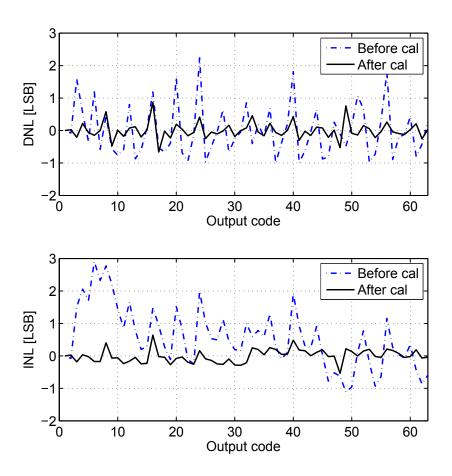

| 4.9  | Measured DNL/INL before calibration (dotted line) and after calibration (solid line)                                                                                                                                                       | 87 |

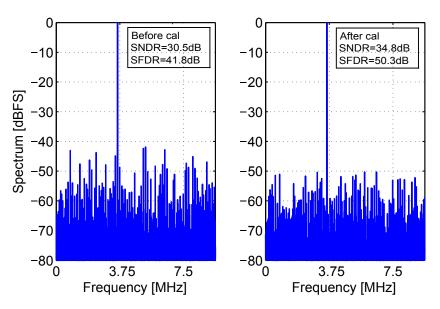

| 4.10 | Measured 1024p FFT spectrum before calibration and after calibration with 600MS/s sampling rate and 100MHz input                                                                                                                           | 88 |

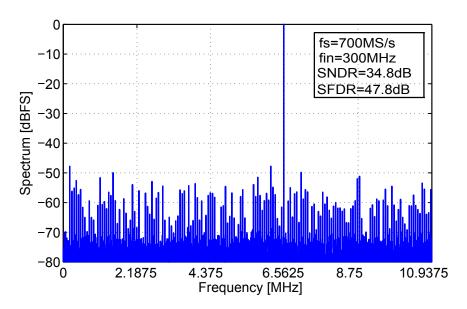

| 4.11 | Measured 1024p FFT spectrum with 700MS/s sampling rate and 300MHz input                                                                                                                                                                    | 89 |

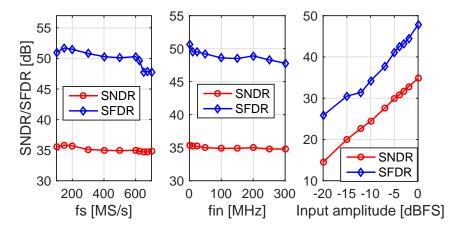

| 4.12 | Measured SNDR/SFDR under different sampling rates with 50MHz input (left), under different input frequencies with 700MS/s sampling rate (middle), and under different input amplitudes with 700MS/s sampling rate and 300MHz input (right) | 90 |

### **Chapter 1**

#### Introduction

#### 1.1 Motivation

The Internet of Things (IoT) is attracting lots of attention from semiconductor industry. It is changing the way how people control their surroundings and environments. In order to provide multiple functions at low cost, a typical IoT system-on-a-chip (SoC) commonly integrates sensor interfaces, analog-to-digital converters (ADCs), local digital processor, embedded memory and multi-protocol wireless transceivers. The integration of ADCs with adequate performance is critical in any IoT SoCs. Since many sensor interfaces and ADCs are battery-powered, low power operation becomes paramount.

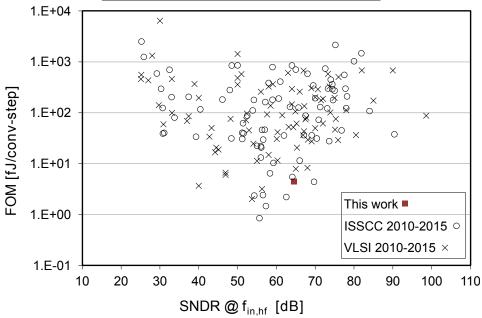

Successive approximation register (SAR) ADC is a popular choice due to its simple architecture and short development cycle. It is more digital friendly and does not require any opamps compared to pipeline ADCs or sigma-delta ADCs. SAR ADC can achieve excellent power efficiency of less than one femtojoule (fJ)/convstep at low resolution with a target effective number of bits (ENOB) below 10 bits. This can be visualized from Fig. 1.1, which shows the Walden figure of merit (FOM) versus the corresponding signal to noise and distortion ration (SNDR) for recently published SAR ADCs in ISSCC and VLSI conferences. The data for the

figure is taken from the survey made available by Dr. Boris Murmann (http://web.stanford.edu/~murmann/adcsurvey.html). However, some wireless sensor nodes and biomedical devices [Verma and Chandrakasan [2007]; Van Helleputte et al. [2012]] require low power ADCs with resolution greater than 10 bits. It is nontrivial to maintain such good power efficiency when extending the ENOB beyond 10 bits due to two design challenges. First, designing a low power comparator with low noise is a main challenge since traditional analog scaling requires four times the comparator power for every 1-bit reduction in noise. This places a steep power-noise trade-off. The second challenge for a high-resolution SAR ADC is its exponentially growing capacitive DAC size, which results in greatly increased DAC switching power. Thus, it is highly desirable to develop power efficient techniques to reduce comparator noise and DAC switching power.

Figure 1.1: FOM versus SNDR plot for recently published SAR ADCs in ISSCC and VLSI conferences.

In this thesis, a statistical estimation based technique is presented which can efficiently reduce comparator noise for SAR ADCs. Instead of designing an accurate comparator with large power consumption, the proposed technique utilizes the low power and noisy comparator and estimates the conversion residue by firing the comparator multiple times for LSB bit comparison. The conversion residue can be estimated by exploring the repeated comparison results. The estimated residue is then subtracted from the ADC output to accurately represent the input. The key challenge here is to build an accurate estimator. It has been proved in statistics that the Bayes estimator achieves lowest estimation error. Thus, Bayes estimator is chosen for the prototype SAR ADC design. The prototype ADC 1 has been implemented in 65nm CMOS and measured in the lab. The measured FOM of the first prototype ADC is 4.5 fJ/conv-step with 64.5dB SNDR, shown in Fig. 1.1. It suits well for the low power applications with low conversion speed.

Another challenge for low power and high resolution SAR ADC design is to reduce the DAC switching energy. The DAC is commonly implemented with binary capacitors in SAR ADCs. To suppress the sampling kT/C noise and provide good matching accuracy in high resolution designs, the capacitive DAC needs to be large, leading to a significant power consumption out of total ADC power. This work proposes a bidirectional single-side switching (BSS) technique, which can save 86% DAC switching power compared to conventional switching technique. Moreover, the comparator input common mode variation is reduced in the technique compared to widely used monotonic switching technique [Liu et al. [2010a]]. The prototype ADC 2 with BSS switching technique is designed in 180nm CMOS. The

measured FOM is 19.9 fJ/conv-step with 63.4dB SNDR. It achieves the state-of-art power efficiency shown in Fig. 1.1, given its relatively old 180nm process.

Modern high speed serial link transceivers and communication systems employ high speed and low resolution ADCs. Although SAR ADC is simple and power efficient, it can not run at a high speed compared to flash ADCs and pipeline ADCs, mainly due to its serial conversion algorithm. This work investigates a loop-unrolled architecture with multiple comparators to increase the speed of SAR ADCs. The loop-unrolled architecture is based on the work of [Jiang et al. [2012]]. However, the linearity in [Jiang et al. [2012]] is not good due to large comparator offset mismatches. This work employs the BSS switching technique and a  $V_{cm}$ -adaptive calibration technique to effectively reduce the comparator offset mismatches and improve the linearity. A third prototype 6-bit loop-unrolled SAR ADC is implemented in 45nm CMOS and the measured SNDR is 34.8 dB at a sampling rate of 700 MS/s.

#### 1.2 Organization

Chapter 2 of the thesis presents the low power SAR ADC with statistical estimation based noise reduction. It also includes the measurement results of the first prototype designed in 65nm CMOS technology. Chapter 3 presents the bidirectional single-side switching technique to reduce the DAC switching power. The measurement results for the second prototype designed in 180nm CMOS technology are also discussed. Chapter 4 presents the third 40nm high speed SAR ADC prototype with improved loop-unrolled architecture. The measured results are also

shown in Chapter 4. The conclusion is drawn in Chapter 5.

### Chapter 2

#### **Statistical Estimation Based Noise Reduction**

This chapter¹presents a power-efficient noise reduction technique for SAR ADCs based on the statistical estimation theory. It suppresses both comparator noise and quantization error by accurately estimating the ADC conversion residue. It allows a high SNR to be achieved with a noisy low-power comparator and a relatively low resolution DAC. The proposed technique has low hardware complexity, requiring no change to the standard ADC operation except for repeating the LSB comparisons. Three estimation schemes are studied and the optimal Bayes estimator is chosen for a prototype 11-bit ADC in 65nm CMOS. The measured SNR is improved by 7dB with the proposed noise reduction technique.

This chapter is organized as follows: an introduction of existing techniques is first presented. The basic idea of proposed noise reduction technique is studied next. Then the formulation is analyzed. Finally, a prototype ADC implementation is presented, followed by its measurement.

<sup>&</sup>lt;sup>1</sup>This chapter is a partial reprint of the publication: Long Chen, Xiyuan Tang, Arindam Sanyal, Yeonam Yoon, Jie Cong, and Nan Sun, "A 10.5-b ENOB 645nW 100kS/s SAR ADC with statistical estimation based noise reduction," IEEE Custom Integrated Circuit Conference (CICC), 2015, pp. 1–4. I thank all the co-authors for their valuable advice in designing and testing of the prototype.

#### 2.1 Introduction

Rapid advances in wireless sensor nodes and biomedical devices place demanding requirements on low power and high resolution analog-to-digital converters (ADCs) [Verma and Chandrakasan [2007]; Van Helleputte et al. [2012]]. Successive approximation register (SAR) ADC is a popular choice due to its simple architecture and short development cycle. It consists of only a capacitive DAC, a comparator, and a digital SAR logic. Since it is highly digital, it scales well with technology, and consumes both low power and low area in advanced CMOS processes. By using a low power but relatively noisy dynamic comparator, a SAR ADC does not consume any static current. As a result, it can achieve an excellent power efficiency of only a few femtojoule (fJ) per conversion step, especially at low resolution with a target effective number of bits (ENOB) below 10-bit [Tai et al. [2014a]; Harpe et al. [2014]]. Despite many advantages of SAR ADCs, it is nontrivial to design a high resolution SAR ADC and maintain a high power efficiency when extending the resolution beyond 10 bits. To reach higher signal-to-noise ratio (SNR), the comparator noise needs to be reduced. This can be accomplished by brute-force analog scaling, which is to increase the transistor sizes and power. However, this requires four times the comparator power for every 1-bit reduction in noise, which is a steep power-noise trade-off. The other challenge for a high-resolution SAR ADC is its exponentially growing capacitive DAC size, which results in greatly increased DAC power. In addition, it makes a SAR ADC hard to drive. Facing these challenges, it is highly desirable to develop a more efficient way to increase SAR ADC resolution without significantly increasing the comparator power and the DAC size.

There are several prior SAR ADC works that aim to reduce the comparator power and noise. The technique of [Giannini et al. [2008]] arranges two comparators with different noise and power levels. For a b-bit SAR ADC, it uses a lowpower but high-noise comparator during the first (b-1) MSB comparison cycles. To tolerate the resulting comparison errors due to the high noise, a redundant LSB bit is added. A high-power but low-noise comparator is used only for the LSB and the redundant bit. As a result, the overall ADC noise is almost the same as the case where the high-power low-noise comparator is used for every comparison cycle, but the total comparator power is greatly reduced. The limitation of this approach is that the offsets of the two comparators need to be tightly matched, which is nontrivial at high resolution. To address the offset mismatch issue, the majority voting technique is developed [Harpe et al. [2013]]. It uses only one low-power high-noise comparator. When low comparator noise is needed at critical decision point with a small comparator input voltage, the comparator is fired multiple times and the decision is made via majority voting. This technique does not have the comparator offset mismatch problem of [Giannini et al. [2008]], but it requires a carefully tuned metastability detector to sense the comparator input voltage, resulting in increased design complexity. Also, its conversion speed is reduced due to multiple comparisons needed. A similar technique using an optimized vote allocation is reported in [Ahmadi and Namgoong [2013]]. It obviates the need for a metastability detector, however, at the cost of further increased number of comparison cycles.

The majority voting technique of [Harpe et al. [2013]; Ahmadi and Nam-goong [2013]] can effectively reduce the comparator noise and power, but they do

not make *full* use of the information embedded in the voting results. It only cares about whether there are more '1's or more '0's, and uses it only to make a 1-bit majority decision. It does not take advantage of the detailed distributions of '1's and '0's, but there is valuable information there that can be exploited. Let us consider an example that the comparator is fired in total 15 times at a given comparison cycle. Let us assume that there are two cases: one is that there are eight '1's and seven '0's, and the other is that there are fifteen '1's and no '0's. Since there are more '1's, there is no difference for majority voting, but there is extra information. The first case indicates that the comparator input is very close to 0, while the second case of fifteen straight '1's means that its comparator input is greater than zero by at least several comparator noise standard deviations. As will be shown later, this extra information can be used to reduce not only the comparator noise but also the quantization error set by the DAC resolution.

This chapter presents a statistical estimation based technique that can reduce both the comparator noise and the quantization error for SAR ADCs. Its circuit implementation is simple. It does not require any change to the standard SAR ADC operation except for repeating the last LSB comparison for multiple times [Chen et al. [2015]]. It exploits *all* the information embedded in the comparator output distribution, not just making a binary majority decision for the LSB bit as in [Harpe et al. [2013]; Ahmadi and Namgoong [2013]], but to estimate the magnitude of the comparator input voltage. A useful property of a SAR ADC is that the comparator input voltage is the ADC conversion residue. If we are able to estimate the residue, we can subtract it from the ADC output to increase the ADC resolution. Note that

this reduces not only the comparator noise, but also the quantization error, which is impossible with prior works [Giannini et al. [2008]; Harpe et al. [2013]; Ahmadi and Namgoong [2013]]. Although a '1'-bit high-noise comparator cannot provide an accurate estimation for its input if used only once, we can improve the estimation accuracy by repeating the comparison for multiple times and examining the number of comparator outputs being '1' or '0'. It turns out that the estimation of an unknown value via multiple noisy binary tests is a classic *statistical estimation problem* [Casella and Berger [1990]]. Thus, we can directly borrow the concepts and theories from *statistics* to solve our estimation problem. Specifically, this chapter discusses three widely used statistical estimators: the averaging based estimator, the maximum likelihood estimator (MLE), and the Bayes estimator. Out of them, the Bayes estimator achieves the lowest estimation error, and thus, is chosen for our proposed SAR ADC. Note that the estimator is essentially a mapping from the comparator output distribution to a digital estimate for the comparator input, which can be easily implemented using a pre-computed look-up table.

This chapter introduces the statistical estimation theory to the field of ADC design and offers a new perspective. In a broad sense, any form of analog-to-digital conversion, regardless of its architecture, can be considered as a statistical estimation problem, as its entire operation is to estimate (or convert) an unknown analog signal by performing a series of comparison tests. The theories from statistics are helpful when we deal with multiple noisy comparator outputs, as in our case. The concept of statistical estimation has been exploited in prior studies. For example, the stochastic flash ADC of [Weaver et al. [2010]] takes advantages of random off-

sets in an array of comparators to obtain a 6-bit estimation of its input. This idea has also been adapted to build a stochastic time-to-digital converter (TDC) [Kratyuk et al. [2009]]. Recently, the stochastic flash ADC has been used as a back-end of a SAR ADC [Verbruggen et al. [2015]]. Though independently developed and published on close dates, the work of [Verbruggen et al. [2015]] shares a similar big picture as our work of [Chen et al. [2015]] as it uses multiple comparison results to estimate the SAR conversion residue. However, there are two key advantages of our work both in the choice of the estimator and the circuit architecture. First, the work of [Verbruggen et al. [2015]] uses MLE, which is a sub-optimal choice compared to the Bayes estimator used in our work. Second, it arranges 16 different comparators for the LSB estimation. Their offsets need to be very carefully calibrated, which is a big design and operation burden especially for high resolution applications and considering process, voltage, and temperature (PVT) variations. By contrast, we just re-use the original comparator in the SAR ADC, and thus, do not have the offset mismatch problem. Our limitation compared to [Verbruggen et al. [2015]] is reduced conversion speed as it requires a larger number of comparison cycles. Yet, for the intended low-speed sensor applications, the speed penalty is a minor issue.

To validate the proposed statistical estimation based noise reduction technique, a prototype 11-bit SAR ADC is implemented in 65nm CMOS. Using the proposed technique, the measured SNR is improved by 7 dB, which matches well with the theoretical prediction. Overall, the prototype ADC achieves an ENOB of 10.5-bit at 100kS/s while consuming  $0.6\mu$ W of power from a 0.7V supply.

## 2.2 Proposed Statistical Estimation Based Noise Reduction Technique: Basic Idea

Fig. 2.1 shows the simplified block diagram of a single-ended b-bit bottomplate sampled SAR ADC. A SAR ADC has a property that its conversion residue  $V_{res}$  is readily available at the comparator input. We can derive the following relationship among the ADC input  $V_{in}$ , output  $D_{out}$ , and  $V_{res}$ :

$$D_{out} = V_{in} + n_s + V_{res} \tag{2.1}$$

where  $n_s$  represents the kT/C noise directly added to  $V_{in}$  during the sampling phase. Here, for simplicity of presentation, we have made the following assumptions that do not undermine the practicality of the proposed technique: a) we assume the parasitic capacitor  $C_P = 0$ . Since its effect is simply attenuating  $V_{res}$ , it can be easily added in (2.1) by applying a scaling factor to  $V_{res}$ ; b) the comparator offset is assumed to be zero, as it does not affect the ADC SNR; and c) we ignore the effect of capacitor mismatch. In practice, if capacitor mismatch is a problem, classic mismatch calibration technique, such as [Lee et al. [1984]], can be applied jointly with the proposed technique.

As shown in (2.1), the ADC conversion error, defined as  $(D_{out} - V_{in})$ , consists of  $n_s$  and  $V_{res}$ . To reduce  $n_s$ , the only option is to increase the DAC capacitance  $C_{DAC}$ , which is not the focus of this work. In a SAR ADC, its conversion error is typically dominated by  $V_{res}$ , not  $n_s$ . For example, for a 12-bit SAR ADC with 2V peak-to-peak differential input swing, 420 fF of single-side DAC capacitance is already sufficient to suppress the sampling noise  $n_s$  to be less than the quantization

Figure 2.1: Diagram for a *b*-bit SAR ADC.

error. Note that 420 fF of total capacitance means that the unit capacitor size is only 0.1 fF, which is smaller than what most SAR ADCs use and what matching requires [Tripathi and Murmann [2013]]. In practice,  $n_s$  is usually smaller than  $V_{res}$ , which is set by the comparator noise and the DAC LSB size. This is especially true for recent SAR ADCs that use low power dynamic comparators without having a preamplifier [Harpe et al. [2013]; Lee et al. [2014]; Yip and Chandrakasan [2013]]. As a result, our work focuses on improving ADC SNR by reducing  $V_{res}$ .

$V_{res}$  consists of three parts: the ADC quantization error (i.e., DAC LSB step), the comparator noise, and the DAC noise. If the ADC does not have any comparator noise or DAC noise,  $V_{res}$  is simply the ADC quantization error and is uniformly distributed between  $\pm 1/2$  LSB. By contrast, in the presence of large comparator noise (in a SAR ADC the comparator noise is typically much large than the DAC noise),  $V_{res}$  is Gaussian distributed with a standard deviation close to

the comparator noise. To reduce  $V_{res}$ , a straightforward way is to use a low-noise comparator and a high-resolution DAC; however, both lead to greatly increased circuit power.

This chapter proposes a simple and power efficient way to reduce  $V_{res}$  by using statistical estimation. The core idea is that if we can estimate the value of  $V_{res}$ , denoted as  $\hat{V}_{res}$ , we can increase the ADC SNR by subtracting  $\hat{V}_{res}$  from  $D_{out}$  as:

$$D_{out}^* = D_{out} - \hat{V}_{res} = V_{in} + n_s + (V_{res} - \hat{V}_{res})$$

(2.2)

which shows that the accuracy of the new ADC output  $D_{out}^*$  is limited not by  $V_{res}$  but by the estimation error  $(V_{res} - \hat{V}_{res})$ . An interesting note is that if the estimation error can be made small, the resolution of  $D_{out}^*$  can even surpass the limit set by the ADC quantization error, because the subtraction of  $\hat{V}_{res}$  reduces both comparator noise and quantization error. This implies that the proposed technique can actually permit, for example, a SAR ADC with a b-bit DAC array to reach more than b-bit resolution.

Now with core idea captured in (2.2), the key question to answer is how we can estimate  $V_{res}$ . We prefer performing estimation without incurring large hardware and power cost. Since  $V_{res}$  is readily available at the comparator input, we propose to use the original noisy SAR comparator to estimate  $V_{res}$ . This may appear counterintuitive because the comparator can only provide a binary decision and its output is error-prone due to its high noise. Certainly 1-time comparison is insufficient. What we propose is to simply repeat the LSB comparison for a total of N times and estimate  $V_{res}$  by examining the number of '1's, denoted as k. This is

doable because the comparator output carries information on its input. Qualitatively speaking, if k=N, we know that  $V_{res}$  is most likely a large positive value; if k=0,  $V_{res}$  is most likely negative with a large magnitude; and if k=N/2,  $V_{res}$  is highly probable to be close to zero.

An intriguing side note is that the estimation of  $V_{res}$  is actually *enabled* by the comparator noise. If the comparator does not have any noise, its output would be straight '1's or '0's, and thus, we cannot extract any information about the magnitude of  $V_{res}$ , except for its sign. Having noise in the comparator actually enables us to improve our estimation accuracy on  $V_{res}$ . This phenomenon is actually an example of *stochastic resonance*, which is observed in a nonlinear system where the presence of a small amount of noise can actually improve the overall system SNR [Harmer et al. [2002]]. Such behavior is impossible in a linear system. In the SAR ADC, the 1-bit comparator is both nonlinear and noisy, which exactly matches the requirement for stochastic resonance.

## 2.3 Proposed Statistical Estimation Based Noise Reduction Technique: Mathematical Formulation

After presenting the basic idea of our proposed noise reduction technique, we now quantitatively answer what is the optimum choice of the estimator  $\hat{V}_{res}$  given the number of LSB comparisons N and the number of '1's k. Let us focus our attention on the repeated LSB comparison, whose model is shown in Fig. 2.2.  $d_{0,i}$  presents the i-th LSB comparison result, where i is from 1 to N.  $n_c$  represents the total noise referred to the comparator input. It includes both the comparator

noise and the DAC noise. It is typically dominated by the comparator noise.  $n_c$  is zero mean, and we denote its standard deviation as  $\sigma$  in the following discussion.

Figure 2.2: Simplified SAR ADC model during the LSB comparison.

Our goal is to form an estimator  $\hat{V}_{res}$  that minimizes the mean square error (MSE), defined as:

$$MSE = Var(V_{res} - \hat{V}_{res}) = E[(V_{res} - \hat{V}_{res})^{2}]$$

(2.3)

where Var and E stands for statistical variance and expectation, respectively [Casella and Berger [1990]].

It turns out that the estimation of an unknown value out of a series of noisy binary tests is a classic statistical estimation problem [Casella and Berger [1990]]. Therefore, we directly borrow the concepts and theories from statistics to solve our estimation problem. Specifically, we discuss three widely used statistical estimators: the simple averaging based estimator, the maximum likelihood estimator (MLE), and the Bayes estimator. They all can be implemented as digital look-up tables with similar hardware costs.

#### 2.3.1 Estimator based on averaging

One straightforward way to define  $\hat{V}_{res}$  is +1 LSB for all straight '1's, -1 LSB for all straight '0's, and performing linear interpolation for other values of k. Mathematically speaking, this definition is as follows:

$$\hat{V}_{res,avg} = \frac{2k - N}{N} \cdot LSB \tag{2.4}$$

where  $\hat{V}_{res,avg}$  linearly increases with k, and is  $\pm 1$  LSB for k=0 and N, respectively. Although  $\hat{V}_{res,avg}$  is easy to construct, it has several drawbacks. First, because  $\hat{V}_{res,avg}$  is bounded by  $\pm 1$  LSB, it cannot accurately approximate  $V_{res}$  that is outside of that range due to comparator noise. This can be clearly observed from Fig. 2.3 that plots the MSE of  $\hat{V}_{res,avg}$  as a function of  $V_{res}$ , N, and the comparator noise  $\sigma$ . If the comparator noise  $\sigma$  is large, there is a high probability for  $|V_{res}| > 1$  LSB, and  $\hat{V}_{res,avg}$  does not work well.

Figure 2.3: MSE of  $\hat{V}_{res,avg}$  for various N and (a)  $\sigma=0.5$  LSB, (b)  $\sigma=2$  LSB, and (c)  $\sigma=1$  LSB.

Second, the shape of its MSE curve varies substantially with the comparator noise  $\sigma$ . The reason is that the comparator noise affects the value of k, but such

influence is not captured in (2.4). For example, for a given nonzero  $V_{res}$ , if the comparator noise is small, the majority of the comparator outputs would be either all '1's (k=N) or all '0's (k=0), leading to  $\hat{V}_{res,avg}$  close to  $\pm 1$  LSB. This results in a low MSE for  $V_{res}=\pm 1$  LSB [see Fig. 2.3(a)], but a large MSE for  $V_{res}$  close to 0. On the other hand, if the comparator noise is large, it is highly likely that half of the comparator outputs are '1' (k=N/2), leading to  $\hat{V}_{res,avg}$  close to 0. This yields a small MSE for  $V_{res}=0$ , but a large MSE elsewhere [see Fig. 2.3(b)]. The overall best performance for  $\hat{V}_{res,avg}$  in terms of a small and relatively flat MSE is obtained only when the comparator noise  $\sigma$  is close to 1 LSB [see Fig. 2.3(c)]. This limits its applicability.

Furthermore, although its MSE decreases as N increases, the region with a small MSE becomes narrower [see Fig. 2.3]. For a nonzero  $V_{res}$ , the MSE of  $\hat{V}_{res,avg}$  does not decrease to 0 even if N goes to infinity. The reason is that  $\hat{V}_{res,avg}$  is a biased estimator of  $V_{res}$ , and the bias does not converge to zero [Casella and Berger [1990]]. As will be shown later, the aforementioned drawbacks for  $\hat{V}_{res,avg}$  do not exist for the other two estimators.

#### 2.3.2 Maximum likelihood estimator (MLE)

A key reason that  $\hat{V}_{res,avg}$  does not achieve a low estimation error is that it does not assume any prior information on the comparator noise  $\sigma$ . In practice,  $\sigma$  is chosen by the designer. It can be extracted via SPICE simulations with good accuracy. Although  $\sigma$  may change due to process, voltage, and temperature (PVT) variations, we can obtain an accurate value of  $\sigma$  by performing a simple foreground

calibration. We can simply set  $V_{in}=0$  by shorting the ADC input, and monitor the standard deviation of  $D_{out}$ . Since we have assumed that comparator noise  $\sigma$  is the dominant random source over the sampling noise  $n_s$ , the standard deviation of  $D_{out}$  simply reflects the value of  $\sigma$ . Since temperature changes slowly, the foreground calibration does not need to be repeated frequently. In addition, since the statistical estimation is performed at the LSB level, a 10% change in the value of  $\sigma$  only causes minor degradation (e.g., a 0.1 LSB error) in the post-estimation ADC SNR. This greatly relaxes the requirement on the calibration accuracy. Given this, we can treat the value of  $\sigma$  as a known quantity during the estimation process. We can take advantage of it to form a much better estimator, which is the maximum likelihood estimator (MLE).

The definition of MLE is easy to understand. Given the number of comparisons N and the number of '1's k, we define the estimator  $\hat{V}_{res}$  to be the value that maximizes the probability of observing k '1's out of N comparisons. MLE has been thoroughly studied in statistics and has several merits. First, it is consistent. As N increases,  $\hat{V}_{res,MLE}$  converges to  $V_{res}$  and can achieve arbitrary precision [Casella and Berger [1990]]. Second, it is highly efficient from the information usage point of view. It achieves the Cramer-Rao lower bound as N goes to infinity, which means that MLE achieves the lowest asymptotic MSE [Casella and Berger [1990]].

We can derive  $\hat{V}_{res,MLE}$  for our problem in the following way. The probability of a comparator output being '1' follows Bernoulli distribution with probability:

$$P(d_0 = 1) = P(V_{res} + n_c > 0) = F(\frac{V_{res}}{\sigma})$$

(2.5)

where F(x) is the cumulative distribution function of normal distribution with mean of 0 and variance of 1, given by:

$$F(x) = \int_{-\infty}^{x} f(x)dt = \int_{-\infty}^{x} \frac{1}{\sqrt{2\pi}} e^{-\frac{s^2}{2}} ds$$

(2.6)

where f(x) is its corresponding probability density function. Assuming the comparator hysteresis is negligible, the repeated LSB comparator outputs,  $\{d_0\}$   $(i \in [1, N])$ , can be considered as independently and identically distributed random variables. Thus, from the probability theory [Casella and Berger [1990]], we know that  $k = \sum_{i=1}^{N} d_{0,i}$  follows the binomial distribution  $B(N, F(V_{res}/\sigma))$  with the probability given by:

$$P(k|V_{res}) = {N \choose k} F(\frac{V_{res}}{\sigma})^k \left(1 - F(\frac{V_{res}}{\sigma})\right)^{N-k}$$

(2.7)

where  $P(k|V_{res})$  means the probability of having k '1's conditioning on  $V_{res}$ . Since  $\hat{V}_{res,MLE}$  maximizes  $P(k|V_{res})$  by definition, we have:

$$\frac{dP(k|V_{res})}{dV_{res}}\Big|_{\hat{V}_{res,MLE}} = 0 \tag{2.8}$$

From (2.8), we can derive that:

$$F(\hat{V}_{res,MLE}/\sigma) = \frac{k}{N}$$

(2.9)

This result is intuitive.  $\hat{V}_{res,MLE}$  ensures that the probability of the comparator output being 1 is k/N, and thus, it achieves the highest probability for having in total k '1's out of N trials. From (2.9), we can solve  $\hat{V}_{res,MLE}$ :

$$\hat{V}_{res,MLE} = \sigma \cdot F^{-1}(\frac{k}{N}) \tag{2.10}$$

It shows that  $\hat{V}_{res,MLE}$  is linearly proportional to the comparator noise  $\sigma$ . This is different from  $\hat{V}_{res,avg}$  that has no dependence on  $\sigma$  [see (2.4)].

$\hat{V}_{res,MLE}$  defined in (2.10) has one limitation that it does not work for k=0 and k=N. If we plug k=0 or k=N into (2.10),  $\hat{V}_{res,MLE}$  is  $\pm\infty$ . This is expected because  $\hat{V}_{res,MLE}=-\infty$  achieves the highest probability for k=0, and  $\hat{V}_{res,MLE}=\infty$  ensures that k=N. This issue may be minor for a large N, because the probability of k=0 and k=N would approach zero. However, for a small N, k=0 and k=N do appear, which causes an estimation failure. To solve this problem, we can re-define:

$$\hat{V}_{res,MLE}(k=0) = \sigma \cdot F^{-1}(\frac{0.2}{N})$$

(2.11)

$$\hat{V}_{res,MLE}(k=N) = \sigma \cdot F^{-1}(\frac{N-0.2}{N})$$

(2.12)

For other k lies in [1, N-1], we still follow the definition of (2.10).

Fig. 2.4 shows  $\hat{V}_{res,MLE}$  as a function of k and N. Different from  $\hat{V}_{res,MLE}$ , the relationship between  $\hat{V}_{res,MLE}$  and k is nonlinear. The range of  $\hat{V}_{res,MLE}$  expands with N, from  $\pm 1.6\sigma$  at N=3 to  $\pm 2.3\sigma$  at N=15. This means that  $\hat{V}_{res,MLE}$  can approximate a wider range  $V_{res}$  as N increases.

To evaluate how accurate  $\hat{V}_{res,MLE}$  is, we plot its estimation error as a function of  $V_{res}$  and N in Fig. 2.5. In general, its MSE decreases as N increases. For the same N, its MSE is small for a small  $V_{res}$ , but increases as the amplitude of  $V_{res}$  increases. The reason is that the value of  $\hat{V}_{res,MLE}$  is bounded for a given N (see Fig. 2.4), and thus, does not work well for a very large  $V_{res}$ . However, unlike  $\hat{V}_{res,avg}$ , the range of  $\hat{V}_{res,MLE}$  increases with N, and thus, its region with a small

Figure 2.4: Value of  $\hat{V}_{res,MLE}$  as a function of N and k.

MSE is broadened. This is a key advantage of  $\hat{V}_{res,MLE}$  compared to  $\hat{V}_{res,avg}$ . It enables  $\hat{V}_{res,MLE}$  to accurately estimate a wide range of  $V_{res}$  especially for a large N. In fact, we can prove that the MSE of  $\hat{V}_{res,MLE}$  goes to zero as N approaches infinity for any  $V_{res}$  [Casella and Berger [1990]].

#### 2.3.3 Bayes estimator

MLE is a significant improvement over the simple averaging based estimator, but it still does not achieve the lowest estimation error. There is one extra piece of information that MLE does not make use of, which is the distribution of  $V_{res}$ . This extra information can be exploited to construct a better estimator with a lower estimation error than MLE.

Before moving ahead, let us first examine the distribution of  $V_{res}$ . Fig. 2.6

Figure 2.5: MSE of  $\hat{V}_{res,MLE}$  for different  $V_{res}$ .

shows the simulated histograms of  $V_{res}$  for an 11-bit SAR ADC assuming the comparator noise  $\sigma=1$  LSB. Three different input signals are used. Sinusoidal inputs with -6-dBFS and -20-dBFS are used in Fig. 2.6(a) and (b), respectively. A Gaussian random input with a standard deviation of 10% ADC full swing is used in Fig. 2.6(c). As can be seen, there is negligible difference in the  $V_{res}$  distribution among the three cases. They are all close to Gaussian distribution with zero mean and a standard deviation of 1 LSB. This shows that the distribution of  $V_{res}$  has very weak dependence on the ADC input  $V_{in}$ . This is not hard to understand. By the end of the 11-bit SAR conversion, the conversion residue  $V_{res}$  is almost completely uncorrelated with  $V_{in}$ , and is basically set by the comparator noise. Given this observation, we can confidently approximate  $V_{res}$  as a Gaussian random variable and its proba-

bility density function (pdf)  $g(V_{res}) \equiv f(V_{res}/\sigma)$ , where  $f(\cdot)$  is the pdf of Gaussian distribution with zero mean and standard deviation of 1.

Figure 2.6: Histogram of  $V_{res}$  for (a) a -6-dBFS sinusoidal input, (b) a -20-dBFS sinusoidal input, and (c) a Gaussian random input with standard deviation of 10% ADC full range.

Now let us derive the optimum estimator for  $V_{res}$  given the prior information on its distribution. This problem has been thoroughly studied in the statistical estimation theory [Casella and Berger [1990]]. It can be rigorously proved that the best estimator that achieves the minimum MSE given the prior distribution is the Bayes estimator (BE), which is defined as the mean of the posterior distribution of  $V_{res}$  after observing k '1's out of N trials. To understand it, let us consider a simple example of N=3. We can have 4 different values for k, which is 0, 1, 2, and 3. For each case, we can calculate the posterior distribution  $g(V_{res}|k)$  using the Bayes theorem[Casella and Berger [1990]]:

$$g(V_{res}|k) = \frac{P(k|V_{res})g(V_{res})}{\int_{-\infty}^{+\infty} P(k|V_{res})g(V_{res})dV_{res}}$$

(2.13)

where  $P(k|V_{res})$  is the probability of observing k '1's conditioning on  $V_{res}$ . Fig. 2.7 plots the  $V_{res}$  prior distribution  $g(V_{res})$  together with its posterior distributions  $g(V_{res}|0)$ ,  $g(V_{res}|1)$ ,  $g(V_{res}|2)$ , and  $g(V_{res}|3)$ . Bayes rule basically allows us to update the distribution of  $V_{res}$  given the observation result k. We can see that the prior and posterior distributions are different, which is enabled by the knowledge of k. For example, compared to  $g(V_{res})$ , the posterior distribution  $g(V_{res}|0)$  is shifted towards the negative side. This is because after observing all '0's from the comparator outputs, we can update the distribution of  $V_{res}$ , which should be more negatively biased.

Figure 2.7: Prior distribution  $g(V_{res})$  and posterior distribution  $g(V_{res}|k)$  for N=3.

The Bayes estimator is defined as the mean of the posterior distribution.

Mathematically, it is given by:

$$\hat{V}_{res,BE}(k) \equiv E(V_{res}|k) = \int_{-\infty}^{+\infty} V_{res} \cdot g(V_{res}|k) dV_{res}$$

(2.14)

For the case of N=3, we can calculate that  $\hat{V}_{res,BE}(0)=-1\sigma$ ,  $\hat{V}_{res,BE}(1)=-0.3\sigma$ ,  $\hat{V}_{res,BE}(2)=+0.3\sigma$ , and  $\hat{V}_{res,BE}(3)=+1\sigma$ , respectively.

Note that (2.13) and (2.14) are computationally intensive. Fortunately, we do not need to solve  $\hat{V}_{res,BE}$  for every ADC output. We only need to compute once, and store the results for all possible k values in a look-up table. This way, once we know k from the comparator outputs,  $\hat{V}_{res,BE}$  can be directly obtained from the table.

Fig. 2.8 shows  $\hat{V}_{res,BE}$  as a function of k and N. Comparing it carefully with  $\hat{V}_{res,MLE}$  shown in Fig. 2.4, we can see that the range of  $\hat{V}_{res,BE}$  is smaller than  $\hat{V}_{res,MLE}$ . The reason is that  $\hat{V}_{res,BE}$  makes use of the prior distribution of  $V_{res}$ . Since  $V_{res}$  is concentrated around zero,  $\hat{V}_{res,BE}$  is biased more towards zero.

Fig. 2.9 shows MSE for  $\hat{V}_{res,BE}$  as a function of  $V_{res}$  and N. Comparing it with Fig. 2.5 of  $\hat{V}_{res,MLE}$ , we see that the MSE of  $\hat{V}_{res,BE}$  is smaller than that of  $\hat{V}_{res,MLE}$  for a small  $V_{res}$  in  $[-2\sigma, +2\sigma]$ , but is slightly larger for  $|V_{res}| > 2\sigma$ . However, because  $V_{res}$  is known to concentrate around 0, it is expected that the overall MSE of  $\hat{V}_{res,BE}$  is smaller than that of  $\hat{V}_{res,MLE}$ .

### 2.3.4 Estimator performance comparison

To compare the estimation error for the three estimators, we compute the MSE of  $\hat{V}_{res,avg}$ ,  $\hat{V}_{res,MLE}$ , and  $\hat{V}_{res,BE}$  for  $\sigma=1$  LSB, and plot them as a function

Figure 2.8:  $\hat{V}_{res,BE}$  as a function of N and k.

Figure 2.9: MSE versus x for  $\hat{V}_{res,BE}$ .

Figure 2.10: MSE versus N for a normal distributed x with  $\sigma = 1$ LSB.

As expected, the MSE of  $\hat{V}_{res,BE}$  is consistently smaller than that of  $\hat{V}_{res,avg}$  and  $\hat{V}_{res,MLE}$ , indicating the highest estimation accuracy. Note that the MSE values for all three estimators are similar for a small N. However, for a large N, there are significant differences. For  $\hat{V}_{res,avg}$ , its MSE saturates to around  $0.2\sigma^2$ . By contrast, the MSE of  $\hat{V}_{res,MLE}$  and  $\hat{V}_{res,BE}$  keep decreasing with N at the slope of 10 dB per decade. This slope is essentially the limit set by Cramer-Rao lower bound [Casella and Berger [1990]], confirming the high efficiency of both  $\hat{V}_{res,MLE}$  and  $\hat{V}_{res,BE}$ . Since  $\hat{V}_{res,BE}$  has the lowest MSE, it is chosen for the prototype ADC.

As mentioned earlier, both MLE and Bayes estimators require the knowledge of the comparator noise  $\sigma$ . It is interesting that the extracted comparator

noise does not need to be 100% accurate when estimating  $\hat{V}_{res,BE}$ . This makes the proposed technique more robust as the comparator noise can drift with Process-Voltage-Temperature (PVT) variation. Let us assume a  $\pm 10\%$  noise drifting happens in the prototype ADC. After  $1\sigma$ =1.0 LSB is extracted, the comparator noise drifts to 0.9 LSB or 1.1 LSB due to PVT variation. However, the comparator noise is supposed to be the same and the  $1\sigma$  comparator noise of 1.0 LSB is used when performing the Bayes estimation. Fig. 2.11 plots the behavioral simulated SNR improvement for different  $\sigma$ s. As can be seen from Fig. 2.11, the SNR is improved effectively even though an inaccurate comparator noise  $1\sigma$ =1.0 LSB is used to estimate  $\hat{V}_{res,BE}$  for  $1\sigma$ =0.9 LSB and  $1\sigma$ =1.1 LSB. Note that the SNR differences among three cases result from different comparator noise used in the ADC model. Fig. 2.11 also shows that the proposed technique can be easily extended to achieve re-configurable resolution by adjusting N. In the prototype design, a 7-dB SNR improvement is expected which requires N = 17.

### 2.3.5 Comparison to oversampling and analog scaling

The standard ADC oversampling can also be used to reduce ADC noise by averaging, and the improvement in SNR is also 10 dB per decade. Thus, it is meaningful to compare it to the proposed statistical estimation technique. The merit of oversampling is that it reduces both the sampling noise  $n_s$  and the comparison noise  $n_c$ , while the proposed technique based on statistical estimation only reduces  $n_c$ . However, as mentioned earlier, in a SAR ADC, the noise is typically dominated by  $n_c$ , and thus, their effect in total noise reduction is similar. The disadvantage of

Figure 2.11: Simulated SNR versus N with  $\pm 10\%$  variations in the comparator noise  $\sigma$ .

oversampling is that it *cannot* improve the ADC power efficiency. Every doubling of the oversampling ratio (OSR) leads to twice the ADC power, as it requires repeating all the sampling, comparison and DAC switching operations. By contrast, the proposed technique only increases the number of LSB comparisons, so its required total number of comparator operations is much smaller. Additionally, the DAC is not switched, and thus, does not dissipate any extra DAC power. As a result, the power efficiency of the proposed technique is much higher than oversampling.

As in any noise reduction technique, there is always a cost of power. For the proposed technique, the total power of the comparator increases due to extra number of LSB comparisons. Take our 11-bit prototype ADC as an example, to reduce noise by 7 dB, the LSB comparison needs to be fired 17 times, which results in an increase of total comparator power by  $(11+17)/11\approx 2.5$  times. By contrast, to obtain the same amount of noise reduction for the same 11-bit ADC, if we choose the brute-force way to reduce comparator noise by increasing its size and power, we need to increase the comparator power by 21 times (see Prototype ADC Design section). Thus, the proposed technique is much more power efficient. The tradeoff for the proposed technique is reduced conversion rate due to increased number of LSB comparisons. However, as mentioned earlier, this is only a minor issue for the intended low-to-medium speed sensor applications.

## 2.4 Prototype ADC Design

## 2.4.1 Detailed circuit schematics

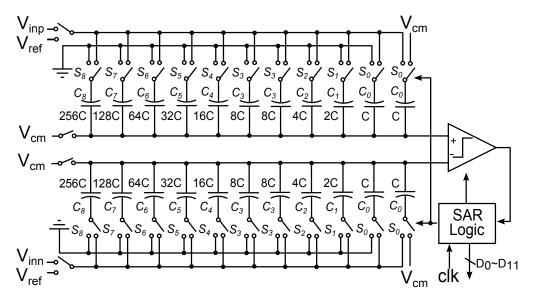

To verify the proposed statistical estimation based noise reduction technique, a 11-bit prototype SAR ADC is designed, whose architecture is shown in Fig. 2.12. There are only two simple changes made to the standard SAR ADC architecture: 1) the SAR logic is modified to repeat the LSB comparison for N=17 times; and 2) a counter is used to count the number of '1's during LSB comparisons to obtain k. A low power supply voltage of 0.7V is chosen to demonstrate the effectiveness of the proposed technique for low voltage and low power applications.

The DAC is implemented with binary-weighted metal finger (or MoM) capacitors. Since the DAC power is proportional to the total capacitor value, it is desired to reduce the unit capacitor  $C_u$  for power saving. Considering the noise and matching requirement, this design chooses  $C_u = 2$  fF. A bidirectional single-side (BSS) switching technique is adopted to further reduce the DAC reference power by

Figure 2.12: Proposed SAR ADC architecture.

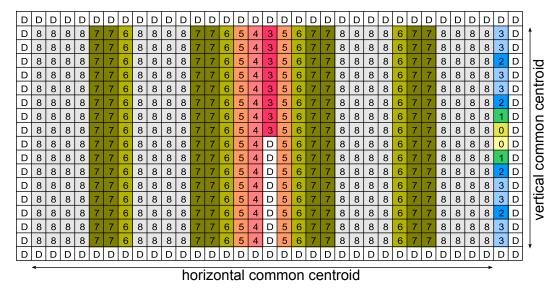

86% compared to the conventional switching scheme [Chen et al. [2014a]; Sanyal and Sun [2014]]. BSS reduces the number of unit capacitors by 4 times, leading to a small capacitor array of {256, 128, 64, 32, 16, 16, 8, 4, 2, 1, 1} $C_u$  for an 11-bit ADC. Compared to widely used monotonic switching technique of [Liu et al. [2010a]], BSS achieves higher SNDR as the comparator input common-mode voltage  $V_{cm}$  variation is reduced and  $V_{cm}$  can converge to half  $V_{dd}$  instead of ground. A redundant capacitor of  $16C_u$  is provided to recover possible errors during the first several MSB comparisons with large  $V_{cm}$  variation [Chen et al. [2014a]]. The total capacitance is  $528C_u = 1056$ fF, leading to 88- $\mu$ V differential sampling kT/C noise. Since the unit capacitor is only 2 fF, the routing parasitic capacitors have a considerable influence on the capacitor matching accuracy. A segmented commoncentroid layout technique is used for better matching. The floor plan for a single side capacitor array is shown in Fig. 2.13. The capacitors are separated into two groups  $\{C_8, C_7, ..., C_4\}$  and  $\{C_3, C_2, C_1, C_0\}$ . The common-centroid rule is applied horizontally for the first group and vertically for the second. Dummy cells, repre-

sented as D, are added for better matching.

Figure 2.13: DAC capacitor array floor plan.

To ensure good sampling linearity, bottom-plate sampling is used. In addition, a clock booster shown in Fig. 2.14(a) is employed to boost the sampling clock voltage from 0.7V to 1.4V. As a result, simple small NMOS transistors can be used to sample  $V_{in}$  instead of an array of bootstrapped switches or large CMOS switches to reduce the design complexity and the switch driving power.

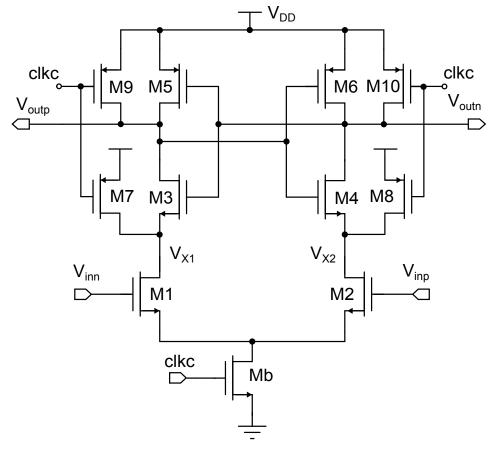

Fig. 2.14(b) shows the dynamic strong-arm latch comparator. It uses a PMOS input pair to minimize the flicker noise and the substrate coupling. Thanks to the proposed noise reduction technique, the comparator thermal noise requirement is relaxed, leading to substantially reduced comparator power. In this design, the SPICE simulated total input referred noise at the comparator input is  $480\mu V$  or 0.7 LSB. Note that this is much larger than the sampling kT/C noise, and thus, the

Figure 2.14: Schematic of (a) the clock booster; (b) the comparator; and (c) the timing diagram.

overall ADC noise is dominated by the comparator noise.

The ADC timing diagram is shown in Fig. 2.14(c). It uses a synchronous clocking scheme. The frequency of the master clock is 32 times faster than the sampling rate. The first 4 clock cycles are used for input sampling to ensure high sampling accuracy; the subsequent 11 cycles are used for normal SAR operation; and the final 17 cycles are used for repeated LSB comparisons. This clock allocation scheme can be easily implemented using a ripple counter based clock divider and several AND gates. The SAR logic is built by standard shift registers. When the normal SAR operation finishes, the last shift register makes transition and ready = 1 is generated. A 5-bit counter shown in Fig. 2.15 is enabled, which records the number of '1's during the LSB comparisons and obtains k for statistical estimation. The counter consumes no power during normal SAR operation. The counted k is given by:

$$k = 16 \times D4 + 8 \times D3 + 4 \times D2 + 2 \times D1 + D0 \tag{2.15}$$

Figure 2.15: 5-bit counter to count k.

Figure 2.16: Die micrograph.

## 2.4.2 Measurement Results

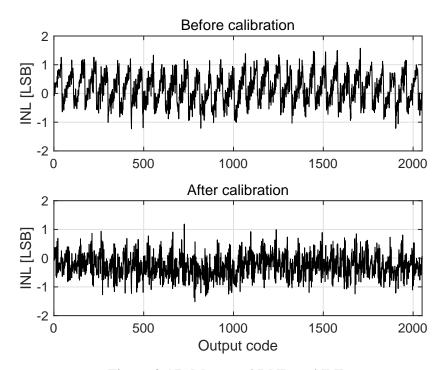

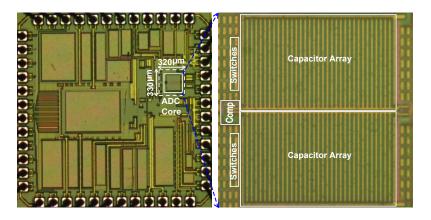

The prototype ADC is implemented in 65nm CMOS process. Fig. 2.16 shows the die photo. The ADC occupies an active area of  $0.03 \text{ mm}^2$ , which is dominated by the DAC. The power supply is 0.7V and the sampling rate is 100kS/s. Fig. 2.17 shows the measured DNL and INL, which are +1.04/-1 LSB and +1.57/-1.23 LSB. According to the INL plot, there exists a 1-LSB systematic mismatch between the 6 MSB capacitors and the 6 LSB capacitors, which arises from the unmatched surrounding environment due to the segmented layout strategy in Fig. 2.13 and inaccurate parasitic capacitor extraction. A simple foreground calibration similar to [Chen and Brodersen [2006]] is performed and the appreciable

periodic INL transition pattern reduces.

Figure 2.17: Measured DNL and INL.

To verify the proposed noise reduction technique, we first measure the ADC noise (e.g., the variation of  $D_{out}$ ) at  $V_{in}=0$ . The measured probability densities for  $D_{out}$  before and after noise reduction are shown in Fig. 2.18 together with fitted normal distributions. Before noise reduction, the standard deviation of  $D_{out}$  is 0.73 LSB. It indicates the comparator input referred noise is about  $500\mu\text{V}$ , which is in agreement with SPICE simulation. After noise reduction, the standard deviation of  $D_{out}^*$  is reduced by 7 dB to 0.33 LSB, which matches well with the estimation theory. Note that if the conventional SAR ADC design approach is used, the comparator noise needs to be reduced to 0.16 LSB in order for the total ADC noise to

be 0.33 LSB, which also includes the 0.29 LSB quantization error. This means that the total comparator power needs to be increased by 21 times. By contrast, in our proposed noise reduction technique, the total comparator power is only increased by 2.5 times, which firmly proves its higher power efficiency compared to bruteforth analog scaling. Once the comparator noise is extracted,  $\hat{V}_{res,BE}(k)$  can be computed using (2.13) and (2.14).

Figure 2.18:  $D_{out}$  distribution with and w/o estimation at  $V_{in} = 0$ .

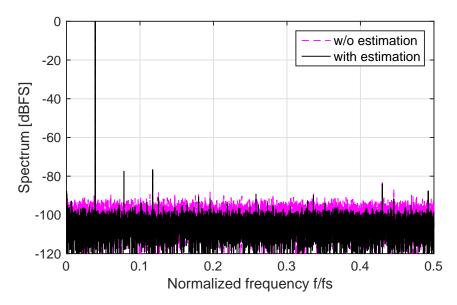

Fig. 2.19 shows the measured spectrum for a 96-kHz full-scale input sampled at 100kS/s. The reason choosing the 96-kHz frequency input is our high-quality low-distortion band-pass filter has a cut-off frequency at 90 kHz. The measured SNDR and SNR are 59.4 and 59.7 dB for 96-kHz input, respectively. After applying the proposed noise reduction technique, the noise floor is clearly lowered. SNDR and SNR are improved to 64.5 dB and 65 dB, respectively. The correspond-

ing ENOB is 10.5-bit.

Figure 2.19: Measured 2<sup>14</sup>-point ADC output spectrum with 96-kHz input.

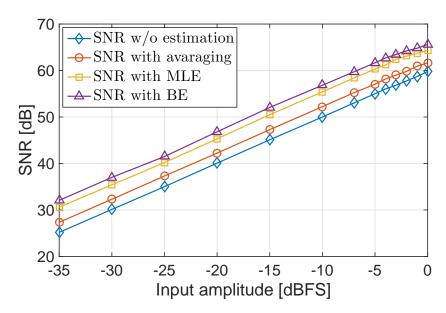

Fig. 2.20 shows the SNR with varying input amplitudes. The SNR improvement using simple averaging based estimator  $\hat{V}_{res,avg}$  is limited to only 2.2dB. Maximum likelihood estimator (MLE) achieves 5.8dB SNR improvement, which is better than averaging based estimator. Using the Bayes estimator  $\hat{V}_{res,BE}$ , the SNR can be improved by 7dB, which is 4.8dB better than that of averaging based estimator and 1.2dB better than that of MLE. This matches well with the analysis. When the input is very large, the SNR improvement decreases slightly to 5.3 dB, which is caused by the unwanted capacitive coupling from the ADC input to the reference lines, discovered during measurements. Such SNR loss can be recovered by layout optimization to reduce the coupling. To evaluate the robustness of SNR improvement using Bayes estimator, various extracted comparator noise  $\sigma$ s, which

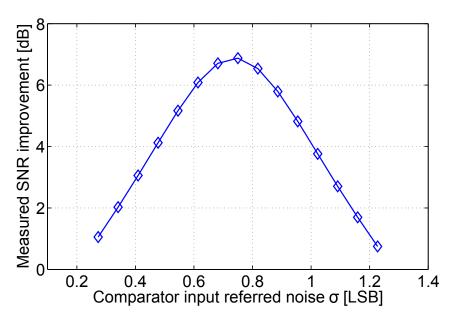

can be caused by PVT variation, are used to estimate  $\hat{V}_{res,BE}$ . Fig. 2.21 shows the measured SNR improvement versus  $\sigma s$ . The peak SNR improvement is large in the middle and small at two sides, just like a parabolic distribution. The peak SNR improvement is 6.9 dB at  $\sigma = 0.73$  LSB. As long as the extracted  $\sigma \in [0.6, 0.86]$  LSB, the SNR improvement is greater than 6 dB and one more effective bit is achieved with Bayes estimation.

Figure 2.20: Measured SNR versus input amplitudes.

The ADC consumes  $0.6~\mu\mathrm{W}$  from a  $0.7~\mathrm{V}$  power supply. The comparator, DAC, clock generator, and SAR logic consume 70 nW, 102 nW, 193 nW and 280 nW, respectively. With the noise reduction technique, the comparator power accounts for only 10% of the total power at the ENOB of 10.5-bit. The digital power, including both clock generator and SAR logic, dominates the overall ADC power. It can be substantially reduced via optimization and/or going to a more

Figure 2.21: Measured SNR improvement versus various comparator noise  $\sigma$ .

advanced technology node, without affecting SNR. The measured figure-of-merit (FOM) for the prototype ADC is 4.5 fJ/conversion-step. The performance of the proposed ADC is summarized in Table 2.1. Fig. 2.22 shows Walden FoM versus SNDR for this work and recently published ADCs in ISSCC and VLSI conferences. The data for the figure is taken from the survey made available by Dr. Boris Murmann (http://web.stanford.edu/~murmann/adcsurvey.html). As can be seen, this work achieves the state-of-the-art power efficiency, especially among ADCs with SNDR greater than 64 dB. Note that there is still large space for further performance improvements especially on the design of the clock generator and the SAR logic.

Table 2.1: Measured performance summary

| Process [nm]                   | 65            |      |

|--------------------------------|---------------|------|

| Sampling rate [kS/s]           | 100           |      |

| Resolution [bit]               | 11            |      |

| Active area [mm <sup>2</sup> ] | 0.03          |      |

| Power supply [V]               | 0.7           |      |

| Total power [µW]               | 0.6           |      |

| DNL [LSB]                      | +1.04 / -1.00 |      |

| INL [LSB]                      | +1.57 / -1.23 |      |

| Noise Reduction?               | No            | Yes  |

| Dynamic range [dB]             | 60            | 67   |

| Peak SNR [dB]                  | 59.7          | 65   |

| Peak SNDR [dB]                 | 59.4          | 64.5 |

| ENOB [bit]                     | 9.6           | 10.5 |

| Walden FoM [fJ/conv-step]      | 9             | 4.5  |

Figure 2.22: FOM versus SNDR plot for this work and recently published ADCs in ISSCC and VLSI conferences.

# Chapter 3

# **Bidirectional Single-side Switching Technique**

This chapter presents a low-power SAR ADC with a bidirectional single-side (BSS) switching technique. Compared to the conventional SAR switching scheme, it reduces the DAC reference power and the total number of unit capacitors by 86% and 75%, respectively. It also minimizes the power dissipated in driving DAC switches as it has only one single-side switching event every comparison cycle. Compared to the monotonic switching technique [Liu et al. [2010a]] that also has only one switching event, it reduces the comparator input common-mode voltage variation by 2 times. Moreover, its comparator input common-mode voltage does not converge to ground but to  $V_{cm}$ . This greatly reduces the comparator offset and noise. It obviates the need for a specially designed comparator and allows the use of a low-power strong-arm latch. A prototype with proposed technique has been developed in 180nm CMOS.

This chapter is organized as follows: an introduction of existing switching techniques is first presented. The effect of comparator common-mode variation is

<sup>&</sup>lt;sup>1</sup>This chapter is a partial reprint of the publication: Long Chen, Arindam Sanyal, Ji Ma and Nan Sun, "A 24-uW 11-bit 1-MS/s SAR ADC with a bidirectional single-side switching technique", *IEEE ESSCIRC*, pp. 219–222, 2014. I thank all the co-authors for their valuable advice in designing and testing of the prototype.

analyzed next. Finally, the proposed BSS switching technique is presented, followed by the prototype implementation and measurement.

## 3.1 Introduction

Successive approximation register (SAR) analog-to-digital converter (ADC) is scaling friendly and power efficient. It is suitable for low power and low voltage applications, such as wireless sensor networks, implantable bio-sensors, and portable medical electronics [Harpe et al. [2013]; Van Elzakker et al. [2010]; Verma and Chandrakasan [2006]; Zhang et al. [2012]]. It consists of a capacitive DAC, a comparator, and a SAR logic block. The DAC can take up a large portion of the total ADC power especially at high resolution with large capacitors. The conventional DAC switching technique based on trial and error is not power efficient. To address this issue, several low-power DAC switching techniques have been developed, including the split capacitor technique [Ginsburg and Chandrakasan [2005]], the  $V_{cm}$ -based switching technique [Zhu et al. [2010]], and the monotonic switching technique [Liu et al. [2010a]]. The split capacitor technique reduces DAC reference power by 37% compared to the conventional switching scheme. The  $V_{cm}$ -based switching technique reduces DAC reference power by 88%, but it requires additional switches to pass  $V_{cm}$ . Due to the reduced overdrive voltage, these switches need to be large, leading to increased power in driving these switches. This limitation is more pronounced at low power supply voltage and high conversion rate [Sanyal and Sun [2014]].

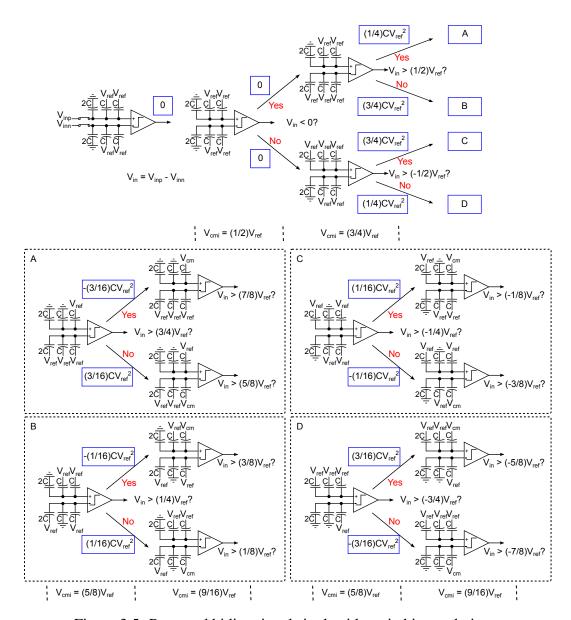

The monotonic switching technique of [Liu et al. [2010a]] has attracted in-