Copyright

by

Xiaoqing Xu

2017

The Dissertation Committee for Xiaoqing Xu certifies that this is the approved version of the following dissertation:

# Standard Cell Optimization and Physical Design in Advanced Technology Nodes

| Committee:               |   |  |  |

|--------------------------|---|--|--|

|                          |   |  |  |

| David Z. Pan, Supervisor |   |  |  |

| Brian Cline              | _ |  |  |

| Michael Orshansky        | _ |  |  |

| Nan Sun                  | _ |  |  |

| Nur A Touba              | _ |  |  |

# Standard Cell Optimization and Physical Design in Advanced Technology Nodes

$\mathbf{b}\mathbf{y}$

Xiaoqing Xu, B.S.; M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2017$

Dedicated to my parents: XU Min and LIU Shufang for their unconditional love

To my wife Shaoting Zhang

# Acknowledgments

I sincerely appreciate the generous guidance and support from my adviser, Professor David Z. Pan. He is a wise, humble and patient leader. Throughout my graduate study, he not only provides insightful technical suggestions toward important research problems, but also shapes my personality to be more humble and patient. Moreover, he is a nice friend in daily life and teaches me how to communicate with senior professionals and benefit from their life experiences. None of my research studies would have been possible without his support and trust.

I express great appreciations to other committee members for their precious efforts on this dissertation. In particular, I would like to thank Professor Michael Orshansky for his technical suggestions during the development of this dissertation. I would like to thank Professor Nan Sun for his comments on the concepts and scopes of my research studies. I would like to thank Professor Nur A. Touba for his kindness and support to this dissertation. I would like to thank Dr. Brian Cline for his detailed technical suggestions and guidance. He has been a dear friend and great mentor during our continuous research collaborations and my internships at ARM Inc.

Besides, I deeply appreciate the help from other industrial mentors and collaborators: Dr. Greg Yeric at ARM Inc., Dr. Tetsuaki Matsunawa, Dr.

Shigeki Nojima and Dr. Chikaaki Kodama at Toshiba Corporation, Dr. Gi-Joon Nam, Dr. Gustavo Tellez and Dr. Hua Xiang at IBM T. J. Watson Research Center, Dr. Zhuo Li and Dr. Charles Alpert from Cadence Design System, and Dr. Lars Liebmann from GLOBALFOUNDRIES. This work would not be possible without their technical suggestions.

It has been a great learning experience to work with other UTDA members: Bei Yu, Jerrica Gao, Subhendu Roy, Yibo Lin, Jiaojiao Ou, Meng Li, Vinicius Livramento, Che-Lun Hsu, Biying Xu and Wei Ye. This dissertation has benefited a lot from the productive collaborations and discussions with them.

I am deeply thankful for my parents back in China, XU Min and LIU Shufang. Although they grow up and live in the countryside of China, they have always believed that knowledge changes life and fate. They have also been providing unconditional love and support for my graduate studies at the very beginning. I am also sincerely grateful for my wife, Shaoting Zhang, for her companion and encouragement, especially during those tiring and gloomy days during my Ph.D. studies.

Portions of this work were supported by SRC, NSF, Toshiba, SPIE BACUS Scholarship and University Graduate Continuing Fellowship.

# Standard Cell Optimization and Physical Design in Advanced Technology Nodes

Publication No.

Xiaoqing Xu, Ph.D.

The University of Texas at Austin, 2017

Supervisor: David Z. Pan

Integrated circuits (ICs) are at the heart of modern electronics, which rely heavily on the state-of-the-art semiconductor manufacturing technology. The key to pushing forward semiconductor technology is IC feature-size miniaturization. However, this brings ever-increasing design complexities and manufacturing challenges to the \$340 billion semiconductor industry. The manufacturing of two-dimensional layout on high-density metal layers depends on complex design-for-manufacturing techniques and sophisticated empirical optimizations, which introduces huge amounts of turnaround time and yield loss in advanced technology nodes. Our study reveals that unidirectional layout design can significantly reduce the manufacturing complexities and improve the yield, which is becoming increasingly adopted in semiconductor industry [61, 89]. The lithography printing of unidirectional layout can be

tightly controlled using advanced patterning techniques, such as self-aligned double and quadruple patterning. Despite the manufacturing benefits, unidirectional layout leads to more restrictive solution space and brings significant impacts on the IC design automation flow for routing closure. Notably, unidirectional routing limits the standard cell pin accessibility, which further exacerbates the resource competitions during routing. Moreover, for postrouting optimization, traditional redundant-via insertion has become obsolete under unidirectional routing style, which makes the yield enhancement task extremely challenging. Regardless of complex multiple patterning and design-for-manufacturing approaches, mask optimization through resolution enhancement techniques remains as the key strategy to improve the yield of the semiconductor manufacturing processes. Among them, Sub-Resolution Assist Feature (SRAF) generation is a very important method to improve lithographic process windows. Model-based SRAF generation has been widely used to achieve high accuracy but it is time-consuming and hard to obtain consistent SRAFs.

This dissertation proposes novel CAD algorithms and methodologies for standard cell optimization and physical design in advanced technology nodes, which ultimately reduces the design cycle and manufacturing cost of IC design. First, a standard cell pin access optimization engine is proposed to evaluate the pin accessibility of a given standard cell library. We further propose novel pin access planning techniques and concurrent pin access optimizations to efficiently resolve the routing resource competitions, which generates much better routing solutions than state-of-the-art, manufacturing-friendly routers. To systematically improve the manufacturing yield in the post-routing stage, a global optimization engine has been introduced for redundant local-loop insertion considering advanced manufacturing constraints. Finally, we propose the first machine learning-based framework for fast yet consistent SRAF generation with the high quality of results.

# **Table of Contents**

| Ackno   | wledgments                                      | $\mathbf{v}$ |

|---------|-------------------------------------------------|--------------|

| Abstra  | act                                             | vii          |

| List of | f Tables                                        | xiii         |

| List of | f Figures                                       | xiv          |

| Chapt   | er 1. Introduction                              | 1            |

| 1.1     | Advanced Physical Design Challenges             | 7            |

| 1.2     | Overview of this Dissertation                   | 9            |

| Chapt   | er 2. Standard Cell Optimization and Evaluation | 11           |

| 2.1     | Introduction                                    | 11           |

| 2.2     | Preliminaries                                   | 16           |

|         | 2.2.1 Standard Cell Architecture                | 16           |

|         | 2.2.2 Track-based Coloring                      | 17           |

|         | 2.2.3 Design Rule Formulation and Legalization  | 18           |

| 2.3     | Problem Formulation                             | 20           |

| 2.4     | Pin Access Optimization                         | 24           |

|         | 2.4.1 Via Assignment                            | 24           |

|         | 2.4.2 Metal Pattern Optimization                | 29           |

| 2.5     | Pin Access and Cell Layout Co-Optimization      | 34           |

| 2.6     | Experimental Results                            | 36           |

| 2.7     | Summary                                         | 40           |

| Chapter 3. |        | Pin Access and Routing Co-Optimization     | <b>41</b> |

|------------|--------|--------------------------------------------|-----------|

| 3.1        | Intro  | duction                                    | 41        |

| 3.2        | Seque  | ential Pin Access Planning                 | 47        |

|            | 3.2.1  | Preliminaries and Problem Formulation      | 47        |

|            | 3.2.2  | Pin Accessibility Prediction               | 49        |

|            | 3.2.3  | Pin Access Planning Guided Regular Routing | 54        |

|            |        | 3.2.3.1 Single Row Pin Access Graph        | 54        |

|            |        | 3.2.3.2 Local Pin Access Planning          | 57        |

|            |        | 3.2.3.3 Global Pin Access Planning         | 59        |

|            | 3.2.4  | Experimental Results                       | 66        |

| 3.3        | Conc   | urrent Pin Access Optimization             | 75        |

|            | 3.3.1  | Preliminaries and Problem Formulation      | 75        |

|            | 3.3.2  | Pin Access Interval Generation             | 77        |

|            | 3.3.3  | Linear Conflict Set Detection              | 80        |

|            | 3.3.4  | Weighted Interval Assignment Problem       | 81        |

|            | 3.3.5  | Lagrangian Relaxation                      | 83        |

|            | 3.3.6  | Concurrent Pin Access Routing              | 87        |

|            | 3.3.7  | Experimental Results                       | 91        |

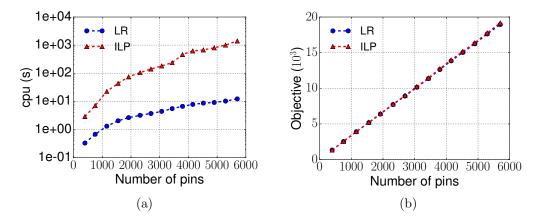

|            |        | 3.3.7.1 Quantifying the LR Suboptimality   | 91        |

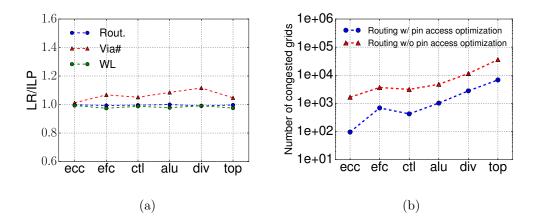

|            |        | 3.3.7.2 Comparison with Related Work       | 93        |

| 3.4        | Sumn   | nary                                       | 98        |

| Chapt      | er 4.  | Redundant Local-Loop Insertion             | 99        |

| 4.1        | Intro  | duction                                    | 99        |

| 4.2        | Prelin | ninaries                                   | 104       |

|            | 4.2.1  | Redundant Local Loop                       | 104       |

|            | 4.2.2  | Advanced Manufacturing Constraints         | 106       |

|            | 4.2.3  | Problem Definition                         | 109       |

| 4.3        | Redu   | ndant Local-Loop Insertion                 | 109       |

|            | 4.3.1  | Timing Impact Analysis                     | 109       |

|            | 4.3.2  | RLLC Generation and Pruning                | 112       |

|            | 4.3.3  | Integer Linear Programming Formulation     | 117       |

|         | 4.3.4  | Special Constraint Structures            | 120 |

|---------|--------|------------------------------------------|-----|

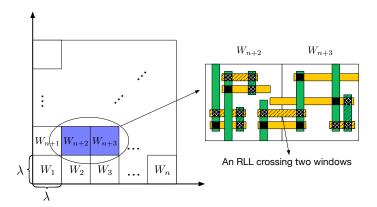

|         | 4.3.5  | IRLS with Incremental Search             | 122 |

| 4.4     | Exper  | rimental Results                         | 126 |

|         | 4.4.1  | Bounded Timing Impact                    | 127 |

|         | 4.4.2  | Comparisons on Different RLLI Schemes    | 129 |

|         | 4.4.3  | Comparisons with Redundant Via Insertion | 135 |

| 4.5     | Sumn   | nary                                     | 139 |

| Chapte  | er 5.  | Sub-Resolution Assist Feature Generation | 140 |

| 5.1     | Introd | luction                                  | 140 |

| 5.2     | Prelin | ninaries                                 | 143 |

|         | 5.2.1  | Mask Optimization Flow                   | 143 |

|         | 5.2.2  | Evaluation Metrics                       | 144 |

| 5.3     | Proble | em Formulation                           | 146 |

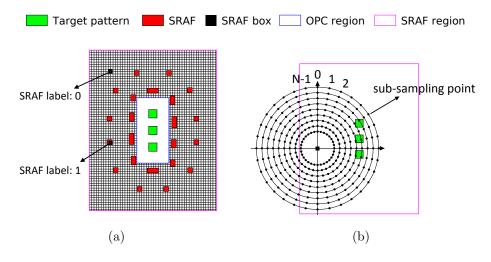

| 5.4     | Classi | ification-based SRAF                     | 148 |

|         | 5.4.1  | Data Preparation                         | 148 |

|         | 5.4.2  | Model Training                           | 153 |

| 5.5     | SRAF   | Generation                               | 154 |

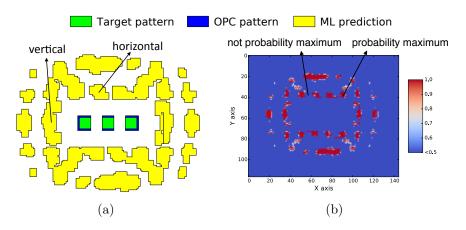

|         | 5.5.1  | Predictions with Probability Maxima      | 154 |

|         | 5.5.2  | SRAF Simplification                      | 155 |

| 5.6     | Exper  | rimental Results                         | 157 |

| 5.7     | Sumn   | nary                                     | 168 |

| Chapte  | er 6.  | Conclusion and Future Work               | 169 |

| Bibliog | graphy | V.                                       | 172 |

| Vita    |        |                                          | 193 |

# List of Tables

| 2.1 | Notations for design rule formulation                               | 9 |

|-----|---------------------------------------------------------------------|---|

| 2.2 | Notations for via assignment                                        | 4 |

| 2.3 | Notations for metal pattern optimization                            | 9 |

| 3.1 | Benchmark statistics for routing                                    | 4 |

| 3.2 | Comparisons on different sequential routing approaches              | 4 |

| 3.3 | Notations for concurrent pin access optimization                    | 8 |

| 3.4 | Comparisons on solution qualities of different routing approaches 9 | 7 |

| 4.1 | Notations for RC networks                                           | 1 |

| 4.2 | Notations for RLLI                                                  | 7 |

| 4.3 | Benchmark statistics for RLLI                                       | 8 |

| 4.4 | Comparisons on sparse routing cases                                 | 1 |

| 4.5 | Comparisons on dense routing cases                                  | 1 |

| 4.6 | Comparisons between DVI and RLLI                                    | 7 |

| 5.1 | Data set statistics for classification                              | 0 |

| 5.2 | Comparisons on different classification models                      | 1 |

| 5.3 | Comparisons on PV band and EPE                                      | 6 |

# List of Figures

| 1.1 | Lithography roadmap in advanced technology nodes [61]                                                                                                                                                             | 2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Integrate proposed studies (light blue boxes) into the physical design flow in advanced technology nodes                                                                                                          | 3  |

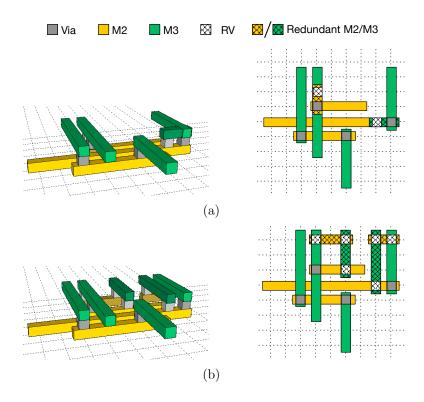

| 1.3 | Unidirectional routing on high-density metal layers, (a) 3D view, (b) top view                                                                                                                                    | 5  |

| 2.1 | Track-based coloring for unidirectional layout patterns, (a) unidirectional target patterns, (b) track-based coloring, (c) SADP with trim masks, (d) SADP with cut masks                                          | 12 |

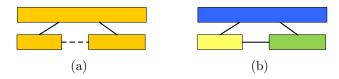

| 2.2 | Line-end extension techniques, (a) anti-parallel line ends, (b) parallel line ends                                                                                                                                | 14 |

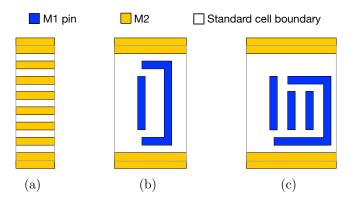

| 2.3 | SC architecture, (a) 7.5 track architecture, (b) "Inverter" layout on M1 and M2, (c) "AND-OR-Inverter" layout on M1 and M2                                                                                        | 17 |

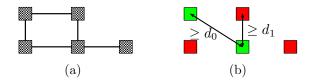

| 2.4 | The potential odd-cycle conflicts of the coloring graph, (a) potential M2 layout, (b) potential odd-cycle conflicts                                                                                               | 18 |

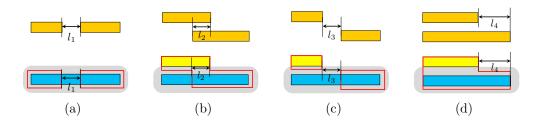

| 2.5 | Design rule formulation, (a) OnTrackSpace, (b) OffTrackOverlap, (c) OffTrackSpace, (d) OffTrackOffset                                                                                                             | 19 |

| 2.6 | (a) Via-1 patterns, (b) layout decomposed to two masks and Via-1 design rules                                                                                                                                     | 20 |

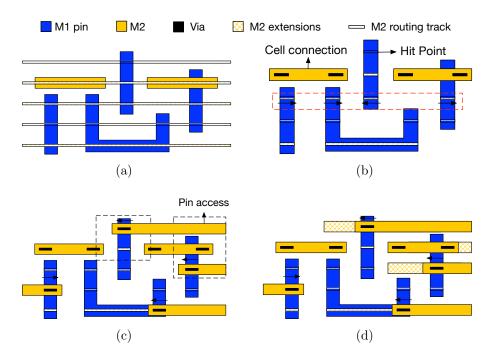

| 2.7 | SC pin access optimization, (a) SC I/O pins and M2 routing tracks, (b) hit points and M2 within-cell connections, (c) a hit point combination with M2 pin access, (d) SADP-friendly pin access with M2 extensions | 22 |

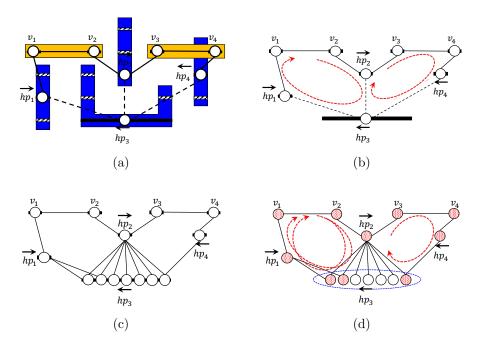

| 2.8 | (a) SC I/O pins and Via-1's for within-cell connections, (b) conflict graph for hit points and Via-1's, (c) conflict graph with grid-based segmentation for long hit points, (d) odd cycles in the conflict graph | 26 |

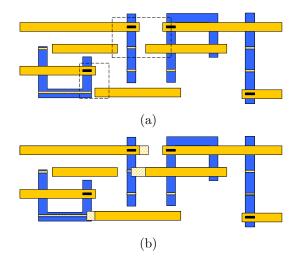

| 2.9 | Pin access and cell connection co-optimization for one hit point combination. (a) design rule violations in layout, (b) MILP-based optimization result                                                            | 37 |

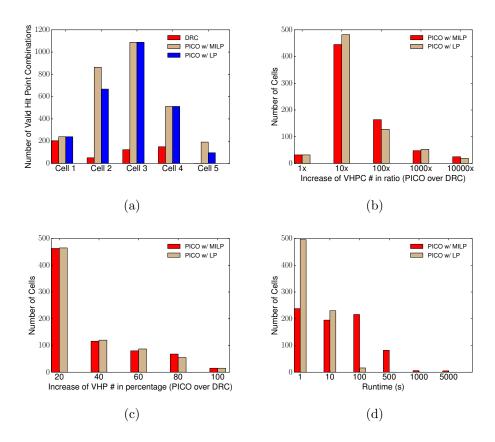

| 2.10 | Standard cell pin accessibility improvement from PICO, (a) increase in number of VHPCs for different cells, (b) increase of VHPC # in ratio across the entire library, (c) increase of VHP # in percentage across the entire library |    |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

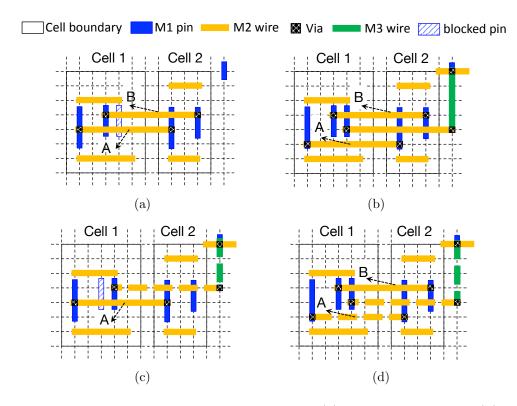

| 3.1  | Pin access for detailed routing, (a) pin access failure, (b) pin access success with smart access point selection, (c) rip-up and reroute failure, (d) rip-up and reroute success                                                    |    |  |  |

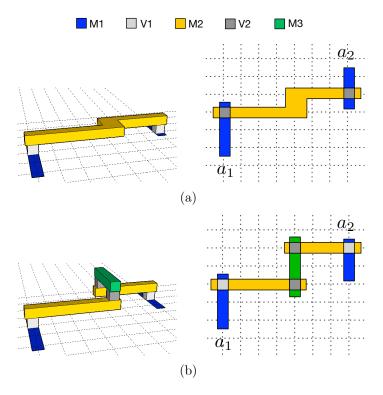

| 3.2  | Two dimensional vs unidirectional routing patterns, 3D view (left) and top view (right), (a) two dimensional routing patterns with a jog, (b) unidirectional routing patterns with extra vias.                                       |    |  |  |

| 3.3  | The inter-cell pin access, (a) two cells placed next to each other and intra-cell pin access introduces a rule violation, (b) fixing the rule violation by line-end extension                                                        |    |  |  |

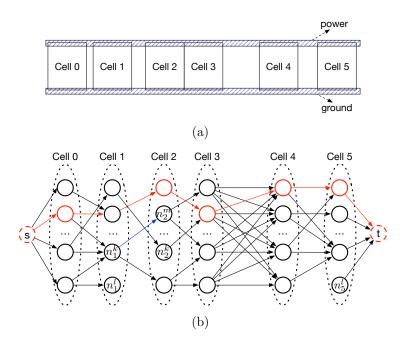

| 3.4  | Single row pin access graph, (a) cell placement, (b) initial pin access graph                                                                                                                                                        | 5. |  |  |

| 3.5  | (a) cell placement with pre-routed wires, (b) simplified pin access graphs with blocked nodes                                                                                                                                        |    |  |  |

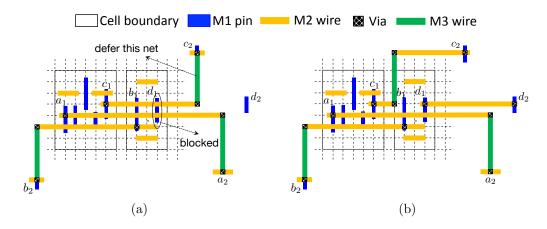

| 3.6  | A net deferring example, (a) defer the routing of net $\{c_1,c_2\}$ , (b) successful routing                                                                                                                                         |    |  |  |

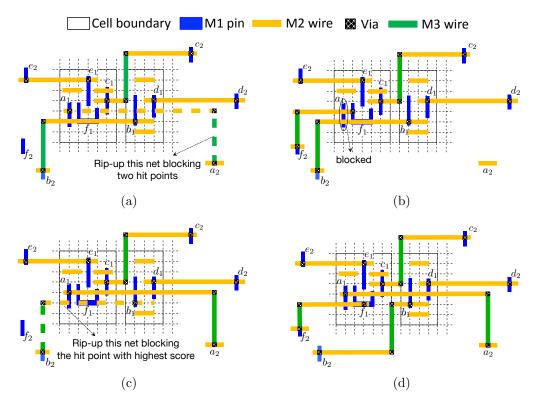

| 3.7  | A rip-up and reroute example, (a) rip up net $\{a_1,a_2\}$ , (b) reroute net $\{f_1,f_2\}$ and pin $a_1$ is blocked, (c) rip-up net $\{b_1,b_2\}$ , (d) successful rip-up and reroute                                                |    |  |  |

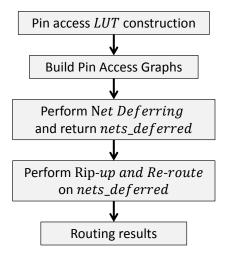

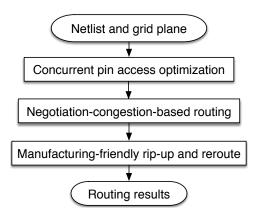

| 3.8  | Sequential routing flow                                                                                                                                                                                                              | 6  |  |  |

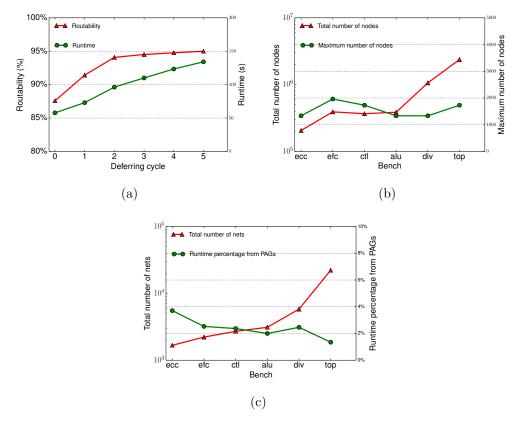

| 3.9  | The computational efforts related to PAGs, (a) routability and runtime tradeoff varying the net deferring cost, (b) PAG size for benchmarks with different sizes, (c) runtime for updating PAGs during detailed routing.             |    |  |  |

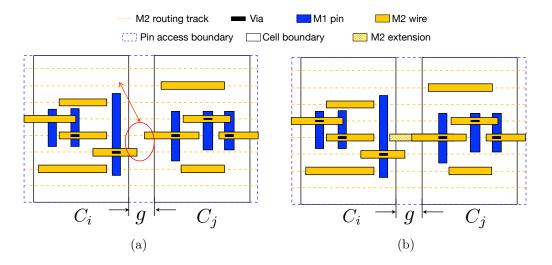

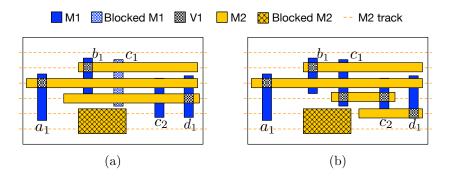

| 3.10 | Pin access interference on the M2 layer, (a) pin access failure, (b) pin access success                                                                                                                                              | 7  |  |  |

| 3.11 | Pin access interval generation, (a) for pin $a_1$ across 3 tracks, (b) for pin $c_1$ and $c_2$ with intra-panel connection                                                                                                           | 7  |  |  |

| 3.12 | Linear conflict set detection for pin access intervals, which can be applied to multiple tracks obtain complete conflict sets                                                                                                        |    |  |  |

| 3.13 | (a) Routing with pin access optimization introducing extra routed wirelength; (b) Routing without pin access optimization introducing extra routed vias                                                                              |    |  |  |

| 3.14 | Concurrent pin access routing flow                                                                                                                                                                                                   | 8  |  |  |

| 3.15 | Comparisons between LR and ILP for different number of pins, (a) runtime, (b) objective value                                                                                                                                        | 9  |  |  |

| 3.16 | (a) LR over ILP after obtaining the routing solutions, (b) the number congested routing grids before rip-up and reroute stage.                                                                                                                |     |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

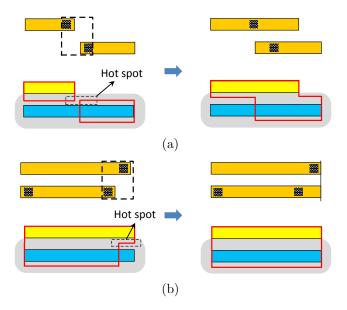

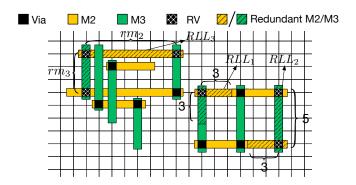

| 4.1  | 3D view (left) and top view (right) of (a) RVI with wire bending, (b) RLLI for unidirectional routing patterns                                                                                                                                |     |  |

| 4.2  | $RLL_1$ , $RLL_2$ and $RLL_3$ with configurations as $3 \times 3 \times 1$ , $5 \times 3 \times 2$ and $rm_3 \times rm_2 \times 3$ , respectively                                                                                             |     |  |

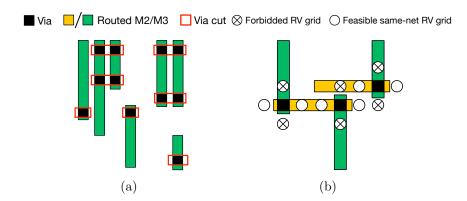

| 4.3  | (a) Via cuts for SAVs, (b) SAV design contraint                                                                                                                                                                                               | 107 |  |

| 4.4  | Via density windows                                                                                                                                                                                                                           | 108 |  |

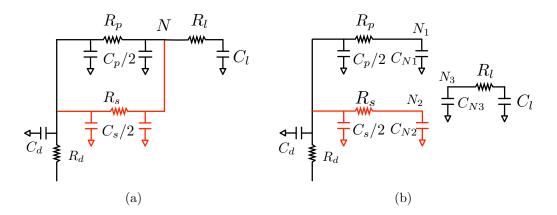

| 4.5  | Elmore delay model for one RLLC, (a) simplified RC network, (c) split RC network                                                                                                                                                              | 112 |  |

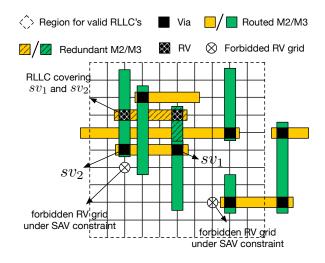

| 4.6  | RLLC generation for one single via                                                                                                                                                                                                            | 113 |  |

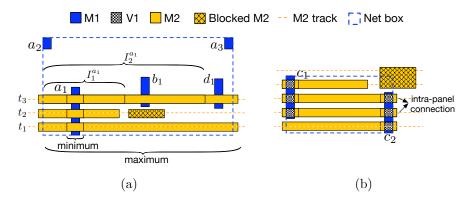

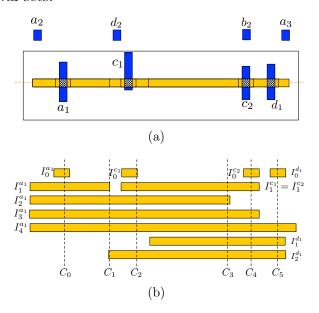

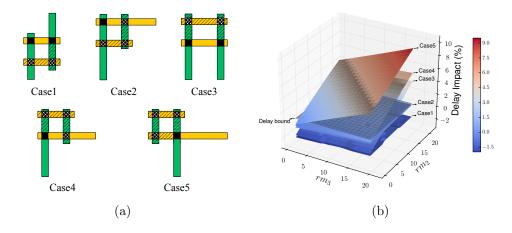

| 4.7  | (a) A complete set of RLLC configurations assuming no detour in a routing solution, (b) timing impact evaluation                                                                                                                              | 129 |  |

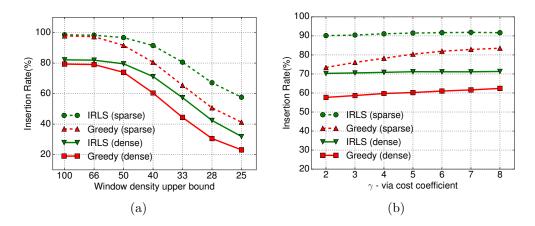

| 4.8  | Parameter analysis with benchmark "alu", (a) degradations of insertion rates as the window density upper bound decreases with $\gamma$ set as 5, (b) change of insertion rate when varying $\gamma$ with window density upper bound set as 40 | 133 |  |

| 4.9  | RLLI vs DVI in terms of timing                                                                                                                                                                                                                | 136 |  |

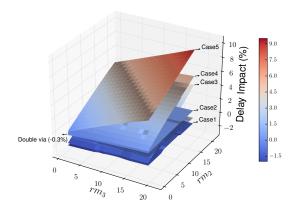

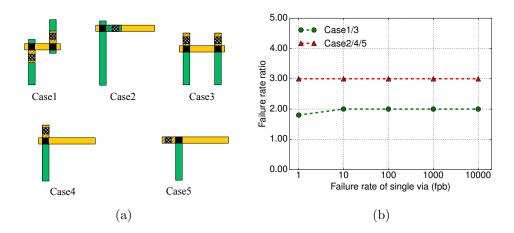

| 4.10 | (a) DVI in different cases and each case corresponds to a case of RLLC in Fig. 4.7(a), (b) failure rate ratio, i.e., RLLI over DVI across various via failure rate                                                                            |     |  |

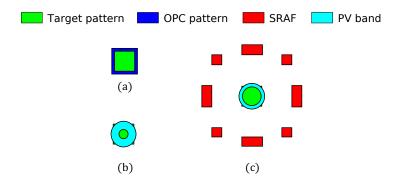

| 5.1  | (a) An isolated contact, (b) printing with OPC, (c) printing with SRAF generation and OPC                                                                                                                                                     | 141 |  |

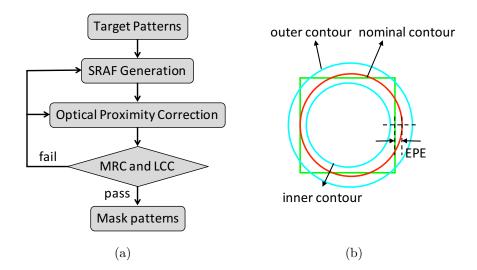

| 5.2  | Mask optimization: (a) mask optimization flow, (b) lithography simulation contours.                                                                                                                                                           | 145 |  |

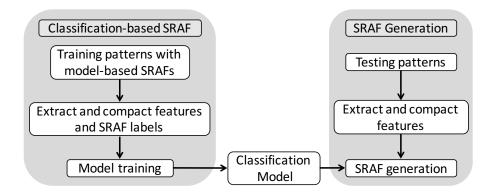

| 5.3  | Machine learning-based SRAF generation                                                                                                                                                                                                        | 148 |  |

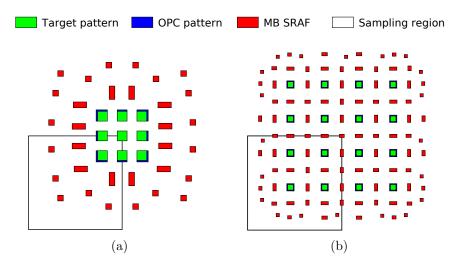

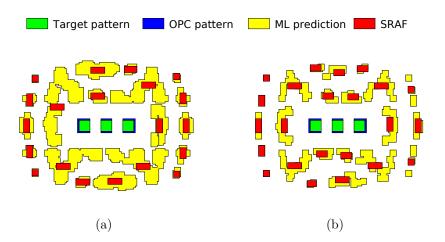

| 5.4  | (a) SRAF label extraction and sampling constraints, (b) CC-CAS at one grid point                                                                                                                                                              | 149 |  |

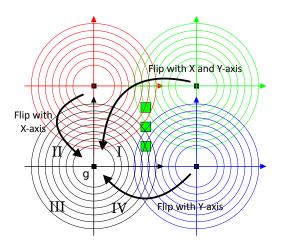

| 5.5  | Feature compaction based on symmetry                                                                                                                                                                                                          | 152 |  |

| 5.6  | SRAF predictions: (a) label predictions, (b) predictions with probability maxima                                                                                                                                                              |     |  |

| 5.7  | Training layout: (a) dense contact patterns, (b) sparse contact patterns                                                                                                                                                                      | 159 |  |

| 5.8  | SRAF generations: (a) label predictions, (b) predictions with probability maxima.                                                                                                                                                             | 163 |  |

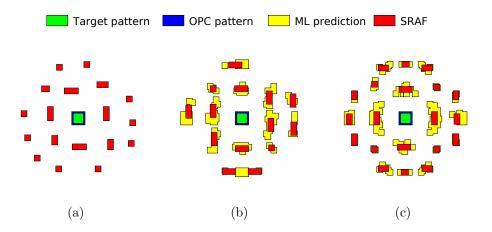

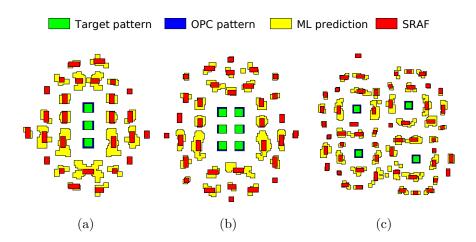

| 5.9  | SRAFs for the isolated contact pattern: (a) model-based, (b) LGR without feature compaction, (c) LGR with feature compaction            | 164 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.10 | Testing contact patterns: (a) $3 \times 1$ dense contact patterns, (b) $3 \times 2$ dense contact patterns, (c) sparse contact patterns | 165 |

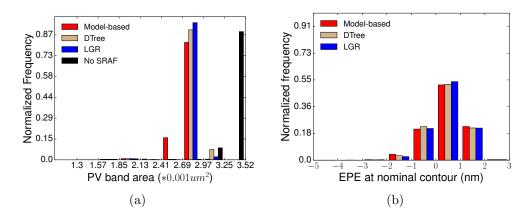

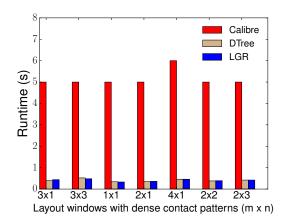

| 5.11 | Comparison among different schemes: (a) PV band distribution, (b) EPE distribution                                                      | 167 |

| 5.12 | Run time comparison among different schemes on different layout windows.                                                                | 168 |

## Chapter 1

## Introduction

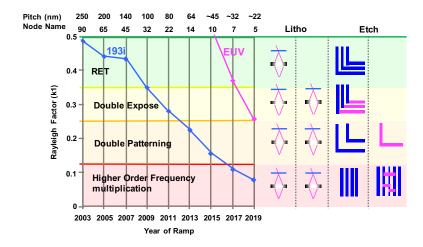

As technology nodes continue to scale down, minimum feature size of the manufacturing process has been shrinking well beyond the resolution limits of the state-of-the-art photolithography tool, i.e., 193nm wavelength immersion lithography with complex resolution enhancement techniques (RETs). Due to the delay of emerging lithography candidates, such as extreme ultraviolet (EUV) lithography, electron-beam lithography (E-beam) and directed self-assembly (DSA), multiple patterning lithography (MPL) with complicated design-for-manufacturing (DFM) techniques has been widely adopted in semiconductor industry to further push the geometric scaling in advanced technology nodes as shown in Fig. 1.1. For example, the 14nm node has introduced double patterning lithography into the semiconductor manufacturing process to maintain the pitch scaling. The 10nm node further increases the level of design complexities and manufacturing constraints by forcing triple patterning lithography and sidewall image transfer solutions [61]. In general, there exist two types of MPL, Litho-Etch-Litho-Etch (LELE) type and self-aligned type. LELE-type of MPL splits the target layout into different masks, which allows stitch insertions and two-dimensional patterns [49,98,113,114,122], but coloring and overlay compensation schemes become extremely complicated for

Figure 1.1: Lithography roadmap in advanced technology nodes [61].

triple patterning lithography and beyond [28, 55, 65, 99, 118, 120]. Self-aligned type of MPL depends on sidewall image transfer techniques, which can minimize electrical variations from overlay and line-edge-roughness, but induces sophisticated coloring and metal line-end constraints for two-dimensional geometries [67, 71, 93]. Regardless of different manufacturing solutions, MPL introduces a significant amount of DFM constraints and design complexities, such as layout coloring, overlay compensations and restrictive design rules, into the physical design flow.

To simplify the DFM constraints aforementioned, unidirectional layout patterns are strongly preferred for lower metal layers with high-density metal patterns in advanced technology nodes [43,82,84,89,119]. Unidirectional layout significantly reduces the coloring complexities while using a track-based coloring scheme, because each layout pattern created by the physical design

tool automatically has a legal coloring solution. However, the unidirectional layout style still generates a set of challenging restrictions, such as restrictive solution space and sophisticated metal line-end rules. This further induces routing-limited scaling in the 7nm technology node, which means routing densities and routing resource competitions on lower metal layers are becoming increasingly high, such that design area has to be relaxed to obtain routing closure [61].

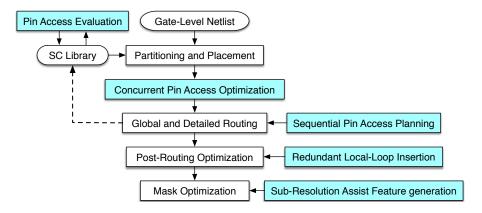

Figure 1.2: Integrate proposed studies (light blue boxes) into the physical design flow in advanced technology nodes.

Despite the problem complexities aforementioned, a typical physical design flow relies heavily on empirical optimizations in an iterative manner as shown in Fig. 1.2, which incurs huge amounts of human intervention and turnaround time. Our study identifies the root cause lies in the restrictive solution space from unidirectional routing, which imposes significant impacts on different design stages across the standard cell (SC) library design, routing and post-routing optimization. Besides the complex DFM optimization

through unidirectional layout design, mask optimization remains as the key strategy to improve the lithographic process window and the yield of the volume production in advanced technology nodes [10, 12, 30, 54, 95]. This means a holistic approach is strongly needed to obtain fast and high-quality design closure in advanced technology nodes.

For the SC library design, our study reveals that pin accessibility is a major bottleneck for unidirectional routing closure. To improve standard cell pin access, one simple option is to go through the physical design flow using a specific design instance. This would detect "hard-to-access" cells for iterative standard cell Input/Output (I/O) pin optimizations in a manual procedure as denoted by the dashed line in Fig. 1.2 [61]. This straightforward approach leads to large turnaround time and design dependency, which motivates the pin access evaluation research for fast and accurate evaluations of standard cell pin accessibility.

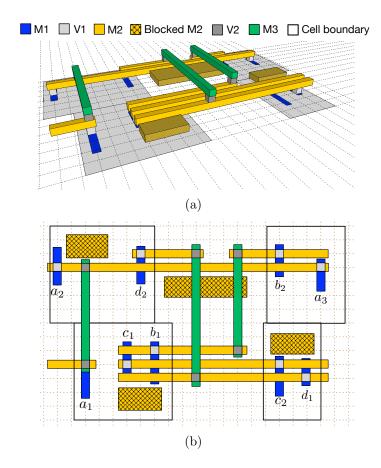

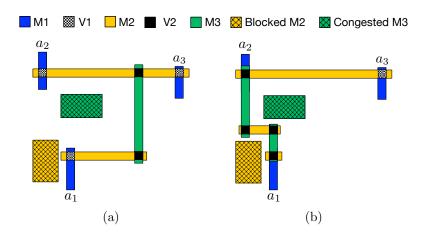

For the routing stage, a router is required to follow complex manufacturing rules and obtain net connections using lithography-friendly routing patterns. However, in advanced technology nodes, routing on lower metal layers is becoming more complicated than dealing with manufacturing constraints. An example of unidirectional routing on metal-2 (M2) and metal-3 (M3) layers is shown in Fig. 1.3. This routing instance includes 4 cells, 9 metal-1 pins  $(a_1, a_2, a_3, b_1, b_2, c_1, c_2, d_1, d_2)$  and 4 nets  $(\{a_1, a_2, a_3\}, \{b_1, b_2\}, \{c_1, c_2\})$  and  $\{d_1, d_2\}$ . Under a routing grid with horizontal and vertical tracks, we observe severe routing resource competitions among multiple nets, especially on the

Figure 1.3: Unidirectional routing on high-density metal layers, (a) 3D view, (b) top view.

M2 layer, where only a small number of horizontal routing tracks overlaps each metal-1 pin within cell boundaries and one routing track may be shared among different pins [111,112]. Thus, it is important to globally allocate routing resources among different pins so that all nets can be connected. In addition, routing resources on lower metal layers, such as M2 and M3, are primarily reserved for short nets. For short-net routing, via minimization is particularly important in advanced technology nodes [24]. Furthermore, compared to the

previous routing studies [6,81], unidirectional routing generates a valuable opportunity to explore the solution space using interval-based search instead of grid-based search. This motivates the research for novel approaches, including sequential pin access planning and concurrent pin access optimization, to effectively resolve routing resource competitions and enable via minimizations.

For the post-routing optimization stage, the unidirectional routing style has made conventional redundant via insertion obsolete for yield improvement. This is because unidirectional routing patterns forbid off-track routing, i.e., wire bending, for the metal coverage of redundant vias. To enhance the yield of unidirectional routing patterns, we identify redundant local-loop insertion as a new way of inserting redundant vias due to its compatibility with the unidirectional layout style [8, 15]. However, redundant local loop insertion introduces complex long-range conflict constraints and timing impacts are no longer negligible for certain redundant local loop candidates. This motivates the research for global optimization techniques to achieve better performance than the traditional approaches.

For the mask optimization stage, to date, the 193nm wavelength immersion lithography with low k1 value is still the mainstream technique to achieve smaller feature size. However, low image contrast and complex target pattern shapes make it extremely difficult for low-k1 lithography to obtain acceptable lithographic process windows [86]. Besides the complex DFM techniques, mask optimization through resolution enhancement techniques remains as the key strategy to improve the lithographic process window and the yield of vol-

ume production in advanced technology nodes [10,12,30,54,95]. Among them, SRAF generation is particularly important to improve the lithographic process window of target patterns. Conventional SRAF generation approaches suffer from large computational overhead or lithographic performance degradations. This motivates the research to adopt machine learning-based approaches for SRAF generation, which demonstrates a new perspective to achieve promising trade-offs between computational efforts and lithographic performance.

This chapter first briefly summarizes the aforementioned physical design challenges in advanced technology nodes. We further overview this dissertation in terms of novel solutions to advanced physical design challenges.

## 1.1 Advanced Physical Design Challenges

Standard Cell Optimization and Evaluation Standard cell library design involves significant amounts of human interventions because the industrial routine follows full custom design and optimization. Typically, designers depend on figures of merit from placed and routed digital blocks to iteratively assess and improve the quality of a standard cell library, which incurs large turnaround time for the design closure. Therefore, an automated standard cell library optimization and evaluation tool is crucial for the designers to obtain quick feedback on the layout design quality considering complex DFM constraints.

Pin Access and Routing Co-Optimization With unidirectional routing, only a small number of routing tracks are available to access each

standard cell I/O pin, which further leads to severe pin access interference, i.e., routing interference caused by pin access, on lower metal layers. The pin access interference significantly degrades the routing solution quality, which makes pin access and routing co-optimization extremely important for unidirectional routing closure in advanced technology nodes.

Redundant Local-Loop Insertion The conventional redundant-via insertion with two-dimensional metal patterns has become obsolete under restrictive unidirectional routing style, because the off-track metal patterns covering redundant vias are strictly forbidden. To enhance the yield of metal and via patterns, redundant local-loop insertion is a new way of inserting redundant vias that is compatible with unidirectional routing but induces complicated long-range conflict constraints, which typically require global optimization techniques to resolve.

Sub-Resolution Assist Feature Generation Regardless of complex DFM techniques, mask optimization through resolution enhancement techniques remains as the key strategy to improve the yield of the semiconductor manufacturing processes. Among them, Sub-Resolution Assist Feature (SRAF) generation is a very important method to improve lithographic process windows. Conventional SRAF generation approaches suffer from large computational overhead or lithographic performance degradations. We propose machine learning-based approaches for fast and high-quality SRAF generations.

## 1.2 Overview of this Dissertation

This dissertation proposes novel CAD algorithms and methodologies to systematically enable standard cell optimization and physical design in advanced technology nodes.

Chapter 2 presents the first cell-level evaluation engine to quantify the pin accessibility of a given standard cell library. The proposed study is based on local routing pattern enumeration and optimization, which has been prototyped by the leading IP vendor, ARM Inc.

Chapter 3 proposes pin access and routing co-optimization techniques to enhance the routing solution quality in advanced technology nodes. To efficiently resolve the severe pin access interference, we first propose pin access planning schemes to improve the pin accessibility during a sequential routing procedure. We further propose concurrent pin access optimization techniques to obtain fast and high-quality routing solutions. We demonstrate that the pin access and routing co-optimization studies can provide much better solution qualities than state-of-the-art manufacturing-friendly routers.

Chapter 4 presents the first global optimization engine for redundant local-loop insertion with bounded timing impact while accommodating advanced manufacturing constraints. This proposed study features an optimal integer linear programming formulation and scalable iterative linear programming solving with an incremental search scheme.

Chapter 5 proposes a machine learning-based framework for sub-resolution

assist feature generation. The classification-based learning model can deliver competitive lithography performance with significant speed up compared with a commercial setup for SRAF generation. The proposed SRAF generation approach has been prototyped within the memory division in Toshiba Microelectronics.

Chapter 6 summarizes this dissertation and discusses potential future research directions.

# Chapter 2

# Standard Cell Optimization and Evaluation

## 2.1 Introduction

Due to the resolution limits of 193nm photolithography, multiple patterning techniques and unidirectional layout have been widely used to extend semiconductor process technology scaling [83, 93, 117]. The design rules that enable multiple patterning (color decomposition, forbidden pitches, etc.) are much more restrictive than the basic rules used previously in technology nodes larger than 20nm. In addition, the expectation to continue Moore's Law translates to the same density and area scaling every node. That means the physical design tools need to access Standard Cell (SC) Input/Output (I/O) pins in more congested areas with increasingly restrictive rules.

One way that SC designers can assist physical design tools is through intelligent, optimized SC I/O pin design. Unfortunately, the complex design rules and neighbor interactions that exist due to various multiple patterning techniques like Litho-Etch-Litho-Etch (LELE) and Self-Aligned Double Patterning (SADP) make human-driven layout almost impossible at 14nm techniques.

This chapter is based on the journal "Xiaoqing Xu, Brian Cline, Greg Yeric, Bei Yu, and David Z Pan. Self-aligned double patterning aware pin access and standard cell layout co-optimization. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 34(5):699712, 2015." I am the main contributor in charge of problem formulation, algorithm development and experimental validations.

nologies and below. That means automated SC layout design and optimization are needed to provide flexible I/O pin access.

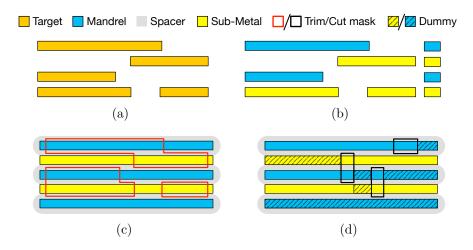

Figure 2.1: Track-based coloring for unidirectional layout patterns, (a) unidirectional target patterns, (b) track-based coloring, (c) SADP with trim masks, (d) SADP with cut masks.

SADP, in particular, is a viable candidate for lower layer metalization with regular patterns at the 10nm technology node, due to better overlay and Line Edge Roughness (LER) [72] control compared to LELE. To deploy the SADP technique for routing layers in practical designs, designers need to ensure that layout patterns are SADP-friendly to achieve successful layout decomposition. The SADP layout decomposition problem has been studied, as shown in [11, 31, 103, 123]. For the regular or unidirectional layout, the line-space array decomposition method can efficiently decompose SADP-based geometries and achieve good pattern fidelity and process margin [67,93]. An example of line-space array decomposition is demonstrated in Fig. 2.1. Fig. 2.1(a) shows regular layout on horizontal tracks. We can assign different

colors to patterns on neighbor tracks in Fig. 2.1(b). With spacer defining the gap between neighboring patterns, the trim mask and cut mask obtain the target layout as demonstrated in Fig. 2.1(c) and Fig. 2.1(d), respectively. For the cut mask solution in Fig. 2.1(d), dummy patterns may be created without affecting the underlying electrical connections.

To incorporate SADP constraints into early design stages, there are several studies [26, 29, 52, 76] dealing with the SADP-aware routing problem. However, to date, works studying how multiple patterning and decomposition impact SC I/O pin design are lacking, especially as pin congestion and routability become increasingly critical to the overall physical design results. Since most modern-day SC designs primarily use Metal-1 (M1) for local connections and I/O pins, Metal-2 (M2) design is essential for SC I/O pin access. There are several works [80, 81] on detailed routing accounting for pin access. [80] focuses on the gridless routing and proposes efficient algorithms to improve the pin accessibility and routability. [81] presents the formulation and solution for the detailed routing for dense pin clusters. None of these previous studies explicitly addresses the pin accessibility problem at the SC level under complex SADP-specific constraints.

SADP-based M2 wires, in particular, present a new set of problems to SC I/O pin access. Specifically, because of the decomposition of SADP into the mandrel and trim masks, one cannot simply rely on via locations to determine line-end positions of M2 wires. As shown in Fig. 2.2, SADP yield can be enhanced by line-end extensions that are dependent on both via

Figure 2.2: Line-end extension techniques, (a) anti-parallel line ends, (b) parallel line ends.

placement and neighboring wire placement. For example, in Fig. 2.2(a) and (b), respectively, the extension of anti-parallel line ends and parallel line-end alignment both help to avoid hot spots on the trim masks [71].

In general, the ideal location of geometries is not as straight-forward under SADP constraints and is more dependent on the neighborhood around the geometry in question. This means all SADP-based metal designs, including pin access and within-cell connections have to be optimized simultaneously during the I/O pin design phase. Previously, line-end extension techniques have been deployed to deal with the cut mask manufacturability in [124,125]. To minimize the effective gaps in the layout, [125] proposes a greedy optimal algorithm to extend the line ends of metal wires. [124] presents a mask cost

reduction formulation to improve the layout manufacturability with the lineend extension techniques. Alternatively, our study enables trim mask friendly, SC-level pin access design under SADP constraints, a priori, before the SC library is ever used in a placed-and-routed block.

In addition, the Via-1 layer is used to connect the M2 wires and M1 I/O pins. Due to the high density of Via-1's in future technology nodes, multiple patterning, e.g., LELE, is needed to manufacture the Via-1 layer. Hence, for the 10nm technology used in this study, we need to enable LELE friendly Via-1 design to achieve legal pin access at the SC level. Determining the double patterning decomposability of given layout patterns is a well-studied topic [49, 98, 113, 114, 122]. If the conflict graph deduced from the given layout patterns does not contain odd cycles, the layout patterns are double patterning (LELE) friendly. The odd-cycle free LELE-aware Via-1 design is equally important to determining SC pin access as SADP-friendly M2 design.

This chapter proposes the first study on the SC-level I/O pin access problem and prototype our methodology on the predictive 10nm SC library. To solve this problem efficiently, we present a Depth First Search (DFS)-based method to achieve LELE-friendly Via-1 assignment and a Mixed Integer Linear Programming (MILP)-based technique that simultaneously optimizes the M2 wires for pin access and within-cell connections of SCs. Moreover, using the backtracking method, we extend this technique to each pin access scenario and maximize the pin accessibility of the predictive 10nm library.

## 2.2 Preliminaries

#### 2.2.1 Standard Cell Architecture

Due to complex design-for-manufacturing constraints, there are finite options of Standard Cell (SC) architecture for a specific advanced technology node [18,61,92]. Fig. 2.3 illustrates a 7.5-track SC architecture at 7nmtechnology node. An SC architecture pre-determines the cell height, which is typically an integer multiple of the M2 routing pitch. The SC boundary decides the region of intra-cell layout patterns on M1 and lower manufacturing layers, which are used for intra-cell connections and SC I/O pins. While occasional M2 usages are allowed for intra-cell connections for complex SCs [105], M2 and upper layers are mainly used for routing connections. Horizontal M2 tracks in the middle of Fig. 2.3(a) are routing tracks used by the router for cell-to-cell I/O connections. The M2 tracks on the top and bottom of SC boundary typically align with the power/ground rails of a specific design, providing a robust power/ground network. The M1 I/O pins of "Inverter" and "AND-OR-Inverter" are shown in Fig. 2.3(b) and Fig. 2.3(c), respectively. In the routing level, these M1 I/O pins can only be accessed with fixed number of M2 routing tracks. As M2 routing patterns are purely unidirectional, there exists a limited number of M2 accessing points (see Fig. 2.7(b)) for each I/O pin, which makes routing density and resource competition increasingly high on lower metal layers. This also makes SC pin access optimization on lower metal layers particularly important for unidirectional routing closure.

Figure 2.3: SC architecture, (a) 7.5 track architecture, (b) "Inverter" layout on M1 and M2, (c) "AND-OR-Inverter" layout on M1 and M2.

#### 2.2.2 Track-based Coloring

The continued geometric scaling of process technology depends on multiple patterning and increased layout regularity [93]. Thus, at the 10nm node and beyond, we assume that the M2 layout will be extremely regular. Furthermore, in the 10nm commercial technology we used, the preferred direction of M2 routing is horizontal. After studying the M2 routing tracks, we make the following observation.

**Observation 1.** A single color is assigned to metal patterns on even routing tracks. The alternate color is then assigned to metal patterns on odd routing tracks.

M2 routing is becoming increasingly congested as we continue to scale towards the 10nm technology node because of the increasing density of transistors and SC I/O pins. Hence, increasing M2 congestion leads to a higher likelihood of having M2 wires on neighbor tracks at the same time, which

Figure 2.4: The potential odd-cycle conflicts of the coloring graph, (a) potential M2 layout, (b) potential odd-cycle conflicts.

leads to the layout patterns illustrated in Fig. 2.4. In Fig. 2.4(a), a solid edge denotes a coloring conflict and a dashed edge denotes a potential coloring conflict. Fig. 2.4(b) demonstrates how a dashed edge changes to solid edge if we assign different colors to M2 wires on the same track, which leads to an odd-cycle conflict in the coloring graph. The SADP technique does not allow stitches during the layout decomposition stage, which means odd-cycle conflicts must be strictly forbidden in SADP-friendly layout patterns [11]. The color assignment strategy from Observation 1 avoids potential odd cycles in the coloring stage for SADP-friendly layout.

#### 2.2.3 Design Rule Formulation and Legalization

Table 2.1 defines SADP-specific notations for the 10nm technology node [66]. First, the minimum area constraint of the M2 layout is converted to the minimum wire length design rule  $(l_0)$  due to the fixed width of M2 wires. Then, we define the space between M2 line ends on the same routing track as  $\mathbf{OnTrackSpace}(l_1)$ , as shown in Fig. 2.5(a). We use  $\mathbf{OffTrackOverlap}(l_2)$  and  $\mathbf{OffTrackSpace}(l_3)$  to define the prohibited region for the anti-parallel M2 wires [66], as shown in Fig. 2.5(b) and Fig. 2.5(c), respectively. Finally,

Table 2.1: Notations for design rule formulation

|                 | MetalWidth               | w                                                                                                                   |  |  |

|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| M2 layer        | MetalSpace               | s                                                                                                                   |  |  |

|                 | $\min MetalArea$         | $A_{min}$                                                                                                           |  |  |

| Spacer deposits | SpacerDepositWidth       | $w_{sp}$                                                                                                            |  |  |

| Trim mask       | minResistWidth           | $w_r$                                                                                                               |  |  |

| IIIII IIIask    | $\min Resist Space$      | $s_r$                                                                                                               |  |  |

|                 | EtchBias                 | $w_e$                                                                                                               |  |  |

|                 | minMetalLength (Rule 0)  | $l_0 \ge \frac{A_{min}}{w}$                                                                                         |  |  |

|                 | OnTrackSpace (Rule 1)    | $l_1 \ge w_r - 2 \cdot w_e$                                                                                         |  |  |

| Design rules    | OffTrackOverlap (Rule 2) | $l_2 \ge s_r + 2 \cdot w_e$                                                                                         |  |  |

|                 | OffTrackSpace (Rule 3)   | $\begin{vmatrix} l_3 \ge \sqrt{(w_r - 2 \cdot w_e)^2 - w_{sp}^2} \\ l_4 \ge w_r & \text{or}  l_4 = 0 \end{vmatrix}$ |  |  |

|                 | OffTrackOffset (Rule 4)  | $l_4 \ge w_r$ or $l_4 = 0$                                                                                          |  |  |

for parallel M2 wires illustrated in Fig. 2.5(d), the line-end design constraint is defined as  $OffTrackOffset(l_4)$ . Table 2.1 summarizes the design rules for M2 layout patterns [66, 71].

Figure 2.5: Design rule formulation, (a) OnTrackSpace, (b) OffTrackOverlap, (c) OffTrackSpace, (d) OffTrackOffset.

The minimum coloring distance  $(d_0)$  and minimum different mask distance  $(d_1)$  are introduced to enable LELE friendly Via-1 assignment. Suppose successful layout decomposition of Via-1 patterns from Fig. 2.6(a) to Fig. 2.6(b),  $d_0$  denotes the minimum center to center spacing of Via-1's on the

same mask and  $d_1$  denotes the minimum center to center spacing of Via-1's on different masks.

Figure 2.6: (a) Via-1 patterns, (b) layout decomposed to two masks and Via-1 design rules.

## 2.3 Problem Formulation

The SC-level pin access optimization involves both LELE-aware Via-1 assignment and SADP-aware M2 wire design. Our I/O pin access design and optimization is based on the practical layout of SCs. For each cell in the library, we observe that I/O pins generally exist on either the M1 or M2 layer. To properly formulate the pin access design and optimization problem, we have the following definitions.

**Definition 1** (Hit Point). The overlap of an M2 routing track (which is predetermined by the place and route tool) and an I/O pin shape is defined as a Hit Point for that particular I/O pin.

Each hit point determines the range of positions for the corresponding Via-1 (the M1 to M2 connection). In the 10nm technology used, M2 is unidirectional and runs horizontally. Thus, for each hit point, there are two accessing directions possible, either from left to right or from right to left. To

access one hit point, we first need to determine the legal location for the Via-1 connection. Then, we need to design the M2 wire assuming one accessing direction for the hit point. In order to connect to every I/O pin in a cell, we need to determine the accessing directions for a set of hit points. Hence, we have several definitions as follows.

**Definition 2** (Hit Point Combination). A set of hit points (with a defined access direction, left or right) where each I/O pin in the SC is accessed exactly once is defined as a Hit Point Combination for that cell.

**Definition 3** (Valid Hit Point Combination). If a hit point combination induces zero design rule violations, it is considered a Valid Hit Point Combination. Otherwise, it is considered to be invalid.

**Definition 4** (Valid Hit Point). If a hit point can be accessed from both directions within some valid hit point combinations for one cell, it is considered a valid hit point. Otherwise, it is considered to be invalid.

An example of the I/O pin access design for one hit point combination is shown in Fig. 2.7. Fig. 2.7(a) demonstrates the M1 I/O pin layout and M2 routing tracks running horizontally above M1. Fig. 2.7(b) shows how the hit points, which represent valid Via-1 locations for I/O pin access, are derived from the overlap of M2 routing tracks and the M1 I/O pins. For most hit points, the length of the hit point is short because it is decided by the minimum width of the vertical M1. However, if an M1 wire runs horizontally, this leads to a long hit point, which allows more flexibility for the Via-1 position. The

Figure 2.7: SC pin access optimization, (a) SC I/O pins and M2 routing tracks, (b) hit points and M2 within-cell connections, (c) a hit point combination with M2 pin access, (d) SADP-friendly pin access with M2 extensions.

set of hit points within the dashed box in Fig. 2.7(b) shows one hit point combination and the dark arrows denote the arbitrary accessing directions chosen for the hit points. Fig. 2.7(c) illustrates one way to access the cell using that hit point combination. After choosing one hit point for each I/O pin and the accessing direction for that hit point, we need to determine the legal Via-1 locations for that hit point combination such that the final Via-1 patterns are LELE friendly. Given the LELE-legal Via-1 assignment, the M2 wires can be designed for pin access, accounting for the minimum enclosure design rule for M2 over Via-1. The dashed boxes in Fig. 2.7(c) denote all pairs

of line ends that cause hot spots in trim mask designs. Fig. 2.7(d) demonstrates that line-end extension techniques can be adopted to fix those hot spots in the trim mask.

In SC design, it is important to achieve both LELE-aware Via-1 assignment and SADP-aware M2 design, i.e., all hot spots are fixable via line-end extension techniques. However, the engineering efforts and iterations involved to fix all of the potential hot spots across the SC library are too large for the average layout design team. Therefore, a general methodology is needed to determine optimal Via-1 assignment and design the M2 wires for pin access and within-cell connections simultaneously. We can now define the SADP-aware pin access optimization problem as follows.

**Problem 1** (Pin Access Optimization (PAO)). Given the SC layout and a specific hit point combination, determine whether or not it is possible to achieve a legal LELE-friendly Via-1 assignment and subsequently optimize the M2 wires for pin access and within-cell connections given the Via-1 assignment under SADP constraints. If possible, show legal Via-1 assignment and all SADP-friendly M2 wires.

As shown in Fig. 2.7(b), we may have multiple hit points for one I/O pin, which leads to numerous hit point combinations for one cell. For one SC, we define the pin access and cell layout co-optimization problem as follows.

**Problem 2** (PICO). Given the SC layout, the Pin Access and Cell Layout Co-Optimization (PICO) problem is to show all Via-1 assignment and M2 wiring cases with successful PAO's and maximize the pin access flexibility under LELE and SADP constraints.

# 2.4 Pin Access Optimization

Given a hit point combination, we seek the LELE-friendly Via-1 assignment, based on which we pre-design the M2 wires for pin access. Then, we propose an MILP-based method to enable efficient SADP-aware M2 design. Finally, the Linear Programming (LP) relaxation is presented to explore the trade-off between runtime and performance for the pin access optimization.

Table 2.2: Notations for via assignment

| ~        |                                                              |

|----------|--------------------------------------------------------------|

| $v_k$    | the $k^{th}$ Via-1 for cell connections                      |

| $hp_k$   | the $k^{th}$ hit point within given hit point combination    |

| $hp_k^m$ | the $m^{th}$ candidate Via-1 location for $k^{th}$ hit point |

| $S_v$    | the LELE-Aware Via-1 assignment                              |

| $S_v^o$  | the optimal LELE-Aware Via-1 Assignment                      |

| $g_0$    | the Via-1 grid size                                          |

### 2.4.1 Via Assignment

In general, there are two kinds of Via-1's at the SC level. The first kind is for internal M1 to M2 (within-cell) connections due to the complexity of SC layout in advanced technology nodes. These connections cannot be modified in the pin access optimization stage. The other kind is for the pin access connections from M2 wires to M1 I/O pins, which is the design target in the Via-1 assignment problem. For instance, in Fig. 2.8(a), there are four internal

Via-1's denoted as  $v_1 - v_4$  and our target is to determine the location of Via-1's for the four hit points denoted as  $hp_1 - hp_4$ . We can drop the Via-1's in the center of short hit points, such as  $hp_1$ ,  $hp_2$  and  $hp_4$ . However, long hit points, such as  $hp_3$ , allow for more flexibility for the Via-1 location. We can build the conflict graph for the Via-1 layer given a specific hit point combination, as illustrated in Fig. 2.8(b). We put a solid edge between conflicting Via-1's of which locations are decided. A dashed edge is added when the location of some Via-1 is not decided and there exists a potential conflict between two Via-1's. For example, the Via-1 associated with the long hit point in Fig. 2.8(b) always conflicts with the Via-1 for  $hp_2$ , but only conflicts with that for  $hp_1$  when dropped on the left end and conflicts with that for  $hp_4$  when dropped on the right end.

To make the best use of the flexibility from the long hit point, we propose a grid-based segmentation, which leads to multiple potential Via-1 candidates for a hit point. For example, we can see several Via-1 candidates for  $hp_3$  in Fig. 2.8(c). The grid size depends on the granularity needed and is constrained by the manufacturing grid imposed by a particular technology node, i.e., the grid size chosen must be greater-than-or-equal-to the manufacturing grid. Related notations are given in Table 2.2. There is an accessing direction assigned to each hit point within the given hit point combination. Hence, we prefer the legal Via-1 location to be on the right end of  $hp_3$  because the hit point will be accessed from right to left. The right most legal Via-1 candidate for  $hp_3$  leads to shortest M2 wire to access that hit point. To dif-

Figure 2.8: (a) SC I/O pins and Via-1's for within-cell connections, (b) conflict graph for hit points and Via-1's, (c) conflict graph with grid-based segmentation for long hit points, (d) odd cycles in the conflict graph.

ferentiate multiple Via-1 candidates for the long hit point, we assign a cost to each candidate according to the accessing direction and distance from the Via-1 location to the left/right end of the hit point. For instance, the cost of the right most Via-1 for the long hit point in Fig. 2.8(c) will be 0 and the cost of the second right most Via-1 will be  $g_0$ . In general, from right to left, the cost of the  $n^{th}$  Via-1 will be  $(n-1)*g_0$ . We assign zero cost to internal Via-1's and Via-1's associated with short hit points. After the grid-based segmentation and cost assignment for each Via-1 candidate, we can build the whole conflict graph for the Via-1 layer, as illustrated in Fig. 2.8(d). There is no conflict among Via-1 candidates for the same hit point.

The overall objective of this step is to choose a set of Via-1 locations, including existing Via-1's for internal cell connections and target Via-1's for each hit point, such that the total cost is minimized and the Via-1 layer is LELE compliant. It is a well-established argument that the layout is LELE compliant if and only if the conflict graph deduced does not contain odd cycles [49]. This means that odd cycles are forbidden in the optimal legal Via-1 assignment.

Algorithm 1 demonstrates the details for achieving optimal LELEfriendly Via-1 assignment. Lines 3-16 explain how to build the conflict graph given existing Via-1's for cell connections and a specific hit point combination. In line 18, all of the odd cycles in the conflict graph are reported (e.g., the 3 odd cycles in Fig. 2.8(d) would be reported). If an odd cycle is detected in the conflict graph, the conflicting set of Via-1 candidates cannot be chosen simultaneously during the legal Via-1 assignment. [49] deploys the Breadth First Search (BFS) and double linked list to iteratively report odd cycles. In this case, our target is different because we need to find all of the odd cycles simultaneously in a given conflict graph. Hence, the Depth First Search (DFS) technique is used. We keep track of the DFS stack while coloring the conflict graph. Once a coloring conflict is reported for double patterning, we backtrack the DFS stack and report the cycle associated with the current coloring conflict, which is repeated until all nodes are visited. The optimal Via-1 assignment is achieved in line 20 with a depth-first-search (DFS) technique. The optimal Via-1 assignment is an empty set if no legal Via-1 assignment can be found, as explained in lines 21-25. Assume n hit points for the input hit point combination and the number of valid Via-1 candidates for the  $i^{th}$  hit point is  $k_i, 0 \le i \le n-1$ , the total number of Via-1 combinations enumerated will be  $\prod_{i=0}^{i=n-1} k_i$ . Due to the linear time complexity of DFS, the theoretical runtime bound for Algorithm 1 will be  $O(k^n), k = \max_i k_i$ . The time complexity of Algorithm 1 grows exponentially with the number of I/O pins, but most SC libraries have the cell I/O pin counts bounded to the order of 10. This means that for a typical SC library, Algorithm 1 can execute in a reasonable runtime.

# Algorithm 1 Via-1 Assignment Algorithm

```

Input: a set of Via-1's for cell connections (S_c), a hit point combination (HPC) and Via-1

grid size (q_0);

1: Define CFGraph as the conflict graph for Via-1 layer;

2: Define S_{via} as the 2-D set of Via-1's;

3: for each element hp in HPC \cup S_c do;

Define S_{pos} as the set of Via-1's for hp;

4:

if hp is a long hit point then;

5:

6:

Segment hp in the grid size g_0;

7:

Push the center of each segment to S_{pos};

8:

else

9:

Push the center of hp to S_{pos};

10:

end if

for each via location pos in S_{pos} do;

11:

Add pos to CFGraph and assign cost;

12:

Detect and add conflict edges;

13:

14:

end for

15:

Push S_{pos} to S_{via}

16: end for

17: Define oddCycles as the 2-D set of nodes in CFGraph;

18: Report all odd cycles in CFGraph to oddCycles;

19: Define S_n^o as the optimal Via-1 assignment;

20: S_v^o = DFS(S_{via}, oddCycles);

21: if S_v^o = \emptyset then;

22:

HPC is invalid;

23: else

24:

S_n^o is the optimal legal Via-1 assignment;

25: end if

```

Table 2.3: Notations for metal pattern optimization

| $c_L, c_R$           | left or right boundary of cell                                   |  |

|----------------------|------------------------------------------------------------------|--|

| $c_W$                | cell width, $c_W = c_R - c_L$                                    |  |

| $S_m$                | set of M2 wires                                                  |  |

| n                    | total number of M2 wires                                         |  |

| $S_k$                | set of pairs of wires for rule $k, \forall k \in \{1, 2, 3, 4\}$ |  |

| $x_{iL}, x_{iR}$     | the left or right line end of $i^{th}$ wire                      |  |

| $x_{iL}^0, x_{iR}^0$ | the initial line ends of $i^{th}$ wire                           |  |

The LELE-aware Via-1 assignment yields a legal Via-1 location for each hit point within the hit point combination. Furthermore, the solution of Algorithm 1 decides the boundary condition for the SADP-aware pin access design of the M2 layer.

### 2.4.2 Metal Pattern Optimization

Given optimal Via-1 assignment and the accessing direction for the corresponding hit point, we can determine the line-end position of the M2 wire for pin access accounting for the minimum enclosure design rule for M2 over Via-1. For pin access design, we focus on SADP-aware layout optimization within an SC boundary. Hence, if one hit point is next to the right boundary of a cell and the access direction is from the right, the right line end of the corresponding M2 wire will be extended to the right boundary. We have similar pre-design if the hit point is accessed from the left boundary of a cell. Fig. 3.1(c) is an example of M2 wires for pin access after the pre-design stage. This is the most common hit point access scenario from the SC perspective. Our primary goal is to achieve the first-order pin accessibility figure-of-merit. Hence, we

exclude special scenarios like Metal-3 wire going down directly through two vias (Metal-3 to M2 and M2 to M1), and also pin access through complex maze routing, instead of straight routing. The pre-design method induces the following observation.

Observation 2. For M2 wires after the pre-design stage, right line ends can only be extended to the right and left line ends can only be extended to the left.

As illustrated in Fig. 3.1(c), if we simply use the Via-1 locations to determine the line end of M2 wires, the SADP constraints may invalidate some hit point combinations. The line-end extension techniques enable us to legalize the M2 layout and ensure SADP-friendly design. The conventional layout migration issue has been formulated as a linear programming problem in [42]. A similar approach has also been deployed to deal with LELE double patterning layout decomposition in [32]. In addition, the line-end extension techniques have also been deployed in [124, 125] to improve the manufacturability of the cut mask process instead of the trim mask process in this work. [125] has proposed a greedy optimal algorithm to minimize the effective gaps in the cut mask process. The constrained shortest path algorithm is presented to optimize the cut mask cost. Instead of mask cost reduction, this study is design rule oriented and guarantees to find an optimal solution with the minimum amount of line-end extensions if a feasible solution exists for the given Via-1 assignment from Section 2.4.1. The greedy algorithm in [125] aims at the gap distribution optimization in cut masks, which is different from the trim mask optimization in this work. The techniques used in [32, 42, 124] cannot be directly applied to SADP-aware I/O pin access design because the relative order of the metal line ends may change during the line-end extension stage, as shown in Fig. 2(a). Instead, we propose an MILP-based optimization methodology to determine the M2 wire design for each specific hit point combination. Table 2.3 shows the related notations. We will first give the mathematical formulation for the SADP-aware pin access problem. Then, we transfer the mathematical formulation to an MILP formulation. The results of the MILP can determine whether feasible solutions exist for the M2 line ends of a particular hit point combination. If feasible solutions exist, the line-end positions of each M2 wire are decided while minimizing the total amount of line-end extensions.

Mathematical Formulation Observation 2 allows us to quantify the total amount of extension in terms of line-end positions. It is known that line-end extension techniques benefit SADP-based wires [71]. However, in next generation technology nodes, the routing resources are becoming increasingly limited, so line-end extensions of M2 wires should be used judiciously. Additionally, line-end extensions can potentially increase both coupling capacitance and ground capacitance on M2 routes. Therefore, line-end extension minimization is a necessity for pin access optimization. The minimization of the total amount of line-end extensions is formulated as the objective function, as shown in (1).

Constraints (1a) - (1c) define the line-end extension limits and minimum wire length design rule ( $Rule\ 0$  in Table 2.1) for each M2 wire. The initial relative order can be determined for each pair of M2 wires. Suppose the  $i^{th}$  wire is on the left of the  $j^{th}$  wire, as demonstrated in Fig. 2.5(a). Constraint (1d) is formulated to define  $Rule\ 1$ . In set  $S_2$ , the line ends originally overlap each other and constraints (1e) and (1f) represent  $Rule\ 2$ . In set  $S_3$ , the line ends initially have no overlap. After extension, the line ends may or may not overlap each other. Constraint (1g) satisfies  $Rule\ 2$  or  $Rule\ 3$ . Then, constraints (1h) and (1i) are formulated to specify  $Rule\ 4$  for each pair of M2 wires in set  $S_4$ .

$$\min \sum_{i=0}^{n-1} (x_{iL}^{0} - x_{iL}) + (x_{iR} - x_{iR}^{0}) \tag{1}$$

s.t.  $c_{L} \leq x_{iL} \leq x_{iL}^{0}$   $\forall i \in S_{m}$   $(1a)$

$$x_{iR}^{0} \leq x_{iR} \leq c_{R} \qquad \forall i \in S_{m} \qquad (1b)$$

$$x_{iR} - x_{iL} \geq l_{0} \qquad \forall i \in S_{m} \qquad (1c)$$

$$x_{jL} - x_{iR} \geq l_{1} \qquad \forall (i, j) \in S_{1} \qquad (1d)$$

$$x_{iR} - x_{jL} \geq l_{2} \qquad \forall (i, j) \in S_{2} \qquad (1e)$$

$$x_{jR} - x_{iL} \geq l_{2} \qquad \forall (i, j) \in S_{2} \qquad (1f)$$

$$x_{jL} - x_{iR} \geq l_{3} \text{ or } x_{iR} - x_{jL} \geq l_{2} \qquad \forall (i, j) \in S_{3} \qquad (1g)$$

$$|x_{iL} - x_{jL}| \geq l_{4} \text{ or } x_{iL} - x_{jL} = 0 \qquad \forall (i, j) \in S_{4} \qquad (1h)$$

$$|x_{iR} - x_{jR}| \geq l_{4} \text{ or } x_{iR} - x_{jR} = 0 \qquad \forall (i, j) \in S_{4} \qquad (1i)$$

**MILP formulation** Next, we explain how to convert (1) into an MILP formulation. We can simplify the objective function by omitting item  $x_{iL}^0$

and  $x_{iR}^0$ , which are constants for a specific hit point combination. We also need to convert constraints (1g)-(1i) to linear constraints based on the big-M transformation [5]. Note that  $|x_{iL} - x_{jR}| \leq c_W, \forall i, j \in S_m$  and  $c_W$  is the width of the cell. Hence, at the SC level, the cell width  $c_W$  is an appropriate big-M parameter for the formulation. Constraint (1g) can be formulated as linear constraints (2a) - (2c) given below.  $s_k$  is an additional integer variable introduced so that both constraints can be satisfied at the same time.

$$x_{iL} - x_{iR} + (c_W + l_3) \cdot s_k \ge l_3$$

(2a)

$$x_{iR} - x_{jL} + (c_W + l_2) \cdot (1 - s_k) \ge l_2 \tag{2b}$$

$$s_k \in \{0, 1\} \qquad \qquad \forall (i, j) \in S_3 \qquad (2c)$$

Similarly, constraints (1h) and (1i) can also be converted to linear constraints by introducing integer variables as follows.

$$x_{jL} - x_{iL} + (c_W + l_4) \cdot s_{m1} \ge l_4 \cdot (1 - t_{n1})$$

(2d)

$$x_{iL} - x_{jL} + (c_W + l_4) \cdot (1 - s_{m1}) \tag{2e}$$

$$\geq l_4 \cdot (1 - t_{n1}) + (c_W + l_4) \cdot t_{n1} \tag{2f}$$

$$s_{m1} + t_{n1} \le 1, s_{m1}, t_{n1} \in \{0, 1\}$$

$\forall (i, j) \in S_4$  (2g)

$$x_{jR} - x_{iR} + (c_W + l_4) \cdot s_{m2} \ge l_4 \cdot (1 - t_{n2})$$

(2h)

$$x_{iR} - x_{jR} + (c_W + l_4) \cdot (1 - s_{m2}) \tag{2i}$$

$$\geq l_4 \cdot (1 - t_{n2}) + (c_W + l_4) \cdot t_{n2} \tag{2j}$$

$$s_{m2} + t_{n2} \le 1, s_{m2}, t_{n2} \in \{0, 1\}$$

$\forall (i, j) \in S_4$  (2k)

For the MILP formulation, the optimization results will decide whether it is possible to achieve a legal solution for the M2 design given the Via-1 assignment of one hit point combination. In particular, the optimal solution of the MILP formulation generates the legal line-end position of each M2 wire with the minimum amount of extensions.

Linear Programming Relaxation In the MILP formulation, integer variables are introduced to allow changing the relative order of metal line ends. This approach is guaranteed to determine the feasibility of the given Via-1 assignment with minimized total line-end extension. However, the MILP formulation may lead to long runtime for large cell designs. To explore the necessity of the MILP formulation and the possibility of speed up, we relax the MILP formulation into a Linear Programming (LP) formulation. Specifically, the relative order of line ends is pre-determined based on the initial position of metal lines, which further converts constraints (1g)-(1i) to linear constraints [106]. As we can see in Section 2.6, this formulation can not optimally determine the feasibility of the given Via-1 assignment but can significantly reduce the runtime, compared with the MILP formulation.

# 2.5 Pin Access and Cell Layout Co-Optimization

Previously, we have shown that the LELE-aware Via-1 assignment and MILP-based optimization for M2 wires determine whether a single hit point combination is valid or not. If it is valid, we can achieve optimal LELE

friendly Via-1 assignment and subsequently optimize the M2 wires for pin access and cell connections simultaneously given the Via-1 assignment. However, as shown in Fig. 3.1, multiple hit points for one I/O pin lead to numerous hit point combinations for one SC. In general, the more valid hit point combinations we have for one cell, the more flexibility we can provide to the routing stage. Thus, we extend the Pin Access Optimization (PAO) to validate all hit point combinations of an SC.