Copyright

by

Donghyi Koh

2016

# The Dissertation Committee for Donghyi Koh Certifies that this is the approved version of the following dissertation:

# **Advanced III-V MOSFET**

| Committee:          |  |

|---------------------|--|

| Sanjay K. Banerjee  |  |

| Jack C. Lee         |  |

| Leonard F. Register |  |

| Paul S. Ho          |  |

| Todd W. Hudnall     |  |

# **Advanced III-V MOSFET**

by

Donghyi Koh, B.E,: M.S.E

## Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2016

# **Dedication**

All my families and my love, Jeong Min Hyun

## Acknowledgements

For the first, I am profoundly grateful to my supervisor, Dr. Sanjay K. Banerjee for being such an excellent advising, mentoring, and guiding during my Ph.D. journey. He has always been responsible, supportive, and attentive. I would like to appreciate him for the encouragement which leads me to complete Ph.D. degree without any worries. His mentorship helps me to have autonomous research with consolidating knowledge and responsibility.

I also thank my father, mother, sister, and my lovely wife, Jeong Min Hyun. My father (Sung-Joo Koh) and my mother (Songhee Lee) love me without condition, and they are fully supporting me. With their love and supporting, my Ph.D. journey could be started and arrived at the goal. Despite my mother can't stay at the moment of my Ph.D. completion, I can feel that she is happy to see my achievement in the heaven. All of her memories help me overcome whenever I have fallen into a slump. I have learned what scarification is from my parents Also, for my sister (Bokyoung Koh), she has always been cheering me up and taking care of all family issues instead of me. Her efforts seem to be a strong breakwater, so any worries can't reach me at all. Lastly, my lovely wife, Jeong Min Hyun, is now the most meaningful person in my life. Her existence gives me huge motivation for all of everything.

I should gratitude all my pickle friends, Seonpil Jang, Jaehyun Ahn, Kyounghwan Kim, Youngkyu Lee, Sangwoo Kang, Seungheon Shin, Hema Movva Chandra Prakash, Tanuj Trivedi, and all Korean brothers. Also, I appreciate that MER staffs always make a lot of effort for all of the students.

**Advanced III-V MOSFET**

Donghyi Koh, Ph.D.

The University of Texas at Austin, 2016

Supervisor: Sanjay K. Banerjee

As scaling of silicon-based CMOS devices approaches its end, there is an ever

increasing interest in high mobility materials. Among potential candidates for future

CMOS devices, III-V materials are the most promising option due to their superior carrier

transport properties. Despite their attractive material properties, they face several critical

challenges that need to be resolved. The main limitation in III-V MOSFETs is lack of a

good native oxide. Recently, devices utilizing a gate stack formed with high-κ and metal

gate electrode are being explored for EOT scaling. Compared to Si MOSFETs, the

surfaces of III-V channel materials are prone to deteriorate, resulting in degradation

threshold voltage control, subthreshold characteristics, and overall device performance.

The purpose of this dissertation is to address improvement of surface

characteristics of III-V materials, especially, InGaAs. First of all, beryllium oxide (BeO)

is considered as interface passivation layer for InGaAs MOSFETs. In order to apply BeO

onto InGaAs, the chemical and mechanical properties are first studied. Liquid BeO

precursor is never used in ALD systems. The chemical properties of ALD BeO film are

revealed from AES, XPS, NRA, RBS, and REELS. Using nano-indentation, the

mechanical characteristics of ALD BeO are investigated.

vi

The second part of the study focuses on the application of ALD BeO to InGaAs MOSFETs. The surface channel MOSFET is employed to understand BeO dielectric with III-V channel. The quantum well (QW) structure is known to withstand InGaAs intrinsic material properties from a device point of view. ALD BeO is applied to QW InGaAs MOSFETs as an interface passivation layer below HfO<sub>2</sub>. The impact of ALD BeO application for interface passivation is presented using the improvement in device characteristics, for example, drive current ( $I_{ON}$ ), low leakage current ( $I_{OFF}$ ), effective mobility ( $\mu_{eff}$ ), and interface trap density ( $D_{it}$ ).

The third and final part are about process research for InGaAs surface quality. III-V channel materials are inherent to create notorious native oxide that needs to be treated before the fabrication process. In order to protect pristine III-V surface, *in-situ* Ar treatment is studied and used before high- $\kappa$  deposition. In addition, deuterium (D<sub>2</sub>) high-pressure annealing is considered to passivate III-V interface with high- $\kappa$ . To demonstrate the efficacy of these treatment processes, InGaAs MOSCAPs are fabricated, and capacitance characteristics are analyzed and compared. The C-V hysteresis and multi-frequency C-V are measured, and the interface trap density (D<sub>it</sub>) is extracted using the C-V result.

# **Table of Contents**

| List of Tablesx                                                         |

|-------------------------------------------------------------------------|

| List of Figuresxi                                                       |

| Chapter 1: Introduction                                                 |

| 1.1 History of MOSFETs Technology1                                      |

| 1.2 Motivation of III-V MOS device study4                               |

| 1.3 Criteria of High-к gate dielectric9                                 |

| 1.4 Outline                                                             |

| Chapter 2: Atomic layer deposition Beryllium oxide on III-V materials15 |

| 2.1 Liquid type Beryllium oxide ALD15                                   |

| 2.2 Beryllium oxide Chemical composition investigation17                |

| 2.3 ALD beryllium oxide Mechanical properties23                         |

| Chapter 3: Surface Channel InGaAs MOSFETs with BeO25                    |

| 3.1 Surface stoichiometry of ALD BeO on InGaAs25                        |

| 3.2 MOS capacitance characteristic comparison                           |

| 3.3 Surface channel InGaAs MOFETs fabrication and characterization31    |

| Chapter 4: Introduction of Quantum Well (QW) III-V MOSFETs35            |

| 4.1 BeO IPL for Quantum well (QW) InGaAs MOSFETs35                      |

| 4.2 Device Process of QW InGaAs MOSFETs36                               |

| 4.3 Fundamental Experiment for device                                   |

| 4.3.1 The Gate recess process                                           |

| 4.3.2 Electrical analysis of BeO QW InGaAs MOS capacitance42            |

| 4.3.3 Device analysis of InGaAs QW MOSFETs with BeO IPL44               |

| Chapter 5: Process development for interface improvement                |

| 5.1 In-situ Ar Plasma Treatment for InGaAs surface50                    |

| 5.2 Argon Ion Plasma Treatment Process                                  |

| 5.2 Result of Ar ion plasma treatment with MOSCAPs52                    |

| Chapter 6: Summary and Future work                              | 58 |

|-----------------------------------------------------------------|----|

| 6.1 Summary                                                     | 58 |

| 6.2 Suggestion for future work                                  | 60 |

| 6.2.1 Concept of D <sub>2</sub> High-Pressure Annealing (HPA)   | 60 |

| 6.2.2 D <sub>2</sub> High-Pressure Annealing for InGaAs surface | 61 |

| 6.2.3 The impact of D <sub>2</sub> HPA on InGaAs surface        | 62 |

| 6.3.1 Concept of Solid phase doping on InGaAs                   | 69 |

| Bibliography                                                    | 74 |

| Vita                                                            | 87 |

# **List of Tables**

| Table 1-1: Intrinsic material property comparison of several semiconductors4      |

|-----------------------------------------------------------------------------------|

| Table 1-2: Material properties comparison of several gate oxides                  |

| Table 1-3: Thermodynamic stability of binary oxides incorporating with silicon 10 |

| Table 2-1: Summary of properties for crystalline and ceramic/poly-crystalline BeO |

| 16                                                                                |

# **List of Figures**

| Figure 1-1: | Historical trend of Si CMOS technology development in transistor gate            |

|-------------|----------------------------------------------------------------------------------|

|             | length [2]1                                                                      |

| Figure 1-2: | Technology innovation toward 22nm node: Strained silicon, high-                  |

|             | $\kappa$ /metal gate stack, and non-planar structure [6]2                        |

| Figure 1-3: | The advantage of transfer characteristic in III-V MOSFETs5                       |

| Figure 1-4: | The trend of intrinsic transistor delay for benchmark technologies. Gate         |

|             | delay commensurate with until 45 nm technology node, but it shows                |

|             | discrepancy from 45 nm node [14]7                                                |

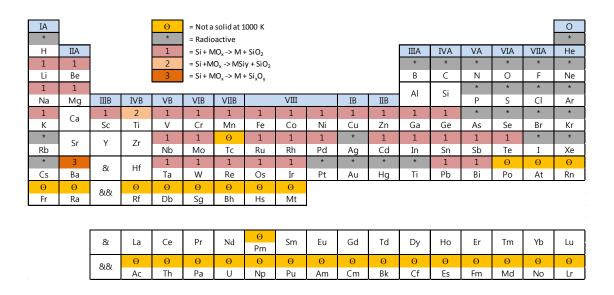

| Figure 2-1: | AES spectra of ALD BeO before and after Ar+ sputtering17                         |

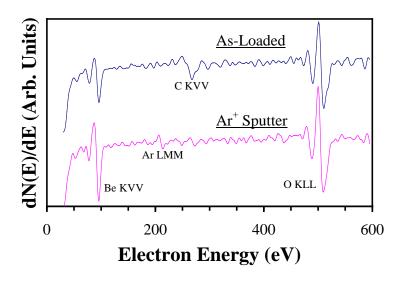

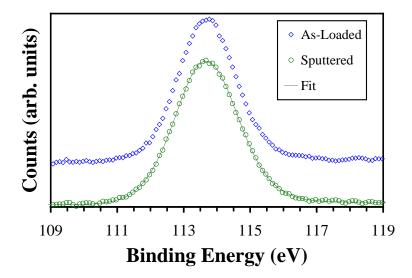

| Figure 2-2: | XPS spectra of ALD BeO Be 1s core level before and after Ar+                     |

|             | sputtering18                                                                     |

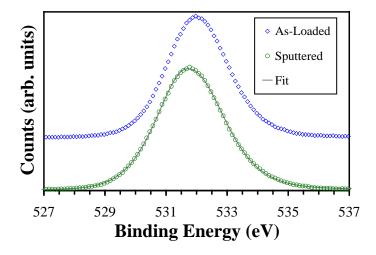

| Figure 2-3: | XPS spectra of ALD BeO O 1s core level before and after Ar+ sputtering           |

|             |                                                                                  |

| Figure 2-4: | Nuclear Reaction Analysis (NRA) spectrum of ALD BeO20                            |

| Figure 2-5: | Rutherford Backscattering Spectrometry (RBS) spectrum of ALD BeO.                |

|             | 21                                                                               |

| Figure 2-6: | REELS spectrum of as-loaded ALD BeO collected using a 2.5 keV                    |

|             | electron beam                                                                    |

| Figure 2-7: | REELS spectrum of ALD BeO collected after Ar <sup>+</sup> sputtering using a 2.5 |

|             | keV electron beams                                                               |

| Figure 3-1: | High resolution cross-sectional TEM analysis of ALD BeO grown on                 |

|             | InGaAs                                                                           |

| Figure 3-2: AFM and surface roughness analysis of ALD BeO and Al2O3 grown on                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|

| InGaAs26                                                                                                                              |

| Figure 3-3: XPS spectrum comparison of ALD Al <sub>2</sub> O <sub>3</sub> and BeO film deposited                                      |

| InGaAs substrate. (a) XPS spectra of initial InGaAs surface, (b) Al <sub>2</sub> O <sub>3</sub>                                       |

| deposited InGaAs surface before and after PDA, and (c) BeO deposited                                                                  |

| InGaAs surface before and after PDA27                                                                                                 |

| Figure 3-4: The MOS C-V characteristic comparison between Al <sub>2</sub> O <sub>3</sub> and BeO                                      |

| MOSCAPs. (a) C-V hysteresis (b) frequency dispersion (c) gate leakage                                                                 |

| current density, (d) interface trap density30                                                                                         |

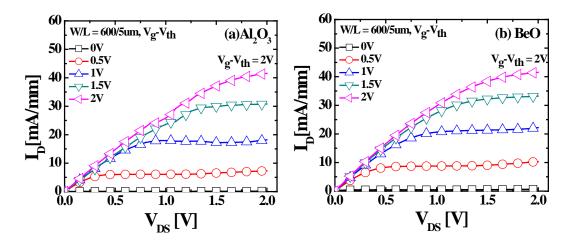

| Figure 3-5: I-V characteristics of n-InGaAs MOSFETs with (a) Al <sub>2</sub> O <sub>3</sub> and (b) BeO                               |

| gate dielectric                                                                                                                       |

| Figure 3-6: Output characteristic of InGaAs MOSFETs with (a) Al <sub>2</sub> O <sub>3</sub> and (b) BeO                               |

| gate dielectric                                                                                                                       |

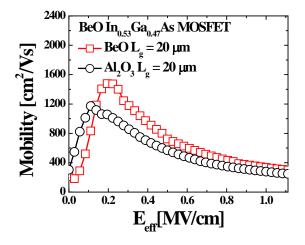

| Figure 3-7: Effective mobility comparison between BeO and Al <sub>2</sub> O <sub>3</sub> MOSFETs .33                                  |

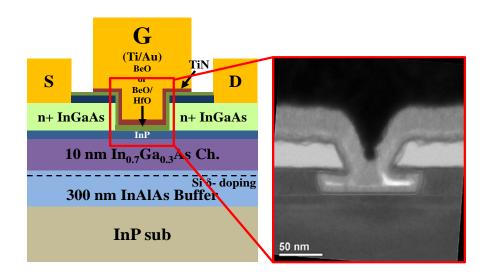

| Figure 4-1: Schematic and TEM images of QW MOSFET device structure with BeO                                                           |

| or BeO/HfO2 as gate dielectric or interfacial layer, respectively.                                                                    |

| Especially, the TEM image indicates 1/1.5 nm BeO/HfO2 deposited gate                                                                  |

| stack36                                                                                                                               |

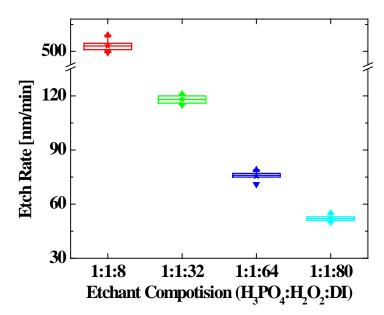

| Figure 4-2: The etch rate of InGaAs in based H <sub>3</sub> PO <sub>4</sub> : H <sub>2</sub> O <sub>2</sub> etchant, which is carried |

| out in room temperature for 1 min38                                                                                                   |

| Figure 4-3: The etch rate of InGaAs in based H <sub>3</sub> PO <sub>4</sub> : H <sub>2</sub> O <sub>2</sub> etchant, which is carried |

| out in room temperature for 1 min39                                                                                                   |

| Figure 4-4: The AFM profile after SiO <sub>2</sub> hard mask dry etching, where SiO <sub>2</sub> is grown                             |

| 25 nm using PECVD40                                                                                                                   |

| Figure 4-5: The AFM profile of etched surface where includes SiO <sub>2</sub> as hard mask                 |

|------------------------------------------------------------------------------------------------------------|

| above the n <sup>+</sup> InGaAs capping layer40                                                            |

| Figure 4-6: The recess current after InGaAs etching in S/D region                                          |

| Figure 4-6: Comparison of C-V characteristics and gate leakage current (inset). 10 nm                      |

| $\text{Al}_2\text{O}_3$ and BeO is grown using the same ALD system at 250 $^\circ\!\text{C}$ . The         |

| MOSCAP structure consists of n+ InP, 20 nm of In <sub>0.53</sub> Ga <sub>0.47</sub> As, and 2              |

| nm of undoped InP layer42                                                                                  |

| Figure 4-7: The comparison of frequency dispersion characteristic between HfO <sub>2</sub> and             |

| BeO MOSCAP43                                                                                               |

| Figure 4-8: Frequency dispersion for InGaAs MOSCAP with 1nm BeO/ 1.5nm HfO <sub>2</sub>                    |

| thickness gate dielectric                                                                                  |

| Figure 4-9: Subthreshold characteristic with different channel length and                                  |

| transconductance (gm) of $L_g = 100 \text{ nm}$ of QW MOSFETs with                                         |

| BeO/HfO <sub>2</sub> (1/1.5 nm) gate stack                                                                 |

| Figure 4-10: The gate leakage current density of $L_{\rm g}$ = 100 nm QW MOSFETs with                      |

| $BeO/HfO_2$ (1/1.5 nm) device at applied drain voltage 0.05 V and 0.5 V.                                   |

| 46                                                                                                         |

| Figure 4-11: The output characteristic of $L_g = 100$ nm QW MOSFET with BeO/HfO <sub>2</sub>               |

| (1/1.5 nm) gate dielectric                                                                                 |

| Figure 4-12: The mobility enhancement of $L_g = 10 \mu m$ BeO/HfO <sub>2</sub> QW MOSFETs47                |

| Figure 5-1: The conceptual diagram of Ar ion plasma treatment on In <sub>0.53</sub> Ga <sub>0.47</sub> As. |

| Note that $In_{0.53}Ga_{0.47}As$ on Silicon MOS capacitor with $Al_2O_3/HfO_2$ bi-                         |

| layer high-κ dielectric layer is fabricated in-situ50                                                      |

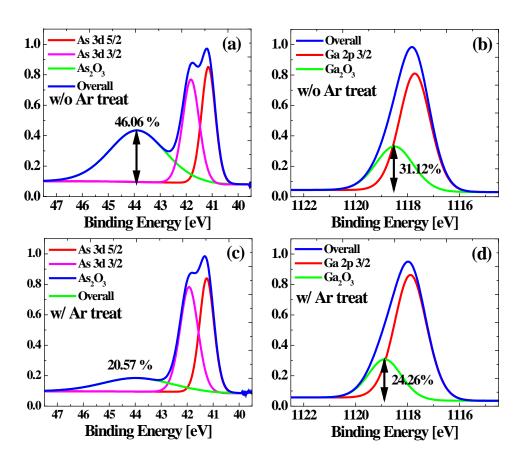

| Figure 5-2: The XPS spectra with and without Ar ion plasma treatment. (a) and (b)                        |

|----------------------------------------------------------------------------------------------------------|

| present non-treatment As and Ga spectra, respectively. (c) and (d)                                       |

| indicate Ar ion-treated As and Ga spectra52                                                              |

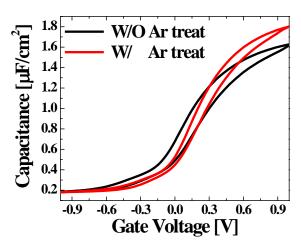

| Figure 5-3: The comparison of the C-V hysteresis with and without surface treatmen                       |

| measured in 1 MHz53                                                                                      |

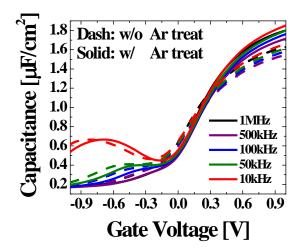

| Figure 5-4: The comparison of frequency dispersion characteristic between with and                       |

| without surface treatment. (Dash line: without Ar treatment, Solid line:                                 |

| with Ar treatment)53                                                                                     |

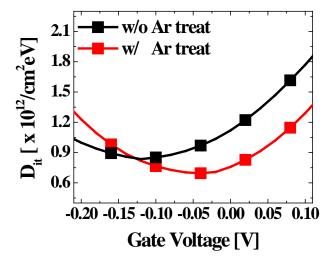

| Figure 5-5: The comparison of the interface trap density between with and without A                      |

| treatment. The interface trap density is extracted by conductance                                        |

| method54                                                                                                 |

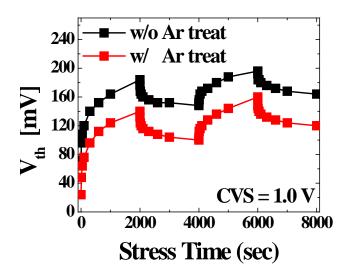

| Figure 5-6: The comparison of constant voltage stress induced threshold voltage shift                    |

| between with and without Ar treatment55                                                                  |

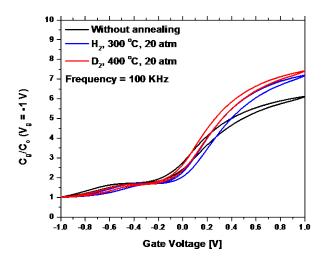

| Figure 6-1: The Cg/Co (gate voltage = -1 V) of the bidirectional capacitance-voltage                     |

| (C-V) characteristics of the In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAPs on Si without HP.          |

| (black), H <sub>2</sub> HPA MOSCAP with 300 °C and 20 atm for 30 min (blue)                              |

| and $D_2$ HPA MOSCAP with 400 °C and 20 atm for 30 min (red)62                                           |

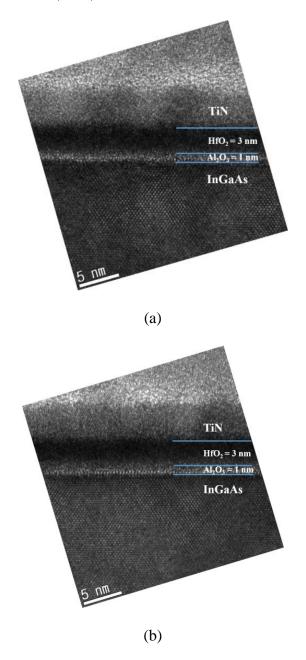

| Figure 6-2: Cross sectional TEM images for the In <sub>0.53</sub> Ga <sub>0.47</sub> As gate stacks: (a) |

| MOSCAP without HPA and (b) D <sub>2</sub> HPA MOSCAP with 400 °C and 20                                  |

| atm for 30 min63                                                                                         |

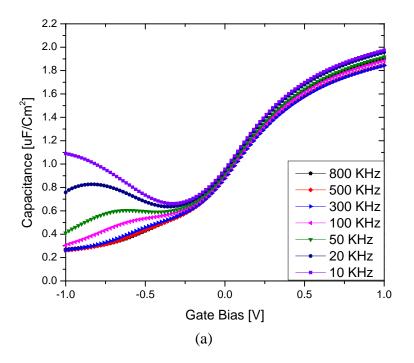

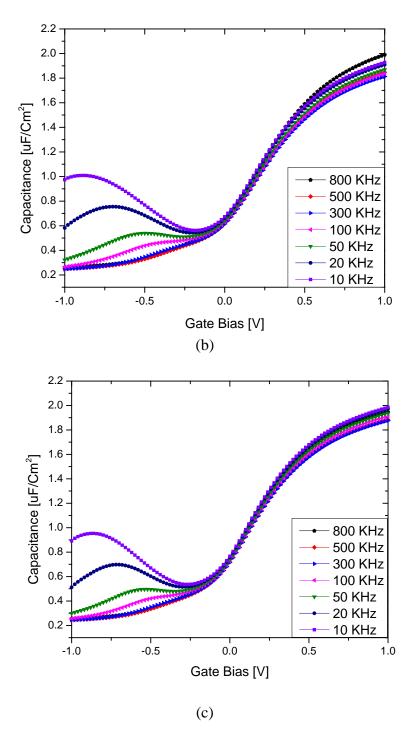

| Figure 6-3: Multi-frequency capacitance-voltage (C-V) characteristics for the                            |

| $In_{0.53}Ga_{0.47}As\ MOSCAPs$ on Si: (a) MOSCAP without HPA, (b) $H_2$                                 |

| HPA MOSCAP with 300 °C and 20 atm for 30 min, and (c) D <sub>2</sub> HPA                                 |

| MOSCAP with 400 °C and 20 atm for 30 min65                                                               |

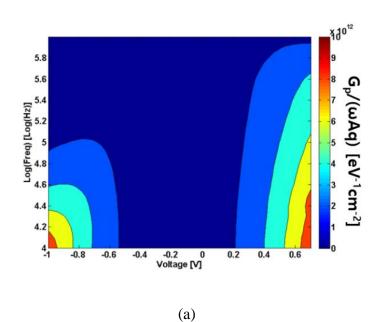

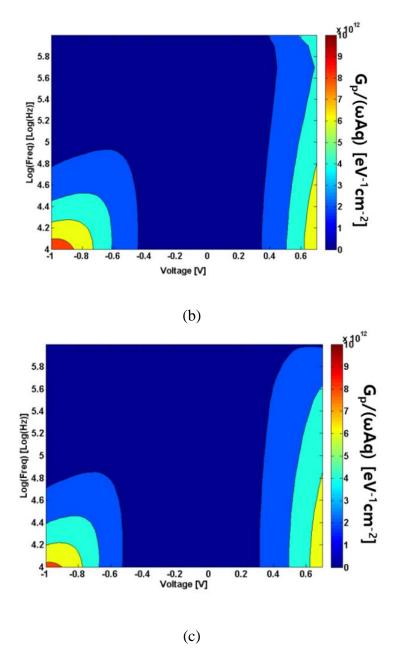

| Figure 6-4: The normalized conductance value, $G_p/(\omega Aq)$ , as a function of gate               |

|-------------------------------------------------------------------------------------------------------|

| voltage. (a) $In0.53Ga_{0.47}As\ MOSCAP$ without HPA, (b) $H_2\ HPA$                                  |

| $In0{53}Ga_{0.47}As\ MOSCAP$ with 300 °C and 20 atm for 30 min, and (c) $D_2$                         |

| HPA In $0.53$ Ga $0.47$ As MOSCAP with 400 °C and 20 atm for 30 min.67                                |

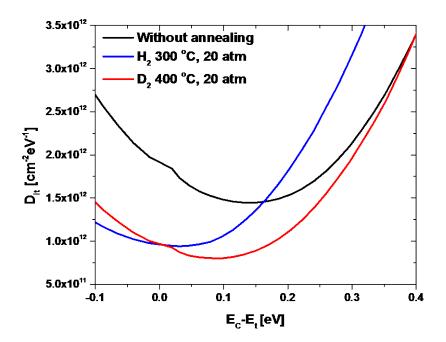

| Figure 6-5: Interface trap density ( $D_{it}$ ) for three types of $In_{0.53}Ga_{0.47}As\ MOSCAPs$ on |

| Si as a function of energy by using the conductance method: MOSCAP                                    |

| without HPA (black), $H_2$ HPA MOSCAP with 300 °C and 20 atm for 30                                   |

| min (blue), and $D_2$ HPA MOSCAP with 400 °C and 20 atm for 30 min                                    |

| (red)68                                                                                               |

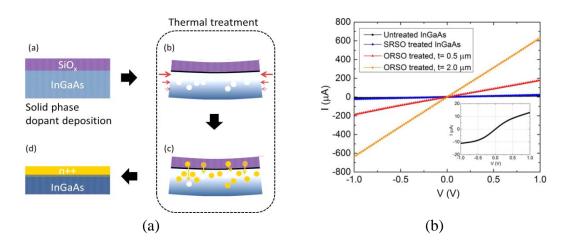

| Figure 6-6: The schematic diagram of solid phase doping process on substrate shown                    |

| in (a) and I-V characteristics for InGaAs layer after solid phase doping                              |

| process. The inset shows the result from the untreated InGaAs as a                                    |

| reference with a magnified scale (b)70                                                                |

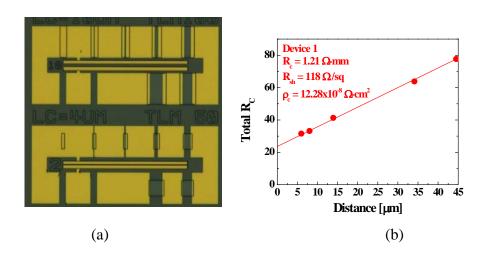

| Figure 6-7: The transfer length measurement for ORSO doped InGaAs. (a) optical                        |

| image of TLM structure, (b) total resistance as a function of pad distance                            |

| 71                                                                                                    |

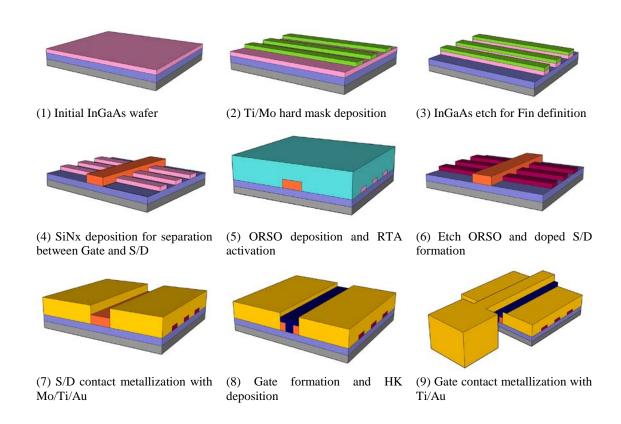

| Figure 6-2: The device process flows for solid phase doped InGaAs FinFETs73                           |

## **Chapter 1: Introduction**

#### 1.1 HISTORY OF MOSFETS TECHNOLOGY

Metal-oxide-semiconductor field effect transistors (MOSFETs) have played a pivotal role as the main component of integrated circuits (ICs). For over 40 years, the semiconductor industry has maintained Moore's law where the number of transistors on a chip doubles every two years [1, 2].

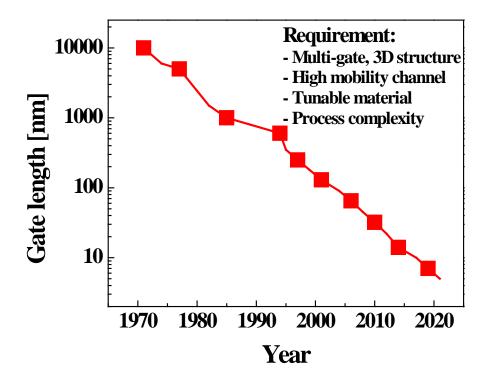

Figure 1-1: Historical trend of Si CMOS technology development in transistor gate length [2].

The key aspect of success in silicon MOSFETs is SiO<sub>2</sub> gate oxide. It is no controversy that SiO<sub>2</sub> is excellent material in silicon CMOS industry, because SiO<sub>2</sub> is well controllable material in thickness and uniformity. First, low defect density is achieved when SiO<sub>2</sub> is used as gate insulator since it forms very stable interface with silicon surface. The P<sub>b0</sub> center (trivalent Si dangling bond) considering one of the crucial defects is easily passivated after annealing in hydrogen ambient [3-5]. In addition, the band gap of SiO<sub>2</sub> is large (around 9 eV), which can be considered that it is superior in electrical isolation in gate stack.

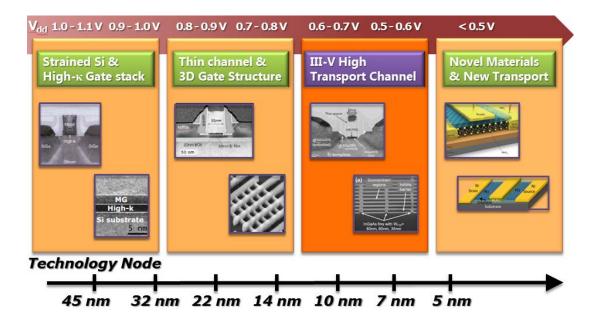

Figure 1-2: Technology innovation toward 22nm node: Strained silicon, high-κ/metal gate stack, and non-planar structure [6].

Owing to prominent properties of SiO2, this tremendous growth in the semiconductor industry can be realized. It is closely related with the continuous enhancement of integrated circuit performance. The increase packing density by reducing dimension of chip size is key component of success. There are a few of the enabling technologies behind this success in Si CMOS technology, as shown in Figure 1.2 [6]. Nano-lithography, high-κ/metal gate, and 3D device structures lead remarkable growth in semiconductor industry. Although the highly developed lithography processes allow nano-sized device features, scaling of the oxide thickness in MOSFETs faces an inherent challenge [7, 8], due to high gate leakage currents through SiO<sub>2</sub> and poly-Si gate stacks. Thus, SiO<sub>2</sub> and poly-Si gate stacks are replaced with high-κ dielectric materials and metal gates in order to reduce gate leakage while maintaining the same effective oxide thickness [7]. Further scaling of feature sizes can also be achieved by utilizing non-planar device structures as shown in Figure 1.2. A multi-gated structure, for example, brings immense benefits to the chip maker, such as fast throughput, and reduction of power consumption [6].

|                                             | Si                  | Ge                  | GaAs                  | InP                   | In <sub>0.53</sub> Ga <sub>0.47</sub> AS | In <sub>0.7</sub> Ga <sub>0.3</sub> As | InAs                  |

|---------------------------------------------|---------------------|---------------------|-----------------------|-----------------------|------------------------------------------|----------------------------------------|-----------------------|

| Lattice Constant (Å)                        | 5.431               | 5.658               | 5.653                 | 5.869                 | 5.869                                    | 5.937                                  | 6.058                 |

| Electron Effectiv Mass (m*/m <sub>0</sub> ) | 0.19                | 0.082               | 0.067                 | 0.077                 | 0.041                                    | 0.034                                  | 0.023                 |

| Electron Affinity (eV)                      | 4.05                | 4                   | 4.07                  | 4.38                  | 4.5                                      | 4.65                                   | 4.9                   |

| Band-gap (eV)                               | 1.12                | 0.66                | 1.42                  | 1.35                  | 0.74                                     | 0.58                                   | 0.35                  |

| Electron mobility (cm²/V·s)                 | 1500                | 3900                | 8500                  | 4600                  | 12000                                    | 20000                                  | 33000                 |

| Hole mobility (cm²/V·s)                     | 450                 | 1900                | 400                   | 150                   | 300                                      | 400                                    | 460                   |

| Saturation velocity at low field (cm/s)     | 1 X 10 <sup>7</sup> | 6 X 10 <sup>6</sup> | 2.1 X 10 <sup>7</sup> | 2.5 X 10 <sup>7</sup> | 3.1 X 10 <sup>7</sup>                    | 6.1 X 10 <sup>7</sup>                  | 7.7 X 10 <sup>7</sup> |

Table 1-1: Intrinsic material property comparison of several semiconductors

It is hard to continuously maintain Moore's law beyond the 7 nm technology node using just the current silicon technology. Revolutionary advances in materials are inevitable to keep increasing chip density and improving performance. In agreement with necessity of further scaling, high mobility channel materials have also been in the limelight for post-Si CMOS devices. III-V materials, such as InGaAs, InAs, or InP have inherent extraordinary transport properties, as highlighted in Table 1.1 [9, 10].

#### 1.2 MOTIVATION OF III-V MOS DEVICE STUDY

The interest in III-V CMOS comes from the outstanding electron transport properties in these materials, which leads to higher electron velocity, and mobility [11]. This results in devices with both a high ON-state current and transconductance [12]. It can be clearly seen in table 1-1 that III-V materials have higher electron mobility and

smaller effective mass compared to Si. It can be easily compared in equation (1.1), (1.2) and table 1-1.

$$I_D = C_{OX} \cdot \mu \cdot \frac{W}{2L} (Vg - V_{th})^2 \tag{1.1}$$

$$\mu = \frac{q \cdot \tau_c}{m^*} \tag{1.2}$$

According to equation (1.1) and (1.2), it can be explained the relation between drive current and effective mass. Considering this relationship, III-V materials produce high drive current in device.

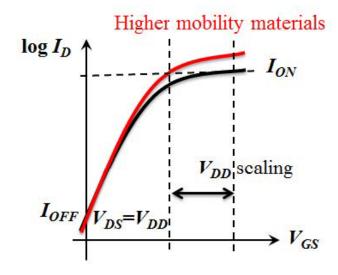

Especially, InGaAs with higher In content shows high electron mobility. This in turn translates into reduced power consumption and gate delay because high electron mobility can lead to a higher drive current at a low supply power, which is described in Figure 1.3.

Figure 1-3: The advantage of transfer characteristic in III-V MOSFETs

As device gate lengths are further shrunk down below 100 nm in Si SCMOS, two main issues, power consumption and gate delay, are on the rise. Power consumption consists of active power ( $P_{active}$ ) and standby power ( $P_{standby}$ ), which can be written as equation (1.3) and (1.4). Low OFF-state current ( $I_{OFF}$ ) and low supply voltage ( $V_{DD}$ ) are required to increase performance while the gate length of MOSFETs is decreased following Moore's Law.

$$P_{active} = a \cdot f \cdot C_{load} \cdot V_{DD}^{2} \tag{1.3}$$

$$P_{standby} = I_{off} \cdot V_{DD}^{2} \tag{1.4}$$

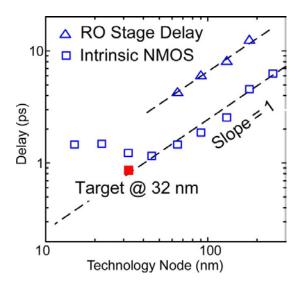

The decrease of intrinsic gate delay time follows with equation (1.5) [13], which explains that the intrinsic gate delay is proportional to gate length. However, the intrinsic gate delay time doesn't decrease proportionally following the decrease in gate length below the 45 nm technology node, as shown in Figure 1.4.

$$\tau = \frac{(1 - \delta)V_{DD} - V_T + (C * f \cdot V_{DD} / C_{inv} \cdot L_G)}{(3 - \delta)V_{DD} / 4 - V_T} \frac{L_G}{v}$$

(1.5)

A continuous increase in carrier velocity is hard to achieve because of short channel effects, which are strongly detrimental for device performance in short channel devices [13, 14]. In other words, carrier velocity is expected to increase as gate length decreases, so the term  $L_G/v$  in equation (1.3) is expected to decrease, but in reality, the carrier velocity does not further increase due to short channel effects.

In fact, as the gate length is reduced below 45 nm node, reduction of  $L_G$  is not the dominant factor because of increase in  $L_G/\nu$ . Therefore, in order to achieve next

generation, higher performance CMOS devices, higher mobility materials should be studied and developed.

Figure 1-4: The trend of intrinsic transistor delay for benchmark technologies. Gate delay commensurate with until 45 nm technology node, but it shows discrepancy from 45 nm node [14].

In addition, high-κ dielectric material is inevitable not only to maintain Moore's Law, but also to improve device performance. Although III-V materials are attractive materials for future CMOS technology, there is a critical issue of interface layers in III-V channel materials. Either native oxide, or SiO<sub>2</sub> on III-V channel substrate results in Fermi level pinning which results in a poor gate modulation [15, 16]. Thus, forming a better interface layer is an important issue in III-V CMOS technology.

As for the gate dielectrics, high-κ materials require 1) a large band gap with sufficient band offsets for both electrons and holes, 2) thermodynamically stable and low

interface trap density with channel layer, 3) compatibility with current gate electrode, as well as with conventional CMOS processing [17-19].

| Properties                    | SiO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> | ZrO <sub>2</sub> | La <sub>2</sub> O <sub>3</sub> | BeO |

|-------------------------------|------------------|--------------------------------|------------------|------------------|--------------------------------|-----|

| Dielectric Constant (κ)       | 3.9              | 8~9                            | 18~25            | 18~30            | 20~36                          | 6~7 |

| Bandgap                       | 9                | 8.8                            | 6.0              | 5.8              | 4.3                            | 7.9 |

| Band offset for electron (eV) | 3.5              | 2.8                            | 1.5              | 1.4              | 2.3                            | 2.6 |

| Band offset for holes (eV)    | 4.4              | 4.9                            | 3.4              | 3.3              | 0.9                            | 4.1 |

Table 1-2: Material properties comparison of several gate oxides

The main challenge in III-V MOSFETs with a higk-κ gate oxide is formation of a high quality interface between the oxide and the III-V channel substrate. Generally, III-V materials form an unstable and poor quality interface with oxygen [7]. A large amount of In-O, Ga-O, or As-O bonds are observed on the interface between high-κ and III-V surfaces which leads to Fermi level pinning and thereby, a high interface trap density due to oxygen diffusion [20-22]. Therefore, in order to improve interface quality, an interface passivation layer, or additional chemical treatment is necessary during device processing [23, 24].

Current silicon device architecture is pursuit the non-planar structure, such as FinFETs. For FinFET device process, source and drain formation is processed with ion implantation. However, ion implantation leads to damage on the S/D region, and it can be

leakage current path during device operation. Also, it gives rise to doping uniformity problem, since it has shadow effect when ion implantation is carried out.

## 1.3 CRITERIA OF HIGH-K GATE DIELECTRIC

As shown in table 1-2, it is seen that many dielectrics with high- $\kappa$  values exist. However, to select suitable high- $\kappa$  dielectric is quite complicated. As for the gate dielectrics, high- $\kappa$  materials require several aspects to utilize as gate dielectric.

- 1) Permittivity: It is necessary to have higher permittivity than that of SiO<sub>2</sub>. It is preferred to use one with high dielectric constant, 20~40. Basically, however, it is considered that there is tradeoff between the dielectric constant and bandgap. In the other words, high-κ value dielectric materials are usually inherent low bandgap.

- 2) Bandgap and band offset: Typically, it is required to be over 5 eV in bandgap. The Schottky emission of electron or holes into the oxide bands can be prevented when the band offset with silicon is over 1.0 eV. For SiO<sub>2</sub> and Si substrate, the conduction band and valance band offsets with silicon present 3.0 eV and 4.8 eV. If the conduction band offsets is not over 1.0 eV, undesired leakage current can be achieved and these oxide will be disregard in gate dielectric application [25].

- 3) Thermodynamic stability: It is obvious to acquire the good interface between all gate dielectric with silicon substrate. The interface property is critical factor in general device performance. High stability in gate oxide represents less reaction with silicon substrate, so that less produce interfacial SiO<sub>2</sub>. It is inevitable to regrow interfacial layer

when high- $\kappa$  oxide deposit on silicon substrate since inter-diffusion or chemical reaction occurs. Therefore, the high- $\kappa$  dielectric inherent high Gibbs free energy can keep from reaction with silicon [26, 27]. Due to its low- $\kappa$  property, the interfacial SiO<sub>2</sub> tends to compromise the total capacitance density of the gate capacitor, and, eventually, it screens out an advantage of high- $\kappa$  application.

Table 1-3: Thermodynamic stability of binary oxides incorporating with silicon

4) Film morphology: Basically, rapid thermal annealing at 1000 C is necessary in Si CMOS process [28]. The gate dielectric materials must stand this process without crystallization. This is severe ambient for high-κ dielectric materials not to change its crystallinity since their crystalline temperature is low and it can be affected in RTA [25]. Typically, some high-κ materials can easily crystallize at lower temperature condition,

which results in high leakage path through crystallized grain boundaries, and failure with EOT scaling [29].

5) CMOS process compatibility: The deposition method of the high-κ dielectric should be compatible with current CMOS process. The high-κ oxide is required to be grown with good thickness uniformity, interfacial properties, and thermal stability. The atomic layer deposition (ALD) is known as the most excellent deposition system for thin gate dielectrics [17-19].

The high- $\kappa$  gate application has several limitations due to its chemical bonding, such as, structural defects, mobility degradation, threshold voltage degradation, and reliability issues. Unfortunately, these challenges are more worse in III-V channel devices because III-V materials are not able to form better interfacial oxide layer compared  $SiO_2$  in silicon substrate [7].

Briefly, high-κ valued oxides have intrinsic defects like oxygen vacancies, oxygen interstitials, or oxygen deficiency [30]. Basically, it is the fact that oxygen vacancy is considered as a main reason for oxide traps. Due to the thermal stability in high-κ oxides, the inter-diffusion occurs, resulting to electrical degradation in device electrical characteristics [31]. Another concern is the carrier mobility degradation. Generally, the channel mobility in the high-κ on silicon is dramatically degraded because higher oxide traps and interface trap densities exist. These defects contribute to Coulomb scattering because defects tend to be an acceptor, thus, these can occupy not only within the bandgap, but also at the energy sites aligned with III-V materials' conduction band [32-34]. Furthermore, the soft optical phonons can be problematic in high-κ oxides

because of their ionic bonds. Moreover, threshold voltage degradation should be concerned. Inside high- $\kappa$  materials, large amount of fixed charges present and they are responsible for charge trapping sites which affect  $V_{th}$  control. In addition, fermi pinning effect pinning (FLP) affects also threshold voltage, because oxygen vacancy, especially, produce charges to metal gate electrode [35-38]. For III-V channel device, a large amount of In-O, Ga-O, or As-O bonds are observed on the interface between high- $\kappa$  and III-V surfaces which leads to Fermi level pinning and thereby, a high interface trap density due to oxygen diffusion [20-22]. Therefore, in order to improve interface quality, an interface passivation layer, or additional chemical treatment is necessary during device processing [23, 24].

#### 1.4 OUTLINE

The objective of this work is to study the improvement of III-V interfaces by applying various scientific processes, as well as III-V device engineering. Among III-V materials, In-rich InGaAs channel material is selected due to its high electron mobility and high drive current capability [39]. As an interface passivation layer, Beryllium oxide (BeO) is employed to InGaAs MOSFETs. BeO is known to have a wide bandgap, high thermal stability, and sufficient valence and conduction band offsets [19, 40-42]. For interface passivation process, the impact of *in-situ* Argon (Ar) ion plasma treatment is studied by fabricating InGaAs MOSCAPs.

In chapter 2, the material properties of Atomic Layer Deposition (ALD) BeO are investigated to reveal its chemical, physical, electrical, and mechanical properties [43]. With ALD BeO, Rutherford backscattering (RBS) and nuclear reaction analysis (NRA) measurement is carried out to quantify the hydrogen content in quantitatively. Also, the band gap of ALD BeO is evaluated using reflection electron energy loss spectroscopy (REELS). The mechanical properties of ALD BeO like the Young's modulus and hardness are evaluated by a nanoindentation measurement.

In Chapter 3, to demonstrate the potent of BeO gate stack, surface channel structure has been applied. InGaAs surface channel MOSFETs with Al<sub>2</sub>O<sub>3</sub> or BeO gate dielectric is studied [19]. By comparing BeO with Al<sub>2</sub>O<sub>3</sub> gate stack with XPS, TEM, and MOS capacitance, the interface quality of BeO and InGaAs is investigated. Long channel BeO MOSFETs is analyzed with transfer and output characteristics and effective mobility by comparing with Al<sub>2</sub>O<sub>3</sub> MOSFETs.

Chapter 4 introduces Quantum Well (QW) InGaAs MOSFETs employing an interface passivation layer (IPL) with BeO [44]. Quantum Well MOSFETs are designed to be immune to short channel effect [45-47]. Device performance including drive current, transconductance, subthreshold swing and effective mobility of devices are examined. Additionally, BeO MOSCAPs are studied to observe the interface property when BeO is applied as an IPL. MOSCAP characteristics are investigated and compared between devices with and without a BeO IPL.

In chapter 5, as a device fabrication approach for interface improvement, *in situ*Ar ion plasma treatment is considered [48]. This process comes from Ar ion

bombardment in a plasma sputtering system. It is done in a plasma enhanced ALD (PEALD) system which allows remote generation of a low-power plasma MOS capacitance characteristics are examined to study the electrical effect of interface property. X-ray photoelectron spectroscopy (XPS) is used to observe chemically changes.

Summary of this dissertation and future work is addressed in chapter 6. Especially, as process development for high- $\kappa$  improvement deuterium (D<sub>2</sub>) high-pressure annealing is utilized on InGaAs substrate. It is reported that D<sub>2</sub> can improve hot carrier injection reliability to compensate Si dangling bond better than hydrogen in Si device process [49, 50]. By measuring general C-V characteristic and comparing interface trap density (D<sub>it</sub>), the effect of D<sub>2</sub> high-pressure annealing is examined, and future action items are suggested. In addition, the solid phase doping is introduced as 3D doping application [51]. Basically, solid phase doping is that dopant film is deposited on substrate and activated by RTA process. It is observed that the change in I-V characteristics after doped InGaAs substrate. In order to uniform dope on 3D device structure, this novel doping method is tried to apply to 3D structure.

## Chapter 2: Atomic layer deposition Beryllium oxide on III-V materials

It is reported that bulk crystalline and ceramic forms of BeO have many excellent materials properties as described in Table 2.1. Unlike other alkaline earth oxides and candidate high-κ gate dielectrics with significant ionic character, [7, 52] the chemical bonding in BeO exhibits significant covalent character. Unfortunately, aside from these basic thin film and interfacial electrical properties, many of the interesting properties for bulk crystalline and ceramic BeO have yet to be reported or are still uncertain for ALD BeO thin films. <sup>1</sup>

#### 2.1 LIQUID TYPE BERYLLIUM OXIDE ALD

Previous ALD BeO was grown with solid-type beryllium source, called dimethylberyllium ((Be(CH)<sub>3</sub>)<sub>2</sub>). It is synthesized with BeCl<sub>2</sub> using Grignard metathesis [53]. Generally, the solid type precursor requires relatively high-temperature to sublimate, even overdrive system limitation. The solid typed ALD source remains some white colored solid in deposition system, which may BeO or dimethylberyllium itself transporting by carrier gas. It can be source of contamination to substrate. Thus, liquid type beryllium precursor is developed lead by Prof. Todd Hudnall in Texas State University.

<sup>&</sup>lt;sup>1</sup>This chapter is based on reference [43]: <u>D. Koh</u>, J. H. Yum, S. K. Banerjee, W. A. Lanford, B. L. French, M. French, P. Henry, H. Li, M. Kuhn, S. W. King. "Investigation of ALD BeO Material Properties for High-к Dielectric Applications", *J. Vac. Sci Technol. B*32,03D117 (2014).

D.Koh contributed to BeO film on Si sample preparation, topological measurement, optical index extraction, and CV measurement.

In this chapter, to observe chemical composition in ALD BeO, Auger Electron Spectroscopy (AES), X-ray Photoelectron Spectroscopy (XPS), Rutherford backscattering (RBS), and Nuclear Reaction analysis (NRA) are carried out with 124 nm bulk BeO on Si substrate. As well as material chemical properties, the experimental work.

| Crystal Structure                                                | Wurtzite                             |

|------------------------------------------------------------------|--------------------------------------|

| Lattice Constant (nm)                                            | a=0.2698, c=0.4378                   |

| Melting point (℃)                                                | $2530 \pm 10$                        |

| Mass density (g/cm <sup>3</sup> )                                | $3.001 \pm 0.001$                    |

| $\Delta H_F^{291}$ (KJ/mol)                                      | $-616.2 \pm 2.4$                     |

| ΔS <sup>298</sup> (J/mol K)                                      | $14.1 \pm 0.2$                       |

| Heat capacity – $C_p^{298}$ (J/mol K)                            | $25.3 \pm 0.2$                       |

| Define otive in deer                                             | 1.719 ⊥ c-axis                       |

| Refractive index – n                                             | 1.733, ∥ c-axis                      |

| Static/low frequency dielectric constant – k                     | 6.94, ⊥ c-axis                       |

|                                                                  | 7.65, ∥ c-axis                       |

| Band gap (eV) - E <sub>g</sub>                                   | 10.6                                 |

| Thermal conductivity (W/mK) – k                                  | 370 (@300K)                          |

| Volume thermal expansion coefficient (10 <sup>-5</sup> /K)       | $2.66 \pm 0.1$                       |

| Linear thermal expansion coefficient (10 <sup>-6</sup> /K)       | 5.99, ⊥ c-axis                       |

| Bulk modulus (GPa)                                               | $212 \pm 3$                          |

| Voume's modulus (CDs)                                            | 369.6, ⊥ c-axis                      |

| Young's modulus (GPa)                                            | 418.9 ∥ c-axis                       |

| Complete (m/s)                                                   | 12370, longitudinal                  |

| Sound velocity (m/s)                                             | 7449, tranverse                      |

| Poisson's ratio – v                                              | $0.2, v_{112} = 0.38, v_{13} = 0.25$ |

| Piezoelectric constant (10 <sup>-12</sup> C/N) – d <sub>33</sub> | 0.24                                 |

| Pyoelectric constant (10 <sup>-6</sup> C/m <sup>2o</sup> C)      | -0.34                                |

Table 2-1: Summary of properties for crystalline and ceramic/poly-crystalline BeO.

## 2.2 BERYLLIUM OXIDE CHEMICAL COMPOSITION INVESTIGATION

To observe chemical composition in ALD BeO, various chemical analysis, such as AES, XPS, NRA, and RBS is carried out with 124 nm bulk BeO on Si substrate. The surface composition and chemical bonding in ALD BeO film is observed with AES and XPS. Figure 2-1 shows an AES spectrum acquired from the ALD BeO film as-loaded and after 60 s Ar+ sputtering. The AES spectra clearly show the presence of a trace level of surface carbon contamination that disappears after light Ar+ sputtering. The remaining features in the sputtered ALD BeO AES spectrum include Be KVV and O KLL Auger peaks whose line shapes are consistent with those obtained from BeO thin films formed via *in-situ* oxidation of metallic Be surfaces or bulk BeO ceramics [54-56].

The higher peak-to-peak ratio for oxygen relative to Be in the AES spectrum is due to the higher sensitivity of AES to the O KLL relative to the Be KVV and is not indicative of an oxygen rich BeO film.

Figure 2-1: AES spectra of ALD BeO before and after Ar+ sputtering.

The surface composition and chemical bonding for the ALD BeO film were additionally investigated using XPS. Similar to AES, an XPS survey spectrum of the asloaded ALD BeO film showed the presence of a surface carbon contamination layer that was reduced by Ar+ sputtering.

Figure 2-2: XPS spectra of ALD BeO Be 1s core level before and after Ar+ sputtering.

Figure 2-3: XPS spectra of ALD BeO O 1s core level before and after Ar+ sputtering.

Figures 2-2 and 2-3 show XPS spectra for the Be 1s and O 1s core levels of the ALD BeO film before and after sputtering. These spectra were corrected for charging by aligning the C 1s core level pre-sputtering to 285.0 eV. The centroid of the Be 1s and O 1s core levels was determined via fitting to a mixed Gaussian–Lorentzian line shape with a Shirley background. As shown in Figure 2-2 and 2-3, the core levels were well fitted using single peaks centered at 113.6 and 531.7-532.0 eV, respectively. These energy positions are consistent with Be-O bonding and other XPS measurements of BeO ceramics [57]. Ar+ sputtering was observed to have minimal effect on the Be 1s position but did result in a slight increase in the full width half maximum (FWHM) from 2 to 2.2 eV. For the O 1s, Ar+ sputtering also resulted in a slight broadening of the FWHM from 2.2 to 2.4 eV but also induced a slight decrease in the O 1s position from 532.0 to 531.7 eV. The large FWHM and slight broadening of the Be 1s and O 1s core levels can be attributed to a combination of the amorphous structure of the ALD BeO film, charging, and sputtering induced surface disorder. The decrease in the O 1s core level position is likely due to the removal of some surface carbonate or adsorbed oxygen species not deconvoluted in fitting the as-loaded O 1s spectra.

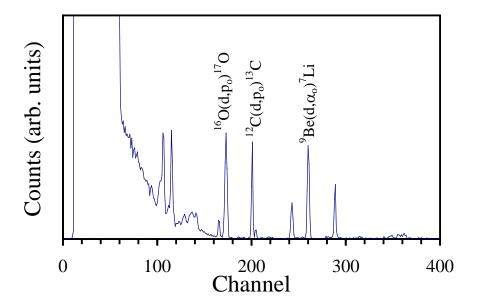

To investigate the bulk composition of the ALD BeO film and more closely check the stoichiometry and presence of residual carbon and hydrogen contamination, additional RBS and NRA measurements are performed. The deuteron induced NRA measurements are shown in Figure 2-4 where a number of strong peaks from nuclear reactions can be observed. Close examination of Figure 2-4 reveals that the carbon peak

is actually a doublet, with the lower energy C peak at channel 198 being an order of magnitude stronger than the higher energy C peak at channel 202. This is indicative of carbon present both at the film/substrate interface (lower energy) and the surface (higher energy). These observations are also consistent with the prior AES and XPS measurements that showed the presence of some surface carbon on the ALD BeO film.

Figure 2-4: Nuclear Reaction Analysis (NRA) spectrum of ALD BeO.

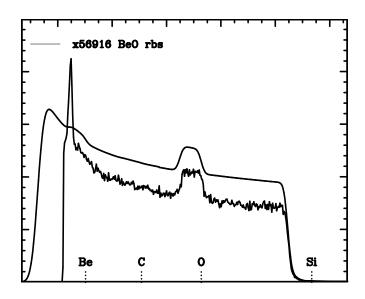

For Be analysis, the strong peak at channel 257 from the  ${}^{9}\text{Be}(d,\alpha_{0})^{7}\text{Li}$  reaction was used. To establish the nuclear reaction cross section/calibration constant for Be, the calibration constant was varied until the Si substrate edge in the RUMP simulation matched the measured RBS spectrum shown in Figure 2-5.

Figure 2-5: Rutherford Backscattering Spectrometry (RBS) spectrum of ALD BeO.

This procedure relies on the energy loss rate of He in the target material. The concentration of Be, O, and H were then determined from RUMP RBS simulations. These simulations yielded concentrations of 7.2, 6.3, and  $0.6 \times 10^{22}$  atoms/cm<sup>3</sup> for Be, O, and H, respectively. The combined NRA–RBS results indicate the film is slightly Be rich (Be/O =  $1.1 \pm 0.05$ ) with a low but significant hydrogen content of 4%. However, the slight deviation from Be/O stoichiometry is nearly within the error bar for Be content. The full elemental composition from RBS also allows the mass density to be estimated at  $2.8 \pm 0.1$  g/cm<sup>3</sup> which is substantially less than the value determined by XRR, but within the XRR error bars and still close to the theoretical density of 3.0 g/cm<sup>3</sup>. The lower RBS

value for mass density is consistent with the as deposited amorphous structure of ALD BeO as confirmed by separate x-ray diffraction measurements [58, 59].

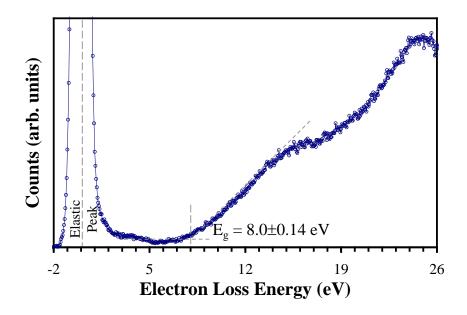

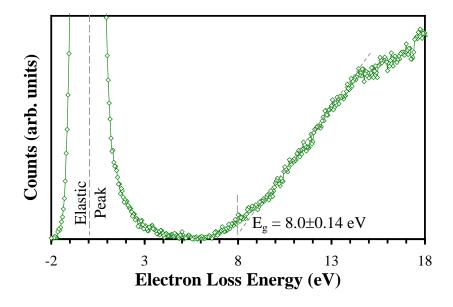

Figure 2-6: REELS spectrum of as-loaded ALD BeO collected using a 2.5 keV electron beam.

Figure 2-7: REELS spectrum of ALD BeO collected after Ar<sup>+</sup> sputtering using a 2.5 keV electron beams.

Figures 2-6 and 2-7 show 2.5 keV REELS spectra acquired from the ALD BeO film before and after  $Ar^+$  sputtering, respectively. The REELS spectrum in Figure 2.6 shows a maximum in loss intensity at approximately  $24.6 \pm 0.1$  eV. The position of this maximum is consistent with prior EELS measurements on single crystalline BeO and BeO thin films where a maximum at 24.5 eV has been observed and attributed to the excitation of a bulk plasmon [60-63].

The position of this plasmon is also consistent with a thin film mass density [60, 62] of 3.0 g/cm<sup>3</sup> which is in excellent agreement with the theoretical density for crystalline BeO. However, ALD BeO has only been observed to crystallize after rapid thermal annealing at temperatures of 600  $\sim$  900 °C and such films are not investigated here. Based on the combined XRR, RBS, and REELS mass density measurements, it is revealed that the mass density for as-deposited ALD BeO is  $3.0 \pm 0.3$  g/cm<sup>3</sup>.

### 2.3 ALD BERYLLIUM OXIDE MECHANICAL PROPERTIES

The mechanical properties of ALD BeO were also investigated via nano-indentation. The Young's modulus and hardness values determined from these measurements are summarized in Table III. As can be seen, a high Young's modulus and hardness of  $330 \pm 30$  and  $33 \pm 5$  GPa were, respectively, determined. The Young's modulus value is lower but close to the values of  $380 \sim 420$  GPa reported for BeO single crystals and ceramics [64]. These values are also substantially higher than those reported for other amorphous ALD high- $\kappa$  dielectrics. Specifically, the Young's modulus and

hardness values reported in the literature for ALD  $Al_2O_3$  are  $180 \sim 220$  and  $10 \sim 12$  GPa [65, 66], respectively, and for HfO<sub>2</sub>, similar values of  $150 \sim 220$  and  $9 \sim 11$  GPa have been reported [66, 67]. For additional comparison, nanoindentation measurements performed on the same 1 lm diamond film utilized in the XRR measurements indicated a Young's modulus and hardness of  $500 \pm 50$  and  $35 \pm 5$  GPa, respectively. These results are consistent with BeO being one of the hardest materials next to diamond[64].

In summary, an array of thin film metrologies has been utilized to investigate the material properties of BeO films prepared by ALD. The as-deposited films show a low H and C content and are nearly stoichiometric. Based on combined XRR, RBS, and REELS measurements, the mass density of ALD BeO was concluded to be  $3.0 \pm 0.3$  g/cm<sup>3</sup> and similar to the theoretical value of 3.0 g/cm<sup>3</sup> for crystalline wurtzite BeO. ALD BeO was also found to exhibit a wide band gap of 8 eV and high Young's modulus of  $330 \pm 30$  GPa. Both of these properties are slightly reduced relative to the reported values for single crystalline wurtzite BeO but are substantially higher than those reported for SiO<sub>2</sub> and other high- $\kappa$  dielectrics (Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>). These results support both the excellent device and reliability performance reported for Si and III-V MOSFET devices fabricated with ALD BeO as the gate dielectric.

# **Chapter 3: Surface Channel InGaAs MOSFETs with BeO**

In previous chapter, chemical and mechanical properties of liquid source ALD BeO were investigated, presenting its possibility of high-κ application. To exam the potent of ALD BeO as high-κ for III-V channel, surface channel InGaAs MOSFETs are fabricated and characterized in this chapter. The interface quality of ALD BeO is evaluated using XPS, TEM, and MOS capacitance. BeO surface channel InGaAs MOSFETs are fabricated to understand electrical properties. <sup>2</sup>

#### 3.1 SURFACE STOICHIOMETRY OF ALD BEO ON INGAAS

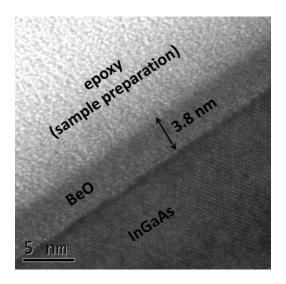

Figure 3-1: High resolution cross-sectional TEM analysis of ALD BeO grown on InGaAs

<sup>&</sup>lt;sup>2</sup>This chapter is based on reference [19]: <u>D. Koh</u>, J-H. Yum, T. Akyol, D. A. Ferrer, M. Lei, T. W. Hudnall, M. C. Downer, C. W. Bielawski, R. Hill G. Bersuker, S. K. Banerjee. "Novel Atomic Layer **Deposited Thin Film Beryllium Oxide for InGaAs FETs**", Aug. 27-30, *IPRM 2012*, Santa Barbara, CA, USA.

J.-H. Yum and T. Akyol designed this experiment and transferred to D. Koh. D. Koh reproduced metrology measurement (AFM and TEM), as well as capacitance characterization.

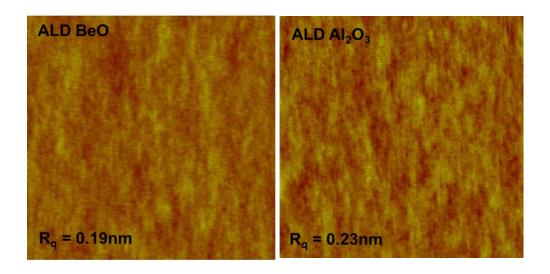

Cross-sectional Transmission Electron Microscopy (TEM) images of BeO on InGaAs are indicated in Figure 3-1, demonstrating a sharp interface with InGaAs surface. Surface Atomic Force Microscope (AFM) images of ALD grown BeO and  $Al_2O_3$  films on InGaAs substrate in Figure 3-2 compare surface roughness values. BeO film presents a low RMS surface roughness of 0.19nm in  $3\times3~\mu m$  sized scan area.

Figure 3-2: AFM and surface roughness analysis of ALD BeO and Al2O3 grown on InGaAs

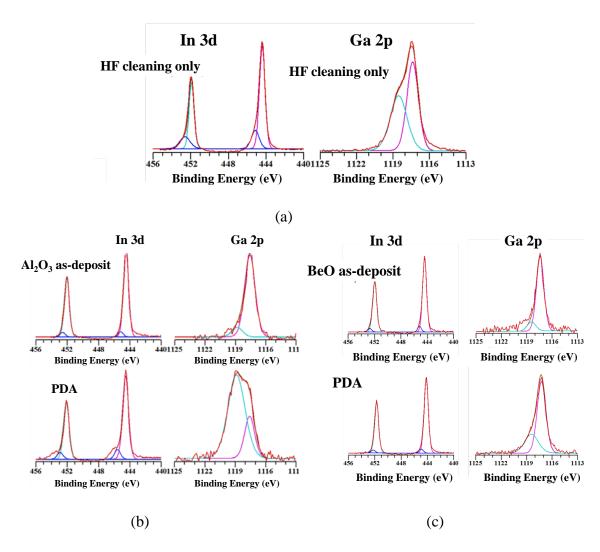

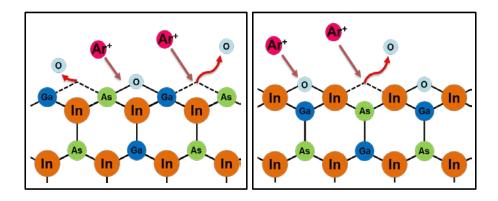

X-ray photoelectron spectroscopy (XPS) demonstrates the interface quality comparison between  $Al_2O_3$  and BeO film before and after without post-deposition annealing (PDA) as shown in Figure 3-3. Comparing as-deposited XPS result, the self-cleaning effect is observed on BeO deposited InGaAs surface by showing native oxides

reduction  $(In_xO_y, Ga_xO_y)$  and  $As_xO_y$ . After post deposition annealing (PDA), XPS presents that the native oxide on BeO deposited InGaAs surface is less grown than that of  $Al_2O_3$  deposited InGaAs surface. It is because BeO has better thermal stability leading less oxide out-diffusion during PDA.

Figure 3-3: XPS spectrum comparison of ALD Al<sub>2</sub>O<sub>3</sub> and BeO film deposited InGaAs substrate. (a) XPS spectra of initial InGaAs surface, (b) Al<sub>2</sub>O<sub>3</sub> deposited InGaAs surface before and after PDA, and (c) BeO deposited InGaAs surface before and after PDA.

#### 3.2 MOS CAPACITANCE CHARACTERISTIC COMPARISON

MOS capacitor is simple experimental structure to estimates the dielectric properties and interface quality with substrate. Before transistor characterization, MOS capacitance is fabricated and compared with Al<sub>2</sub>O<sub>3</sub> MOSCPAs. For MOS capacitor fabrication, InGaAs grown on semi-insulating InP is used for substrate. Initial cleaning with diluted HF is carried out. ALD Al<sub>2</sub>O<sub>3</sub> or BeO is deposited up to around 10nm and 9 m, respectively, to adjust the same EOT (5 nm). TaN is deposited as gate metal pad and then residual area is etched by using TaN as a hard mask.

Figure 3-4

Figure 3-4

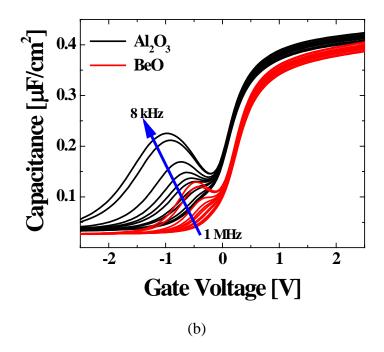

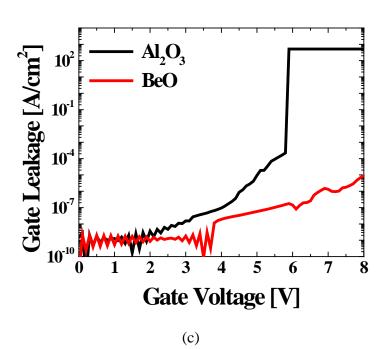

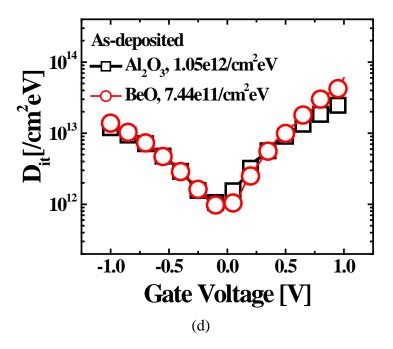

Figure 3-4: The MOS C-V characteristic comparison between Al<sub>2</sub>O<sub>3</sub> and BeO MOSCAPs. (a) C-V hysteresis (b) frequency dispersion (c) gate leakage current density, (d) interface trap density

BeO InGaAs MOS capacitor demonstrates that the threshold voltage shifts in positive direction. It means that BeO includes less interface charges because the ideal threshold voltage equation is calculated with metal-semiconductor work function ( $\Phi_{ms}$ ), interface charge ( $Q_i$ ), depletion charge ( $Q_d$ ), and the surface potential ( $\phi_B$ ) shown in equation (3.1).

$$V_{th} = \Phi_{ms} - \frac{Q_i}{C_i} - \frac{Q_d}{C_i} + 2\phi_F$$

eq. (3-1)

It is assumed that the work function, depletion charge, and surface potential are the same since MOSCAPs are fabricated on the same substrate, but positive charged interface trap is only different parameter. Therefore, the positive shifted threshold voltage indicates the

less interface trap density. The C-V frequency dispersion in Figure 3-4 (c) is in agreement with interface trap density shown in Figure 3-4 (d) by demonstrating less dispersion. Since the band-gap of BeO is larger than Al<sub>2</sub>O<sub>3</sub>, lower gate leakage current density is measured at BeO MOSCAPs.

#### 3.3 SURFACE CHANNEL INGAAS MOFETS FABRICATION AND CHARACTERIZATION

Based on BeO film properties on InGaAs substrate and MOS capacitance characteristic, surface channel InGaAs MOSFETs is fabricated and characterized. The gate last MOSFET process is employed with 200 nm undoped In<sub>0.53</sub>Ga<sub>0.47</sub>As epi-layer which is grown on semi-insulating (100) InP wafers. The native oxide on InGaAs surface was cleaned in 1% HF solution for 1 min. A capping layer of 100A° ALD Al<sub>2</sub>O<sub>3</sub> dielectric was deposited to prevent As-out-diffusion and surface degradation during the S/D activation annealing. Based on align mark, S/D regions were defined and doped with Si ion implantation at 35 keV,  $5 \times 10^{14}$ /cm<sup>2</sup>. After removal of photoresist, S/D activation annealing was done at 700 °C for 10 ~15 s and Al<sub>2</sub>O<sub>3</sub> capping layer was etched off using buffered oxide etchant (BOE). Surface was cleaned and passivated in 1% HF solution for 1 min, and then in 20% (NH<sub>4</sub>)<sub>2</sub>S solution for 10 min at room temperature. Subsequently, 100 cycle BeO and 90 cycle Al<sub>2</sub>O<sub>3</sub> gate dielectrics were grown in the ALD system at 250°C in order to achieve the same EOT. Next, a post-deposition (rapid thermal) annealing (PDA) step was performed at 500 °C for 2 min in N<sub>2</sub> ambient, followed by a 2000 Å thick TaN metal-gate deposition using a dc magnetron sputtering system. TaN gate was patterned and etched by CF<sub>4</sub> plasma RIE process. For S/D contacts, BeO/Al<sub>2</sub>O<sub>3</sub> dielectric layer where covered on S/D region is etched in BOE after S/D patterning. S/D metallization was finished with AuGe/Ni/Au (40/10/50 nm) lift-off process.

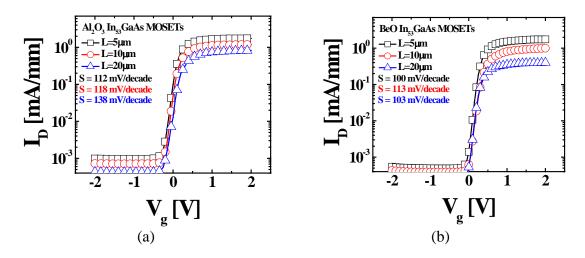

Figure 3-5: I-V characteristics of n-InGaAs MOSFETs with (a) Al<sub>2</sub>O<sub>3</sub> and (b) BeO gate dielectric

The minimum subthreshold swing (SS) of InGaAs MOSFETs (L=5μm) with BeO dielectric is 100 mV/decade, comparing to that with Al<sub>2</sub>O<sub>3</sub> (112 mV/decade). It is notable that BeO MOSFETs have positive threshold voltage and lower off-state current, which is in agreement with the result from BeO MOSCAPs as shown in Figure 3-4. Since BeO is able to form better interface with InGaAs in terms of low roughness and less interface trap density, BeO MOSFETs also show better performance characteristics in terms of low resistance in linear region presenting in Figure 3-6.

Figure 3-6: Output characteristic of InGaAs MOSFETs with (a) Al<sub>2</sub>O<sub>3</sub> and (b) BeO gate dielectric

Figure 3-7: Effective mobility comparison between BeO and Al<sub>2</sub>O<sub>3</sub> MOSFETs

Figure 3-7 illustrates the effective electron mobility using split C-V method. The peak mobility of BeO MOSFET is 1477 cm<sup>2</sup>/Vs, and that of Al2O3 MOSFET is 1172 cm<sup>2</sup>/Vs. BeO gate stack MOSFET performs 26% higher effective mobility.

In summary, InGaAs surface channel n-MOSFETs with ALD BeO dielectric is fabricated and characterized. By comparing with Al<sub>2</sub>O<sub>3</sub> gate stack in MOSCAPs and MOSFETs, BeO gate dielectric shows better interface properties in low roughness, less interface trap density, and low gate leakage current in MOSCAPs. For device performance, BeO MOSFETs indicates low off-state current, positive shifted threshold voltage, low resistance in linear region, and higher effective mobility.

# Chapter 4: Introduction of Quantum Well (QW) III-V MOSFETs

In device characterization point of view, InGaAs Quantum Well (QW) structure is a promising for device performance, because it is still hard to achieve intrinsic carrier mobility in III-V MOSFETs. Quantum well structure indicates that the channel layer is located in a distance from top surface where touches with high-κ gate oxide. By inserting an InP buffer layer between the high-κ and channel layer, it prevents the channel layer from creating notorious interface with high-κ dielectric layer. In order to fully benefit from its intrinsic electrical properties in aggressively scaled III-V devices, it is imperative to adopt a quantum-well QW) design to mitigate the short-channel-effects (SCEs), similar to ultra-thin-body architecture (UTB) in Si MOSFETs. Especially, the movement of electrons under the gate, easily turns into ballistic transport in a quantum well structure [45].<sup>3</sup>

### 4.1 BEO IPL FOR QUANTUM WELL (QW) INGAAS MOSFETS

Although InP buffer layer is employed to protect the channel layer, InP, itself is also one of the III-V materials. It has the possibility to form poor interface property with high-κ gate dielectric layer. Therefore, BeO is considered as an IPL, because it has

<sup>&</sup>lt;sup>3</sup>This chapter is based on reference [44]: <u>D. Koh</u>, H. M. Kwon, T.-W. Kim, D.-H. Kim, T. W. Hudnall, C. W. Bielawski, W. Maszara, D. Veksler, D. Gilmer, P. D. Kirsch, and S. K. Banerjee. "L<sub>g</sub> = 100 nm In<sub>0.7</sub>Ga<sub>0.3</sub>As Quantum Well MOSFETs with Atomic Layer Deposited Beryllium Oxide as interfacial layer", *Appl. Phy. Lett.* 104, 163502 (2014)

D.Koh designed experiments. D.Koh carried out fabrication BeO/HfO<sub>2</sub> IPL MOSFETs and electrical measurement.

including high melting point,[40, 68, 69] large dissociation energy,[70] high thermodynamic chemical stability,[71, 72] high thermal conductivity,[73-75] high bulk modulus,[76-79] and high electrical resistivity,[80, 81] in addition to a large band gap of 10–10.6 eV (Refs. [60, 82, 83]), and low interfacial trap density with III-V channel. In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors with ALD BeO as gate dielectric and IPL are fabricated to evaluate interface improvement. Electrical characteristics of nanometer-scale In<sub>0.7</sub>Ga<sub>0.3</sub>As QW MOSFETs with ALD BeO IPL are observed.

## 4.2 DEVICE PROCESS OF QW INGAAS MOSFETS

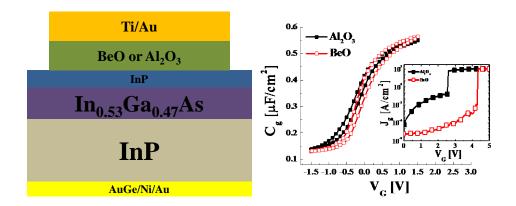

Figure 4-1: Schematic and TEM images of QW MOSFET device structure with BeO or BeO/HfO<sub>2</sub> as gate dielectric or interfacial layer, respectively. Especially, the TEM image indicates 1/1.5 nm BeO/HfO<sub>2</sub> deposited gate stack.

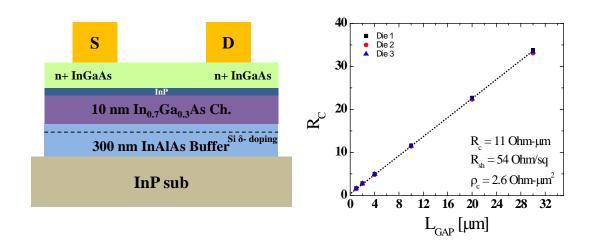

The cross-sectional view of  $In_{0.7}Ga_{0.3}As$  QW MOSFET is shown in Figure 4-1. The layer structure is grown by molecular beam epitaxy (MBE) on an InP substrate. A

300 nm  $In_{0.52}Al_{0.48}As$  is grown on InP substrate as a backside barrier layer. The quantum well channel consists of a 10 nm thick  $In_{0.7}Ga_{0.3}As$  channel and an  $In_{0.52}Al_{0.48}As$  barrier layer with inverted Si  $\delta$ -doping. Subsequently, a 2nm undoped InP barrier and 20nm n+  $In_{0.53}Ga_{0.47}As$  capping layer are sequentially grown. The capping layer decreases the potential barrier through both InP layers in the source and drain access region, and increases the electron concentration in the channel [47].

In order to achieve well-functioning device with this QW wafer structure, the device fabrication process is required to optimize, especially, the process for gate definition, and high- $\kappa$ /metal gate stack. Therefore, fundamental experiments are conducted for process optimization.

#### 4.3 FUNDAMENTAL EXPERIMENT FOR DEVICE

The quantum well InGaAs MOSFETs consists of raised n<sup>+</sup> InGaAs layer, InP buffer layer, channel InGaAs layer, and InAlAs buffer layer on InP substrate, sequentially. To define gate region, the recess process is considered to be suitable, since the recess process is wet chemical etching which forms less damaged InP surface where is behavior as stopping layer as well as buffer layer for carrier mobility [84]. In order to obtain proper etching rate and good quality etched surface, the gate recess process should be optimized and it is necessity to confirm with electrical measurement.

### **4.3.1** The Gate recess process

To etch n<sup>+</sup> InGaAs S/D layer, phosphoric acid (H<sub>3</sub>PO<sub>4</sub>) and peroxide (H<sub>2</sub>O<sub>2</sub>) are selected since they are popular chemical etchant for InGaAs. Based on general etching information [85], The chemical composition of etchant is started from H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:DI (1:1:32), which is reported to etch InGaAs on InP 120 nm/min. Since n+ InGaAs layer is 40 nm above the InP layer, and slow etching is more controllable, highly diluted H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> in DI (1:1: 80) is used.

Figure 4-2: The etch rate of InGaAs in based H<sub>3</sub>PO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub> etchant, which is carried out in room temperature for 1 min.

Figure 4-2 indicates that InGaAs etch rate in different composition of  $H_3PO_4$ :  $H_2O_2$  in DI water. Each etching experiment is conducted 7 times each and Atomic Force Microscopy (AFM) is used to measure etching profile. All measured etching depth

profile is compared with mean etching rate. The highly diluted etchant produces stable and constant result. The etchant composition, 1:1:64 is selected for gate recess.

Figure 4-3: The etch rate of InGaAs in based H<sub>3</sub>PO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub> etchant, which is carried out in room temperature for 1 min.

After MESA isolation, ohmic contact is completed with Mo/Ti/Au, and contact resistance and specific contact resistivity is extracted using TLM structure. The contact resistance of 11  $\Omega$ - $\mu$ m is achieved, and the specific contact resistivity is about 2.6  $\Omega$ - $\mu$ m<sup>2</sup>, which is comparable result with ref. [86].

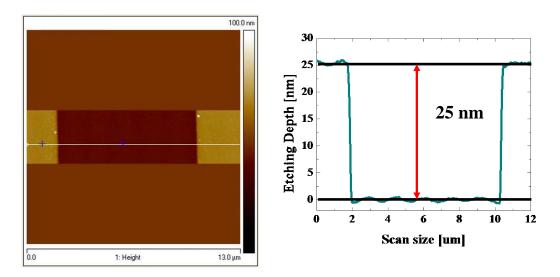

For short channel gate definition,  $n^+$  InGaAs is covered by  $SiO_2$  which is deposited as a hard mask. The  $SiO_2$  is grown by 25 nm in PECVE system and etched up to expose n+ InGaAs surface using dry etch process. The  $SiO_2$  etching profile is shown in Figure 4-4. The 25 nm thick  $SiO_2$  is well etched with plasma dry etch process.

Figure 4-4: The AFM profile after SiO<sub>2</sub> hard mask dry etching, where SiO<sub>2</sub> is grown 25 nm using PECVD.

Figure 4-5: The AFM profile of etched surface where includes SiO<sub>2</sub> as hard mask above the n<sup>+</sup> InGaAs capping layer.

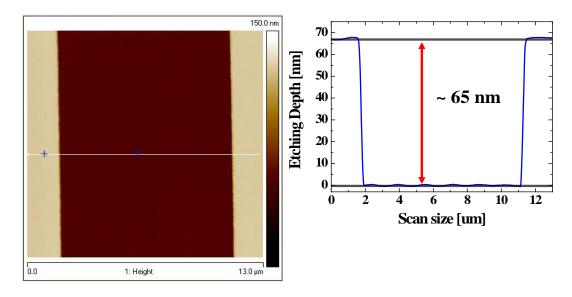

Based on InGaAs etching rate, 40nm thick n<sup>+</sup> InGaAs S/D layer is etched away for 30 sec. Figure 4-5 presents the gate recess profile after 30 sec etching. The etching profile

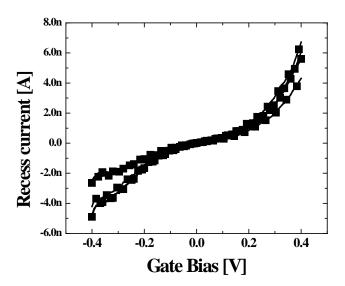

in Figure 4-5 includes etching  $SiO_2$ , hard mask which is shown Figure 4-4. Since gate recess means that highly doped InGaAs layer is electrically shorted, the current measurement is another way to investigate the gate recess process. After the InGaAs etching, electrical measure is carried out to observe current lowering. In Figure 4-6, very low current through shorted S/D layer is obtained. According to recess current measurement, the level of resistance in the shorted S/D region is close to insulator range where is around  $\sim 10^6 \, \Omega$  order.

Figure 4-6: The recess current after InGaAs etching in S/D region.

The H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> based etching rate is implement by changing composition and measuring depth profile using AFM, and constant etching rate is accomplished in lower concentration of H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> etchant. The recess current measurement is useful to monitor and confirm the gate recess accomplishment.

### 4.3.2 Electrical analysis of BeO QW InGaAs MOS capacitance

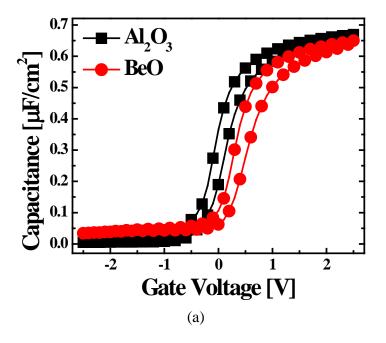

Figure 4-6 presents comparison of capacitance-voltage (C-V) and gate leakage current density characteristics of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors with ALD Al<sub>2</sub>O<sub>3</sub> and BeO. C-V Hysteresis in BeO MOSCAPs is slightly larger than that in Al<sub>2</sub>O<sub>3</sub> MOSCAPs, possibly due to the presence of carbon impurities in the beryllium precursor used for ALD, as reported in ref. [40].

Figure 4-6: Comparison of C-V characteristics and gate leakage current (inset). 10 nm Al<sub>2</sub>O<sub>3</sub> and BeO is grown using the same ALD system at 250 °C. The MOSCAP structure consists of n+ InP, 20 nm of In<sub>0.53</sub>Ga<sub>0.47</sub>As, and 2 nm of undoped InP layer.

However, the MOSCAP with BeO exhibits better modulation behavior of channel carriers than one with  $Al_2O_3$ . As gate bias swipes, the capacitance curve of BeO transits shows shaper than that of  $Al_2O_3$  due to interface trap density difference. The interface traps created by high- $\kappa$  deposition usually affect C-V characteristics, resulting in that C-V curves is distort. More importantly, a remarkable reduction in the gate leakage current density ( $\sim 10^{-7} \, \text{A/cm}^2$ ) is observed at forward bias region, as shown in Figure 4-6

(inset). This is due to not only large energy band-gap of BeO [87] , but also higher conduction band offset between BeO and  $In_{0.53}Ga_{0.47}As$  channel material than one with  $Al_2O_3$  [88, 89].

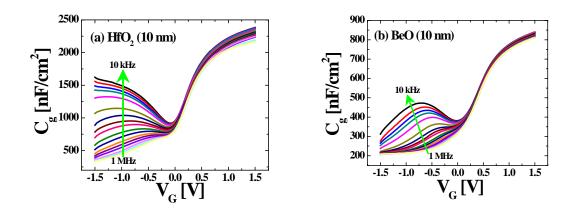

Figure 4-7: The comparison of frequency dispersion characteristic between HfO<sub>2</sub> and BeO MOSCAP

Figure 4-8: Frequency dispersion for InGaAs MOSCAP with 1nm BeO/ 1.5nm HfO<sub>2</sub> thickness gate dielectric.

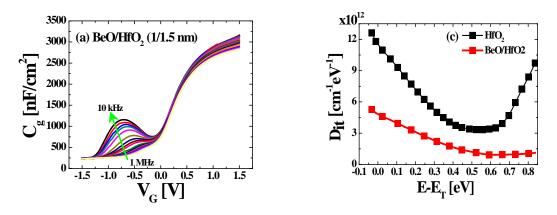

Figure 4-7 compare C-V frequency dispersion characteristics for  $In_{0.7}Ga_{0.3}As$  QW MOS capacitor with single dielectric, (a)  $HfO_2$  or (b) BeO, which are deposited 10 nm each. The device with 10 nm  $HfO_2$  in Figure 4-7 (a) shows worse frequency

dispersion than one with 10 nm BeO in Figure 4-7 (b), since HfO<sub>2</sub> film contains large defect sites inside film and forms poor interface with InGaAs. When BeO interface passivation layer is inserted between channel and high- $\kappa$ , the large stretch-out shown at HfO<sub>2</sub> single MOSCAP is alleviated in Figure 4-8 (a), while BeO/HfO<sub>2</sub> bi-layer dielectric MOSCAPs is maintaining similar interfacial trap density as single BeO and improving EOT scalability, as shown in Figure 4-8 (a).  $D_{it}$  distribution in Figure 4-8 (b) is extracted by conductance method with split C-V. The devices with BeO and BeO/HfO<sub>2</sub> yields a fairly low value of  $D_{it} = 2 \times 10^{12}$ / eV·cm and  $1 \times 10^{12}$ / eV·cm at mid-gap, whereas one with HfO<sub>2</sub> yields larger frequency dispersion and higher value of  $D_{it}$ . This indicates that BeO acts as a good interfacial-layer for  $In_{0.53}Ga_{0.47}As$  channel material.

# 4.3.3 Device analysis of InGaAs QW MOSFETs with BeO IPL

With those fundamental experiment results, BeO interface passivated InGaAs QW MOSFETs is fabricated and characterized. Firstly, electrical isolation of the active region is carried out using an H<sub>3</sub>PO<sub>4</sub> based wet etchant. Source and drain ohmic contacts to the n<sup>+</sup> InGaAs are made using e-beam evaporation and subsequent lift-off of Mo/Ti/Au metal stack. PECVD-grown SiO<sub>2</sub> layer is used to form a hard mask and the gate pattern is defined with ZEP-520A by JEOL 6000FX e-beam lithography. Then, CF<sub>4</sub>-based plasma dry etching is used to transfer the defined pattern onto the n<sup>+</sup> InGaAs capping layer. According to etching experiment result with H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> based solution, the n<sup>+</sup> InGaAs capping layer is etched for 30 sec to expose the InP layer. ALD BeO/HfO<sub>2</sub> is deposited at

250 °C 1/1.5 nm for IL and 5 nm BeO is grown for gate dielectric layer in Cambridge Nano ALD system. Subsequently, TiN metal gate is deposited with ALD system in an *in situ* manner. Finally, Ti/Au gate metal pad is deposited by e-beam evaporation.

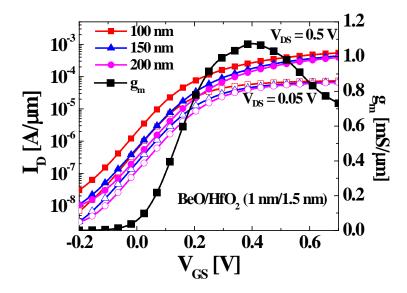

Figure 4-9 shows the electrical characteristics of  $In_{0.7}Ga_{0.3}As$  QW MOSFET with  $BeO/HfO_2$  composite gate dielectric layers. Figure 4-9 displays subthreshold and transconductance ( $g_m$ ) behavior of  $In_{0.7}Ga_{0.3}As$  QW MOSFETs with three different values of gate length ( $L_g = 200$  nm, 150 nm and 100 nm).

Figure 4-9: Subthreshold characteristic with different channel length and transconductance (gm) of  $L_{\rm g}=100$  nm of QW MOSFETs with BeO/HfO<sub>2</sub> (1/1.5 nm) gate stack.

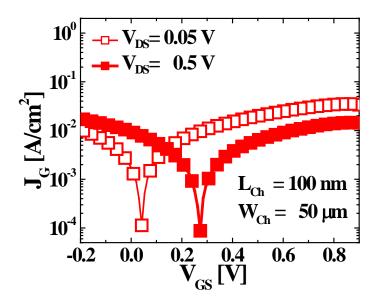

Figure 4-10: The gate leakage current density of  $L_g = 100$  nm QW MOSFETs with BeO/HfO<sub>2</sub> (1/1.5 nm) device at applied drain voltage 0.05 V and 0.5 V.

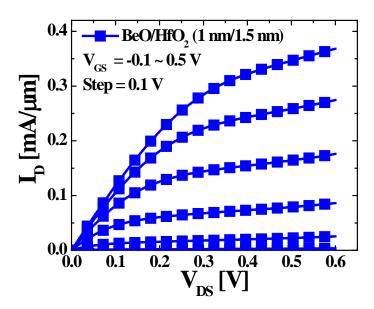

Figure 4-11: The output characteristic of  $L_{\rm g}$  = 100 nm QW MOSFET with BeO/HfO<sub>2</sub> (1/1.5 nm) gate dielectric.

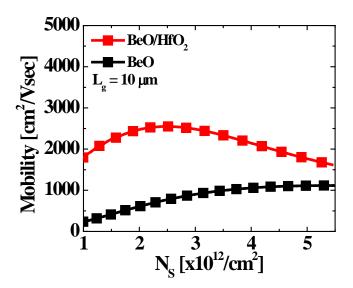

Figure 4-12: The mobility enhancement of  $L_g = 10 \mu m$  BeO/HfO<sub>2</sub> QW MOSFETs

The maximum transconductance  $(g_{m\_max})$  for the 100 nm gate length QW MOSFET is 1.1 mS/ $\mu$ m at  $V_{DS} = 0.5$  V. Low interface trap density in Figure 4-8 (b) leads to excellent subthreshold-swing (SS) of 100 mV/dec at  $L_g = 100$  nm. A fairly low value of gate leakage current density is observed as shown in Figure 4-10, which is around  $\sim 10^{-2}$  A/cm<sup>2</sup> at a drain bias  $V_{DS} = 0.5$  V, arising from the fact that BeO is very strong oxygen diffusion barrier and a dense oxide layer. Output characteristics of  $L_g = 100$  nm QW MOSFET are shown in Figure 4-11. The device with  $L_g = 100$  nm shows excellent current driving capability, such as  $I_D = 0.35$  mA/ $\mu$ m at  $V_{GS} = 0.6$  V. The bilayer oxide stack consists of a 1nm BeO and 1.5 nm HfO<sub>2</sub>, yielding an effective oxide thickness (EOT) of 0.93 nm. Excellent effective mobility ( $\mu_{e,eff}$ ) of 2500 cm<sup>2</sup>/V·sec is extracted from long-channel QW MOSFETs with the same BeO/HfO<sub>2</sub> composite dielectric layers.

These results highlight that the BeO forms excellent interface with InGaAs channel material.

In summary, we have demonstrated  $L_g=100$  nm  $In_{0.7}Ga_{0.3}As$  QW MOSFET with ALD BeO. The MOSCAPs with BeO exhibit reduced C-V stretch-out and yield fairly low values of  $D_{it} \sim 1\times 10^{12}$  /eV·cm<sup>2</sup>, since BeO is a dense oxide material and serves as a strong oxygen diffusion barrier. Besides, low gate leakage characteristic is a very attractive advantage of BeO.  $L_g=100$  nm  $In_{0.7}Ga_{0.3}As$  QW MOSFET with BeO/HfO<sub>2</sub> composite dielectric layers represent promising results at  $V_{DS}=0.5$  V, such as  $g_{m,max}=1.1$  mS/ $\mu$ m, SS = 100 mV/dec, DIBL = 100 mV/V, and  $\mu_{e,eff}=2500$  cm<sup>2</sup>/V·sec, with EOT = 0.93 nm.