Copyright by Rashid Kaleem 2017 The Dissertation Committee for Rashid Kaleem certifies that this is the approved version of the following dissertation:

# Efficient execution of irregular programs on heterogeneous systems

Committee:

Keshav Pingali, Supervisor

Donald Fussell

Vijay Janapa Reddi

Tatiana Shpeisman

Emmett Witchel

# Efficient execution of irregular programs on heterogeneous systems

by

Rashid Kaleem, B.S., M.S.

## DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

August 2017

In the name of Allah<sup>1</sup>, the Most Gracious, the Most Merciful.

Dedicated to AK & SK HR HR & MHR

<sup>&</sup>lt;sup>1</sup>Allah is the Arabic word for God in Islam

## Acknowledgments

All parise is due to Allah, the Cherisher and Sustainer of all the worlds. I would like to thank my parents who have always encouraged the pursuit of knowledge. I would also like to thank my spouse, whose patience and support was critical for me to focus on my research.

I am indebted to my advisor, Keshav Pingali, for his mentorship and support. His passion, patience, and persistence for research has been a great source of inspiration. His insistence on clarity and excellence has transformed my approach towards research.

While the list of all those who have supported my research directly or indirectly is too long to mention by name, I would like to thank each and everyone who I have interacted with during my graduate studies.

I am thankful to all the wonderfull collaborators and mentors I have had over my tenure as a graduate student. My colleagues, who made our window-less lab a second home, have undoubtedly contributed to my research. I have had the privilege to spent the time with such good colleagues and friends – Donald Nguyen, Dimitris Prountzos, Xin Sui, M. Amber Hassaan, and Gurbinder Gill.

I would also like to thank Tatiana Shpeisman and Raj Barik at Intel Labs, and Gabriel Tanase at IBM Research for hosting me as an intern. I am very fortunate to have enrolled in Professor Fussell's graduate course during my first semester - not only has his interactions proved invaluable for my research, his course undoubtedly helped my transition to a foreign country tremendously. I am also thankful to my committee members Vijay Reddi and Emmett Witchel for their constructive feedback on my research.

I would like to mention some of my close friends, who have been beside me through thick and thin - Ahmed Abrar, Shahzad Afzal, Fahad Khalil, Jawad Zafar, and Muhammad Shoaib Sehgal (late). I am also thankful for having wonderful mentors over the years – Shaiq A. Haq, Mian M. Saleem, Muhammad Afzal, Syed M. Ahsan, and Margaret Kilvington. Last but not least, I would like to mention Talha Waheed - who encouraged me to attend graduate school in the US.

# Efficient execution of irregular programs on heterogeneous systems

Publication No. \_\_\_\_\_

Rashid Kaleem, Ph.D. The University of Texas at Austin, 2017

Supervisor: Keshav Pingali

Programmable accelerators such as GPUs, FPGAs, and DSPs enable modern systems to provide higher performance for many workloads than is possible by using conventional processors alone. Traditionally, portability of applications to these accelerators and between accelerators was a major hurdle in utilizing accelerators in a heterogeneous system. With the emergence of standardized programming APIs such as OpenCL, this problem is being ameliorated and many accelerators can now be programmed using a single API.

In this work, we address the efficient execution of *irregular* programs on heterogeneous systems. Irregular programs are used extensively in problem domains like graph analytics and finite-element methods, and they are characterized by data-dependent control flow and memory accesses that cannot be predicted at compile time. We focus on heterogeneous systems that provide a coherent memory to all devices.

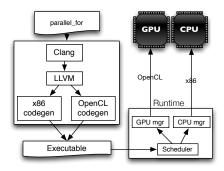

First, we describe a set of compiler and runtime techniques to support efficient execution of irregular programs on heterogeneous systems composed of a CPU and an integrated GPU. The compiler allows applications written in C++ to be executed on the GPU without any programmer effort. The runtime system solves the load imbalance arising from irregularity in the applications by dynamically assigning work to each device.

Next, we present an alternative implementation strategy for irregular applications on a system with more heterogeneity. Specifically, graph applications can be expressed as *producer-consumer* computations on FPGA+CPU heterogeneous systems. This approach allows for better utilization of the capabilities of each device and suggests a programming model for accelerators that goes beyond the *offload* model.

Finally, we explore efficient execution of irregular applications on accelerators that do not share a coherent memory with the master processor. For discrete GPUs, we explore implementation strategies of graph application, focusing on synchronization tradeoffs and present optimizations that address the synchronization overheads both within and across devices.

## **Table of Contents**

| Acknowled    | gments v                                                              |

|--------------|-----------------------------------------------------------------------|

| Abstract     | vii                                                                   |

| List of Tab  | es xiii                                                               |

| List of Figu | res xiv                                                               |

|              | Introduction       1         ntributions       2         line       3 |

| Chapter 2.   | Background 5                                                          |

| 2.1 He       | erogeneous Systems                                                    |

| 2.1          | 1 big.LITTLE                                                          |

| 2.1          | 2 Intel Haswell                                                       |

| 2.1          | 3 Terasic DE1-SoC                                                     |

| 2.2 Irre     | gular Applications                                                    |

| 2.2          | 1 Parallelism                                                         |

| 2.3 Gra      | ph Applications                                                       |

| 2.3          | 1 Operator                                                            |

| 2.3          | 2 Schedules                                                           |

| 2.4 Im       | blementation Issues                                                   |

| 2.4          | 1 Graph representation                                                |

| 2.4          | 2 Pull Implementations                                                |

| 2.4          | 3 Push Implementations                                                |

| 2.5 Ab       | stractions                                                            |

| 2.5          | 1 CUDA                                                                |

| 2.5          | 2 OpenCL                                                              |

| Chapte | r 3. I | Data-parallel execution with Integrated GPUs | 29 |

|--------|--------|----------------------------------------------|----|

| 3.1    | Introd | luction                                      | 29 |

| 3.2    | Comp   | iler                                         | 31 |

|        | 3.2.1  | Programming constructs                       | 32 |

|        | 3.2.2  | Shared Virtual Memory (SVM) support          | 34 |

|        | 3.2.3  | Virtual Functions                            | 37 |

|        | 3.2.4  | Reduction                                    | 38 |

|        | 3.2.5  | Compiler Optimizations                       | 39 |

|        |        | 3.2.5.1 Reduce SVM implementation overhead   | 40 |

|        |        | 3.2.5.2 Reduce GPU cache-line contention     | 41 |

| 3.3    | Heter  | ogeneous execution                           | 43 |

| 3.4    | Naïve  | profiling                                    | 48 |

|        | 3.4.1  | Analysis                                     | 50 |

|        | 3.4.2  | Determining profiling size                   | 53 |

| 3.5    | Asym   | metric profiling                             | 55 |

|        | 3.5.1  | Analysis                                     | 57 |

|        | 3.5.2  | Addressing load imbalance                    | 59 |

|        | 3.5.3  | Multiple invocations per kernel              | 60 |

|        |        | 3.5.3.1 Update functions:                    | 60 |

| 3.6    | Evalu  | ation                                        | 61 |

|        | 3.6.1  | Environment                                  | 61 |

|        | 3.6.2  | Benchmarks                                   | 62 |

|        | 3.6.3  | Comparison schemes                           | 65 |

|        | 3.6.4  | Results                                      | 67 |

| 3.7    | Sumn   | nary                                         | 70 |

| Chapte | r4. I  | Data-parallel execution with discrete GPUs   | 72 |

| 4.1    | Introd | luction                                      | 72 |

| 4.2    | Graph  | algorithms on discrete GPUs                  | 73 |

|        | 4.2.1  | Stochastic Gradient Descent (SGD)            | 75 |

| 4.3    | Offlin | e Schedules                                  | 78 |

|        | 4.3.1  | Maximal matchings schedules                  | 79 |

|        |              | 4.3.1.1 All-Graph Matching-Edge schedule (AGM-E) | • | 79  |

|--------|--------------|--------------------------------------------------|---|-----|

|        |              | 4.3.1.2 All-Graph Matching-Node schedule (AGM-N) | • | 81  |

|        |              | 4.3.1.3 Sub-Graph Matching (SGM)                 | • | 82  |

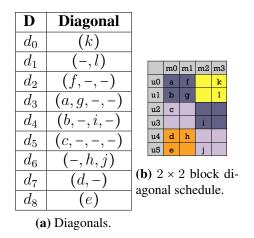

|        | 4.3.2        | Diagonal matchings schedules                     | • | 83  |

|        |              | 4.3.2.1 Diagonal (Diag) schedule                 | • | 84  |

|        |              | 4.3.2.2 Block-Diagonal (BlkDiag) schedule        | • | 84  |

| 4.4    | Online       | e Schedules                                      | • | 85  |

|        | 4.4.1        | Edge-locked (EL)                                 | • | 86  |

|        | 4.4.2        | Node-locked (NL)                                 | • | 88  |

| 4.5    | Hetero       | ogeneous schedules                               | • | 89  |

|        | 4.5.1        | Graph partitioning                               | • | 90  |

| 4.6    | Evalu        | ation                                            | • | 93  |

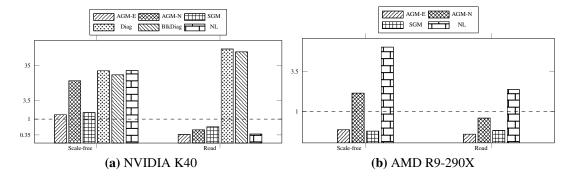

|        | 4.6.1        | Overall performance                              | • | 95  |

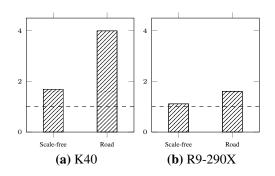

|        | 4.6.2        | Hybrid schedules                                 | • | 98  |

|        | 4.6.3        | Offline schedules                                | • | 99  |

|        | 4.6.4        | Heterogeneous schedules                          | • | 100 |

| 4.7    | Data c       | driven algorithms                                | • | 102 |

|        | 4.7.1        | Base implementation                              | • | 105 |

|        | 4.7.2        | Combiners                                        | • | 106 |

|        | 4.7.3        | Synchronization                                  | • | 108 |

|        | 4.7.4        | Partitioning                                     | • | 110 |

|        | 4.7.5        | Results                                          | • | 111 |

| 4.8    | Concl        | usion                                            | • | 115 |

| Chanta | <i>5</i> T   | Pipeline-parallel execution with FPGAs           |   | 117 |

| -      |              |                                                  |   |     |

| 5.1    |              |                                                  |   |     |

| 5.2    |              | eneck Analysis                                   |   |     |

| 5.3    |              | tion Models                                      |   |     |

|        | 5.3.1        | Data-parallel Execution                          |   |     |

|        | 5.3.2        | Gather-Apply Execution                           |   |     |

|        | <b>5 0 0</b> | 5.3.2.1 Implementation choices                   |   |     |

|        | 5.3.3        | Apply-Scatter implementation                     | • | 128 |

| 5.4     | Evaluation                             | 131 |  |

|---------|----------------------------------------|-----|--|

|         | 5.4.1 Applications                     | 132 |  |

|         | 5.4.2 Overall performance              | 136 |  |

|         | 5.4.3 Data-parallel implementations    | 137 |  |

|         | 5.4.4 Gather-Apply implementations     | 139 |  |

|         | 5.4.5 Apply-Scatter implementations    | 142 |  |

|         | 5.4.6 Work-list driven implementations | 143 |  |

| 5.5     | Conclusion                             | 146 |  |

| Chapte  | er 6. Related work                     | 148 |  |

| 6.1     | Graph programming models               | 148 |  |

| 6.2     | GPU programming                        | 148 |  |

| 6.3     | FPGA programming                       | 150 |  |

| 6.4     | Heterogeneous execution                | 151 |  |

| 6.5     | Data partitioning and layout           | 154 |  |

| Chapte  | Chapter 7. Future work 157             |     |  |

| Chapte  | Chapter 8. Conclusion 160              |     |  |

| Bibliog | Bibliography 10                        |     |  |

## List of Tables

| 3.1 | Key statistics for the kernels of benchmarks used in the evaluation.<br><i>Oracle-time</i> is the time taken by the best offline distribution, and is<br>also used as the normalizing factor in Fig. 3.14 and Fig. 3.15 62                                                              |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | GPU work percentages computed by different schemes for single-<br>kernel applications                                                                                                                                                                                                   |

| 4.1 | Specifications of the platforms used for evaluation                                                                                                                                                                                                                                     |

| 4.2 | Characteristics of the scale-free and uniform inputs. $ V $ is the total number of vertices in the graph, $ E $ is the number of edges in the graph, and $D_{max}$ represents the maximum degree of any node in the graph. $EL(s)$ is the running time of the EL versions in seconds 94 |

| 5.1 | Application node and edge data. The initial work-list sizes for the work-list driven implementations are also shown                                                                                                                                                                     |

| 5.2 | Application node and edge computations. The push implementa-<br>tions require atomic updates on the edges                                                                                                                                                                               |

| 5.3 | Inputs and their key properties                                                                                                                                                                                                                                                         |

| 5.4 | Differences in the number of regular and random reads and writes for the node labels of each variant                                                                                                                                                                                    |

## **List of Figures**

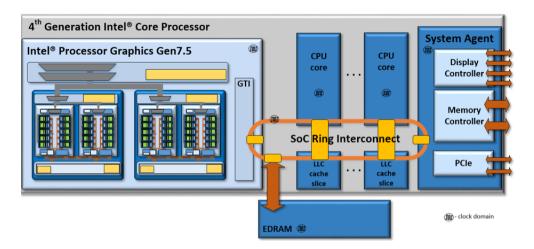

| 2.1  | Intel Haswell (4 <sup>th</sup> generation) processor architecture [Junkins, 2014].                                                                                                                                                                                                                                                                                                     | 8  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

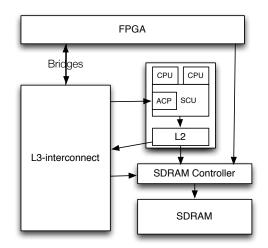

| 2.2  | Organization of a Cyclone-V SoC from Altera. The DE1-SoC from Terasic is an instance of this SoC.                                                                                                                                                                                                                                                                                      | 9  |

| 2.3  | Adding two array elements. The first snippet add two arrays se-<br>quentially, the second one performs an indirect read, while the third<br>one performs an indirect write.                                                                                                                                                                                                            | 11 |

| 2.4  | Control flow irregularity.                                                                                                                                                                                                                                                                                                                                                             | 12 |

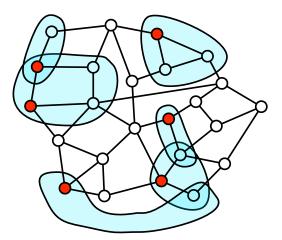

| 2.5  | A graph colored to represent the different dynamic components dur-<br>ing execution. <i>Red</i> nodes indicate <i>active elements</i> – nodes where a<br>computation needs to be performed, and the shaded region around<br>each active element denote the <i>neighborhood</i> of each activity – sets<br>of nodes and edges that are accessed during the execution of the<br>activity | 14 |

| 26   | activity.                                                                                                                                                                                                                                                                                                                                                                              | 14 |

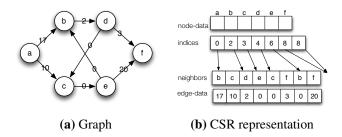

| 2.6  | A directed graph and its CSR representation. Node <b>e</b> does not have<br>any outgoing edges, so the indices entries for its edges point to the<br>end of neighbors array.                                                                                                                                                                                                           | 21 |

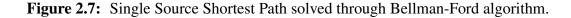

| 2.7  | Single Source Shortest Path solved through Bellman-Ford algorithm.                                                                                                                                                                                                                                                                                                                     | 22 |

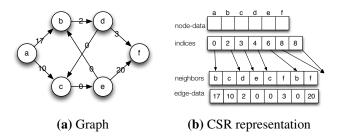

| 2.8  | A directed graph and its CSR representation. Node f does not have<br>any outgoing edges, so the indices entries for its edges point to the<br>end of neighbors array.                                                                                                                                                                                                                  | 22 |

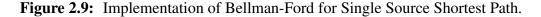

| 2.9  | Implementation of Bellman-Ford for Single Source Shortest Path                                                                                                                                                                                                                                                                                                                         | 23 |

| 2.10 | Single Source Shortest Path topology-driven push algorithm                                                                                                                                                                                                                                                                                                                             | 25 |

| 2.11 | Single Source Shortest Path work-list driven push algorithm                                                                                                                                                                                                                                                                                                                            | 26 |

| 3.1  | Concord programming constructs                                                                                                                                                                                                                                                                                                                                                         | 32 |

| 3.2  | Example demonstrating use of Concord <i>parallel_for</i> construct                                                                                                                                                                                                                                                                                                                     | 33 |

| 3.3  | Concord compiler and runtime overview.                                                                                                                                                                                                                                                                                                                                                 | 34 |

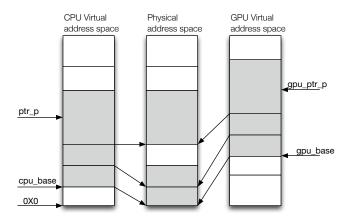

| 3.4  | Address translation from CPU virtual address space to GPU virtual address space.                                                                                                                                                                                                                                                                                                       | 35 |

| 3.5  | Example demonstrating Concord SVM implementation. Left side shows the C++ implementation provided by the programmer. Right side shows the transformed code including translation code to convert from CPU virtual addresses to GPU virtual addresses                                                                                                                                   | 36 |

| 3.6  | Example illustrating compiler transformation of shared pointers on GPU: lazy vs. eager                                                                                                                                                                                                                    |   | 40 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 3.7  | Reducing cache-line contention among GPU cores. Left side shows the original code.                                                                                                                                                                                                                        |   | 42 |

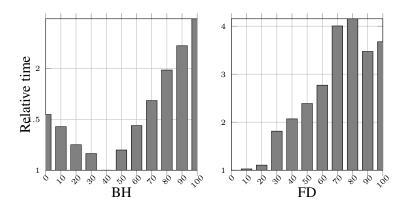

| 3.8  | Relative execution time of <b>BH</b> -BarnesHut (left) and <b>FD</b> -Facedetect (right) as ratio of work offloaded to the GPU is varied from $0\%$ to 100% in increments of 10% ( <i>lower is better</i> ). <b>BH</b> is optimal at $40\%$ and <b>FD</b> is optimal at $0\%$ .                           |   | 44 |

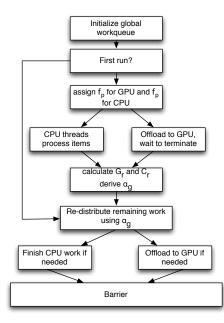

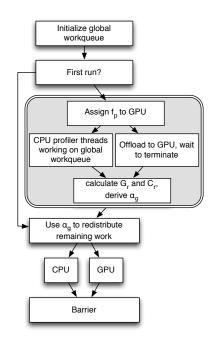

| 3.9  | Heterogeneous execution via Naïve profiling.                                                                                                                                                                                                                                                              |   | 51 |

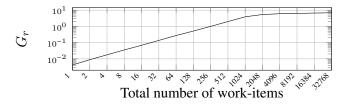

| 3.10 | Plot showing the change in $G_r$ with increasing number of work-<br>items for a regular kernel (note the logarithmic scales)                                                                                                                                                                              |   | 54 |

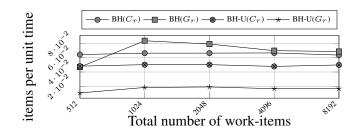

| 3.11 | Plot showing average $C_r$ and $G_r$ for different values of $Nf_p$ for BarnesHut ( <b>BH</b> ) and BarnesHut-unoptimized ( <b>BH-U</b> )                                                                                                                                                                 |   | 54 |

| 3.12 | Heterogeneous execution through symmetric profiling                                                                                                                                                                                                                                                       | • | 57 |

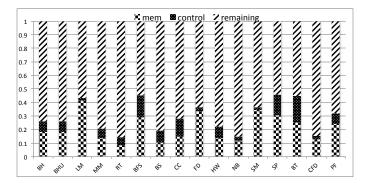

| 3.13 | Total number of dynamic instructions of benchmarks divided into three categories: <i>memory</i> , <i>control</i> , and <i>remaining</i> , obtained via a serial CPU execution. The number of dynamic instructions is given in Table 3.1(column 9).                                                        |   | 63 |

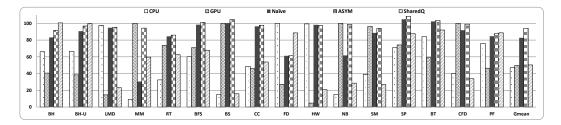

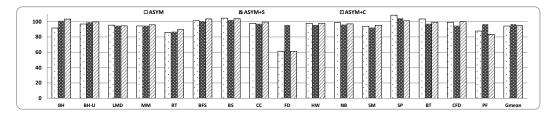

| 3.14 | Relative speedup for all benchmarks compared to Oracle. Oracle is at 100% (higher is better).                                                                                                                                                                                                             |   | 64 |

| 3.15 | Comparison of different adaptive schemes. Vertical axis shows rel-<br>ative speedup vs. Oracle (higher is better).                                                                                                                                                                                        |   | 66 |

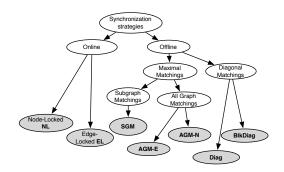

| 4.1  | Taxonomy of scheduling strategies.                                                                                                                                                                                                                                                                        |   | 74 |

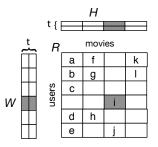

| 4.2  | Low-rank approximation of a sparse matrix $R$ by low rank matrices $W :  U  \times t$ and $H : t \times  M $ , usually $t \approx 16$ .                                                                                                                                                                   |   | 76 |

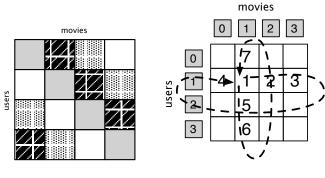

| 4.3  | Sample bipartite graph between 6 users and 4 movies. Edge labels indicate ratings.                                                                                                                                                                                                                        |   | 76 |

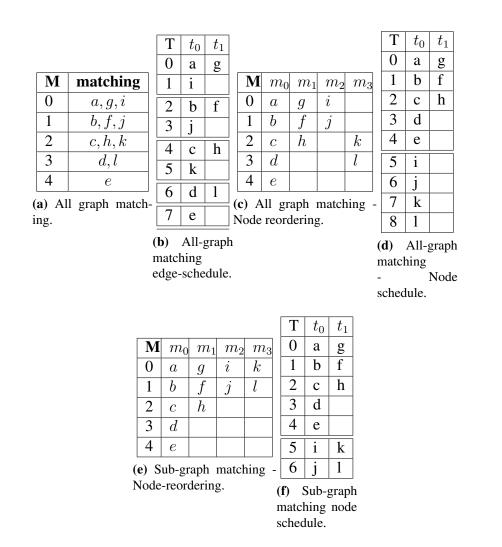

| 4.4  | Maximal matchings schedules executed by different strategies for sample input. Tables with <b>M</b> in top-left cell indicate matching sets, whereas tables with <b>T</b> in top-left cell indicate schedules where each row indicates a time-step and each column lists the edges processed by a thread. |   | 80 |

| 4.5  | Diagonal matchings schedules for the sample input                                                                                                                                                                                                                                                         |   | 83 |

| 4.6  | Schedules observed for sample input under EL(without and with shuffle) and NL on the hypothetical GPU. Each row indicates edges scheduled at that time slot, and each column indicates the item processed, if any, by each thread.                                                                        |   | 86 |

|      |                                                                                                                                                                                                                                                                                                           |   |    |

| 4.7  | Partitioning the graph along movies and users for multi-device ex-<br>ecution. Arrows indicate the search pattern for more work for a<br>device which has just completed work on partition $(1, 1)$ . First it<br>searches horizontally to maximize user-locality, and if it fails, it<br>retries vertically. The numbers indicate the search order 91 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.8  | Geomean normalized runtime of scheduling schemes over the two<br>input classes evaluated over two platforms. The runtimes are nor-<br>malized to EL's runtime. Lower is better                                                                                                                                                                         |

| 4.9  | Speedup of hybrid schedule over EL on the different GPUs across the two input classes. Higher is better                                                                                                                                                                                                                                                |

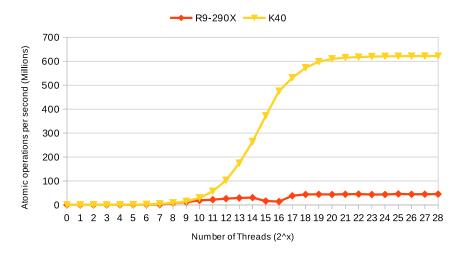

| 4.10 | Atomic throughput of the NVIDIA K40 and AMD R9-290X. X-<br>axis shows the number of threads launched, and Y-axis shows the<br>throughput of atomics operations <i>achieved</i> . The K40 peaks at about<br>600M atomic operations per second, while the R9-290X saturates<br>at about 45M                                                              |

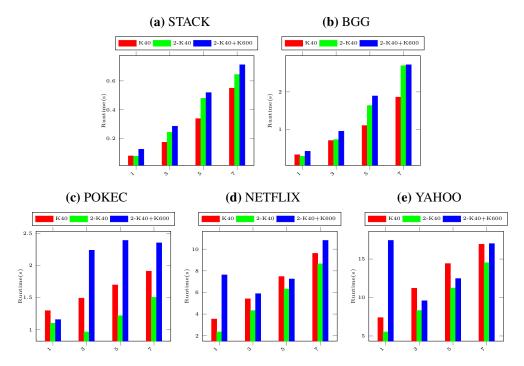

| 4.11 | Absolute runtime of multi-device SGD on different inputs. Each plot represents an input with varying over-decomposition along the x-axis. Different colors represent different device configurations. Lower is better                                                                                                                                  |

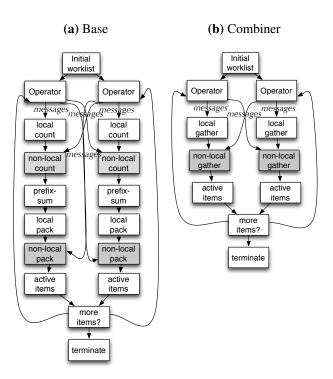

| 4.12 | Baseline vertex-program implementations for 2 devices. Gray boxes indicate cross-device communication. (a) shows the baseline version, whereas (b) shows the <i>combiner</i> version                                                                                                                                                                   |

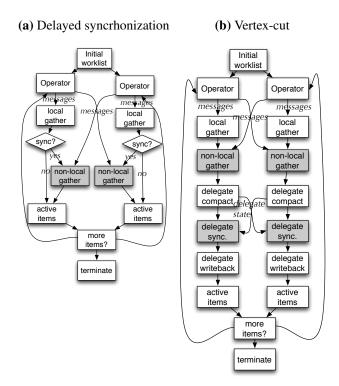

| 4.13 | Different optimization for vertex-program implementations on 2 devices. Gray boxes indicate cross-device communication. (a) shows the delayed synchronization strategy and (b) shows the vertex-cut implementation                                                                                                                                     |

| 4.14 | A Pregel program for single source shortest path                                                                                                                                                                                                                                                                                                       |

| 4.15 | A combiner implementation for single source shortest path 106                                                                                                                                                                                                                                                                                          |

| 4.16 | Vertex cut implementations. (a) shows a high degree node $x$ , also known as a hub, whereas (b) shows the hub split into two low degree nodes $xa$ and $xb$                                                                                                                                                                                            |

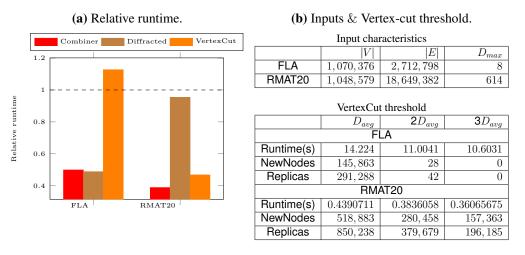

| 4.17 | (a) Relative runtime for different schemes compared to a base-version.<br>Lower is better. (b)Characteristics of the input and impact of degree<br>threshold vertex-cut performance                                                                                                                                                                    |

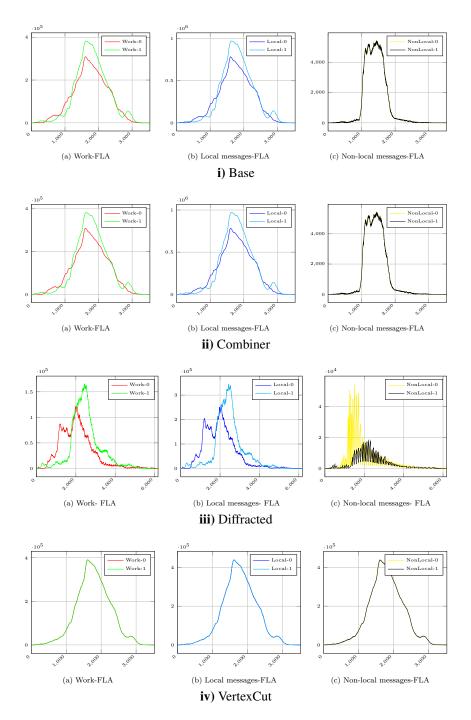

|      | Performance metrics for SSSP on two K40s for FLA road input.<br>The time-step is along the x-axis, and the size of the data structure<br>(work queue - left, local messages - center, and non-local messages<br>- right) are shown along the y-axis                                                                                                    |

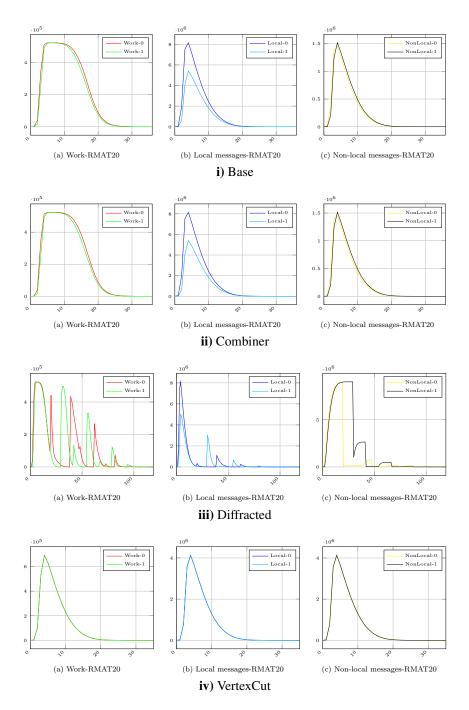

| 4.19 | Performance metrics for SSSP on two K40s for RMAT20 input.<br>The time-step is along the x-axis, and the size of the data structure<br>(work queue - left, local messages - center, and non-local messages<br>- right) are shown along the y-axis                                                                                                      |

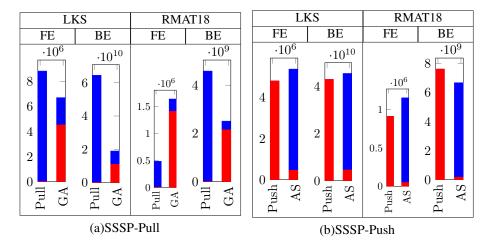

| 5.1  | SSSP front-end and back-end stalls for pull and push versions on scale-free and road network inputs. The bars for GA and AS shows the breakdown of metric for the two phases using different colors. 121                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2  | A simple gather-apply implementation for Single Source Shortest<br>Path                                                                                                                                                                                             |

| 5.3  | An optimized implementation of Single Source Shortest Path where<br>some computation is performed in the gather implementation re-<br>ducing the overall traffic to the apply                                                                                       |

| 5.4  | Single Source Shortest Path topology-driven apply-scatter algo-<br>rithm                                                                                                                                                                                            |

| 5.5  | Single Source Shortest Path work-list driven apply-scatter algorithm. 130                                                                                                                                                                                           |

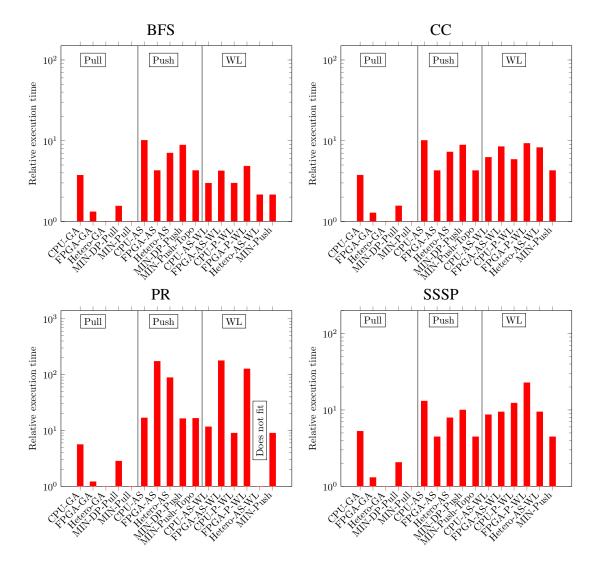

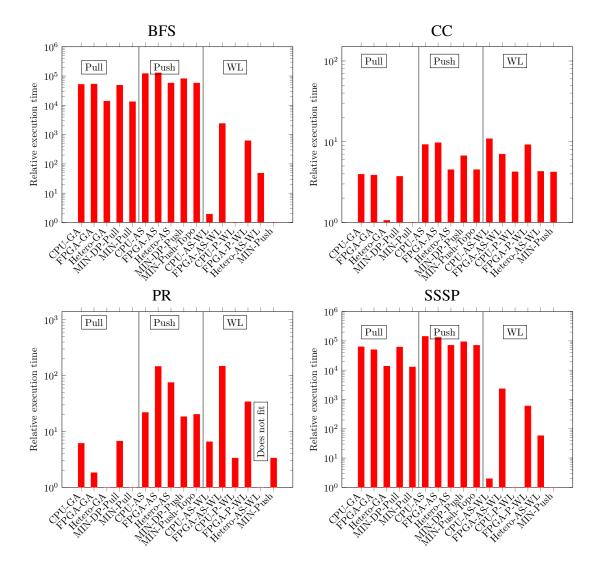

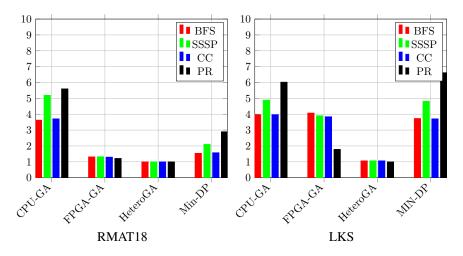

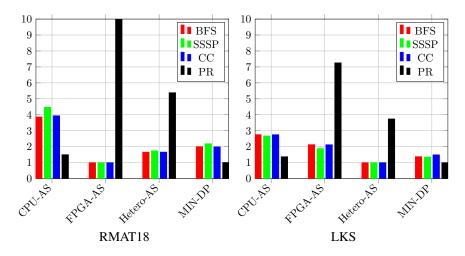

| 5.6  | Geometric means of relative execution time for all variants of dif-<br>ferent applications on RMAT networks. The fastest variant is at 1.<br>The logic synthesized for Hetero-AS-WL variant for PR did not fit<br>the area, hence was not executed. Lower is better |

| 5.7  | Geometric means of relative execution time for all variants of dif-<br>ferent applications on ROAD networks. The fastest variant is at 1.<br>The logic synthesized for Hetero-AS-WL variant for PR did not fit<br>the area, hence was not executed. Lower is better |

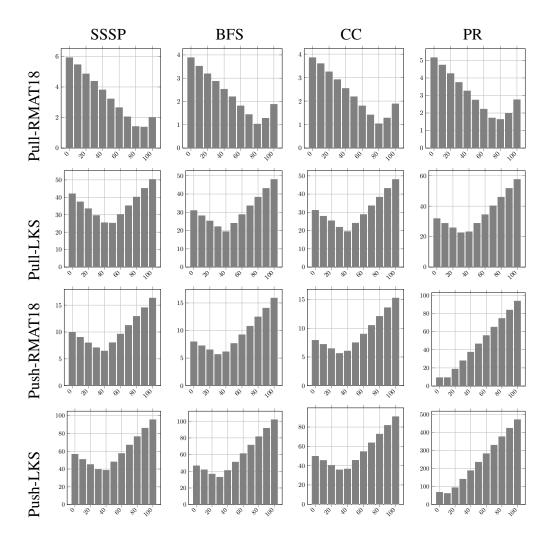

| 5.8  | Absolute runtime for different edge-distribution of the graph on a heterogeneous system. $x$ -axis shows the percentage of edges processed on the FPGA and $y$ -axis shows the absolute execution time. 138                                                         |

| 5.9  | Relative execution time for different configurations of gather and apply relative to the best implementation, lower is better                                                                                                                                       |

| 5.10 | Relative execution time for different configurations of apply and scatter relative to the best implementation, lower is better 141                                                                                                                                  |

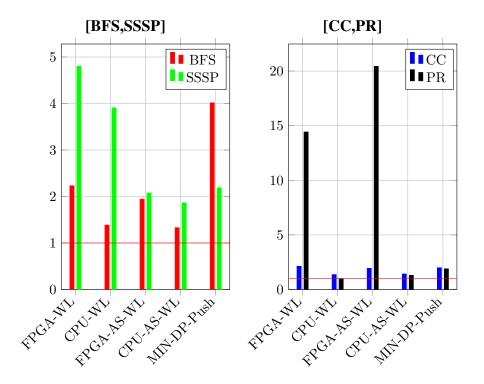

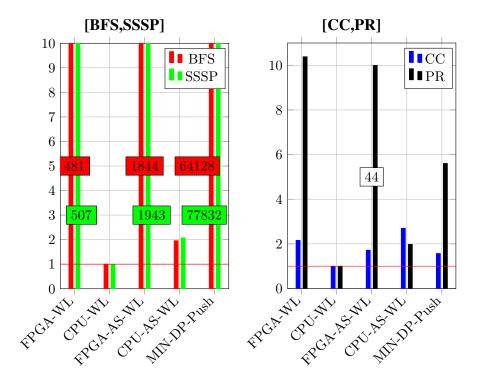

| 5.11 | Relative execution time for different configurations of apply and scatter relative to the best implementation on RMAT18, lower is better. The <i>red</i> horizontal line indicates 1                                                                                |

| 5.12 | Relative execution time for different configurations of apply and scatter relative to the best implementation on LKS, lower is better. The <i>red</i> horizontal line indicates 1                                                                                   |

## Chapter 1

## Introduction

Heterogeneous hardware is emerging as a key direction taken by industry to satisfy expectations of continuous improvement in performance, especially in the datacenter. Traditionally, large-scale deployments of computers were used to execute scientific and financial applications, since these applications required a lot of computational power. In the last decade, applications from new problem domains like machine learning and graph analytics have also become major consumers of cycles in datacenters.

Scaling these diverse applications requires developing new hardware platforms that go beyond traditional latency-optimized cores, which have been shown to be limited by physical design constraints [Beamer et al., 2015, Ozdal et al., 2016, Ham et al., 2016]. Programming these next-generation platforms will require new abstractions as well as revamped tool-chains to support these abstractions efficiently on hardware platforms. While traditionally, a single ISA and architecture design made the transition between platforms very smooth, the transition from homogeneous parallelism to heterogeneous parallelism presents a set of interesting challenges. The trade-off between software and hardware complexity is one of the key challenges - should programmers have to learn new abstractions to express their algorithms efficiently, or should hardware architects develop hardware that implements existing abstractions more efficiently?

In this dissertation, we explore the execution of irregular programs on heterogeneous systems. Irregular programs capture a large class of problems that are not amenable to compiler optimizations since in these applications, most of the optimization opportunities are available only during execution. Our work shows that while existing programming constructs can be used to efficiently utilize heterogeneous hardware without having programmer effort spent in porting the applications across different hardware platforms, opportunities for further improvement are available if these abstractions are expanded to benefit from the diversity in a heterogeneous system.

## **1.1 Contributions**

This dissertation explores efficient implementation of irregular programs on heterogeneous systems and proposes techniques across the software stack necessary to achieve that goal. Specifically, we highlight contributions in three areas.

- 1. *Compilers:* These assist in porting applications across devices. While vendors do provide APIs for programming accelerators, programmers have to learn a new API to port applications for accelerators. We show that a compiler can transform existing applications to target these accelerators efficiently.

- 2. *Runtime systems:* These are necessary to exploit information available only during execution. In a heterogeneous system, the runtime is responsible for

load balancing, communication management and synchronization across the different devices.

3. *Programming abstractions:* The current range of programming models designed for accelerators rely on the *offload* model in which a master processor off-loads computations to the accelerator and obtains the result. We show that this model is inadequate, especially for more diverse accelerators such as the FPGA, and propose new abstractions.

## 1.2 Outline

The outline of the rest of this dissertation is as follows. We first present some background for the work, covering the hardware and software aspects needed to understand the dissertation. In Chapter 3, we describe a set of compiler and runtime techniques that assist in executing irregular applications on a heterogeneous system composed of a commodity CPU and an integrated GPU. The key challenge addressed here is to reduce the overhead of dynamic load balancing between the heterogeneous processors in such a system. In Chapter 4, we focus on discrete GPUs that provide more computational capabilities at the expense of increased communication latencies and complexity. We explore and present guidelines for implementing efficient synchronization strategies necessary to execute graph applications on discrete GPUs. We also explore heterogeneous execution of graph applications for multi-GPU systems in which optimizing for communication becomes a key challenge in the face of heterogeneity. In Chapter 5, we explore a system composed of an FPGA and a CPU, which offers increased heterogeneity, and hence presents a different set of opportunities to optimize graph applications. We present a novel strategy of executing graph applications on such heterogeneous systems which addresses CPU performance limitations by offloading some work to the FPGA.

We discuss related work in Chapter 6, present some directions for future work in Chapter 7, and conclude in Chapter 8.

## Chapter 2

## Background

In this chapter, we present some background to put the dissertation into context. We first briefly describe the motivation for heterogeneous hardware, and describe some heterogeneous platforms available today. Next, we describe irregular applications which is the domain of applications addressed in this dissertation.

## 2.1 Heterogeneous Systems

There are two factors that have led to a continuous improvement in processor performance over the past two decades - *Moore's Law* and *Dennard's scaling*. Moore's law [Moore et al., 1998] is the observation that the number of of transistors per unit area doubles every 2 years. Equivalently, this can be phrased as shrinking of the transistor sizes - every 2 years, the size of a transistor shrinks to half. Dennard's scaling [Dennard et al., 1974], describes the power requirements of transistors decreases as the size decreases. This roughly translates to a constant power per unit area. However, Dennard's scaling does not take into account power leakage which becomes significant when transistor sizes become small enough. This new scenario, where Dennard's scaling does not apply, but Moore's law does, has led to a different set of challenges for hardware designers. Fundamentally, this means that although

more transistors can be placed into the same area, not all of these can be powered simultaneously due to power and thermal constraints.

Traditionally, these transistors were used to speed up serial processing of a program by different techniques such as pipelining, out-of-order execution, and vectorization. However, the limits of Dennard's scaling prevent future progress along those lines. The alternate direction adopted by the industry has been to turn to parallelism. Instead of accelerating the execution of a single stream of instructions, the hardware provides more throughput by enabling the execution of multiple streams of instructions, possibly at a lower rate.

The simplest strategy to utilize parallelism in a multi-processor is to replicate cores, and add a coordination network. While this approach is simple, an alternative is to use the extra transistors to provide heterogeneous capabilities. We present several different designs next, some of which are used to evaluate software implementations of graph applications in the remainder of the document. The three devices describe different levels of heterogeneity - from using the same ISA in the case of Sec. 2.1.1, to having different design points as demonstrated by Sec. 2.1.3.

#### 2.1.1 big.LITTLE

To satisfy the wide range of requirements presented by applications on a mobile platform, especially power constraints, ARM has developed heterogeneous systems composed of cores that execute the same ISA but differ in power/performance tradeoffs. The central idea is to provide small *LITTLE* cores that can provide power efficiency, and large *big* cores that run at higher clock rates and have greater

instruction throughput while consuming more power than the *LITTLE* cores. The operating system task scheduler [big.LITTLE, 2013] can move tasks from a *LIT*-*TLE* core to a *big* core or vice versa according to different dynamic schemes. As the cores share the same ISA, process migration is relatively simple. This design offers the simplest form of heterogeneity, which stems from architecture, contrasted with homogeneous cores behaving differently under dynamic voltage-frequency scaling (DVFS) [Macken et al., 1990].

#### 2.1.2 Intel Haswell

The Intel Haswell, also known as  $4^{th}$  generation Intel Processor, is a commodity x86 processor introduced in 2013. The high level organization of the processor is shown in Fig. 2.1. The processor also contains a generation 7.5 graphics processor. The HD – 4600 integrated GPU consists of a number of slices, each containing two sub-slices. Each sub-slice consists of 10 execution units (EU), and each EU can execute 7 threads. Each level of the organization has a different set of shared components, allowing for a scalable design for different market segments. The GPU also shares the physical memory with the CPU cores.

The GPUs and the CPUs share a last-level cache (LLC), with a cache line size of 64-bytes. Cache coherency is provided through the shared distributed last-level cache where each "core" (CPU core or a slice) gets a slice of the cache. This is done through a hash of the physical address. Both the integrated GPUs and CPU cores are connected by a bi-directional 32-byte wide ring interconnect. Some models are equipped with an on-die EDRAM which acts as a victim cache. A system

Figure 2.1: Intel Haswell (4<sup>th</sup> generation) processor architecture [Junkins, 2014].

agent, connected through the ring-interconnect, manages the communication between the CPU/GPU with the memory or other devices.

This system provides a middle ground for heterogeneity, providing a CPU and an integrated GPU which can be used to accelerate graphics workloads at a modest energy budget.

#### 2.1.3 Terasic DE1-SoC

The Terasic DE1-SoC is a system-on-chip with a dual core ARM Cortex-A9 and a Altera Cyclone-V FPGA. The high-level organization of the architecture is given in Fig. 2.2. The MPU subsystem consists of the Cortex-A9 CPU as well as a L2 cache and an accelerator coherency port (ACP) IP mapper which is responsible for coherency with accelerators. The Cortex-A9 has a snoop-control unit (SCU), which snoops for data-accesses to physical addresses shared with the FPGA. Co-

**Figure 2.2:** Organization of a Cyclone-V SoC from Altera. The DE1-SoC from Terasic is an instance of this SoC.

herency is managed by mapping a window of physical memory to be shared between the CPU and the FPGA. The FPGA fabric communicates with the MPU through a number of bridges which enable bi-directional transfers. The FPGA also has a direct path to the memory subsystems through the SDRAM controller subsystem that bypasses the caches and the L3-controller.

This system provides another extreme design point on the heterogeneous spectrum. The accelerator has a fundamentally different design compared to the CPU, while still providing the ability of general workloads to be executed on the accelerator.

## 2.2 Irregular Applications

To understand the sources of irregularity and what features distinguish an *irregular* application from a regular one, we start with a simple example of adding two arrays. In a imperative language such as C++, the procedure involves going over the two arrays, and adding the two corresponding elements while storing the result at the current location indexed by a loop counter. This is a fairly simple application, and modern processors excel at this template as it has a very predictable behavior, both in terms of what instructions to execute as well as what data to access.

#### 2.2.1 Parallelism

We first consider a simple program that adds two arrays and stores the result in a new array. The first snippet in Fig. 2.3 illustrates the example where two arrays, *arr\_a* and *arr\_b*, each containing *num\_elements* items, are added and the result is stored in the *result* array. A processor will go over all the entries in order, reading them from both arrays, computing and writing the result into the destination array's corresponding index. Since the addition of individual entries is independent of one another, they can be performed out of order. A modern processor is equipped with a hardware prefetcher, which can detect simple memory access patterns and prefetch addresses before they are accessed by an instruction. In this case, it will detect that consecutive locations of arrays *arr\_a* and *arr\_b* are being read and *result* being written.

On a multi-core system, which is equipped with multiple processors, the uti-

```

///Sample 1

1

for(int i=0; i< num_elements; ++i) {</pre>

2

result[i] = arr_a[i] + arr_b[i];

3

4

///Sample 2

5

6

for(int i=0; i< num_elements; ++i) {</pre>

result[i] = arr_a[i] + arr_b[index[i]];

7

8

9

10

///Sample 3

for(int i=0; i<num_elements;++i){</pre>

11

12

result[index[i]] = arr_a[i] + arr_b[i];

13

```

**Figure 2.3:** Adding two array elements. The first snippet add two arrays sequentially, the second one performs an indirect read, while the third one performs an indirect write.

lization of all the processor requires more coordination. One of the simplest way of utilizing all the cores is to partition the workload between the cores. This is possible for simple computations such as our running example. If *num\_elements* is large enough, all the participating cores can work on their individual partitions. Here, too, the prefetchers on each core will be able to detect that each core is working on a sequence of memory locations and prefetch values from each array.

While the *Sample 1* code can be parallelized in a simple and efficient way, most applications do not have such simple patterns. As described later in more detail, most graph applications require accessing memory locations through an indirection array. This is shown in the code annotated *Sample 2* in Fig. 2.3. Here, the application is going over an array of elements, and each iteration adds two values, one from a sequential access of  $arr_a$ , and the other an indirect access of  $arr_b$  through *index*. In this case, a serial as well as a parallel execution will show poor locality in referencing  $arr_2$  as the accesses cannot be predicted by the prefetcher

```

///Sample 1

1

for(int i=0; i< num_elements; ++i) {</pre>

2

for(int j=0; j < WORK_SIZE; ++j) {</pre>

3

4

//do work

5

}

6

}

///Sample 2

7

for(int i=0; i< num_elements; ++i) {</pre>

8

for(int j=0; j<work_size[i]; ++j){</pre>

9

10

//do work

11

}

12

}

```

Figure 2.4: Control flow irregularity.

and performance suffers. Another source of access irregularity is having irregular writes as shown in *Sample\_3* in Fig. 2.3. Here, *index* array is used to access the location where the result of the addition will be placed.

Just as we have described memory access irregularity above, the control flow of an application can also exhibit irregularity. To observe this, we consider a derivative of the sample codes in the Fig. 2.3. The first code sample in Fig. 2.4 shows a nested loop where the outer loop iterates over *num\_elements* items, and for each iteration, performs *WORK\_SIZE* inner loop iterations. Assuming that the body of the inner loop has a fixed amount of work, if the value of *WORK\_SIZE* is known at compile time, the compiler can perform certain optimizations such as unrolling to avoid the inner loop from requiring a conditional statement. If *WORK\_SIZE* is not known at compile time, these optimizations cannot be performed.

When executing the code in *sample\_1* of Fig. 2.4 on a parallel system, the scheduler can divide the *num\_elements* evenly among the different processors. This balances the load across the different processors since the work performed by each inner loop iteration is the same, even if it is not known at compile time. This can

be shown by the second code sample in Fig. 2.4. Here, each inner loop performs a different amount of iterations, which is known only at runtime through a *work\_size* array. This poses two challenges. *First*, the inner loop cannot be optimized by the compiler as described above. *Second*, load balancing across multiple processors becomes difficult since the different inner loop iterations have different amount of work.

For the discussion, we have ignored data-races between the concurrent threads executing the kernel. If the array *index* is not a permutation or contains duplicates, concurrent threads may access the same data. In the case of *Sample\_2*, multiple threads maybe reading the same element in *arr\_b*, which constitutes a benign race if the element accessed is less than the machine word. However, the code in *Sample\_3* results in concurrent threads writing to the same locations if they update the same entry in *result* array. A data race is used to refer to situations where multiple threads concurrently access the same location and at least one of the accesses is a write. This require some form of *synchronization* between the concurrent updates.

There are many solutions to synchronize concurrent access to shared data such as transactional memory (hardware [Herlihy and Moss, 1993] and software [Shavit and Touitou, 1995]), mutual exclusion [Dijkstra, 1965] through locks, and inspectorexecutor [Saltz et al., 1997].

We have described two of the characteristics of an *irregular* applications - memory access irregularity and control-flow irregularity. Addressing these two behaviors efficiently on modern systems is the key to irregular applications.

**Figure 2.5:** A graph colored to represent the different dynamic components during execution. *Red* nodes indicate *active elements* – nodes where a computation needs to be performed, and the shaded region around each active element denote the *neighborhood* of each activity – sets of nodes and edges that are accessed during the execution of the activity.

## 2.3 Graph Applications

Graphs are a convenient way of representing irregular computations since they allow the representation of arbitrary data structures as well as capture arbitrary relationships through edges. Many irregular applications are expressed using maps and the emergence of large scale social data has helped highlight the need for schema-less representations - which graphs excel at. This prevalence of graphs in modern applications makes it worthwhile to spend some time on characterizing key components of graphs and potentially categorizing the graph instances into sub-group which can then be targeted individually for optimization.

A graph can be described as a set of nodes V and a set of edges E, where each end-point of an edge is a node in the graph. The set of nodes and edges collectively encapsulate the *topology* or structure of the graph - what the graph looks like. There may be application specific data labels associated with the nodes and the edges. For instance, the nodes may represent individuals on a social network and the edges may represent interactions between the individuals.

Given a graph G(V, E) and the data labels  $D_V, D_E$ , a graph application is a program that performs some computation over the graph and generates new label(s) for the nodes or the edges or summarizes the graph. For instance, in a *Single Source Shortest Path*(SSSP) application, the nodes may represent cities and the edges represent the length of the roads between them. The goal of the computation is to find the length of the shortest path from a specific node or city (*source*) to every other node. The data labels on the node are all initialized to *infinity* except for the source which is set to 0. While there are many different algorithms for computing SSSP, there is one key operation common to all – *if a shorter path is available for a city, the distance label of that city should be updated*. If no such update exists, the computation has terminated, and each node (city) has its shortest distance as its label.

A graph application can be specified through two key components - *operator* and *schedule*. The *operator* defines what computation needs to be performed, whereas the *schedule* defines when and where the computation needs to be performed.

#### 2.3.1 Operator

We refer to this computation as the *operator*. An operator can be applied to different components of a graph - nodes, edges or sub-graphs. These are the *active elements* of the application and define what component of the graph the operator is applied to. For SSSP, the active elements are nodes. An operator applied to an active element may access elements in the graph besides the active element itself. For instance, in SSSP, an operator will scan the adjacent nodes of a node to check if a shorter path is available. The region of the graph accessed by an activity constitutes the neighborhood of the activity and may span beyond the immediate neighbors.

One dimension along which an operator can be classified is how the operator updates the graph. A *morph* computation changes the structure of the graph by adding or removing nodes and edges. Most graph analytics applications only update the labels on the nodes and edges of the graph, and do not modify the structure of the graph by adding/removing nodes and edges. Furthermore, the operator for these applications only accesses directly adjacent to the active elements. These operators, which access direct neighbors and do not modify the structure of the graph are also called *local computations*.

A local computation operator can be further classified according to the accesses it performs on the graph. If the operator reads from multiple nodes and only updates the label of the active node, it is known as a *pull* operator as it pulls updates from nodes adjacent to the active element. Conversely, a *push* operator writes to the nodes adjacent to the active element. Note that some algorithms may fall in both categories as they have a mixture of the characteristics of both operator styles.

Fig. 2.5 shows the key concepts in a graph application. The graph shown has circular nodes connected by edges. At any point during the execution, the operator may be applied to many of the active elements. In the figure, nodes circles colored *red* are candidates for execution. For each candidate, the shaded regions represents the neighborhood of the activity. As described earlier, the neighborhood of an activity is not necessarily adjacent to the active element.

#### 2.3.2 Schedules

Given an operator, we can repeatedly apply it to all graph nodes until no nodes changes its label. For instance, in SSSP, we can repeatedly scan the nodes to see if a shorter path is available. This algorithm, also known as *Bellman-Ford*, computes the shortest path from a specified source in O(|V||E|) steps. These algorithms are called *topology-driven* algorithms, as the topology of the graph drives the computations. While these are simple to implement, for many algorithms a topology-driven algorithm is very inefficient. Consider SSSP where initially all the nodes are at a distance *infinity*, and the source node is initialized to be at distance *zero*. For a topology-driven schedule, all the nodes execute the operator, but only a small subset of the nodes adjacent to the source node are updated. In the next round, nodes adjacent to those updated in the first step will be updated. This process will repeat until all the nodes have settled on their final version or some other termination criteria is reached (such as the maximum number of operator executions). For many graph applications, the fraction of nodes updated in each round is very small - leading to a large fraction of wasted work. An alternate is to track the active elements and execute operators only at sites that potentially contain updates to be propagated. As described above, for SSSP, if the distance of a node is updated as the result of the application of an operator, it needs to propagate those updates to nodes adjacent to it - hence it becomes *active*. Initially, only the *source* is active, and the result of applying the operator to the source will activate adjacent nodes that update their distances. This reduces the wasted work significantly at the expense of tracking the active elements.

Another key property described by the schedule is whether the operator is *ordered* or not. Given a set of active elements, an ordered operator defines a strict order in which the active elements are to be executed. *Dijkstra's* algorithm is an ordered algorithm for SSSP where the active element with the least distance is to be executed first. This *ordered*, *data-driven* algorithm is the most work-efficient algorithm for SSSP. The Bellman-Ford algorithm for SSSP, as described above, is an example of an *unordered* algorithm as the nodes will be updated to their correct distance even if they are not performed in a specific order. However, it is a very inefficient algorithm.

## **2.4 Implementation Issues**

In this section we briefly describe the different issues relevant to implementing graph algorithms. First, we describe a data structure to represent graphs. Next we describe different implementation strategies for implementing graph algorithms using this data structure.

We use Single Source Shortest Path (SSSP) to illustrate the issues that arise

in implementing graph analytics algorithms. In the SSSP application, a directed graph represents a collection of nodes which are connected through some weighted edges. Each node maintains a label *dist* representing its distance from a start node, initialized to *infinity*. The goal of the algorithm is to compute the shortest distance of every node from a given start node. This can be achieved through different algorithms as described in the Sec. 2.4.2 and Sec. 2.4.3.

### 2.4.1 Graph representation

One of the challenges of implementing a graph application is the choice of representation. While the node or edge labels can be represented by arrays indexed by the node or edge ID, the topology of the graph can be specialized. We can start with a naive adjacency matrix representation where we store the topology of the graph in a boolean matrix M of dimension  $|V| \times |V|$ . A node a is adjacent to b iff the entry M[a][b] is *true*. While this representation provides efficient access to the adjacency information, it can waste memory for sparse graph. Most real world graphs are sparse, meaning  $|E| << |V|^2$ . This means that a large fraction of the adjacency matrix will be *false*. If the operator has to go over the adjacent nodes of an active node, it has to scan the entire row of |V| entries for any *true* entries. This results in not only wasted memory but also wasted computation.

An alternate representation trades the simplicity of an adjacency matrix for efficiency in both memory and computation. The *compressed sparse row*(CSR) representation packs all the adjacency information of each node contiguously. This compression not only reduces the memory required to store the topology of the

graph but also makes it more efficient to traverse the adjacent nodes of an active element. A graph and its CSR representation are shown in Fig. 2.6. In the CSR representation, for a graph G(V, E), where V is the set of nodes, and E is the set of edges, each node is given a unique number between 1 and |V|. The representation uses four arrays, whose role is described below.

- *node-data*: an array of size |V|, indexed by node number, that contains the label of each node.

- *indices*: an array of size |V| + 1 used to access the edges connected to a node.

The elements between *indices*[n] and *indices*[n + 1] 1 in the *neighbors* and *edge-data* arrays below contain information about the edges connected to node n.

- *neighbors*: an array of size |E| that stores the IDs of the out-neighbors of each node.

- *edge-data*: an array of size |E| that stores the data on edges.

Edge or node labels can be omitted as necessary for applications; for example, Page-Rank does not require labels associated with edges. An undirected graph can be represented by storing edges in both directions. The pull-style SSSP algorithm needs the transpose of the hyper-link graph since each node needs to access fields in nodes that point to it.

While many other graph representations are good candidates for different algorithms and devices, a single representation is necessary, especially if the graph

**Figure 2.6:** A directed graph and its CSR representation. Node **e** does not have any outgoing edges, so the indices entries for its edges point to the end of neighbors array.

is to be loaded from disk. The work in this dissertation assumes that the graph is represented in a CSR representation, unless otherwise specified.

#### 2.4.2 Pull Implementations

We first describe a pull algorithm for computing the single source shortest path for a graph. Fig. 2.9 shows a sequential implementation of SSSP using the CSR representation. Each node has the fields dist that store the distance of the node from the start node.

The algorithm operates in rounds. In each round, every node n is visited, its incoming neighbors are scanned to determine if a shorter distance is available by summing the distance of the incoming neighbor and the weight of the edge connecting n to it. If a shorter distance is available, the label on n is updated to the shorter distance. This is known as the *Bellman-Ford* algorithm for Single Source Shortest Path, and shown in Fig. 2.7. This algorithm is a *topology-driven algorithm* because each round visits all the nodes, and the computation at each node is said to

```

void sssp_pull(Graph g) {

1

for (Node n : g.nodes()) {

2

3

int min_dist=INT_MAX;

for(Edge e : n.in_edges()) {

4

5

min_dist= min(e.source.dist + e.weight, min_dist);

6

n.dist = min(n.dist, min_dist);

7

8

}

9

}

```

**Figure 2.8:** A directed graph and its CSR representation. Node f does not have any outgoing edges, so the indices entries for its edges point to the end of neighbors array.

be a *pull-style operator* because the label at that node is updated by reading labels from the immediate neighbors.

There are four key memory accesses in this implementation.

- Line 3 Accesses the data of the node currently being processed. This is a sequential access since nodes are accessed in sequence by the outer loop.

- Line 5 Accesses the starting and ending locations of edges for the current node. This is also a sequential access since the indices array stores endpoints sequentially.

```

void sssp_pull(Graph &g){

1

for(int i=0; i<g.n_nodes; ++i) {</pre>

2

3

NodeData & src = g.node_data[i];

int min_dist=INT_MAX;

4

for(int e=g.indices[i];e!=g.indices[i+1]; ++e) {

5

int dst_id = g.neighbors[e];

6

int weight = g.edge_data[e];

7

NodeData & dst = g.node_data[dst_id];

8

9

min_dist = min(min_dist, dst.dist + weight);

10

}//end for-edges

11

src.dist = min(src.dist, min_dist);

12

}//end for-nodes

13 }//end sssp

```

- Line 6 Accesses the destination node of the edge currently being processed. This too is a sequential access since the neighbor array is accessed sequentially via e.

- Line 7 Accesses the data associated with the destination of the edge currently being processed. This is an irregular access since the destination of the edge can be any node.

To get good performance for graph applications such as Single Source Shortest Path, each of these accesses must be performed efficiently. Implementations of the other graph algorithms are similar, except that the computation performed at nodes is different. For BFS for example, the labels  $v_1, ..., v_i$  of the neighbors are read, and the label of the node is set to the minimum of its current label and the values of  $v_1+1, ..., v_i+1$ .

#### **2.4.3** Push Implementations

The algorithm described in Fig. 2.7 can be classified as a *pull*-algorithm. In such a graph algorithm, each node goes over its neighbors and pulls updates from them. These are relatively simpler to implement as there is only one writer per node. This obviates the need for synchronizations.Furthermore, these algorithms can be implemented efficiently in a bulk synchronous parallel manner on modern architectures.

The drawback of pull-style algorithms is that updates in the graph are not tracked - every node has to check its neighbors for any updates that might lead to an update in the node itself. Most graph algorithms such as *Breadth First Search* (BFS) and *Connected Components* converge when no node modifies its label in a give round. This can lead to a large waste in computation as each node scans its neighbors, and does not find any updates, even if there is only one node in the graph that was updated in the round. The extreme example is performing BFS on a linked list. Only one node is updated in each round, but all the node have to be scanned in every round.

An alternate implementation style is the *push*-style algorithm. Here, each node pushes updates to its neighbors. In the basic topology-driven implementation, all the node are repeatedly processed, and each node will send its update to its outgoing neighbors. Fig. 2.10 shows an implementation of SSSP using a push algorithm. The graph is loaded with the source node initialized to zero. Next, *sssp\_push* is repeatedly applied to the graph. If any node is updated in a call to *sssp\_push*, the node is updated, and a boolean flag *updated* is set to true, to indicate

```

1 bool updated = false;

2 void sssp_push(Graph g) {

3

updated = false;

for(Node n : g.nodes()){

4

for(Edge e : n.out_edges()) {

5

new_dist = n.dist+e.wt;

6

if(e.destination.dist>new_dist) {

7

e.destination.dist= new_dist;

8

9

updated=true;

10

}//end if

}//end for-e

11

}//end for-n

12

13 }//end sssp

14 . . .

15 Graph g(...);//load graph

16 do{}

sssp_push(g);

17

18 }while(updated);

```

Figure 2.10: Single Source Shortest Path topology-driven push algorithm.

that at least one node was updated in the graph, and the changes will need to be updated further.

At first, this seems like a very inefficient implementation. There can be concurrent writes which requires synchronization between multiple writes to the same memory location (destination distance). For Fig. 2.10, the write in line 8 has to be execute atomically. However, we can observe that any update that needs to be propagated in the next rounds are those that set the *updated* flag to true. We can use this to track active node and only go over active node in every pass. Any node that had not been updated in the previous round has no new information that needs to be propagated to its neighbors. For instance, in SSSP, if the distance of a node has been lowered, it will be scheduled to push its distance to its outgoing neighbors in the next round. This is also known as a work-list driven or data-driven implementation since the data-values on the nodes and edges dictates which nodes are processed.

```

1 WorkList sssp_wl(Graph g, WorkList wl){

WorkList next_wl;

2

3

for(Node n : wl) {

for(Edge e : n.out_edges()) {

4

new_dist = n.dist+e.wt;

5

if(e.destination.dist>new_dist) {

6

e.destination.dist= new_dist;

7

next_wl.push_back(e.destination);

8

9

}//end if

10

}//end for-e

}//end for-n

11

12 }//end sssp

13 Graph g(...);//load graph

14 WorkList wl(...);//initialize

15 while(!wl.empty()) {

wl = sssp_wl(g,wl);

16

17 }

```

Figure 2.11: Single Source Shortest Path work-list driven push algorithm.

In contrast, a topology-driven algorithm has all the nodes nodes executed in every pass.

A data-driven implementation, as shown in Fig. 2.11 for SSSP, uses a worklist to track the active items. The graph is first loaded, and the distance of source node initialized to zero. The source node is also added to the work-list since it has updates that need to be propagated. Next, we call the *sssp\_wl* procedure which goes over all the nodes in the work-list, and adds nodes to the next work-list if their distances have been updated. This is repeated until no node is updated. These algorithms are more work-efficient since they do not touch the whole graph in every pass - unless it is required. The drawback of this approach is the extra synchronization required, not only from having multiple writes being performed to each node from its neighbors, but also maintaining the work-list where active nodes for the next round are maintained.

## 2.5 Abstractions

Given a graph algorithm specification as described above, we would like to program it to execute on an accelerator. A simple approach is to understand the native instruction set of the accelerator and to translate the algorithm specification to it. Clearly, this approach is not productive for application developers looking to port applications to these accelerators. Alternatively, high level abstractions can be used to express the graph algorithms at a higher level. This requires a compiler and runtime to support the translation and execution of the application on the accelerator.

### 2.5.1 CUDA

*Compute Unified Device Architecture(CUDA)* is a proprietary application programmer interface developed by Nvidia. The language is designed to make general purpose GPU (GPGPU) programming more accessible by extending C++ with certain constructs. CUDA provides support for executing kernels on the GPU which are specified in an augmented subset of C. This makes it very attractive for application developers experienced with structured programming as kernels require minor modifications. CUDA also provides a comprehensive set of functions for management, memory, and event management. A large number of libraries have been developed to support CUDA which has added to its popularity in many domains. One key drawback to using CUDA is vendor lock-in – only devices from Nvidia currently support it.

#### 2.5.2 OpenCL

In response to the growing popularity of CUDA, *Open Compute Language(OpenCL)* was developed by *Khronos group*, a consortium of companies. The OpenCL specification describes an API that different accelerators must support to obtain compliance. The original 1.0 of the standard was released in 2009. Similar to CUDA, OpenCL provides API for device, memory and event management. Programming in OpenCL is slightly more difficult compared to CUDA as the API is designed to support a larger range of devices. Currently, OpenCL is supported by a range of devices such as CPUs, GPUs, FPGAs, and DSPs.

# Chapter 3

# **Data-parallel execution with Integrated GPUs**<sup>1</sup>

Heterogeneous systems composed of integrated GPUs and multi-core CPUs are ubiquitous in commodity systems. In this chapter, we explore the efficient execution of irregular programs on such heterogeneous systems by first addressing the portability of existing applications to these platforms, and then describe runtime techniques to address load imbalance between the CPU and the GPU in a heterogeneous execution.

## 3.1 Introduction

Graphics processing units (GPUs) have become increasingly popular for accelerating general purpose computations. GPUs provide massive parallelism on a small energy budget and offer opportunities for significant energy savings and performance improvements compared to multi-core CPUs.

Integrated GPUs are manufactured onto the same die as the CPU, where they share resources like physical memory (and on Intel's integrated processors, the last-

<sup>&</sup>lt;sup>1</sup>Portions from this chapter have been published in peer-reviewed conferences. The Concord compiler was presented in [Barik et al., 2014]. The scheduling strategies described have been published in [Kaleem et al., 2014]. The first author was responsible for implementation and evaluation of graph applications as well as conception, design and evaluation of heterogeneous schedule.