### New Views for Stochastic Computing: From Time-Encoding to Deterministic Processing

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

M. Hassan Najafi

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Advisor: David J. Lilja

© M. Hassan Najafi 2018 ALL RIGHTS RESERVED

نىر نام ز ما و نىر نشار خواهد بود زىيىنى پىس چو نباشىم سار خواهد بود

ری بس که نباشی و جهار بخواهد بود زیستر پیش نبودیم و نبد همیج خلل

The world will long be, but of you and me No sign, no trace for anyone to see; The world lacked not a thing before we came, Nor will it miss us when we cease to be.

-KHAYYAAM

### Acknowledgements

First and foremost, I like to extend my sincere thanks to my advisor, Prof. David J. Lilja, for being such a wonderful mentor during my PhD. It has been a privilege to be mentored by him and my great honor to be his PhD student. He was full of encouragement and support and gave me great latitude in determining my own direction and pursuing my ideas. I learned many essential research skills from him and I appreciate his financial support which allowed me to devote all of my attention to my research.

I would like to thank the other members of my graduate committee, Prof. Marc Riedel, Prof. Kia Bazargan, and Prof. Pen-Chung Yew for not only agreeing to be on my committee but also for their valuable suggestions and feedback along the way. I like to give a big thanks to Marc and Kia for their help and input to my research. Many of the ideas of this research are derived from our weekly stochastic research group meeting with David, Marc, and Kia. I would also like to thank Shiva Jamali-Zavareh and Prof. Ramesh Harjani for their contribution to the time-based computing project, and Bingzhe Li and Rasoul Faraji for their contribution to the stochastic computing-based neural networks project.

Finally, I would like to thanks all my friends in Minneapolis. I have been fortunate to have made some wonderful friends during these four years. To Ali, Mohammad, Saeed, Arash, Amirreza, and Rasoul; I am very appreciative of the fun experiences shared with you guys as well as your support. You were my family here and I am blessed and thankful to have you as my friends.

This work was supported in part by National Science Foundation grant no. CCF-1408123 and CCF-1438286. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the NSF. The author also acknowledges the Graduate School at University of Minnesota for the funding support through the Doctoral Dissertation Fellowship.

# To My Parents and Brothers

For their endless love, support, and encouragement

#### Abstract

Stochastic computing (SC), a paradigm first introduced in the 1960s, has received considerable attention in recent years as a potential paradigm for emerging technologies and "post-CMOS" computing. Logical computation is performed on random bitstreams where the signal value is encoded by the probability of obtaining a one versus a zero. This unconventional representation of data offers some intriguing advantages over conventional weighted binary. Implementing complex functions with simple hardware (e.g., multiplication using a single AND gate), tolerating soft errors (i.e., bit flips), and progressive precision are the primary advantages of SC. The obvious disadvantage, however, is latency. A stochastic representation is exponentially longer than conventional binary radix. Long latencies translate into high energy consumption, often higher than that of their binary counterpart. Generating bit streams is also costly. Factoring in the cost of the bit-stream generators, the overall hardware cost of an SC implementation is often comparable to a conventional binary implementation.

This dissertation begins by proposing a highly unorthodox idea: performing computation with digital constructs on time-encoded analog signals. We introduce a new, energy-efficient, high-performance, and much less costly approach for SC using time-encoded pulse signals. We explore the design and implementation of arithmetic operations on time-encoded data and discuss the advantages, challenges, and potential applications. Experimental results on image processing applications show up to 99% performance speedup, 98% saving in energy dissipation, and 40% area reduction compared to prior stochastic implementations. We further introduce a low-cost approach for synthesizing sorting network circuits based on deterministic unary bit-streams. Synthesis results show more than 90% area and power savings compared to the costs of the conventional binary implementation. Time-based encoding of data is then exploited for fast and energy-efficient processing of data with the developed sorting circuits.

Poor progressive precision is the main challenge with the recently developed deterministic methods of SC. We propose a high-quality down-sampling method which significantly improves the processing time and the energy consumption of these deterministic methods by pseudo-randomizing bitstreams. We also propose two novel deterministic methods

of processing bitstreams by using low-discrepancy sequences. We further introduce a new advantage to SC paradigm-the skew tolerance of SC circuits. We exploit this advantage in developing polysynchronous clocking, a design strategy for optimizing the clock distribution network of SC systems. Finally, as the first study of its kind to the best of our knowledge, we rethink the memory system design for SC. We propose a seamless stochastic system, StochMem, which features analog memory to trade the energy and area overhead of data conversion for computation accuracy.

# Contents

| A  | ckno  | wledge  | ements                                     | i    |

|----|-------|---------|--------------------------------------------|------|

| D  | edica | tion    |                                            | ii   |

| A  | bstra | ıct     |                                            | iii  |

| Li | st of | Table   | S                                          | ix   |

| Li | st of | Figur   | es                                         | xi   |

| 1  | Intr  | roducti | ion                                        | 1    |

| 2  | Tin   | ne-Bas  | ed Computing with Stochastic Constructs    | 6    |

|    | 2.1   | Motiv   | ation                                      | 6    |

|    | 2.2   | PWM     | as the Stochastic Number Generator         | 9    |

|    | 2.3   | Stocha  | astic Systems with Time-Encoding Signals   | 12   |

|    |       | 2.3.1   | Stochastic Operations with PWM signals     | 12   |

|    |       | 2.3.2   | Multilevel Circuit PWM signals             | 25   |

|    | 2.4   | Exper   | imental Results                            | 26   |

|    |       | 2.4.1   | Case Study 1: Robert's cross edge detector | 29   |

|    |       | 2.4.2   | Case Study 2: Gamma Correction             | . 31 |

|    | 2.5   | Error   | Analysis                                   | 35   |

|    |       | 2.5.1   | Sources of Computational Error             | 35   |

|    |       | 2.5.2   | Noise Modeling                             | 38   |

|    | 2.6   | Applio  | cations                                    | 40   |

|   | 2.7  | Challe | enges                                       | . 41 |

|---|------|--------|---------------------------------------------|------|

|   |      | 2.7.1  | Analog Noise                                | . 41 |

|   |      | 2.7.2  | Resolution                                  | . 41 |

|   |      | 2.7.3  | Truncation                                  | 42   |

|   |      | 2.7.4  | Synchronization                             | 42   |

|   |      | 2.7.5  | Skew                                        | 42   |

|   |      | 2.7.6  | Rotation                                    | 43   |

|   |      | 2.7.7  | Sequential Circuits                         | 43   |

|   | 2.8  | Conclu | usion                                       | 43   |

| 3 | Low  | -Cost  | Sorting Network Circuits                    | 45   |

|   | 3.1  | Motiva | ation                                       | 45   |

|   | 3.2  | Backg  | round                                       | 47   |

|   |      | 3.2.1  | Sorting Networks                            | 47   |

|   |      | 3.2.2  | Unary processing                            | 48   |

|   | 3.3  | Comp   | lete Sort System                            | 50   |

|   |      | 3.3.1  | Conventional Design                         | 50   |

|   |      | 3.3.2  | Unary Design                                | . 51 |

|   |      | 3.3.3  | Design Evaluation                           | 52   |

|   | 3.4  | Highly | Efficient Median Filters                    | 56   |

|   |      | 3.4.1  | Circuit Design                              | 56   |

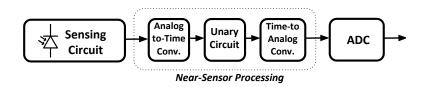

|   |      | 3.4.2  | Time-based unary design                     | 58   |

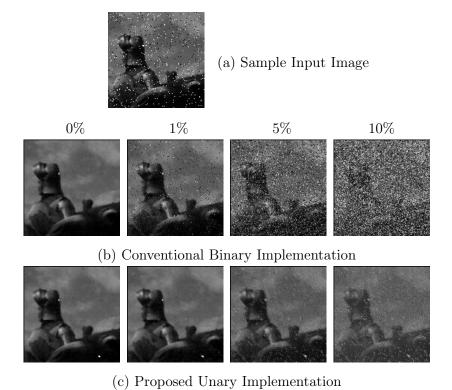

|   | 3.5  | Noise- | Tolerant Behavior                           | 62   |

|   | 3.6  | Summ   | ary                                         | 63   |

| 4 | Fast | t-Conv | verging Deterministic Bitstream Computing   | 65   |

|   | 4.1  | Motiva | ation                                       | 65   |

|   | 4.2  | Deterr | ministic Approaches to Stochastic Computing | 67   |

|   | 4.3  | Pseud  | o-Random Bitstreams for Deterministic SC    | 69   |

|   |      | 4.3.1  | Proposed Method                             | 69   |

|   |      | 4.3.2  | Evaluation                                  | 73   |

|   | 4.4  | Low-D  | Discrepancy Bistreams for Deterministic SC  | 78   |

|   |      | 111    | Low-Discrepancy Sequences in SC             | 78   |

|   |      | 4.4.2   | First Proposed Method                            |

|---|------|---------|--------------------------------------------------|

|   |      | 4.4.3   | Second Proposed Method                           |

|   |      | 4.4.4   | Accuracy Evaluation                              |

|   |      | 4.4.5   | Cost Comparison                                  |

|   | 4.5  | Scalab  | sility Evaluation                                |

|   | 4.6  | Summ    | ary                                              |

| 5 | Doly | zevneh  | ronous Stochastic Circuits 92                    |

| J | 5.1  |         | ation                                            |

|   | 5.2  |         | round                                            |

|   | 0.2  | 5.2.1   | Stochastic Operations                            |

|   |      | 5.2.1   | Stochastic Circuits                              |

|   | 5.3  | -       | rnchronous Clocking                              |

|   | 5.4  |         | rnchronous System Design: A Case Study           |

|   | 0.4  | 5.4.1   | Synchronous Design: Global CDN                   |

|   |      | 5.4.2   | Polysynchronous Design: Removing the CDN         |

|   |      | 5.4.3   | Polysynchronous Design: Relaxed CDN              |

|   | 5.5  |         | imental Setup                                    |

|   | 5.6  | -       | imental Results                                  |

|   | 5.0  | -       |                                                  |

|   |      | 5.6.1   |                                                  |

|   | F 7  | 5.6.2   | Performance Comparisons                          |

|   | 5.7  |         | Analysis                                         |

|   |      | 5.7.1   | Sources of Computational Errors                  |

|   |      | 5.7.2   | Metastability                                    |

|   | F 0  | 5.7.3   | Input to Output Synchronization                  |

|   | 5.8  |         | Tolerance of Polysynchronous Circuits            |

|   | 5.9  |         | ed Work and Discussion                           |

|   | 5.10 | Summ    | ary                                              |

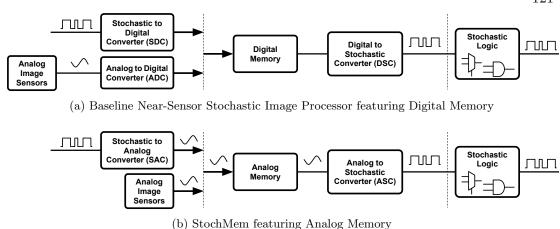

| 6 | Sear | mless 1 | Memory Design for SC 119                         |

|   | 6.1  | Motiva  | ation                                            |

|   | 6.2  | Towar   | d Seamless SC                                    |

|   |      | 6.2.1   | Baseline: Stochastic Logic + Conventional Memory |

|   |        | 6.2.2  | Stoch<br>Mem: Stochastic Logic + Analog Memory | 122 |

|---|--------|--------|------------------------------------------------|-----|

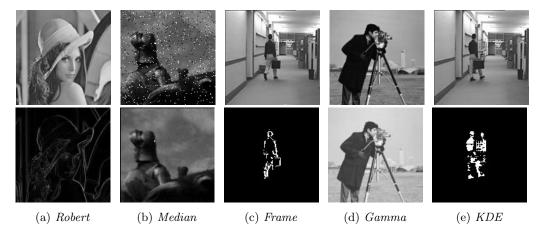

|   | 6.3    | Evalua | ation Setup                                    | 123 |

|   |        | 6.3.1  | System Design                                  | 123 |

|   |        | 6.3.2  | Stochastic Applications                        | 123 |

|   |        | 6.3.3  | Hardware Parameters                            | 124 |

|   | 6.4    | Evalua | ation                                          | 124 |

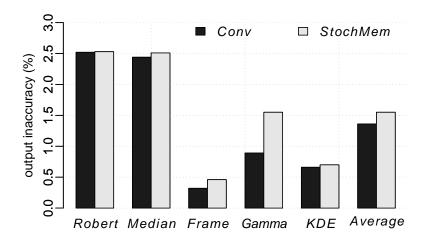

|   |        | 6.4.1  | Output Accuracy of StochMem                    | 125 |

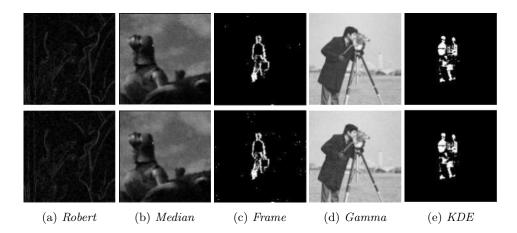

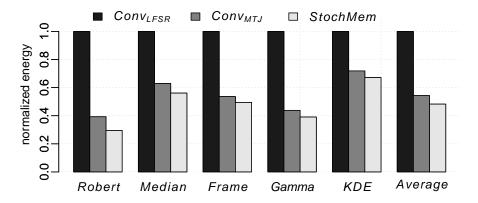

|   |        | 6.4.2  | Reduction in Energy Consumption                | 126 |

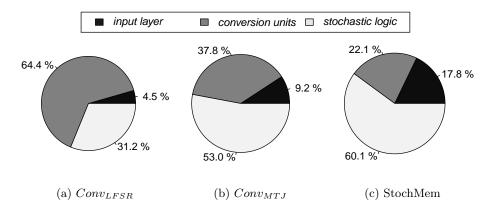

|   |        | 6.4.3  | Reduction in Area                              | 128 |

|   | 6.5    | Summ   | ary                                            | 130 |

| 7 | Con    | cludin | g Remarks                                      | 131 |

|   | 7.1    | Summa  | ary of Contributions                           | 131 |

|   | 7.2    | Future | e Directions                                   | 133 |

| R | eferei | nces   |                                                | 135 |

# List of Tables

| 2.1 | Area-Power comparison of different SNGs                                        | 10 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | Area, delay, power and energy comparison of the implemented circuits for       |    |

|     | the conventional binary, prior stochastic and the proposed PWM approach.       |    |

|     | For the prior stochastic approach, we ignore the cost of the ADC. Delay        |    |

|     | and power numbers are reported for the maximum working frequency               | 32 |

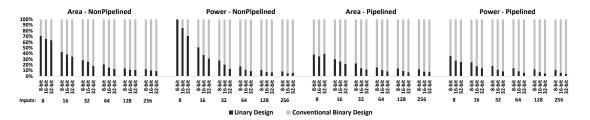

| 3.1 | Synthesis results of complete bitonic sort networks (Non-Pipelined)            | 53 |

| 3.2 | Synthesis results of complete bitonic sort networks (Pipelined)                | 54 |

| 3.3 | Synthesis results of the sorting network-based median filters for data-        |    |

|     | width=8                                                                        | 58 |

| 3.4 | Average error rate of processing the sample image using the time-based         |    |

|     | unary circuits                                                                 | 61 |

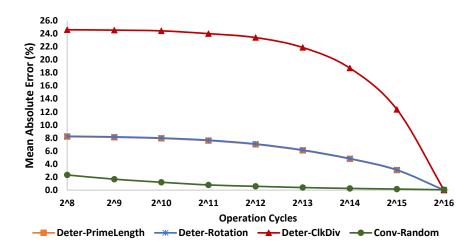

| 4.1 | Mean Absolute Error (%) comparison of the prior random and determin-           |    |

|     | istic approaches to stochastic computing and the proposed deterministic        |    |

|     | approaches based on pseudo-randomized streams when multiplying two             |    |

|     | 8-bit precision stochastic streams with different numbers of operation cycles. | 71 |

| 4.2 | Area $(um^2)$ , Power $(mW)$ (@ 1GHz), and Energy consumption $(pJ)$ of        |    |

|     | the Robert's cross stochastic circuit synthesized with the 8- and 16-bit       |    |

|     | conventional random approach, and also the prior structures and the            |    |

|     | proposed structures of the three deterministic approaches (Relatively          |    |

|     | Prime Lengths, Clock Division, and Rotation)                                   | 75 |

| 4.3 | Comparing different sources of generating numbers (3-bit precision) for        |    |

|     | stochastic stream generator                                                    | 80 |

| 4.4 | Mean Absolute Error (%) comparison of the prior approximate and deter-               |       |

|-----|--------------------------------------------------------------------------------------|-------|

|     | ministic approaches to SC and the proposed deterministic approach when               |       |

|     | multiplying two 8-bit precision stochastic streams with different numbers            |       |

|     | of operation cycles.                                                                 | 86    |

| 4.5 | Hardware area cost $(\mu m^2)$ of the bitstream generator for different data         |       |

|     | precision and number of inputs (N=Input Data Precision - i=Number of                 |       |

|     | Inputs)                                                                              | 86    |

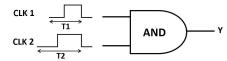

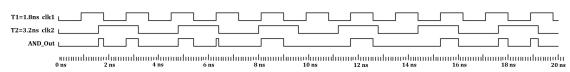

| 5.1 | Different observed lengths of high pulses at the output of the AND gate              |       |

|     | and the number of occurrences of each one for three pairs of clock periods           |       |

|     | when executing the multiplication operation for 1000 ns                              | 100   |

| 5.2 | The measured output of the MUX when three polysynchronous clocks                     |       |

|     | with distinct periods are connected to its inputs for 1000 ns                        | . 101 |

| 5.3 | Stochastic multiplication and scaled addition, using an AND gate and a               |       |

|     | $\operatorname{MUX},$ respectively, with inputs generated by unsynchronized SNGs. $$ | . 101 |

| 5.4 | Synthesis results for a single Robert's cross cell with and without a local          |       |

|     | clock generator                                                                      | 107   |

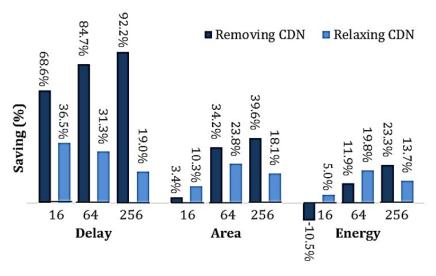

| 5.5 | Delay, area, power, and average error rate comparison of the implemented             |       |

|     | circuits for different approaches of synthesizing the CDN                            | 108   |

| 5.6 | The average error rate of the stochastic circuits for different soft error           |       |

|     | injection rates.                                                                     | 116   |

| 6.1 | Area and energy breakdown                                                            | 125   |

| 6.2 | Area in $um^2$                                                                       | 129   |

# List of Figures

| 1.1 | Stochastic Number Generator                                                 | 3  |

|-----|-----------------------------------------------------------------------------|----|

| 2.1 | PWM signals with different duty cycles. (a) $20\%$ duty cycle. (b) $50\%$   |    |

|     | duty cycle. (c) 80% duty cycle                                              | 8  |

| 2.2 | SNG proposed in [1] for vision chips                                        | 9  |

| 2.3 | A common analog PWM generator                                               | 9  |

| 2.4 | The design of our PWM generator. The duty cycle is determined by            |    |

|     | the current coming from the sensing circuit (a photodiode, or a voltage     |    |

|     | controlled current source, etc) and the Reset pulse defines the frequency   |    |

|     | of the PWM signal. Vref is a fixed reference voltage                        | 10 |

| 2.5 | The ENOB of the proposed PWM generator shown in Figure 2.4 when             |    |

|     | generating PWM signals with frequencies from $0.5$ to $3$ GHz. More detail  |    |

|     | on the noise modeling of the implemented PWM generator will be discussed    |    |

|     | in Section 2.5.2                                                            | 11 |

| 2.6 | Time-based computing with stochastic constructs. An ATC converts            |    |

|     | the sensed data to a time-encoded pulse signal. The converted signal is     |    |

|     | processed using the stochastic circuit, and the output is converted back to |    |

|     | a desired analog format using a TAC                                         | 12 |

| 2.7 | Discretizing a continuous PWM signal                                        | 14 |

| 2.8 | Average error rates when performing a multiplication operation using an     |    |

|     | AND gate for 1000 ns on 1000 sets of random input values when the inputs    |    |

|     | are represented using PWM signals. The period of the first input is set at  |    |

|     | 20 ns while the period of the second changes from 1 to 20 ns                | 15 |

| 2.9  | Example of multiplying two PWM signals using an AND gate. IN1                                                                                  |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | represents $0.5~(50\%$ duty cycle) with a period of $20~\mathrm{ns}$ , and IN2 represents                                                      |    |

|      | $0.6~(60\%~{\rm duty~cycle})$ with a period of 13 ns. The output signal from t=0                                                               |    |

|      | to 260 ns represents 0.30 (78 ns/260 ns= $3/10$ ), the expected value from                                                                     |    |

|      | multiplication of the inputs                                                                                                                   | 16 |

| 2.10 | Average error rate of multiplying 1000 pairs of random numbers represented                                                                     |    |

|      | by PWM signals when varying the operation time. The period of the                                                                              |    |

|      | PWM signals corresponding to the first and to the second number in each                                                                        |    |

|      | trial is 20 and 13 ns, respectively                                                                                                            | 17 |

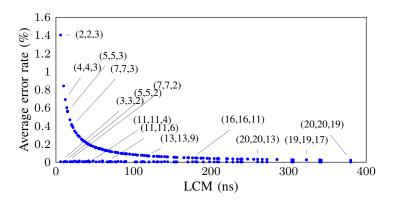

| 2.11 | The average error rate for multiplying 1000 pairs of random numbers                                                                            |    |

|      | represented by PWM signals when the period of the first and the second                                                                         |    |

|      | PWM signal are relatively prime integers in the interval [2, 20]. A lower                                                                      |    |

|      | average error rate in the figure means a higher ENOB in the computations.                                                                      | 18 |

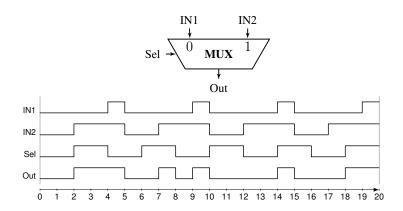

| 2.12 | Example of the scaled addition of two PWM signals using a MUX. IN1                                                                             |    |

|      | and IN2 represent $0.2$ and $0.6$ with a period of 5 ns, and Sel represents $0.5$                                                              |    |

|      | with a period of 4 ns. The output signal from $t=0$ to 20 ns represents                                                                        |    |

|      | $0.40~(8~\mathrm{ns}/20~\mathrm{ns}=4/10),$ the expected value from the scaled addition of                                                     |    |

|      | the inputs                                                                                                                                     | 19 |

| 2.13 | Average error rate of performing scaled addition on 1000 pairs of random                                                                       |    |

|      | numbers represented by PWM signals when the period of the first and the                                                                        |    |

|      | second PWM signal is the same but different and relatively prime with the                                                                      |    |

|      | period of the PWM select signal. The periods are selected from integers                                                                        |    |

|      | in [2, 20] interval                                                                                                                            | 20 |

| 2.14 | Examples of choosing an $\hat{a}\check{A}IJodd\hat{a}\check{A}\check{I}$ or an $\hat{a}\check{A}IJeven\hat{a}\check{A}\check{I}$ number as the |    |

|      | period of the MUXâĂŹs select signal. The input is a PWM signal with                                                                            |    |

|      | D=30%. Black (blue) lines are parts of the input signal that will be                                                                           |    |

|      | connected to the output of the MUX when the input is connected to the                                                                          |    |

|      | first (second) input.                                                                                                                          | 21 |

| 2.15 | Example of performing stochastic absolute value subtraction using an            |    |

|------|---------------------------------------------------------------------------------|----|

|      | XOR gate when two synchronized PWM signals are used as the inputs of            |    |

|      | the gate, one representing 0.5 (D = $50\%$ ) and the other 0.8 (D = $80\%$ ).   |    |

|      | Both PWM signals have a period of 20 ns. The output signal from $\mathbf{t}=0$  |    |

|      | to 20 ns represents 0.3, the expected value for $ IN1 - IN2 $                   | 22 |

| 2.16 | Performing minimum and maximum operations on two synchronized PWM               |    |

|      | signals: IN1 represents 0.3 and IN2 represents 0.7. Both PWM signals            |    |

|      | have a period of 10 ns                                                          | 23 |

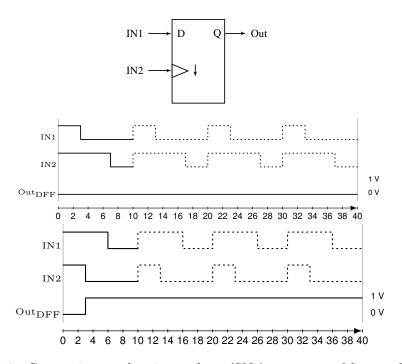

| 2.17 | Comparing stochastic numbers (SNs), represented by synchronized PWM             |    |

|      | signals, using a D-type flip-flop: (up) $IN1 < IN2$ , and thus $Out=0$ ; (down) |    |

|      | IN1 > IN2, and thus $Out=1$                                                     | 24 |

| 2.18 | Examples of multilevel stochastic circuits                                      | 26 |

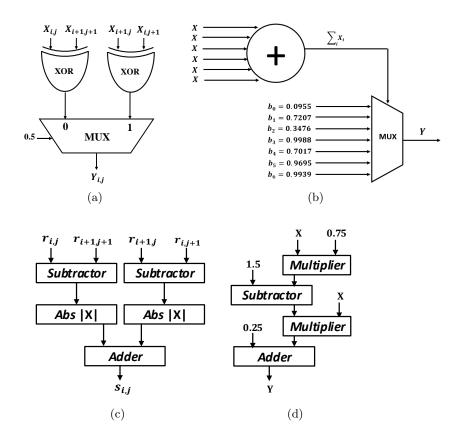

| 2.19 | Robert's cross edge detection algorithm a) core stochastic logic [1], c)        |    |

|      | conventional binary implementation. Gamma correction function b) core           |    |

|      | stochastic logic based on ReSC architecture [2], d) a conventional binary       |    |

|      | implementation [1]                                                              | 27 |

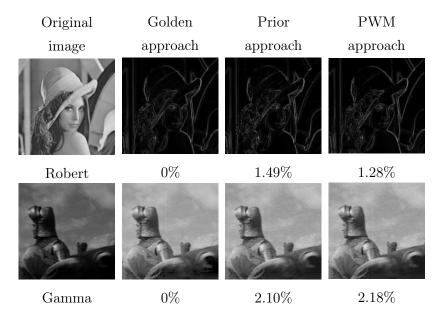

| 2.20 | Original $128 \times 128$ sample images and the outputs of processing the input |    |

|      | images using the "golden approach", the "prior approach", and the proposed      |    |

|      | PWM approach with the Robert's cross stochastic circuit (first row) and         |    |

|      | the Gamma correction stochastic circuit (second row)                            | 28 |

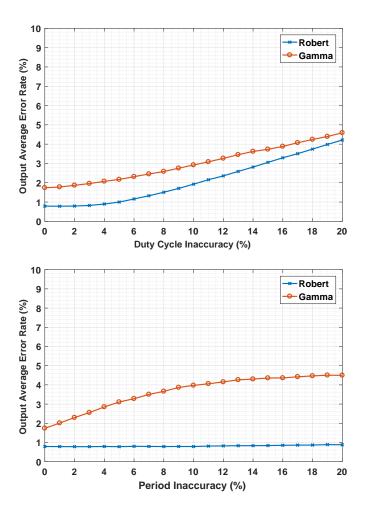

| 2.21 | Average error rate of the output images when processing the sample images       |    |

|      | using the proposed PWM-based approach for different rates of inaccuracy         |    |

|      | in the duty cycle (top) and in the period (bottom) of the PWM input             |    |

|      | signals. PWM signals are generated using an ideal PWM generator in              |    |

|      | HSPICE and the output signals are converted back to real values using an        |    |

|      | ideal integrator. Twenty trials were performed for each inaccuracy rate to      |    |

|      | ensure statistically significant results                                        | 37 |

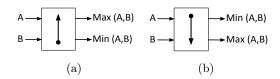

| 3.1  | The schematic symbol of a CAS block a) ascending b) descending                  | 47 |

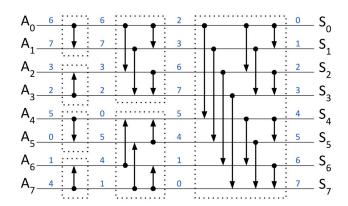

| 3.2  | The CAS network for an 8-input bitonic sorting [3]                              | 48 |

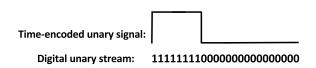

| 3.3  | Time-based vs. digital-stream unary representation                              | 49 |

| 3.4  | Example of performing maximum and minimum operations on unary                   |    |

|      | streams.                                                                        | 50 |

| 3.5  | Hardware implementation of a CAS block a) Conventional binary design            |    |

|------|---------------------------------------------------------------------------------|----|

|      | b) Unary design                                                                 | 51 |

| 3.6  | Unary stream generator                                                          | 52 |

| 3.7  | Normalized area and power ( $@50\mathrm{MHz}$ ) cost numbers reported for the   |    |

|      | non-pipelined and pipelined structures of the implemented complete sort         |    |

|      | networks                                                                        | 55 |

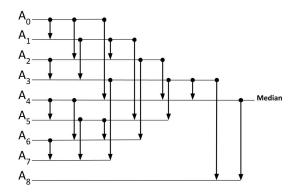

| 3.8  | The CAS network for a $3x3$ Median Filter made of $19$ CAS blocks [4]           | 57 |

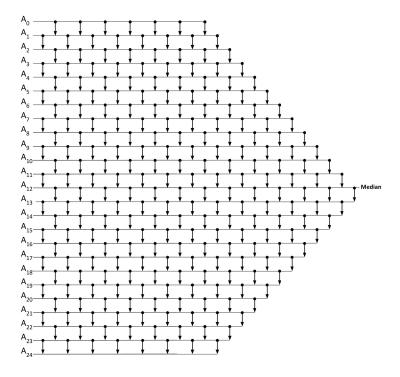

| 3.9  | The CAS network for a $5x5$ Median Filter made of $246$ CAS blocks [5]          | 57 |

| 3.10 | Near Sensor Processing with unary circuits                                      | 59 |

| 3.11 | (a) Sample input image, and comparison of the noise-tolerance capability        |    |

|      | of (b) the conventional binary vs. (c) the proposed unary implementation        |    |

|      | for the $3\times3$ median filtering circuit for different noise injection rates | 62 |

| 4.1  | Progressive Precision comparison of the conventional random stream-based        |    |

|      | SC with the unary stream-based deterministic approaches of SC when              |    |

|      | multiplying two 8-bit precision input values                                    | 67 |

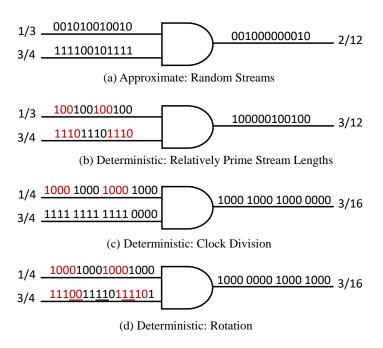

| 4.2  | Examples of performing stochastic multiplication: a) conventional approx-       |    |

|      | imate SC with random bitstreams (b)-(d) recently proposed deterministic         |    |

|      | approaches to SC with unary bitstreams                                          | 68 |

| 4.3  | Different types of stochastic bitstreams                                        | 70 |

| 4.4  | Deterministic approaches to SC by two pseudo-randomized bitstreams              | 72 |

| 4.5  | Proposed sources of generating pseudo-random numbers for the three              |    |

|      | deterministic approaches to SC                                                  | 74 |

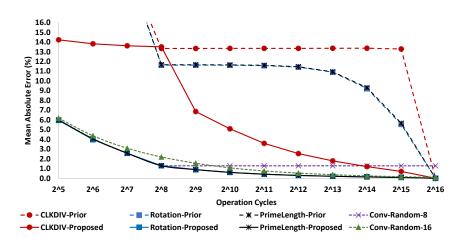

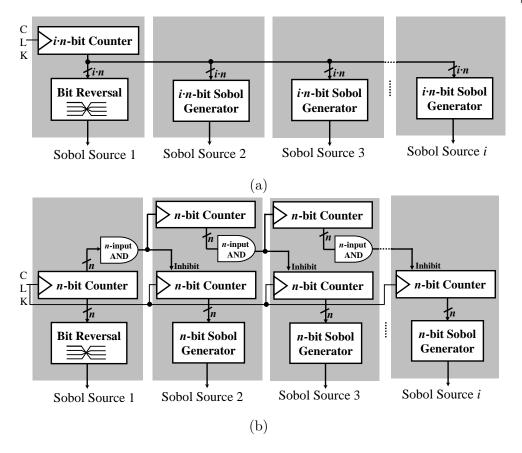

| 4.6  | Mean Absolute Error (%) when processing random input values with the            |    |

|      | Robert's cross stochastic circuit using different stochastic approaches         | 76 |

| 4.7  | Standard deviation of the absolute error of processing random input             |    |

|      | values with the Robert's cross stochastic circuit using different stochastic    |    |

|      | approaches                                                                      | 77 |

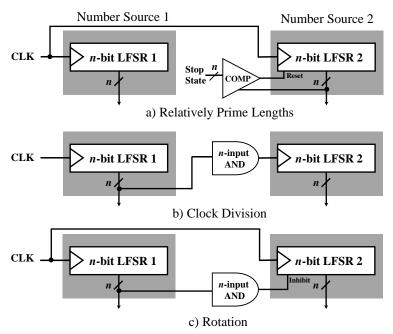

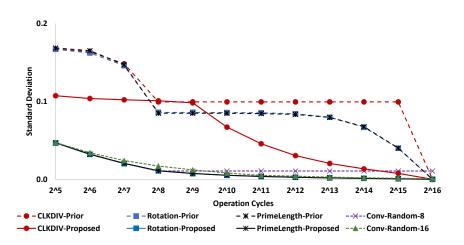

| 4.8  | (a) Halton sequence generator [6] (b) Sobol sequence generator [7, 8]           | 79 |

| 4.9  | First 16 numbers of the first four Sobol sequences from MATLAB built-in         |    |

|      | Sobol sequence generator, and the category of each one based on their           |    |

|      | position in the $[0, 1]$ interval                                               | 81 |

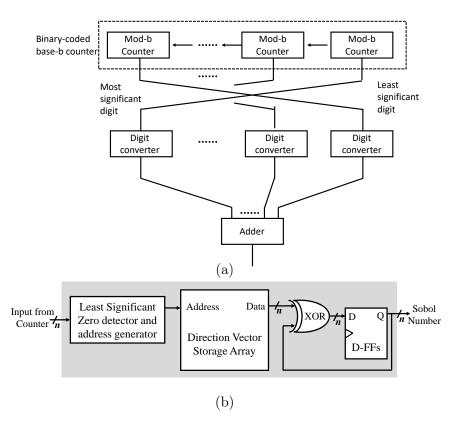

| 4.10 | Structures of the sources of generating Sobol sequences based on (a) first    |     |

|------|-------------------------------------------------------------------------------|-----|

|      | proposed method (b) second proposed method                                    | 83  |

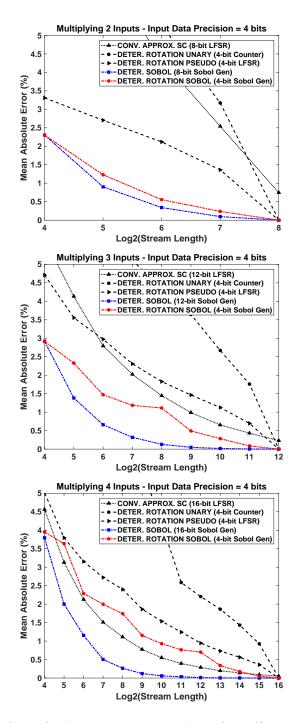

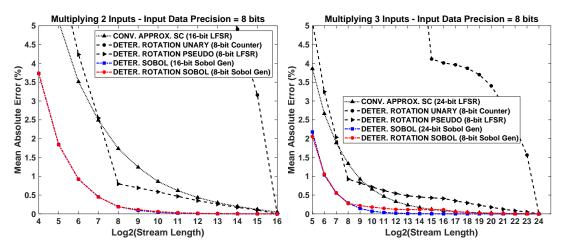

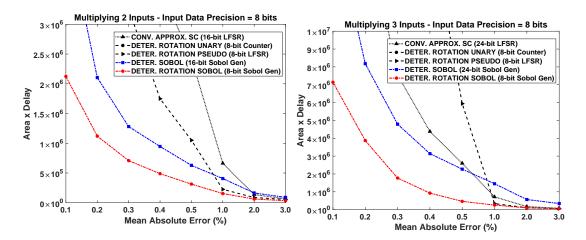

| 4.11 | MAEs of 4-bit precision multipliers for different stream lengths              | 89  |

| 4.12 | MAEs of 8-bit precision multipliers for different stream lengths              | 90  |

| 4.13 | Area x Delay of 8-bit precision multipliers for different MAEs. Note that     |     |

|      | the Area x Delay numbers for the deterministic rotation unary method          |     |

|      | were much larger than other method and out of the range shown in the          |     |

|      | figure)                                                                       | 90  |

| 5.1  | Example of stochastic multiplication using an AND gate                        | 94  |

| 5.2  | Stochastic multiplication using an AND with unsynchronized bitstream.         | 94  |

| 5.3  | Example of stochastic scaled addition using a MUX unit                        | 95  |

| 5.4  | Stochastic scaled addition using a MUX with unsynchronized bitstreams.        | 95  |

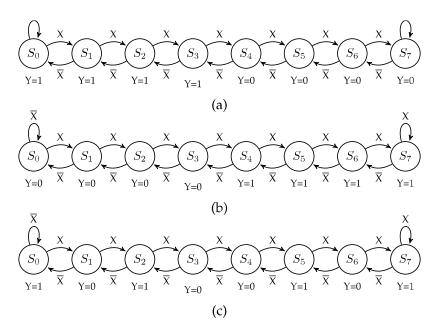

| 5.5  | State transition diagram of the FSM implementing a) the stochastic            |     |

|      | exponentiation function b) the stochastic tanh function c) stochastic         |     |

|      | absolute value function. For details of the implementation, the readers are   |     |

|      | referred to [9]                                                               | 96  |

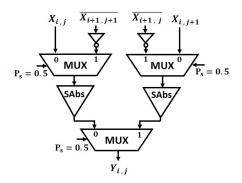

| 5.6  | Stochastic implementation of the Robert's cross edge detection algorithm [4]. | 97  |

| 5.7  | Stochastic implementation of basic sorting unit                               | 98  |

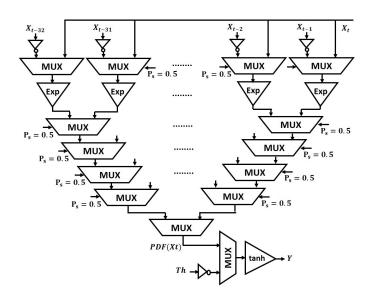

| 5.8  | Stochastic implementation of the KDE-based image segmentation algo-           |     |

|      | rithm [10]                                                                    | 99  |

| 5.9  | An AND gate connected to polysynchronous clock sources                        | 99  |

| 5.10 | Input clock signals and the corresponding output from connecting polysyn-     |     |

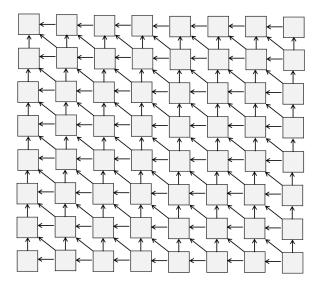

|      | chronous inputs to an AND gate                                                | .00 |

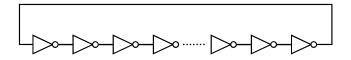

| 5.11 | 64 Robert's Cross Cells processing a $8\times 8$ input image concurrently 1   | .04 |

| 5.12 | Ring oscillator circuit with odd number of stages                             | .05 |

| 5.13 | Comparing the savings due to using different approaches of polysyn-           |     |

|      | chronous clocking on various sizes of the Robert's cross circuit $1$          | .09 |

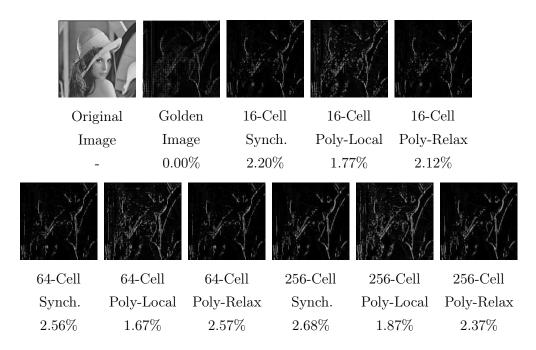

| 5.14 | The original sample input and the output images produced by post-             |     |

|      | synthesis simulations of the synthesized Robert's cross circuits              | 11  |

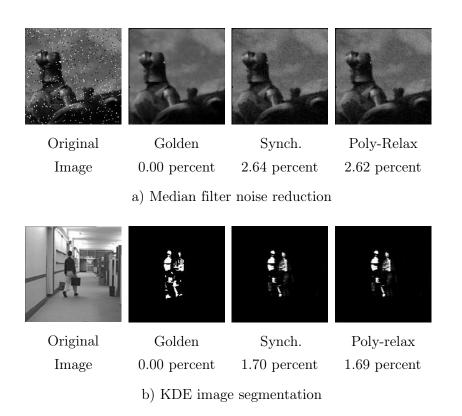

| 5.15 | The original sample inputs and the outputs of processing the sample       |       |

|------|---------------------------------------------------------------------------|-------|

|      | images by post-synthesis simulations of the synthesized circuits with a   |       |

|      | relaxed CDN: a) Median filter noise reduction circuit, b) KDE image       |       |

|      | segmentation circuit                                                      | 112   |

| 6.1  | Baseline Near-Sensor Stochastic Image Processor vs. StochMem              | . 121 |

| 6.2  | Input (expected output) per application on top (bottom)                   | 123   |

| 6.3  | Output inaccuracy of the baseline vs. StochMem                            | 126   |

| 6.4  | Output images: Baseline (StochMem) on top (bottom)                        | 127   |

| 6.5  | Energy consumption normalized to $Conv_{LFSR}$                            | 127   |

| 6.6  | Share of energy consumed by different units                               | 128   |

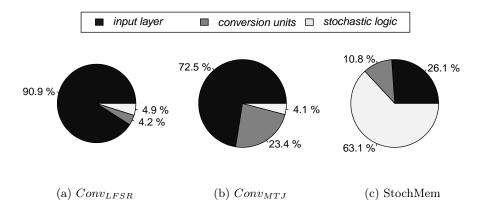

| 6.7  | Pie-charts demonstrating share of hardware cost (in terms of area) across |       |

|      | different units                                                           | 120   |

## Chapter 1

## Introduction

Stochastic Computing (SC), first advocated by Gaines [11, 12] and Poppelbaum [13] in 1967, has received renewed attention in recent years [14, 15, 2, 16, 4, 17, 18, 19]. This is due to the growing uncertainty in design parameters, and therefore, in design functionality, as induced by imbalances in modern technology scaling. Image and video processing [1, 4, 20, 21, 22], digital filters [23, 24, 25], low-density parity check decoding and error correction [26, 27, 28, 29, 30] and neural networks [31, 32, 33, 34, 35, 36, 37, 38, 39, 40, 41] have been the main target applications for SC.

In SC, circuits operate on randomized bitstreams. Independent of the length (and interleaving of 0s and 1s), the ratio of the number of 1s to the length of the stream determines the value of the bitstream. Computation accuracy increases with the length of the bitstream. In contrast to conventional binary radix, all digits of a bitstream have the same weight. In the "unipolar" representation, a real-valued number x ( $0 \le x \le 1$ ) is represented by a stream in which each bit has probability x of being one and probability 1-x of being zero. In the "bipolar" representation, a real-valued number y ( $-1 \le y \le 1$ ) is represented by a stream in which each bit has probability  $\frac{y+1}{2}$  of being one and probability  $1-\frac{y+1}{2}$  of being zero. For example, 1101010000 is a representation of 0.4 in the unipolar and -0.2 in the bipolar format. While the unipolar format can only be used for representing positive data, the bipolar format can deal with both positive and negative values. With the same length bit-stream, however, the precision of unipolar format is twice that of the bipolar format. To represent a real number with a resolution of  $2^{-M}$  in the unipolar format, a stream of  $2^{M}$  bits is required.

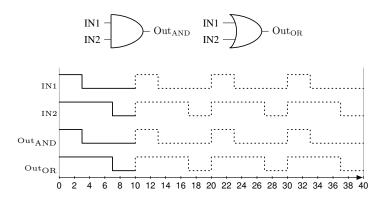

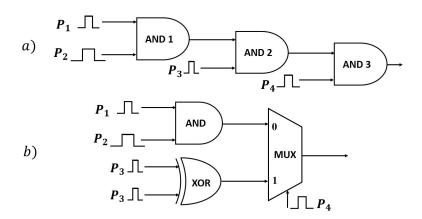

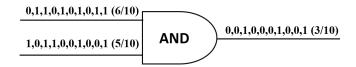

Weighted binary radix has been the dominant format for representing numbers in the field of computer engineering since its inception. The representation is compact; however, computing on this representation is relatively complex, since each bit must be weighted according to its position. A stochastic representation is much less compact than conventional weighted binary radix. However, complex operations can be performed with remarkably simple logic. For example, a single standard AND gate performs multiplication with the unipolar representation; a single XNOR gate performs multiplication with the bipolar representation. A multiplexer implements scaled addition and subtraction. Complex functions, such as exponentials and trigonometric functions, can be computed through polynomial approximations with less than a dozen gates [42, 4]. Over a wide range of arithmetic functions, a reduction in area of  $50 \times$  or  $100 \times$  compared to conventional implementations is common [6], [4].

In addition to producing simple and compact logic, a stochastic representation offers the advantage of error tolerance [2, 21, 4, 1]. In a noisy environment, bit flips will affect all the bits with equal probability. With a conventional binary radix representation, the high-order bits represent a large magnitude; accordingly, faults in these bits can produce large errors. In contrast, with a stochastic representation, all the bits are equally weighted. Hence, a single flip results in a small error. This error tolerance scales to high error rates so that multiple bit flips produce only small and uniform deviations from the nominal value.

Progressive precision [1] is another interesting advantage of computation on stochastic bit-streams. The quality of the results improves as the computation proceeds. This is because short sub-sequences of long random bit-streams provide low-precision estimates of the streams $\mathring{\text{a}}\mathring{\text{A}}\mathring{\text{Z}}$  values. This property can be exploited in making quick decisions on the input data and so increasing the processing speed.

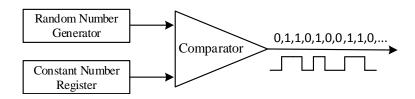

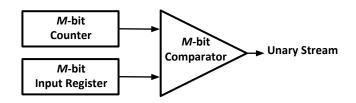

Given an input value, say in binary radix, the conventional approach for generating a stochastic bitstream with probability x is as follows. Obtain an unbiased random value  $0 \le r \le 1$  from a random [43][44] or pseudorandom source [45, 46]; compare it to the target value x; output a one if  $r \le x$  and a zero otherwise. Figure 1.1 illustrates the approach. The "random number generator" is usually a linear-feedback shift register (LFSR), which produces high quality pseudo-randomness [45]. Assuming that the pseudorandom numbers are uniformly distributed between  $0 \dots 2^M - 1$ , the value stored in

Figure 1.1: Stochastic Number Generator.

the constant number register should be  $2^M \cdot x$ . In the output, each bit is one with pseudo-probability  $2^M \cdot x/2^M = x$  [12, 31].

The obvious disadvantage of SC, however, is the latency. A stochastic representation is exponentially longer than conventional binary radix. This translates to long operation times, particularly if high accuracy is required. Long bitstreams can be compensated for, to some extent, by shortened clock cycles. Nevertheless, long latencies translate into high energy consumption which is often higher than that of its binary counterpart. Another disadvantage is the cost overhead of generating bitstreams. While the hardware to perform the computation is simple, generating random bitstreams is costly. Indeed, in prior work, stochastic bitstream generators accounted for as much as 80% of the area and power of stochastic circuit designs [2]. Factoring in the cost of the bit-stream generators, the overall hardware cost of an SC implementation is often comparable to that of a conventional binary implementation.

Recent work has shown that the same constructs used for computation on stochastic bit-streams can be used for computation on deterministic bitstreams, if these bitstreams are generated in some specific ways [47, 48]. The results are completely accurate with no inaccuracy caused by random fluctuation or correlation. While these deterministic methods are able to provide completely accurate results, they do not offer progressive precision. The output converges to the expected correct value slowly. This slow convergence makes the deterministic approaches inefficient for applications that can tolerate some inaccuracy (e.g., image processing and neural network applications).

Furthermore, the common focus of SC proposals from 1960s onwards has been stochastic logic (arithmetic), neglecting memory, which represents a crucial system component. Due to the difference in data representation, integrating conventional memory (designed and optimized for non-SC) in SC systems inevitably incurs a significant data conversion overhead.

This dissertation provides some new views to SC paradigm to address the abovementioned limitations and challenges. We introduce novel synthesis methodologies and research directions to SC with the goal of mitigating the hardware cost overhead, reducing the processing time and energy consumption, and improving the accuracy. The remainder of this dissertation is organized as follows.

- In Chapter 2, we introduce a new, energy-efficient, high-performance, and much less costly approach for performing SC using time-encoded pulse signals. We explore the performance of different stochastic operations for data processing of time-encoded inputs. We discuss the advantages, challenges, and potential applications for computation on such time-encoded signals.

- In Chapter 3, we propose a novel area- and power-efficient approach for synthesizing sorting network circuits based on deterministic unary-style bit-streams. To mitigate the long latency of processing input digital bitstreams, we exploit the idea of time-encoding data. We validate the method with two implementations of an important application of sorting, median filtering.

- Chapter 4 addresses an important challenge with the recently developed deterministic methods of SC, the poor progressive precision of processing unary bitstreams. We improve the progressive precision property of these deterministic methods by generating pseudo-random and low-discrepancy deterministic bitstreams. Experimental results show a significant improvement in the processing time and energy consumption compared to prior work when the application can tolerate slight inaccuracy.

- Chapter 5 introduces a new advantage to SC paradigm, the skew tolerance of SC circuits. We develop Polysynchronous Clocking, a design strategy for optimizing the clock distribution network (CDN) of stochastic systems. By removing and relaxing the clock network, we achieve a significant improvement in the latency, area, and energy consumption of stochastic systems while keeping the quality of the results. We show that circuits designed with either of these polysynchronous approaches are as tolerant of errors as conventional synchronous stochastic circuits.

- In Chapter 6, we rethink the memory system design for SC by integrating analog

memory with conventional stochastic systems. A seamless stochastic system, StochMem, is introduced which features analog memory to trade the energy and area overhead of data conversion for computation accuracy. StochMem can reduce the energy wasted in the conversion units significantly at the cost of a slight loss in computation accuracy.

• Chapter 7 summarizes the contributions of this dissertation and present important future directions.

## Chapter 2

# Time-Based Computing with Stochastic Constructs

This chapter explores an evolution of the concept of stochastic computing (SC). Instead of encoding data in space, as random bitstreams, we encode values in time. Computation is performed on analog periodic pulse signals. We review the performance of different stochastic operations including operations with independent inputs and operations with correlated input for data processing of time-encoded data. We show how input data from a sensing circuit can be converted to time-encoded data and processed with digital stochastic logic. We discuss the advantages, challenges, and potential applications for computation on time-encoded signals. This chapter's material has been published in [48], [49], [18], and [50].

#### 2.1 Motivation

A premise for SC is the availability of stochastic bitstreams with the requisite probabilities. Sensing circuits, such as image sensors, convert the sensed data (e.g., light intensity) to an analog voltage or current. The voltages or currents are then converted to digital form, as binary radix, with costly analog-to-digital convertors (ADCs). Finally, stochastic bitstream generators, consisting of random number generators (i.e., LFSRs) and comparators, are used to convert the data from binary radix format to stochastic bitstreams. Generating streams with a resolution of  $2^{M}$  requires a generator that can

produce  $2^M$  unique values. Even ignoring the cost of ADCs which are similarly required in the conventional binary radix-based systems, the high cost of the pseudo-random number generation diminishes one of the main advantages of SC: low hardware cost. A high hardware cost also means a significant amount of power. Prior work has shown that bitstreams 256 to 1024 bit long are often required to satisfy output quality with SC circuits [4, 2]. Noting that  $energy = power \times time$ , the long run-time of stochastic circuits, together with the high power consumption of the SNGs, could lead to significantly higher energy use than their conventional binary counterparts [51].

In this chapter, we introduce a new, energy-efficient, high-performance, and much less costly approach for generating stochastic bitstreams using analog periodic pulse signals. As technology has scaled and device sizes have gotten smaller, the supply voltages have dropped while the device speeds have improved [52]. Control of the dynamic range in the voltage domain is limited; however, control of the length of pulses in the time domain can be precise [52, 53]. Encoding data in the time domain may be more accurate and efficient than converting signals into binary radix. This time-based representation is an excellent fit for low-power applications that include time-based sensors, such as image processing circuits in vision chips. Converting a variety of signals from an external voltage to a time-based representation can be done much more efficiently than a full conversion to binary radix.

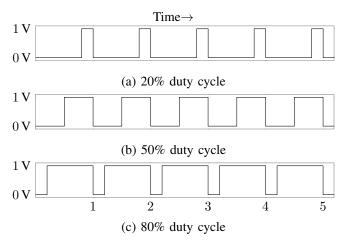

The time encoding consists of periodic signals, with the value encoded as the fraction of the time that the signal is in the high (on) state compared to the low (off) state in each cycle. We call these pulse-width modulated (PWM) signals. By exploiting pulse width modulation, signals with specific probabilities can be generated by adjusting the frequency and duty cycles of the PWM signals. These signals can be treated as inputs to the same logical structures used in SC, with the value defined by the duty cycle. The duty cycle  $(0 \le D \le 1)$  describes the amount of time the signal is in the high (on) state as a percentage of the total time it takes to complete one cycle. As a result, the signal is encoded in time. The frequency  $f = \frac{1}{T}$  of the PWM signal determines how long it takes to complete a cycle T and, therefore, how fast it switches between the high and the low

Figure 2.1: PWM signals with different duty cycles. (a) 20% duty cycle. (b) 50% duty cycle. (c) 80% duty cycle.

states. Thus, a PWM signal f(t) is defined as:

$$f(t) = \begin{cases} y_{\text{high}} & N.T < t \le N.T + (1 - D).T \\ y_{\text{low}} & N.T + (1 - D).T < t \le (N + 1).T \end{cases}$$

where  $y_{high}$  and  $y_{low}$  are the high and low values of the signal,  $N = 0, 1, 2, \cdots$  are the consecutive PWM cycles, and D is the duty cycle. Figure 2.1 shows three PWM signals with different duty cycles D when T = 1,  $y_{high} = 1V$ , and  $y_{low} = 0V$ .

Our approach is motivated by the following observation: a stochastic representation is a uniform, fractional representation. All that matters in terms of the value that is computed is the fraction of the time the signal is high. For example, if a signal is high 25% of the time, it is evaluated as 0.25 in the unipolar format. Similarly, PWM signals can be treated as time-encoded inputs with values defined by their duty cycle. For example, the PWM signals shown in Figure 2.1 represent 0.2, 0.5, and 0.8 in the unipolar and -0.6, 0.0, and 0.6 in the bipolar representation.

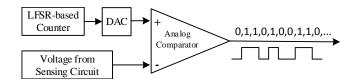

Alaghi et al. [1] proposed a specific design of an SNG unit for vision chips. Vision chips have image sensors that convert the perceived light intensity to an analog electrical voltage. The sensed voltage is converted to a stochastic number by comparing it to a random voltage generated by an LFSR-based counter and a digital-to-analog converter (DAC). Figure 2.2 illustrates their approach. We will show that, by working with PWM

Figure 2.2: SNG proposed in [1] for vision chips.

Figure 2.3: A common analog PWM generator.

signals, we can eliminate both the DAC as well as the LFSR. The result is a much less costly SNGs for applications that have analog electrical voltages as inputs.

#### 2.2 PWM as the Stochastic Number Generator

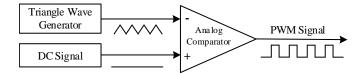

In many electronic systems, existing analog inputs or onboard microcontrollers can be employed to generate PWM signals [54]. The simplest way to generate a PWM signal is to feed a sawtooth wave into the first input of an analog comparator and a control voltage into the second. The frequency of the sawtooth waveform determines the sampling rate of the signal. Thus, by changing the frequency of this wave, one can adjust the frequency of the generated PWM signal.

Figure 2.3 shows a common design for an analog PWM generator. The duty cycle of the PWM signal is set by changing the DC level of the input signal. The higher the DC level is, the wider the PWM pulses. The range of the DC signal varies between the minimum and maximum voltages of the triangle wave. For example, if we adjust the DC signal to have a level exactly half-way between the minimum and maximum, the circuit will generate a PWM signal with a duty cycle of 50%. This will correspond to an input value of 0.5 in the unipolar and 0.0 in the bipolar representation.

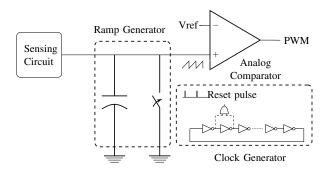

Figure 2.4 shows the design of a low-cost PWM generator, consisting of a ramp generator, a clock signal generator, and an analog comparator. The input is a current coming from a sensing circuit that controls the duty cycle of the PWM signal. The clock

Figure 2.4: The design of our PWM generator. The duty cycle is determined by the current coming from the sensing circuit (a photodiode, or a voltage controlled current source, etc) and the Reset pulse defines the frequency of the PWM signal. Vref is a fixed reference voltage.

generator provides the required *Reset* signal which determines the frequency of the PWM signal. Ring oscillators consisting of an odd number of inverter gates can be used as the clock generator. The frequency of the *Reset* clock can be adjusted by either changing the supply voltage or changing the number of inverters in the oscillator. In the 45nm technology, a ring of approximately 89 inverter gates can generate a local clock with a period of 1ns with a supply voltage of 1.0V.

Table 2.1 shows an area-power comparison of the proposed PWM generator shown in Figure 2.4 with prior methods for SNGs: 1) the LFSR-based method in [2], and 2) the method proposed for vision chips in [1]. The results are for 45nm technology. We assume that the inputs are analog voltages or currents coming from a sensing circuit.

Table 2.1: Area-Power comparison of different SNGs

| SNGs                             | Unit             | Area $(\mu m^2)$     | Power @1-3GHz $(\mu W)$ |

|----------------------------------|------------------|----------------------|-------------------------|

| Conventional SNG [2]             | LFSR+Comparator  | 248                  | 335-1013                |

| (with 8-bit LFSR)                | ADC [55]         | >400,000             | >10,000                 |

| Special SNG                      | LFSR             | 167                  | 298-892                 |

| for vision chips [1]             | DAC + Comparator | equivalent to an ADC |                         |

| PWM Generator<br>(1-3 GHz freq.) | Comparator       | 20-58                | 65-192                  |

|                                  | Ramp Generator   | 10-32                | 11-29                   |

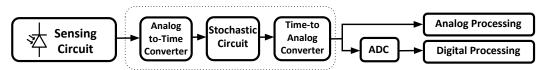

|                                  | Clock Generator  | 124-37               | ~175                    |

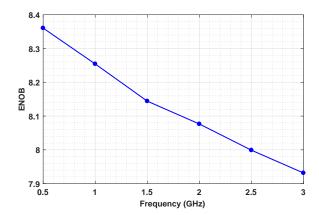

Figure 2.5: The ENOB of the proposed PWM generator shown in Figure 2.4 when generating PWM signals with frequencies from 0.5 to 3 GHz. More detail on the noise modeling of the implemented PWM generator will be discussed in Section 2.5.2.

The effective number of bits (ENOB) corresponding to different frequencies of the PWM generator is shown in Figure 2.5. Analog-to-digital convertors (ADCs) are used to obtain a digital representation for the LFSR-based method. The cost of a 45nm SAR ADC is taken from [55]. The special SNG proposed for vision chips resembles an ADC; we assume that it is roughly as expensive as a SAR ADC. The Synopsys Design Compiler was used to synthesize the SNGs. The results in Table 2.1 demonstrate that our mixed-signal method, based on PWM generators, has much lower area and power costs than the prior methods in cases where the inputs are in analog voltage or current form. Accordingly, the approach is a good fit for real-time image processing circuits, such as those in vision chips. These have image sensors that convert the perceived light intensity to an analog voltage or current.

Note that in prior methods a counter was used to convert stochastic streams back into real values in the digital domain. To convert the stochastic signals directly to a value in the analog domain, prior work used a simple RC integrator circuit to average the signal [56, 57]. For a faster response time, we use a Gm-C active integrator to average the output from processing PWM signals and measure the fraction of the time that the signal is high. For example, for a PWM signal with a period of T, duty cycle of D,  $y_{\text{high}} = 1V$ , and  $y_{\text{low}} = 0V$ , the integrator gives the average value of the first period of

Figure 2.6: Time-based computing with stochastic constructs. An ATC converts the sensed data to a time-encoded pulse signal. The converted signal is processed using the stochastic circuit, and the output is converted back to a desired analog format using a TAC.

the signal as follow:

$$\bar{y} = \frac{1}{T} \int_0^T f(t)dt = \frac{1}{T} \left( \int_0^{(1-D)T} y_{\text{low}} dt + \int_{(1-D)T}^T y_{\text{high}} dt \right)$$

$$= \frac{1}{T} \left( T.(1-D).y_{\text{low}} + T.D.y_{\text{high}} \right) = D$$

### 2.3 Stochastic Systems with Time-Encoding Signals

Figure 2.6 shows the flow of computing on time-encoding signals. Assuming that the sensing circuitâĂŹs output is in voltage or current form, an analog-to-time converter (ATC) circuit (i.e., a PWM signal generator) is used to convert the sensed data to a time-encoded pulse signal. The converted signal is processed using the same circuit constructs as are used in SC. The output is converted back to a desired analog format using a time-to-analog converter (TAC) (i.e.,a voltage integrator). In what follows, we discuss the implementation of basic stochastic operations operating with PWM signals. Then we extend the discussion to more complex examples consisting of a multi-level combination of stochastic operations.

#### 2.3.1 Stochastic Operations with PWM signals

Stochastic operations can be divided into two main categories with respect to correlation between their inputs: operations that require independent (i.e., uncorrelated) inputs such as multiplication and scaled addition, and operations that require highly correlated inputs such as absolute-valued subtraction, minimum and maximum value function, and comparison.

#### Multiplication

In the SC representation, a single AND (XNOR) gate performs multiplication if the unipolar (bipolar) format is used. The multiciplication operation presumes that the inputs are independent, uncorrelated streams [31]. Connecting two PWM signals with the same duty cycle and the same frequency to the inputs of an AND gate will evidently not work. It produces an output signal equal to the two inputs, not the square of the value as required. However, as we will show, one can use PWM signals provided that they have different frequencies (recall that we represent values by the duty cycle of PWM signals, not their frequency).

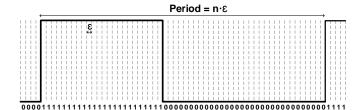

Instead of continuous-valued time signals, assume for the sake of argument that PWM signals are represented as bitstreams. For instance, assume an input value X=3/5 (a signal with duty cycle of 60%) is represented by the bitstream 11100, and an input Y=1/2 (a duty cycle of 50%) is represented by the bitstream 1100. Note that the stream for X has length 5 while that for Y has length 4. Suppose we multiply X and Y with an AND gate. Let the bitstreams run for 20 clock cycles, corresponding to 4 repetitions of X and 5 repetitions of Y. Taking the bit-wise AND of the streams

$egin{array}{lll} X &= 11100111001110011100 \\ Y &= 11001100110011001100 \\ \hline X.Y &= 11000100000010001100 \\ \hline \end{array}$

we observe 6/20 ones in the output, the expected value, since  $3/5 \times 1/2 = 6/20$ . The results of this sort of multiplication operation is always correct if one chooses stream lengths that are relatively prime and let them run up to the common multiple. This is because when the length of the inputs are relatively prime, the difference between the lengths results in a new phase between the signals in each repetition until they get to the common multiple. A new initial phase in each repetition causes each bit of the first bitstream to see every bit of the second stream. This is, intuitively, equivalent to sliding one bitstream past the other. The bitstreams are therefore multiplied by convolving through sliding and ANDing repeatedly [58, 59, 47].

**Proof.** Let a/m be represented by a stream of m bits consisting of a bits of 1's with the rest of the bits being 0. Similarly, let b/n be represented by a stream of n bits with b bits of 1's and the remaining bits being 0. Assume that we repeat both streams to reach

Figure 2.7: Discretizing a continuous PWM signal.

a total of the least common multiple (LCM) number of bits, or for simplicity mn bits in each stream. Applying an AND gate to these streams, we will have  $a \times b$  bits of 1's if and only if the set  $\{mk+i \pmod n: k=0,1,\ldots,n-1\}$  is a complete set of residues mod n. Here, i is the position of any 1 bit in the first stream. The first observation is that, whether the above holds or not does not depend on i. The second observation is that, when i=0, this statement is true if and only if m and n are relatively prime. Therefore, ANDing the above streams produces  $\frac{a}{m} \times \frac{b}{n}$  if and only if m and n are relatively prime. Q.E.D.

This argument can be easily expanded to analog PWM signals if the continuous signals are discretized into bitstreams, as illustrated in Figure 2.7. A PWM signal can be discretized into a bitstream by dividing the signal into pulses of size epsilon and assigning 0/1 bits to these pulses. The relatively prime length rule is then applicable to this discrete representation of the PWM signals and continues to hold as  $\epsilon \to 0$ . Note that in signal processing terminology, PWM signals with relatively prime periods are inharmonic.

To illustrate this argument, we simulated multiplication on a thousand sets of random input values represented by PWM signals in MATLAB [60]. We fixed the period of the first PWM signal at 20 ns while varying the period of the second from 1 ns to 20 ns in increments of 0.1 ns. For each pair of periods, we converted the randomly generated sets into corresponding PWM signals and then performed multiplication for 1000 ns. The accuracy of the results was verified by calculating the difference between the expected value and the measured output value for all sets. To convert the output signals into deterministic real values, we measured the fraction of the time that the output is high and divided this by the total time. The average error rates for multiplication for different

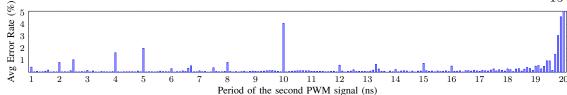

Figure 2.8: Average error rates when performing a multiplication operation using an AND gate for 1000 ns on 1000 sets of random input values when the inputs are represented using PWM signals. The period of the first input is set at 20 ns while the period of the second changes from 1 to 20 ns.

pairs of periods are shown in Figure 2.8.

As can be seen in Figure 2.8, with the period of the first PWM input signal fixed at 20 ns, choosing 1 ns, 2 ns, 2.5 ns, 4 ns, 5 ns, 8 ns, 10 ns, 12 ns, 15 ns, 16 ns, or values very close to 20 ns as the period of the second PWM input signal produces poor results. This can be attributed to an aliasing effect that occurs with periodic signals that are harmonically related. Eliminating these choices, the measured average error rate for other values was always less than 0.5%. Note that these results could ideally be extended to any other range of periods.<sup>1</sup> For example, knowing that 20 ns and 13 ns is a good pair, periods of 2 ns and 1.3 ns, or 10 ns and 6.5 ns would work equally well. From this observation we make our first conclusion:

Conclusion 1. Stochastic multiplication of numbers represented by PWM signals produces highly accurate results if the signals are not harmonically related.

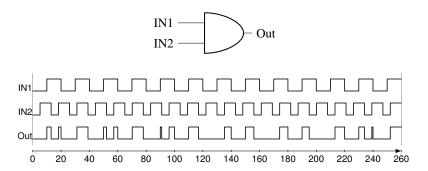

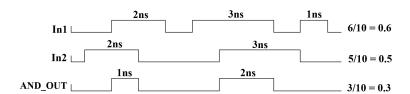

With inharmonic PWM signals as inputs of multiplication, the fraction of time that the output signal is high will converge to the expected value eventually. However, stochastic circuits are not energy-efficient if the operations run more than what they actually need to. The question is: How many cycles of PWM signals are required to reach to a reasonable accuracy? Figure 2.9 shows an example of multiplying two stochastic numbers, 0.5 and 0.6, represented using two PWM signals. The period of the first PWM signal is 20 ns and that of the second is 13 ns. The figure shows that, after performing the operation for 260 ns, the fraction of the total time the output signal is high equals the value expected, when multiplying the two input values, namely 0.3.

<sup>&</sup>lt;sup>1</sup> In practice, the resolution or effective number of bits (ENOB) of the PWM signals can affect the accuracy and so limits the extension range.

Figure 2.9: Example of multiplying two PWM signals using an AND gate. IN1 represents 0.5 (50% duty cycle) with a period of 20 ns, and IN2 represents 0.6 (60% duty cycle) with a period of 13 ns. The output signal from t=0 to 260 ns represents 0.30 (78 ns/260 ns=3/10), the expected value from multiplication of the inputs.

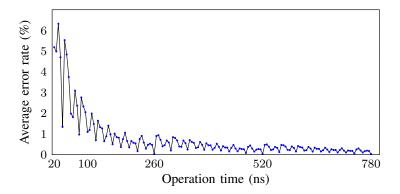

Expanding the example above to different operation times, Figure 2.10 shows the average error rates of multiplying 1000 pairs of random numbers represented by PWM signals when a fixed period of 20 ns is selected for the first and a fixed period of 13 ns is chosen for the second. We vary the operation time. As the figure shows, the output of multiplications converges to the expected value if the operations continue at least up to the least common multiple (LCM) of the periods of the input signals (here,  $20 \times 13 = 260 \text{ ns}$ ). The best possible accuracy is obtained when the operation is run for exactly the LCM (260 ns) or multiples of the LCM (520 ns and 780 ns). Running the operation longer than the LCM does not help the accuracy. This is in contrast to prior SC approaches where increasing the length of bitstreams improves the quality of the results [2, 4, 1].

Let us consider the X.Y stream produced before. The LCM of the input streams was  $4 \times 5 = 20$  and after exactly 20 cycles the expected output was produced. Continuing the operation for another 20 cycles produces exactly the same output with the same ratio of ones to the length of stream:

Thus, we can say that the output has a period of 20 cycles. A similar result is observed when ANDing continuous PWM signals. The output has a period of the LCM. The

Figure 2.10: Average error rate of multiplying 1000 pairs of random numbers represented by PWM signals when varying the operation time. The period of the PWM signals corresponding to the first and to the second number in each trial is 20 and 13 ns, respectively.

signal produced from the first LCM to the second LCM is exactly the same as the signal produced from time=0 to the first LCM. This motivates our second conclusion:

Conclusion 2. The best accuracy when multiplying numbers represented by PWM signals is obtained when running the operation for the LCM or multiples of the LCM of the period of the inputs.

Knowing that relatively prime periods must be selected for the input signals and the multiplication operation should be run for the LCM of the periods, a new question arises:

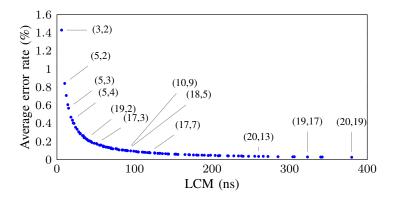

Considering available sets of relatively prime periods, each with a different LCM, what is the best set of periods to reach to a desired accuracy? For example, (17 ns, 3 ns) and (17 ns, 7 ns) are two possible sets of periods to generate the PWM input signals for a multiplication operation. The first set has an LCM of 51 ns while the second's is 119 ns. Which one of these two sets is a better choice?

Figure 2.11 shows the average error rates of multiplying 1000 pairs of random numbers represented by PWM signals when different sets of relatively prime periods are selected as the periods of the input signals and the operations are run for the LCM of the periods. Each set of periods has a different LCM. As can be seen in the figure, the larger the LCM, the lower the average error rate. The reason is that larger LCMs are produced

Figure 2.11: The average error rate for multiplying 1000 pairs of random numbers represented by PWM signals when the period of the first and the second PWM signal are relatively prime integers in the interval [2, 20]. A lower average error rate in the figure means a higher ENOB in the computations.

by longer periods and a longer period means a higher ENOB in representing the input values and so a higher ENOB in the computations. Note that while generating PWM signals with longer periods and so larger LCMs gives more accurate results, this requires a longer operation time. Thus, if a set of periods with a smaller LCM can satisfy the accuracy requirements, this might be the better choice. Thus, we conclude the following:

Conclusion 3. The larger the LCM of the periods of the PWM input signals, the higher the accuracy when performing multiplication.

## Scaled Addition and Subtraction

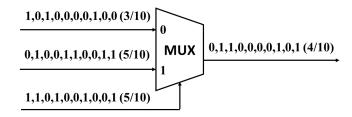

Stochastic values are restricted to the interval [0, 1] (in the unipolar case) or the interval [-1, 1] (in the bipolar case). So one cannot perform addition or subtraction directly, since the result might lie outside these intervals. However, one can perform scaled addition and subtraction. These operations can be performed with a multiplexer (MUX) [4]. The performance of a MUX as a stochastic scaled adder/subtracter is insensitive to the correlation between its inputs. This is because only one input is connected to the output at a time. Thus, highly overlapped inputs like PWM signals with the same frequency can be connected to the inputs of a MUX. The important point when performing scaled

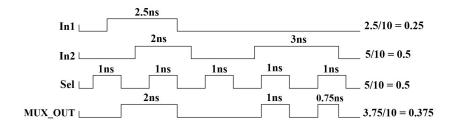

Figure 2.12: Example of the scaled addition of two PWM signals using a MUX. IN1 and IN2 represent 0.2 and 0.6 with a period of 5 ns, and Sel represents 0.5 with a period of 4 ns. The output signal from t=0 to 20 ns represents 0.40 (8 ns/20 ns = 4/10), the expected value from the scaled addition of the inputs.

addition and subtraction with a MUX on PWM signals is that the period of the select signal should not be harmonically related to the period of the input signals. For example, 5, 5, and 4 ns is a good set of numbers for the period of the first, the second, and the select input signals, respectively.

Figure 2.12 shows an example of scaled addition on two stochastic numbers, 0.2 and 0.6, represented by two PWM signals (both have periods of 5 ns). A PWM signal with duty cycle of 50% and period of 4 ns is connected to the select input of the MUX. As shown, after performing the operation for 20 ns, the fraction of the total time the output signal is high equals the expected value, 0.40. The same argument we had for the multiplication operation also exists here – the scaled addition/subtraction operation should be run for the LCM or multiples of the LCM of the period of the input signals and that of the select signal to produce the correct output. Note that choosing different periods for the main inputs of the MUX results in a larger LCM and so results in a longer operation time. Furthermore, generating inputs with different periods requires extra clock generator circuitry. We conclude that it is most efficient to generate signals for the main inputs of the MUX with the same period.

A unique property of MUX-based operations is that large LCMs are not necessarily required to produce accurate results. Similar to what we saw for the multiplication

Figure 2.13: Average error rate of performing scaled addition on 1000 pairs of random numbers represented by PWM signals when the period of the first and the second PWM signal is the same but different and relatively prime with the period of the PWM select signal. The periods are selected from integers in [2, 20] interval.

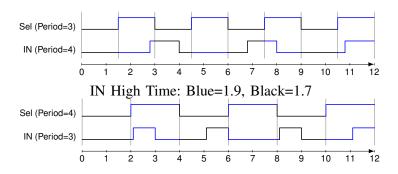

operation, selecting inharmonic periods with a large LCM guarantees the accuracy of the results for the scaled addition/subtraction. However, it is possible for the stochastic MUX-based operations to produce accurate results even with inputs with very small periods. Figure 2.13 shows the average error rate of performing scaled addition when inharmonic PWM signals are connected to the main and select inputs of the MUX.

Each point in Figure 2.13 represents the accuracy and the LCM corresponding to one set of periods. The first and the second numbers in each set are the period of the main PWM inputs and the third number is the period of the select input. As the results show, when the period of the PWM select signal is an "even" value (2 ns, 4 ns,...) choosing "odd" periods as the period of the main PWM inputs result in highly accurate outputs. When choosing an "even" period for the inputs and an "odd" period for the select signal, a large LCM is needed to produce accurate results. The reason is shown in Figure 2.14. A select signal with an "even" period perfectly splits an input with an "odd" period in two periodic parts with the same duration at the high level. Thus, it does not matter to which input of the MUX the input signal is connected. However, in the case of an "odd" period for the select signal, connecting the input signal to different inputs of the MUX selects different parts of the input signal with different high durations. This motivates

IN High Time: Blue=1.8, Black=1.8.

Figure 2.14: Examples of choosing an  $\hat{a}$ AIJodd $\hat{a}$ Aİ or an  $\hat{a}$ AIJeven $\hat{a}$ Aİ number as the period of the MUX $\hat{a}$ AZs select signal. The input is a PWM signal with D = 30%. Black (blue) lines are parts of the input signal that will be connected to the output of the MUX when the input is connected to the first (second) input.

our fourth conclusion:

Conclusion 4. Optimal choices for MUX-based operations are those with an "even" value for the period of the select input and an "odd" value for the period of the main inputs. The operation should run for the LCM of the periods.

#### Absolute Value subtraction

Correlation between the inputs of a stochastic circuit can sometimes change the functionality of a circuit, which might result in a more desirable operation. An XOR gate with independent inputs performs the function  $z = x_1(1 - x_2) + x_2(1 - x_1)$ . However, when fed with correlated inputs where the two input streams have maximum overlap in their 1s, the circuit computes  $|x_1 - x_2|$ . Consider  $x_1 = 11101$  and  $x_2 = 10001$ , two 5-bit long correlated stochastic streams representing 4/5 and 2/5. Connecting these streams to the inputs of an XOR gate produces Y = 01100, the expected value from performing absolute valued subtraction. In this case, the output stream has the same number of bits as the input streams. This operation is particularly useful in stochastic implementation of image-processing algorithms, such as Robert's cross edge detection algorithm [1].

When working with PWM signals, high correlation or maximum overlap is provided

Figure 2.15: Example of performing stochastic absolute value subtraction using an XOR gate when two synchronized PWM signals are used as the inputs of the gate, one representing 0.5 (D = 50%) and the other 0.8 (D = 80%). Both PWM signals have a period of 20 ns. The output signal from t = 0 to 20 ns represents 0.3, the expected value for |IN1 - IN2|.

by satisfying two requirements: 1) choosing the same frequency for the input signals, and 2) having maximum overlap between the high parts of the signals. Thus, two PWM signals that have the same period, with the high part in each one located at the start or end of each period, are called correlated (or synchronized) signals. Figure 2.15 shows an example of performing absolute value subtraction on two synchronized PWM signals. As the figure shows, the correct output with the highest possible accuracy is ready right after performing the operation for only one period of the PWM input signals. Thus, the following holds.

Conclusion 5. For operations, such as absolute value subtraction, which work only with correlated inputs (synchronized PWM signals), the period of the output signal, and, thus, the operation time, equals the period of the input signals.

This conclusion introduces an important advantage of working on the synchronized PWM signals which is that they eliminate the requirement of running the operation for several repetitions of the input signals to obtain an accurate output signal. An important point, however, is that there is a limitation in using such operations that require highly correlated inputs. Providing the required synchronization (maximum high part overlap between the input signals) is difficult for the second (or higher) level of the circuit where the signals are the outputs of a previous level. Nonetheless, performing these operations

Figure 2.16: Performing minimum and maximum operations on two synchronized PWM signals: IN1 represents 0.3 and IN2 represents 0.7. Both PWM signals have a period of 10 ns.

can still be advantageous at the first level of circuits.

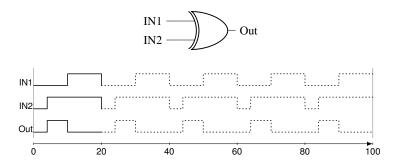

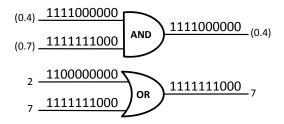

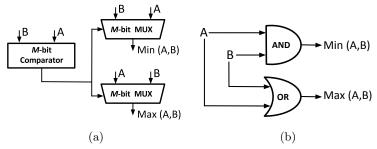

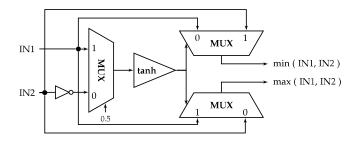

## Minimum and Maximum

An AND gate with independent inputs works as a multiplier. However, with highly correlated inputs, it gives the minimum of the two stochastic streams. An OR gate supplied with highly correlated streams gives the maximum of the two stochastic streams. Thus, a basic sorting unit can be constructed with only an AND and an OR gate: supplied with two correlated inputs, it produces the smaller of the two values on one output line, and the greater of the two on the other. Such a low-cost implementation of sorting can save orders of magnitude in hardware resources and power when compared to the costs of a conventional binary implementation. As we will discuss in Chapter 3, such circuits are important for low-cost implementation of applications such as median filtering.

Figure 2.16 shows two synchronized PWM signals and the outputs of performing the minimum and maximum operations on these. As can be seen, the expected output is produced after a single cycle of the PWM input signals. Continuing the operations for additional cycles (the dotted lines) does not improve the accuracy of the results.

Figure 2.17: Comparing stochastic numbers (SNs), represented by synchronized PWM signals, using a D-type flip-flop: (up) IN1 < IN2, and thus Out=0; (down) IN1 > IN2, and thus Out=1.

## Comparison