Copyright

by

Zhuojie Wu

2013

# The Dissertation Committee for Zhuojie Wu Certifies that this is the approved version of the following dissertation:

# Study of Initial Void Formation and Electron Wind Force for Scaling Effects on Electromigration in Cu Interconnects

| Committee:             |

|------------------------|

|                        |

|                        |

| Paul S. Ho, Supervisor |

|                        |

|                        |

| Maxim Tsoi             |

|                        |

|                        |

| Chih-Kang Shih         |

|                        |

| Rui Huang              |

|                        |

|                        |

| Zhen Yao               |

# Study of Initial Void Formation and Electron Wind Force for Scaling Effects on Electromigration in Cu Interconnects

by

Zhuojie Wu, B.S.; M.S.

### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2013

## **Dedication**

To my family

### Acknowledgements

It is a great pleasure for me to express my gratitude to many people for their support to this dissertation.

First of all, I would like to express my very great appreciation to Professor Paul S. Ho for his guidence and support throughout my doctoral work. I am deeply indebted to him and truly appreciate his constant encouragement and advising to my research.

I would like to thank other members of my committee, Professor Maxim Tsoi, Professor Chih-Kang Shih, Professor Rui Huang and Professor Zhen Yao, for their support and advice. I am particularly grateful to Professor Rui Huang for the helpful discussions in developing the stress model in Cu electromigration.

I would also like to thank Dr. Ki-Don Lee from Texas Instruments for providing test samples as well as patient discussions.

I would like to offer my special thanks to Dr. Junjun Liu for many patient discussions on the work of electron wind force. I also truly appreciate him for his valuable suggestions in general.

I would like to thank Xi Chen for his help in fluorescence microscopy of nanochannels.

I'm grateful to Dr. Jang-Hi Im for his help in my research and proofreading my dissertation. Special thanks to Ms. Jo Ann Smith for her administrative support and help in the past few years.

My thanks are extended to my colleagues and friends in the Laboratory of Interconnect and Packaging including former members, Scott Smith, Bin Li, Zhiquan Luo, Junjing Bao, Huangliang Shi, Gary Lu, Xuefeng Zhang, Lijuan Zhang, Brook Chao, Soo Young Choi, Seung-Hyun Chae, Matthias Kraatz, Huai Huang, and current members, Qiu Zhao, Yiwei Wang, Linjun Cao, Tengfei Jiang and Laura Spinella for their help, collaboration, advices and discussions of my doctoral work. Special thanks to Zhiquan Luo for training me on semiconductor processes.

Finally, my great thanks go to my parents, my sister and my wife for their endless and unconditional love, trust, caring, understanding and patience.

Study of Initial Void Formation and Electron Wind Force for Scaling **Effects on Electromigration in Cu Interconnects**

Publication No.

Zhuojie Wu, Ph.D.

The University of Texas at Austin, 2013

Supervisor: Paul S. Ho

The continuing scaling of integrated circuits beyond 22nm technology node poses increasing challenges to Electromigration (EM) reliability for Cu on-chip interconnects. First, the width of Cu lines in advanced technology nodes is less than the electron mean

free path which is 39nm in Cu at room temperature. This is a new size regime where

any new scaling effect on EM is of basic interest. And second, the reduced line width

necessitates the development of new methods to analyze the EM characteristics. Such

studies will require the development of well controlled processes to fabricate suitable test

structures for EM study and model verification. This dissertation is to address these

critical issues for EM in Cu interconnects.

The dissertation first studies the initial void growth under EM, which is critical

for measurement of the EM lifetime and statistics. A method based on analyzing the

resistance traces obtained from EM tests of multi-link structures has been developed.

The results indicated that there are three stages in the resistance traces where the rate of

vii

the initial void growth in Stage I is lower than that in Stage III after interconnect failure and they are linearly correlated. An analysis extending the Korhonen model has been formulated to account for the initial void formation. In this analysis, the stress evolution in the line during void growth under EM was analyzed in two regions and an analytic solution was deduced for the void growth rate. A Monte Carlo grain growth simulation based on the Potts model was performed to obtain grain structures for void growth analysis. The results from this analysis agreed reasonably well with the EM experiments.

The next part of the dissertation is to study the size effect on the electron wind force for a thin film and for a line with a rectangular cross section. The electron wind force was modeled by considering the momentum transfer during collision between electrons and an atom. The scaling effect on the electron wind force was found to be represented by a size factor depending on the film/line dimensions. In general, the electron wind force is enhanced with increasing dimensional confinement.

Finally, a process for fabrication of Si nanotrenches was developed for deposition of Cu nanolines with well-defined profiles. A self-aligned sub-lithographic mask technique was developed using polymer residues formed on Si surfaces during reactive ion etching of Si dioxide in a fluorocarbon plasma. This method was capable to fabricate ultra-narrow Si nanotrenches down to 20nm range with rectangular profiles and smooth sidewalls, which are ideal for studying EM damage mechanisms and model verification for future technology nodes.

### **Table of Contents**

| Chapter 1: | Introduction                                                | 1  |

|------------|-------------------------------------------------------------|----|

| 1.1        | General Background                                          | 2  |

| 1.2        | The Damascene Process                                       | 4  |

| 1.3        | EM in Cu Interconnects                                      | 8  |

| 1.4        | Scaling Challenges to Cu EM                                 | 11 |

| 1.5        | Motivation                                                  | 15 |

| 1.6        | Scope of this Work                                          | 18 |

| Chapter 2: | Electromigration Induced Void Formation in Cu Interconnects | 19 |

| 2.1 I      | ntroduction                                                 | 20 |

| 2.2 A      | analysis of Resistance Change Induced by Void Formation     | 25 |

| 2.3 S      | ample Information and EM Experimental Procedure             | 30 |

| 2.4 F      | Results and Discussion                                      | 36 |

|            | 2.4.1 Resistance Traces and Failure Mode                    | 36 |

|            | 2.4.2 Joule Heating and TCR                                 | 45 |

|            | 2.4.3 Failure Time Statistics                               | 48 |

|            | 2.4.4 Statistics for $R_{step}$ and $R_{slope}$             | 61 |

|            | 2.4.5 Comparison between $t_{f\_calc}$ and $t_f$            | 67 |

| 2.5 (      | Conclusions                                                 | 71 |

| Chapter 3: | Stress Modeling for Initial Void Growth in Cu Interconnects | 72 |

| 3.1 F      | Review of EM Models                                         | 73 |

|            | 3.1.1 Introduction of EM Models                             | 73 |

|            | 3.1.2 the Korhonen Model                                    | 73 |

|            | 3.1.3 Void Growth in the Korhonen Model                     | 75 |

|            | 3.1.4 Microstructure-based Statistical Model                | 78 |

| 3.2 I      | nitial Void Formation Model                                 | 81 |

| 3.3 I      | nitial Void Growth Rate Results and Discussion              | 87 |

| 3.4 N      | Monte Carlo Simulation of Grain Growth                      | 96 |

| 3.4.1 the Potts Model                                                                     | 97  |

|-------------------------------------------------------------------------------------------|-----|

| 3.4.2 Simulation Details                                                                  | 98  |

| 3.4.3 Simulation Results and Discussion                                                   | 100 |

| 3.5 Conclusions                                                                           | 108 |

| Chapter 4: Size Effect on the Electron Wind Force for Electromigration Interconnects      |     |

| 4.1 Introduction                                                                          | 111 |

| 4.2 Thin Film                                                                             | 114 |

| 4.3 Rectangular Line                                                                      | 119 |

| 4.4 Grain Boundary Scattering                                                             | 125 |

| 4.5 Temperature Effect                                                                    | 129 |

| 4.6 Conclusions                                                                           | 130 |

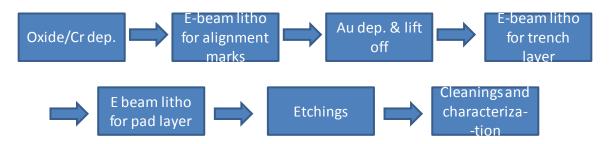

| Chapter 5: Fabrication of Silicon Nanotrenches by Self-aligned Sub-lith Masking Technique |     |

| 5.1 Introduction and Motivation                                                           | 133 |

| 5.2 Fabrication of Si Nanolines                                                           | 136 |

| 5.3 Fabrication of Si Nanotrenches with Contact Pads                                      | 142 |

| 5.4 Self-aligned Sub-lithographic Mask                                                    | 147 |

| 5.4.1 Fundamentals of Fluorocarbon Plasma                                                 | 147 |

| 5.4.2 Polymer Residue Layer as an Etch Mask                                               | 148 |

| 5.4.3 Sub-lithographic Mask                                                               | 150 |

| 5.4.4 Potential Applications                                                              | 159 |

| 5.5 Conclusions                                                                           | 164 |

| Chapter 6: Conclusions and Suggestions for Future Work                                    | 165 |

| 6.1 Conclusions                                                                           | 165 |

| 6.2 Suggestions for Future Work                                                           | 167 |

| References                                                                                | 170 |

| Vita                                                                                      | 182 |

### **List of Tables**

| Table 2.1 | Number of big resistance jump observed in different links                              | 44 |

|-----------|----------------------------------------------------------------------------------------|----|

| Table 2.2 | Procedures to deconvolute 100-link distribution into 1-link distribution.              |    |

|           | The method for data analysis follows [Nelson, 1990].                                   | 56 |

| Table 2.2 | The $t_{50}$ and $\sigma$ of intrinsic failures for N = 2, 10 and 100, and the         |    |

|           | deconvolution to $N = 1$ with two methods. CP: conditional probabilities;              |    |

|           | WLA: weakest link approximation.                                                       | 60 |

| Table 2.4 | Median value and standard deviation of $R_{step}$ and $R_{slope}$ for $N = 2$ , 10 and |    |

|           | 100                                                                                    | 63 |

| Table 3.1 | Summary of Failure time and critical current density for void nucleation               |    |

|           | and void growth.                                                                       | 92 |

| Table 4.1 | Temperature effect on $Z^*$ and electron wind force for different                      |    |

|           | technology nodes                                                                       | 30 |

# **List of Figures**

| Figure1.1  | SEM image of Intel 32nm interconnects (a) from metal-1 to metal-8 and           |     |

|------------|---------------------------------------------------------------------------------|-----|

|            | (b) metal-9 to Cu bump. [Brain et al., 2009]                                    | 3   |

| Figure1.2  | Schematic diagrams of (a) conventional RIE process for Al                       |     |

|            | interconnects and (b) damascene process for Cu interconnects                    | 7   |

| Figure 1.3 | Schematic of the collisions between the electron wind and an metal ion.         |     |

|            | With the electric field E, electrons collide with metal atoms in the            |     |

|            | electron flow direction resulting in EM phenomenon.                             | 8   |

| Figure 1.4 | Schematic of major diffusion pathways in Cu interconnects                       | 0   |

| Figure 1.5 | Schematic showing flux divergence sites in a Cu interconnect [Ogawa et          |     |

|            | al., 2002]                                                                      | 0   |

| Figure 1.6 | Resistance trace for EM of Cu interconnects including a flat region, an         |     |

|            | abrupt jump and a gradual increase region                                       | . 1 |

| Figure 1.7 | Normalized EM lifetime as function of critical void dimensions for              |     |

|            | various technology generations. [Hu et al., 2006]                               | 3   |

| Figure 1.8 | Evolution of $J_{max}$ (from device requirement) and $J_{EM}$ (from targeted EM |     |

|            | lifetime). [ITRS, 2011]                                                         | 4   |

| Figure 1.9 | Schematic showing that narrower lines are more sensitive to process             |     |

|            | variations. (a) 100nm wide line with a 10nm square notch; (b) 30nm line         |     |

|            | with a 10nm square notch.                                                       | .7  |

| Figure 2.1 | (a) Schematic showing voids formed at weak Cu/cap interface. (b) TEM            |     |

|            | image showing an initial void formed close to the interface [Zhang,             |     |

|            | 2010]                                                                           | 21  |

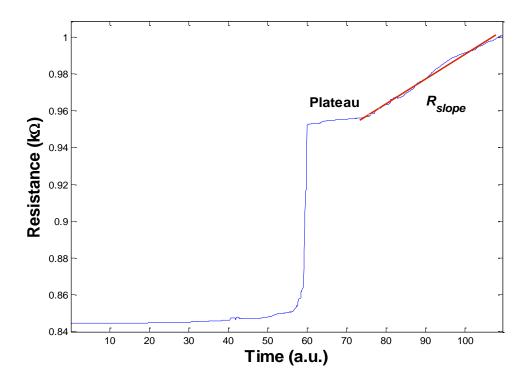

| Figure 2.2  | Typical EM resistance traces with definition of three Stages and the           |    |

|-------------|--------------------------------------------------------------------------------|----|

|             | parameters $R_{step}$ and $R_{slope}$ .                                        | 22 |

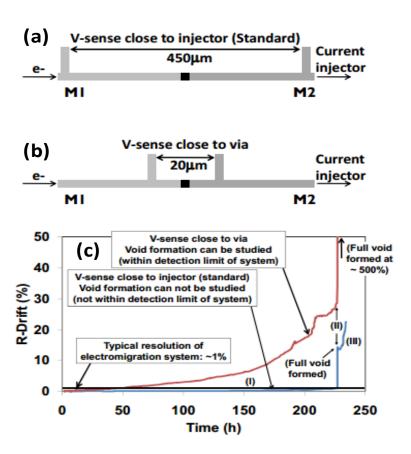

| Figure 2.3  | (a) Standard EM test structure with the voltage-senses close to the            |    |

|             | current injector; (b) New local sense test structure with voltage-sensors      |    |

|             | close to via; (c) Typical EM resistance traces when sensing at the             |    |

|             | injector/local senses. [Croes et al., 2011]                                    | 24 |

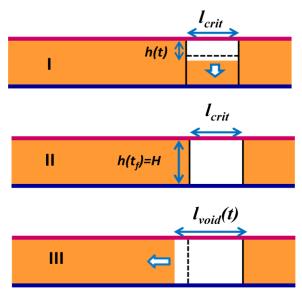

| Figure 2.4  | Schematics for the growth process of a rectangular void.                       | 25 |

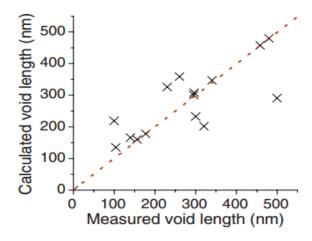

| Figure 2.5  | Comparison of the calculated and physically measured void                      |    |

|             | length.[Doyen et al., 2008]                                                    | 27 |

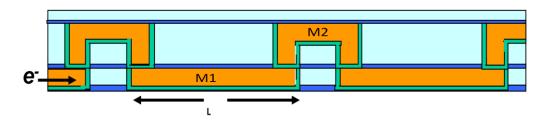

| Figure 2.6  | Schematic of the cross-section of a multi-link EM test structure               | 30 |

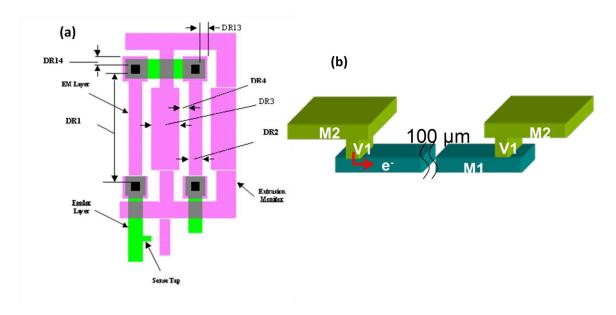

| Figure 2.7  | (a) Layout of the 2-link EM structure tested. (b) 3D schematic of              |    |

|             | M2V1M1 downstream test configuration.                                          | 31 |

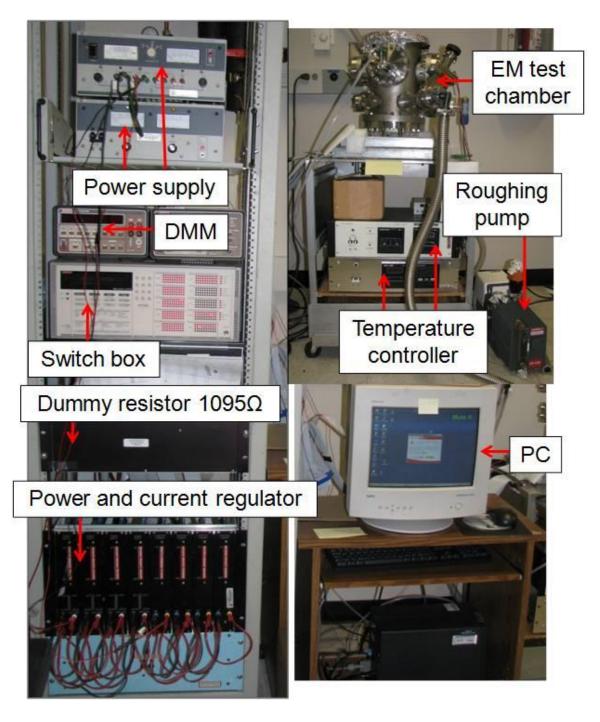

| Figure 2.8  | Package-level EM test system.                                                  | 33 |

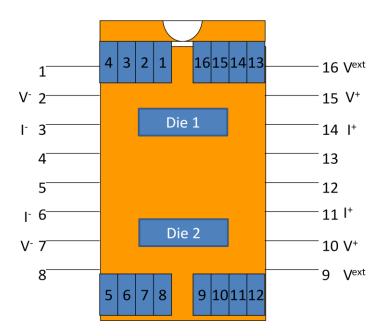

| Figure 2.9  | 16-pin DIP package with two dies attached                                      | 34 |

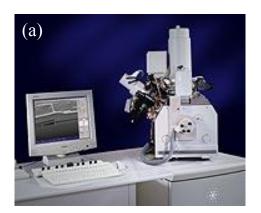

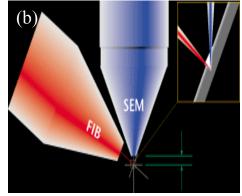

| Figure 2.10 | (a) FEI Strata $^{\text{TM}}$ DB235 dual beam FIB/SEM system and (b) schematic |    |

|             | illustration of the configuration of the two beams (52° in between)            | 35 |

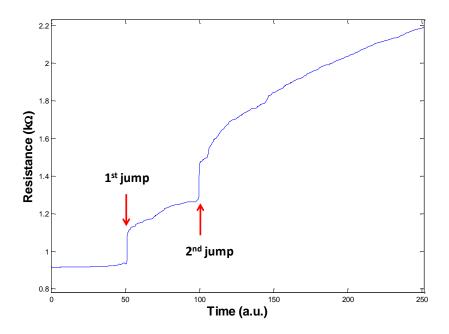

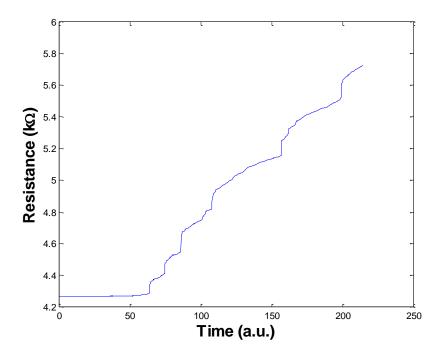

| Figure 2.11 | Typical resistance trace for 2-link structure showing two resistance           |    |

|             | jumps                                                                          | 37 |

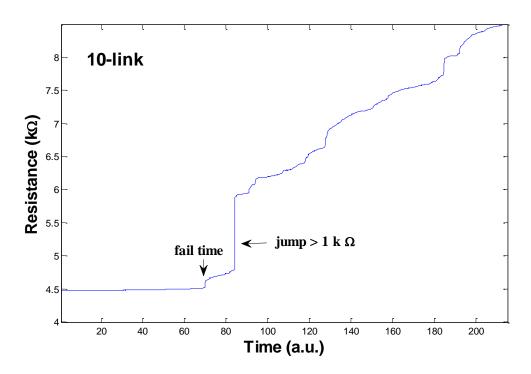

| Figure 2.12 | Typical resistance trace for 10-link structure.                                | 37 |

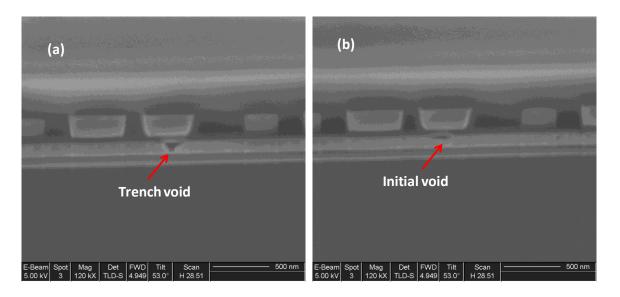

| Figure 2.13 | SEM images of void formed. (a) trench type void fails the line; (b) initial    |    |

|             | long slit type void formed at the Cu/cap interface.                            | 38 |

| Figure 2.14 | A plateau followed by a gradual increase region in a trace.                    | 39 |

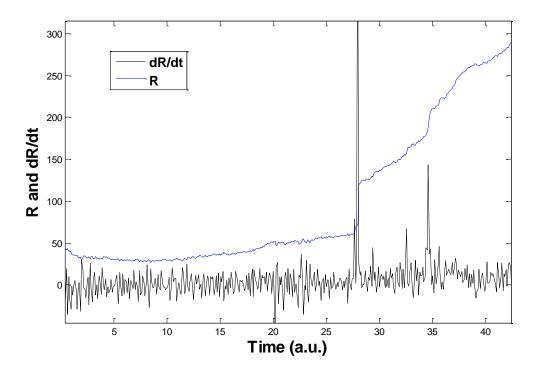

| Figure 2.15 | Noisy resistance trace with its time differentiation.                          | 40 |

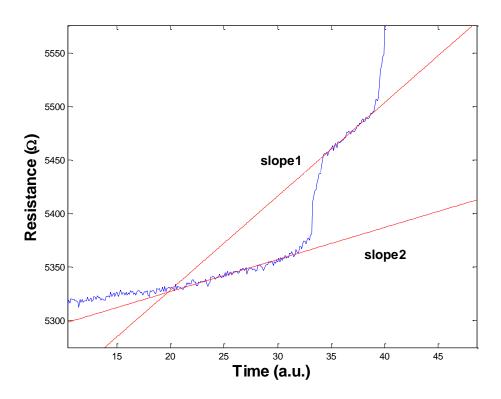

| Figure 2.16 | The large amount of small voids formation cause resistance increase                      |    |

|-------------|------------------------------------------------------------------------------------------|----|

|             | before line failure. The $R_{slope}$ is the difference between slope1 and                |    |

|             | slope2                                                                                   | 41 |

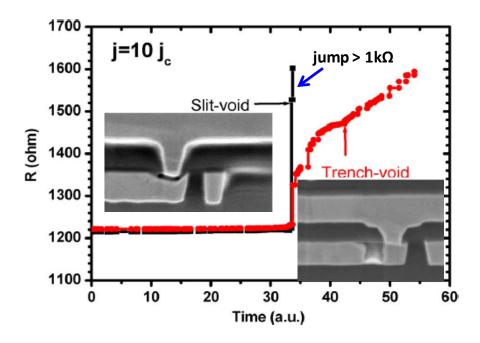

| Figure 2.17 | Big resistance jump observed in a 10-link structure                                      | 42 |

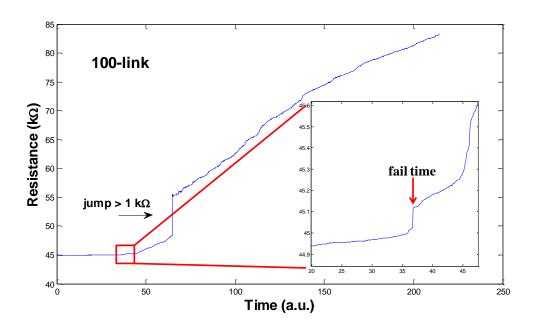

| Figure 2.18 | Big resistance jump observed in a 100-link structure.                                    | 43 |

| Figure 2.19 | Big resistance jump ( $> 1 \text{ k}\Omega$ ) corresponds to a slit-void. [Oates et al., |    |

|             | 2009b]                                                                                   | 43 |

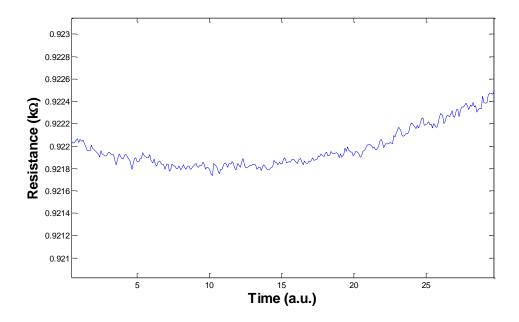

| Figure 2.20 | Initial resistance decrease in an EM resistance versus time trace                        | 48 |

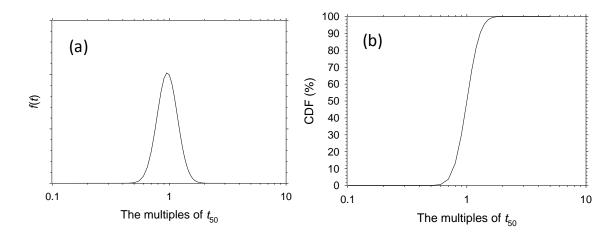

| Figure 2.21 | (a) PDF and (b) CDF plot of a lognormal distribution with $\sigma$ = 0.2. [Lee,          |    |

|             | 2003]                                                                                    | 50 |

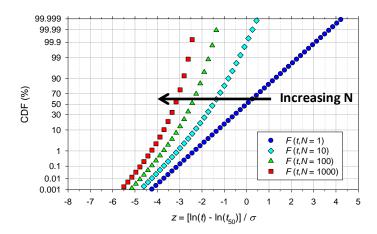

| Figure 2.22 | CDF plots for N-link structures with N=1, 10, 100, 1000. [Ogawa et al.,                  |    |

|             | 2001]                                                                                    | 51 |

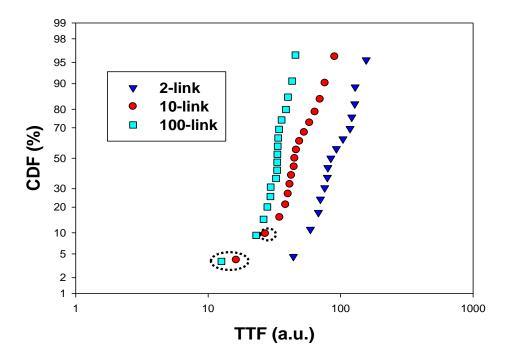

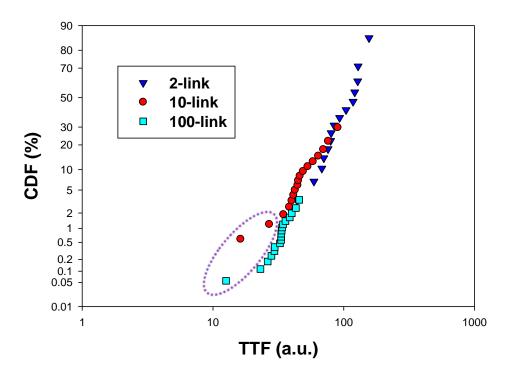

| Figure 2.23 | Experimental CDF plots for multi-link structures with N=2, 10, 100. The                  |    |

|             | 3 data points in the dotted ellipses are probably failed in a different                  |    |

|             | mode                                                                                     | 52 |

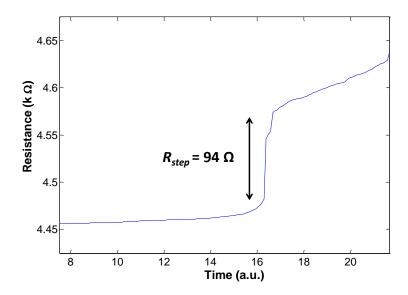

| Figure 2.24 | Resistance trace for the earliest failure detected for 10-link structures.               |    |

|             | The resistance jump is 94 $\Omega$ .                                                     | 53 |

| Figure 2.25 | Monte-Carlo simulations for a bi-modal failure with $N=1,10$ and $100.$                  |    |

|             | The strong mode parameters are $t_{50} = 500$ hours and $\sigma = 0.5$ . The weak        |    |

|             | mode parameters are $t_{50} = 50$ hours and $\sigma = 0.3$ . The probability for         |    |

|             | weak mode is set as 1%.                                                                  | 54 |

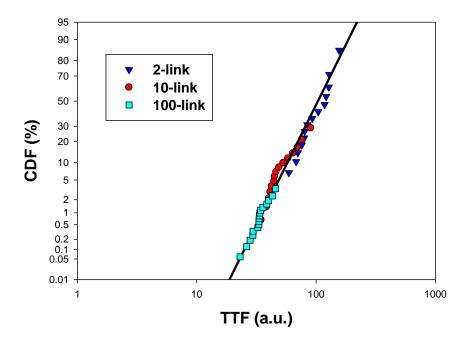

| Figure 2.26 | Deconvoluted failure time distribution for $N = 2$ , 10 and 100,                         |    |

|             | representing a single link distribution. The three data points in the dotted             |    |

|             | ellipse clearly appear to be a different failure mode                                    | 57 |

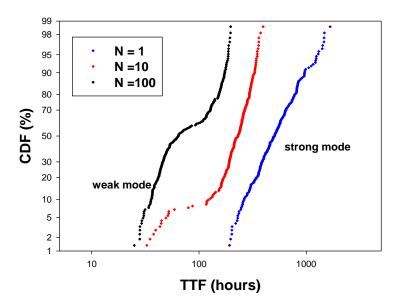

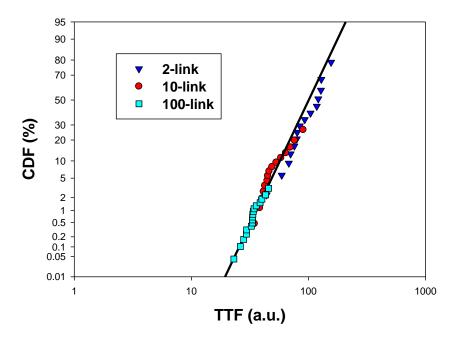

| Figure 2.27 | The failure time distribution for $N = 2$ , 10 and 100 in the intrinsic failure    |    |

|-------------|------------------------------------------------------------------------------------|----|

|             | mode are deconvoluted into $N = 1$ based on CP. They follow a single               |    |

|             | lognormal distribution. Deconvolution is performed based on                        |    |

|             | conditional probabilities.                                                         | 58 |

| Figure 2.28 | The failure time distribution for $N = 2$ , 10 and 100 in the intrinsic failure    |    |

|             | mode are deconvoluted into $N = 1$ based on WLA. They follow a single              |    |

|             | lognormal distribution. Deconvolution is performed based on WLA                    | 59 |

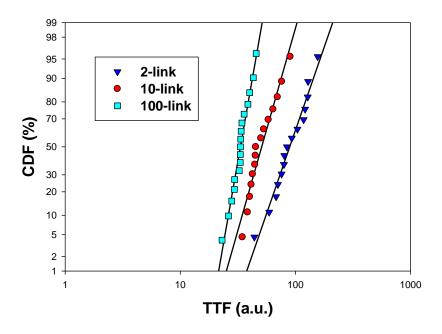

| Figure 2.29 | Intrinsic failure time distribution for multi-link structure with $N = 2$ , 10     |    |

|             | and 100                                                                            | 60 |

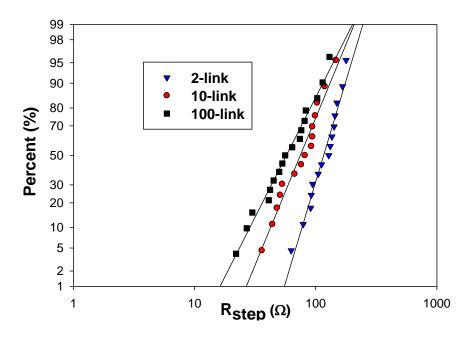

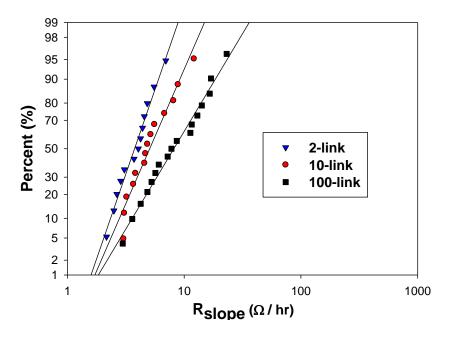

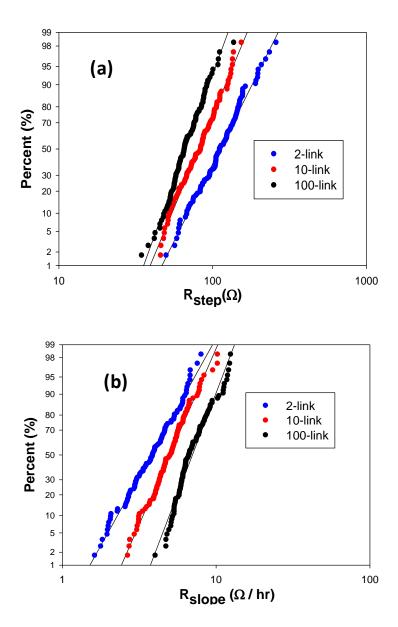

| Figure 2.30 | $R_{step}$ distribution for multi-link structures with $N = 2$ , 10 and 100        | 61 |

| Figure 2.31 | $R_{slope}$ distribution for multi-link structures with $N = 2$ , 10 and 100       | 62 |

| Figure 2.32 | Monte-Carlo simulation of $R_{step}$ and $R_{slope}$ distributions for multi-link  |    |

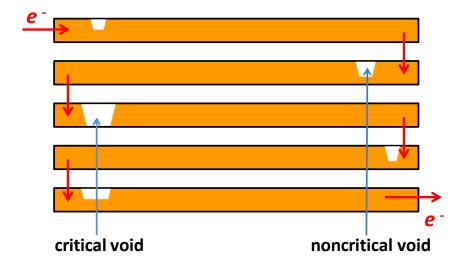

|             | structures with link number $N = 2$ , 10 and 100                                   | 64 |

| Figure 2.33 | Schematic showing small void formation in lines of multi-link structure.           |    |

|             | The critical void causes line failure. While the noncritical void causes           |    |

|             | small resistance increase.                                                         | 66 |

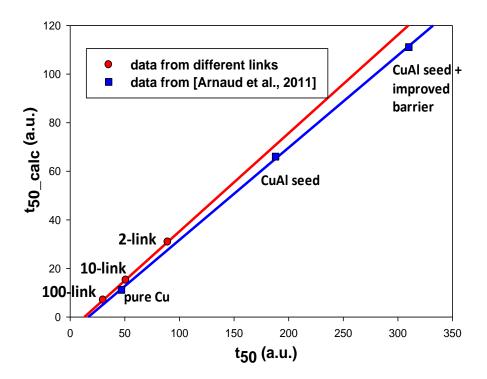

| Figure 2.34 | Comparison between the calculated median failure time $t_{50\_calc}$ based on      |    |

|             | $R_{step}/R_{slope}$ and the measured median failure time $t_{50}$ .               | 67 |

| Figure 2.35 | (a) Extrapolation of the resistance trace to define incubation time $t_0$ for      |    |

|             | dopants. [Arnaud et al., 2011] (b) Extrapolation performed on a                    |    |

|             | resistance trace of the multi-link samples.                                        | 69 |

| Figure 2.36 | Stress evolution of a void-free metal line under EM. [Hau-Riege, 2002]             | 70 |

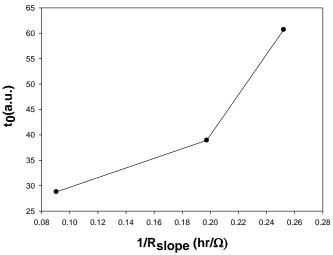

| Figure 2.37 | The plot of $t_0$ vs $1/R_{slope}$ showing void nucleation time cannot explain the |    |

|             | observed phenomenon.                                                               | 70 |

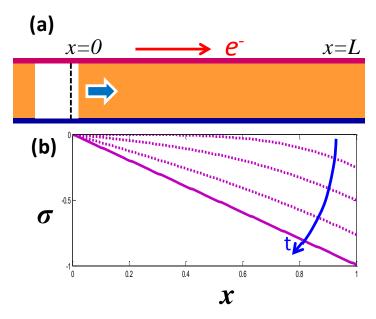

| Figure 3.1  | (a) Schematic for a metal line with a void at cathode; (b) stress evolution                 |    |

|-------------|---------------------------------------------------------------------------------------------|----|

|             | in the metal line as shown in (a).                                                          | 76 |

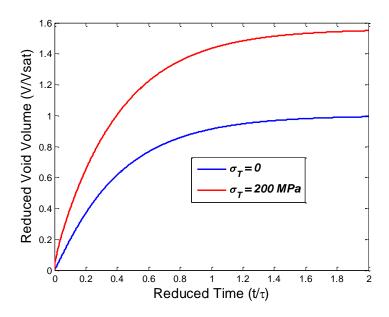

| Figure 3.2  | Void growth in the Korhonen model with initial stress 0 and 200 MPa                         | 78 |

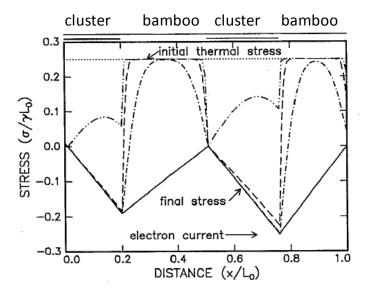

| Figure 3.3  | Cluster and bamboo segments in a metal line and the stress evolution in                     |    |

|             | each segment. [Korhonen et al., 1993a]                                                      | 79 |

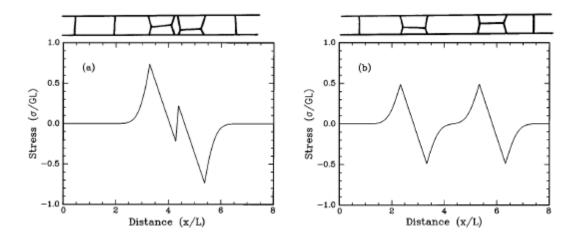

| Figure 3.4  | Stress profiles for an interacting (a) and non-interacting (b) cluster pairs.               |    |

|             | [Brown et al., 1995b]                                                                       | 81 |

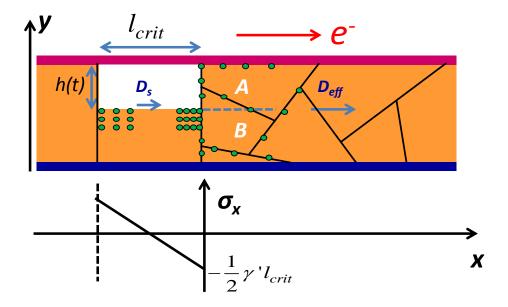

| Figure 3.5  | Schematic of void growth at Stage I and stress distribution inside the                      |    |

|             | void segment.                                                                               | 83 |

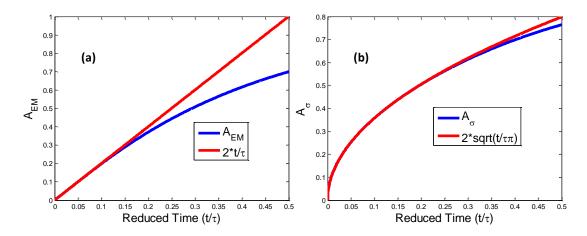

| Figure 3.6  | Within a short time scale, $A_{EM}$ can be approximated by $2*t/\tau$ (a), and $A_{\sigma}$ |    |

|             | can be approximated by $(2/\sqrt{\pi})*\sqrt{t/\tau}$ (b)                                   | 87 |

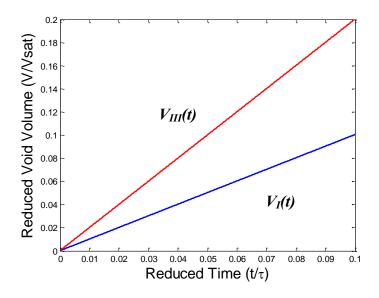

| Figure 3.7  | Void volume change with time at Stage I (lower curve) and Stage III                         |    |

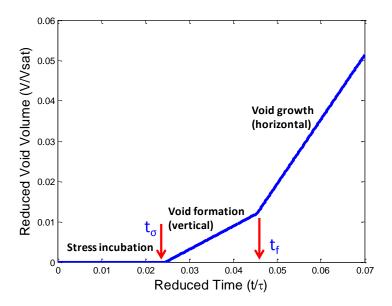

|             | (upper curve) shows a slope ratio of 0.5 when thermal stress is 0                           | 88 |

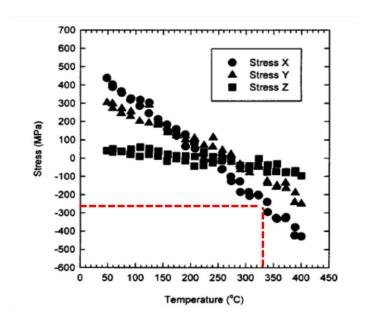

| Figure 3.8  | Thermal stress components of a Cu/low-k interconnect measured by                            |    |

|             | XRD at different temperatures. X is in Cu line length direction. [Rhee et                   |    |

|             | al., 2003]                                                                                  | 89 |

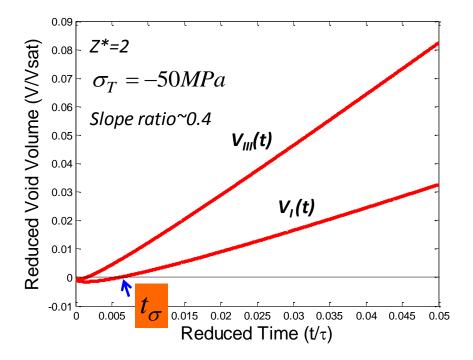

| Figure 3.9  | Void volume change with time at Stage I (lower curve) and III (upper                        |    |

|             | curve) under compressive line stress.                                                       | 90 |

| Figure 3.10 | Simplified model of void growth at different stages.                                        | 91 |

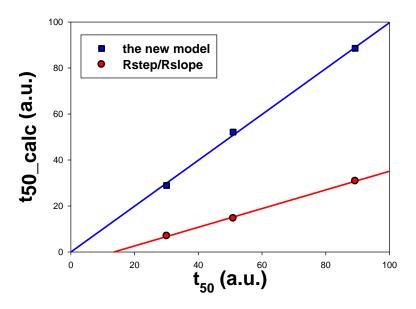

| Figure 3.11 | Comparison between calculated $t_{50}$ based on the new model and                           |    |

|             | measured t <sub>50</sub> .                                                                  | 93 |

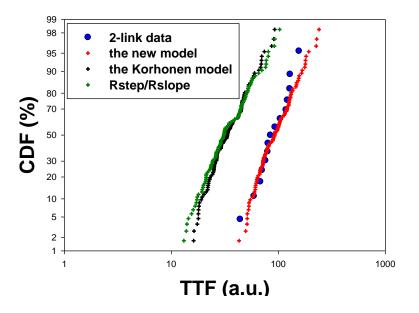

| Figure 3.12 | Failure time statistics simulation using $R_{step}$ and $R_{slope}$ distributions           | 94 |

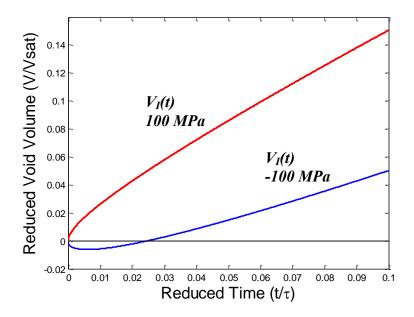

| Figure 3.13 | Comparison of initial void growth under tensile (upper curve) and                           |    |

|             | compressive stress (lower curve).                                                           | 96 |

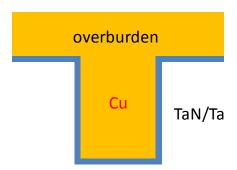

| Figure 3.14 | Schematic of the cross-section of a simulated Cu line with the            |

|-------------|---------------------------------------------------------------------------|

|             | overburden and liner. 98                                                  |

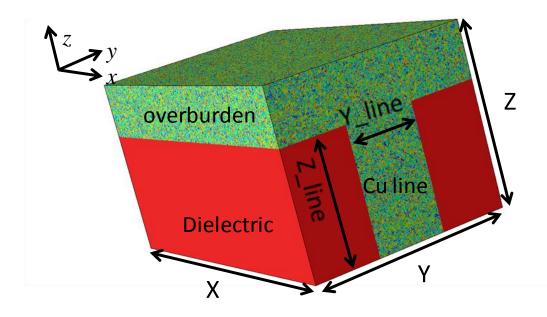

| Figure 3.15 | A simulated Cu line structure with overburden and dielectric              |

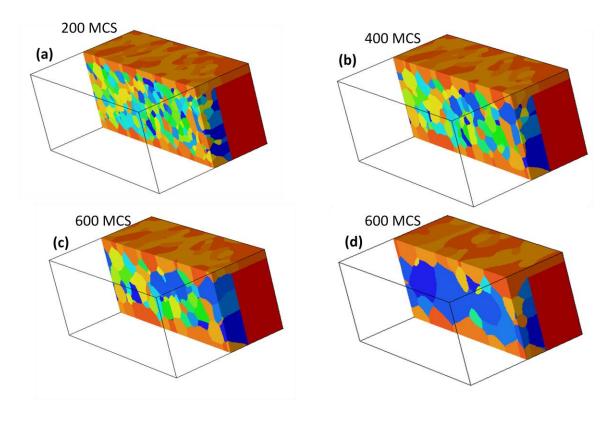

| Figure 3.16 | Different cross-sections of a simulated Cu line. 500x300x200x100x180;     |

|             | 200 MCS. 102                                                              |

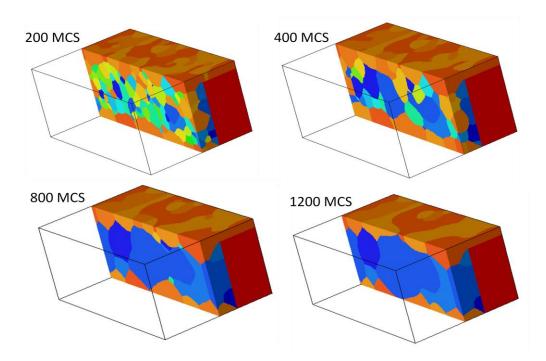

| Figure 3.17 | Time evolution of grain growth in a Cu line. 500x300x260x100x180; 50      |

|             | MCS                                                                       |

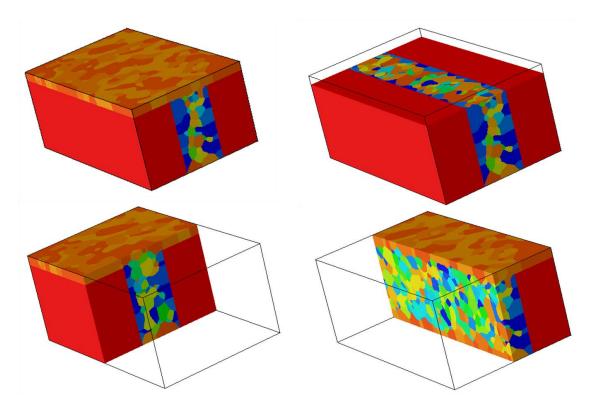

| Figure 3.18 | (a), (b) and (c) Time evolution of grain growth in a Cu line with         |

|             | dimension 500x300x200x100x180. (d) A Cu line with dimension               |

|             | 350x210x140x70x126, which is 0.7X scaled from those in (a), (b) and       |

|             | (c). 104                                                                  |

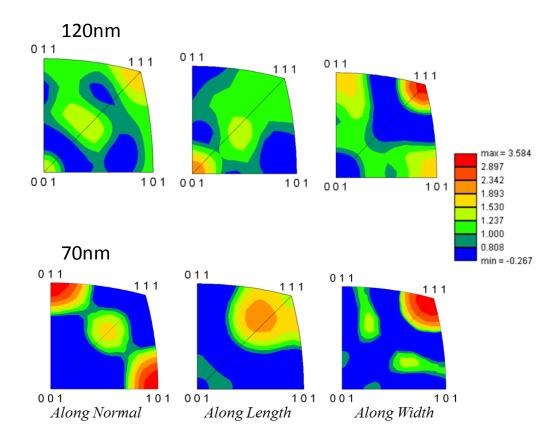

| Figure 3.19 | Inverse pole figures for a 120nm wide and a 70nm wide Cu interconnect     |

|             | line measured by precession microscopy with TEM. [Kameswaran,             |

|             | 2011]                                                                     |

| Figure 3.20 | Grain size evolutions for grains at trench bottom. Dimensions             |

|             | 350x210x140x70x126                                                        |

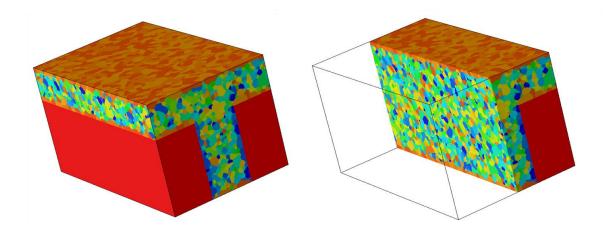

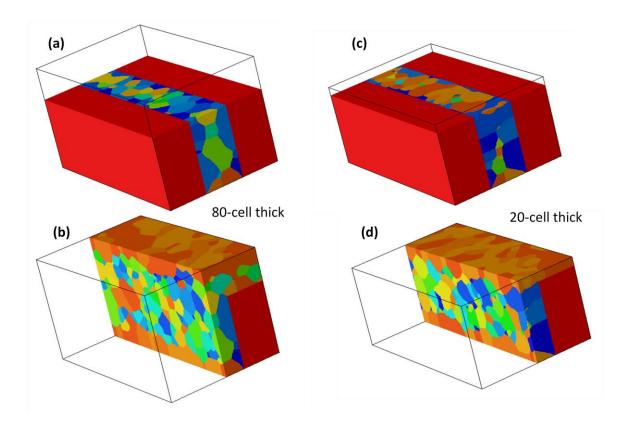

| Figure 3.21 | Effect of overburden thickness to grain growth. The dimensions for (a)    |

|             | and (b) are 500x300x260x100x180. The dimensions for (c) and (d) are       |

|             | 500x300x200x100x180. The only difference between two structures is        |

|             | the overburden thickness: one 80-cell thick, the other 20-cell thick. 500 |

|             | MCS for both simulations. 108                                             |

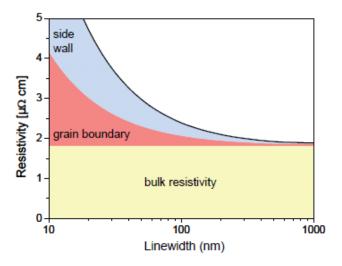

| Figure 4.1  | Increase of Cu resistivity as the scaling of line dimension due to grain  |

|             | boundary and side wall scattering. [ITRS, 2009]                           |

| Figure 4.2  | Schematic showing the scattering between electrons and atoms causes                    |

|-------------|----------------------------------------------------------------------------------------|

|             | both electrical resistivity and EM. 113                                                |

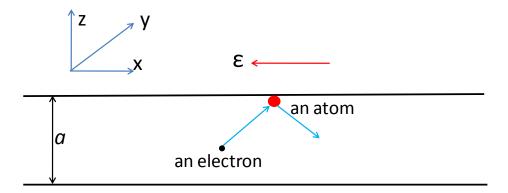

| Figure 4.3  | Schematic of the model for a thin film with Cartesian coordinates 115                  |

| Figure 4.4  | (a) Size factor $S$ and (b) electron wind force for a thin film as a function          |

|             | of film thickness $a$ normalized by electron mean free path $\lambda$                  |

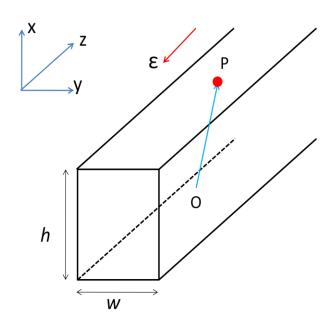

| Figure 4.5  | Schematic of the model for a rectangular line with Cartesian                           |

|             | coordinates. 119                                                                       |

| Figure 4.6  | Schematics showing the line cross-section divided into 4 subsections for               |

|             | calculation of the size factor for electron wind force                                 |

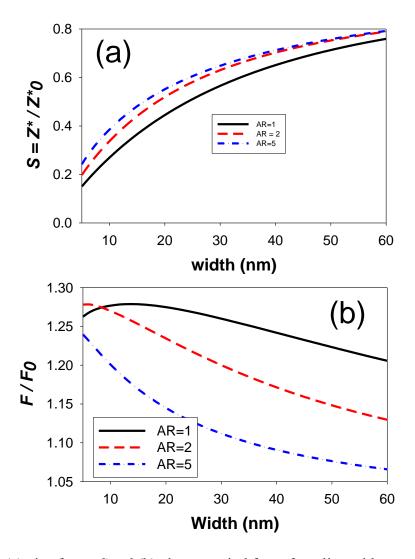

| Figure 4.7  | (a) size factor $S$ and (b) electron wind force for a line with rectangular            |

|             | cross-section as a function of line width for lines with different aspect              |

|             | ratios (ARs). 122                                                                      |

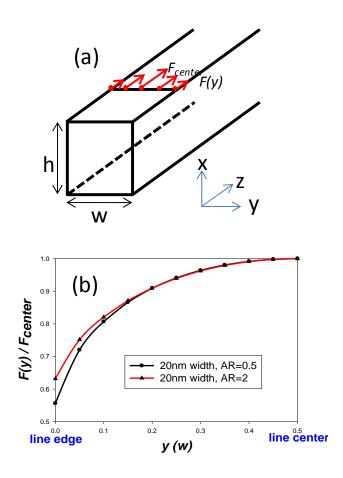

| Figure 4.8  | (a) Schematic showing the non-uniform distribution of electron wind                    |

|             | force along line width direction. (b) Plot of electron wind force at                   |

|             | different locations along line width for AR 0.5 and 2. $p=0$                           |

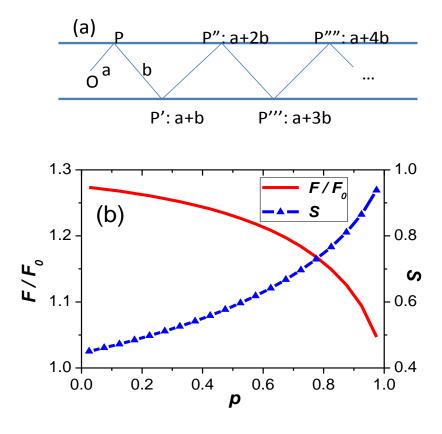

| Figure 4.9  | (a) Schematic showing successive reflections of electrons at interfaces.               |

|             | (b) $F/F_{\theta}$ and $S$ as a function of specularity parameter $p$ for a line width |

|             | 20nm and aspect ratio 2. 125                                                           |

| Figure 4.10 | A Cu line composed of multiple grains, which provide scattering at grain               |

|             | boundaries in addition to interfaces. 126                                              |

| Figure 4.11 | (a) Size factor $S$ and (b) electron wind force for a rectangular line as a            |

|             | function of line width taking into account interface scattering and grain              |

|             | boundary scattering. $p=0.5, R=0.4, AR=1, D=3*w$                                       |

| Figure 4.12 | Cu resistivity as a function of temperature. [Sun et al., 2010]                        |

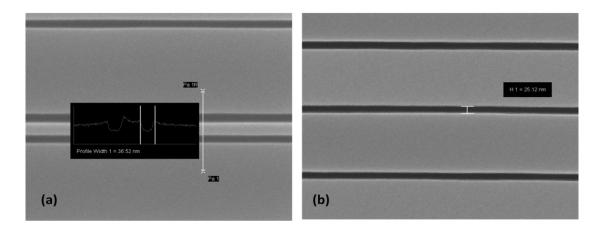

| Figure 5.1  | (a) Common model structure with rectangular cross-section and smooth       |     |

|-------------|----------------------------------------------------------------------------|-----|

|             | side walls; (b) Cu interconnect line cross-section showing a taped profile |     |

|             | [Cabral et al., 2010]; (c) Cr line fabricated showing LER                  | 134 |

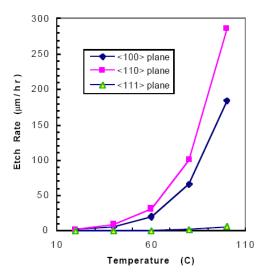

| Figure 5.2  | Si etching rates in KOH with respect to temperature for different          |     |

|             | crystalline planes. [Marchetti et al., 1998]                               | 135 |

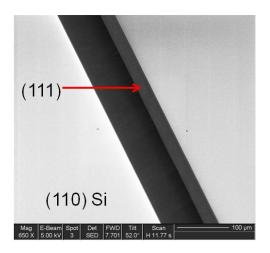

| Figure 5.3  | Si trench etched on an (110) wafer in TMAH solution. [Wu et al.,           |     |

|             | 2011]                                                                      | 136 |

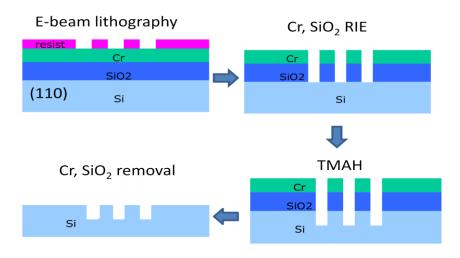

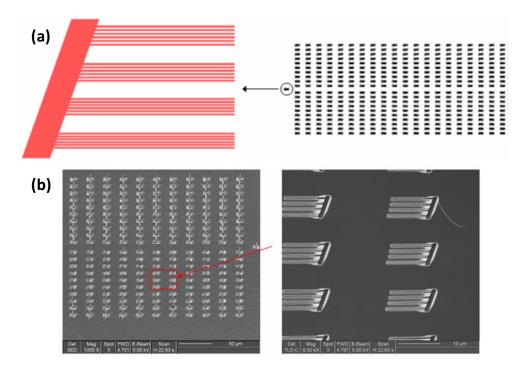

| Figure 5.4  | Process flow for fabrication of Si nanolines with EBL and TMAH             |     |

|             | etching                                                                    | 137 |

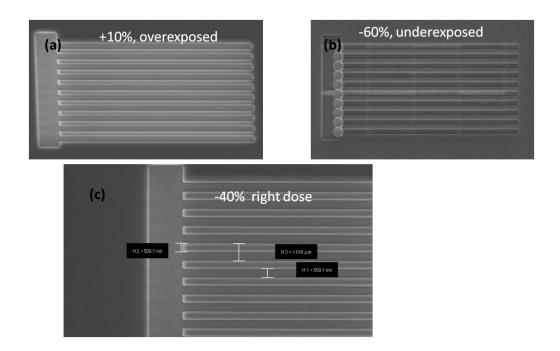

| Figure 5.5  | An example of dose test for EBL                                            | 138 |

| Figure 5.6  | (a) The designed angle alignment test pattern. An array contains 401       |     |

|             | patterns. The angle between 2 neighboring patterns is 0.01°. (b) The       |     |

|             | alignment test pattern after TMAH etching.                                 | 139 |

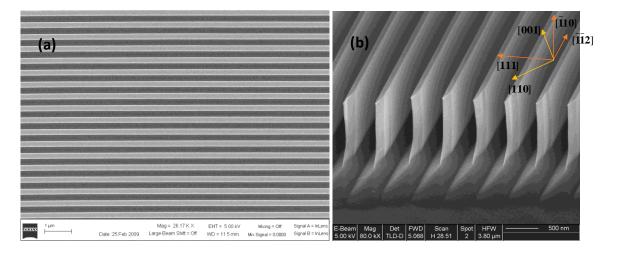

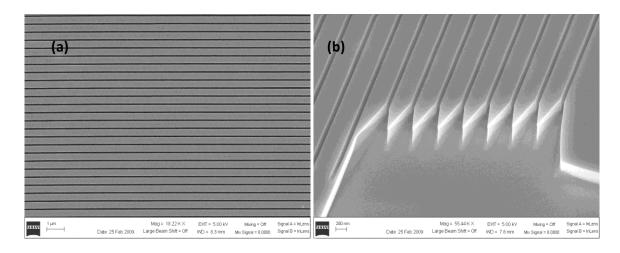

| Figure 5.6  | (a) Plan view and (b) side view (52°) of Si nanolines fabricated by EBL    |     |

|             | and AWE                                                                    | 140 |

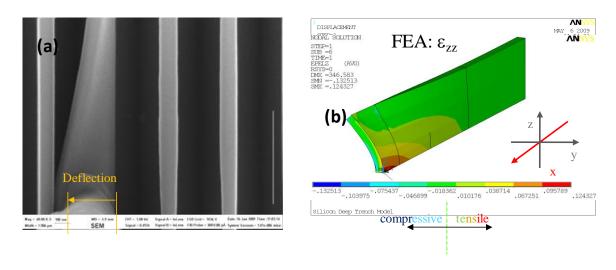

| Figure 5.7  | (a) Si nanoline deflected by a tungsten tip; (b) FEA shows the strain      |     |

|             | distribution in a Si nanoline when deflected                               | 141 |

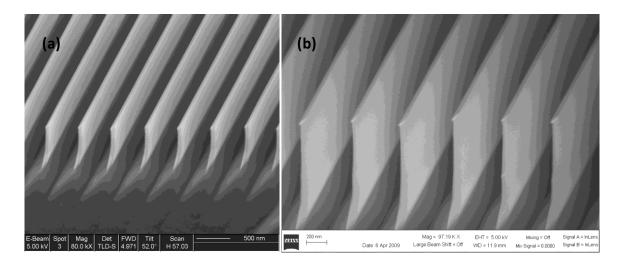

| Figure 5.8  | (a) 30nm wide Si nanolines; (b) Si nanolines with AR of 40                 | 141 |

| Figure 5.9  | (a) Plan view and (b) side view (tilt = 30°) of Si nanotrenches fabricated |     |

|             | by EBL and AWE                                                             | 142 |

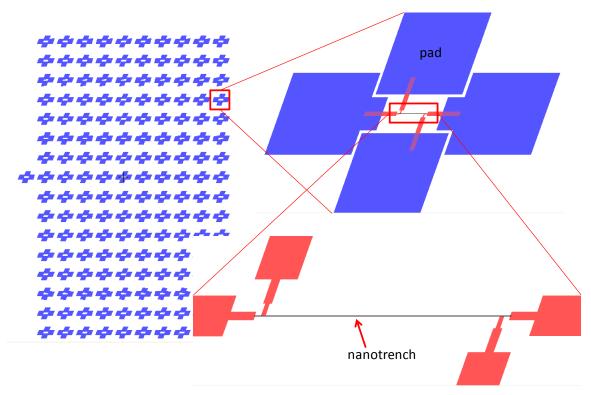

| Figure 5.10 | Designed pattern for an array of nanotrenches integrated with contact      |     |

|             | pads1                                                                      | 143 |

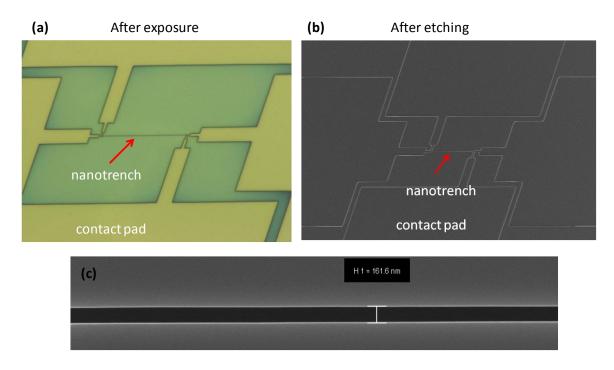

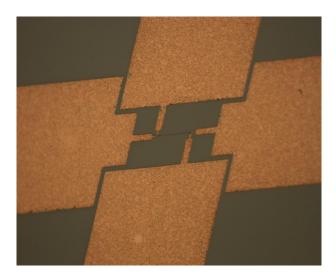

| Figure 5.12 | (a) Optical microscopy (OM) image of a nanotrench with contact pads            |

|-------------|--------------------------------------------------------------------------------|

|             | after resist development; (b) SEM image of a Si nanotrench with contact        |

|             | pads after etching; (c) SEM image of the Si nanotrench                         |

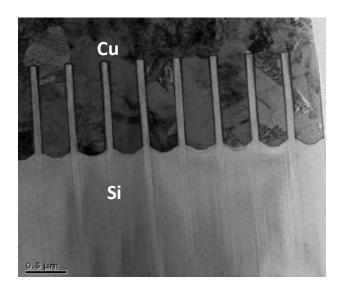

| Figure 5.13 | TEM image of the cross-section of Si nanotrenches deposited with ECD           |

|             | Cu                                                                             |

| Figure 5.14 | OM image of a Cu line deposited in the Si nanotrench connected with            |

|             | contact pads. The image was taken after Cu CMP                                 |

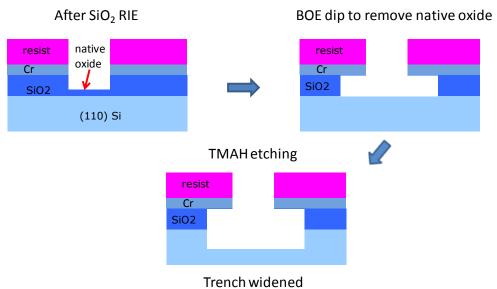

| Figure 5.15 | Process flows showing the trench widening effect in Si nanotrench              |

|             | fabrication. 146                                                               |

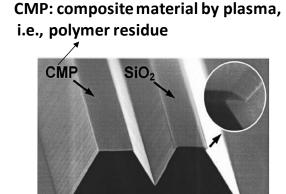

| Figure 5.16 | SEM image of mesas on (100) Si anisotropically etched by EPW. Both             |

|             | the polymer residue (CMP) and SiO <sub>2</sub> work as etch masks. [Normand et |

|             | al., 2001]                                                                     |

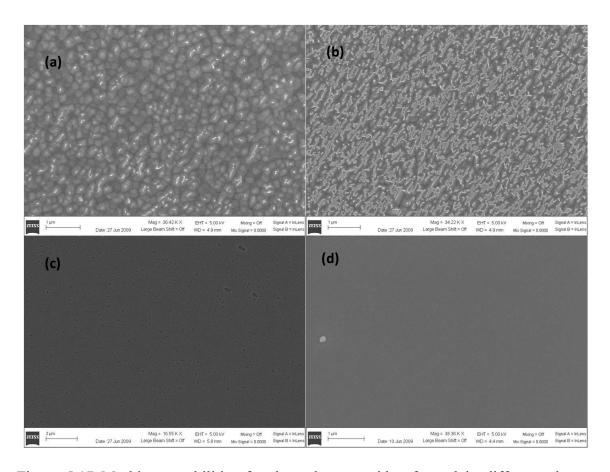

| Figure 5.17 | Masking capabilities for the polymer residue formed in different plasma        |

|             | conditions in the TMAH solution. The mask protects Si underneath               |

|             | better and better from (a) to (d).                                             |

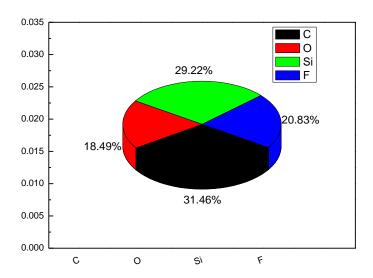

| Figure 5.18 | Chemical composition analysis of the polymer residue layer by XPS 150          |

| Figure 5.19 | (a) Cross-sectional SEM image of microtrenching effect; (b) mechanism          |

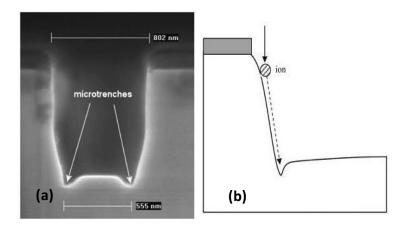

|             | of microtrenching—sidewall reflection of ions. [Cui, 2008]                     |

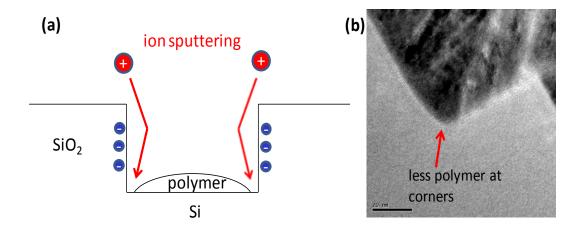

| Figure 5.20 | (a) Schematic of sidewall charging leading to more ion sputtering near         |

|             | trench corners; (b) TEM cross-sectional view of the distribution of            |

|             | polymer residue layer in a trench after SiO <sub>2</sub> RIE                   |

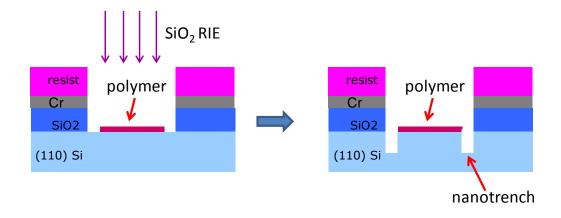

| Figure 5.21 | Process to fabricate nanotrenches by using the polymer residue as SSM 152      |

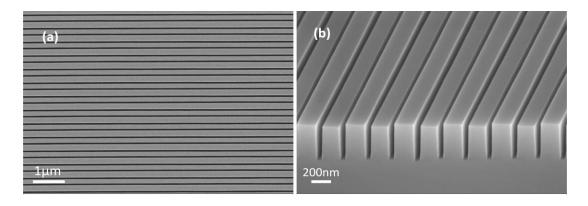

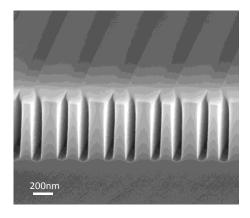

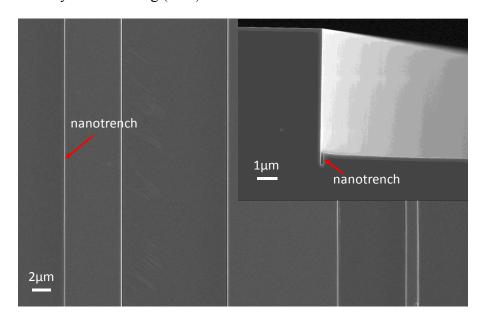

| Figure 5.22 | Nanotrenches fabricated by SSM technique. Trench width is 60nm. (a)            |

|             | Plane view; (b) Side view (tilt = 45°).                                        |

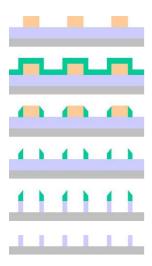

| Figure 5.23 Process flow of self-aligned double patterning: first pattern; deposition; |

|----------------------------------------------------------------------------------------|

| spacer formation by etching; first pattern removal; etching with spacer                |

| mask; final pattern                                                                    |

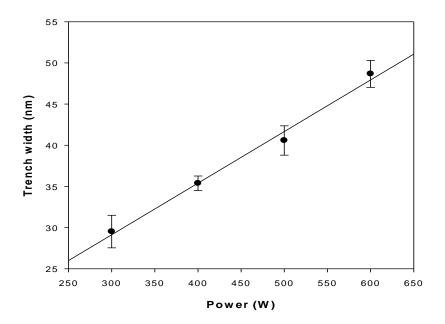

| Figure 5.24 Control the width of Si nanotrenches by SiO <sub>2</sub> RIE power         |

| Figure 5.25 Nanotrenches with (a) 35nm width and (b) 25nm width                        |

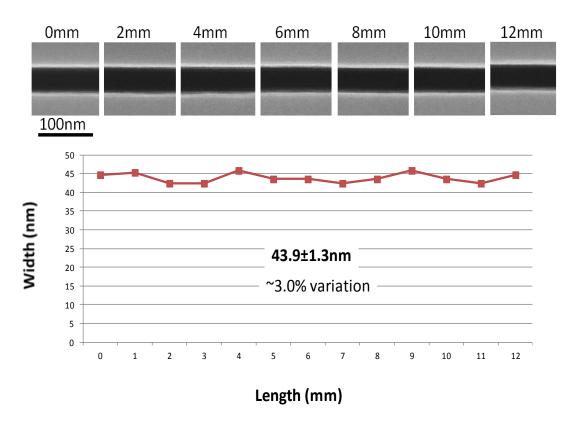

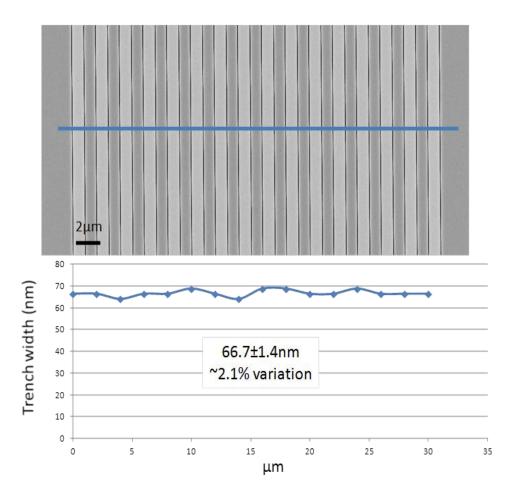

| Figure 5.26 Width uniformity along a single nanotrench. 157                            |

| Figure 5.27 Width uniformity along an array of nanotrenches. 158                       |

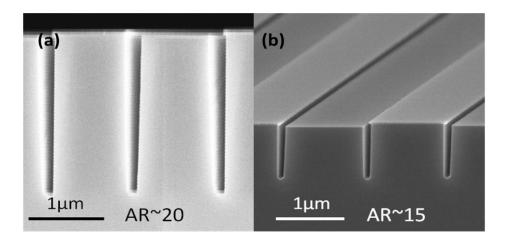

| Figure 5.28 (a) Cross-sectional view of nanotrenches with AR~20; (b) Side view of      |

| nanotrenches with AR $\sim$ 15 (tilt = 45°)                                            |

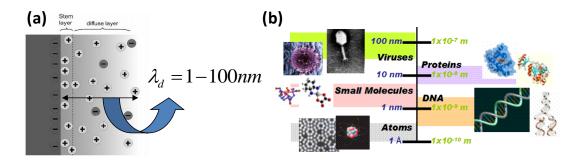

| Figure 5.29 (a) Schematic of the electrical double layer at solid/liquid interface     |

| [Abgrall et al., 2008]; (b) Size range of bio-molecules                                |

| Figure 5.30 Nanotrenches sealed by PECVD SiO <sub>2</sub> to form nanochannels         |

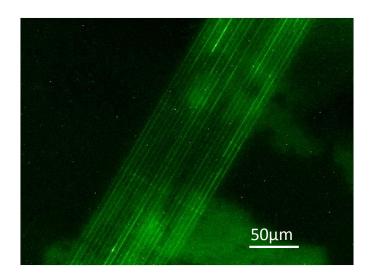

| Figure 5.31 Fluorescence microscopy image of nanochannels flowed with solutions 161    |

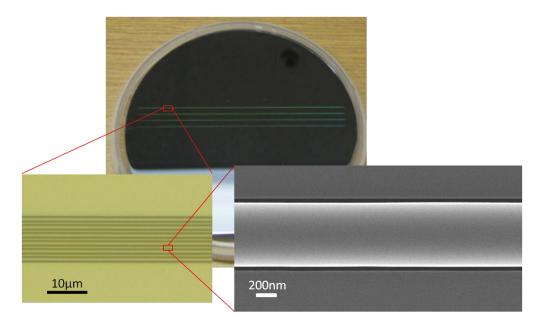

| Figure 5.32 Arrays of ultra-long (9cm) nanotrenches. 163                               |

| Figure 5.33 Nanotrenches fabricated by using a conventional optical lithography. The   |

| inset is a cross-sectional view                                                        |

### **Chapter 1: Introduction**

This chapter introduces the general background for the development of Cu interconnects. The increased complexity of the interconnect structures necessitates the studies of long term reliability such as electromigration (EM). Cu interconnects have unique EM characteristics originated from the damascene structure and its fabrication process. This chapter also provides a brief introduction of the EM phenomenon and the challenges to Cu EM reliability raised by interconnect scaling. This motivates the research work in this dissertation. The scope of the dissertation is outlined at the end of this chapter.

#### 1.1 GENERAL BACKGROUND

For several decades, integrated circuit (IC) has distinguished itself by the rapid pace in scaling. Following Moore's law, the density of transistors on ICs doubles every 18 to 24 months. To meet this requirement, dimensional scaling occurs both in front-end-of-line (FEOL), where transistors locate, and back-end-of-line (BEOL), where metal interconnects are made to connect transistors. BEOL interconnects perform essential functions in an IC-system by providing clock signals, electrical signals, power distribution and ground distribution.

The scaling of ICs always comes with innovation of materials. The interconnect is no exception. When ICs were first produced, Al was used as interconnecting metallization due to its ease of deposition and etching. The resistivity of Al is 2.8  $\mu\Omega$ -cm, lower than that of most metals. The interconnect wires at that time were wide and thick and thus had low resistance. The resistance-capacitance (RC) delay of the Al interconnects was negligible compared to the switching delay of the transistors, also known as gate delay. As the device channel length shrinks during scaling, the transistors switch faster and faster. However, the interconnect wires become narrower, driving up the resistance so that interconnect RC delay becomes the bottleneck for the chip performance. For that reason, Cu was introduced to replace Al interconnects by IBM in 1997 [Edelstein *et al.*, 1997, Rosenberg *et al.*, 2000]. Cu has a lower resistivity of 1.7  $\mu\Omega$ -cm, considerably lower than that of Al.

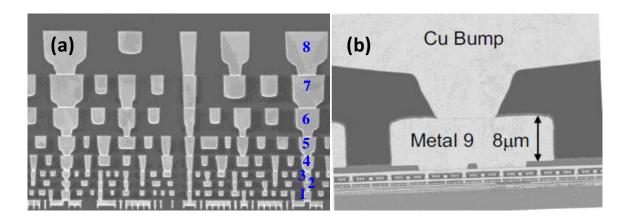

The Cu interconnects in the advanced ICs have highly complex hierarchical structures. As an example, Figure 1.1 shows scanning electron microscopy (SEM) images of the interconnects of an Intel's 32nm high performance logic chip, where the whole structure contains 9 metal levels. The overall metal wiring structure follows the reverse

scaling rule, where the lower-levels of the local interconnects employ thin Cu wires to match the size and pitch of the transistors in Si while wires with increasing dimensions are used in the upper-levels of global interconnects. Metallization following the reverse scaling rule is adopted to reduce the RC delay and power consumption.

Figure 1.1 SEM image of Intel 32nm interconnects (a) from metal-1 to metal-8 and (b) metal-9 to Cu bump. [Brain *et al.*, 2009]

As a result of the progressive scaling, billions of transistors and interconnects can now be packed into an advanced micro-chip. This poses increasing concern in the reliability of ICs. The failure of one out of billions of units in a micro-chip may cause the failure of the entire chip. The BEOL reliability is generally assessed by studying electromigration (EM), stress induced voiding (SIV) and time dependent dielectric breakdown (TDDB). With the aggressive scaling of metal line dimensions and density, EM and TDDB are becoming increasingly important reliability concerns. Chip package interaction (CPI) is also an important reliability problem if the full IC-system is considered. This dissertation studies the EM of Cu interconnects. The local interconnects in metal-1 (M1) and metal-2 (M2) levels are more subjected to EM damage due to much smaller dimensions and higher current density.

Compared to Al interconnects, Cu interconnects have the advantage of a higher resistance to EM. EM is a diffusion process, the activation energy of which scales with the melting temperature of the material. Cu has a higher melting point of 1083°C compared with Al of 660°C. At a given temperature, the diffusion in Cu is thus reduced compared with Al.

### 1.2 THE DAMASCENE PROCESS

Besides the improved performance of RC delay and EM, Cu has other properties very different from Al, which requires a different process to fabricate and to implement the interconnects. The processes and integration scheme in turn greatly affect the EM characteristics of Cu interconnects.

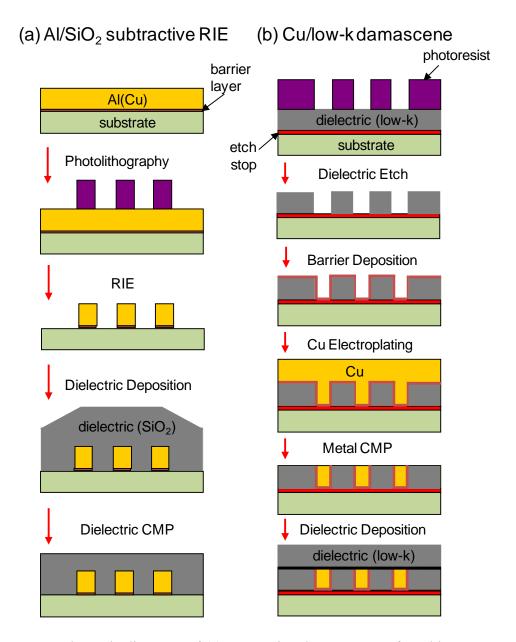

First of all, there is no good dry etch process for Cu due to the lack of volatile Cu compound at low temperature. A prerequisite requirement for the dry etch process is that the main etching byproducts should be volatile at low temperatures. For example, the chlorine plasma reacts with Al, forming AlCl<sub>3</sub>. AlCl<sub>3</sub> sublimates at 178°C [Plummer *et al.*, 2000], i.e., volatile at a low temperature. Ion bombardment can then easily remove AlCl<sub>3</sub> from the surface and pump it out of the system. Therefore, a subtractive reactive ion etching (RIE) process can be employed to fabricate the Al interconnects, as shown in Figure 1.2(a). In the fabrication process, the patterning by photolithography is first performed on an Al film. Then the RIE process is used to form Al wiring structure which is followed by a subsequent dielectric deposition process to insulate the Al wires. Finally, a chemical mechanical polishing (CMP) process is used to planarize the dielectric layer to complete one level of Al interconnect.

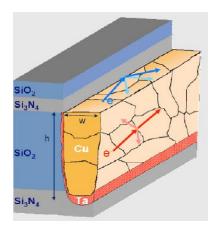

In comparison, the sublimation temperature for CuCl is 1490°C [Plummer et al., 2000], due to a tight binding of CuCl with the surface. It is difficult to remove CuCl from the surface even with ion bombardment and thus no good dry etching process is available for Cu. Instead, a different "damascene" process is used to fabricate Cu interconnects, as shown in Figure 1.2(b). First, the photolithography and RIE process are performed on the dielectric layer. The alignment of photolithography on the transparent dielectric film is easier than on the opaque and shiny metal film. However, the RIE of low-k dielectrics turns out to be difficult since it is prone to plasma damage in the RIE process. The low-k dielectrics were introduced to replace SiO<sub>2</sub> to further reduce the RC delay, crosstalk noise and power consumption of the interconnects but can be easily damaged by plasma processing [Baklanov et al., 2012, Shi et al., 2008]. After the patterning of the dielectric layer, Cu is electroplated into the via and trench openings on the dielectric layer. In a single damascene process, the vias and trenches are patterned and electroplated in separate steps. In a dual damascene process, the electroplating of Cu into the vias and the trenches are performed simultaneously. The dual damascene process not only simplifies process steps, but also decreases the via resistance and improves the EM reliability. Therefore, it is widely used in most of the advanced ICs.

Another undesired property of Cu is its high diffusivity in Si and silicate dielectrics, which can cause electrical leakage between adjacent Cu lines or TDDB of the dielectric. The Cu in the active Si can create deep trap states thus degrades the device performance. To prevent the potential out-diffusion of Cu, a barrier, also called a liner, has to be formed before the Cu seed layer deposition and electroplating, as demonstrated in Figure 1.2(b). Besides the capability of blocking Cu diffusion, the candidate material for the barrier must have low diffusivity itself and adhere well to the low k dielectric

material. Low resistivity is also required to reduce RC delay. Tantalum (Ta) with melting temperature of 3020°C fulfills these requirements. The body-centered cubic (BCC)  $\alpha$ -Ta has a resistivity of 15-50  $\mu\Omega$ -cm [Baklanov *et al.*, 2012]. Cu also has a fairly low surface diffusivity on  $\alpha$ -Ta,  $2.0\times10^{-12}$  cm²/s at 550°C [Fillot *et al.*, 2007]. To improve the adhesion between the Ta barrier and the low-k dielectric, a TaN layer is usually buffered in between. The Ta/TaN bilayered diffusion barrier is deposited using a physical vapor deposition (PVD) process.

The electroplating of Cu starts from the trenches and the surface of the dielectric layer simultaneously. An overhang of Cu, also called overburden, forms after the trenches are filled. Then a low temperature annealing (150-250°C) is performed to promote the Cu grain growth to stabilize the Cu microstructure. By comparison, the annealing of Al interconnects is performed on the Al thin film. This leads to different microstructures for Cu and Al interconnects.

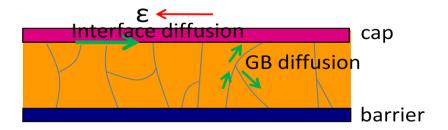

While Al has a stable native oxide Al<sub>2</sub>O<sub>3</sub> as a good passivation layer, the easily oxidized Cu surface is not passivated well by the unstable oxide layer. Therefore, a capping layer, such as SiN<sub>x</sub> is applied, by plasma-enhanced chemical vapor deposition (PECVD), to the Cu surface after it is planarized by CMP. This capping layer also functions as an etch stop for the patterning on the dielectric layer. Carbon can be added to form SiC<sub>x</sub>N<sub>y</sub> to reduce the dielectric constant of this layer [Prasad *et al.*, 2002], but with the risk of decreasing the adhesion with Cu [Wang *et al.*, 2006]. As a result, the Cu/cap interface becomes a major diffusion path in Cu interconnects [Vairagar *et al.*, 2005].

Figure 1.2 Schematic diagrams of (a) conventional RIE process for Al interconnects and (b) damascene process for Cu interconnects.

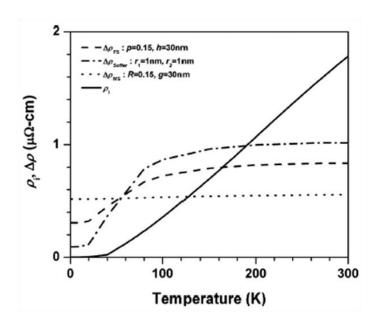

#### 1.3 EM IN CU INTERCONNECTS

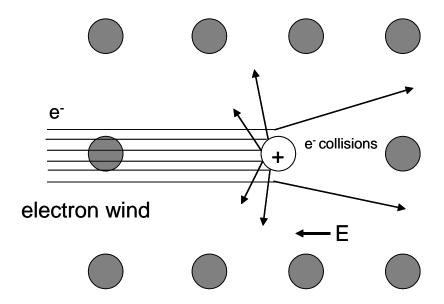

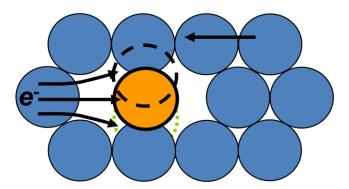

EM describes a mass transport process where metallic ions are driven by an electron current. Accelerated by the electric field, the electrons collide with an ion near a lattice vacancy as illustrated in Figure 1.3. The momentum transfer in the collision gives rise to an "electron wind" force, driving the atom to diffuse along a diffusion path, resulting in EM. The EM driving force  $F_{EM}$  excreted on the ion is composed of two parts: the electron wind force  $F_{wind}$  and the direct force  $F_{direct}$  from the applied electric field.  $F_{wind}$  and  $F_{direct}$  have opposite directions. In materials such as Cu, the wind force dominates and the  $F_{EM}$  can be expressed as:

$$F_{EM} = F_{wind} + F_{direct} \approx F_{wind} = Z^* e \rho j, \qquad (1.1)$$

where  $Z^*$  is the effective charge number, e the electron charge,  $\rho$  the resistivity of the conductor and j the electric current density.

Figure 1.3 Schematic of the collisions between the electron wind and an metal ion. With the electric field E, electrons collide with metal atoms in the electron flow direction resulting in EM phenomenon.

The first report of EM can be traced back to 1861, when Gerardin observed it in molten lead-tin and mercury-sodium alloy [Ho *et al.*, 1989]. EM received much attention only after the major semiconductor companies observed it as a failure mechanism for Al interconnects in the late 1960s [Lloyd, 1999, Ceric *et al.*, 2010]. For a short period of time, the existence of ICs was threatened by EM [Sello *et al.*, 1966, Tan *et al.*, 2007].

EM is a diffusion-controlled mass transport process, which is directly proportional to the atomic drift velocity  $v_d$  given by

$$v_d = \mu F \,, \tag{1.2}$$

where  $\mu$  is the mobility of the ion and F is the driving force including  $F_{EM}$  and stress induced back flow force if any. The mobility is directly related to the diffusivity D of the metal ion through the Einstein relationship:  $\mu = D/k_BT$ .  $k_B$  is the Boltzmann constant and T the absolute temperature.

Atoms can diffuse along two major diffusion pathways in Cu interconnects: Cu/cap interfaces and grain boundaries, as demonstrated in Figure 1.4. In general, the diffusion along Cu/barrier interfaces is relatively slow and can be ignored. The effective diffusivity of a Cu line can be expressed as:

$$D_{eff} = \frac{\delta_N}{h} D_N + \frac{\delta_{GB}}{d} D_{GB}, \qquad (1.3)$$

where the subscripts N and GB denote Cu/cap interface and grain boundary, respectively.  $\delta$  is the effective width for corresponding diffusion pathways. h is the line thickness and d is the average grain size. For a line mostly composed of bamboo type grains, the diffusion along grain boundaries can be ignored as well.

Figure 1.4 Schematic of major diffusion pathways in Cu interconnects.

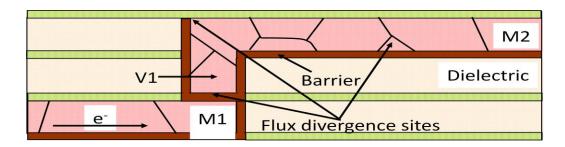

The atomic diffusion itself does not necessarily lead to void formation. Voids only occur at flux divergence sites, where more atoms flow out and less atoms flow in. Such flux divergence sites are commonly located at geometric discontinuity points and grain boundary triple points. Figure 1.5 shows three possible flux divergence sites for Cu interconnects fabricated by dual damascene process. In this example, electrons flow from metal-1 (M1) through via-1 (V1) to metal-2 (M2). Voids are commonly observed at the cathode end of M2 line, where the supply of atoms is blocked by the Cu/barrier interface although the atoms can diffuse out freely through the Cu/cap interface. Process defects generated on the upper surface of the Cu line by CMP process also makes this site more prone to void formation. Voids within the vias are more often observed in the initial process development stage, when the via fabrication process has not been optimized.

Figure 1.5 Schematic showing flux divergence sites in a Cu interconnect [Ogawa *et al.*, 2002].

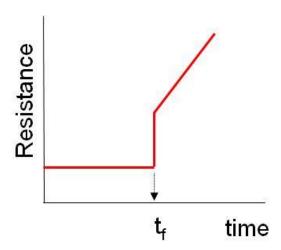

The initial void formation at the Cu/cap interface can also be observed in the resistance versus time trace recorded during EM tests, as shown schematically in Figure 1.6. The trace first appears as a flat region when an initial void forms at the Cu/cap interface with a very small increase in the line resistance. An abrupt jump in the line resistance is usually observed when the void is large enough to fail the line. This is followed by a region with gradual resistance increase when the void continues to grow after the line fails.

Figure 1.6 Resistance trace for EM of Cu interconnects including a flat region, an abrupt jump and a gradual increase region.

### 1.4 SCALING CHALLENGES TO CU EM

The scaling of transistor and interconnects continues to further improve the chip performance and reduce the cost per function. However, beyond the 22nm technology node, the scaling of interconnects becomes extremely difficult. One of the problems comes from the resistivity increase of Cu due to increasing sidewall scattering of the

conducting electrons as the line width continues to be reduced. So far, the solution to mitigate the impact of this size effect has yet to be discovered. Together with the scaling of Cu line width, the barrier thickness also scales down accordingly to reduce the resistance. It is very challenging to form a barrier of only several monolayer thick, but maintaining the barrier function to block the out-diffusion of Cu. Reliability challenges are becoming an important limiting factor as well. Aware of the difficulty, some semiconductor companies are actually planning to use 14nm node FEOL mixed with 22nm node BEOL to meet the time-to-market requirement.

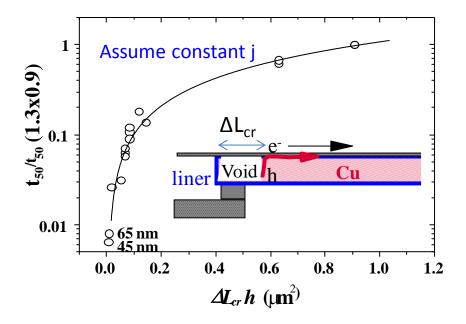

The most severe scaling challenge to Cu EM is that the EM lifetime is reduced approximately by half for each new technology node even with a fixed current density. This is demonstrated in Figure 1.7. The void at the cathode end of a line will cause line failure when its length  $\Delta L_{cr}$  is longer than the via diameter which is about the line width w. The EM lifetime is proportional to  $\Delta L_{cr}/v_d$ . When the interface diffusion through Cu/cap interface dominates, the drift velocity scales with I/h as indicated in Equation (1.3). Therefore the EM lifetime scales with w\*h if the current density j is constant. Since both line width and thickness are reduced by 0.7x drop each generation, the EM lifetime decreases by half for each technology node. The experimental data points for various nodes, represented by the open circles in Figure 1.7, agree well with the prediction by this simple scaling model.

Figure 1.7 Normalized EM lifetime as function of critical void dimensions for various technology generations. [Hu *et al.*, 2006]

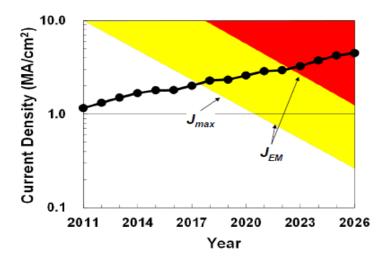

The situation is even more severe if one takes the scaling of current density into account. Figure 1.8 shows the evolution of  $J_{max}$  and  $J_{EM}$  in conventional Cu interconnects.  $J_{EM}$  is the maximum current density which meets the targeted EM lifetime requirement. It scales down with w\*h.  $J_{max}$  is defined by the maximum equivalent DC current expected in a digit circuit divided by the cross-sectional area of an intermediate interconnect line. It keeps increasing not only because the cross-section of the line is decreasing, but also because the high performance device requires a larger drive current. FEOL devices are now in transition from planar transistors to FinFETs which can carry much larger current. This poses even more difficult scaling challenge to EM reliability.

Figure 1.8 Evolution of  $J_{max}$  (from device requirement) and  $J_{EM}$  (from targeted EM lifetime). [ITRS, 2011]

Bamboo type grains are commonly observed in Cu interconnects prior to 65nm node. However, at 65nm node and beyond, the Cu lines in interconnects are usually composed of a mixture of bamboo and polycrystalline grains [Zhang *et al.*, 2007, Steinhogl *et al.*, 2005, Hu *et al.*, 2007a]. The grain boundaries associated with such grain structures provide additional diffusion pathways, and thus reduce the resistance to EM [Hu *et al.*, 2007a]. Further scaling of line width introduces more small grains in the trench bottom [Kameswaran, 2011], which further degrades the EM performance.

Significant efforts have been taken in introducing new materials to Cu interconnects to improve the EM reliability. Approaches can be categorized into two directions: improving the Cu/cap interface and/or engineering the Cu seed layer. For the first approach, methods include inserting a metal capping layer, alloying Cu surface with Al and forming Cu silicides at the top surface. Among these, a CoWP metal cap deposited by electroless plating was found to be particularly effective in suppressing the diffusion at the Cu/cap interface [Christiansen *et al.*, 2011, Gambino *et al.*, 2006, Zhang,

2010, Hu *et al.*, 2004a]. This is due to the fact that Co can form a strong adhesive interface with Cu. However, this process is difficult to implement and it also degrades the TDDB performance of low-k dielectrics [Tan *et al.*, 2008, Chen *et al.*, 2010]. This prevents it from being adopted in advanced interconnects. For the approach of using a Cu seed layer, elements such as Ti, Al, Mn, Ge, Co have been added as dopants [Hu *et al.*, 2012, Nogami *et al.*, 2010, Christiansen *et al.*, 2011, ITRS, 2011]. Upon annealing, the dopants at the sidewalls can diffuse to the Cu/cap interface and segregate there to strengthen the interface. The dopants can also segregate at the grain boundaries, blocking the grain boundary diffusion. This approach is limited, however, by the electrical resistance increase induced by the Cu alloying process [ITRS, 2011].

#### 1.5 MOTIVATION

The research performed in this dissertation is motivated by the challenges for the future scaling of the Cu interconnects beyond 22nm technology node. First, the ever decreasing line width and increasing number of new materials introduced require new methodology to be developed for Cu EM study. For example, EM-induced void formation is a problem of paramount importance and fundamental interest. Due to resolution limitation, it becomes more and more difficult to directly use SEM to investigate the void formation beyond 22nm node. In addition, EM and void formation are subjected to statistical variation and its investigation requires a large number of samples. It is also impractical to use transmission electron microscopy (TEM) to study the void formation, considering the effort required to prepare even a single sample for TEM observation. Therefore, it is highly desirable to develop a method to extract the void growth information based on analysis of EM data. Recently, it has been found that useful

information for EM can be extracted from the resistance traces [Arnaud *et al.*, 2011, Doyen *et al.*, 2008, Federspiel *et al.*, 2007, Lamontagne *et al.*, 2010, Doyen *et al.*, 2007, Arnaud *et al.*, 2010]. However, the void growth rate deduced in these works seemed to have referred to that after EM failure, i.e., the gradual increase region in Figure 1.6. Clearly, the void growth at the flat region actually determines how fast a line fails, so extracting information from this initial void growth stage is more critical. To develop such an approach for studying EM will be the research focus of this dissertation.

Second, the dimensions of interconnect lines are now in a new size regime. The line width for M1 interconnects at 22nm node is 32nm. It is comparable to the electron mean free path which is 39nm for Cu at room temperature. It is well known that, in this so called classical size regime, the electrical resistivity increases significantly due to increased interface scattering and grain boundary scattering. The electrical resistance in a metal is caused by the scattering between electrons and atoms. As shown in Figure 1.3, the same scattering events also deliver momentum to the atom and cause it to migrate along the diffusion path. In this sense, EM closely correlates with electrical resistance. This raises an important question: Does a similar significant size effect exist on EM? It will be addressed in this dissertation as well.

Third, as scaling continues, the EM of Cu interconnects is more sensitive to small process variations. This is schematically illustrated in Figure 1.9. While a 10nm square notch causes 10% width variation in a 100nm wide line as shown in Figure 1.9(a), the notch with the same size accounts for 30% width reduction in a 30nm wide line as shown in Figure 1.9(b). A 30% reduction of line width may easily induce a different EM failure mode and early failures [ITRS, 2011]. Due to the random nature of process variations, the lifetime could yield different distributions for different sets of samples. This poses

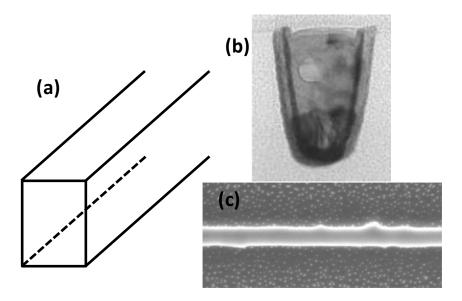

critical challenges for EM mechanism study. Such line edge roughness (LER) problem is expected to have more effect on EM reliability beyond the 22nm node, mainly because of lithography limitation. The current generation of optical lithography system with a 193nm wavelength source, combined with the optimization of computational lithography, reaches a resolution limit at 22nm node [ITRS, 2011]. The next generation lithography system using extreme ultraviolet (EUV) source with 13.5nm wavelength will not be ready for at least another two technology nodes. Therefore, it is of great importance to develop alternative processes to fabricate well-controlled Cu nanolines for investigation of EM mechanisms. Furthermore, due to the increasing difficulty in experimental study, modeling work is becoming more useful and important for Cu EM in advanced nodes. For simplicity in modeling, Cu line is commonly assumed to have a rectangular cross-section. However, an actual Cu interconnect line usually has a taped profile. It would be greatly valuable to have Cu lines with ideal profiles for model verification. Developing processes to fabricate such ideal test structures is also one of the objectives of this dissertation.

Figure 1.9 Schematic showing that narrower lines are more sensitive to process variations. (a) 100nm wide line with a 10nm square notch; (b) 30nm line with a 10nm square notch.

#### 1.6 SCOPE OF THIS WORK

The work contained in this dissertation is organized into 6 chapters as follows:

Chapter 1 provides an introduction of Cu interconnects and challenges of Cu EM caused by interconnect scaling.

Chapter 2 investigates the EM induced initial void formation in Cu interconnects by analyzing the EM resistance traces. A method of resistance trace analysis is developed for this purpose. EM tests are performed with multi-link structures to extract the statistics of resistance parameters and the initial void growth rate.

Chapter 3 develops a void growth model based on the stress evolution in a Cu line under EM. The model is compared with the EM data presented in Chapter 2. Monte Carlo grain growth simulations based on the Potts model are performed to investigate the microstructure characteristics of a Cu line.

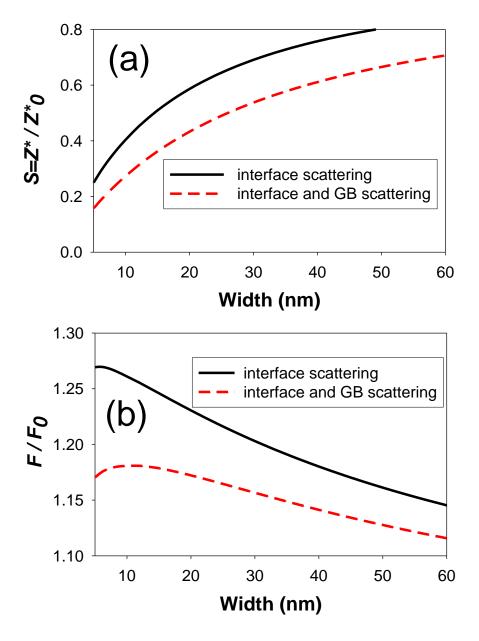

Chapter 4 studies the size effect of electron wind force for a Cu thin film and a Cu line. The dimensions under discussion are close to the electron mean free path of Cu.

Chapter 5 describes a process development for fabrication of Si nanotrenches for deposition of Cu nanolines with well-defined profiles. A method to use the polymer residues formed in fluorocarbon plasma as self-aligned sub-lithographic mask is developed.

Chapter 6 summarizes the research results obtained in this dissertation and suggests future studies.

# Chapter 2: Electromigration Induced Void Formation in Cu Interconnects

This chapter studies electromigration (EM) induced void formation mechanism in Cu interconnects. A method was developed to investigate the kinetics of the initial void formation based on the analysis of resistance traces recorded during EM tests. EM tests were performed using multi-link structures to measure the EM failure time and their statistical distributions together with the resistance traces. The method of resistance trace analysis was applied to deduce the correlation of the void growth rates before and after line failure.

#### 2.1 Introduction

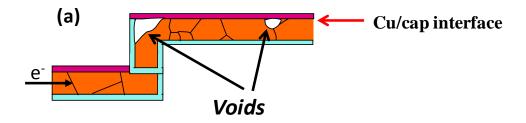

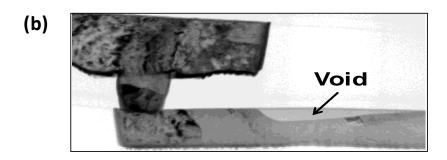

Electromigration (EM) describes the diffusion of metal atoms in a metallic conductor driven by an electron current. For Al or Cu interconnects, the EM induced mass transport occurs along surfaces, interfaces and grain boundaries, moving in a direction from the cathode towards the anode. The local imbalance of the mass transport gives rise to flux divergence which can lead to void formation at the cathode or hillock growth at the anode of the interconnect structure [Bauguess et al., 1996]. The formation of void or hillocks can result in circuit open and short failure at a rate depending on the interconnect dimensions, fabrication process and temperature. As device scaling continues to reduce the interconnect dimensions, the increase in the current density will accelerate the EM induced void formation rate, raising a major reliability concern for onchip interconnects. For Cu interconnects, the mass transport is dominated by diffusion at the interface between the Cu line and the SiCN capping layer due to the relatively weak bonding in this interface. Defects generated on the upper surface of a Cu line by the chemical-mechanical polishing (CMP) process, also makes the Cu/cap interface most prone to void formation. This is schematically shown in Figure 2.1 (a) where void formation takes place at the interface. Figure 2.1 (b) shows that such a void was indeed observed by TEM at its initial stage and close to the interface. Such a void will continue to grow until it spans the whole cross-section of the Cu line and fails the interconnect line. This void formation mechanism as illustrated is different from that observed in Al interconnects where the Al interface is relatively defect free due to the presence of the natural aluminum oxide which is a good passivation layer. Instead, the voids usually form at grain boundary triple points in Al interconnects.

Figure 2.1 (a) Schematic showing voids formed at weak Cu/cap interface. (b) TEM image showing an initial void formed close to the interface [Zhang, 2010].

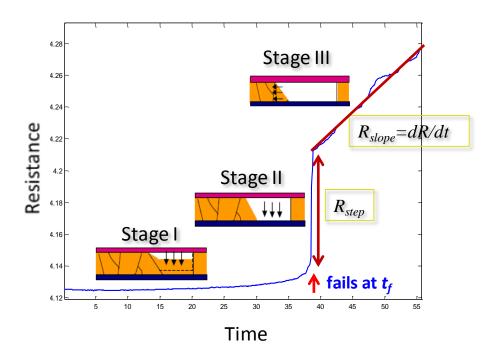

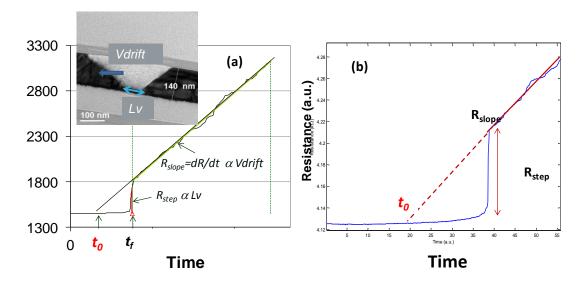

This unique feature of EM void formation for Cu interconnects is reflected in the resistance trace recorded during EM tests as a function of time. As shown in Figure 2.2, three stages are commonly observed in a resistance trace. Stage I is a relatively flat region when the voids are initially formed. The dominance of the interfacial mass transport renders the downward outgrowth of the void from the interface. During this stage, the resistance increase is usually quite small and barely detectable in the resistance trace. Once a void spans the whole cross-section of the Cu line, the electric current is forced to shunt through the resistive barrier layer. This causes line failure at Stage II and a steep resistance jump is observed in the trace. This is followed by a gradual resistance increase region at Stage III when the void further grows along the direction of line length. Clearly the first stage determines how fast the line fails. However, this most critical stage is least studied, perhaps because the resistance trace at Stage I remains nearly flat with no

significant increase in resistance. It may also be due to the fact that there is no good model so far to analyze the initial void formation stage in Cu lines.

Figure 2.2 Typical EM resistance traces with definition of three Stages and the parameters  $R_{step}$  and  $R_{slope}$ .

One way to study the initial void formation at Stage I is to use in-situ SEM to observe the void during EM stressing [Liniger *et al.*, 2002, Vairagar *et al.*, 2005, Liniger *et al.*, 2003]. However, the continuing scaling in microelectronic devices makes such direct SEM observation impractical when the line dimension is close the spatial resolution limit of SEM.

Recently, a technique using a local sense structure close to the void is developed to detect the initial void growth rate at Stage I [Croes *et al.*, 2011, Kirimura *et al.*, 2012]. For a standard EM test structure, the voltage sense terminals are placed very close to the

current injector so that the resistance of a long entire line is measured, as shown in Figure 2.3(a). Any resistance change caused by void formation in the line is relatively small compared to the line resistance. So the resistance trace does not provide enough sensitivity for observing void formation. In the newly proposed local sense structure, the voltage sense terminals are placed very close (only 10 µm away) to the via where void usually forms, as shown in Figure 2.3(b). In this way, the resistance change caused by void formation can be readily detected as a considerable portion of the resistance measured by the sensor. Figure 2.3(c) shows the increased sensitivity of such a local sensing structure. The drift velocity obtained by this technique at Stage I was found to be between 0.1 and 2 nm/h [Croes *et al.*, 2011]. In comparison, the drift velocity at Stage III has been reported to be larger from 0.1 up to 25 nm/h at 330°C. [Yokogawa, 2004, Doyen *et al.*, 2008, Lin *et al.*, 2010, Hu *et al.*, 2007].

Figure 2.3 (a) Standard EM test structure with the voltage-senses close to the current injector; (b) New local sense test structure with voltage-sensors close to via; (c) Typical EM resistance traces when sensing at the injector/local senses. [Croes *et al.*, 2011]

However, such dedicated local structure requires extra fabrication efforts. In addition, being adjacent to the void, the presence of the local sensing structure may affect the void formation kinetics. Considering the fact that extensive experiments have been performed on EM with standard test structures, there is a need to develop a method to analyze the initial void growth behavior at Stage I with standard EM test structures. This is the goal of this chapter.

## 2.2 ANALYSIS OF RESISTANCE CHANGE INDUCED BY VOID FORMATION

For simplicity, a rectangular void is assumed. The void starts from the weak Cu/cap interface with an initial long slit shape growing downwards. After it reaches the bottom, the void further grows in the horizontal direction. Although the actual voiding behavior is more complex, this model catches the essential feature of EM voiding in Cu lines. Therefore it has also been used by other authors [Arnaud *et al.*, 2011, Lamontagne *et al.*, 2010]. Figure 2.4 shows the schematics for this voiding process.

Figure 2.4 Schematics for the growth process of a rectangular void.

It is further assumed that the line failure time is dominated by void growth instead of void nucleation. This seems to be a reasonable assumption, since the CMP process, a unit process used to fabricate the damascene Cu interconnects, commonly induces significant amount of process defects on the upper surface of Cu lines. It is reasonable to believe that enough number of small voids have already been nucleated during subsequent annealing and room temperature storage. In this void growth dominated case,

the failure time  $t_f$  can be calculated from the amount of material needs to be removed and how fast the material is removed.

$$t_f = V_{crit} / A * v_{d,I} = l_{crit} / v_{d,I}.$$

(2.1)

The time  $t_f$  is the measured failure time which is defined as the time corresponding to the first abrupt resistance jump in the resistance trace, as shown in Figure 2.2. In Equation (2.1),  $V_{crit}$  is the critical void volume causing line failure.  $l_{crit}$  is the critical void length. A is the line cross-sectional area.  $v_{d,I}$  is the drift velocity at Stage I. Rigorously speaking, the drift velocity can only be applied to void growth by edge displacement mechanism, where the drift velocity is the velocity of the void front, which is also identical to the velocity of atom motion. As indicated in the schematic in Figure 2.2, the void growth at Stage I follows a grain thinning mechanism instead of an edge displacement mechanism as at Stage III. However, one can mathematically define an effective drift velocity based on the void growth rate.  $v_{d,I}$  can be interpreted as the void growth rate at Stage I normalized by A.

Once the void spans the line cross-section, the electric current forced to shunt through the resistive TaN/Ta barrier layer. The resistance trace shows a steep jump with resistance increase  $R_{step}$ , as shown in Figure 2.2. The resistance of the failed line is equivalent to the resistance of two resistors in series: the remaining Cu line and the barrier in the void segment.

$$R = R_{Cu} + R_b = \frac{\rho_{Cu}}{A} (L - l_{void}) + \frac{\rho_b}{A_b} l_{void}, \qquad (2.2)$$

where  $\rho_{Cu}$  and  $\rho_b$  are the resistivity of Cu and TaN/Ta barrier, respectively, L the total line length,  $A_b$  the cross-sectional area of the barrier,  $l_{void}$  the length of void. The critical void length upon failure is typically on the order of 100nm. The Cu line length L under EM test is typically on the order of 10-100 $\mu$ m. So the first term in Equation (2.2) is rather

independent of the void length and the increase of the resistance comes essentially only from the second term in Equation (2.2) which is the barrier resistance at the void segment. Upon failure,  $l_{void}$  is identical to  $l_{crit}$ . Therefore the resistance jump at Stage II is

$$R_{step} = \frac{\rho_b}{A_b} l_{crit} \,. \tag{2.3}$$

This suggests that the critical void length is proportional to the resistance jump upon failure. For example, assume the effective resistivity of barrier as 2  $\mu\Omega$ -m [Doyen *et al.*, 2008]. When a void with length of 100nm fails a line with cross-section area of 50nm\*100nm and barrier thickness of 10nm, the resistance jump can be calculated from Equation (2.3) as 87  $\Omega$ . As one will find in Section 2.4, this is a typical resistance jump value commonly observed in the EM tests for this study. By knowing the effective barrier resistivity and barrier cross-section, one can also calculate the void length from the resistance increase. In Figure 2.5, the void length calculated by this method is compared to the actual void length measured by SEM to verify this linear relationship [Doyen *et al.*, 2008].

Figure 2.5 Comparison of the calculated and physically measured void length.[Doyen et al., 2008]

At Stage III, the slope of the region with gradual resistance increase is

$$R_{slope} = \frac{\rho_b}{A_b} \frac{dl_{void}}{dt} = \frac{\rho_b}{A_b} v_{d,III}, \qquad (2.4)$$

where  $v_{d,III}$  is the drift velocity at Stage III. Here the drift velocity and the void growth rate are defined for two different Stages (I and III) of void growth. In previous EM studies,  $R_{slope}$  as defined in Equation (2.4) is commonly used to extract the drift velocity or the void growth rate that determines the EM lifetime [Doyen *et al.*, 2008, Arnaud *et al.*, 2011, Yokogawa, 2004, Lin *et al.*, 2010, Hu *et al.*, 2007b]. However, most of these studies did not differentiate the void growth rates between Stage I and III. But there is no evidence to show that the void growth rate at Stage I is identical to that at Stage III.

Nonetheless, a failure time can be defined based on the drift velocity at Stage III:

$$t_{f\_calc} = \frac{l_{crit}}{v_{d.III}} = \frac{R_{step}}{R_{slope}}.$$

(2.5)

Defined in this way, the parameter  $t_{f\_calc}$  can be determined by measuring both  $R_{step}$  and  $R_{slope}$  from the resistance trace. This calculated failure time  $(t_{f\_calc})$  is based on the assumption (or model) that  $v_{d,I}$  equals to  $v_{d,III}$ . In the following sections, the calculated failure time  $(t_{f\_calc})$  and the measured failure time  $(t_f)$  will be compared. If the calculated failure time  $(t_{f\_calc})$  and the measured failure time  $(t_f)$  are identical, then the plot of  $t_{f\_calc}$  and  $t_f$  will yield a linear curve with slope of 1 and passing the origin of the coordinates. Otherwise, the plot would provide an indication about how much difference exists between  $v_{d,I}$  and  $v_{d,III}$  [Wu *et al.*, 2013].

Since  $R_{step}$ ,  $R_{slope}$  and  $t_f$  are all statistically distributed, one has to control these parameters to obtain several sets of  $t_{f\_calc}$  and  $t_f$ . There are several possible ways to achieve this.  $R_{slope}$  is proportional to the drift velocity. And in general, the drift velocity is proportional to diffusivity following the Einstein relation:

$$v_d = \mu F = \frac{D}{k_B T} F \,, \tag{2.6}$$

where  $\mu$  is mobility, F the driving force, D the diffusivity,  $k_B$  the Boltzmann constant, and T the absolute temperature. So by varying the diffusivity one can change  $R_{slope}$ . There are two major diffusion paths in Cu interconnects: Cu/cap interface diffusion and grain boundary diffusion. Selective metal capping based on Co alloys, such as CoWP [Zhang, 2010, Christiansen et al., 2011, Hu et al., 2004a, Gambino et al., 2006], has been demonstrated as an effective way to suppress the interface diffusion, although this process may potentially reduce the time dependent dielectric breakdown (TDDB) [Chen et al., 2010, Tan et al., 2008] performance of low-k dielectrics— another major reliability concern for interconnects. Another way to suppress the diffusion, especially grain boundary diffusion, is to add dopants, such as Ti, Al, Ge, Mn to the Cu seed layer [Christiansen et al., 2011, Hu et al., 2012, Nogami et al., 2010, ITRS, 2011]. Those dopants will diffuse to grain boundaries and interfaces during the subsequent annealing process and slow down the Cu atom diffusion along these paths. The other parameter  $R_{step}$ is proportional to the critical void volume. In principle, this can be varied by tuning the grain size. Smaller grain size in a line may results in a smaller critical void volume. On the other hand, more grain boundaries in small-grain structures also provide more diffusion paths and larger diffusivity. The degradation of EM lifetime in lines with small grains has also been reported [Zhang et al., 2011].

All these approaches mentioned necessitates a change of the processing conditions for Cu lines, which potentially changes the resistivity of the line, stress conditions etc.. Furthermore, the change of processes also requires samples to be fabricated in different wafers, which would cause more uncontrollable variations. To overcome these issues, multi-link structures from the same wafer are used in this study.