### Design of PVT Tolerant Inverter Based Circuits for Low Supply Voltages

### A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

#### RAKESH KUMAR PALANI

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

**RAMESH HARJANI**

June, 2015

### © RAKESH KUMAR PALANI 2015 ALL RIGHTS RESERVED

## Acknowledgements

There are many people who have helped, supported and guided me to reach this juncture in my life and this thesis will be incomplete without offering my gratitude to them. Firstly, I would like to express my gratitude to Prof. Ramesh Harjani for giving me the opportunity to work in his lab and guiding me through my PhD. I am extremely thankful for the freedom he provided me to pursue the research way I liked. But nevertheless he always knew what I did and advised me when he felt I was spending too much time on something unreasonable or chasing something unachievable. From my conversations with my friends in other universities, I have realized that I have been very lucky in terms of number of tape-outs and the testing facilities at my disposal. I am indebted to Prof. Harjani for making these facilities available to us and not have to worry about these things. I have not only benefited technically but also learnt many other skills such as technical writing, making quality presentations and proposal writing.I would like to thank Savita ma'am for her wonderful lecture on getting things done.

I would like to thank Prof. Chris Kim, Prof Anand Gopinath and Prof Hubert Lim for agreeing to chair my defense and preliminary oral committee. The comments given by the committee during the preliminary oral exam were very insightful and helpful towards the latter half of my PhD.

I am thankful to Martin for the discussions we had and also for his help in teaching me soldering and use of lab equipment. I am thankful to Martin for teaching me paper writing and presentation skills along with his grammar correction.

I am thankful to Hundo for his availability in CLASIC project testing. I am thankful to Anindya for offering me help in making figures for papers. I was privileged to work and share chip space with Sachin and Mohammad. I cannot forget my sharing my frustations with Sachin and Mohammad which they were never bored off. I am grateful to them for sharing the intense workload during the tape outs. I am also thankful to Sriharsha Vadlamani for giving me a coffee company throughout my PhD. Many ideas in my PhD is evolved from the coffee discussions. I am also thankful to Saurabh, Shiva, Ashutosh, Rahman, Naser, Kang and Xingyi.

I am grateful to DARPA for supporting my project. I am thankful to the DARPA CLASIC Team, Prof Danijela, Prof Dejan Markovic, Fang Li Yuan for helping me in understanding the digital back end of a software defined radio.

I learnt a lot during my internships at Broadcom and Qualcomm. I was able to imbibe some of the design methodology and practices that ensure the success of design in my project as well. I am indebted to my managers Myron Buer, Carl Monzel and Yifei zang at Broadcom for teaching me the memory design and testing with focus on PVT variations. I am also thankful for my mentor Wang Yan at Qualcomm who introduced me to discrete time delta sigma modulators and also Ganesh Kiran , Liang Dai, Dinesh Alladi for technical discussions.

There are many people in the ECE department who silently work behind the scenes and ensure that we students always have the best possible facilities. They ensure that we spend minimum time on the administrative work and focus most of the time on our research. I would like to thank Carlos Soria, Chimai Nguyen, Dan Dobrick, Becky Colberg, Linda Jagerson, Kyle Dukart, Jim Aufderhar, Paula Beck and Linda Bullis. Finally, I will be ever grateful to my parents for believing in me and supporting me in every endeavor that I undertook. They always ensured the best for me and gave me all the freedom to do what I liked the most. My brother has been funny and good companion for last three years on my PhD.

I sincerely thank you all!

# Dedication

Dedicated to Lord Muruga

#### Abstract

Rapid advances in the field of integrated circuit design has been advantageous from the point of view of cost and miniaturization. Although technology scaling is advantageous to digital circuits in terms of increased speed and lower power, analog circuits strongly suffer from this trend. This is becoming a crucial bottle neck in the realization of a system on chip in scaled technology merging high-density digital parts, with high performance analog interfaces. This is because scaled technologies reduce the output impedance (gain) and supply voltage which limits the dynamic range (output swing). One way to mitigate the power supply restrictions is to move to current mode circuit circuit design rather than voltage mode designs.

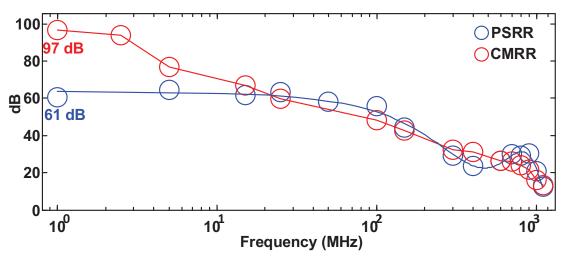

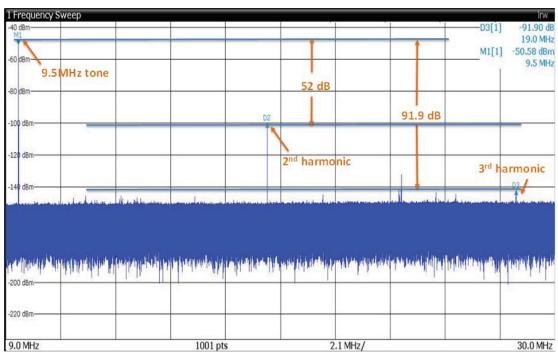

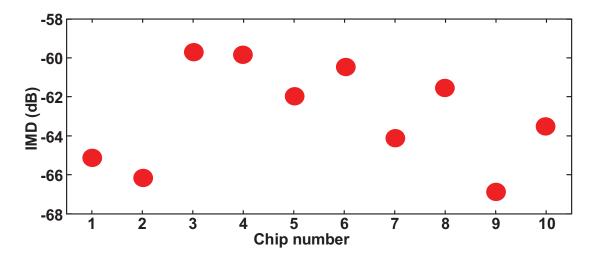

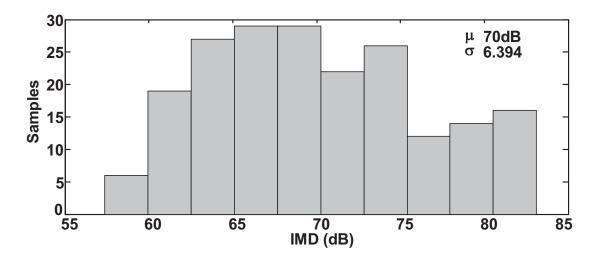

This thesis focuses on designing Process Voltage and Temperature (PVT) tolerant base band circuits at lower supply voltages and in lower technologies. Inverter amplifiers are known to have better transconductance efficiency, better noise and linearity performance. But inverters are prone to PVT variations and has poor CMRR and PSRR. To circumvent the problem, we have proposed various biasing schemes for inverter like semi constant current biasing, constant current biasing and constant gm biasing. Each biasing technique has its own advantages, like semi constant current biasing allows to select different PMOS and NMOS current. This feature allows for higher inherent inverter linearity. Similarly constant current and constant gm biasing allows for reduced PVT sensitivity. The inverter based OTA achieves a measured THD of -90.6 dB, SNR of 78.7 dB, CMRR 97dB, PSRR 61 dB wile operating from a nominal power of 0.9V and at output swing of  $0.9V_{pp,diff}$  in TSMC 40nm general purpose process. Further the measured third harmonic distortion varies approximately by 11.5dB with 120° variation in temperature and 9dB with a 18% variation in supply voltage. The linearity can be increased by increasing the loop gain and bandwidth in a negative feedback circuit or by increasing the over drive voltage in open loop architectures. However both these techniques increases the noise contribution of the circuit. There exist a trade off between noise and linearity in analog circuits. To circumvent this problem, we have introduced nonlinear cancellation techniques and noise filtering techniques. An analog-to-digital converter (ADC) driver which is capable of amplifying the continuous time signal with a gain of 8 and sample onto the input capacitor(1pF) of 1 10 bit successive approximation register (SAR) ADC is designed in TSMC 65nm general purpose process. This exploits the non linearity cancellation in current mirror and also allows for higher bandwidth operation by decoupling closed loop gain from the negative feedback loop. The noise from the out of band is filtered before sampling leading to low noise operation. The measured design operates at 100MS/s and has an  $OIP_3$  of 40dBm at the nyquist rate, noise power spectral density of  $17nV/\sqrt{Hz}$  and inter modulation distortion variation across 10 chips is 6dB and 4dB across a temperature variation of 120°C.

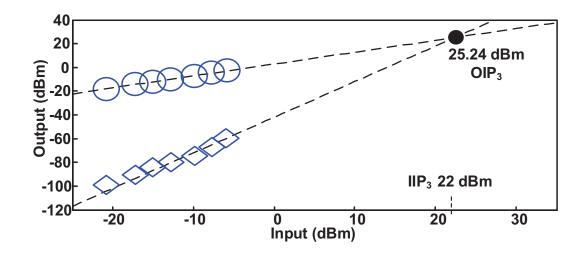

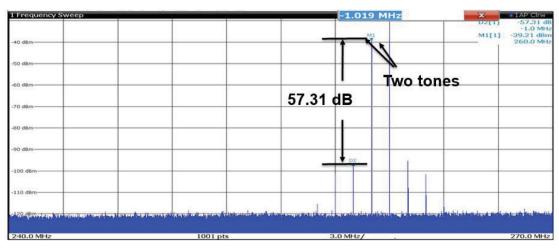

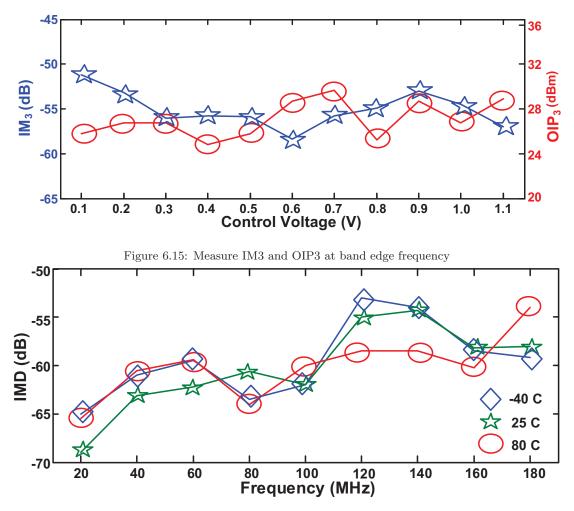

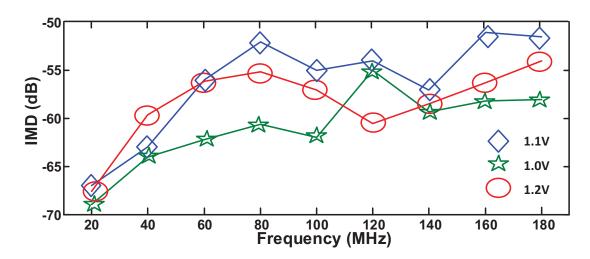

Non linearity cancellation is exploited in designing two filters, an anti alias filter and a continuously tunable channel select filter. Traditional active RC filters are based on cascade of integrators. These create multiple low impedance nodes in the circuit which results in a higher noise. We propose a real low pass filter based filter architecture rather than traditional integrator based approach. Further the entire filtering operation takes place in current domain to circumvent the power supply limitations. This also facilitates the use of tunable non linear metal oxide semiconductor capacitor (MOSCAP) as filter capacitors. We introduce techniques of self compensation to use the filter resistor and capacitor as compensation capacitor for lower power. The anti alias filter designed for 50MHz bandwidth is fabricated in IBM 65nm process achieves an IIP3 of 33dBm, while consuming 1.56mW from 1.2 V supply. The channel select filter is tunable from 34MHz to 314MHz and is fabricated in TSMC 65nm general purpose process. This filter achieves an OIP3 of 25.24 dBm at the maximum frequency while drawing 4.2mA from 1.1V supply. The measured intermodulation distortion varies by 5dB across 120°C variation in temperature and 6.5dB across a 200mV variation in power supply. Further this filter presents a high impedance node at the input and a low impedance node at the output easing system integration.

SAR ADCs are becoming popular at lower technologies as they are based on device switching rather than amplifying circuits. But recent SAR ADCs that have good energy efficiency have had relatively large input capacitance increasing the driver power. We present a 2X time interleaved (TI) SAR ADC which has the lowest input capacitance of 133fF in literature. The sampling capacitor is separated from the capacitive digital to analog converter (DAC) array by performing the input and DAC reference subtraction in the current domain rather than as done traditionally in charge domain. The proposed ADC is fabricated in TSMC's 65nm general purpose process and occupies an area of  $0.0338mm^2$ . The measured ADC spurious free dynamic range (SFDR) is 57dB and the measured effective number of bits (ENOB) at nyquist rate is 7.55 bit while using 1.55mW power from 1 V supply.

A sub 1V reference circuit is proposed, that exploits the complementary to absolute temperature (CTAT) and proportional to absolute temperature (PTAT) voltages in the beta multiplier circuit to attain a stable voltage with temperature and power supply. A one-time calibration is integrated in the architecture to get a good performance over process. Chopper stabilization is employed to reduce the flicker noise of the reference circuit. The prototype was simulated in TSMC 65nm process and we obtain the nominal output of 236mW, while consuming 0.7mW from power supply. Simulations show a temperature coefficient of 18 ppm/°C from -40 to 100°C and with a power supply ranging from 0.8 to 2V.

# Contents

| A             | cknov | wledgements                              | i    |

|---------------|-------|------------------------------------------|------|

| D             | edica | tion                                     | iv   |

| $\mathbf{A}$  | bstra | $\mathbf{ct}$                            | v    |

| $\mathbf{Li}$ | st of | Tables                                   | xiii |

| $\mathbf{Li}$ | st of | Figures                                  | xiv  |

| 1             | Intr  | oduction                                 | 1    |

|               | 1.1   | Traditional Operational Transconductance | 6    |

|               | 1.2   | Differential pair versus Inverter        | 10   |

|               | 1.3   | Non linearity Analysis                   | 12   |

|               | 1.4   | Noise Analysis                           | 15   |

|               | 1.5   | Inverter transconductor                  | 16   |

|               | 1.6   | Non-linearity cancellation techniques    | 18   |

|               | 1.7   | Organization                             | 20   |

| <b>2</b>      | Bias  | sing                                     | 23   |

|               | 2.1   | Semi-constant current biasing            | 24   |

|   |      | 2.1.1 Case 1: Small input                     | 29 |

|---|------|-----------------------------------------------|----|

|   |      | 2.1.2 Case 2: Large input                     | 30 |

|   |      | 2.1.3 Simulation $\ldots$                     | 31 |

|   | 2.2  | Constant current biasing                      | 32 |

|   | 2.3  | Constant-gm biasing                           | 33 |

|   | 2.4  | Conclusion                                    | 36 |

| 3 | Inve | erter based OTA Design                        | 37 |

|   | 3.1  | OTA design                                    | 39 |

|   |      | 3.1.1 Common mode rejection stage             | 40 |

|   |      | 3.1.2 Gain and Driver stage                   | 42 |

|   | 3.2  | Measurement Results                           | 46 |

|   | 3.3  | Conclusion                                    | 52 |

| 4 | AD   | C Driver                                      | 53 |

|   | 4.1  | ADC Driver                                    | 54 |

|   | 4.2  | OTA driving load                              | 56 |

|   |      | 4.2.1 Driving load capacitor directly         | 56 |

|   |      | 4.2.2 Driving load capacitor through resistor | 56 |

|   | 4.3  | Continuous and discrete time ADC driver       | 60 |

|   |      | 4.3.1 Continuous time driver                  | 60 |

|   |      | 4.3.2 Discrete time driver                    | 63 |

|   | 4.4  | Simulation to verify noise filtering          | 66 |

|   | 4.5  | ADC Driver Architecture                       | 67 |

|   | 4.6  | Components of the ADC Driver                  | 68 |

|   |      | 4.6.1 Current Mirror Design                   | 68 |

|   |      | 4.6.2 Trans-impedance Amplifier (TIA) Design  | 71 |

|          |     | 4.6.3  | Anti-Alias Filter                                 | 74  |

|----------|-----|--------|---------------------------------------------------|-----|

|          |     | 4.6.4  | Sampler                                           | 74  |

|          |     | 4.6.5  | Passive Amplification                             | 75  |

|          | 4.7 | Measu  | rements                                           | 75  |

|          | 4.8 | Conclu | usion                                             | 82  |

| <b>5</b> | Cur | rent N | Airror Based Filter                               | 83  |

|          | 5.1 | Integr | ator Design                                       | 86  |

|          |     | 5.1.1  | Non-Linearity Cancellation                        | 89  |

|          |     | 5.1.2  | Bandwidth limitation effects                      | 92  |

|          |     | 5.1.3  | Gain limitation effects                           | 93  |

|          |     | 5.1.4  | Noise analysis                                    | 93  |

|          | 5.2 | Filter | Design                                            | 94  |

|          |     | 5.2.1  | Current-domain biquad                             | 95  |

|          |     | 5.2.2  | Effect of OTA nonidealities on Biquad             | 96  |

|          |     | 5.2.3  | Butterworth filter design                         | 97  |

|          |     | 5.2.4  | Compensation of the amplifiers                    | 99  |

|          |     | 5.2.5  | Noise comparison with active RC integrator filter | 102 |

|          | 5.3 | Measu  | rements                                           | 107 |

|          | 5.4 | Conclu | usion                                             | 111 |

| 6        | All | MOSC   | CAP Based Continuously Tunable Filter             | 112 |

|          | 6.1 | Filter | Architecture                                      | 114 |

|          |     | 6.1.1  | Root locus                                        | 114 |

|          |     | 6.1.2  | First-order system                                | 116 |

|          |     | 6.1.3  | Third order filter                                | 122 |

|          | 6.2 | Biasin | g and CMFB                                        | 123 |

|   | 6.3 | Measurement Results                     | 3 |

|---|-----|-----------------------------------------|---|

|   | 6.4 | Conclusion                              | C |

| 7 | AD  | C 13:                                   | 2 |

|   | 7.1 | ADC Architecture                        | 8 |

|   | 7.2 | DAC Design                              | 9 |

|   | 7.3 | Sampler Design                          | G |

|   | 7.4 | Preamp Design                           | 0 |

|   |     | 7.4.1 Input voltage range 144           | 4 |

|   |     | 7.4.2 Preamp transconductance linearity | 5 |

|   |     | 7.4.3 Input capacitance linearity       | 6 |

|   |     | 7.4.4 Gate Leakage                      | 0 |

|   | 7.5 | Measurement Results                     | 1 |

|   | 7.6 | Conclusion                              | 6 |

| 8 | Sub | 1V Voltage Reference 158                | 3 |

|   | 8.1 | Voltage Reference Circuit               | 0 |

|   | 8.2 | OTA and Start up circuit                | 2 |

|   | 8.3 | Calibration Algorithm                   | 3 |

|   | 8.4 | Chopper Stabilization                   | 5 |

|   | 8.5 | Simulation Results                      | 6 |

|   | 8.6 | Conclusion                              | 8 |

| 9 | Con | clusions and Contributions 169          | 9 |

|   | 9.1 | Future work                             | 1 |

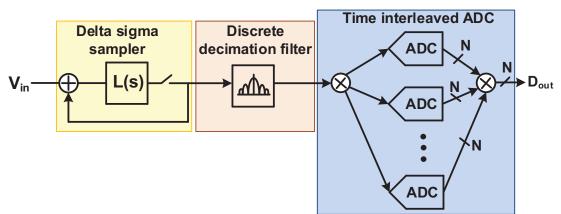

|   | 9.2 | Delta sigma sampler                     | 3 |

|   |     | 9.2.1 Time interleaved ADC              |   |

#### References

179

# List of Tables

| 1.1 | Comparison of traditional OTA architectures                              | 10  |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | Measurement summary and comparison with prior art $\ldots \ldots \ldots$ | 51  |

| 4.1 | Summary and comparison with prior art                                    | 81  |

| 5.1 | Summary and comparison of proposed filter with prior art                 | 110 |

| 6.1 | Performance summary and comparison with prior art                        | 129 |

| 7.1 | Performance summary and comparison with prior art                        | 156 |

| 8.1 | Performance Summary                                                      | 167 |

# List of Figures

| 1.1  | ITRS Roadmap                                                                 | 2  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Development in mobile industry                                               | 3  |

| 1.3  | Typical RF Receiver                                                          | 4  |

| 1.4  | Analog design octagon [1]                                                    | 4  |

| 1.5  | Five transistor differential pair                                            | 5  |

| 1.6  | Telescopic folded OTA                                                        | 6  |

| 1.7  | Folded cascode OTA                                                           | 7  |

| 1.8  | Current mirror OTA                                                           | 8  |

| 1.9  | Two stage telescopic cascoded OTA                                            | 9  |

| 1.10 | Input and output swings of differential pair and inverter OTAs $\ldots$ .    | 11 |

| 1.11 | Output current of a differential pair and pseudo- differential inverter      | 13 |

| 1.12 | Output impedance variation with output swing in differential pair and        |    |

|      | inverter                                                                     | 14 |

| 1.13 | Nauta inverter transconductor                                                | 16 |

| 1.14 | Inverter based 2 stage OTA                                                   | 17 |

| 1.15 | Traditional non-linearity cancellation techniques                            | 19 |

| 2.1  | Circuit schematic for semi-constant current inverter biasing $\ldots \ldots$ | 24 |

| 2.2  | Biasing network current with power supply variation                          | 25 |

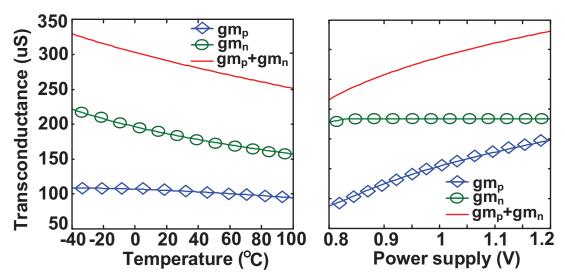

| 2.3  | Variation of inverter transconductance with temperature and supply           | 26 |

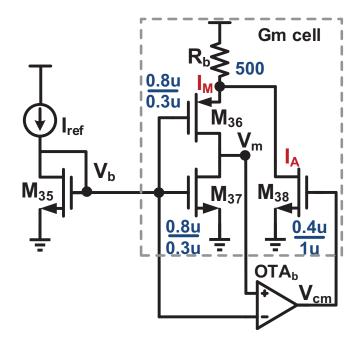

| 2.4  | Variation of inverter transconductances with power supply across process         |    |

|------|----------------------------------------------------------------------------------|----|

|      | corner for traditional replica biased inverters and SCCB inverters               | 27 |

| 2.5  | Circuit schematic for constant current biasing for inverters                     | 28 |

| 2.6  | Variation of constant current biased inverter $gm$ with power supply across      |    |

|      | process corners at 27°C and with temperature in typical corner                   | 29 |

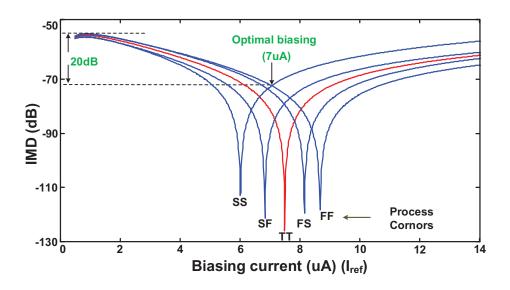

| 2.7  | Choice of bias current based on intermodulation distortion                       | 32 |

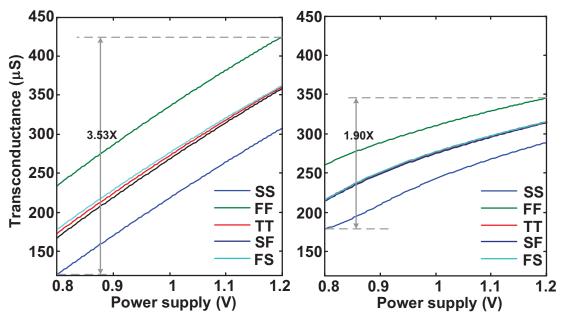

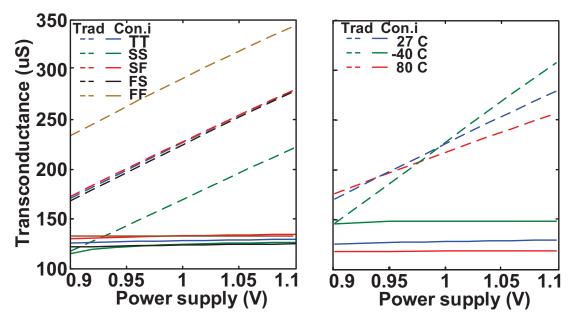

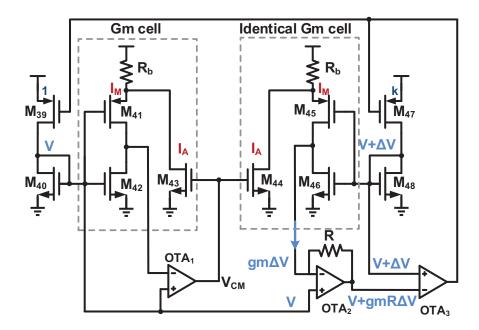

| 2.8  | Circuit schematic for constant gm biasing for inverters                          | 34 |

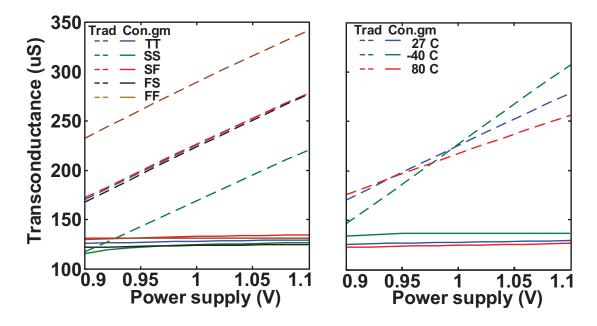

| 2.9  | Variation of constant gm biased inverter transconductance with power             |    |

|      | supply across process corners                                                    | 34 |

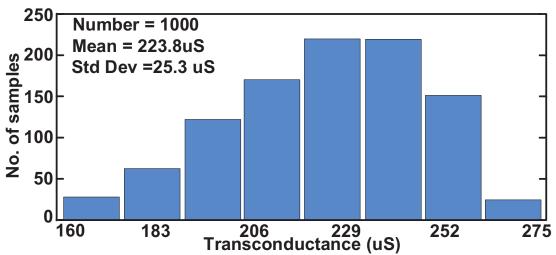

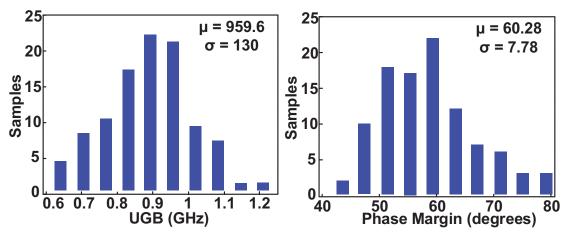

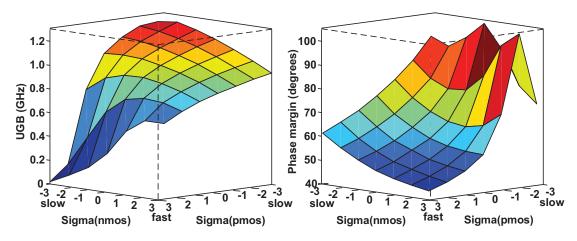

| 2.10 | Monte Carlo simulation for a constant gm inverter                                | 35 |

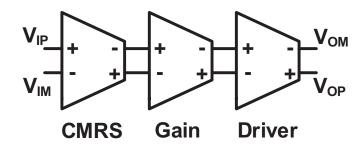

| 3.1  | Block diagram of the proposed inverter based OTA                                 | 40 |

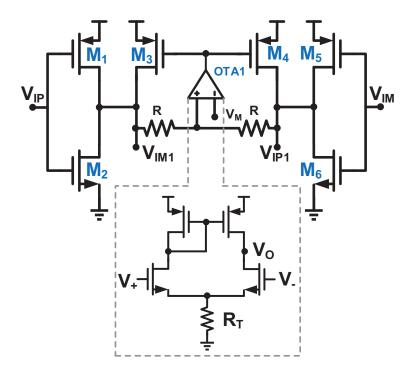

| 3.2  | Circuit schematic of CMRS stage                                                  | 41 |

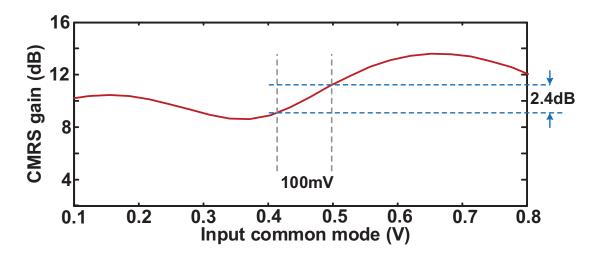

| 3.3  | Simulated CMRS gain with input common mode voltage                               | 41 |

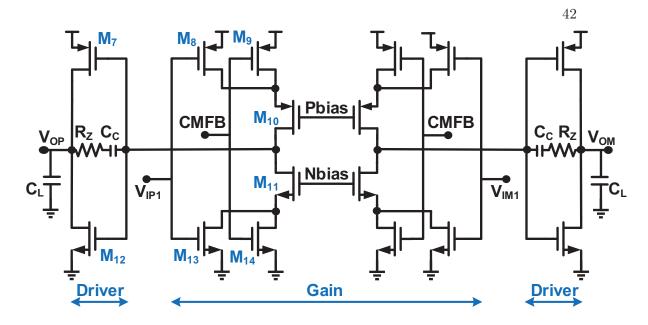

| 3.4  | Circuit schematic of gain and driver stage                                       | 42 |

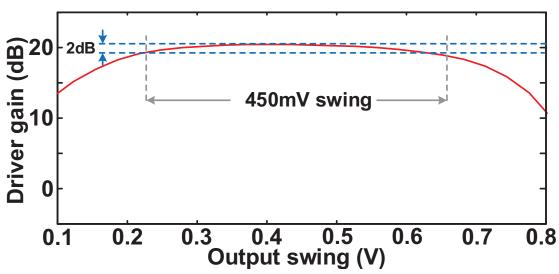

| 3.5  | Simulated driver gain with output swing                                          | 43 |

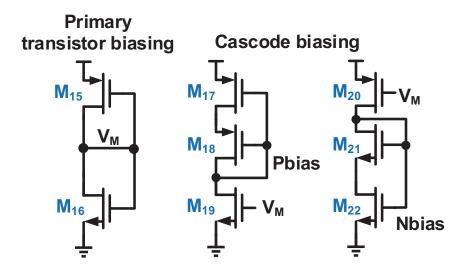

| 3.6  | Biasing of transistors in gain stage                                             | 44 |

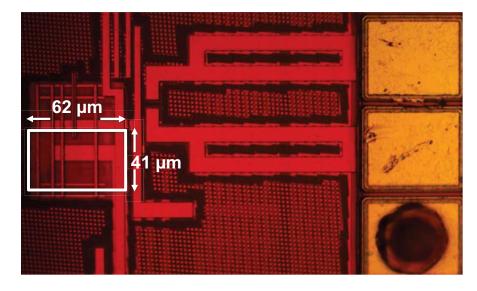

| 3.7  | Micrograph of proposed OTA                                                       | 45 |

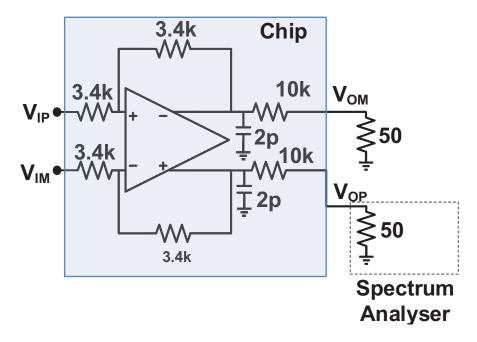

| 3.8  | Test setup of the OTA                                                            | 45 |

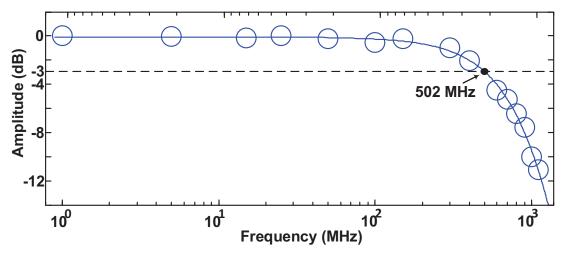

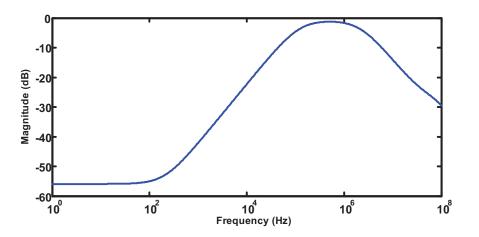

| 3.9  | Measured magnitude response of the OTA $\ldots$                                  | 46 |

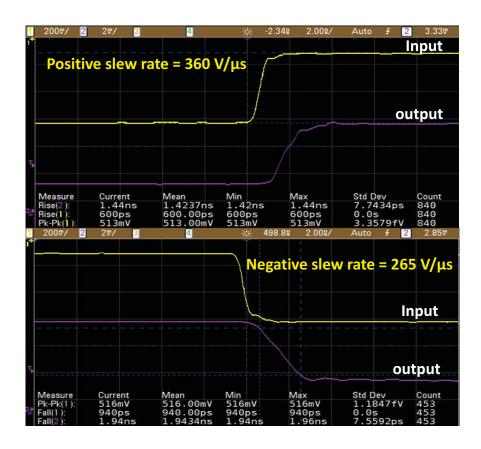

| 3.10 | Measured slew rate of the OTA                                                    | 47 |

| 3.11 | Measured common mode rejection ratio (CMRR) and power supply re-                 |    |

|      | jection ratio (PSRR) of OTA                                                      | 48 |

| 3.12 | Screen shot of single ended measured spectrum of OTA output at $9.5\mathrm{MHz}$ |    |

|      | 900 $mV_{ppdiff}$                                                                | 49 |

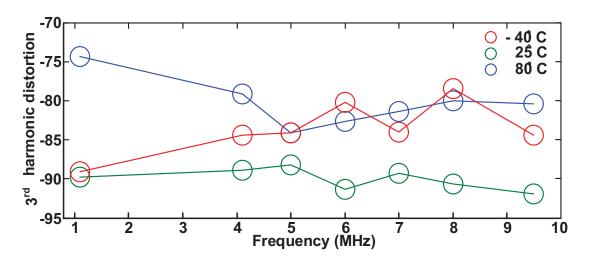

| 3.13 | Measured $3^{rd}$ order distortion versus frequency over temperature $\ldots$    | 50 |

| 3.14 | Measured $3^{rd}$ order distortion versus frequency over power supply            | 50 |

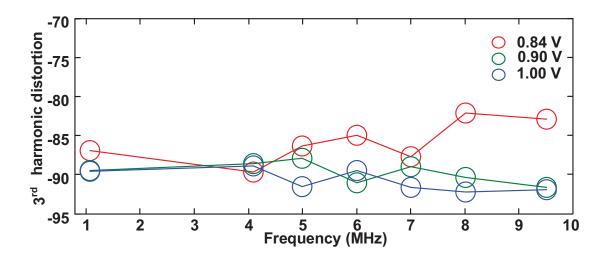

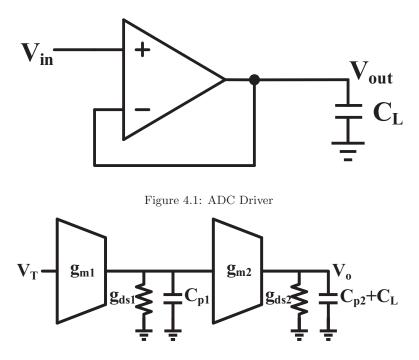

| 4.1                                                                                                          | ADC Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                 |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 4.2                                                                                                          | Loop gain of the ADC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                                 |

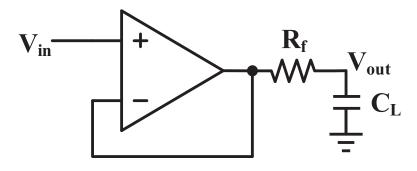

| 4.3                                                                                                          | ADC Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57                                                                                 |

| 4.4                                                                                                          | Loop gain of the ADC driver while driving capacitive load through resistor                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                 |

| 4.5                                                                                                          | Bode plot of loop gain of ADC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                 |

| 4.6                                                                                                          | Continuous time ADC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                 |

| 4.7                                                                                                          | Discrete time ADC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63                                                                                 |

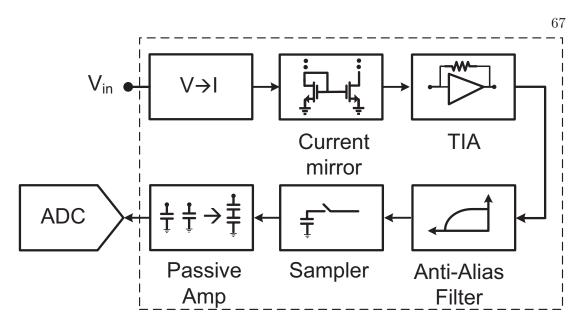

| 4.8                                                                                                          | Simulation test bench to verify noise filtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                                 |

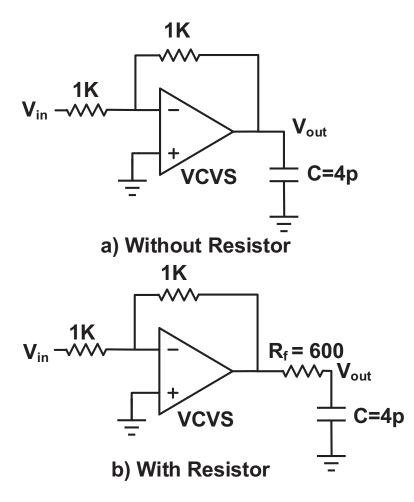

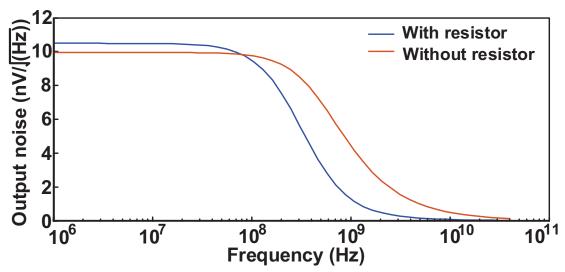

| 4.9                                                                                                          | Output noise power spectral density with and without series resistor $R_f$                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                 |

| 4.10                                                                                                         | cumulative noise integral with and without series resistor $R_f$                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                                                                                 |

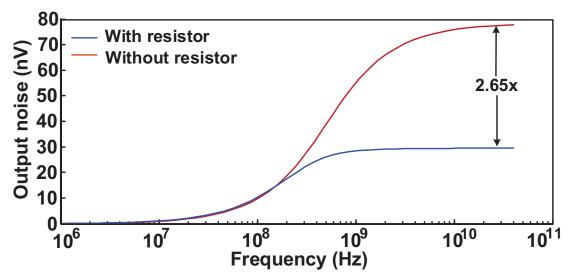

| 4.11                                                                                                         | Block diagram of the rail-to-rail output sampled ADC driver $\ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                                 |

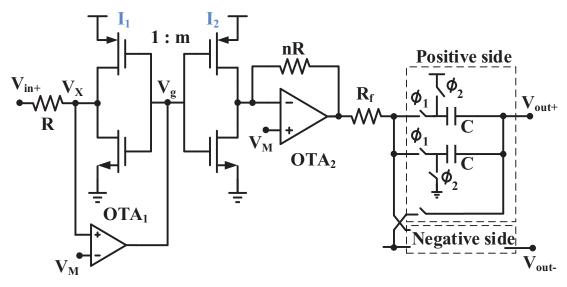

| 4.12                                                                                                         | Circuit schematic for the ADC driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69                                                                                 |

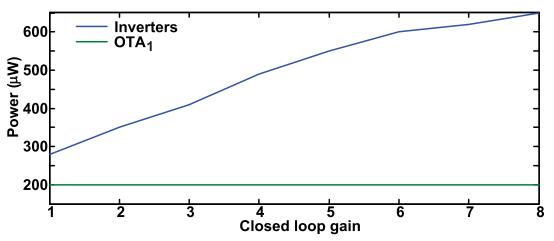

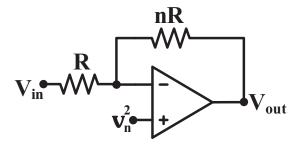

| 4.13                                                                                                         | Simulation of the voltage to current converter circuit over different closed                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |

|                                                                                                              | loop gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                 |

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |

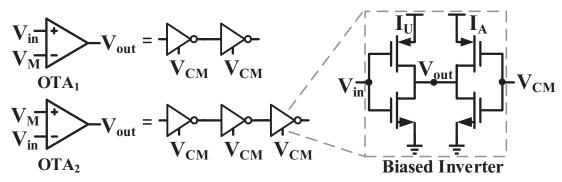

| 4.14                                                                                                         | Circuit schematic for the OTAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                 |

|                                                                                                              | Circuit schematic for the OTAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71<br>72                                                                           |

| 4.15                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |

| 4.15<br>4.16                                                                                                 | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72                                                                                 |

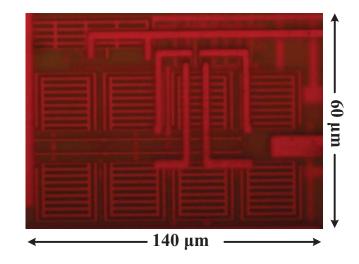

| <ul><li>4.15</li><li>4.16</li><li>4.17</li></ul>                                                             | Comparison of inverting (a) and transimpedance (b) amplifiers<br>Micrograph of the ADC Driver                                                                                                                                                                                                                                                                                                                                                                                                                        | 72<br>73                                                                           |

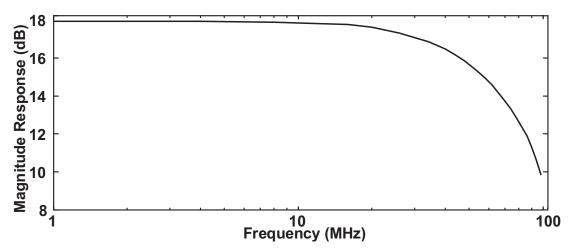

| <ul><li>4.15</li><li>4.16</li><li>4.17</li><li>4.18</li></ul>                                                | Comparison of inverting (a) and transimpedance (b) amplifiers<br>Micrograph of the ADC Driver                                                                                                                                                                                                                                                                                                                                                                                                                        | 72<br>73<br>76                                                                     |

| <ul><li>4.15</li><li>4.16</li><li>4.17</li><li>4.18</li></ul>                                                | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ Micrograph of the ADC Driver $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                         | 72<br>73<br>76                                                                     |

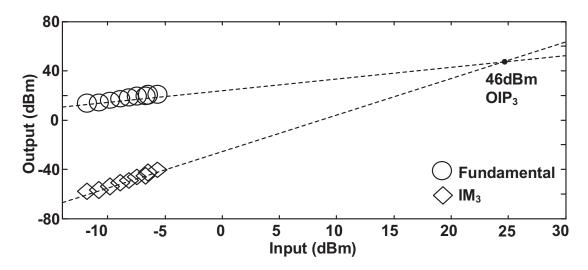

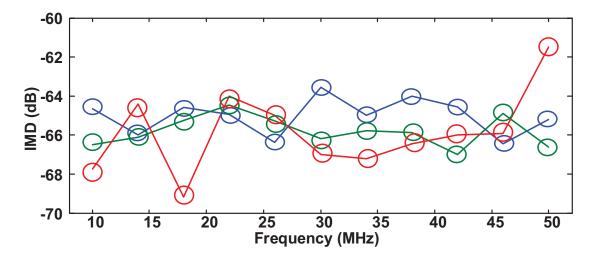

| <ul><li>4.15</li><li>4.16</li><li>4.17</li><li>4.18</li><li>4.19</li></ul>                                   | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ .<br>Micrograph of the ADC Driver $\ldots$ .<br>Magnitude response of the ADC Driver $\ldots$ .<br>Measured IIP <sub>3</sub> at 50MHz using two tones with 1MHz offset $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation. Red,                                                                                                                                                                                  | 72<br>73<br>76<br>77                                                               |

| <ul><li>4.15</li><li>4.16</li><li>4.17</li><li>4.18</li><li>4.19</li></ul>                                   | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ .<br>Micrograph of the ADC Driver $\ldots$ .<br>Magnitude response of the ADC Driver $\ldots$ .<br>Measured IIP <sub>3</sub> at 50MHz using two tones with 1MHz offset $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation. Red,<br>blue and green lines indicate three different chips $\ldots$ .                                                                                                                | 72<br>73<br>76<br>77                                                               |

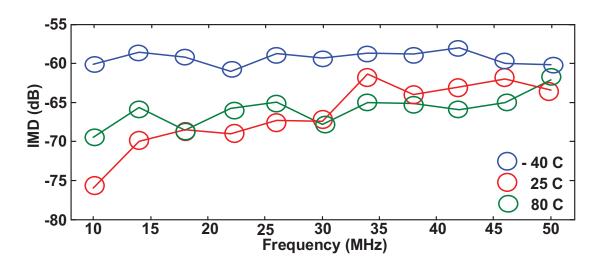

| <ul> <li>4.15</li> <li>4.16</li> <li>4.17</li> <li>4.18</li> <li>4.19</li> <li>4.20</li> </ul>               | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ .<br>Micrograph of the ADC Driver $\ldots$ .<br>Magnitude response of the ADC Driver $\ldots$ .<br>Measured IIP <sub>3</sub> at 50MHz using two tones with 1MHz offset $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation. Red,<br>blue and green lines indicate three different chips $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation at differ-                                | 72<br>73<br>76<br>77<br>77                                                         |

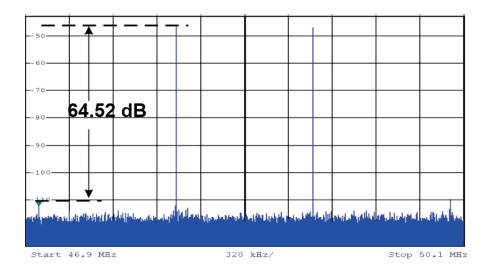

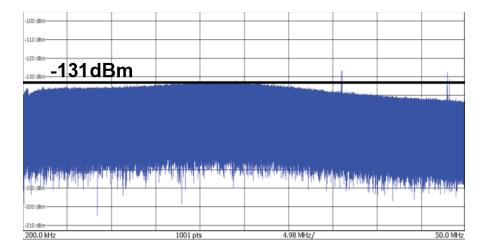

| <ul> <li>4.15</li> <li>4.16</li> <li>4.17</li> <li>4.18</li> <li>4.19</li> <li>4.20</li> <li>4.21</li> </ul> | Comparison of inverting (a) and transimpedance (b) amplifiers $\ldots$ .<br>Micrograph of the ADC Driver $\ldots$ .<br>Magnitude response of the ADC Driver $\ldots$ .<br>Measured IIP <sub>3</sub> at 50MHz using two tones with 1MHz offset $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation. Red,<br>blue and green lines indicate three different chips $\ldots$ .<br>Measured IMD for $2V_{pp-diff}$ output with 1MHz tones separation at differ-<br>ent temperatures $\ldots$ . | <ul> <li>72</li> <li>73</li> <li>76</li> <li>77</li> <li>77</li> <li>78</li> </ul> |

| 4.24                                                                                           | Screen capture of the noise measurement                                                                                     | 80                                                                                                                             |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

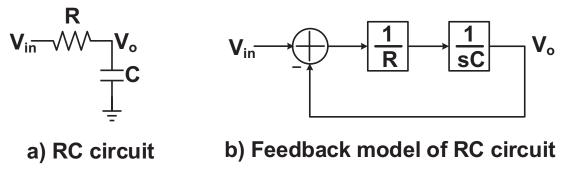

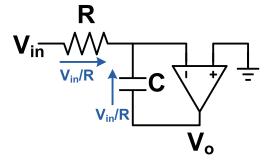

| 5.1                                                                                            | Passive RC low pass circuit and its feedback model                                                                          | 84                                                                                                                             |

| 5.2                                                                                            | Active RC integrator                                                                                                        | 85                                                                                                                             |

| 5.3                                                                                            | Poles in an active RC filter                                                                                                | 86                                                                                                                             |

| 5.4                                                                                            | A conventional active-RC integrator (a) and the proposed integrator (b).                                                    | 87                                                                                                                             |

| 5.5                                                                                            | A conventional $\mathrm{G}_{\mathrm{m}}\text{-}\mathrm{C}$ integrator (a) and a functional diagram of the pro-              |                                                                                                                                |

|                                                                                                | posed design which linearizes its $G_m\mbox{-}C$ output section (b)                                                         | 88                                                                                                                             |

| 5.6                                                                                            | Non-Linear Cancellation in proposed integrator                                                                              | 90                                                                                                                             |

| 5.7                                                                                            | Monte carlo simulation on the current mirror                                                                                | 91                                                                                                                             |

| 5.8                                                                                            | Noise sources in the proposed Integrator                                                                                    | 94                                                                                                                             |

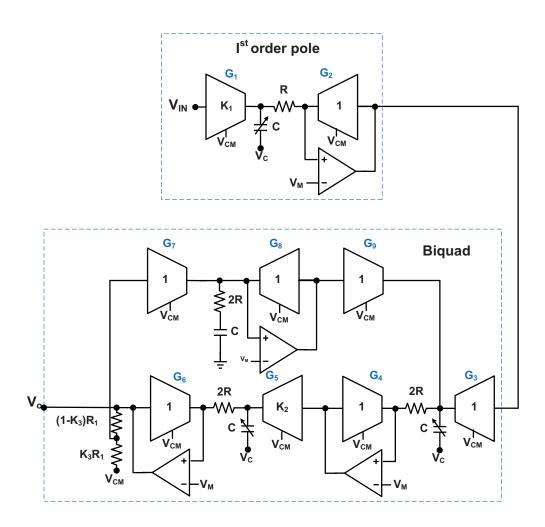

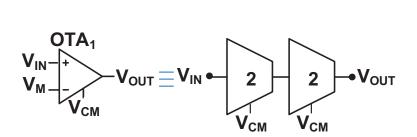

| 5.9                                                                                            | Current mode low pass filter based Biquad                                                                                   | 95                                                                                                                             |

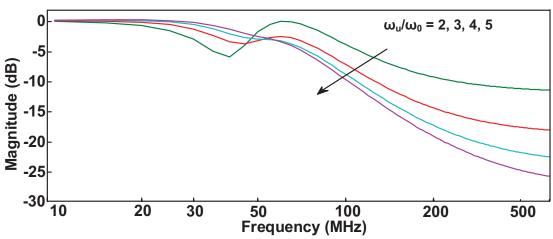

| 5.10                                                                                           | Effect of OTA non-idealities on Biquad                                                                                      | 97                                                                                                                             |

| 5.11                                                                                           | Schematic of the 3rd order filter using the proposed integrator and                                                         |                                                                                                                                |

|                                                                                                |                                                                                                                             |                                                                                                                                |

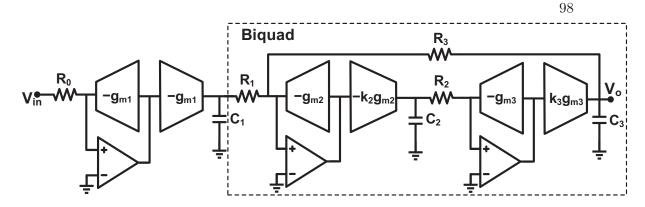

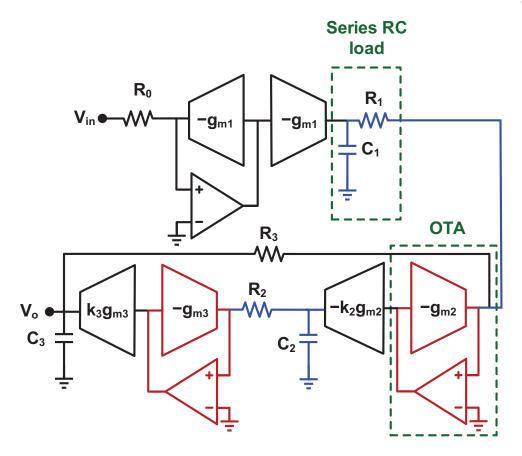

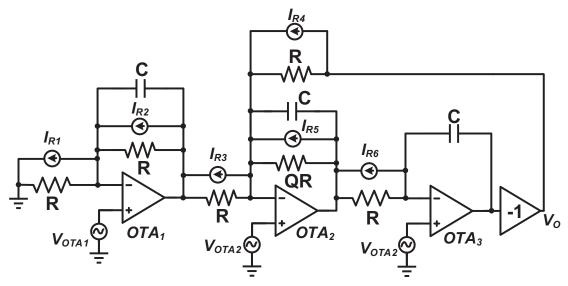

|                                                                                                | current-mode biquad                                                                                                         | 98                                                                                                                             |

| 5.12                                                                                           | current-mode biquad                                                                                                         |                                                                                                                                |

|                                                                                                |                                                                                                                             |                                                                                                                                |

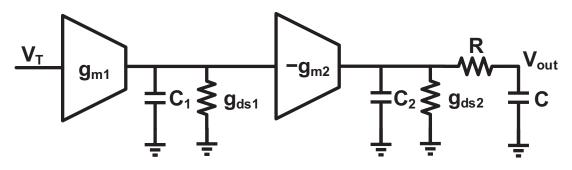

| 5.13                                                                                           | Compensation of negative feedback loops in biquad using filter components                                                   | s 99                                                                                                                           |

| 5.13<br>5.14                                                                                   | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | $\frac{99}{100}$                                                                                                               |

| 5.13<br>5.14<br>5.15                                                                           | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | s 99<br>100<br>102                                                                                                             |

| <ol> <li>5.13</li> <li>5.14</li> <li>5.15</li> <li>5.16</li> </ol>                             | Compensation of negative feedback loops in biquad using filter components.<br>Schematic of Loop gain of one stage in Biquad | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> </ul>                                                                  |

| <ol> <li>5.13</li> <li>5.14</li> <li>5.15</li> <li>5.16</li> <li>5.17</li> </ol>               | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> <li>104</li> </ul>                                                     |

| <ol> <li>5.13</li> <li>5.14</li> <li>5.15</li> <li>5.16</li> <li>5.17</li> <li>5.18</li> </ol> | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> <li>104</li> <li>106</li> </ul>                                        |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19                                           | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> <li>104</li> <li>106</li> <li>107</li> </ul>                           |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20                                   | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> <li>104</li> <li>106</li> <li>107</li> <li>108</li> </ul>              |

| 5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20<br>5.21                           | Compensation of negative feedback loops in biquad using filter components<br>Schematic of Loop gain of one stage in Biquad  | <ul> <li>99</li> <li>100</li> <li>102</li> <li>103</li> <li>104</li> <li>106</li> <li>107</li> <li>108</li> <li>109</li> </ul> |

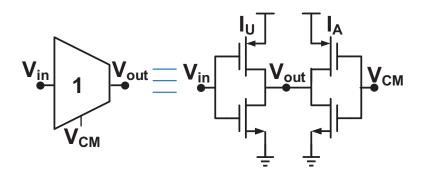

| 6.2  | OTA realization with biased inverter gm cell                                                     | 115 |

|------|--------------------------------------------------------------------------------------------------|-----|

| 6.3  | Circuit schematic of the gmcell $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 117 |

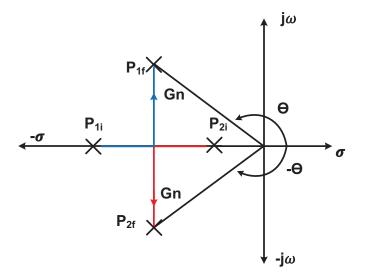

| 6.4  | Root locus of the two poles system                                                               | 118 |

| 6.5  | Circuit schematic of the first order system $\ldots \ldots \ldots \ldots \ldots \ldots$          | 118 |

| 6.6  | Voltage swing across various nodes in the $1^{st}$ order system                                  | 119 |

| 6.7  | First order system with parasitics                                                               | 120 |

| 6.8  | Circuit schematic to evaluate loop gain                                                          | 121 |

| 6.9  | Bode plot of the loop gain                                                                       | 122 |

| 6.10 | Common mode feedback circuit for tunable filter $\ldots \ldots \ldots \ldots$                    | 124 |

| 6.11 | Micrograph of proposed tunable channel select filter $\ldots \ldots \ldots$                      | 124 |

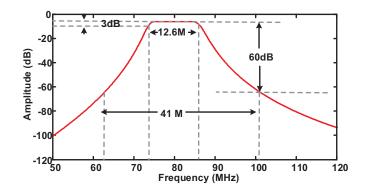

| 6.12 | Measured magnitude response of proposed filter                                                   | 125 |

| 6.13 | Measured IIP3 of proposed filter at 260MHz input                                                 | 125 |

| 6.14 | Measured $IM_3$ at 260MHz, $V_c$ =1.1V, with tones separated bt 1MHz                             | 126 |

| 6.15 | Measure IM3 and OIP3 at band edge frequency                                                      | 127 |

| 6.16 | Measure IM3 with frequency at Vc=1V over temperature $\ldots \ldots \ldots$                      | 127 |

| 6.17 | Measure IM3 with frequency at Vc=1V with power supply                                            | 128 |

| 6.18 | Measure IM3 at band edge across 15 chips                                                         | 128 |

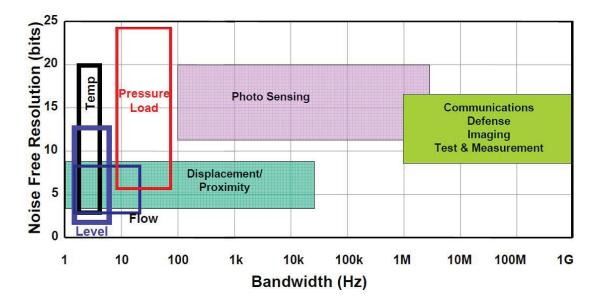

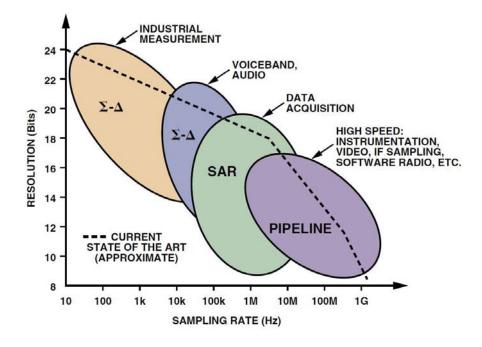

| 7.1  | Real world versus Bandwidth                                                                      | 133 |

| 7.2  | Architectural choice based on applications                                                       | 133 |

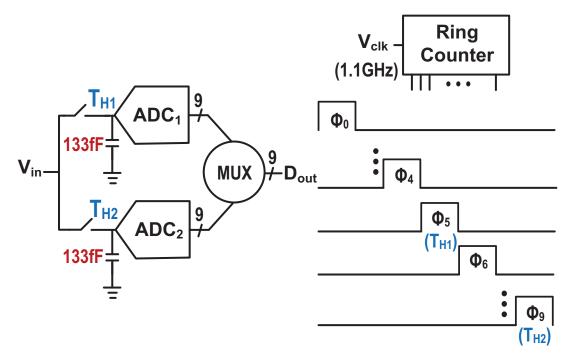

| 7.3  | Overall architecture and timing diagram for the time-interleaved ADC $% \mathcal{A}$ .           | 135 |

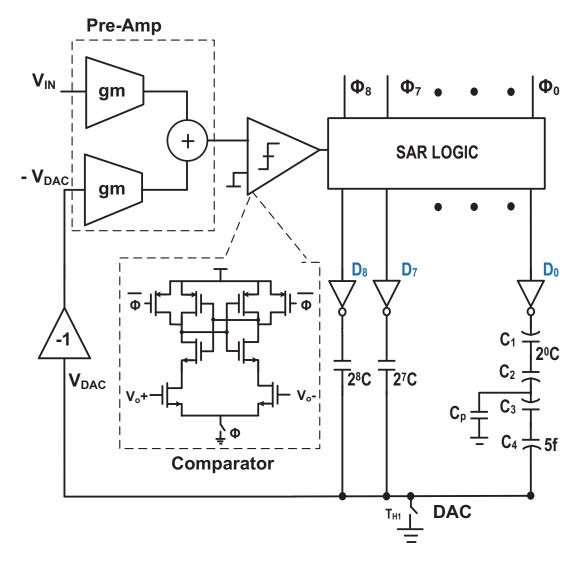

| 7.4  | Simplified single ended circuit schematic for SAR sub-ADC                                        | 137 |

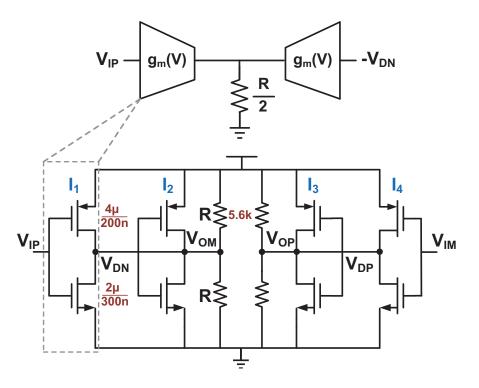

| 7.5  | Circuit schematic for the preamp and subtractor within each sub-ADC .                            | 139 |

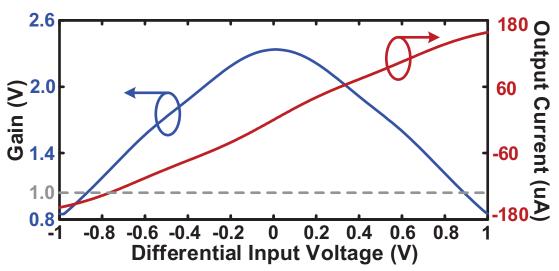

| 7.6  | Simulated preamp gain and transconductance output current                                        | 140 |

| 7.7  | Simulation of the impact of $g_m$ cell non-linearity upon the ADC (blue),                        |     |

|      | and the effect when the DAC is predistorted by the same $g_m$ cell (red) .                       | 141 |

| 7.8  | Transconductance current of the signal input and the DAC input                                   | 143 |

| 7.9  | Simulated maximum droop in the sampled voltage vs. the input voltage             |     |

|------|----------------------------------------------------------------------------------|-----|

|      | $(V_{pp-diff})$ due to gate leakage at 27°C                                      | 144 |

| 7.10 | Variation of capacitance with input voltage for NMOS (blue), PMOS                |     |

|      | (green) and CMOS implementation for equal transconductance (red) $~$ .           | 145 |

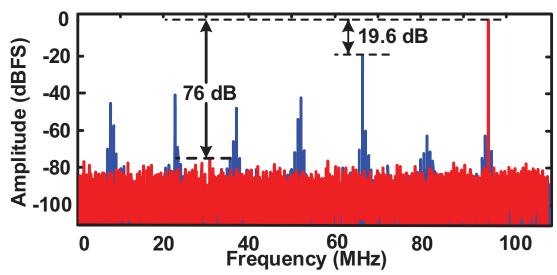

| 7.11 | Simulated output spectrum of the ADC at different temperatures                   | 147 |

| 7.12 | Simulated output spectrum of ADC with $10\%$ variation in power supply           | 147 |

| 7.13 | Monte carlo simulation on the ADC over 50 trials                                 | 148 |

| 7.14 | Measured output FFT spectrum of sub-ADC                                          | 148 |

| 7.15 | Measured output FFT spectrum of TI-ADC                                           | 149 |

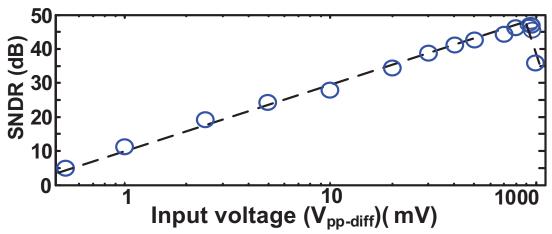

| 7.16 | Plot of SNDR vs signal amplitude $(V_{pp})$ at $f_{in}=49$ MHz                   | 150 |

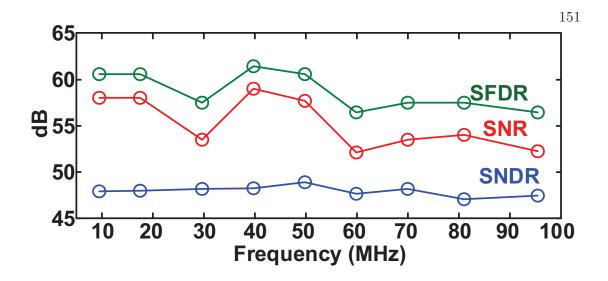

| 7.17 | Measured SNR, SNDR and SFDR versus input frequency $\hdots \ldots \hdots \ldots$ | 151 |

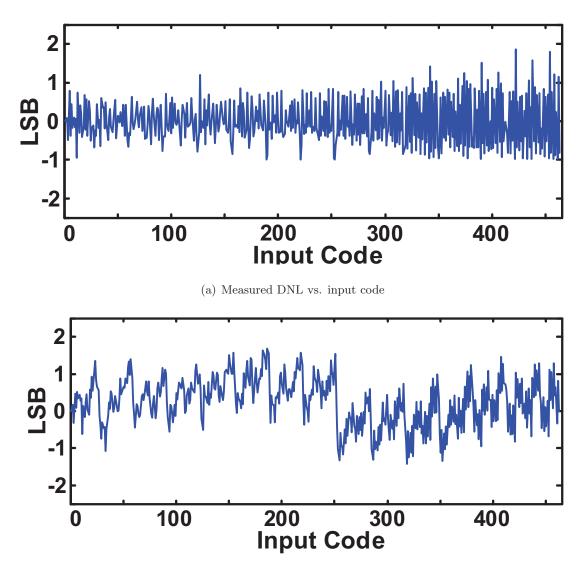

| 7.18 | Measured DNL and INL vs. input code for the sub-ADC                              | 152 |

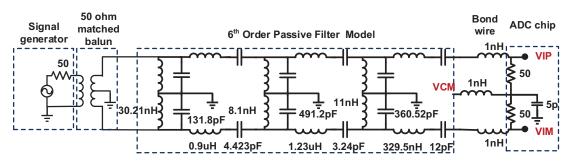

| 7.19 | Test bench for testing ADC                                                       | 153 |

| 7.20 | Magnitude response of the simulated passive band pass filter $\ .\ .\ .$ .       | 154 |

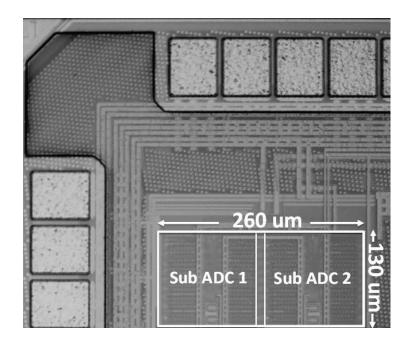

| 7.21 | Micrograph of proposed time-interleaved SAR ADC                                  | 154 |

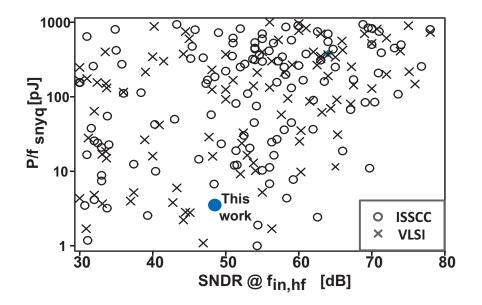

| 7.22 | Comparison of prototype ADC with state of art ADCs over energy                   | 155 |

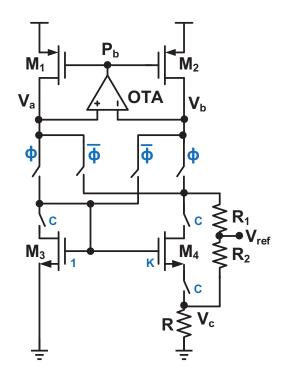

| 8.1  | Schematic diagram of the Voltage Reference circuit                               | 160 |

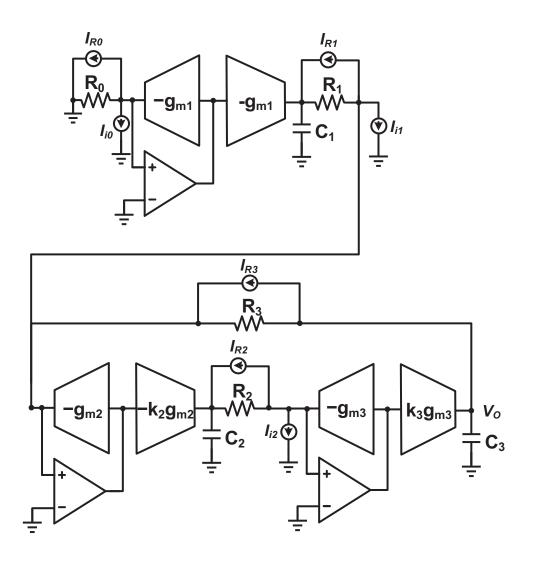

| 8.2  | Schematic diagram of the OTA                                                     | 162 |

| 8.3  | Simulated reference voltage with temperature across power supply $\ . \ .$       | 163 |

| 8.4  | Simulated reference voltage with temperature across power supply and             |     |

|      | process corners without calibration                                              | 164 |

| 8.5  | Simulated reference voltage with temperature across power supply and             |     |

|      | process corners with one time calibration                                        | 165 |

| 8.6  | Simulated power supply rejection with frequency                                  | 166 |

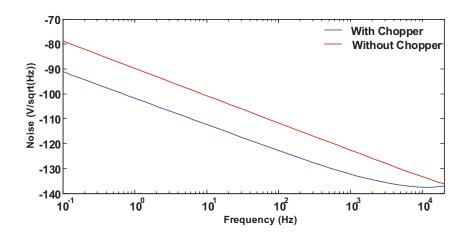

| 8.7  | Simulated flicker noise with and without chopper stabilization                   | 167 |

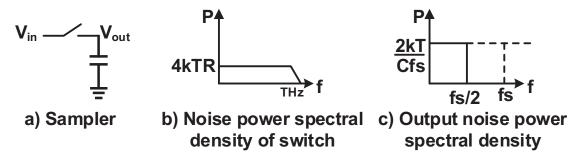

| 9.1  | Sampling operation                                                               | 173 |

| 9.2 | Jitter immune ADC                                                      | 174 |

|-----|------------------------------------------------------------------------|-----|

| 9.3 | Matlab simulation of delta sigma sampler $\ldots \ldots \ldots \ldots$ | 175 |

| 9.4 | Architecture of sub ADC                                                | 176 |

| 9.5 | Output spectrum of the sub-ADC                                         | 177 |

### Chapter 1

# Introduction

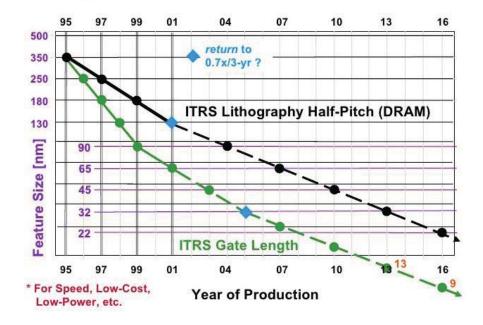

The increase in chip complexity over past few years has created the need to implement complete analog and digital subsystems on the same integrated circuit using the same technology. Fig. 1.1 shows the roadmap for the technology scaling. The increase in demand for battery operated portable devices and implantable medical devices has placed added pressure on lowered supply voltages. Technology scaling reduces the delay of the circuit elements, enhancing the operating frequency of an integrated circuit. The density and number of transistors on an IC increases with the scaling of the feature sizes. Today we are at 14nm FINFET technology. Reducing power dissipation has become an important objective in the design of digital circuits. One common technique for reducing power is to reduce the supply voltage. Reduction in supply voltage demands proportional scaling of threshold voltage to maintain the same ON current. However scaling of threshold voltage increases the sub threshold leakage or the OFF current. Hence threshold voltage does not scale proportional to the supply voltage. Technology scaling Fig. 1.1 is a robust roadmap [2] for digital circuits, while analog circuits strongly suffer from this trend, and this is becoming a crucial bottle neck in the realization of a system on chip in a scaled technology merging high-density digital parts, with high

#### Scaling -- Traditional Enabler of Moore's Law\*

Figure 1.1: ITRS Roadmap

performance analog interfaces. This is because scaled technologies reduce the supply voltage, and this limits the analog performance in qualitative (is it possible to operate from a low voltage?) and quantitative (if it is possible to operate, which performance is achievable?) terms [3].

Portable devices like mobiles Fig. 1.2 continue to drive the need for circuits that achieve low power without sacrificing linearity. Analog baseband circuits, including filters and programmable gain amplifiers (PGA), are indispensable in wireless sensors and communication systems. These analog filters typically consume tens of mWs of power and and have a considerable impact on the the total power consumption. Hence implementation of analog functions in MOS technology has become increasingly important, and great strides have been made in implementing functions such as ADCs, DACs, filters, voltage references, instrumentation amplifiers in CMOS technology. Operational transconductance amplifiers (OTAs) are widely employed as active elements in filters,

Figure 1.2: Development in mobile industry

data converters and buffer amplifiers.

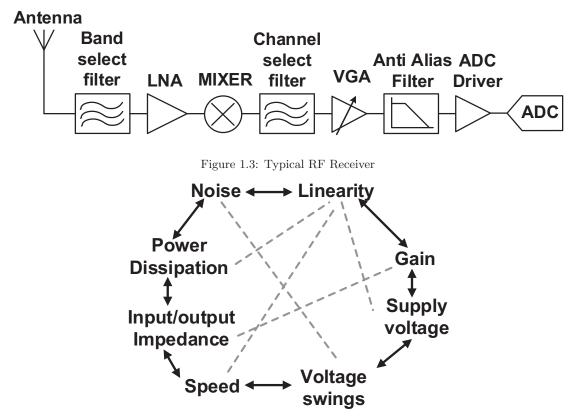

Each mobile will have many radios. One typical simplest RF receiver chain is shown in Fig. 1.3. These has couple of filters for filtering different band signals and also has amplifiers to amplify inband signals. The small signal from antenna is band selected using an off chip passive band pass filter. Low noise amplifier (LNA) is used to amplify these signals with minimal noise addition. The signal at RF carrier frequency is down converted to baseband using a mixer. A channel select filter is used to select the signal channel. A cascade of IF amplifiers and VGA is used to amplify the signal. Anti alias filter is used to remove all the components away from the nyquist band. This is used to prevent aliasing of out of band signals and noise into the signal band after sampling. If the signal swing is less than the dynamic range of ADC (rail-rail), an ADC driver can be used to amplify and sample the signal onto the input capacitance of the ADC.

The trade of in analog circuit design is explained in Fig. 1.4 [1]. The parameters like gain, speed, power dissipation, supply voltage, linearity, noise and maximum voltage swings are important in analog design and trades off with each other. Furthermore, the input and output impedances determine how the circuit interacts with the preceding

Figure 1.4: Analog design octagon [1]

and subsequent stages. For example at lower supply voltages, we are hit by the noise floor. Hence we need to operate the transistors at lower overdrive voltages for better noise performance which in turn hurts the linearity of the transistor. Similarly we need to burn more power to reduce the noise and increase the speed of amplifier. The gain, supply voltage and impedances along with voltage swings determine the maximum signal to noise ratio achievable from the circuit. Similarly higher linearity demands higher overdrive voltage which increases the noise contribution. This thesis focuses on the design of baseband circuits in a wireless receiver like amplifiers, channel select filter, anti alias filter and time interleaved ADC. The circuits are optimised for lower noise and techniques like non linear cancellation are used to increase the inherent linearity.

Figure 1.5: Five transistor differential pair

Further filter circuits are designed in current mode where both low noise and higher linearity demands higher overdrive voltages. The design of high performance baseband circuits in MHz range is always challenging. It is difficult to get the negative feedback loop gain at these frequencies due to higher threshold voltage at lower power supply and also with lower output impedances. This thesis provides a different architecture for filters to achieve high linearity and low noise at lower power. Further the channel select filters is made tunable to select the channels from 34 MHz to as wide as 314MHz. The ADC driver is designed with a gain of 8 to increase the swing of the signals to rail to rail and sample onto the input capacitance of the ADC. Finally a time interleaved ADC is designed to convert analog to digital for signal processing. This ADC offers high impedance to the preceding circuits and thereby lowering the power of the entire system.

Figure 1.6: Telescopic folded OTA

#### **1.1** Traditional Operational Transconductance

Operational amplifier is required to realize an integrator in negative feedback circuit. Since the loop gain of the negative feedback circuit determines the performance of the circuit, design of operational amplifier is an hot area of research in analog VLSI circuits. Since the negative feedback amplifiers puly the difference between the input and the feedback path, the operational amplifier should amplify only the input differences. Further in fully differential circuits, the operational amplifier is a five transistor differential pair Fig. 1.5. This forms the core in more complex operational amplifier design.

We apply the input voltage across across the differential pair transistors. The tail transistor(biased at ntail) acts like a current source thereby acting like a source degeneration resistor for common mode signals. Hence the differential pair transistors convert only the

Figure 1.7: Folded cascode OTA

differential mode components in input voltage to current. The common mode voltage appears directly at the tail node. This current is pumped into output impedance of the transistors through a current mirror to get voltage gain. The finite output impedance of the transistors limits the gain of the circuit. Hence attempts were made to improve the output impedance of the transistors. A common gate amplifier has the low input impedance due to inherent negative feedback but higher output impedance. Hence the current from the common source differential pair acts like an input to common gate amplifier. This leads to an architecture of telescopic cascoded operational amplifier Fig. 1.6. The output impedance of the OTA is amplified by the gain of the common gate amplifier. This leads to have an increased gain. The output swing is small as each transistor requires overdrive voltage to maintain them in saturation region. Folded cascoded amplifier is introduced to increase the output swing by one overdrive voltage. Here instead of cascading NMOS based common source amplifier with NMOS based common gate gate amplifier, we cascade NMOS common source amplifier with PMOS common gate amplifier Fig. 1.7. This architecture gives increased gain but at the cost

Figure 1.8: Current mirror OTA

of increased power and noise. The advantage of this architecture is decoupled input and output common mode voltages and increased output swing.

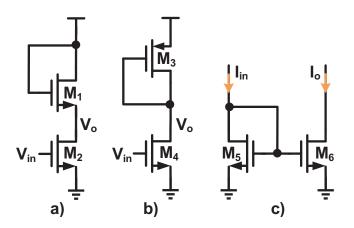

The cascode architectures take current converted by the input differential pair transistors through a low impedance nodes. Hence these typically do not require compensation as the poles created at the low impedance nodes are at higher frequencies. A current mirror based OTA is proposed Fig. 1.8, to increase the gain with the aid of number of fingers in current mirror. Here the gain is increased by increasing the number of fingers in the current mirror. This in turn increases the bias current which result in higher power consumption.

The common source telescopic amplifier can be cascaded with another common source amplifier to obtain higher gain Fig. 1.9). We obtain the maximum possible swing in this architecture as the second stage common source amplifier has only one PMOS and NMOS transistor. The swing at the output of telescopic cascoded stage is reduced by

Figure 1.9: Two stage telescopic cascoded OTA

the gain of the second stage. This amplifier gives highest gain, lowest noise. The internal high impedance node at the cascade point of common source amplifiers results in a low frequency pole which has to be compensated.

Table 1.1 shows the comparison between various operational amplifier architectures. H represents high and L represents Low in this table. If the linearity of the operational amplifier is dominated by the input differential pair, all the architectures has similar linearity performance. Similarly we assume all the OTA architectures are designed in same technology with identical power supply. The output swing is highest in current mirror OTA and two stage design. Two stage design gives the highest possible output swing, gain and contributes lower noise but suffers from the low frequency response. Hence this architecture is preferred mostly in high resolution negative feedback loops. The scaling of power supply makes the design of differential pair difficult. Further

|       | 5 transistor | Telescopic | Folded cascode | Current mirror | Two stage |

|-------|--------------|------------|----------------|----------------|-----------|

| Swing | Н            | L          | HH             | HHH            | HHH       |

| BW    | HHH          | HH         | Н              | HH             | L         |

| Gain  | L            | HH         | HH             | Н              | HHH       |

| Noise | L            | L          | HHH            | Н              | L         |

Table 1.1: Comparison of traditional OTA architectures

becomes the core of any OTA architecture, it is compared with the proposed inverter based OTA in section 1.2. A two stage inverter based two stage telescopic operational amplifier is proposed for high resolution applications.

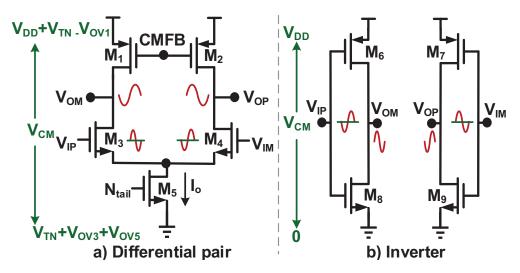

#### **1.2** Differential pair versus Inverter

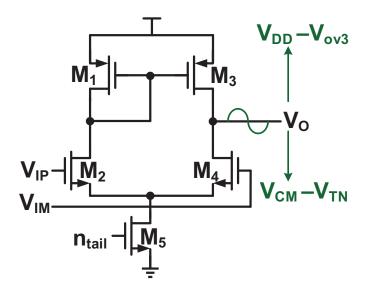

In conventional differential pair based OTAs, the minimum input common mode voltage is bounded by a threshold voltage and the overdrive voltages of the differential pair plus that of the tail source limiting the input voltage swing. Input and output common mode voltages are equal in a typical continuous time systems to avoid any common mode currents in the system. Hence the input common mode limitation restricts the overall output swing in the system. Lower supply voltage severely constraints the tail current overdrive voltage deteriorating CMRR and also prevents the use of cascode devices limiting gain. Further, the large signal linearity of differential pairs is limited by the finite tail current. Body input OTA designs is proposed in [4, 5] at lower supply voltages. However this results in lower frequency response and also increased non-linearity. Current reuse in inverters enables at least a 2X higher transconductor  $(g_m/I_d)$  efficiency compared to a differential pair. Inverters allow rail-to-rail input swing because of the class AB operation. Hence the input and output common mode can be at mid supply

Figure 1.10: Input and output swings of differential pair and inverter OTAs

for optimal signal swing at lower supply voltages. The poor PVT tolerance, CMRR and PSRR challenges inverter based designs. Non-cascoded inverter based OTA designs with common mode cancellation was proposed in [6, 7]. Linearity improvement using cancellation cancelation techniques have been proposed for higher supply voltages [8, 9, 10, 11]. Use of ring oscillators as amplifiers in switched capacitor circuits is proposed in [12].

Fig. 1.10 shows a comparison of a traditional differential pair and a pseudo differential inverter. The bias current in both the designs is assumed to be equal to  $I_o$ . The minimum input common mode voltage for the differential pair is given by Eq. 1.1 and optimal common mode voltage for inverter is half the power supply.

$$V_{CM,diff,min} = V_{T3} + V_{ov3} + V_{ov5}$$

(1.1)

The threshold voltage of the transistor  $M_{3,4}$  is higher than that of  $M_{6-9}$  due to the body effect. This results in lower swing as described by a simulation example in TSMC's 65nm CMOS technology. We will use some typical numerical numbers to illustrate our example. The overdrive voltage  $(V_{ov})$  of all the devices are assumed to 125mV. Due to body effect the transistors (M3, M4) have a threshold voltage ( $V_{TN}$ ) of 440mV (50mV above nominal). Therefore, the minimum input common mode voltage for the differential pair is  $V_{T3} + V_{OV3} + V_{OV5} = 690$ mV. This clearly limits the input signal range. Furthermore, in most continuous time systems, that are once again becoming popular due to the limited headroom for switches, the input and output common mode voltages become equal due to the DC negative feedback around the loop. Hence the minimum output common mode is also 690mV. With a power supply of 0.9V and one overdrive drop at the PMOS transistor, the maximum attainable swing is now 170mVpp. Inverter based designs ( $M_{6,8}$  and  $M_{7,9}$ ) allow rail-to-rail input swing because of the class AB operation. This translates to a maximum attainable output swing of 650mVpp (4x larger than traditional OTAs). Further the transistors do not suffer from body effect resulting in higher linearity and trans conductance.

#### **1.3** Non linearity Analysis

The linearity of a trans conductor is limited by its trans conductance linearity and output impedance linearity. The differential output current in the differential pair can be derived by assuming square law model for the transistors  $M_{3-4}$  as Eq. 1.2

$$I_{out} = -(V_{IP} - V_{IM})\beta_n \sqrt{\frac{2I_o}{\beta_n} - (V_{IP} - V_{IM})^2}$$

(1.2)

where  $\beta_n = \mu_n C_{ox} W/2L$ ,  $\mu_n$  is the mobility of the electrons,  $C_{ox}$  is the oxide capacitance and W and L are the width and length of the devices. For smaller input voltages  $(V_{IP} - V_{IM} \approx 0)$ , the output current is given by

$$I_{out,diff} = -G_{m,diff}(V_{IP} - V_{IM}) \tag{1.3}$$

where  $G_{m,diff} = \sqrt{2\beta_n I_o}$ . Eq. 1.2 also suggests that  $G_m$  falls to zero for  $(V_{IP} - V_{IM}) = \sqrt{2I_o/\beta_n}$ . The output current has odd order harmonics and even order harmonics are

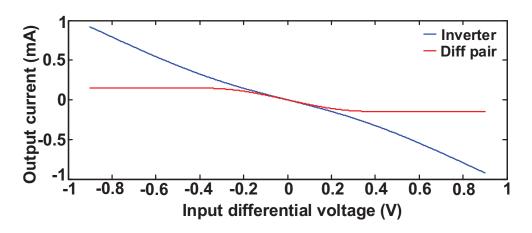

Figure 1.11: Output current of a differential pair and pseudo- differential inverter

suppressed by the differential operation. The odd order harmonics created is a result of current limitation with tail current source  $M_5$  in differential pair. Although the tail current source biases the differential pair at constant current and also give common mode rejection ratio, this results in non linearity. Further the body effect in transistors  $M_{3,4}$  also increases the non-linearity.

However the pseudo-differential output current of inverter based amplifier is given by Eq. 1.4

$$I_{out,inv} = -(V_{IP} - V_{IM}) \left(\beta_p \left[V_{DD} - V_{CM} - V_{TP}\right] + \beta_n \left[V_{CM} - V_{TN}\right]\right)$$

(1.4)

The output differential current for an inverter with transistors obeying square law is highly linear as all the even order harmonics are suppressed by the differential operation. The small signal trans conductance is given by

$$G_{m,inv} = (\beta_p [V_{DD} - V_{CM} - V_{TP}] + \beta_n [V_{CM} - V_{TN}])$$

(1.5)

Fig. 1.11 shows the output current of the differential pair and pseudo differential inverter with identical small signal transconductance. The tail current in the differential pair saturates the current to  $I_o$  resulting in nonlinearity. However the output current in an

Figure 1.12: Output impedance variation with output swing in differential pair and inverter

inverter increases with the input voltage due to its class AB operation. The non linearity in the output current of the inverter is primarily due to its short channel effects and its deviation from square law model.

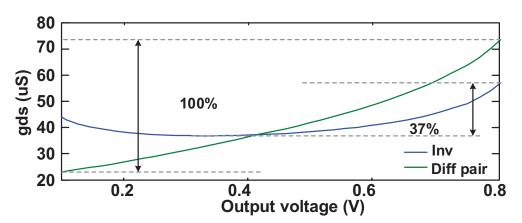

In analog design the channel length is typically selected to be higher than the minimum to increase the output impedance of the transistor. The transistors in output stage of OTA design typically has a smaller channel length to reduce the parasitic capacitance and also to create a low impedance output node. The gain of this stage is typically between 5-10. For amplifiers driving larger load currents, the non-linearity in the output impedance becomes significant. Fig. 1.12 shows the output impedance variation with output swing for class A (differential pair) and class AB (inverter) amplifiers. The output impedance of a transistor decreases with increase in the current. Hence for differential pair the conductance increases with the swing. However for inverter the PMOS current increases and NMOS current decreases with output swing resulting in lower output impedance variation. Although the output current in inverter based amplifiers are linear, unlike differential pair it strongly depends on the input common mode voltage which restricts the use of inverter based designs.

#### 1.4 Noise Analysis

The input referred noise for a differential pair and for a pseudo differential inverter is given by Eq. (1.6).

$$v_{n,diffpair}^2 = \frac{8kT\gamma}{gm_3} \left(1 + \frac{gm_1}{gm_3}\right) \tag{1.6}$$

$$v_{n,inv}^2 = \frac{8kT\gamma}{gm_6 + gm_8}$$

(1.7)

The transconductance  $g_{m3}$  is assumed to be equal to the inverter transconductance  $gm_6 + gm_8$  for the sake of comparison. The excess noise factor for the inverter is 1 which is less than that for the corresponding differential pair  $[(1 + gm_1/gm_3)]$ . This is because all the transistors in the inverter contribute both to the signal and to the noise whereas in the differential pair the load transistor  $(M_1 \text{ and } M_2)$  contribute only to the noise.

A doubling in the width of both the PMOS and NMOS transistors does not change its gain. It is equivalent to adding the gm cells in parallel where both gm and gds increases by same amount. Hence only the channel length determines the gain of the inverter. Any increase in the width of the transistor results in an increase in its gm resulting in an increase in the system UGF. This property of inverter based designs separates the gain and gm parameters simplifying design. Simulations show that with constant gm biasing, the effective gds varies less than 20% across PVT variations.

Inverter based amplifier supports higher signal swings with higher linearity and lower noise compared to differential pair based amplifiers. This makes the inverter amplifiers attractive especially at lower technologies and lower power supplies. However the dependence of the inverter amplifier's bias voltage and currents with PVT restricts their use in modern technologies.

Figure 1.13: Nauta inverter transconductor

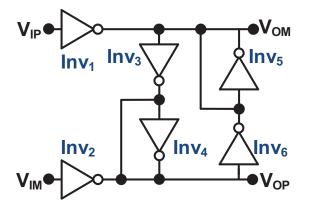

### **1.5** Inverter transconductor

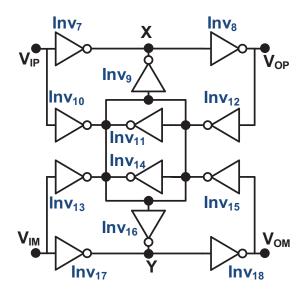

Fig. 1.13 shows the inverter transconductor circuit from Nauta [7, 13]. The inverters  $Inv_{1,3,5}$  are identical to those of the differential counterpart  $Inv_{2,4,6}$ . The common mode level of the output voltages  $V_{OP}$  and  $V_{OM}$  is controlled by the four inverters  $Inv_{3-6}$ . The output common mode voltage is at the meta stable point of the inverters  $(Inv_{4,5})$ . The common mode and differential mode impedance offered by these inverters are  $1/(g_{m3} + g_{m4})$  and  $1/(g_{m4} - g_{m3})$ . The common mode gain is given by Eq. (1.8) and the differential mode gain is given by Eq. (1.9)

$$A_{cm} \approx \frac{g_{m1}}{g_{m3} + g_{m4}} \tag{1.8}$$

$$A_d = \frac{g_{m1}}{(g_{m4} - g_{m3}) + g_{ds1} + g_{ds5} + g_{ds6}}$$

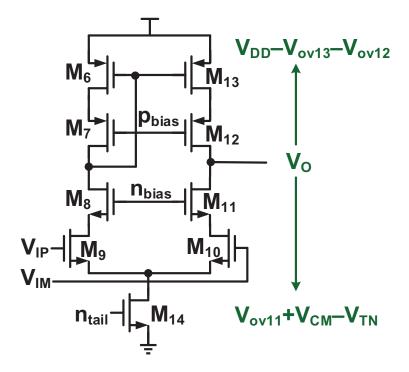

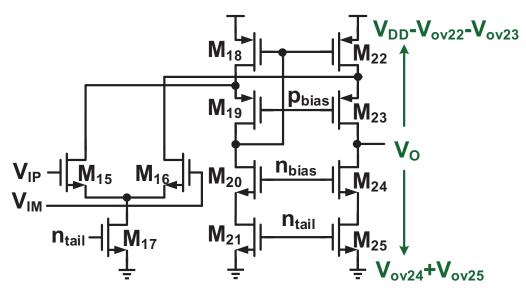

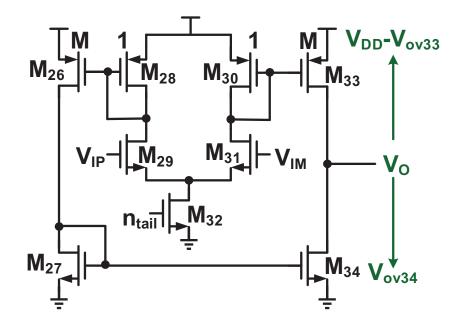

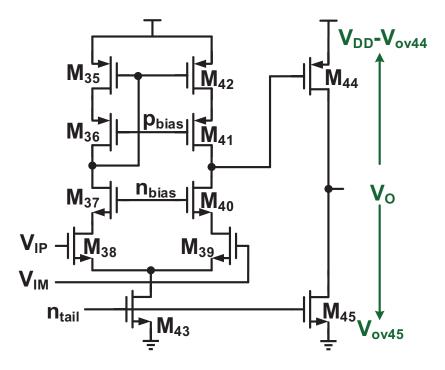

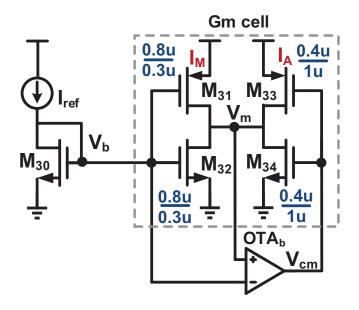

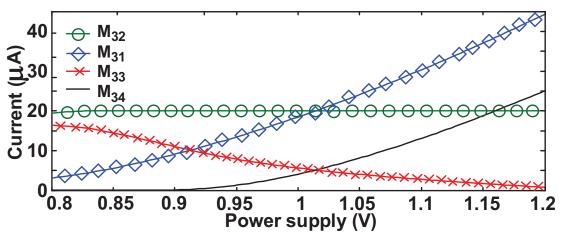

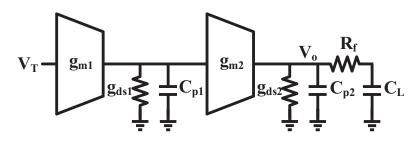

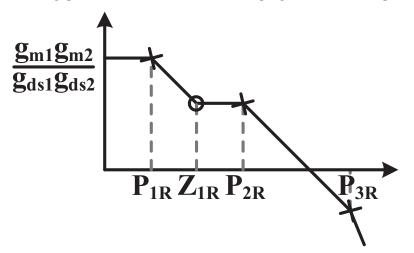

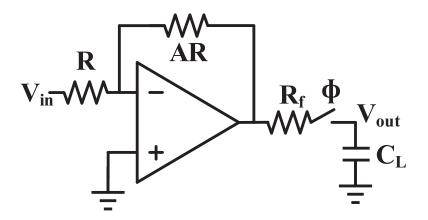

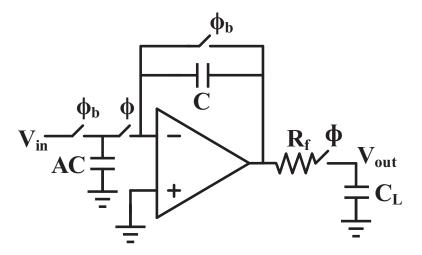

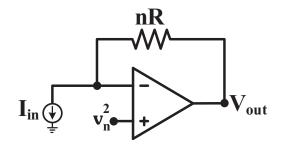

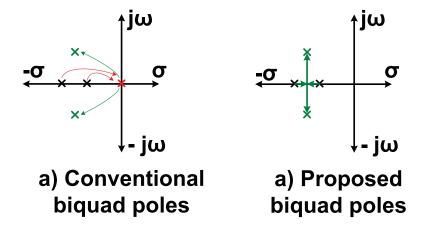

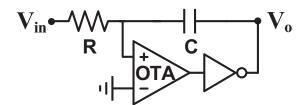

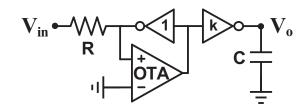

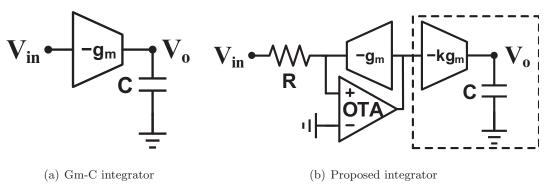

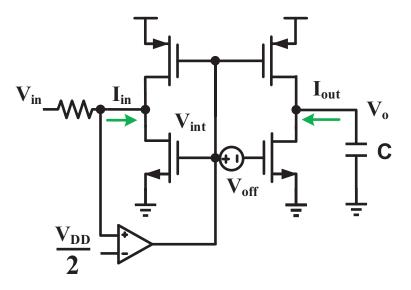

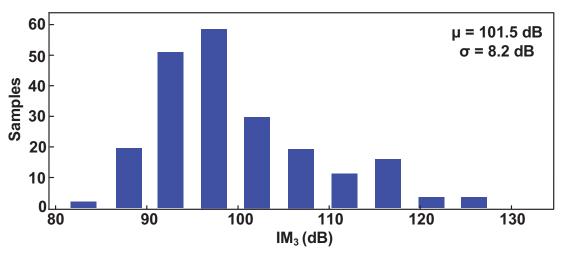

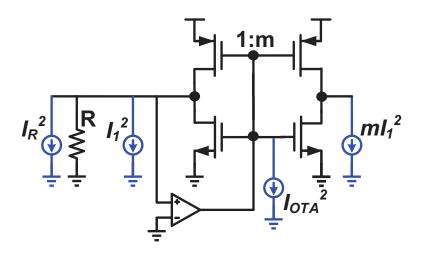

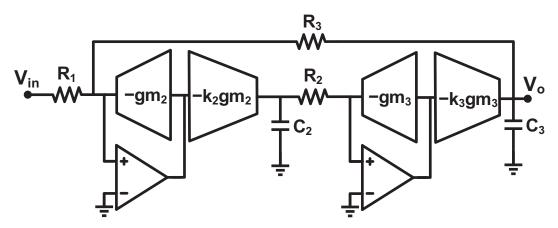

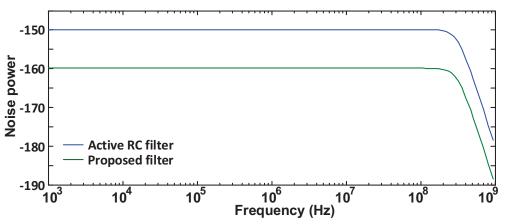

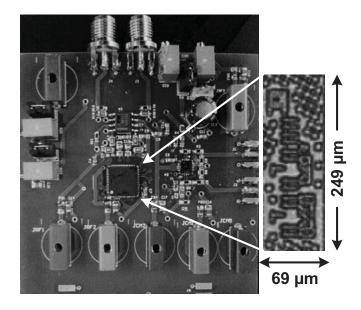

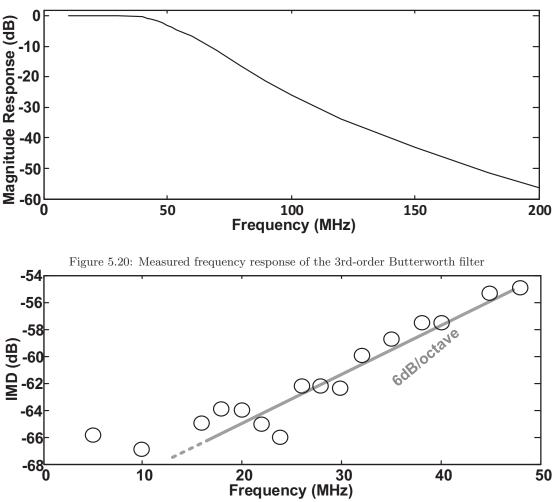

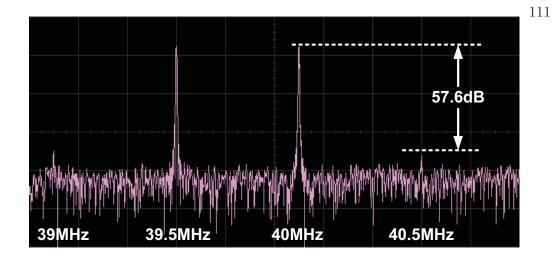

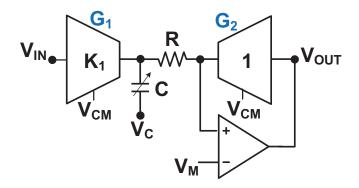

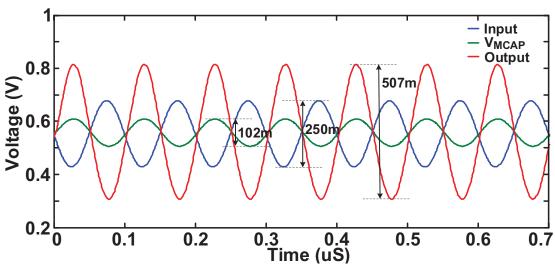

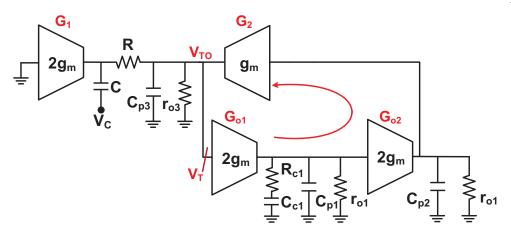

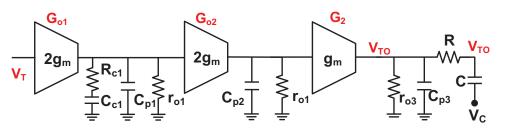

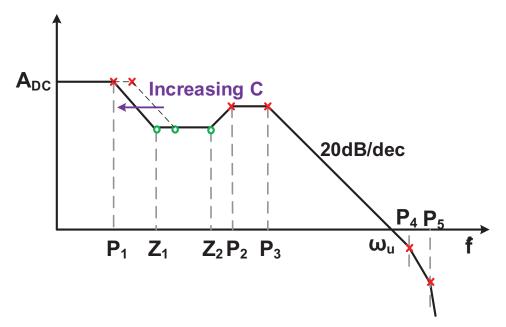

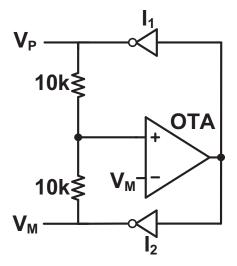

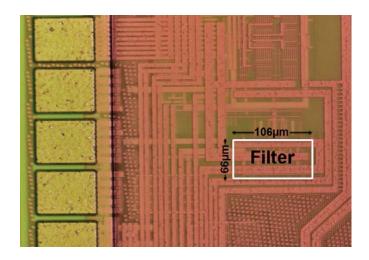

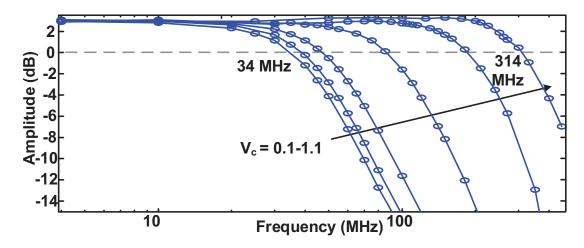

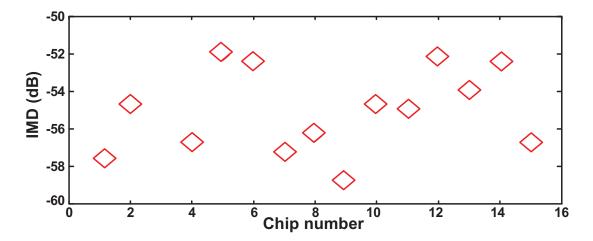

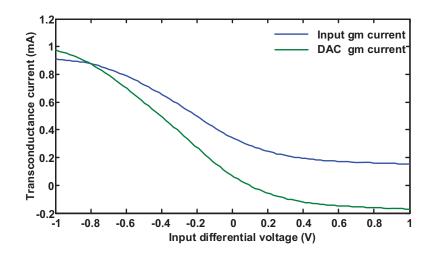

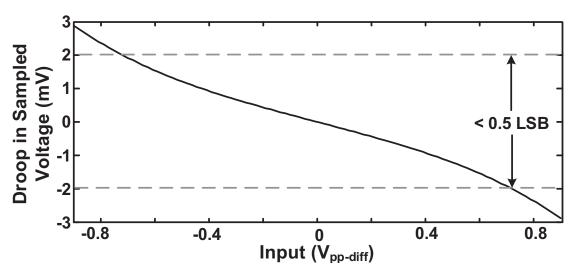

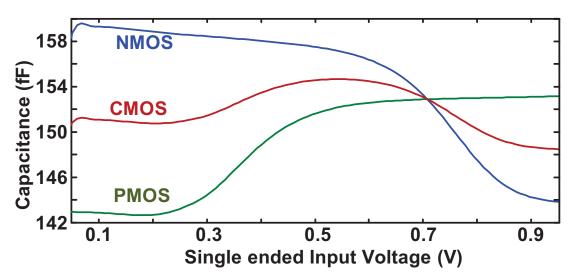

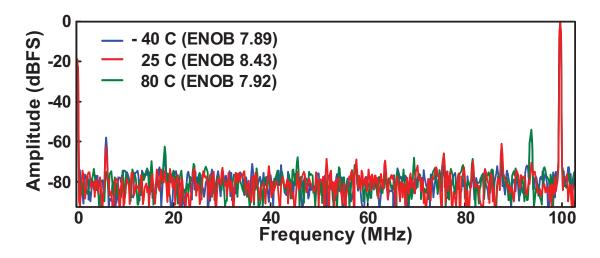

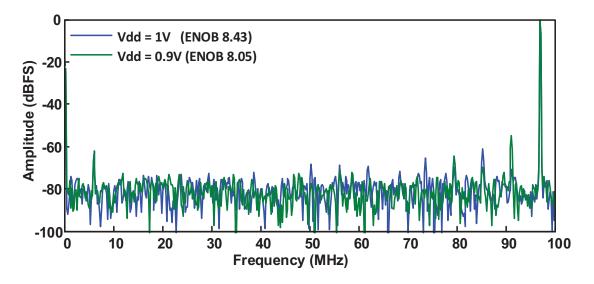

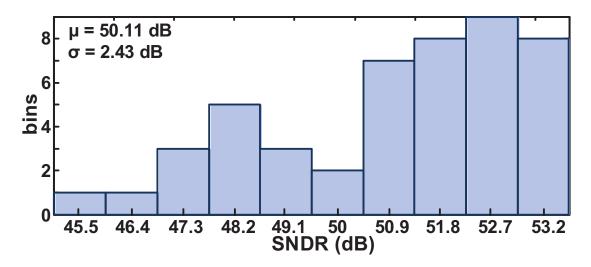

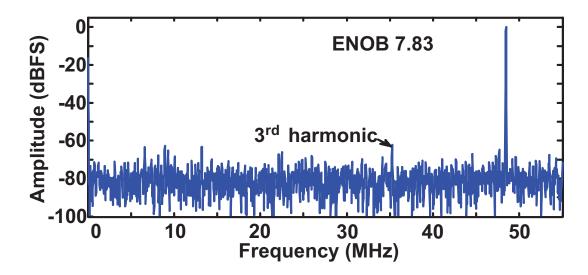

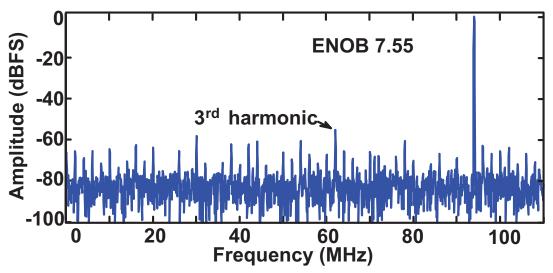

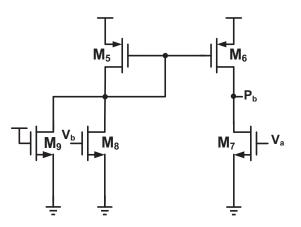

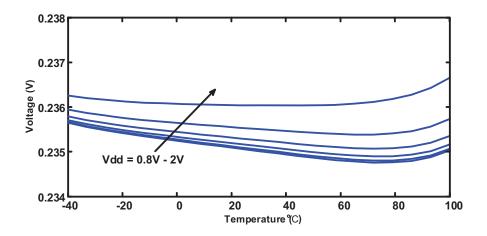

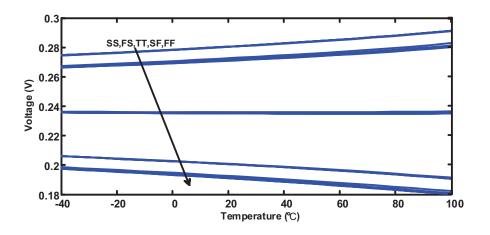

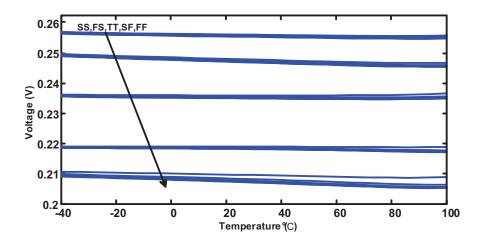

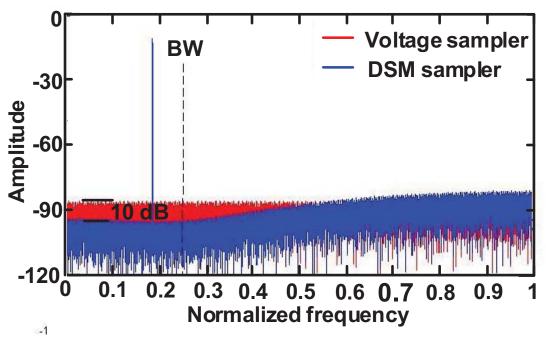

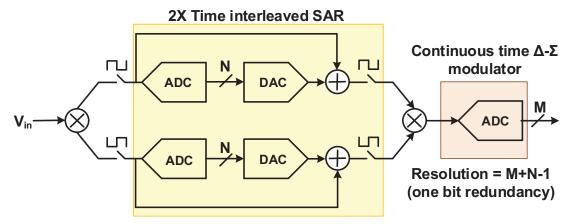

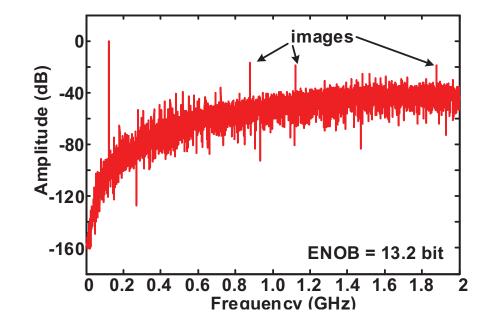

(1.9)