### Architectural Exploration of Data Recomputation for Improving Energy Efficiency

### A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

Ismail Akturk

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy

Ulya R. Karpuzcu

**July, 2017**

© Ismail Akturk 2017 ALL RIGHTS RESERVED

# Acknowledgements

I would like to thank my advisor Ulya R. Karpuzcu for her continued support, advice, and guidance through the years. She was always ready to help, and she never lost her patience and never gave up on me to make me a better researcher. I could never thank her enough.

I am grateful to my final exam committee members David Lilja, Sachin Sapatnekar, and Pen-Chung Yew for their support and time.

Furthermore, I would like to thank my colleagues in the department, existing and former members of the ALTAI, and folks in 4-166. They made my time better by their friendship; special thanks to Karen and Hari.

Finally, I would like to express my heartfelt gratitude to my family for their patience and support, especially to Aysegul.

# Dedication

All praise is due to God alone, the Sustainer of all the worlds, the Most Gracious, the Dispenser of Grace.

#### Abstract

There are two fundamental challenges for modern computer system design. The first one is accommodating the increasing demand for performance in a tight power budget. The second one is ensuring correct progress despite the increasing possibility of faults that may occur in the system.

To address the first challenge, it is essential to track where the power goes. The energy consumption of data orchestration (i.e., storage, movement, communication) dominates the energy consumption of actual data production, i.e., computation. Oftentimes, recomputing data becomes more energy efficient than storing and retrieving pre-computed data by minimizing the prevalent power and performance overhead of data storage, retrieval, and communication. At the same time, recomputation can reduce the demand for communication bandwidth and shrink the memory footprint. In the first half of the dissertation, the potential of data recomputation in improving energy efficiency is quantified and a practical recomputation framework is introduced to trade computation for communication.

To address the second challenge, it is needed to provide scalable checkpointing and recovery mechanisms. The traditional method to recover from a fault is to periodically checkpoint the state of the machine. Periodic checkpointing of the machine state makes rollback and restart of execution from a safe state possible upon detection of a fault. The energy overhead of checkpointing, however, as incurred by storage and communication of the machine state grows with the frequency of checkpointing. Amortizing this overhead becomes especially challenging, considering the growth of expected error rates as an artifact of contemporary technology scaling. Recomputation of data (which otherwise would be read from a checkpoint) can reduce both the frequency of checkpointing, the size of the checkpoints and thereby mitigate checkpointing overhead. In the second half, quantitative characterization of recomputation-enabled checkpointing (based on recomputation framework) is provided.

# Contents

| Α            | ckno              | wledge           | ements                                            | i             |

|--------------|-------------------|------------------|---------------------------------------------------|---------------|

| D            | edica             | ntion            |                                                   | ii            |

| Α            | bstra             | nct              |                                                   | iii           |

| $\mathbf{L}$ | ist of            | <b>Table</b>     | S                                                 | vii           |

| $\mathbf{L}$ | ist of            | Figur            | es                                                | viii          |

| 1            | <b>Int</b><br>1.1 | roduct<br>Struct | ion<br>ture of The Dissertation                   | <b>1</b><br>4 |

| <b>2</b>     | Mo                | tivatio          | n                                                 | 5             |

| 3            | Am                | nesiac           | : Proof-of-Concept Framework for Recomputation    | 8             |

|              | 3.1               | Introd           | luction                                           | 8             |

|              | 3.2               | Amne             | sic Execution Semantics                           | 9             |

|              |                   | 3.2.1            | Recomputation Slice $(RSlice)$                    | 10            |

|              |                   | 3.2.2            | Non-recomputable Inputs                           | 11            |

|              |                   | 3.2.3            | Side Effects                                      | 12            |

|              | 3.3               | An Ill           | ustrative Proof-Of-Concept Amnesic Implementation | 12            |

|              |                   | 3.3.1            | Amnesic Compiler and Instruction Set Extensions   | 13            |

|              |                   | 3.3.2            | Amnesic Microarchitecture                         | 15            |

|              |                   | 3.3.3            | Amnesic Scheduler                                 | 16            |

|              |                   | 3.3.4            | Putting It All Together                           | 17            |

|   |     | 3.3.5  | Storage Complexity                                                                                                                               | 18 |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.3.6  | Technicalities                                                                                                                                   | 19 |

|   | 3.4 | Evalua | ation Setup                                                                                                                                      | 20 |

|   | 3.5 | Evalua | ation                                                                                                                                            | 22 |

|   |     | 3.5.1  | Impact on Energy Efficiency                                                                                                                      | 22 |

|   |     | 3.5.2  | Impact on Instruction Count and Mix                                                                                                              | 26 |

|   |     | 3.5.3  | Memory Access Characteristics                                                                                                                    | 27 |

|   |     | 3.5.4  | RSlice Characteristics                                                                                                                           | 30 |

|   |     | 3.5.5  | Break-even Point                                                                                                                                 | 31 |

|   |     | 3.5.6  | Data Locality Analysis                                                                                                                           | 34 |

|   | 3.6 | Relate | ed Work                                                                                                                                          | 34 |

| 4 | Rec | omput  | tation Taxonomy                                                                                                                                  | 37 |

|   | 4.1 | Introd | luction                                                                                                                                          | 37 |

|   | 4.2 | Recon  | nputation Taxonomy                                                                                                                               | 38 |

|   |     | 4.2.1  | Recalculation Based Recomputation                                                                                                                | 39 |

|   |     | 4.2.2  | Prediction Based Recomputation                                                                                                                   | 40 |

|   |     | 4.2.3  | $\label{eq:Recalculation} {\rm Recalculation} \ + \ {\rm Prediction} \ {\rm Based} \ {\rm Recomputation} \ \ . \ . \ . \ . \ . \ . \ . \ . \ . $ | 40 |

|   | 4.3 | Evalua | ation Setup                                                                                                                                      | 41 |

|   | 4.4 | Evalua | ation                                                                                                                                            | 42 |

|   |     | 4.4.1  | Impact on Energy and Performance                                                                                                                 | 42 |

|   |     | 4.4.2  | Impact on Execution Semantics                                                                                                                    | 46 |

|   | 4.5 | Summ   | nary                                                                                                                                             | 50 |

| 5 | Rec | omput  | tation-enabled Checkpointing and Recovery                                                                                                        | 51 |

|   | 5.1 | Introd | luction                                                                                                                                          | 51 |

|   | 5.2 | Recon  | nputation: Basic Idea                                                                                                                            | 53 |

|   |     | 5.2.1  | Support for Recomputation                                                                                                                        | 53 |

|   |     | 5.2.2  | Recap: Recomputation Framework                                                                                                                   | 54 |

|   | 5.3 | Check  | pointing and Recovery                                                                                                                            | 55 |

|   |     | 5.3.1  | Checkpointing                                                                                                                                    | 55 |

|   |     | 5.3.2  | Error Detection and Recovery                                                                                                                     | 56 |

|   | 5.4 | Incorp | porating Recomputation in Checkpointing and Recovery                                                                                             | 57 |

|   |     |        |                                                                                                                                                  |    |

|   |       | 5.4.1   | Recomputation Enabled Checkpointing                             | 57 |

|---|-------|---------|-----------------------------------------------------------------|----|

|   |       | 5.4.2   | Recomputation Enabled Recovery                                  | 58 |

|   |       | 5.4.3   | Microarchitecture Support for Recomputation-Enabled Checkpoint- |    |

|   |       |         | ing                                                             | 58 |

|   |       | 5.4.4   | Overheads                                                       | 60 |

|   | 5.5   | Evalua  | ation Setup                                                     | 61 |

|   | 5.6   | Evalua  | ation                                                           | 63 |

|   |       | 5.6.1   | Checkpointing Overhead in Fault-Free Execution                  | 63 |

|   |       | 5.6.2   | Recovery Overhead in Fault-Occurring Execution                  | 65 |

|   |       | 5.6.3   | Checkpoint and Footprint Size Reduction                         | 68 |

|   |       | 5.6.4   | Impact of Thread Count on Checkpointing Overhead                | 69 |

|   |       | 5.6.5   | Impact of Fault Rate on Recovery Overhead                       | 72 |

|   |       | 5.6.6   | Impact of Checkpoint Frequency on Checkpointing Overhead        | 74 |

|   |       | 5.6.7   | Coordinated Local vs. Global Checkpointing                      | 77 |

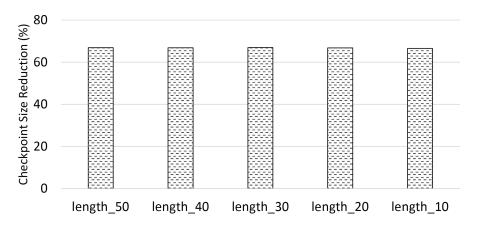

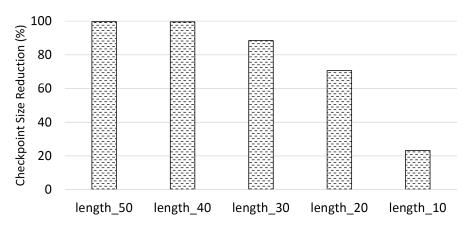

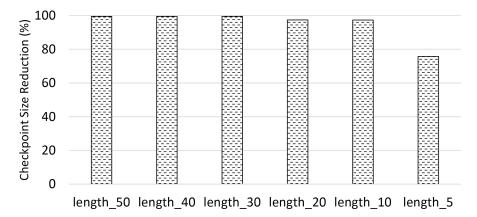

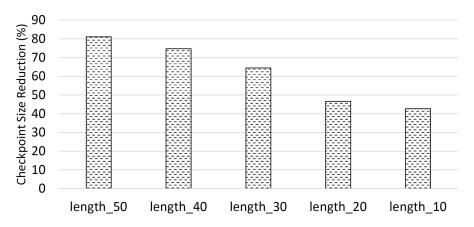

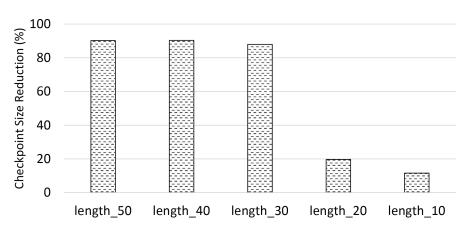

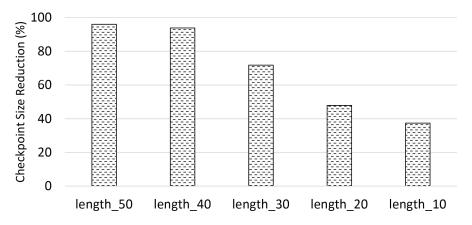

|   |       | 5.6.8   | Impact of <i>RSlice</i> Length on Checkpoint Size               | 82 |

|   | 5.7   | Relate  | ed Work                                                         | 84 |

| 6 | Cor   | nclusio | n                                                               | 87 |

| R | efere | nces    |                                                                 | 89 |

| A | ppe   | ndix A  | . Impact of <i>RSlice</i> Length on Checkpoint Size             | 97 |

# List of Tables

| 2.1 | Strong vs. weak scaling for an n-fold increase in core count. Best case      |    |

|-----|------------------------------------------------------------------------------|----|

|     | scenario, excluding communication overhead. PS: problem size                 | 6  |

| 2.2 | Energy consumption of 64-bit computation and communication adapted           |    |

|     | from $[6]$                                                                   | 7  |

| 3.1 | Benchmarks deployed to quantify the potential of amnesic execution.          | 21 |

| 3.2 | Simulated architecture to quantify the potential of amnesic execution.       | 22 |

| 3.3 | Dynamic instruction mix and energy breakdown under amnesic execution.        | 27 |

| 3.4 | Memory access profile of load instructions under classic execution, which    |    |

|     | are swapped for recomputation under $Compiler$ , $FLC$ , and $LLC$ policies, |    |

|     | respectively                                                                 | 28 |

| 3.5 | Break-even point (for <i>C-Oracle</i> )                                      | 32 |

| 4.1 | Benchmarks deployed to quantify the potential of different recomputation     |    |

|     | techniques.                                                                  | 42 |

| 5.1 | Simulated architecture to evaluate the impact of recomputation on check-     |    |

|     | pointing and recovery.                                                       | 61 |

| 5.2 | The summary of configurations evaluated.                                     | 63 |

# List of Figures

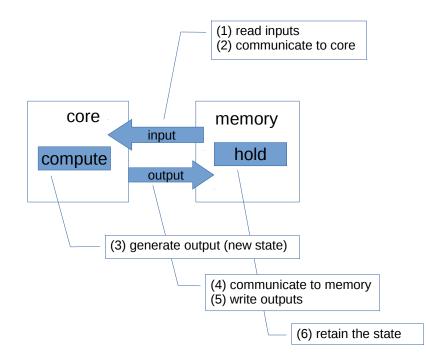

| 1.1 | Microscopic view per machine state transition.                                                                                                                      | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

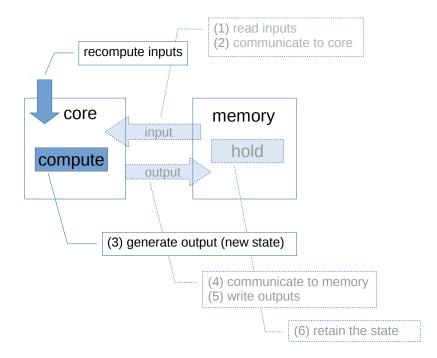

| 1.2 | Execution semantic under recomputation                                                                                                                              | 3  |

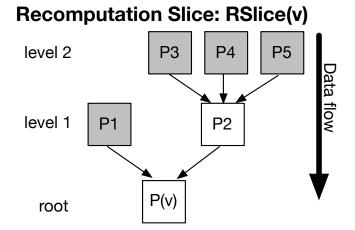

| 3.1 | Example Recomputation Slice, $RSlice(v)$                                                                                                                            | 10 |

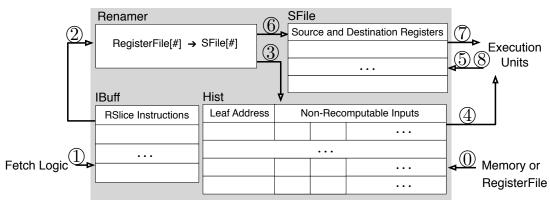

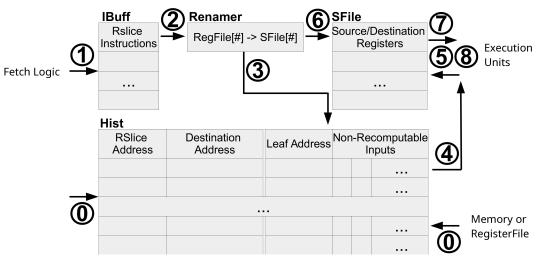

| 3.2 | Amnesic Microarchitecture & Scheduler                                                                                                                               | 15 |

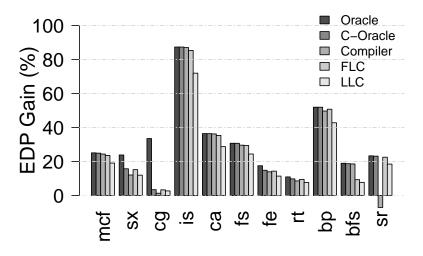

| 3.3 | EDP gain under amnesic execution.                                                                                                                                   | 23 |

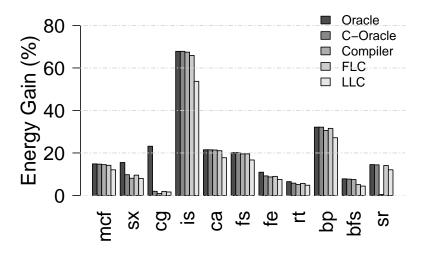

| 3.4 | Energy gain under amnesic execution.                                                                                                                                | 25 |

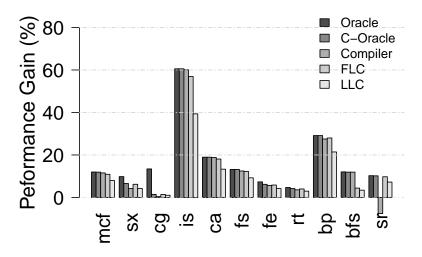

| 3.5 | % reduction in execution time.<br>                                                                                                                                  | 26 |

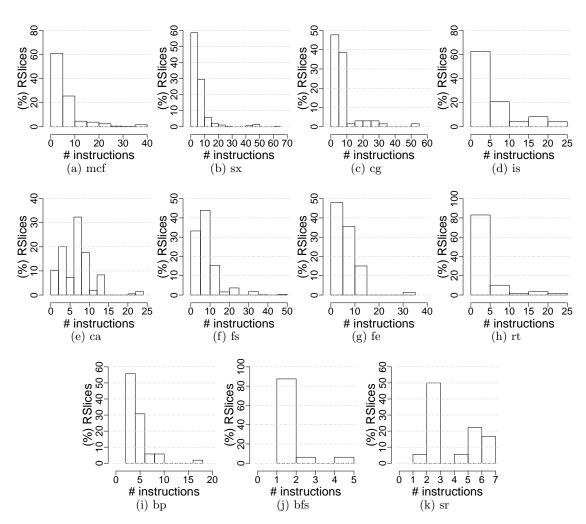

| 3.6 | Histograms of instruction count per recomputed $RSlice$ under $Compiler$                                                                                            |    |

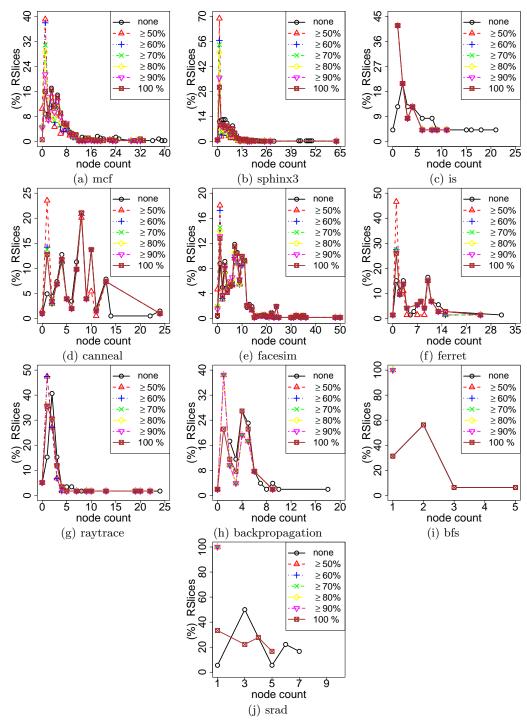

|     | policy                                                                                                                                                              | 29 |

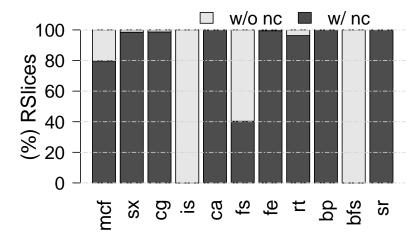

| 3.7 | % of $RSlices$ with <b>n</b> on-recomputable leaf inputs                                                                                                            | 31 |

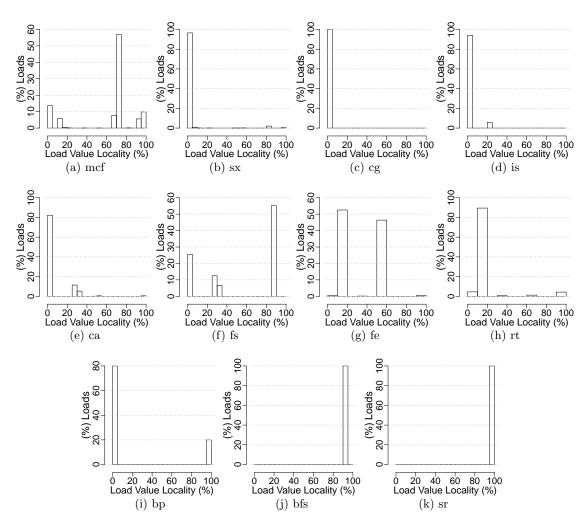

| 3.8 | % value locality of loads (under classic execution), which are swapped for                                                                                          |    |

|     | recomputation by the <i>Compiler</i> policy                                                                                                                         | 33 |

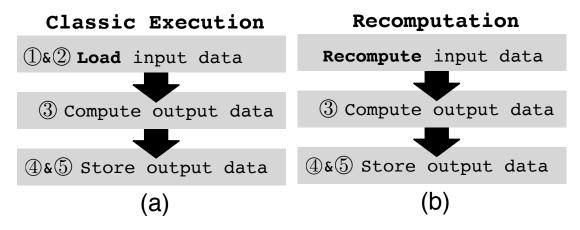

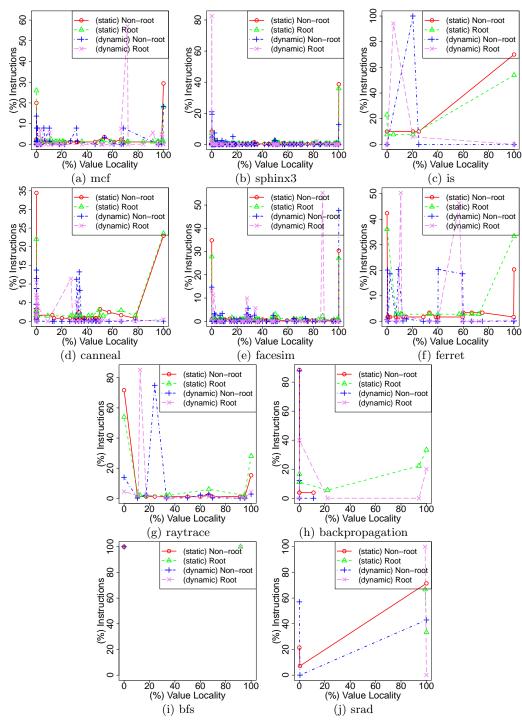

| 4.1 | Classic execution vs. Recomputation                                                                                                                                 | 37 |

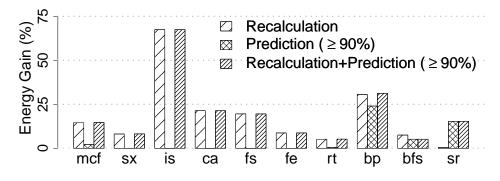

| 4.2 | Energy gain under recomputation.                                                                                                                                    | 43 |

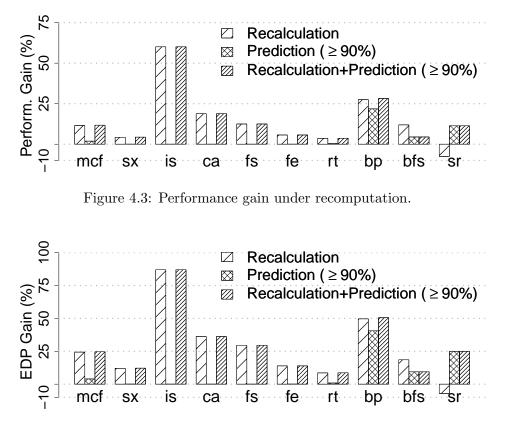

| 4.3 | Performance gain under recomputation                                                                                                                                | 44 |

| 4.4 | EDP gain under recomputation.                                                                                                                                       | 44 |

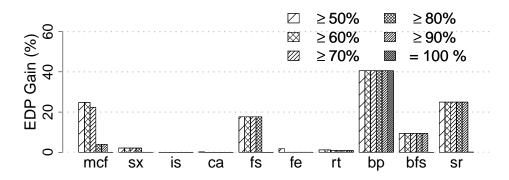

| 4.5 | EDP gain under <b>prediction</b> as a function of value locality threshold for                                                                                      |    |

|     | prediction.                                                                                                                                                         | 45 |

| 4.6 | EDP gain under <b>recalculation+prediction</b> as a function of value lo-                                                                                           |    |

|     | cality threshold for prediction.                                                                                                                                    | 46 |

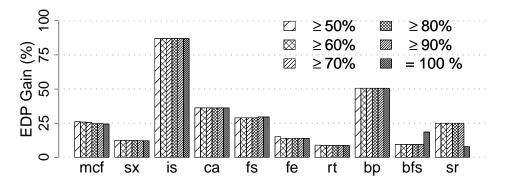

| 4.7 | Value locality of <i>RSlice</i> instructions                                                                                                                        | 47 |

| 4.8 | Node count of $RSlices$ before ( <b>recalculation</b> ) and after pruning ( <b>recal-</b>                                                                           |    |

|     | ${\bf culation+prediction}). \qquad \ldots \qquad $ | 49 |

| 5.1 | Microarchitectural support needed to facilitate recomputation.                                                                                                      | 54 |

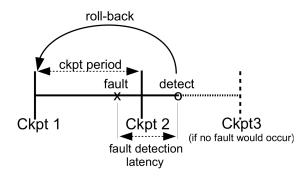

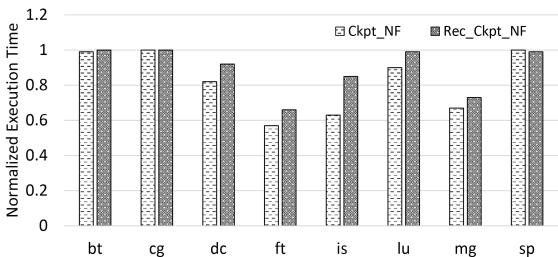

| 5.2  | Recovery from a fault                                                         | 56 |

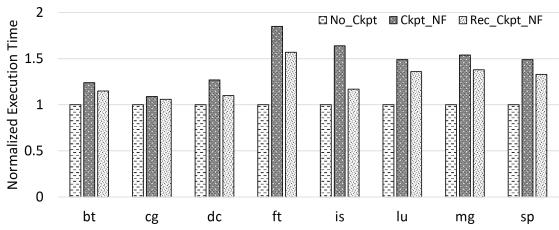

|------|-------------------------------------------------------------------------------|----|

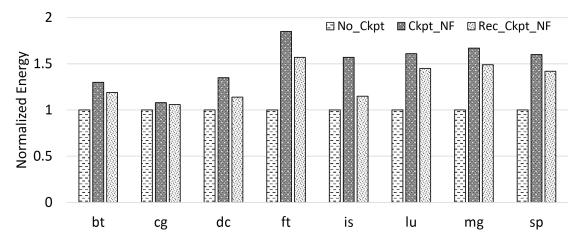

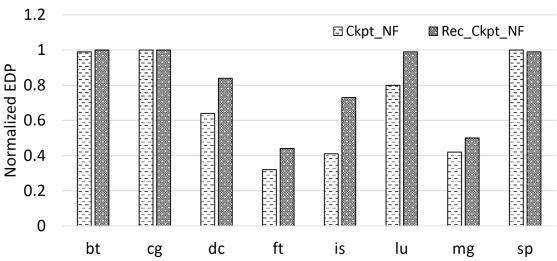

| 5.3  | Normalized execution time of benchmarks (w.r.t. $No\_Ckpt$ ) under $Ckpt\_NF$ |    |

|      | and $Rec_Ckpt_NF$ configurations                                              | 64 |

| 5.4  | Normalized energy consumption of benchmarks (w.r.t. $NoCkpt$ ) under          |    |

|      | $Ckpt_NF$ and $Rec_Ckpt_NF$ configurations                                    | 64 |

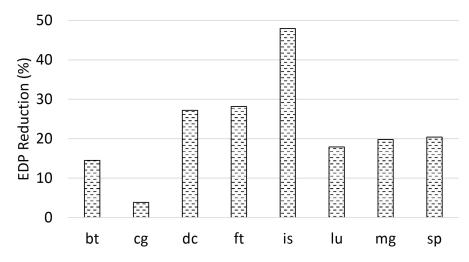

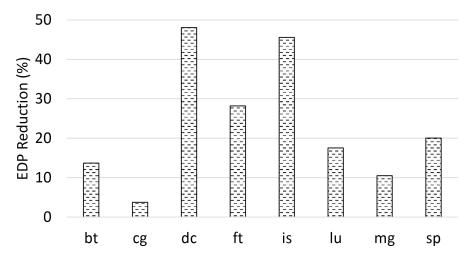

| 5.5  | EDP reduction of benchmarks under $Rec_Ckpt_NF$ configuration (w.r.t.         |    |

|      | $Ckpt_NF$ )                                                                   | 65 |

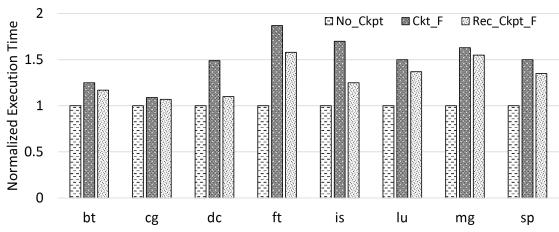

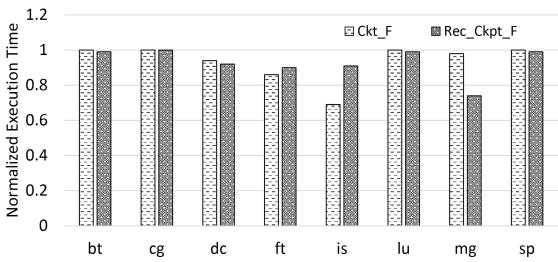

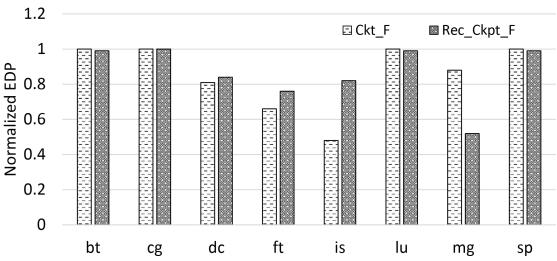

| 5.6  | Normalized execution time of benchmarks (w.r.t. $No\_Ckpt$ ) under $Ckpt\_F$  |    |

|      | and $Rec_Ckpt_F$ configurations                                               | 66 |

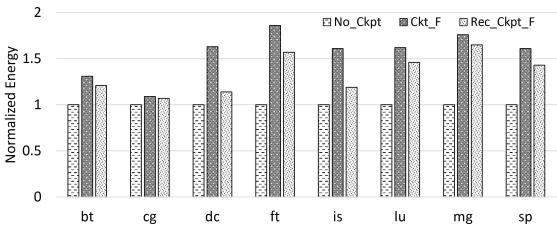

| 5.7  | Normalized energy consumption of benchmarks (w.r.t. $NoCkpt$ ) under          |    |

|      | $Ckpt_F$ and $Rec_Ckpt_F$ configurations                                      | 67 |

| 5.8  | EDP reduction of benchmarks under $Rec_Ckpt_F$ configuration (w.r.t.          |    |

|      | $Ckpt_F$ )                                                                    | 67 |

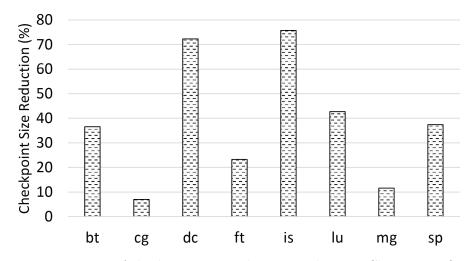

| 5.9  | Percentage of checkpoint size reduction under $Rec_Ckpt_NF$ configuration.    | 69 |

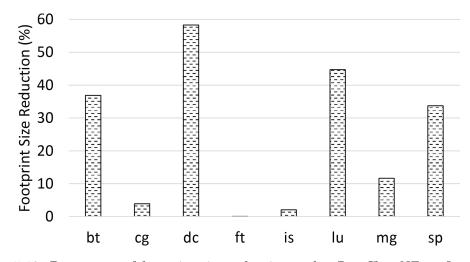

| 5.10 | Percentage of footprint size reduction under $Rec_Ckpt_NF$ configuration.     | 70 |

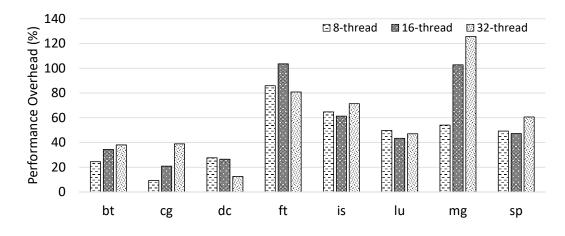

| 5.11 | Performance overhead of checkpointing for 8- 16- and 32-threaded execu-       |    |

|      | tions under $Ckpt_NF$ configuration                                           | 71 |

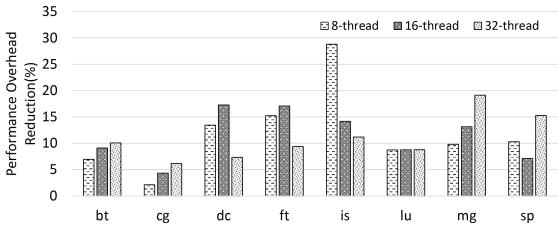

| 5.12 | Performance overhead reduction of checkpointing for benchmarks running        |    |

|      | with 8-, 16-, and 32-threads under $Rec_Ckpt_NF$ configuration                | 72 |

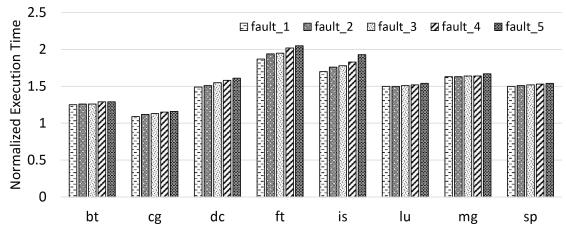

| 5.13 | Normalized execution time under $Ckpt_F$ (w.r.t. $NoCkpt$ ) with different    |    |

|      | fault rates.                                                                  | 73 |

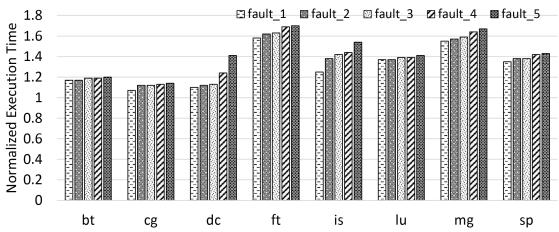

| 5.14 | Normalized execution time under $Rec_Ckpt_F$ (w.r.t. $No_Ckpt$ ) with dif-    |    |

|      | ferent fault rates                                                            | 74 |

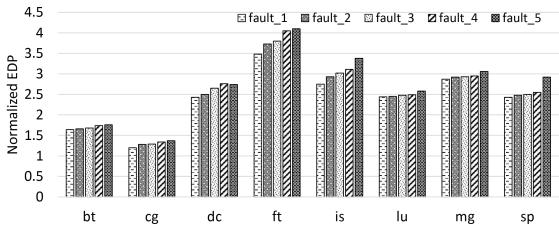

| 5.15 | Normalized EDP under $Ckpt_F$ (w.r.t. $No_Ckpt$ ) with different fault rates. | 75 |

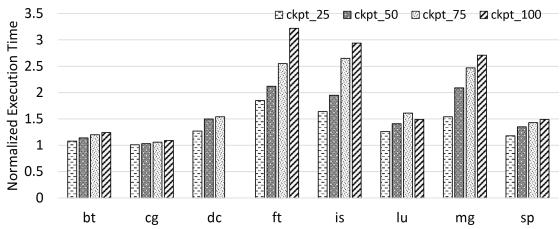

| 5.16 | Normalized execution time under $Ckpt_NF$ (w.r.t. $NoCkpt$ ) with differ-     |    |

|      | ent checkpoint frequencies                                                    | 76 |

| 5.17 | Normalized execution time under $Rec_Ckpt_NF$ (w.r.t. $No_Ckpt$ ) with        |    |

|      | different checkpoint frequencies                                              | 77 |

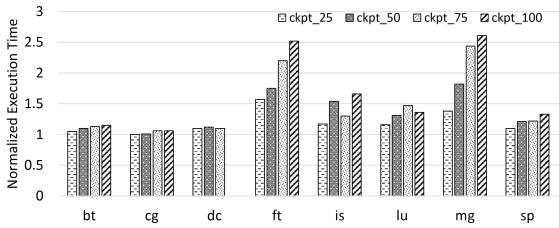

| 5.18 | Normalized EDP under $Ckpt_NF$ (w.r.t. $NoCkpt$ ) with different check-       |    |

|      | point frequencies.                                                            | 77 |

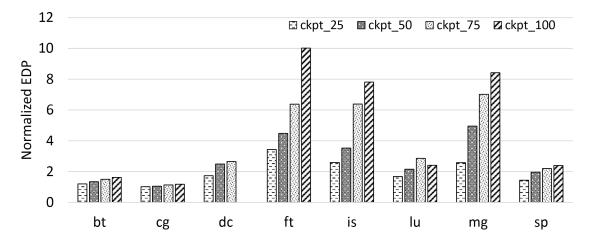

| 5.19 | Normalized execution time of $Ckpt_NF$ and $Rec_Ckpt_NF$ for coordinated                           |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | local checkpointing (w.r.t. $Ckpt_NF$ and $Rec_Ckpt_NF$ for global check-                          |    |

|      | pointing, respectively)                                                                            | 78 |

| 5.20 | Normalized EDP of $Ckpt_NF$ and $Rec_Ckpt_NF$ for coordinated local                                |    |

|      | checkpointing (w.r.t. $Ckpt_NF$ and $Rec_Ckpt_NF$ for global checkpoint-                           |    |

|      | ing, respectively)                                                                                 | 79 |

| 5.21 | Normalized execution time of $Ckpt_F$ and $Rec_Ckpt_F$ for coordinated lo-                         |    |

|      | cal checkpointing (w.r.t. $Ckpt_F$ and $Rec_Ckpt_F$ for global checkpointing,                      |    |

|      | respectively)                                                                                      | 81 |

| 5.22 | Normalized EDP of $Ckpt_F$ and $Rec_Ckpt_F$ for coordinated local check-                           |    |

|      | pointing (w.r.t. $Ckpt_F$ and $Rec_Ckpt_F$ for global checkpointing, respec-                       |    |

|      | tively)                                                                                            | 82 |

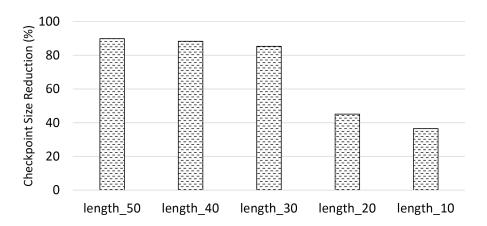

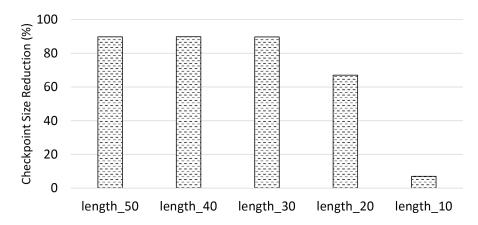

| 5.23 | Total checkpoint size reduction as a function of $RSlice \ length \ for \ bt. \ .$                 | 83 |

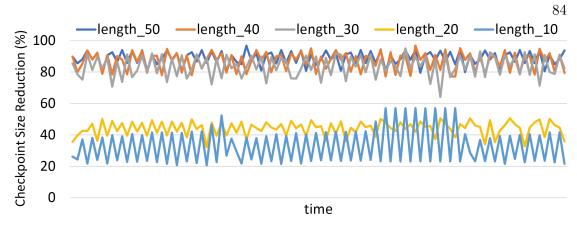

| 5.24 | Impact of <i>RSlice</i> length on checkpoint size over time for bt                                 | 84 |

| A.1  | Total checkpoint size reduction as a function of $RSlice \ {\rm length} \ {\rm for} \ {\rm cg.}$   | 97 |

| A.2  | Total checkpoint size reduction as a function of $RSlice \ {\rm length} \ {\rm for} \ {\rm dc.}$   | 98 |

| A.3  | Total checkpoint size reduction as a function of $RSlice$ length for ft                            | 98 |

| A.4  | Total checkpoint size reduction as a function of $RSlice$ length for is                            | 98 |

| A.5  | Total checkpoint size reduction as a function of $RSlice$ length for lu                            | 99 |

| A.6  | Total checkpoint size reduction as a function of $RSlice \ {\rm length} \ {\rm for} \ {\rm mg.}$ . | 99 |

| A.7  | Total checkpoint size reduction as a function of $RSlice \ {\rm length} \ {\rm for} \ {\rm sp.}$   | 99 |

|      |                                                                                                    |    |

## Chapter 1

## Introduction

Under contemporary scaling, a given chip area can still accommodate more compute engines (in the form of general-purpose cores or accelerators) each technology generation. However, cooling and power delivery limitations prevent a proportional expansion of the power budget. As a result, we can simultaneously utilize only a progressively diminishing fraction of on-chip resources, and the rest has to stay un-powered, aka *dark* [1, 2]. To illuminate dark silicon, we need to carefully track where the power goes among the components of the chip. The data and control flow throughout the execution of a program trigger a sequence of machine state transitions. As depicted in Figure 1.1, each state transition encompasses the following tasks:

- retrieval of input state (i.e., inputting)

- compute output state from inputs (i.e., processing)

- write output state (i.e., outputting)

- hold new machine state (i.e., storing)

These tasks are carried over six basic steps: Upon retrieval of input state (i.e., (1) & (2)), compute engines derive output state from inputs (i.e., (3)). Next comes storage of output state (i.e., (4) & (5)) and retention of new machine state (i.e., (6)) until the next transition.

Power goes to all of these steps, with the actual computation (i.e., (3)) representing the least energy-hungry [3, 4].

Figure 1.1: Microscopic view per machine state transition.

The building blocks of classic computing, transistors, consume dynamic power as they toggle and static power due to leakage when turned off (because of restrictions from technology scaling). Typically only a subset of transistors toggle during a state transition, therefore, dynamic-power-heavy steps such as (3) can also consume static power. On the other hand, static-power-heavy steps such as (6) also consume dynamic power due to control logic. The breakdown of total power consumption across steps, and the ratio of dynamic to static power per step evolve as a function of the operating regime and technology.

Unfortunately, emerging technology solutions are not mature enough to meet the growing capacity, bandwidth, and performance demand with-in the stringent power budget. Imbalances between logic and memory technologies further result in rising time and power, hence energy (time  $\times$  power) expenditure in steps (1), (2), (4) and (5) (along with (6) depending on the memory technology) [3, 4]. As a consequence, reproducing, i.e., recomputing data oftentimes becomes more energy efficient than storing

and retrieving pre-computed data.

Data recomputation replaces the load of inputs with the reproduction of the input data. Step (1) incurs the time and power overhead of the memory access to perform the read; and (2) incurs the time and power overhead of the subsequent communication of inputs to the compute engines. Recomputation transforms the overhead of (1) & (2) to the overhead of the recomputation of inputs. The energy savings comes from (1) & (2) being much more energy-hungry than computation (i.e., (3)).

Replacing loads with recomputation may unlock further opportunities for energy savings: Each input represents the output of a previous step in execution. In other words, each consumer load has a matching producer store. For each load replaced with recomputation, the corresponding store (to the same memory address) can become redundant if no other load (from the same address) depends on it. Therefore, recomputation can also filter out output stores and cut off the time and power overhead of (4) & (5). Step (4) incurs the overhead of communication of outputs to memory; and (5) incurs the overhead of the subsequent memory access to perform the write.

Figure 1.2: Execution semantic under recomputation.

Putting it all together, data recomputation can improve energy efficiency by

- Replacing input loads with recomputation of inputs, hence transforming (1) & (2) into the less energy-hungry (3).

- Filtering out stores which represent the producers of the loads replaced with recomputation, hence cutting off the overhead of (4) & (5) (along with (6) depending on the memory technology).

#### 1.1 Structure of The Dissertation

The rest of the dissertation is organized as follows:

- Chapter 2 presents the motivation behind the data recomputation and its potential to improve energy efficiency.

- Chapter 3 illustrates a proof-of-concept recomputation framework and provides quantitative characterization.

- Chapter 4 explores different forms of recomputation and provides a recomputation taxonomy.

- Chapter 5 introduces recomputation-enabled checkpointing, and provides quantitative characterization.

- Chapter 6 summarizes our contribution and concludes the discussion.

## Chapter 2

# Motivation

In general, the communication of data can be categorized into two. The first one is *vertical* communication where data is communicated to the compute engine through local memory hierarchy. The data retrievals performed by sequential applications are examples of this kind of communication. It can also be referred as intra-core communication. The second one is *horizontal* communication where data generated by a compute engine is communicated to the other compute engines through memory (in case of shared-memory system), or through off-chip interconnection network (in case of distributed memory system). Since data communication takes place across the compute engine boundaries, this type of communication. Regardless of type, communication energy dominates the energy used for actual data production, i.e. computation. Therefore, oftentimes, recomputing data becomes more energy efficient than communicating data in both horizontal (i.e., inter-core) and vertical (i.e., intra-core) directions.

The magnitude and the frequency of inter-core communication depends on how the problem being solved distributes the data among the cores. Problem size dictates the total amount of data processed across all cores. As more cores become available, the problem can scale in two distinct ways to translate the increase in core count into enhanced performance (as measured by the total amount of data processed over the overall processing time): *strong scaling* or *weak scaling*.

Table 2.1 captures how the total and per core problem size (PS), execution time (t), and throughput performance (PS/t) evolve for an n-fold increase in core count. Under

|         | (Total) | PS per | time |      | PS share   |

|---------|---------|--------|------|------|------------|

| Scaling | PS      | core   | (t)  | PS/t | (per core) |

| Strong  | -       | /n     | /n   | ×n   | /n         |

| Weak    | ×n      | -      | -    | ×n   | /n         |

Table 2.1: Strong vs. weak scaling for an n-fold increase in core count. Best case scenario, excluding communication overhead. PS: problem size.

strong scaling, the overall problem size, the total amount of data processed, remains constant. Each core processes progressively smaller chunk of data as the core count increases (*PS per core* decreases by  $n\times$ ), and in return finishes earlier. As a result, *PS/t* increases by  $n\times$ . The share of the problem per core reduces proportionally to the (increase in) core count.

On the other hand, under weak scaling [5], the problem size per core (thus the amount of data processed per core) remains constant which renders no change in the per core processing time (which dictates the overall processing time) as the core count increases. At the same time, the overall problem size (the total amount of data processed across all cores), grows proportionally to the (increase in) core count (increases by  $n \times$ ). Therefore, each core processes a progressively smaller fraction of the total amount of data as the core count increases as tabulated in the last column. The share of the problem per core still reduces proportionally to the (increase in) core count.

Under both scaling scenarios, higher levels of concurrency imply a lower fraction of the total amount of data in close physical proximity to each core, which hurts *data locality*, and increases the likelihood of more frequent communication. As concurrency hurts data locality, each core must spend both more time and power in communication. Consequently, communication energy, as induced by data movement and the orchestration thereof, is expected to dominate computation energy [3].

Emerging non-volatile memories can minimize hold energy due to the premise of (practically) zero static power, but suffer from excessive write energy. Thus memory energy would still dominate computation energy.

Table 2.2 adapted from [6], shows how communication energy, as characterized by a 64-bit data transfer across chip, changes as technology scales. Communication energy increases from  $1.55 \times$  computation energy at 40nm to approximately  $6 \times$  at 10nm

| Process Technology             | 40nm           | 10nm              |                |

|--------------------------------|----------------|-------------------|----------------|

| Operating Voltage              | 0.9V           | 0.75V (HP)        | 0.65V (LP)     |

| 64-bit double precision FLOP   | 50pJ           | 8.7pJ             | 6.5pJ          |

| 64-bit transfer on chip (10mm) | 77.5pJ (1.55x) | 50.02 pJ (5.75 x) | 37.5pJ (5.77x) |

Table 2.2: Energy consumption of 64-bit computation and communication adapted from [6].

(considering processes optimized for high performance, HP, and low power, LP). Since communication energy tends to grow with distance, a similar trend applies for off-chip communication. Therefore, communication energy becomes even more prominent with technology scaling.

3D Stacking, or emerging photonics based interconnects, can render a lower off-chip (and potentially on-chip) communication energy when compared to state-of-the-art, but would not alter the communication-centric nature of parallel processing: Engaging more cores into computation reduces per core work, therefore, the mean time to communication, orthogonal to the technology of the communication medium. Accordingly, communication would still be the most energy-hungry phase.

As a consequence, recomputing data can become more energy-efficient than storing and retrieving pre-computed data. In this dissertation, we hence investigate the effectiveness of recomputing data values in minimizing, if not eliminating, the overhead of expensive off-chip memory accesses.

## Chapter 3

# Amnesiac: Proof-of-Concept Framework for Recomputation

#### 3.1 Introduction

In this chapter, we investigate the effectiveness of recomputing data values in minimizing, if not eliminating, the overhead of expensive off-chip memory accesses. The idea is replacing a load with a sequence of instructions to recompute the respective data value, only if it is more energy-efficient. We call the resulting execution model *amnesic*<sup>1</sup> to contrast recomputation with conventional, *classic* execution.

Whether recomputation of a data value v can improve the energy efficiency or not tightly depends on where in the memory hierarchy the corresponding load would be serviced under classic execution, i.e., where in the memory hierarchy v resides. This is because the location of v in the memory hierarchy dictates the energy consumption of the respective load,  $E_{ld,v}$ , which in turn sets the energy budget for recomputation. Recomputation of v itself incurs an energy cost,  $E_{rc,v}$ , due to the (re)execution of the sequence of instructions to generate v. We will refer to each instruction in such a sequence as a *recomputing* instruction. Therefore, unless  $E_{ld,v}$  exceeds  $E_{rc,v}$ , amnesic execution cannot improve energy efficiency.

Under amnesic execution, the sequence of recomputing instructions to generate v

<sup>&</sup>lt;sup>1</sup> amnesia [am'n $\bar{e}ZH\bar{e}$ ]: noun, a partial or total loss of memory. amnesiac [am'n $\bar{e}z\bar{e}$ ,ak], amnesic [-zik, -sik]: noun & adjective.

form a backward slice, which we will refer to as *recomputation slice*, *RSlice*. The first instruction in the slice is the immediate producer of v, P(v). To be able to (re)execute P(v), each input operand of P(v) should be readily available at the anticipated time of recomputation. This may not always be the case, and (re)execution of P(v) may trigger the re(execution) of producers of P(v)'s input operands, recursively.

The recomputation slice to generate v, RSlice(v), can grow by tracking producerconsumer dependencies for recomputing instructions, however, not indefinitely. First of all, the energy cost of recomputation of v,  $E_{rc,v}$ , increases with the number of recomputing instructions in RSlice(v), and amnesic execution cannot be energy-efficient if  $E_{rc,v}$ exceeds the energy consumption of the respective load,  $E_{ld,v}$ . At the same time, not all of the input operands of recomputing instructions can be (re)generated by recomputation. This may be the case if input operands correspond to (i) read-only values to be loaded from memory, such as program inputs; or (ii) register values which are lost, i.e., overwritten at the time of recomputation.

Swapping loads for recomputation slices can reduce the pressure on memory bandwidth and unlock further opportunities for energy savings: For each load replaced with an *RSlice*, the corresponding store (to the same memory address) can become redundant if no other load (from the same address) depends on it. Therefore, amnesic execution can also filter out energy-hungry stores, and reduce the pressure on memory capacity by shrinking the memory footprint.

Under amnesic execution, the workload becomes more compute-intensive to make a better use of classic processors optimized for computation, as opposed to communication. In the following, we quantitatively characterize the energy efficiency potential of amnesic execution.

#### **3.2** Amnesic Execution Semantics

Under amnesic execution, an energy-hungry load is swapped with a sequence of recomputing instructions, which form a recomputation slice, *RSlice*, iff the energy cost of recomputation along the *RSlice* remains below the energy consumption of the respective load. In other words, the energy consumption of the load sets the energy budget for recomputation along the *RSlice*. If the anticipated energy cost of recomputation

Figure 3.1: Example Recomputation Slice, RSlice(v).

exceeds this budget, the respective load is performed and amnesic execution becomes equivalent to classic execution.

#### 3.2.1 Recomputation Slice (*RSlice*)

For each data value v to be recomputed under amnesic execution, data dependencies determine the order of the recomputing instructions in RSlice(v). RSlice(v) includes the immediate producer instruction of v, P(v), and possibly, producer instructions of the input operands of P(v), in a recursive manner. Producer instructions may come from different basic blocks or functions.

Recomputation slices are very unlikely to comprise all producer instructions (i.e., producers of the producers) along a dependency chain, as the energy cost of recomputation along an *RSlice* increases with the number of recomputing instructions, and can easily exceed the energy consumption of the respective load. Amnesic execution prohibits recomputation in this case.

Each recomputation slice, RSlice(v), can be regarded as an upside-down tree with P(v) residing at the root. Each node represents a producer instruction to be (re)executed. During recomputation along RSlice(v), data flows from the leaves to the root. Figure 3.1 demonstrates an example. Nodes at level 1 correspond to immediate producers of the (input operands of the) root, nodes at level *l* correspond to the producers of nodes at

level *l-1*. The number of incoming branches at each node reflects the number of producers of the node. Hence, RSlice(v) is not necessarily a balanced tree. As (re)executing only a finite number of nodes can fit into the energy budget set by  $E_{ld,v}$ , RSlice(v) cannot grow indefinitely. At the same time, the energy cost of recomputation along RSlice(v) includes the cost of retrieving input operands of the leaf nodes (which cannot rely on producers to recompute their inputs).

In the example from Figure 3.1, P1 and P2 at level 1 correspond to producers of P(v)'s input operands. (Re)execution of P1 does not require any more (re)execution. (Re)execution of P2, on the other hand, requires the (re)execution of three of P2's producers: P3, P4, and P5, respectively. The leaf producers are all shaded in gray. The leaves either represent terminal instructions which do not have any producers (e.g., instructions with constants as input operands), or instructions for which (re)execution of their producers is not energy-efficient. Amnesic execution can only function, if the input operands of leaf instructions are available at their anticipated time of (re)execution.

#### 3.2.2 Non-recomputable Inputs

Not all of the input operands of leaf instructions of an *RSlice* can be (re)generated by recomputation. This may be the case if input operands correspond to (i) read-only values to be loaded from memory, such as program inputs; or (ii) register values which are lost, i.e., overwritten at the time of recomputation. We will refer to such input operands as *non-recomputable* inputs. For amnesic execution to work, non-recomputable inputs of *RSlice* leaves should not only be available at the anticipated time of recomputation, but also be retrievable in an energy-efficient manner. Recomputation cannot eliminate any memory access to retrieve the non-recomputable inputs of *RSlice* leaves. If non-recomputable inputs do not reside in close physical proximity to the processor, the energy cost of their retrieval may easily exceed  $E_{ld,v}$ , rendering recomputation useless. In Section 3.3.2, we discuss dedicated buffering for non-recomputable inputs. No dedicated buffering is necessary if the leaf input operands correspond to constants or live register values.

#### 3.2.3 Side Effects

For the discussion in this chapter, we focus on single-threaded amnesic execution<sup>2</sup>. Therefore, within the course of execution, recomputation along only one *RSlice* can be performed at a time. Amnesic execution should prevent corruption of the architectural state during recomputation, which can be achieved by allocating dedicated buffers (Section 3.3.2) similar to classic microarchitectural storage for speculative state.

Amnesic execution can orchestrate exception handling similar to exception handling under speculation, as well: record exceptions as long as recomputation along an *RSlice* is taking place, and defer their handling after recomputation finishes. However, we may need to revisit the definition of (im)precise exceptions in this case, since recomputation modifies the architectural control flow by executing extra (recomputing) instructions, as opposed to speculation.

## 3.3 An Illustrative Proof-Of-Concept Amnesic Implementation

The critical question under amnesic execution is when to fire recomputation. Potentially, the compiler can extract RSlice(v) for each load (to read v), by tracking data dependencies. Whether recomputation along RSlice(v) is more energy-efficient than performing the respective load, however, depends on where in the memory hierarchy vresides. Being able to only speculate where v can reside during execution, the compiler can at most probabilistically estimate the energy consumption of the respective load,  $E_{ld,v}$ , which sets the energy budget for recomputation. For each v where recomputation is estimated to be more energy-efficient, the compiler can modify the binary to swap the load for RSlice(v). In the following, we will discuss various implementation options and how microarchitectural support can help.

$<sup>^2</sup>$  Under parallel execution, communication with memory expands along two dimensions: accesses to thread-local data and accesses to shared data. In this chapter, we focus on the first, in the context of single-threaded execution. In principle, loads swapped for recomputation may be triggered by coreto/from-memory (thread-local) or core-to-core (shared) communication.

The basic proof-of-concept implementation covered in this section features an amnesic compiler (Section 3.3.1), microarchitectural support for amnesic execution (Section 3.3.2), and a runtime (instruction) scheduler to orchestrate amnesic execution (Section 3.3.3). We first let the compiler identify and annotate a set of independent recomputation slices. Then, at runtime, the amnesic scheduler fires or skips recomputation along each RSlice(v), by tracking where in the memory hierarchy v resides at the anticipated time of recomputation.

#### 3.3.1 Amnesic Compiler and Instruction Set Extensions

The amnesic compiler first extracts a set of independent *RSlices* as potential targets for recomputation, and annotates each, such that the amnesic scheduler (see Section 3.3.3) can identify them at runtime. The amnesic scheduler triggers recomputation along any given RSlice(v) only if loading the data value v is more energy-hungry than recomputation.

#### Slice Formation

The amnesic compiler pass first estimates, probabilistically (as detailed in the following and Section 3.4), the energy consumption of loading v,  $E_{ld,v}$ . Next comes dependency analysis to identify the producer instructions of v, in order to calculate the anticipated cost of potential recomputation. This step starts building RSlice(v) (where the immediate producer of v, P(v), resides at the root), and lets RSlice(v) grow level by level, as long as the cumulative cost of recomputation along RSlice(v) being constructed remains below  $E_{ld,v}$ .

As the compiler traverses the dependency chains in constructing RSlice(v), it may hit load instructions. In the proof-of-concept implementation, the compiler replaces each such load with the respective recomputing slice, recursively. Therefore, loads and stores cannot be present as intermediate nodes in RSlice(v).

To derive the energy cost of recomputation,  $E_{rc,v}$ , the compiler pass uses instruction mix and count within RSlice(v), along with machine specific energy per instruction (EPI) estimates:  $E_{rc,v}$  is the sum of [*instruction count per category*] × [*EPI per category*], over all instruction categories represented in RSlice(v)'s instruction mix.  $E_{ld,v}$  calculation, on the other hand, relies on probabilistic estimates:  $\Pr_{Li}$ , the probability of having a load serviced by level Li in the memory hierarchy, is derived from hit and miss statistics of Li under profiling. Let the EPI estimate for a load serviced in Li be EPI<sub>Li</sub>. Then, the sum of  $Pr_{Li} \times EPI_{Li}$  over all levels *i* in the memory hierarchy (including off-chip) gives the probabilistic energy cost per load.

#### Slice Annotation

As a hint for the amnesic scheduler, the compiler replaces each load, the swap of which with recomputation is likely to be more energy-efficient (according to the probabilistic energy cost comparison explained above) with a special control flow instruction, RCMP. In this case, the compiler also inserts the constructed *RSlice* in the binary.

Semantically, RCMP corresponds to the fusion of a conditional branch with a load<sup>3</sup>. The resolution of the branching condition is left to the amnesic scheduler (see Section 3.3.3) at runtime. Depending on the branching condition (which is dictated by where in the memory hierarchy v resides at runtime), RCMP can act either as a branch to the entry point (starting from the leaves) of RSlice(v), or as a classic load which reads v from memory. The latter is the case if the amnesic scheduler determines at runtime that recomputation is less energy-efficient than performing the load, i.e.,  $E_{rc,v}$  exceeds  $E_{ld,v}$ . Accordingly, as input operands, RCMP inherits all input operands of the respective load, in addition to the starting address of RSlice(v).

At the exit of each such RSlice(v) embedded in the binary resides a return instruction, RTN, which returns the control to the instruction following RCMP in program order after recomputation along RSlice(v) finishes. RTN semantics closely mimic procedure return instructions. Before return, the recomputed data value v gets copied into the destination register of the eliminated load (recall that RCMP inherits all source and destination parameters of the respective load).

Only if the leaves of RSlice(v) have non-recomputable input operands, the compiler places REC instructions into the binary, which serve buffering of non-recomputable input operands such as overwritten register values. An REC instruction goes right after each instruction, a replica of which serves as a leaf in RSlice(v). REC has a single integer operand: leaf-address which points to the address of the respective leaf instruction

$<sup>^{3}</sup>$  Depending on the specifics of the underlying instruction set architecture (ISA), RCMP can also be synthesized by a pair of branch and load instructions, without loss of generality.

Figure 3.2: Amnesic Microarchitecture & Scheduler.

in RSlice(v). REC practically checkpoints the input operands to a dedicated buffer (see Sections 3.3.2 and 3.3.3).

Unless the compiler can prove that all input operands of RSlice(v)'s leaves correspond to constants or live register values at the anticipated time of recomputation, REC instructions are necessary. Finally, how the compiler orders the leaves in RSlice(v) code is not critical, as leaf instructions cannot depend on each other.

#### 3.3.2 Amnesic Microarchitecture

Amnesic execution should meet two conditions for safe and effective recomputation:

- **Condition-I**: Prevent corruption of the architectural state during recomputation (see Section 3.2.3).

- **Condition-II**: Have (non-recomputable) input operand values of *RSlice* leaves available at the anticipated time of recomputation (see Section 3.2.2).

Figure 3.2 captures microarchitectural support to meet **Condition-I** and **Condition-I** II in orchestrating amnesic execution. Recall that only one *RSlice* can be active, i.e., traversed for recomputation, at a time<sup>4</sup>.

Scratch-File (SFile): To satisfy Condition-I, the amnesic microarchitecture deploys the dedicated buffer SFile. During recomputation, as program control traverses an

$<sup>^4</sup>$  Offloading recomputation to spare or idle cores, or using helper threads may improve energy efficiency further by enabling concurrent recomputation. However, the basic proof-of-concept implementation assumes strictly sequential execution semantics.

*RSlice*, the data flows through the SFile, leaving the (physical) registerfile intact. Recomputing instructions from an *RSlice* do not perform any memory access, and communicate over SFile only.

**Renamer:** During traversal of each *RSlice*, a dedicated Renamer maps register references per recomputing instruction to SFile entries. Semantically, the amnesic renamer closely mimics the rename logic of classic out-of-order machines. In this context, SFile becomes not any different than the physical registerfile and follows similar rules for space (de)allocation.

**History Table (Hist):** For each *RSlice* where the leaf input operands correspond to constants or live values from the (physical) registerfile, **Condition-II** is automatically satisfied. Only for non-recomputable leaf input operands, dedicated storage is required to satisfy **Condition-II**. The amnesic microarchitecture can buffer non-recomputable input operands for each *RSlice* leaf in the dedicated history table Hist. Each entry of Hist keeps the address (leaf-address) and non-recomputable input operands of a leaf instruction.

**Instruction Buffer (IBuff)** can cache recomputing instructions within each *RSlice*, in order to relax amnesic execution's potential pressure on the instruction cache. Each entry of IBuff corresponds to a recomputing instruction.

SFile, Hist, and IBuff all feature an **invalid** field per entry to orchestrate (de)allocation of space as necessary.

#### 3.3.3 Amnesic Scheduler

#### **Runtime Policies**

At runtime, the amnesic scheduler decides whether recomputation along each RSlice(v) embedded into the binary by the compiler (Section 3.3.1) can improve energy efficiency or not, depending on where in the memory hierarchy v resides. Specifically, each time a RCMP instruction is fetched, the scheduler has to decide whether to branch to the entry point of the respective RSlice(v), or whether to perform the load to read v from memory. A control flag, recompute, remains set as recomputation – traversal of an RSlice – is in progress. recompute is reset by default.

To be able to draw a safe decision, the amnesic scheduler needs to track where in the

memory hierarchy v resides. There are different options to track or predict the location of v at runtime. In the proof-of-concept implementation, the amnesic scheduler lets the corresponding load probe on-chip memory (caches), and fires recomputation upon a miss in the first-level cache (*FLC*), or alternatively, upon a miss in the last-level cache (*LLC*) – by using either a first or a last level cache miss as an indicator for an energy-hungry offchip memory access. In this case, RCMP becomes the equivalent to **branch on FLC miss** or, alternatively, **branch on LLC miss**, with the branch target being the entry point of the respective *RSlice*. The amnesic scheduler fires recomputation by setting the **recompute** flag. Otherwise, execution follows the classic trajectory by performing the load.

In this case, recomputation cost includes the cost of probing the on-chip memory hierarchy. FLC and LLC policies are heuristic-based and may result in false-negatives (lost recomputation opportunity) and false-positives (energy-inefficient recomputation). Better amnesic policies can be devised by using more accurate (miss) predictors [7, 8, 9], which can also help eliminate the probing overhead. We leave further refinement and exploration of such policies to future work – the design space is pretty rich. In Section 3.5, we will also compare FLC and LLC policies to a runtime-oblivious policy, *Compiler*, which *always* triggers recomputation each time a RCMP instruction is fetched.

#### 3.3.4 Putting It All Together

Amnesic activity when recompute is reset: No recomputation takes place as long as the recompute flag stays reset. During this period, amnesic execution is equivalent to classic execution, if no *RSlice* in the binary features non-recomputable leaf inputs. Otherwise, the amnesic scheduler has to record such non-recomputable input operands into Hist. To this end, the scheduler tracks REC instructions (Section 3.3.1). REC instructs the scheduler to record all non-recomputable input operands in a Hist entry (0 in Figure 3.2), along with leaf-address.

**Triggering recomputation:** For each RCMP instruction fetch-ed, the amnesic scheduler first needs to resolve the branching condition: whether recomputation is more energy-efficient than performing the memory access, i.e., whether  $E_{ld,v}$  exceeds  $E_{rc,v}$ . This decision can be drawn following any of the runtime policies from Section 3.3.3, *FLC* or *LLC*. For example, under *LLC*, the amnesic scheduler probes the caches, and fires

recomputation by setting the **recompute** flag upon an LLC miss. Otherwise, the load is performed following the classic execution trajectory.

Amnesic activity when recompute is set: RCMP branches to the entry point of RSlice(v), and instruction fetch starts from the first leaf. Each leaf instruction first has its destination register renamed (2) in Figure 3.2). Each leaf instruction with non-recomputable input operands next probes Hist with leaf-address (3) to read its input operands, which directly are fed into the corresponding execution units (4). Leaf instructions with constant or live register input operands do not need to probe Hist. Upon finishing execution, each leaf writes its result to the SFile (5).

Non-leaf recomputing instructions which represent intermediate nodes in RSlice(v) read their input operands from SFile (<sup>6</sup>) after having their source and destination registers renamed (<sup>2</sup>). Upon collecting the input operands, recomputing instructions proceed to the execution units (<sup>7</sup>), and write their results back to the SFile once execution completes (<sup>8</sup>). All (non-leaf) recomputing instructions in RSlice(v) execute sequentially in this manner until the RTN instruction of the slice is fetched. Before return, the recomputed data value v gets copied from SFile into the destination register of the eliminated load (recall that RCMP inherits all source and destination parameters of the respective load). The amnesic scheduler then resets **recompute** flag to demarcate the end of recomputation. Execution continues from the instruction following RCMP in program order.

IBuff is an optional structure to help reduce the pressure on instruction cache under recomputation. Very much like the instruction cache, fetch logic can fill IBuff with recomputing instructions (①). IBuff in turn feeds the Renamer with recomputing instructions (②).

#### 3.3.5 Storage Complexity

We next analyze the expected storage complexity for each component of the amnesic microarchitecture from Figure 3.2. Recall that the amnesic microarchitecture only processes instructions with register source operands and register destinations, and excludes memory or control flow instructions. Without loss of generality, the following analysis assumes a RISC-style ISA.

SFile: A recomputing instruction typically writes its result to one destination register,

and reads its input operands from two source registers. Accordingly, the maximum possible number of renaming requests per recomputing instruction,  $max_{\#rename}$  becomes

$$max_{\text{\#rename}} = max_{\text{\#src}} + max_{\text{\#dest}} = 3$$

where  $max_{\#src}$  ( $max_{\#dest}$ ) is the maximum number of source (destination) register operands per recomputing instruction. At any given time, only one *RSlice* can be traversed. Therefore, SFile capacity does not depend on the total *RSlice* count in the binary, but grows with the instruction count per *RSlice*, which can exponentially increase with the tree height *h*. A tall *RSlice*, however, is very unlikely to find any place in the binary, as it can easily result in excessive recomputation overhead to render recomputation useless. The amnesic compiler captures such diminishing returns and prevents excessive growth of the *RSlice* (see Section 3.3.1): practically, the compiler not only influences *RSlice* topology, but also caps the tree height *h* to maximize energy savings. Accordingly, we can derive a loose upper-bound for SFile capacity as

$max_{\#inst per RSlice} \times max_{\#rename} = max_{\#inst per RSlice} \times 3$

where  $max_{\#inst per RSlice}$  corresponds to the maximum of instruction count per RSlice across all RSlices in the binary.

**Hist:** Hist can keep data for multiple *RSlices* during execution. For each *RSlice*, Hist can contain as many entries as the *RSlice*'s number of leaves. Thus, a loose upper-bound for the number of entries in Hist becomes

#### $\#RSlice \times max_{\#leaf per RSlice}$

where #RSlice is the number of RSlices in the binary; and  $max_{\#leaf per RSlice}$ , the maximum of the number of leaves per RSlice (which may grow with tree height h). Each Hist entry accommodates at most  $max_{\#src}$  values, to cover all non-recomputable input operands per leaf.

**IBuff:** The capacity of IBuff grows with the number of instructions per *RSlice*. Hence, a loose upper-bound for IBuff capacity becomes  $max_{\#inst per RSlice}$ .

#### 3.3.6 Technicalities

The proof-of-concept implementation represents a basic design, which neglects various optimization opportunities such as instruction reuse among recomputing slices, or hardware resource sharing with the underlying microarchitecture.

During traversal of an RSlice, latency per recomputing instruction remains very

similar to its classic counterpart, as the amnesic microarchitecture follows the pipelining semantics of the underlying microarchitecture (just with an alternative instruction and operand supply of similar latency).

The storage complexity of amnesic structures from Figure 3.2 tends to be low (Section 3.3.5). Only the unlikely capacity overflow of Hist can impair recomputation, and only for *RSlices* with non-recomputable leaf input operands. The amnesic scheduler can track these cases by failed REC instructions (Section 3.3.1) and enforce the corresponding RCMP to skip recomputation (i.e., to perform the load). To this end, the amnesic scheduler has to uniquely identify the matching RCMP. This can be achieved by assigning a unique ID, RSlice-ID, to each *RSlice* in the binary, and providing it as an operand to both REC and RCMP.

In processing recomputing instructions, the amnesic microarchitecture has to differentiate between leaves and intermediate nodes, since different structures supply the input source operands to each: The inputs of leaves can come from the registerfile (a live value) or Hist (an overwritten value). The inputs of intermediate nodes come from SFile. The compiler annotates leaves and accesses to Hist to distinguish between these cases. Specifically, the compiler changes source register identifiers of leaf instructions reading their operands from Hist to an invalid number. Leaf instructions with valid source register identifiers directly access the registerfile. Non-leaf recomputing instructions follow the paths ② and ⑥ in Figure 3.2.

Recall that there is another potential class of leaves with non-recomputable input operands: read-only values to be loaded from memory, such as program inputs. In principle, replacing the load to read v from memory with RSlice(v) which features possibly more than one such load at the leaves does not make sense. Hist is designated to record overwritten register input operands, but Hist can also keep such read-only values, and may make recomputation along such RSlice(v) energy-efficient.

#### 3.4 Evaluation Setup

**Benchmarks:** To quantify the energy efficiency potential of amnesic execution, we experiment with 33 sequential or single-threaded benchmarks from SPEC-2006 [10], NAS [11], PARSEC [12] and Rodinia [13] suites, which span various application domains

| Suite   | Benchmarks                                                                                                                                           | Inputs                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| SPEC    | mcf, perlbench, gobmk, calculix<br>GemsFDTD, libquantum, soplex, lbm<br>omnetpp, sphinx3 (sx)                                                        | test                          |

|         | is                                                                                                                                                   | A                             |

| NAS     | cg                                                                                                                                                   | W                             |

|         | ft, mg                                                                                                                                               | S                             |

| PARSEC  | canneal (ca), facesim (fs), ferret (fe)<br>raytrace (rt), blackscholes, x264<br>dedup, freqmine, fluidanimate<br>streamcluster, swaptions, bodytrack | simsmall                      |

|         | backpropagation (bp)                                                                                                                                 | 65536                         |

|         | bfs                                                                                                                                                  | $graph1MW_{-}6.txt$           |

| Rodinia | kmeans                                                                                                                                               | kdd_cup                       |

| nouina  | nw                                                                                                                                                   | 2048 10 1                     |

|         | particlefilter                                                                                                                                       | -x 128 -y 128 -z 10 -np 10000 |

|         | srad (sr)                                                                                                                                            | $100 \ 0.5 \ 502 \ 458 \ 1$   |

|         | hotspot                                                                                                                                              | 512 512 2 1                   |

Table 3.1: Benchmarks deployed to quantify the potential of amnesic execution.

and memory access characteristics, as listed in Table 3.1.

**Binary generation:** We implement the greedy compiler pass detailed in Section 3.3.1 as a (*binary generator*) Pin [14] tool. The EPI estimates (see Section 3.3.1) come from measured data from [15]. Although these estimates are for a parallel processor (Intel's Xeon Phi), the simulated microarchitecture is very similar to its per core configuration (Table 3.2). We also fine-tune these estimates by extracting EPI values for different instruction categories from McPAT [16] integrated with the Sniper-6.1 [17] microarchitectural simulator. We derive  $Pr_{Li}$  (see Section 3.3.1), the probability of having a load serviced by level Li in the memory hierarchy, using hit and miss statistics for Li from Sniper. We also implement a *runtime profiler* in Pin, which collects dependency information for binary generation. Using the dependency information (from the Pin-based runtime profiler) and EPI estimates, the (binary generator) Pin tool identifies *RSlices* that can improve energy efficiency, and instruments them for inclusion into the binary.

| Technology node:    | 22nm          |                |         |

|---------------------|---------------|----------------|---------|

| Operating frequency | 1.09 GHz      |                |         |

| L1-I (LRU):         | 32KB, 4-way   | 0.88nJ         | 3.66ns  |

| L1-D (LRU, WB):     | 32KB, 8-way   | 0.88nJ         | 3.66ns  |

| L2 (LRU, WB):       | 512KB, 8-way  | 7.72nJ         | 24.77ns |

| Main Memory         | Read: 52.14nJ | Write: 62.14nJ | 100ns   |

Table 3.2: Simulated architecture to quantify the potential of amnesic execution.

**Recomputation at runtime:** We implement the amnesic microarchitecture from Figure 3.2 in Sniper, and run the annotated binaries on it. Sniper facilitates seamless integration with Pin. Runtime energy and performance statistics come from Sniper (+ McPAT) simulations. Table 3.2 gives EPI and (round-trip) access latency for each level in the simulated memory hierarchy. We conservatively model EPI and access latency for Hist after L1-D; for SFile, after the physical registerfile; and for IBuff, after L1-I. Accordingly, we model RCMP's overhead after a conditional branch; REC's, after a store to L1-D; RET's, after a jump.

#### 3.5 Evaluation

#### 3.5.1 Impact on Energy Efficiency

Figure 3.3 captures the impact of amnesic execution on energy-delay product, EDP [18], as a proxy for energy efficiency. The y-axis is normalized to the EDP under classic execution. Out of 33 benchmarks we deployed, only 11 have the potential to provide more than 10% EDP gain. In the following, we will focus on these benchmarks. The rest of the benchmarks did not benefit much from recomputation (only 4 provided more than 5% EDP gain) because they did not have many energy-hungry loads and/or recomputation degraded temporal locality. Recomputation cannot improve energy efficiency of compute-bound applications unless they incorporate a few but very energy-hungry memory references.

In Figure 3.3, we compare representative runtime policies from Section 3.3.3 - FLC, LLC and Compiler, to two oracular policies: Oracle and C(onservative)-Oracle. FLC, LLC, Compiler and C-Oracle select from the very same set of RSlices for recomputation

Figure 3.3: EDP gain under amnesic execution.

at runtime – this set is identified by the compiler pass using the probabilistic energy model (see Section 3.3.1). At runtime, FLC (*LLC*) fire recomputation along RSlice(v) if the respective load of v misses in FLC (LLC). *Compiler*, on the other hand, *always* fires recomputation, for each RCMP encountered.

C-Oracle can predict with 100% accuracy where the load of v will be serviced in the memory hierarchy as the amnesic scheduler decides whether to perform the load or whether to fire recomputation along RSlice(v). C-Oracle hence bases the runtime decision on this 100% accurate prediction. Oracle, too, can predict at runtime with 100% accuracy where a load would be serviced. The key difference of Oracle from C-Oracle comes from a different (i.e., optimal) set of RSlices baked in the binary, than the compiler's probabilistic energy model based set (which applies to the rest of the policies). The EDP difference between Oracle and C-Oracle therefore illustrates how accurate compiler's probabilistic energy model is. The smaller the EDP difference, the more accurate is the probabilistic energy model in characterizing an application's loads. In other words, C-Oracle demonstrates the maximum possible EDP gain with the given probabilistic energy model of the loads.

We fine-tune the probabilistic energy model of the amnesic compiler pass using dynamic execution traces (see Section 3.3.1). Notice that the EDP gain under *Compiler* evolves with the accuracy of this probabilistic energy model, but such fine-tuning may not always be possible. The more accurate the energy model, the more accurate becomes

amnesic compiler's prediction of where the load reading v will be serviced at runtime. And the more accurate this prediction, the more energy efficiency can the *Compiler* policy harvest, under which each RCMP always triggers recomputation. The EDP gains under *Compiler* therefore reflect best-case estimates.

Recall that the set of *RSlices* recomputed by each policy is different: *Compiler* recomputes along each *RSlice* embedded in the binary, which form the set *S. C-Oracle* picks the optimal subset from  $S(S_{C-Oracle})$  for recomputation, i.e., only recomputes RSlice(v) if recomputation is exactly more energy-efficient than performing the load of v. *FLC* (*LLC*), on the other hand, picks the subset of *S*,  $S_{FLC}$  (*S<sub>LLC</sub>*), which only includes RSlice(v)s where the respective load to read v misses in L1 (L2). Subject to the accuracy of the probabilistic energy model and such runtime decisions, the set of RSlices recomputed by *Oracle* may be very different: *Oracle*'s decisions are based on actual (not probabilistic or predicted) energy costs.

Overall, with the exception of sx and cg (and fe, rt to a lower extent), we observe that *C-Oracle* closely tracks *Oracle*, rendering the probabilistic energy model accurate. Except sr, the best-case *Compiler* closely tracks *C-Oracle*. On the other hand, the difference between the best-case *Compiler* and *FLC* is barely visible, with the exception of sx, bfs and sr. *LLC* is consistently worse than *FLC*. The main delimiter for *LLC* is the overhead of probing the last-level cache (L2) to detect a miss which is much larger than the overhead of probing the first-level cache (L1) to detect a miss under *FLC*.

EDP(Compiler) < EDP(FLC): In principle, as the amnesic compiler can only probabilistically take into account where a load might get serviced at runtime, by firing recomputation along RSlice(v) for each RCMP encountered, the *Compiler* policy can easily trigger unnecessary recomputations, and hence, hurt energy efficiency – particularly if v resides in L1. *FLC*, on the other hand, prevents recomputation in this case. This is clearly visible for sr, where *Compiler* triggers too many recomputations that do not provide sizable energy gain (due to recomputed data mostly being in L1), but introduce performance overhead (since RSlices recomputed usually take longer than accessing L1). Since the energy gain due to recomputation does not offset the performance degradation, the EDP of sr degrades 7% under *Compiler*. Although the difference is small, *Compiler* yields lower EDP gain than *FLC* in sx, cg, fe, rt and bp.

EDP(Compiler) > EDP(FLC): Compiler can provide higher gains than FLC (LLC)

Figure 3.4: Energy gain under amnesic execution.

when they recompute the very same set of *RSlices*; i.e.,  $S_{FLC}$  ( $S_{LLC}$ ) overlaps with S – when none of the vs is present in L1 (L2). This is because *Compiler* does not need to probe the caches, so there is no probing cost. Although the difference is mostly small, this is the tendency in mcf, is, ca, fs, and bfs.

**EDP**(**FLC**) vs. **EDP**(**LLC**): If v resides in L1, both *FLC* and *LLC* simply skip recomputation. If v resides in L2, only *FLC* fires recomputation. In this case, depending on the instruction mix and count in RSlice(v), recomputation may be less expensive than retrieving v from L2, particularly for short RSlice(v). At the same time, the probing cost is lower for *FLC* than *LLC*. As Section 3.5.4 reveals, the benchmark applications feature predominantly short RSlice(v)s, with much less than 50 instructions. Overall, *FLC* renders the higher EDP gain, since recomputation along RSlice(v) remains usually cheaper than retrieving v from L2.

Impact on energy & execution time: Due to memory accesses being both energyhungry and slow, most of the time, the reduction in EDP comes from a reduction in both energy and execution time. Figure 3.4 shows the corresponding reduction in energy consumption; Figure 3.5, in execution time, under amnesic execution, normalized to classic execution. We observe similar trends to EDP for both.

**Putting it all together:** An amnesic design which always fires recomputation following compiler hints (i.e., *Compiler*, as opposed to following policies like *FLC* or *LLC*) can be very effective as Figure 3.3 reveals, but it is limited by the accuracy of compiler's

Figure 3.5: % reduction in execution time.

probabilistic energy model. Overall, *Compiler* improves the EDP of all benchmarks, with the exception of sr and mg where EDP is degraded by 7% and 1.37%, respectively. Eight of the benchmarks obtain more than 10% EDP gain under *Compiler*, where the range changes from 12.04% to 87%. *FLC* and *LLC* yield slightly lower EDP gains than *Compiler*, in general. Since they tend do make more conservative decisions on recomputation, they do not experience any EDP degradation. For the aforementioned 8 benchmarks, EDP gain under *FLC* (*LLC*) range from 14.37% to 85.3% (11.39% to 71.92%).

To shed further light on these findings, we will next look into instruction mix (see Section 3.5.2), memory access characteristics (see Section 3.5.3) and *RSlice* characteristics (see Section 3.5.4) under amnesic execution.

# 3.5.2 Impact on Instruction Count and Mix

Under amnesic execution, the sequence of recomputing instructions in each RSlice(v) replaces the respective load to read v from memory. Therefore, we expect an increase in the number of (dynamic) instructions along with a decrease in the number of (dynamic) load instructions under amnesic execution. Table 3.3 shows how the dynamic instruction mix and energy breakdown changes under amnesic execution. For comparison, we also provide the energy breakdown under classic execution. Without loss of generality,

|        | 1            |         |                      |       |         |       |       |         |           |

|--------|--------------|---------|----------------------|-------|---------|-------|-------|---------|-----------|

|        | % incr.      | % decr. | Energy Breakdown (%) |       |         |       |       |         |           |

| Bench. | (dyn.)       | load    | Classic              |       | Amnesic |       |       |         |           |

|        | instr. count | count   | Load                 | Store | Non-mem | Load  | Store | Non-mem | Hist Read |

| mcf    | 4.47         | 6.19    | 91.67                | 2.12  | 6.20    | 75.33 | 2.88  | 6.77    | 0.48      |

| SX     | 4.55         | 6.68    | 70.43                | 2.70  | 26.86   | 58.44 | 3     | 28.01   | 2.42      |

| cg     | 3.97         | 2.11    | 82.43                | 0.45  | 17.10   | 80.03 | 0.51  | 17.99   | 0.51      |