Copyright by

Jiwoo Pak

2014

## The Dissertation Committee for Jiwoo Pak certifies that this is the approved version of the following dissertation:

##

| Committee:               |

|--------------------------|

|                          |

| David Z. Pan, Supervisor |

| Sung Kyu Lim             |

| Nur A. Touba             |

| Michael Orshansky        |

| Nan Sun                  |

# Electromigration Modeling and Layout Optimization for Advanced VLSI

by

Jiwoo Pak, B.S.; M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2014$

## Acknowledgments

My first thanks go to my advisor, Prof. David Z. Pan, for his guidance, understanding, and support during my Ph.D. studies at the University of Texas at Austin. He guided me to become an independent researcher with my own thoughts, rather than just to follow the instructions from someone else. Also, he allows me to devote time to my family, which was really beneficial to my toddler girl who was born during my Ph.D. studies. Retrospectively, I was so lucky to meet Prof. Pan and receive guidance from him, because he is one of the strongest leaders in this area and a kind man with a warm heart.

I would like to thank the current and former UTDA members, who spent years with me and/or had valuable discussions with me: Minsik Cho, Kun Yuan, Ashutosh Chakraborty, Wooyoung Jang, Jae-Seok Yang, Yongchan (James) Ban, Duo Ding, Samuel Ward, Wen Zhang, Yang Li, Yilin Zhang, Jerrica Gao, Bei Yu, Joydeep Mitra, Subhendu Roy, Xiaoqing Xu, Jiaojiao Ou, Abhishek Bhaduri, Che-Lun Hsu, and Yibo Lin. As an international student, I learned a lot from these group members, from using good communication skills to the proper way to present my thoughts. I am pretty sure that I am going to miss the days that I worked with my UTDA colleagues at UT Austin.

I am also deeply thankful to Prof. Sung Kyu Lim in the ECE department at Georgia Institute of Technology, who is almost like a 'co-advisor' to

me. My collaboration with a leader in 3D IC research helped me a lot during my Ph.D. studies; Prof. Lim's advice during our regular meetings intensified my technical details in my 3D IC studies. I would also like to thank the GTCAD students, who collaborated with me, helped me with the benchmark circuits, and suggested a better direction for the research: Mohit Pathak, Moongon Jung, Krit Athikulwongse, Xin Zhao and Taigon Song.

My sincere thanks also goes to my three other Ph.D. committee members, Prof. Nur A. Touba, Prof. Michael Orshansky and Prof. Nan Sun. In Prof. Touba's VLSI testing class, I was able to learn the systematic testing of VLSI and became interested in the reliability of the system. Prof. Orshansky gave me some insights into the trends of nano-scale circuit design and statistical analysis, and Prof. Sun's feedback during my Ph.D. proposal exam helped me to explore interesting problems that I could not think of.

As an intern and a part-time employee of Cadence Design Systems, I would deeply like to thank Chin-Chi Teng, Inki Hong and Ram Iyer at Cadence, who encouraged me to pursue my Ph.D. degree and work part-time with a world leading EDA company at the same time. I feel that the GigaOpt team fits well to me, and I am so glad that I joined the right team to work with. Thanks to Mohit Pathak (again!) and other team members, who guided me during my summer internship at Cadence. I am also thankful to my previous manager, Yu-Yen Mo, at Oracle, who helped me to learn from the real designs in the industry and gave me lots of self-confidence. He is the one who suggested me to have a work-life balance, and that became the No. 1 goal in my life.

I am deeply thankful to my husband Sangman Kim. He is my best friend, best co-worker for house chores, and best advisor for the important decisions in my life. This work would not exist without his endless support and understanding. Owing to the breakfasts he prepared and his playtime with our little one, I could focus on my research for the past five years. Sangman, thank you for editing my paper, thank you for giving me advice on programming, and thank you for understanding me as a graduate-student wife. Another thank you should go to my dearest daughter, Yoon Kim. Born to busy graduate-student parents, she could not spend lots of time with her mom, which makes me feel sorry for her. Still, she gave me unimaginable happiness as a parent, and she makes me realize what a meaningful life is. Thank you, Yoon, for all of your understanding of mom's work during the weekdays and nights. Last but not least, I would like to thank my parents, who are the 'perfect' parents to me.

# Electromigration Modeling and Layout Optimization for Advanced VLSI

Publication No.

Jiwoo Pak, Ph.D.

The University of Texas at Austin, 2014

Supervisor: David Z. Pan

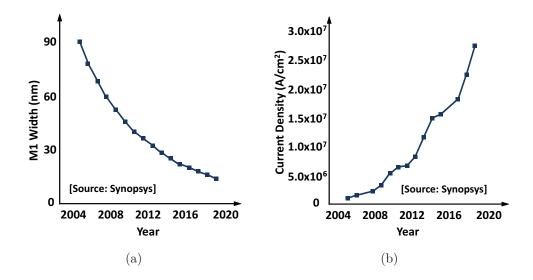

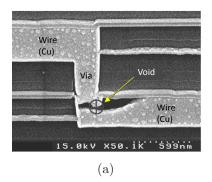

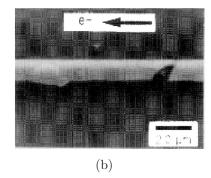

Electromigration (EM) is a critical problem for interconnect reliability in advanced VLSI design. Because EM is a strong function of current density, a smaller cross-sectional area of interconnects can degrade the EM-related lifetime of IC, which is expected to become more severe in future technology nodes. Moreover, as EM is governed by various factors such as temperature, material property, geometrical shape, and mechanical stress, different interconnect structures can have distinct EM issues and solutions to mitigate them. For example, one of the most prominent technologies, die-stacking technology of three-dimensional (3D) ICs, can have different EM problems from that of planer ICs, due to their unique interconnects such as through-silicon vias (TSVs).

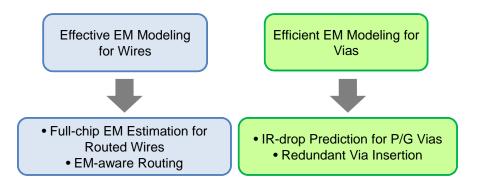

This dissertation investigates EM in various interconnect structures, and applies the EM models to optimize IC layout. First, modeling of EM is de-

veloped for chip-level interconnects, such as wires, local vias, TSVs, and multiscale vias (MSVs). Based on the models, fast and accurate EM-prediction methods are proposed for the chip-level designs. After that, by utilizing the EM-prediction methods, the layout optimization methods are suggested, such as EM-aware routing for 3D ICs and EM-aware redundant via insertion for the future technology nodes in VLSI.

Experimental results show that the proposed EM modeling approaches enable fast and accurate EM evaluation for chip design, and the EM-aware layout optimization methods improve EM-robustness of advanced VLSI designs.

## Table of Contents

| Ackno            | wledg  | ments                                                                 | V       |

|------------------|--------|-----------------------------------------------------------------------|---------|

| Abstra           | act    |                                                                       | viii    |

| List of          | Table  | es                                                                    | xiv     |

| List of          | Figu   | res                                                                   | xvi     |

| Chapt            | er 1.  | Introduction                                                          | 1       |

| Chapt            | er 2.  | Modeling of Electromigration in TSV Structures                        | 7       |

| 2.1              | Intro  | duction                                                               | 7       |

| 2.2              | Backg  | ground                                                                | 8       |

| 2.3              | EM N   | Modeling of TSV                                                       | 10      |

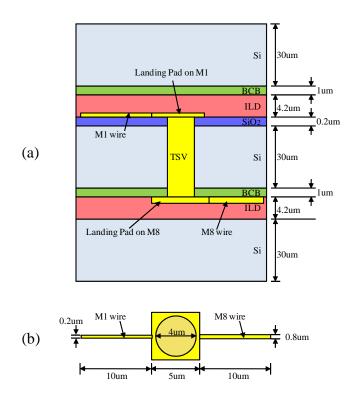

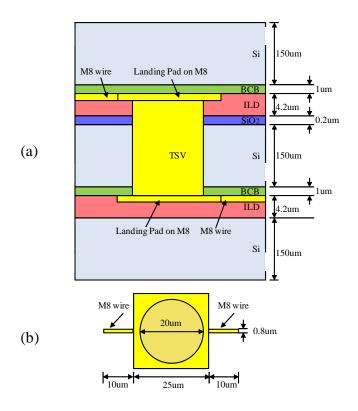

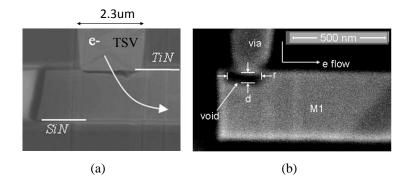

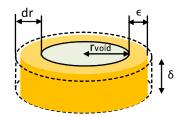

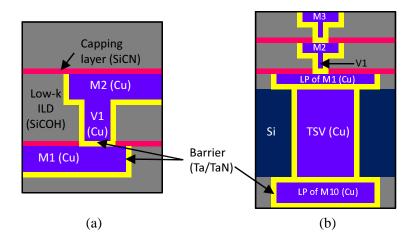

|                  | 2.3.1  | TSV Structure for EM Evaluation                                       | 10      |

|                  | 2.3.2  | Impact of TSV Radius on EM                                            | 12      |

|                  | 2.3.3  | Impact of Landing Pad Size on EM                                      | 15      |

|                  | 2.3.4  | Study of Via-last Structure                                           | 16      |

|                  | 2.3.5  | Summary                                                               | 17      |

| $\mathbf{Chapt}$ | er 3.  | EM Modeling of Wire Structures and Full-chip EN Prediction for 3D ICs | Л<br>19 |

| 3.1              | Intro  | duction                                                               | 19      |

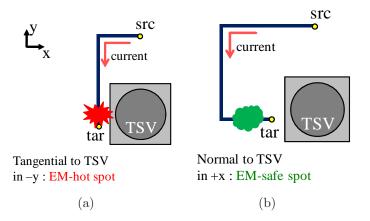

| 3.2              | Impa   | ct of Relative Position of Wires and TSV on EM                        | 20      |

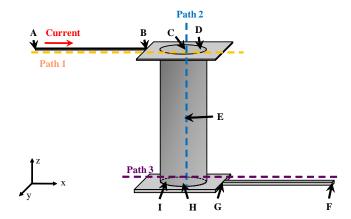

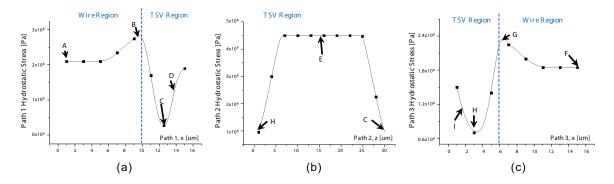

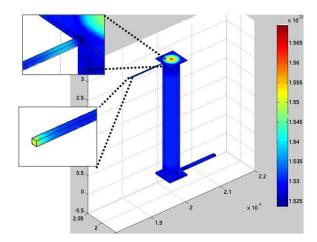

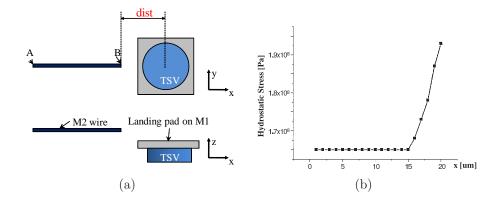

|                  | 3.2.1  | EM Modeling of Wires Near the TSV                                     | 20      |

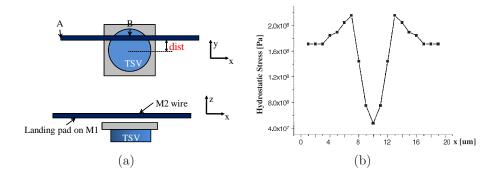

|                  | 3.2.2  | EM Modeling of Wires Go Across the TSV                                | 21      |

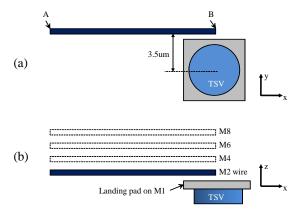

| 3.3              | Impa   | ct of Routing Layers on EM                                            | 23      |

|                  | 3.3.1  | Impact of TSV Radius on Safe Margin                                   | 26      |

| 3.4              | Full-c | chip Level EM Risk Prediction                                         | 27      |

|        | 3.4.1  | Full-chip EM Prediction for 3D ICs                                  | 28         |

|--------|--------|---------------------------------------------------------------------|------------|

|        | 3.4.2  | Effect of Routing Blockage Around TSVs on EM                        | 29         |

| 3.5    | Sumn   | nary                                                                | 31         |

| Chapte | er 4.  | Electromigration-aware Routing in 3D ICs                            | 32         |

| 4.1    | Intro  | duction                                                             | 32         |

| 4.2    | Stress | s-aware EM Modeling for 3D ICs                                      | 34         |

|        | 4.2.1  | Modeling of EM with Stress Consideration                            | 34         |

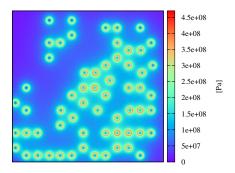

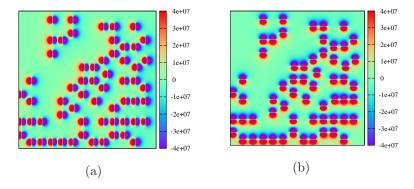

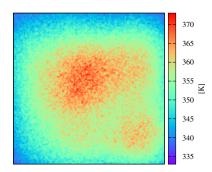

|        | 4.2.2  | Generating Stress Gradient Maps                                     | 35         |

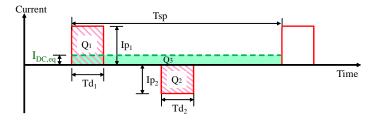

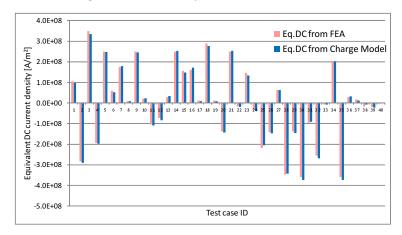

|        | 4.2.3  | Modeling Equivalent DC Current for AC Nets                          | 36         |

|        | 4.2.4  | Thermal Consideration                                               | 39         |

| 4.3    | EM-a   | ware Routing for 3D ICs                                             | 40         |

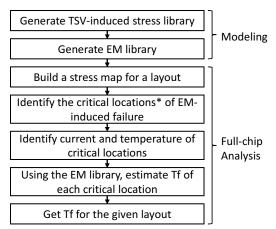

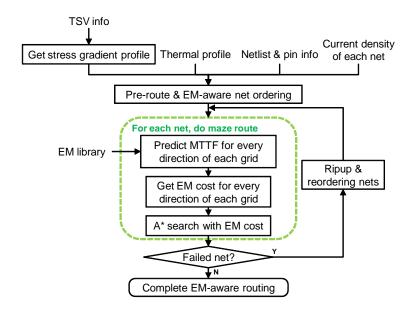

|        | 4.3.1  | Overall Flow                                                        | 42         |

|        | 4.3.2  | Lifetime Prediction with EM Library                                 | 42         |

|        | 4.3.3  | EM-aware Net Ordering for Routing                                   | 44         |

|        | 4.3.4  | Cost Function for EM-aware Maze Routing                             | 46         |

|        | 4.3.5  | Routing Algorithm                                                   | 49         |

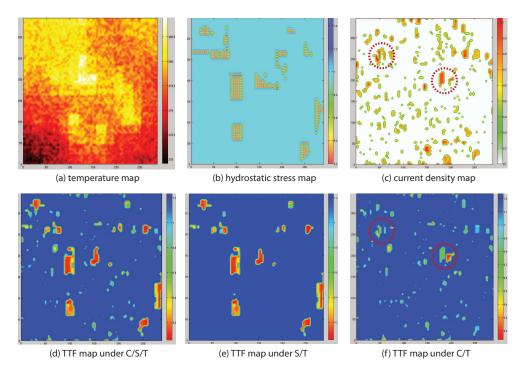

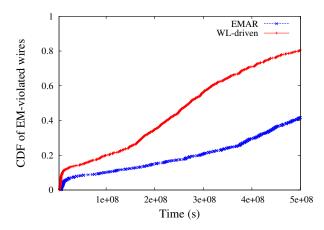

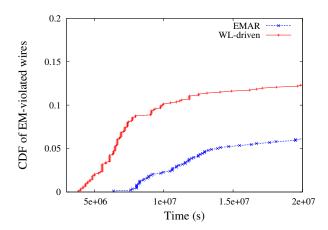

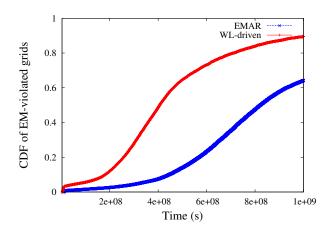

| 4.4    | Exper  | rimental Results                                                    | 50         |

| 4.5    | Sumn   | nary                                                                | 57         |

| Chapte | er 5.  | Electromigration Study with Multi-scale Power/Gro<br>Via Structures | ound<br>60 |

| 5.1    | Intro  | duction                                                             | 60         |

| 5.2    | Prelin | ninaries                                                            | 62         |

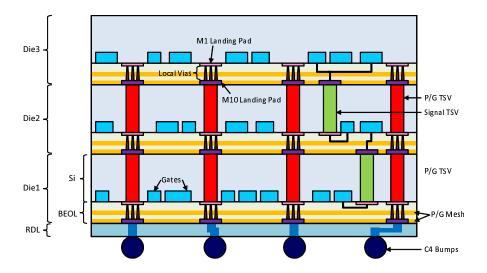

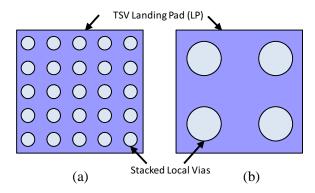

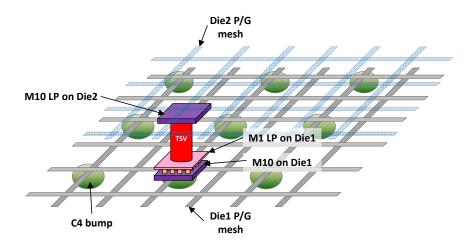

|        | 5.2.1  | Structure of 3D Power Distribution Network                          | 62         |

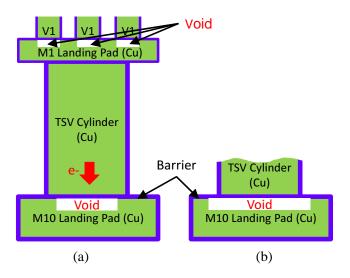

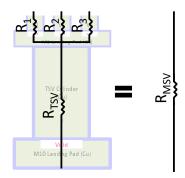

|        | 5.2.2  | Basics of EM of Multi-scale Via (MSV)                               | 63         |

| 5.3    | Mode   | eling of Electromigration for Multi-scale Vias in 3D PDN .          | 67         |

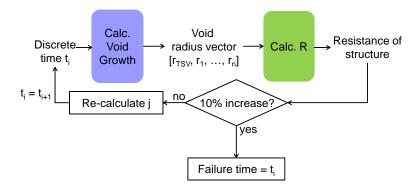

|        | 5.3.1  | Calculating Void Growth                                             | 67         |

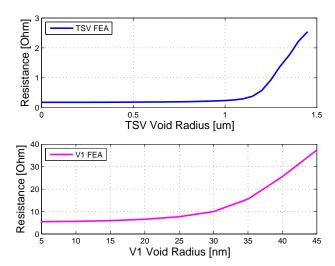

|        | 5.3.2  | Calculating Resistance of Multi-scale Via                           | 71         |

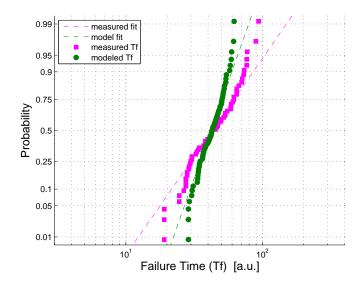

|        | 5.3.3  | Evaluation of Our Model                                             | 74         |

| 5.4    | Study  | on EM of Multi-scale Vias with Various Factors                      | 76         |

|        | 5.4.1  | Study on Barrier Resistivity                                        | 76         |

|        | 5.4.2  | Impact of Void-free Local Vias                                      | 79         |

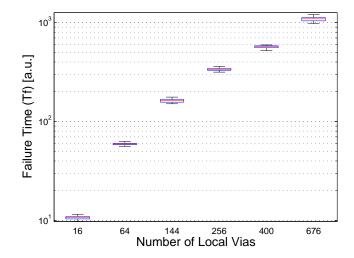

|        | 5.4.3          | Study on Number of Local Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82                                |

|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|        | 5.4.4          | Trade-off Between Via Size and Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83                                |

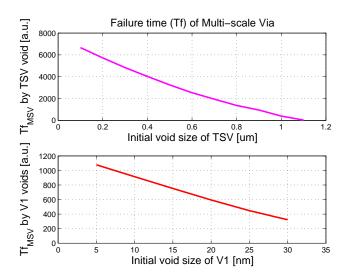

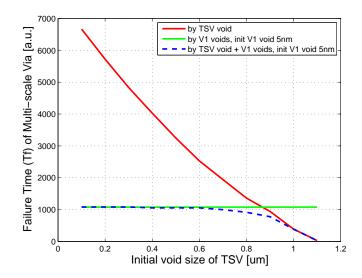

|        | 5.4.5          | Analysis of Initial Void Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                |

| 5.5    | Electr         | comigration of Full-chip 3D PDNs with Multi-scale Vias .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88                                |

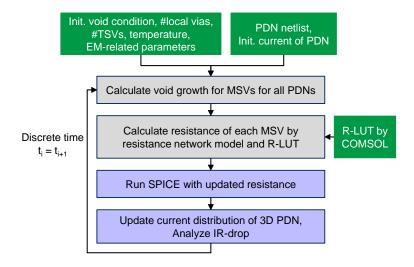

|        | 5.5.1          | Overall Flow of EM Analysis for 3D PDNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88                                |

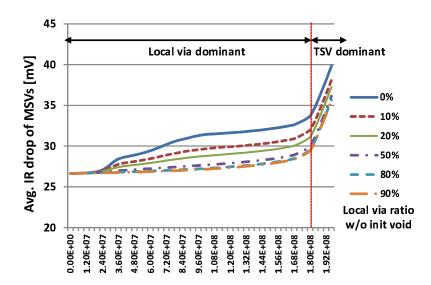

|        | 5.5.2          | EM and IR-drop Analysis of MSV-based PDNs $\ .\ .\ .\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92                                |

|        | 5.5.3          | Full-chip EM Analysis on Initial Void Condition of MSVs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96                                |

|        | 5.5.4          | Temperature and Current Density Impact on EM Reliability of Full-chip 3D PDNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98                                |

| 5.6    | Sumn           | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                               |

| O1 4   | C              | De less de statistiques de la Contraction de la | - 100                             |

| Chapte |                | Redundant Via Insertion in Future Technology node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |

| 6.1    |                | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103                               |

| 6.2    |                | ninaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105                               |

|        | 6.2.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105                               |

| 6.2    | 6.2.2          | Layout Cases with Redundant Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106                               |

| 6.3    |                | nodeling for Redundant Vias with Various Layouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110<br>111                        |

|        | 6.3.1<br>6.3.2 | EM Modeling Flow of Redundant Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |

|        |                | Effect of Current Imbalance in Void Growth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>113</li><li>115</li></ul> |

|        | 6.3.3          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 117                               |

| 6.4    | 6.3.4          | EM Library for Layout Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |

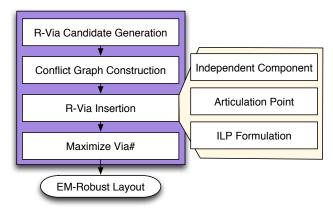

| 0.4    | 6.4.1          | Redundant Via Candidate Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1117                              |

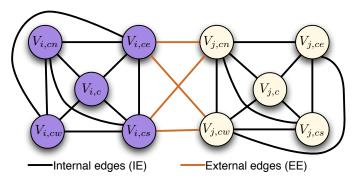

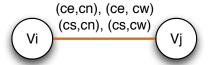

|        | 6.4.1          | Conflict Graph Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 119                               |

|        | 6.4.2          | ILP Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 121                               |

|        | 6.4.4          | Maximizing Vias After EM-optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121                               |

| 6.5    | _              | l-Up Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 123                               |

| 0.0    | 6.5.1          | Simplified Conflict Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123                               |

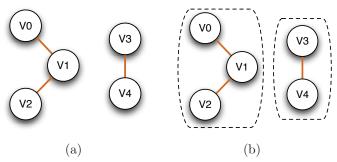

|        | 6.5.2          | Independent Component Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 124                               |

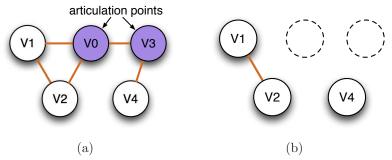

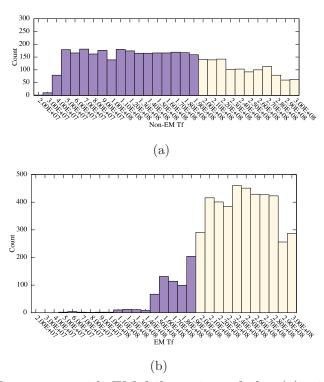

|        | 6.5.2          | Articulation Point Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125                               |

| 6.6    |                | ware Redundant Via Optimization Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 125<br>126                        |

|        |                | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 130                               |

| U. 1   | DULLI          | 1011 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 ( )( )                          |

| Chapter 7. Conclusion | 132 |

|-----------------------|-----|

| Bibliography          | 135 |

| Vita                  | 147 |

## List of Tables

| 2.1 | Parameter values for EM modeling of TSV and neighboring wires                                         | 9  |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.2 | Material Properties of TSV structure                                                                  | 12 |

| 2.3 | Normalized failure time $(Tf)$ for different TSV radius                                               | 13 |

| 2.4 | Normalized failure time $Tf$ for different landing pad size                                           | 16 |

| 2.5 | Normalized $Tf$ for via-last versus via-first TSV $\dots$                                             | 18 |

| 3.1 | Normalized failure time $(Tf)$ for wire in a normal directions .                                      | 21 |

| 3.2 | Normalized failure time when wire runs over TSV                                                       | 23 |

| 3.3 | Routing layer impact on EM-induced lifetime                                                           | 24 |

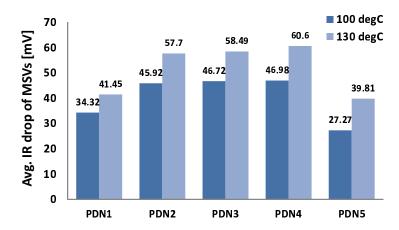

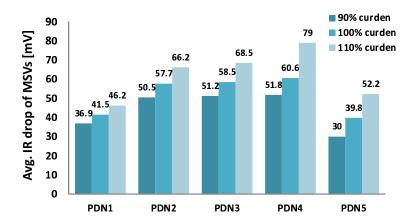

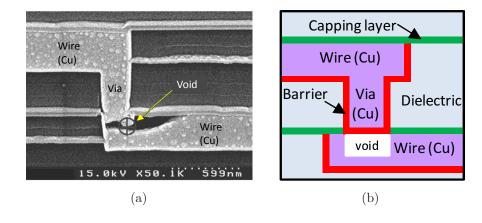

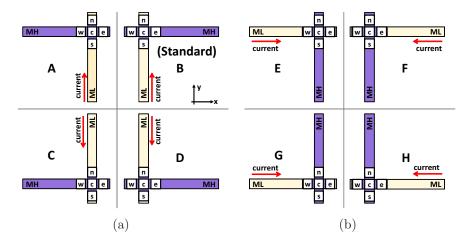

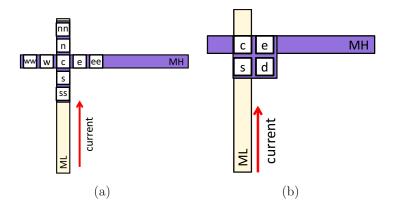

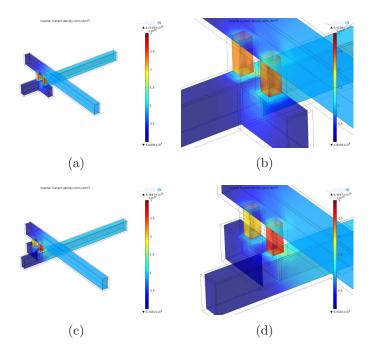

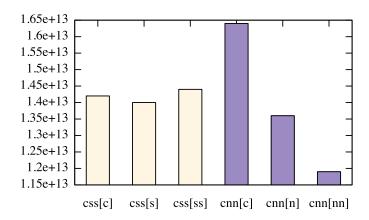

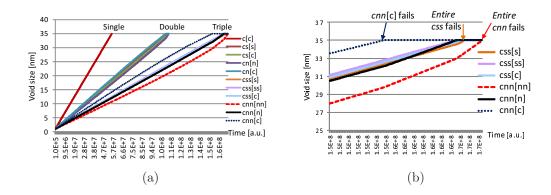

| 3.4 | Structure specification for the experiment                                                            | 25 |