Copyright

by

Sk. Fahad Chowdhury

2015

| The Dissertation Committee for Sk. | Fahad Chowdhury       | Certifies that this is the |

|------------------------------------|-----------------------|----------------------------|

| approved version of                | f the following disse | rtation:                   |

Design, Fabrication and Characterization of Field-Effect Transistors Based on Two-dimensional Materials and Their Circuit Applications

| Committee:                         |

|------------------------------------|

|                                    |

| Deji Akinwande, Supervisor         |

| Sanjay K. Banerjee , Co-Supervisor |

|                                    |

| Ananth Dodabalapur                 |

| Nan Sun                            |

|                                    |

| Keji Lai                           |

## Design, Fabrication and Characterization of Field-Effect Transistors Based on Two-dimensional Materials and Their Circuit Applications

by

Sk. Fahad Chowdhury, B.S.E.E.; M.S.E.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

August 2015

## **Dedication**

To my parents, wife and daughter

#### Acknowledgements

The journey towards earning the PhD degree has been a strenuous one, with few moments of joy and success in an overall difficult and challenging period. It will be unjustified to claim that it has been made possible without the help and support of numerous wonderful persons in my graduate school and personal life.

First of all, I would like to express my deepest gratitude to my supervisor Dr. Deji Akinwande, a person with a perfect mixture of technical and much needed human qualities. His technical guidance in all the projects, calm and composed demeanor and continued support throughout the whole period are very much appreciated. I am also privileged to have Dr. Sanjay Banerjee, a leading figure in semiconductor research, as my co-supervisor. His vast wealth of technical expertise, along with all his helps in various aspects, has been a great support. I am, in particular, very grateful to both of them for letting me develop as an independent researcher. I would like to thank Dr. Ananth Dodabalapur, Dr. Nan Sun and Dr. Keji Lai for their valuable time and effort for serving on my dissertation committee. I would also like to thank Dr. Nicole Benedek for serving on my qualifying examination committee.

I would like to thank Mr. Jeffrey Hicks, my manager during my internship at Intel, for providing me with the wonderful opportunity. I very much appreciate the mentorship of Dr. Shah Jahinuzzaman, whose technical guidance and support have enabled me to learn about a new technical area within a short period of three months. Working in a corporate environment with an industry leading semiconductor process node has been a really confidence boosting experience.

A very important part of this journey is the friendship and support of my colleagues at microelectronics research center. Jongho Lee and Hema CP Movva deserve special mention. They always had time for work related help and technical discussions, as well as refreshing friendly chats. I also appreciate the friendship of Maruthi Yogeesh, Sushant Sonde and Anupam Roy. I would also like to sincerely thank all my colleagues and friends including Nassibe Rahimi, Kristen Parrish, Milo Holt, Maryam Mortazavi, Li Tao, Hsiao-Yu Chang, Ajith Gopalakrishnan, Wei Li, Joonseok Kim, Weinan Zhu, Avinash Nayak, Saungeun Park, Haiyu Hunag, Michael Ramon, Rudresh Ghosh, Chris Corbet, Sangwoo Kang, Harry Chou, Amritesh Rai, Tanuj Trivedi, Atresh Sanne, Rik Dey, Tanmoy Pramanik, Sayan Saha, Praveen Pashupathy. I also appreciate the technical and administrative supports of center's staffs, including Jo Ann Smith, Amy Jablon, Ricardo Garcia, Johny Johnson, William Ostler, Jesse James.

The biggest encouragement to pursue PhD came from my parents. I am infinitely indebted to them for their unconditional love, support and motivation throughout my entire life in all aspects. Their love and guidance have shaped me significantly into the person who I am. I am very thankful to my brother for his constant love and inspiration.

I am also very grateful to the government and people of Bangladesh for providing me with a solid educational foundation at little or almost no cost to me, which has enabled me to pursue PhD in a world renowned institution like UT Austin.

I am thankful for my newest source of joy and inspiration; my daughter. And finally, no word is enough to describe the love, support and sacrifice of my wife. She has been taking care of our family tirelessly, while pursuing her own doctoral work and studies. Thank you for being a loving wife, a wonderful mother to our daughter and a strong, reliable friend.

**Design, Fabrication and Characterization of Field-Effect Transistors**

**Based on Two-dimensional Materials and Their Circuit Applications**

Sk. Fahad Chowdhury, Ph.D.

The University of Texas at Austin, 2015

Supervisor: Deji Akinwande

Co-Supervisor: Sanjay K. Banerjee

The field of two-dimensional layered materials has witnessed extensive research

activities during the past decade, which commenced with the seminal work of isolating

graphene from bulk graphite. In addition to providing a rich playground for scientific

experiments, graphene has soon become a material of technological interest for many of

its fascinating electrical, thermal, mechanical and optical properties. The controllability

of carrier density with electric field in graphene, along with very high carrier mobility

and saturation velocity, has motivated the use of graphene channel in field-effect devices.

Also, the two-dimensional layered materials family has grown very rapidly with the

application of the graphene exfoliation technique and many of these elemental and

compound materials are considered useful for transistor applications.

In this work, various aspects of the use of two-dimensional layered materials for

transistor applications were analyzed. Starting with material synthesis, field-effect

transistors (FETs) were designed, fabricated and tested for their DC and high frequency

performances. Through the detailed electrical and spectroscopic investigations of several

processing techniques for enhanced FET performance, numerous insights were obtained

into the FET operation and performance bottlenecks. The reduction of charged impurity

vii

scattering in graphene FET by Hexamethyldisilazane interaction improved field-effect mobility and reduced residual carrier concentration. This technique was also shown to be promising for other two-dimensional materials based FET. A useful technique for reducing the thickness of black phosphorus flake with oxygen plasma etching was developed. Both back-gated and top-gated FETs were implemented with good performances. Secondary ion mass spectroscopy and x-ray photoelectron spectroscopy revealed vital structural information about layered black phosphorus. Lastly, these exotic materials based FETs were characterized for their high frequency performance, resulting in gigahertz range transit frequency and operated in a variety of important circuit configurations such as frequency multiplier, amplifier, mixer and AM demodulator.

### **Table of Contents**

| List of Fig | rures                                                           | xii         |

|-------------|-----------------------------------------------------------------|-------------|

| Chapter 1:  | Introduction                                                    | 1           |

|             | 1.1 Motivation                                                  | 1           |

|             | 1.2 Outline                                                     | 3           |

| Chapter 2:  | CVD Graphene Transfer to Arbitrary Substrates                   | 4           |

|             | 2.1 Process Steps for Graphene Transfer                         | 5           |

|             | 2.2 Empirical Observations                                      | 8           |

| Chapter 3:  | Transistor Performance Improvement by Surface Treatment         | 9           |

|             | 3.1 Device Fabrication and Measurement Procedure                | .10         |

|             | 3.2 Room Temperature Electrical Transport                       | .12         |

|             | 3.3 Time Evolution of Characteristics                           | .14         |

|             | 3.4 Performance Improvement Mechanisms                          | .15         |

|             | 3.5 Temperature Dependent Transport Characteristics             | .17         |

|             | 3.6 HMDS Treatment of FET Fabricated on Hydrophobic Surface     | .19         |

|             | 3.7 Raman Spectroscopic Analysis                                | .21         |

|             | 3.8 Stability Considerations                                    | .22         |

|             | 3.9 HMDS treatment of MoS <sub>2</sub> based FET                | .23         |

| Chapter 4:  | Thickness Tuning of Black Phosphorus Flakes by Plasma Treatment | t <b>29</b> |

|             | 4.1 Experimental Methods                                        | .31         |

|             | 4.2 Optical and AFM Characterizations of Flake Thinning Process | .32         |

|             | 4.3 Impact of Thinning Process on Field-Effect Transistor       | .38         |

|             | 4.3.1 Back-gated FET                                            | .38         |

|             | 4.3.2 Top-gated FET                                             | .41         |

|             | 4.4 Spectroscopic Analysis                                      | .48         |

|             | 4.4.1 Raman Spectroscopic Analysis                              | .48         |

|             | 4.4.2 TOF-SIMS Analysis                                         | .49         |

|             | 4.4.3 XPS Analysis                                              | .55         |

| 4.5 Stability of O <sub>2</sub> Plasma Treated BP57                                                          |

|--------------------------------------------------------------------------------------------------------------|

| Chapter 5: High Frequency Performance of Two-Dimensional Materials Based FETs and Their Circuit Applications |

| 5.1 High Frequency Characterization and Circuit Applications of BP FET60                                     |

| 5.1.1 Device Fabrication60                                                                                   |

| 5.1.2 DC and High Frequency Characterizations61                                                              |

| 5.1.3 High Frequency Circuit Applications of BP FET: CS Amplifier64                                          |

| 5.1.4 High Frequency Circuit Applications of BP FET: Mixer65                                                 |

| 5.1.5 High Frequency Circuit Applications of BP FET: AM  Demodulator                                         |

| 5.1.6 Impacts of Device Design and Measurement Setup on Performance                                          |

| 5.2 Frequency Multiplier with Graphene FET72                                                                 |

| 5.2.1 Device Fabrication                                                                                     |

| 5.2.2 High Frequency Characterization and Frequency Doubler Operation                                        |

| Chapter 6: Conclusion76                                                                                      |

| 6.1 Summary76                                                                                                |

| 6.2 Suggestions for Future Works77                                                                           |

| 6.2.1 CVD Grown Graphene Transfer77                                                                          |

| 6.2.2 Transistor Performance Improvement by HMDS Treatment77                                                 |

| 6.2.3 Black Phosphorus Flake Thinning with O <sub>2</sub> Plasma Treatment78                                 |

| 6.2.4 High Frequency Characterization and Circuit Applications of 2D materials79                             |

| Appendix80                                                                                                   |

| A.1 CVD Graphene Transfer to Arbitrary Substrates80                                                          |

| A.2 Hexamethyldisilazane (HMDS) Treatment of Two-Dimensional Materials                                       |

| A.3 Black Phosphorous (BP) Thickness Reduction by Oxygen | Plasma |

|----------------------------------------------------------|--------|

| Treatment                                                | 82     |

| A.4 Top-Gated Black Phosphorous (BP) FET Fabrication     | 83     |

| References                                               | 85     |

## **List of Figures**

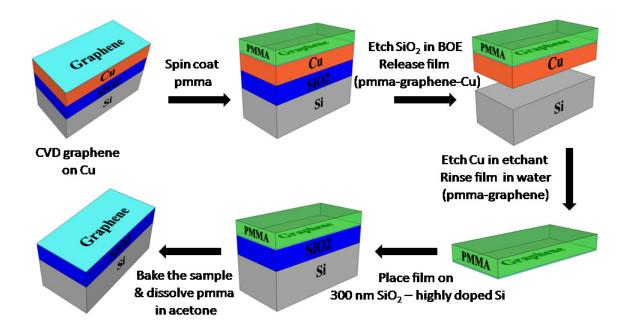

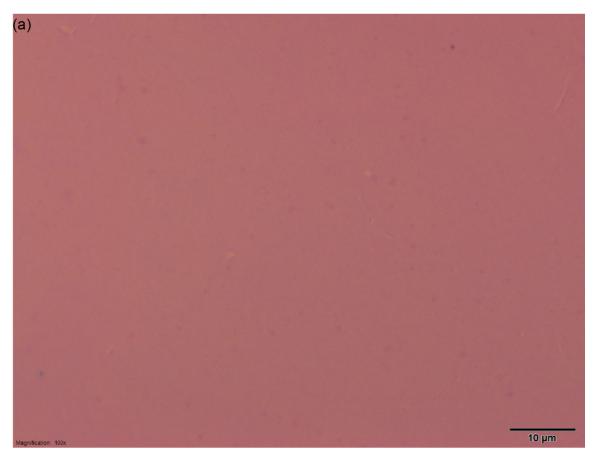

| Figure 2.1: | Process steps for transferring CVD grown graphene5                                                 |

|-------------|----------------------------------------------------------------------------------------------------|

| Figure 2.2: | (a) Graphene transferred on 300 nm SiO <sub>2</sub> -Si substrate. Scale bar is 10                 |

|             | μm. (b) Representative Raman spectrum from the sample showing high                                 |

|             | quality graphene                                                                                   |

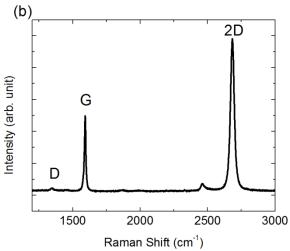

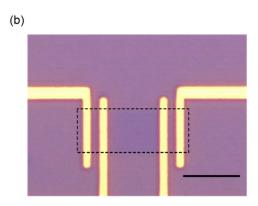

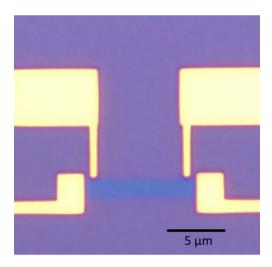

| Figure 3.1: | (a) Fabrication steps and measurement procedure for HMDS surface                                   |

|             | treatment method. (b) Optical image of a fabricated back-gated graphene                            |

|             | FET with four contacts. Patterned graphene area is outlined with dashed                            |

|             | line. Scale bar is 5 µm                                                                            |

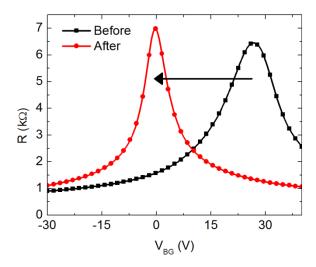

| Figure 3.2: | Resistance, R versus back-gate voltage, $V_{\text{BG}}$ plot of a representative                   |

|             | device before (black square) and after (red circle) HMDS treatment.13                              |

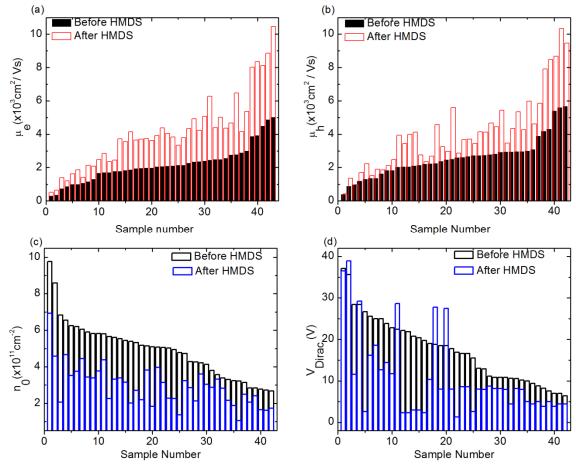

| Figure 3.3: | Statistics of fabricated devices before and after HMDS application, (a)                            |

|             | electron mobility, $\mu_{e}\left(b\right)$ hole mobility, $\mu_{h}\left(c\right)$ residual carrier |

|             | concentration, n <sub>0</sub> and (d) Dirac voltage, V <sub>Dirac</sub> 14                         |

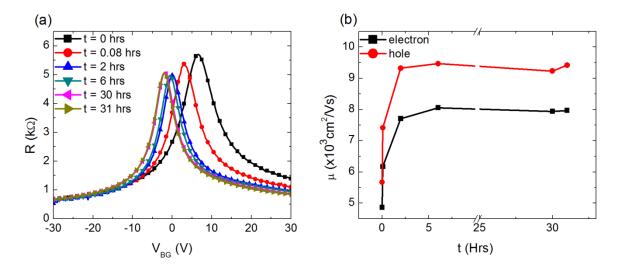

| Figure 3.4: | Evolution of the electrical characteristics with HMDS soak time. (a)                               |

|             | Resistance, R versus back-gate voltage, VBG plots at different times,                              |

|             | and (b) electron (black square) and hole (red circle) mobility, $\boldsymbol{\mu}$                 |

|             | evolution with time, t                                                                             |

| Figure 3.5: | Temperature dependent electrostatic measurements. Resistance, R                                    |

|             | versus back-gate voltage, $V_{BG}$ plot at 295K (black square) and 77K (red                        |

|             | circle). (a) Before HMDS application, and (b) after HMDS application.                              |

|             | (c) Electron mobility, $\mu_e$ and (d) hole mobility, $\mu_h.$ The straight lines                  |

|             | serve as visual guides only19                                                                      |

| Figure 3.6:  | Resistance, R versus back-gate voltage, V <sub>BG</sub> (both forward and reverse      |

|--------------|----------------------------------------------------------------------------------------|

|              | sweeps) plot for a representative device fabricated with graphene                      |

|              | transferred on hydrophobic $SiO_2$ substrate with HMDS treatment prior to              |

|              | graphene transfer. Data for before and after HMDS treatment of top                     |

|              | surface of fabricated device are represented by black squares and red                  |

|              | circles, respectively                                                                  |

| Figure 3.7:  | Raman Spectroscopic Analysis (a) G peak position, Pos(G) of graphene                   |

|              | Raman spectra for 121 scans before (black square) and after (red circle)               |

|              | HMDS treatment. (b) G peak full width half max, FWHM(G) before                         |

|              | (black square) and after (red circle) HMDS treatment. (d) Intensity ratio              |

|              | between 2D and G peaks, $I(2D)$ / $I(G)$ before (black square) and after               |

|              | (red circle) HMDS treatment                                                            |

| Figure 3.8:  | (a) Evolution of transfer characteristics with time for a sample stored                |

|              | under ambient conditions. (b) Transfer characteristics for PMMA                        |

|              | encapsulation                                                                          |

| Figure 3.9:  | Optical image of a fabricated BGFET with monolayer MoS <sub>2</sub> channel.           |

|              |                                                                                        |

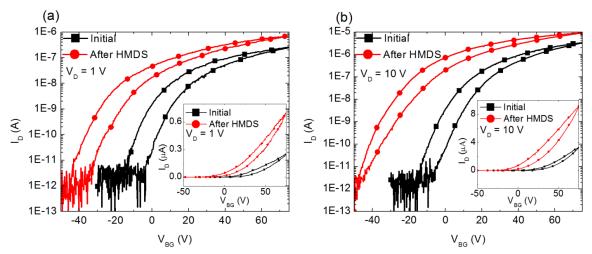

| Figure 3.10: | Transfer characteristics (log scale) of fabricated BGFET on monolayer                  |

|              | MoS <sub>2</sub> before and after HMDS treatment. Insets show same                     |

|              | characteristics in linear scale. (a) $V_D = 1 \text{ V}$ . (b) $V_D = 10 \text{ V}$ 25 |

| Figure 3.11: | BGFET with multilayer MoS <sub>2</sub> channel26                                       |

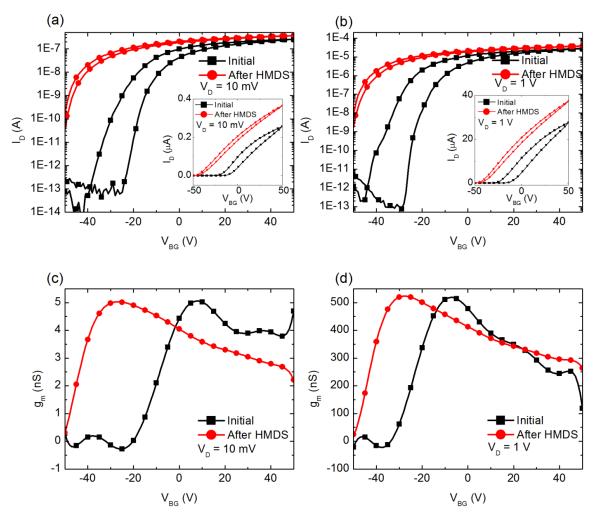

| Figure 3.12: | Transfer characteristics (log scale) and corresponding trans-conductance                          |

|--------------|---------------------------------------------------------------------------------------------------|

|              | plots of a multilayer MoS <sub>2</sub> based FET before and after HMDS treatment.                 |

|              | (a) $I_D$ - $V_{BG}$ plot for $V_D$ = 10 mV. (b) $I_D$ - $V_{BG}$ plot for $V_D$ = 1 V. Insets of |

|              | (a) and (b) show the characteristics in linear scale. (c) Trans-                                  |

|              | conductance, $g_m$ plot for $V_D$ = 10 mV. (d) Trans-conductance, $g_m$ plot                      |

|              | for $V_D = 1 V$                                                                                   |

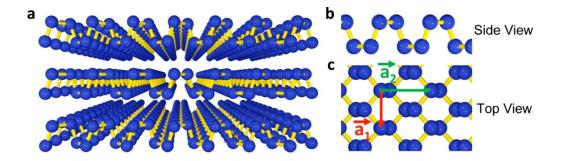

| Figure 4.1:  | Crystal structure of few-layer phosphorene. (a) Perspective side view of                          |

|              | few-layer phosphorene. (b) Side and (c) Top views of few-layer                                    |

|              | phosphorene. Adapted with permission from reference <sup>56</sup> . Copyright                     |

|              | (2014) American Chemical Society30                                                                |

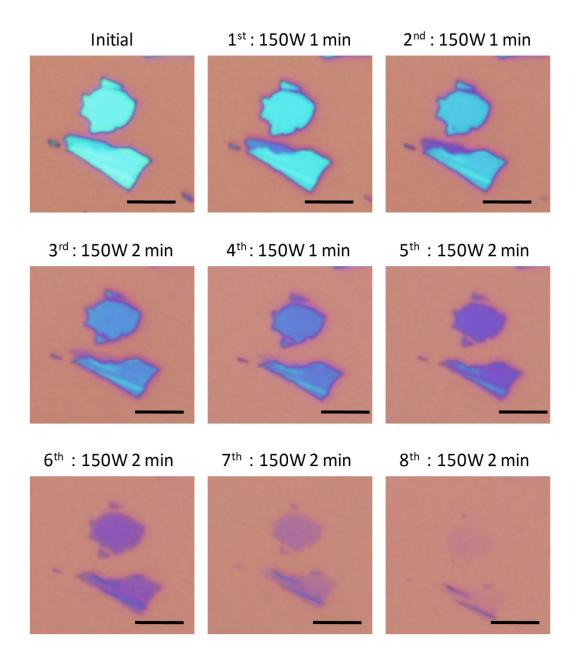

| Figure 4.2:  | Temporal sequence of flake thinning process. Caption on each optical                              |

|              | image include etch number, plasma power and duration. Scale bar is 5                              |

|              | μm33                                                                                              |

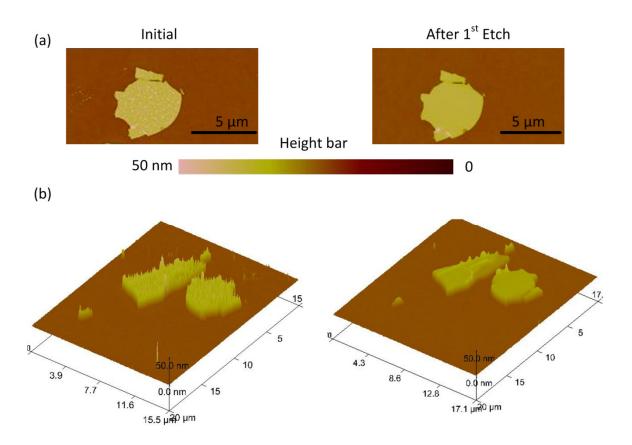

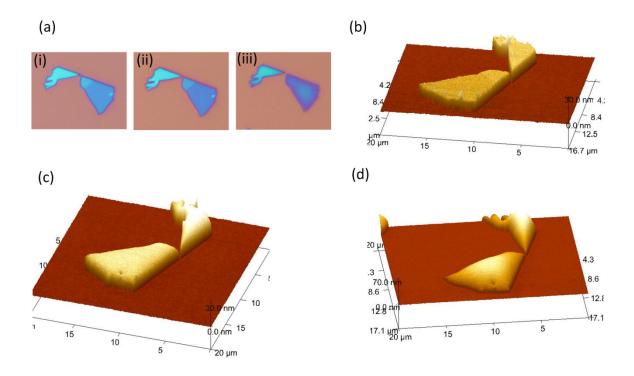

| Figure 4.3:  | AFM images of the BP flakes shown in Figure. 4.2. before and after                                |

|              | plasma treatment. (Left: as exfoliated, right: after first etch) (a) Top view                     |

|              | of the top flake in Figure 4.2. (b) 3D view of the flakes34                                       |

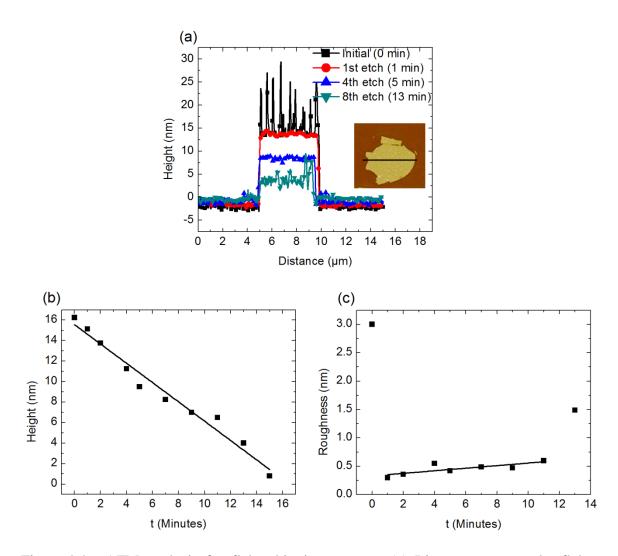

| Figure 4.4:  | AFM analysis for flake thinning process. (a) Line scan across the flake.                          |

|              | Time in parenthesis is cumulative time of current and all previous etch                           |

|              | steps. (b) Temporal evolution of flake height. (c) Temporal evolution of                          |

|              | flake roughness. The straight lines serve as visual guides only36                                 |

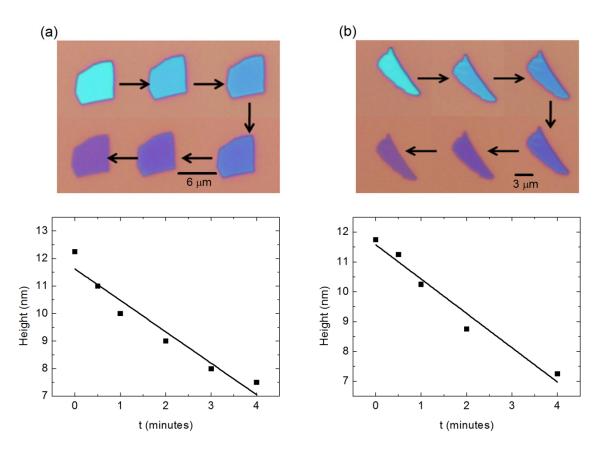

| Figure 4.5:  | Flake thinning process for couple of other flakes. Height evaluation data                         |

|              | obtained from AFM are placed below corresponding flakes37                                         |

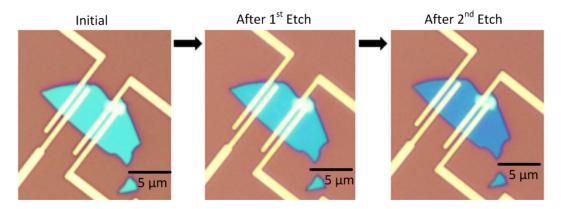

| Figure 4.6:  | O <sub>2</sub> plasma treatment of fabricated BGFET38                                             |

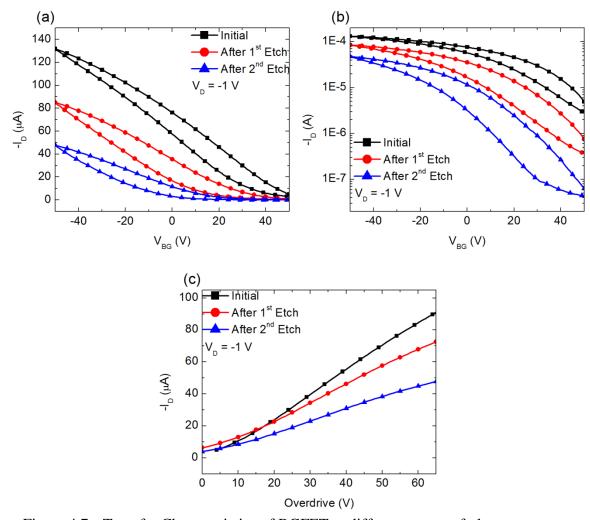

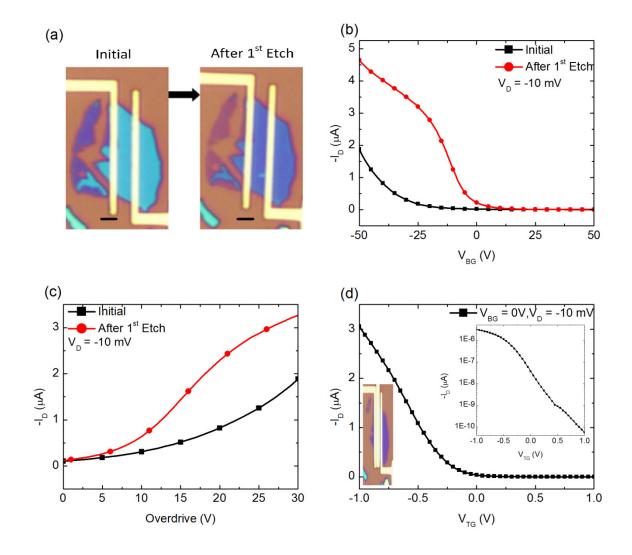

| Figure 4. /: | Transfer Characteristics of BGFET at different stages of plasma                                       |

|--------------|-------------------------------------------------------------------------------------------------------|

|              | treatment. (a) $-I_D$ Vs $V_{BG}$ (linear scale) for bidirectional sweep of $V_{BG}$                  |

|              | (b) $-I_D \; Vs \; V_{BG} \; (log \; scale)$ for bidirectional sweep of $V_{BG} \; (c) \; -I_D \; Vs$ |

|              | overdrive voltage ( $V_{BG}$ - $V_{TH}$ ) for +50V to -50V $V_{BG}$ sweep39                           |

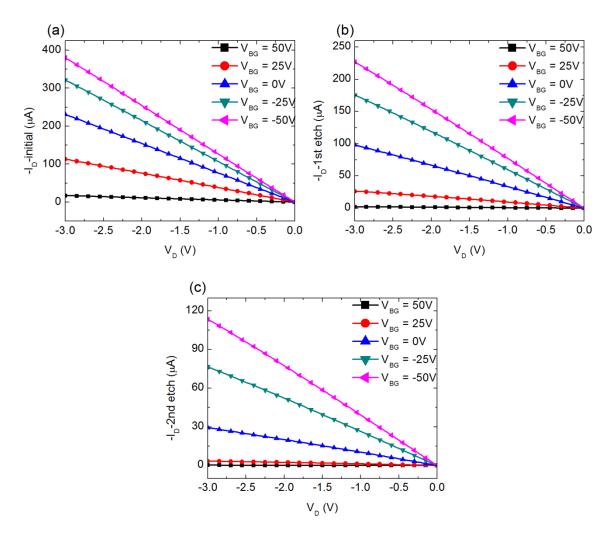

| Figure 4.8:  | Output Characteristics (drain current, - $I_D$ Vs drain bias, $V_D$ ) of BGFET                        |

|              | for different back-gate voltages at different stages of plasma treatment.                             |

|              | (a) Initial (b) After 1 <sup>st</sup> etch (c) After 2 <sup>nd</sup> etch41                           |

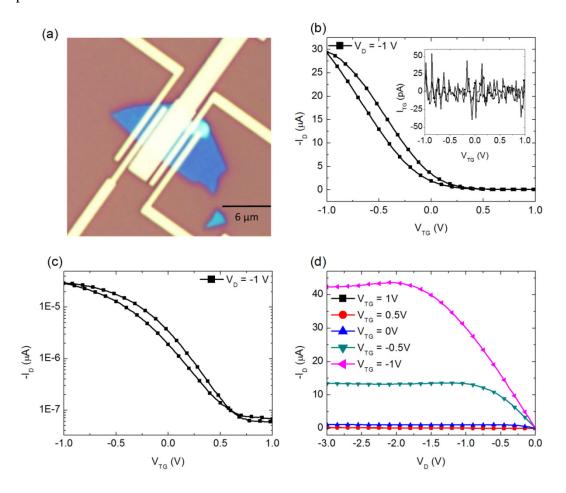

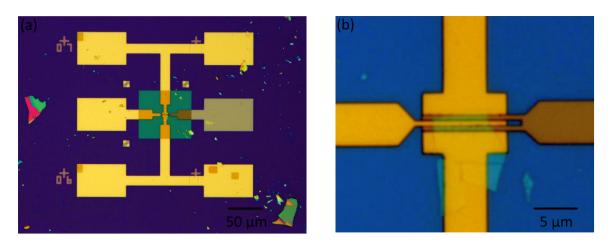

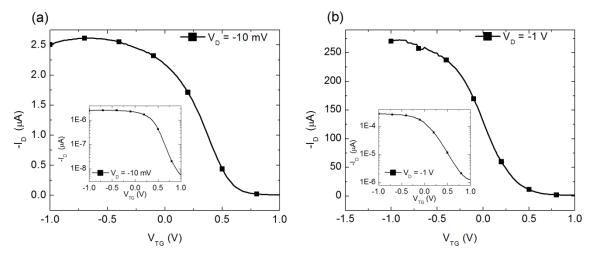

| Figure 4.9:  | Electrical characteristics of top-gated FET (TGFET) with unbiased                                     |

|              | back-gate. (a) Optical Image of the TGFET. (b) Transfer characteristics                               |

|              | for $V_D$ = -1V in linear scale for bidirectional $V_{TG}$ sweep. Inset shows                         |

|              | top-gate leakage current. (c) Transfer characteristics for $V_D$ = -1V in log                         |

|              | scale for bidirectional $V_{TG}$ sweep. (d) Output characteristics for different                      |

|              | top-gate voltages                                                                                     |

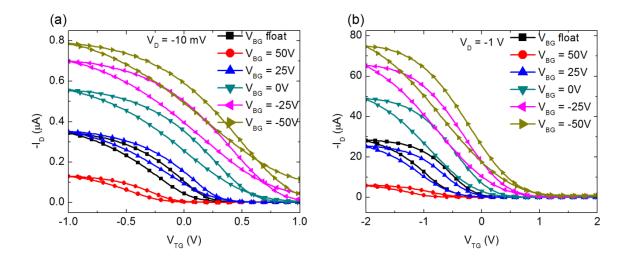

| Figure 4.10: | Top-gated transfer characteristics under different back-gate bias                                     |

|              | conditions. (a) $V_D = -10 \text{ mV}$ (b) $V_D = -1V$ 44                                             |

| Figure 4.11: | Output characteristics for different top-gate voltage, $V_{\text{TG}}$ under different                |

|              | back-gate voltage, $V_{BG}$ conditions. (a) $V_{BG}$ = 50 V, (b) $V_{BG}$ = 0 V, and                  |

|              | (c) $V_{BG} = -50 \text{ V}.$                                                                         |

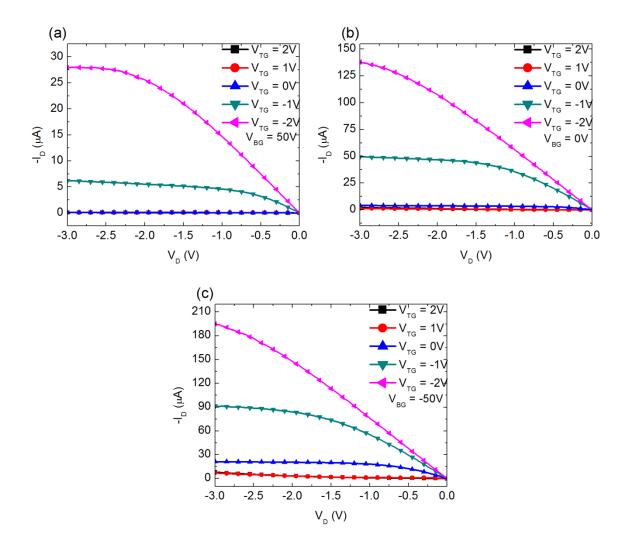

| Figure 4.12: | Transistor data for another device with thinned flake. (a) Optical images                             |

|              | before and after $O_2$ plasma etch. Scale bar is 1 $\mu m$ . (b) Back-gated                           |

|              | transfer characteristics before and after etching at $V_D = -10$ mV. (c)                              |

|              | Device current plotted with available overdrive for BGFET. (d) Top-                                   |

|              | gated transfer characteristics with $V_{BG}$ = 0 V and $V_{D}$ = -10 mV. Inset                        |

|              | shows the same plot in log scale. An optical image of the TGFET is                                    |

|              | included at the bottom left corner                                                                    |

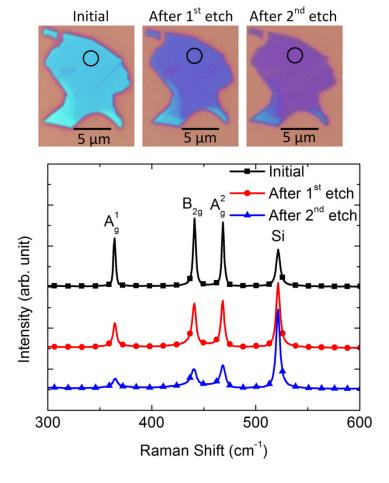

| Figure 4.13: | Raman Analysis of a thinned BP flake at different stages. The black                         |

|--------------|---------------------------------------------------------------------------------------------|

|              | circles in the optical images indicate the scan spot. The associated                        |

|              | Raman spectra are shown below the optical images49                                          |

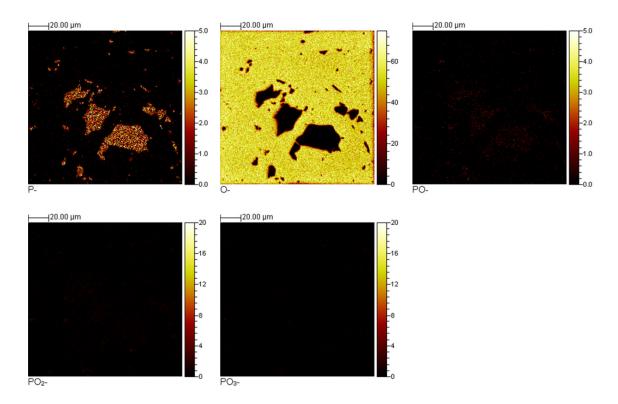

| Figure 4.14: | TOF-SIMS mapping for BP flakes before O <sub>2</sub> plasma treatment51                     |

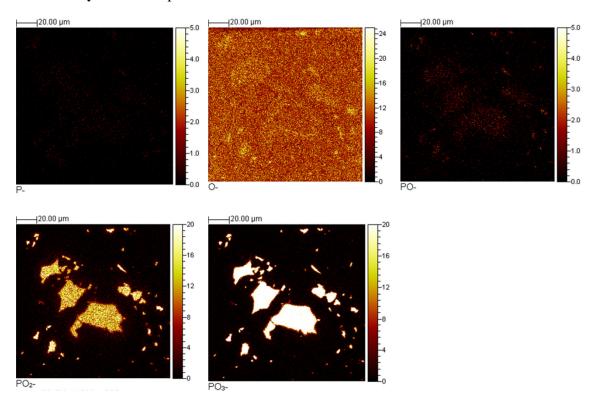

| Figure 4.15: | TOF-SIMS mapping for BP flakes after O <sub>2</sub> plasma treatment52                      |

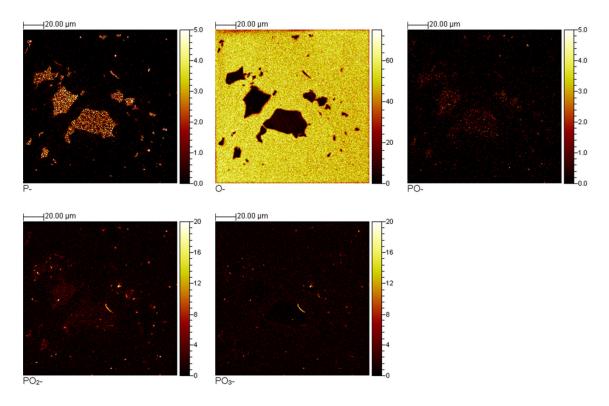

| Figure 4.16: | TOF-SIMS mapping for O <sub>2</sub> plasma treated BP flakes after sputtering               |

|              | with 1 kV Cs <sup>1+</sup> beam for 5 seconds                                               |

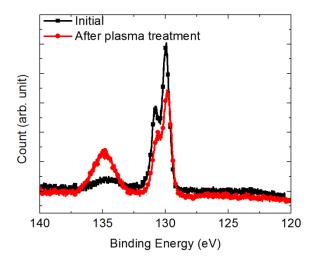

| Figure 4.17: | XPS spectrums of BP before and after O <sub>2</sub> plasma treatment55                      |

| Figure 4.18: | Plasma treated BP flake stability. (a) Optical images at different stages;                  |

|              | (i) Initial, (ii) After 28 hours (iii) After 100 hours. (b) 3D AFM image of                 |

|              | initial BP flakes. (c) 3D AFM image of BP flakes after 28 hours. (d) 3D                     |

|              | AFM image of BP flakes after 100 hours58                                                    |

| Figure 5.1:  | Optical images of fabricated BP FET (W / L = 13 $\mu$ m / 0.5 $\mu$ m). (a)                 |

|              | Complete device. (b) Magnified image of channel area60                                      |

| Figure 5.2:  | DC transfer characteristics. (a) $V_D = -10 \text{ mV}$ . (b) $V_D = -1 \text{ V}$ . Insets |

|              | show corresponding log scale plots61                                                        |

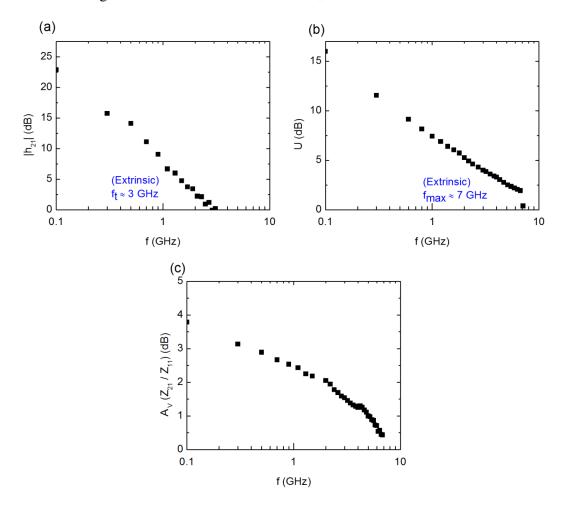

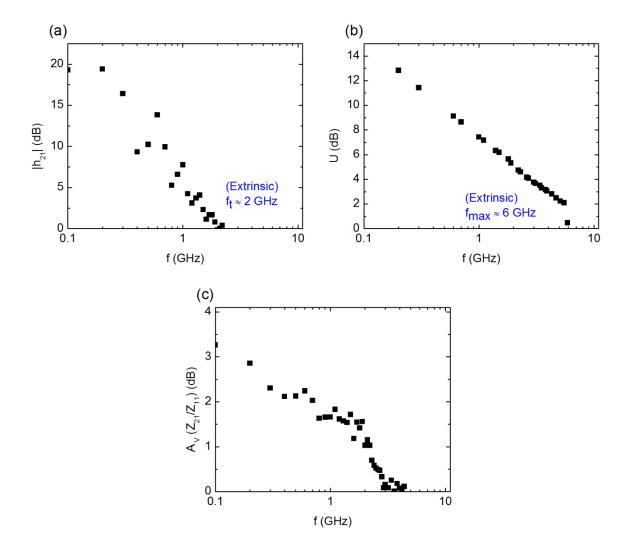

| Figure 5.3:  | (a) Short circuit current gain, $ h_{21} $ plotted as a function of frequency, f.           |

|              | Extrinsic transit frequency is ~ 3 GHz. (b) Power gain, U plotted as a                      |

|              | function of frequency, f. Extrinsic maximum oscillation frequency is ~ 7                    |

|              | GHz. (c) Intrinsic voltage gain, A <sub>v</sub> plotted as a function of frequency          |

|              | showing availability of voltage gain upto ~ 7 GHz63                                         |

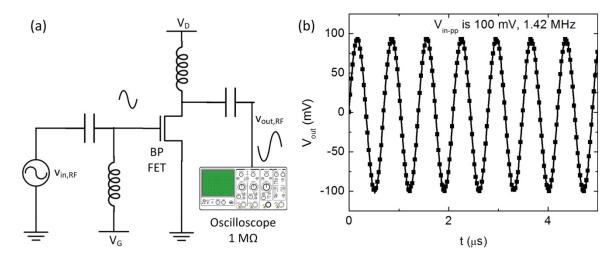

| Figure 5.4:  | (a) Schematic of a common source (CS) amplifier configuration. (b)                          |

|              | Output waveform of the CS amplifier for 1.42 MHz input signal,                              |

|              | revealing 6 dB gain65                                                                       |

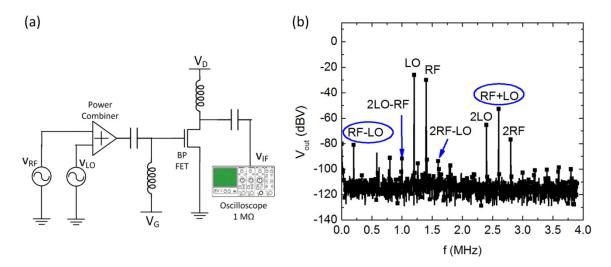

| Figure 5.5:  | (a) Schematic of a single FET mixer configuration. (b) Output FFT                       |

|--------------|-----------------------------------------------------------------------------------------|

|              | spectrum obtained from oscilloscope. Both up-converted ( $\omega_{RF} + \omega_{LO}$ )  |

|              | and down-converted $(\omega_{RF}$ - $\omega_{LO})$ frequency components are clearly     |

|              | present66                                                                               |

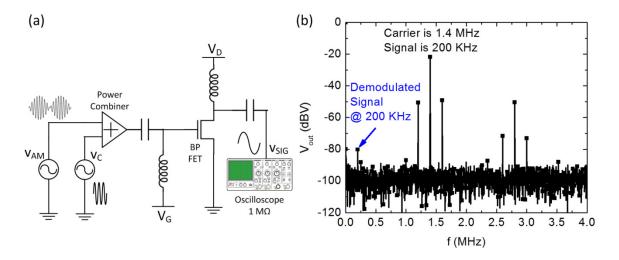

| Figure 5.6:  | (a) Schematic diagram of AM demodulator. (b) Output spectrum of AM                      |

|              | demodulator showing the recovered AM signal at 200 KHz along with                       |

|              | other generated frequency components67                                                  |

| Figure 5.7:  | RF characterization of BP FET used in CS amplifier. (a) Short circuit                   |

|              | current gain, $ h_{21} $ plotted as a function of frequency, f. Extrinsic transit       |

|              | frequency is ~ 2 GHz. (b) Power gain, U plotted as a function of                        |

|              | frequency, f. Extrinsic maximum oscillation frequency is ~ 6 GHz. (c)                   |

|              | Intrinsic voltage gain, A <sub>v</sub> plotted as a function of frequency showing       |

|              | availability of voltage gain upto ~ 3-4 GHz71                                           |

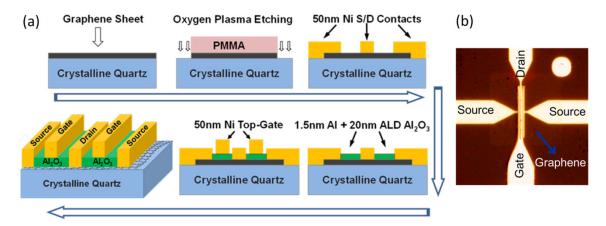

| Figure 5.8:  | (a) Process flow for top-gated Graphene FET. (b) Optical image of a                     |

|              | fabricated GFET in ground-signal-ground (GSG) structure, W/L = 50                       |

|              | μm/0.5 μm. © 2012 IEEE73                                                                |

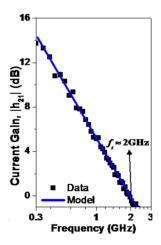

| Figure 5.9:  | Short circuit current gain plot for GFET showing (extrinsic) transit                    |

|              | frequency of 2 GHz © 2012 IEEE74                                                        |

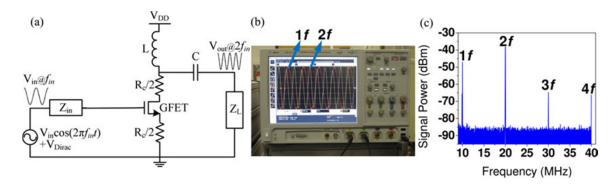

| Figure 5.10: | (a) Schematic of GFET frequency doubler. (b) Real time oscilloscope                     |

|              | output showing frequency doubling operation with 1f = 1 MHz and 2f =                    |

|              | 2 MHz. (c) Spectrum analyzer output with 10 MHz, 0 dBm input. $\ensuremath{\mathbb{O}}$ |

|              | 2012 IEEE                                                                               |

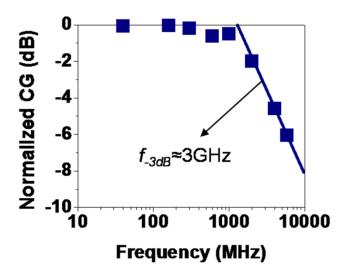

| Figure 5.11: | Normalized CG plotted with input frequency, revealing 3 GHz                             |

|              | Bandwidth. © 2012 IEEE                                                                  |

#### **Chapter 1: Introduction**

#### 1.1 Motivation

Computing and electronics have been playing an ever increasing role in the advancement of civilization for the past fifty years. The semiconductor industry has been consistently delivering innovative products and solutions with ever increasing functionalities and reduced cost by keeping pace with the famous Moore's law, which dictates that the transistor count in a chip doubles every 18-24 months. The sustenance of this rapid progression has largely been enabled by making silicon based transistors smaller, faster and power efficient. Performance and density improvements had been accomplished by classical geometric scaling according to Dennard's law till the beginning of this millennium and recently, several additional technological breakthroughs such as strained channel, high  $\kappa$  – metal gate, FinFETs etc. have been employed. However, with device dimensions approaching sub-10 nm and device operation hitting fundamental physical and quantum mechanical barriers, researchers have been rigorously deliberating at alternative materials, devices and architectures to deliver exciting new systems with unprecedented functionality and performance.

Two-dimensional layered materials have recently gained enormous interest for transistor applications, which were initially motivated by the ultrahigh carrier mobility and ultimate thickness scalability of graphene.<sup>3</sup> Within a few years, the number of two-dimensional materials has literally exploded with various elemental and compound materials such as  $MX_2$  (M = Mo, W etc. and X = S, Se, Te etc.), silicene, phosphorene etc., among others. The family of two-dimensional materials is a rich one with diverse properties and field-effect transistors (FETs) have been demonstrated with many of its members.

Although these FETs are at their nascent stage in the research labs at present, they are envisioned to be widely integrated into future electronic systems in varying capacities. One long term goal is to use the best suitable material / materials combination as a replacement of silicon for beyond CMOS device applications. In reality, this seems to be a distant goal due to the inertia of the multibillion dollar Silicon industry dominated by digital applications and other comparatively matured candidates, such as III-V materials and germanium, in queue. Heterogeneous integration of these materials and FETs with existing CMOS to deliver enhanced functionality is a more promising application. While digital applications almost exclusively use silicon, analog/mixed signal systems use variety of materials and devices and they are more open towards new technologies.<sup>3</sup> Several two-dimensional materials show excellent high frequency performance. For example, ~500 GHz cut off frequency for graphene FET has already been demonstrated with projected performance in the terahertz frequency range.<sup>4</sup> One of the greatest promises of these FETs lies in the area of flexible and wearable electronics due to their superior electrical and mechanical properties compared to their existing counterparts.<sup>5</sup>

In summary, the initial results with two-dimensional materials based FETs show substantial promises and a variety of prospective applications have been identified. However, in order to fully realize the potential of these materials and their FETs, it is imperative to thoroughly understand their operating mechanisms and performance limiting factors and also develop processing technology solutions to mitigate these factors. To this end, several important issues of technological importance regarding two-dimensional materials based FETs are addressed in this dissertation through the design, fabrication and characterization of these FETs and their circuit applications.

#### 1.2 Outline

This dissertation is organized as follows.

In chapter 2, a wet transfer procedure for large area, CVD grown graphene is described and several observations are made to improve the quality of the process.

In chapter 3, a performance enhancement technique is reported for graphene FETs with Hexamethyldisilazane (HMDS) treatment. Room temperature electrical characteristics with statistical distribution of performance metrics and low temperature transport characteristics are analyzed with and without HMDS treatment. Raman spectroscopic analysis data are presented in support of proposed performance enhancement mechanism. This technique is extended to MoS<sub>2</sub> devices as well.

An Oxygen (O<sub>2</sub>) plasma etching process for black phosphorus flake thickness reduction is presented in chapter 4. After detailed optical and atomic force microscopy (AFM) analysis of the flake thinning process, its impact on electrical characteristics are analyzed by characterizing back-gated and top-gated transistors fabricated with plasma processed flakes. To assess the chemical impact of the flake thinning process, Raman spectroscopy, secondary ion mass spectroscopy and X-ray photoelectron spectroscopy analyses are presented.

The high frequency performance of graphene and black phosphorus based FETs fabricated in GSG structures are investigated in chapter 5. After initial DC characterization, transit or cut-off frequencies are measured for these devices. Useful circuit operations are demonstrated using these devices as well.

Finally, the key results of the above mentioned works are summarized in chapter 6 and suggestions for future works are presented based on these results.

#### **Chapter 2: CVD Graphene Transfer to Arbitrary Substrates**

Graphene, a single layer of sp<sup>2</sup> bonded carbon atoms arranged in two-dimensional honeycomb lattice, has been regarded as the wonder material of 21<sup>st</sup> century for its exceptional electronic, thermal, mechanical and optical properties.<sup>6–10</sup> Extremely high charge carrier mobilities, high saturation velocity, high current carrying capacity etc. have made graphene a material of great interest for electronic applications.<sup>11,12</sup> Graphene was first isolated from bulk graphite crystal using scotch tape based exfoliation technique and it has remained a popular method for obtaining pristine, high quality crystals.<sup>6</sup> Typically small graphene flakes of few tens of micrometers in size are produced by this method. While these flakes are sufficiently big for scientific research and proof of concept device demonstrations, commercial and technological applications require large area graphene films with a quality comparable to exfoliated flakes.

One successful and widespread pathway to large area graphene is growth via chemical vapor deposition (CVD) on metallic substrates such as copper, nickel etc. However, in order to make field-effect transistors (FET), this large area graphene needs to be transferred to desired insulating substrate with minimal degradations. In this chapter, a wet transfer method of CVD grown graphene to arbitrary substrate is developed. The transfer process is illustrated in Figure 2.1 and optimized based on the structural and electrical qualities of transferred graphene.

Figure 2.1: Process steps for transferring CVD grown graphene.

#### 2.1 Process Steps for Graphene Transfer

- Monolayer graphene is grown by CVD on a 1μm thick copper (Cu) film evaporated on top of 300 nm thick SiO<sub>2</sub>, thermally grown on a Si substrate.<sup>13</sup>

- The transfer process begins by spin coating PMMA on the growth substrate (graphene-Cu-SiO<sub>2</sub>-Si). The sample is left in a desiccator overnight in order to drive off solvent.

- The sample is then immersed in 6:1 buffered oxide etch (BOE) to etch the SiO<sub>2</sub> which leaves PMMA-graphene-Cu film detached from the growth substrate. A piece of clean Si is placed at an inclined angle in the BOE solution to gently take the film out of the solution and rinse it with Di-Ionized (DI) water.

- The PMMA-graphene-Cu film is then placed in 10:1 H<sub>2</sub>0 : Ammonium Persulfate (APS-100, Transene INC.) solution to etch Cu. After Cu is completely etched

within  $\sim 10$  minutes, the clean Si is used to take the floating PMMA-graphene film from etchant solution and rinse it in DI water several times. Finally, the target substrate (300 nm SiO<sub>2</sub> – highly doped Si or any other arbitrary substrate) is partially immersed in DI water at an inclined angle to place the PMMA-graphene film on the substrate.

- The substrate is left in desiccator box for several hours. After the sample has dried and PMMA-graphene film is visibly lying dry and flat on the substrate, the sample is heated at 130°C for 2-3 minutes on a hotplate in order to remove remaining moisture and improve the adhesion between the film and substrate.

- The sample is left in acetone for several hours to remove the PMMA on top of graphene. Finally, the sample is rinsed with Isopropyl Alcohol (IPA) and blown dry with nitrogen which leaves graphene on SiO<sub>2</sub>-Si substrate.

Figure 2.2(a) shows an optical image of graphene transferred on SiO<sub>2</sub>-Si which demonstrates successful transfer of large area, smooth graphene with very few cracks and tears. Raman spectroscopy is a versatile tool graphene characterization.<sup>14</sup> A representative Raman spectrum of transferred graphene with characteristic peaks is shown in Figure 2.2(b). Negligible defect peak intensity at ~1350 cm<sup>-1</sup>, a narrow (~32 cm<sup>-1</sup>) 2D peak at 2680 cm<sup>-1</sup> and modest intensity ratio (~ 2) between 2D and G (at ~1590 cm<sup>-1</sup>) peaks demonstrate high quality of transferred graphene film.

Figure 2.2: (a) Graphene transferred on 300 nm SiO<sub>2</sub>-Si substrate. Scale bar is 10  $\mu$ m. (b) Representative Raman spectrum from the sample showing high quality graphene.

#### 2.2 Empirical Observations

We can make several empirical observations based on numerous transfer runs spanning over few years.

- The concentration of PMMA used for the transfer process impacts the final graphene quality. Higher concentration PMMA leaves more residues after removal in acetone compared to lower concentration PMMA. On the other hand, higher concentration PMMA results in higher thickness which makes the manual transfer process more robust. This observation has been reported in literature. <sup>15</sup>

- It should be mentioned that the transfer process described above is a two-step transfer process: SiO<sub>2</sub> on the growth substrate is etched first in BOE, and then Cu is etched in dilute Cu etchant. It is possible to put the growth substrate directly in as supplied Cu etchant. However, Cu etching and the release of PMMA-graphene film takes several hours in this case and graphene is immersed in Cu etchant for the whole time period. This results in degraded graphene quality which shows up in the poor electrical characteristics and Raman spectra.

- The PMMA baking temperature after PMMA-graphene film has dried on target substrate seems to have important effect. Baking is necessary to improve the adhesion between the film and substrate. Also, baking the sample above the glass transition temperature (T<sub>g</sub>) of PMMA (95-100°C) results in PMMA reflow which smoothens the film. However, baking at high temperature also leaves more residues after PMMA removal in acetone. Considering this aspect, we have chosen to bake the sample at 130°C, slightly above the T<sub>g</sub> of PMMA.

- Careful and proper rinsing of PMMA-graphene film in DI water after Cu etching is crucial to avoid defective and doped graphene with lower mobility.

# **Chapter 3: Transistor Performance Improvement by Surface Treatment**

Since its isolation, graphene has triggered a tremendous amount of interest for its exceptional electronic properties making it potentially interesting as a channel material for field-effect transistors (FET), especially for analog and RF applications. Among other things, carrier mobility is an important performance metric for FET application. FETs made by suspending graphene have reached mobility values in excess of ~ 200,000 cm²/Vs under high vacuum and low temperature condition revealing the intrinsically high mobility of charge carriers in graphene. The use of hexagonal boron nitride (h-BN) as a substrate for graphene FET has yielded mobility values comparable to this under similar conditions. However, the current prospect of h-BN is limited by the challenge of growing large area, high quality films with controllable thickness. The most practical and technologically viable substrate is still the widely used SiO<sub>2</sub>/Si.<sup>a</sup>

Typical room temperature mobility values for graphene devices fabricated on SiO<sub>2</sub> are below or around 10,000 cm<sup>2</sup>/Vs.<sup>21</sup> Various intrinsic and extrinsic performance limiting factors for graphene FETs have been identified.<sup>22,23</sup> In graphene, optical phonon energies are too high to participate at room temperature. Carrier interaction with graphene's acoustic phonon and remote interfacial phonon scattering by SiO<sub>2</sub> optical phonons indicate room temperature mobility upper limits of ~200,000 and ~ 40,000 cm<sup>2</sup>/Vs respectively, which are still very high compared to experimentally achieved mobility values for graphene devices. Coulomb scattering from impurities has been largely accepted to be the dominant scattering mechanism for experimental graphene FETs at room temperature. Hence, minimizing impurity scattering is a matter of

<sup>&</sup>lt;sup>a</sup> Part of this chapter is reprinted with permission from [Sk. F. Chowdhury, S. Sonde, S. Rahimi, L. Tao, S. Banerjee, and D. Akinwande, "Improvement of graphene field-effect transistors by hexamethyldisilazane surface treatment", *Applied Physics Letters*, vol. 105, no. 3, 2014.]. Copyright 2014, AIP Publishing LLC.

substantial importance for high performance graphene FET. One widely used approach is to passivate the graphene surface with different organic or inorganic materials, which enhance the electrostatic characteristics. 15,24,25

In this work, we report the improvement of graphene FET characteristics by treating the graphene surface with hexamethyldisilazane (NH(Si(CH<sub>3</sub>)<sub>3</sub>)<sub>2</sub>), commonly known as HMDS.<sup>26</sup> One unique aspect of HMDS compared with many other passivation layers is that it can react with the surface of SiO<sub>2</sub> to form a self-assembled monolayer and transform the hydrophilic surface to hydrophobic.<sup>27</sup> It should be mentioned here that HMDS has been previously used to construct hydrophobic SiO<sub>2</sub> surface before graphene exfoliation, which makes the graphene-SiO<sub>2</sub> interface free of adsorbed water.<sup>28</sup> Our approach is unique because we apply HMDS on graphene rather than SiO<sub>2</sub>, thus taking care of the adsorbed impurities on the top surface of graphene after device fabrication, which is not possible by the previous approach. Also in our case, we expect the HMDS molecules to form an adsorbed layer or clusters. But in the SiO<sub>2</sub> surface treatment method, HMDS molecules actually react with the silanol groups on SiO<sub>2</sub> surface. As will be discussed later, we applied HMDS on the top surface of graphene FETs fabricated on a HMDS treated, hydrophobic SiO<sub>2</sub> substrate and also observed improvement in characteristics. Hence these two techniques are different and, in principle, both of them should be combined for best performance improvement.

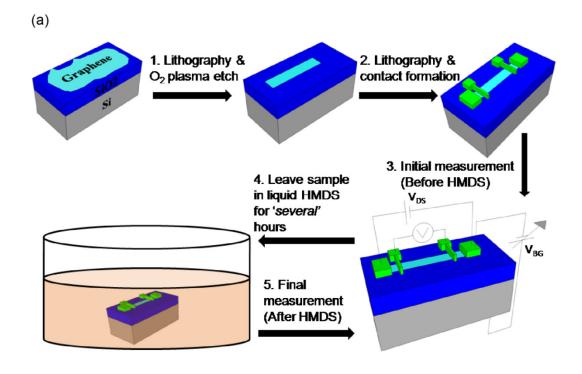

#### 3.1 Device Fabrication and Measurement Procedure

Figure 3.1(a) shows the fabrication steps and measurement procedure for our experiment. We start with CVD grown graphene transferred on 300 nm  $SiO_2$  - highly doped Si substrate, as described in chapter 2. Clean, continuous device active regions

were patterned using electron beam lithography and subsequent oxygen plasma etching.

Contacts to active region were defined by electron beam lithography, electron beam

Figure 3.1: (a) Fabrication steps and measurement procedure for HMDS surface treatment method. (b) Optical image of a fabricated back-gated graphene FET with four contacts. Patterned graphene area is outlined with dashed line. Scale bar is  $5~\mu m$ .

evaporation of Ti-Au metal stack (typically 1nm Ti - 49 nm Au) and liftoff. This completed the fabrication of back-gated field-effect transistors (BGFET) with four contacts where the highly doped Si and 300 nm SiO<sub>2</sub> acted as gate terminal and gate oxide, respectively. After initial measurement, the BGFET samples were immersed in liquid HMDS for several hours. Samples were then taken out of HMDS and dried in air. Figure 3.1(b) shows an optical micrograph of a fabricated BGFET.

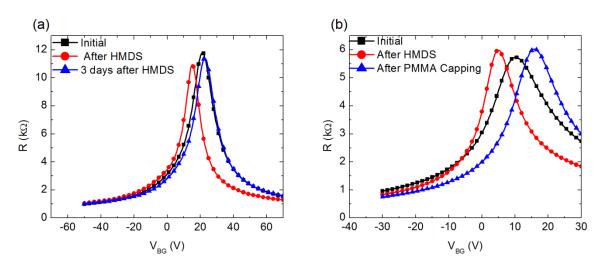

#### 3.2 Room Temperature Electrical Transport

The resistance of a representative device as a function of back-gate voltage before and after HMDS treatment is shown in Figure 3.2. The slopes of resistance versus gate voltage curve in the linear regime on both sides of maximum resistance point became sharper after HMDS application which indicates that both electron and hole field-effect mobilities were improved. We calculated mobility values along with residual carrier concentration based on a well-established diffusive transport model.<sup>29</sup> For this particular device, electron (hole) mobility increased from 2989 (2511) cm<sup>2</sup>/Vs to 4872 (5596) cm<sup>2</sup>/Vs. The maximum resistance point, also known as the Dirac point, moved from ~25 V to ~0 V. This indicates that initial p-type doping of as-fabricated device was reduced after HMDS application. The residual carrier concentration, n<sub>0</sub> was reduced from 4.26×10<sup>11</sup> cm<sup>-2</sup> to 2.12×10<sup>11</sup> cm<sup>-2</sup>, which is close to the theoretical intrinsic limit ~1.6×10<sup>11</sup> cm<sup>-2</sup>.<sup>30</sup> We also saw similar improvement for FETs made with exfoliated graphene.

The statistics of fabricated devices before and after HMDS application is presented in Figure 3.3. The data include devices made from several different batches. The general trend in electron and hole mobility improvement and reduction in residual carrier concentration is clear. However, the improvement factor is diverse for different

devices, which can be attributed to the initial and local graphene quality of fabricated devices. We usually observe mobility improvement of 1.5-2 times (50-100%) for most of our devices. Dirac voltage usually moves closer to 0 V. Hysteresis was usually suppressed after HMDS application but most of our devices had low hysteresis to begin with. There was no significant change in the ratio between maximum and minimum resistance values in transfer characteristics with HMDS treatment.

Figure 3.2: Resistance, R versus back-gate voltage, V<sub>BG</sub> plot of a representative device before (black square) and after (red circle) HMDS treatment.

Figure 3.3: Statistics of fabricated devices before and after HMDS application, (a) electron mobility,  $\mu_e$  (b) hole mobility,  $\mu_h$  (c) residual carrier concentration,  $n_0$  and (d) Dirac voltage,  $V_{Dirac}$ .

#### 3.3 Time Evolution of Characteristics

Evolution of electrical characteristics at different stages of HMDS application is shown in Figure 3.4. The sample was taken out of HMDS and measured after certain time periods. Changes in electrical characteristics were observed even after 5 minutes and the mobility values saturated within ~ 6 hours. The improvement factor was similar in range even for a week of soak time.

Figure 3.4: Evolution of the electrical characteristics with HMDS soak time. (a) Resistance, R versus back-gate voltage, VBG plots at different times, and (b) electron (black square) and hole (red circle) mobility,  $\mu$  evolution with time, t.

#### 3.4 Performance Improvement Mechanisms

Being a two-dimensional material, graphene is strongly influenced by its environment. Several atmospheric species such as moisture and oxygen molecules can adsorb on graphene's surface. Moreover, there can be polymer and organic residues during device fabrication. For example, PMMA used for graphene transfer and device fabrication cannot be completely removed by solvent or even by annealing. These adsorbed molecules and residues can serve as scattering sources and/or dopants resulting in an uncontrolled shift of the Dirac point with degraded mobility. The experimental results indicate that some of these degradation mechanisms are neutralized to varying degree upon HMDS treatment. For example, HMDS is widely used as hydrophobization agent, especially in biological science HMDS and it is efficient in removing water molecules present on a sample's surface. It has been shown that HMDS can react with water to form Trimethylsilanol (TMS) according to the following reaction Teact with water to form

$$((CH_3)_3Si)_2NH + 2H_2O \rightarrow 2(CH_3)_3SiOH + NH_3$$

(3.1)

The conversion of HMDS vapor in air at 50% relative humidity and 25°C to TMS has been verified experimentally by Fourier Transform Infrared Spectroscopy (FTIR).<sup>37</sup> HMDS may also modify the PMMA residues present on sample surface.<sup>38</sup> The reduction in residual carrier concentration upon HMDS treatment, as shown in Figure 3.3(c), supports our hypothesis.

Performance improvement is also likely to come from dielectric screening of charged impurities. <sup>39,40</sup> Charged impurities in the vicinity of graphene can cause long range Coulomb scattering. The presence of HMDS (dielectric constant,  $\kappa = 2.27$ ) instead of air ( $\kappa = 1$ ) increases the local dielectric constant. This, in turn, decreases the dimensionless fine structure constant which determines the interaction strength of charge carriers in graphene and charged impurities. Both theoretical and experimental studies have shown that reduction in fine structure constant results in improved carrier mobility along with reduced residual carrier density. <sup>24,40</sup>

In contrast, it has been shown in some Hall measurement experiments that the presence of high- $\kappa$  dielectric on graphene can significantly enhance the effective backgate capacitance and the change in electrostatic characteristics is mainly due to enhanced effective capacitance rather than mobility. It is difficult to conclude the extent of this mechanism from our electrostatic measurement. First of all, HMDS is a low- $\kappa$  liquid ( $\kappa$  = 2.27) and HMDS treated samples are completely dried in air before measurement, which should leave a very thin residual layer or trace amount of HMDS molecules. On the other hand, high- $\kappa$  liquids used in those experiments ( $\kappa$  > 25) were applied in droplets during measurement and capacitive enhancement was found to be proportional to the size of droplet. Also in those experiments, mobility was increased up to 100% which is consistent with our results. It has been proposed that these high- $\kappa$  polar solvents can

degrade mobility by additional Coulomb scattering from charged ion and dipole moment, which are not significant for HMDS.<sup>25</sup> More importantly, device capacitance measured for suspended graphene sample in non-polar ( $\kappa$ <5) liquid was found to be close to geometric capacitance of 300 nm SiO2, while for high- $\kappa$  solvents, capacitance increases by orders of magnitude compared to that.<sup>25</sup> Therefore, in light of previous studies and our current results, we attribute the enhancement in electrostatic characteristics to mobility improvement rather than capacitive enhancement.

#### 3.5 Temperature Dependent Transport Characteristics

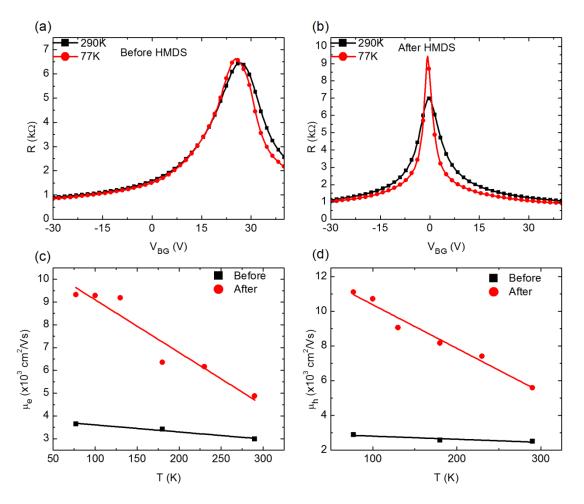

The temperature-dependent electrostatic measurements before and after HMDS application are shown in Figure 3.5. As-fabricated graphene FET shows small variation in the characteristics between 77K and room temperature, as shown in Figure 3.5(a). This is expected because transport is limited by relatively temperature insensitive charge impurity scattering in this temperature range.<sup>23</sup> On the other hand, there is a large variation in electrical characteristics between 77K and room temperature after HMDS treatment, as shown in Figure 3.5(b). Extracted electron and hole mobility values are shown as a function of temperature before and after HMDS application in Figure 3.5(c) and Figure 3.5(d), respectively. Carrier mobility increases by small amount only with decreasing temperature before HMDS application. But mobility at 77K is almost 2 times higher than room temperature mobility after HMDS treatment.

The reduction of charged impurities upon HMDS treatment may allow the relative contribution of rather temperature dependent phonon limited process to increase. As temperature is reduced, there is less thermal agitation of lattice, hence less scattering, which, in turn, causes mobility to improve with decreasing temperature. However, as mentioned before, remote oxide phonon scattering from SiO<sub>2</sub> substrate is the next

mobility limiting factor after charged impurities, which imposes an upper limit of 40,000 cm<sup>2</sup>/Vs at room temperature. This value is almost an order of magnitude higher than the device mobility in Figure 3.5. Hence this device is likely to be in the charged impurity limited regime for the temperature range of interest.

Mobility improvement with decreasing temperature can be attributed to temperature dependent dielectric constant of HMDS and/or TMS.<sup>43</sup> These are slightly polar molecules consisting of atoms with different electronegativities which can lead to dipole formation.<sup>44,45</sup> These dipoles align with electric field under applied bias. However, random thermal motion prevents good alignment at ambient temperature. As temperature is lowered, there is less thermal motion allowing the dipoles to align more perfectly with the field. This phenomenon, in effect, increases the orientational polarization and hence, the dielectric constant. Increase in dielectric constant leads to improvement of electrical characteristics with decreasing temperature by improved dielectric screening. Dielectric constant can also change at phase transition since material structures are usually different at different phases. The freezing points of HMDS and TMS are 193K and 214K, respectively. Hence these materials go through phase transitions in the temperature range of interest.

Figure 3.5: Temperature dependent electrostatic measurements. Resistance, R versus back-gate voltage,  $V_{BG}$  plot at 295K (black square) and 77K (red circle). (a) Before HMDS application, and (b) after HMDS application. (c) Electron mobility,  $\mu_e$  and (d) hole mobility,  $\mu_h$ . The straight lines serve as visual guides only.

#### 3.6 HMDS Treatment of FET Fabricated on Hydrophobic Surface

In order to further understand the effect of HMDS, back-gated graphene FETs were fabricated on hydrophobic SiO<sub>2</sub> substrate and HMDS treatment was applied after device fabrication. Before transferring graphene, the Si-SiO<sub>2</sub> target substrate was cleaned with piranha solution known to have silanol (Si-OH) terminated hydrophilic substrate.<sup>46</sup> In order to achieve a robust hydrophobic substrate, we applied HMDS vapor in an oven at

150°C ensuring proper dehydration prior to HMDS treatment, which results in a hydrophobic surface with methyl termination.<sup>27</sup> BGFETs were fabricated with graphene transferred on this hydrophobic substrate and we applied HMDS with our solution phase process after device fabrication. Figure 3.6 shows the characteristics before and after HMDS application for both forward and reverse sweeps of back-gate voltage. The Dirac point shifted from 9.3V to 1.8V, initially low hysteresis reduced slightly and electron (hole) mobility changed from 1330 (1768) to 1818 (2100) cm<sup>2</sup>/Vs. A total of 6 devices were measured and they all showed changes in electrical characteristics. This was not a high quality sample to begin with. We expect higher values for mobilities in good samples.

Figure 3.6: Resistance, R versus back-gate voltage, V<sub>BG</sub> (both forward and reverse sweeps) plot for a representative device fabricated with graphene transferred on hydrophobic SiO<sub>2</sub> substrate with HMDS treatment prior to graphene transfer. Data for before and after HMDS treatment of top surface of fabricated device are represented by black squares and red circles, respectively.

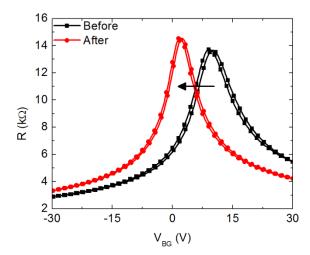

#### 3.7 Raman Spectroscopic Analysis

In addition to electrical measurements, we also performed Raman spectroscopic analysis of graphene transferred on SiO<sub>2</sub>. Raman spectroscopic data were gathered with a Renishaw In-Via Raman Microscope using a 532 nm laser. 121 high resolution data points were gathered for both before and after HMDS application dataset from a nominally identical 10μm × 10μm area of a CVD fabricated device. Figure 3.7(a), 3.7(b) and 3.7(c) shows the position of the G peak, width of the G peak and intensity ratio between the 2D and G peaks (I(2D) / I(G)), respectively, before and after HMDS application. As seen from the data, position of the G peak downshifted (from 1587.33±1.14 cm<sup>-1</sup> to 1586.47±0.44 cm<sup>-1</sup>), width of the G peak increased (from 17.05±2.19 cm<sup>-1</sup> to 22.71±1.25 cm<sup>-1</sup>) and the I(2D)/I(G) increased (from 2.81±0.38 to 3.56±0.21). More pronounced changes in these parameter were observed for an exfoliated flake (for e.g. I(2D)/I(G) increased from 2.02±0.05 to 4.94±0.11 ). Decrease in I(2D)/I(G), decrease in G peak width and up shift of G peak position have been associated with increased doping by impurities. <sup>14,32,47</sup> Therefore, our Raman data suggest that impurities are getting screened or mitigated after HMDS application.

Figure 3.7: Raman Spectroscopic Analysis (a) G peak position, Pos(G) of graphene Raman spectra for 121 scans before (black square) and after (red circle) HMDS treatment. (b) G peak full width half max, FWHM(G) before (black square) and after (red circle) HMDS treatment. (d) Intensity ratio between 2D and G peaks, I(2D) / I(G) before (black square) and after (red circle) HMDS treatment.

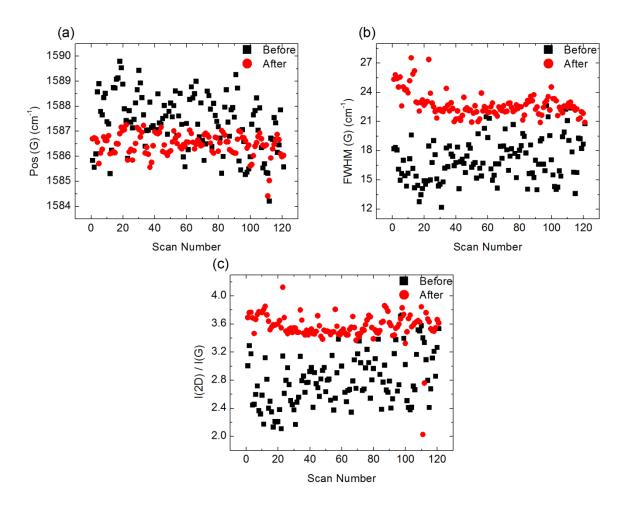

### 3.8 Stability Considerations

One obvious issue with this type of solution process is the stability of the mechanism with time. HMDS treated devices usually returned to their initial state within ~ 3 days when left in ambient, as shown in Figure 3.8(a). HMDS is known to degrade in humid air due to hydrolysis and TMS is a volatile compound.<sup>37</sup> In order to preserve the improvement by HMDS treatment, samples should be protected with suitable capping

layer formed by vapor deposition or atomic layer deposition which does not degrade the HMDS and graphene quality. Unfortunately, graphene is usually degraded with most type of common depositions on it. We have tried several capping scheme with no success. For example, we tried to encapsulate the device with spin coating PMMA after HMDS treatment, as shown in Figure 3.8(b). Unfortunately, the device returned almost to its initial state after PMMA encapsulation. Development of suitable capping process will come with its own set of challenges and will need considerable further research.

Figure 3.8: (a) Evolution of transfer characteristics with time for a sample stored under ambient conditions. (b) Transfer characteristics for PMMA encapsulation.

### 3.9 HMDS treatment of MoS<sub>2</sub> based FET

In addition to improving graphene based FET performance, we wanted to examine if HMDS treatment can be used in general to improve two-dimensional materials based FET characteristics. Like graphene, other two-dimensional materials such as MoS<sub>2</sub>, WSe<sub>2</sub> etc. are also expected to be perturbed by atmospheric impact, if the flakes are very thin. For example, it has been experimentally demonstrated that adsorbed moisture can degrade monolayer MoS<sub>2</sub> based FET performance.<sup>48</sup> To this end, we treated

MoS<sub>2</sub> based BGFET with HMDS and compared the transfer characteristics before and after HMDS treatment. Both monolayer and multilayer MoS<sub>2</sub> flakes were used for device fabrication.

Monolayer  $MoS_2$  was grown by a vapor transport technique using  $MoO_3$  and S powder on 285-300 nm  $SiO_2$  – highly doped Si substrate. Thickness of the grown film was confirmed by Raman spectroscopy and photoluminescence measurement. The details of the growth process and characterization have been reported in another study.<sup>49</sup> In order to find suitable device area in the film and ensure proper alignment for subsequent lithography steps, 1 nm Ti – 49 nm Au metal stack were deposited as alignment marks using e-beam evaporation and lithography. The active area was patterned by etching the superfluous  $MoS_2$  with chlorine plasma (75Watt, 1 minute, 10 sccm chlorine in Plasma-Therm 790 RIE system). The patterned  $MoS_2$  region was contacted with ~30 nm Ni – ~20 nm Au stack. This completed the fabrication of a simple back-gated monolayer  $MoS_2$  based FET. An optical picture of a fabricated FET with 10  $\mu$ m channel length is shown in Figure 3.9. The HMDS treatment procedure is same as stated in section 3.1.

Figure 3.9: Optical image of a fabricated BGFET with monolayer MoS<sub>2</sub> channel.

Figure 3.10: Transfer characteristics (log scale) of fabricated BGFET on monolayer  $MoS_2$  before and after HMDS treatment. Insets show same characteristics in linear scale. (a)  $V_D = 1 \text{ V}$ . (b)  $V_D = 10 \text{ V}$ .

The transfer characteristics of the fabricated BGFET before and after HMDS treatment are shown in Figure 3.10.The on-off ratio increased and threshold voltages shifted towards more negative values after HMDS treatment. However, after adjusting for the threshold voltage shift, the drive current after HMDS treatment is higher than the initial case for same amount of overdrive ( $V_{BG}$ - $V_{TH}$ ). We extracted the field-effect mobility values using the equation:  $\mu = \frac{dI_D}{dV_{BG}} \frac{L}{W^*C^*V_D}$ , where L = channel length, W = channel width, C = gate capacitance (300 nm SiO<sub>2</sub> in this case),  $V_D$  = drain bias,  $I_D$  = drain current,  $V_{BG}$  = back-gate voltage and  $\frac{dI_D}{dV_{BG}}$  is trans-conductance, whose peak value is used for mobility extraction. The field-effect mobility with  $V_D$  = 1 V increased from 3.63 cm²/Vs to 6.83 cm²/Vs after HMDS treatment. For  $V_D$  = 10 V, it increased from 4.6 cm²/Vs to 8.1 cm²/Vs. Several other FETs were fabricated and they all showed similar degree of improvement. Thus, like in the case of graphene, HMDS treatment can also improve monolayer MoS<sub>2</sub> based FET performance.

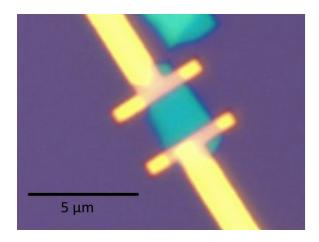

Unlike monolayer system, where current flow is confined in one single layer, multilayer BGFETs can have their current distributed among several layers and based on the flake thickness, one or two layers located in middle of the flake can carry the bulk of the current.<sup>50,51</sup> Therefore, surface treatment methods like HMDS treatment may not be effective for multilayer system as it is for monolayer FETs. To verify this conjecture, multilayer MoS<sub>2</sub> based FETs were fabricated and treated with HMDS. Indeed, there was no improvement in field-effect mobility.

Multilayer  $MoS_2$  flakes were exfoliated from bulk crystal using scotch tape method and transferred onto 300 nm  $SiO_2$  – highly doped Si substrate. Suitable flakes were identified for device fabrication and were contacted with Ag-Au metal to serve as source and drain electrode. An optical image of a fabricated BGFET with multilayer  $MoS_2$  channel is shown in Figure 3.11. The height of the flake was measured with Atomic Force Microscopy (AFM) and it was  $\sim 6$  nm, which constitutes roughly 10 monolayers of  $MoS_2$ .

Figure 3.11: BGFET with multilayer MoS<sub>2</sub> channel.

Figure 3.12: Transfer characteristics (log scale) and corresponding trans-conductance plots of a multilayer  $MoS_2$  based FET before and after HMDS treatment. (a)  $I_D\text{-}V_{BG}$  plot for  $V_D=10$  mV. (b)  $I_D\text{-}V_{BG}$  plot for  $V_D=1$  V. Insets of (a) and (b) show the characteristics in linear scale. (c) Trans-conductance,  $g_m$  plot for  $V_D=10$  mV. (d) Trans-conductance,  $g_m$  plot for  $V_D=1$  V.

The transfer characteristics and corresponding trans-conductance plots before and after HMDS treatment are shown in Figure 3.12. Like the monolayer case, threshold voltage shifted towards more negative value after HMDS treatment. However, from the trans-conductance plot, it is evident that field-effect mobility remained almost exactly the same before and after HMDS treatment. Extracted field-effect mobility for this device is

~55 cm²/Vs. Thus, unlike monolayer case, HMDS treatment was not effective in improving performance of FETs with multilayer channel.

# Chapter 4: Thickness Tuning of Black Phosphorus Flakes by Plasma Treatment

Two-dimensional layered materials have gained a renewed scientific and technological interest in the last decade, thanks to the isolation of graphene from bulk graphite. Graphene has been regarded as a promising material for next generation electronic applications for its numerous fascinating properties such as high carrier mobility and thermal conductivity, high current carrying capacity and ultimate transistor scalability for being an atomically thin material. 11,52,53 However, transistors employing graphene as a channel material exhibit a poor ratio of on state current to the off state current (on-off ratio) due to lack of band gap in graphene. This prohibits the use of graphene based conventional FETs as digital switches. Graphene is more suitable for high frequency analog/RF applications which can be operated with the transistors always on, hence they do not need a channel material with band gap. Nonetheless, it is not possible to attain current saturation in graphene by conventional pinch off mechanism due to the lack of a depletion region (which is, again, a consequence of zero band gap). With the exception of few reports of current saturation via velocity saturation, most graphene based FETs show linear output characteristics. 54,55 The high value of output conductance reduces the intrinsic gain (ratio of trans-conductance and output conductance) and makes it difficult to get power gain out of a graphene FET based amplifier. These challenges have motivated researchers to explore various other twodimensional materials beyond graphene for use in FET applications.

Black phosphorus (BP) has recently emerged as a new member in the twodimensional materials family for electronic applications.<sup>56–58</sup> It is popularly known as Phosphorene. BP is an elemental semiconductor of phosphorus atoms and structurally

Figure 4.1: Crystal structure of few-layer phosphorene. (a) Perspective side view of few-layer phosphorene. (b) Side and (c) Top views of few-layer phosphorene. Adapted with permission from reference<sup>56</sup>. Copyright (2014) American Chemical Society.

similar to graphene, but with a puckered structure. The crystal structure of BP is shown in Figure 4.1. It has decent carrier mobility value up to ~1000 cm<sup>2</sup>/Vs. It has a band gap of 0.3-0.36 eV in the bulk limit which can be tuned up to 1-2 eV for monolayer. It is a direct band gap semiconductor material which makes it useful for both electronic and optoelectronic applications.

Controlling the thickness of exfoliated BP flakes is of utmost technical importance for several reasons. First, the thickness dependent band gap of BP increases with decreasing thickness. Band gap directly affects the device off state current, hence on-off ratio which is an important performance metric for FET applications.<sup>3</sup> In addition, it is very important to maintain good electrostatic control of the channel by gate terminal over drain terminal in scaled MOSFETs in order to overcome several short channel effects (SCE).<sup>59</sup> Therefore, monolayer channel is desirable from the on-off ratio and SCE perspectives. On the contrary, charge carriers are most adversely affected by the surrounding environment in a monolayer. For layered materials, it has been suggested that the effective field-effect mobility in back-gated or embedded-gate FET structures reaches maximum value for a certain flake thickness; usually 5-10 nm.<sup>51,56,57,60,61</sup> The

layers closest to the gate dielectric are the ones which are most affected by the gate field (hence the substrate also). If the flake is too thin, charge carriers are affected by impurities or fixed charges present in the substrate. On the other hand, source and drain metal electrodes directly contact the top most layer only and charge carriers need to overcome finite interlayer resistance in order to be injected to the layers beneath the top most layer. If the flake is too thick, high interlayer resistance can lower the amount of injected carriers and hence current. This is not the case for a top-gated FET where the same top most layer is concurrently in the closest proximity of the gate and contacted by the source and drain electrodes. Even so, proper flake thickness is critical for optimum screening, electrostatics and SCE control.

In this chapter, we report our experimental work on tuning the thickness of few-layer BP by oxygen plasma treatment. Detailed optical and Atomic Force Microscopy (AFM) analyses are presented for the thickness reduction process. Plasma treatment on fabricated BGFETs shows proper device functionality with little or no degradation. Most significantly, we have fabricated well behaved, top-gated FET with good performance on the plasma treated surface of BP for the first time. In addition to the electrical data, we have performed Raman Spectroscopy, Time of Flight Secondary Ion Mass Spectrometry (TOF-SIMS) and X-Ray Photoelectron Spectroscopy (XPS) in order to understand the physical and chemical impacts of the thickness reduction process.

#### **4.1 Experimental Methods**

Few-Layer BP flakes were exfoliated from layered bulk BP crystal using scotch tape method and transferred onto 300 nm SiO<sub>2</sub> – highly doped n type Si substrate.<sup>6</sup> Flake thinning process was carried out in Plasma-Therm 790 RIE system using Oxygen plasma (150 watt RF power, 200 mTorr chamber pressure, 18 sccm flow rate; unless otherwise

stated). For optical and AFM characterization, idle times between etching and microscopy processes at successive etching steps were minimized in order to avoid any environment induced degradation of BP flakes.<sup>62,63</sup> In order to make back-gated FET (BGFET), the SiO<sub>2</sub>-Si substrate was treated with HMDS before transferring the flakes to make the surface hydrophobic, which prevents water accumulation at the interface between the substrate and flake.<sup>64</sup> The substrate was spin coated with PMMA right after transferring the flakes, again to avoid ambient exposure. Suitable flakes in the thickness range of ~ 10-20 nm were identified for device fabrication. The contacts were defined by electron beam lithography. Ni (~ 50-60 nm) or Ni (~30-40 nm) – Au (20 nm) metal stack was deposited as contact metal using electron beam evaporation and liftoff process in acetone. For top-gated device, the gate area was patterned using electron beam lithography. Aluminum Oxide (~30 nm) – Ni (~40 nm) gate stack was deposited in a single electron beam evaporation process. The experimental details of the Raman, XPS and TOF-SIMS analyses will be discussed along with the data.

### 4.2 Optical and AFM Characterizations of Flake Thinning Process

Figure 4.2 shows the optical images of two adjacent flakes at different stages of the flake thinning process. A total of 9 successive etch runs were performed, each with a duration of 1 or 2 minutes. As can be seen from the images, the flakes are getting thinner uniformly, maintaining the relative thickness differences between different portions of the flake. This is more evident from the relatively non uniform bottom flake. The thinner portions of the flakes are faintly visible after the 8<sup>th</sup> etch and become optically invisible after the 9<sup>th</sup> etch.

Figure 4.2: Temporal sequence of flake thinning process. Caption on each optical image include etch number, plasma power and duration. Scale bar is  $5~\mu m$ .

Figure 4.3: AFM images of the BP flakes shown in Figure. 4.2. before and after plasma treatment. (Left: as exfoliated, right: after first etch) (a) Top view of the top flake in Figure 4.2. (b) 3D view of the flakes.

AFM images before and after plasma treatment of the flakes shown in Figure 4.2 are presented in Figure 4.3. It is evident from the initial AFM image that as-exfoliated BP flakes may have rough surfaces with protrusions which are not visible in the optical images. Similar findings have been reported in other studies.  $^{62,63}$  It has been suggested that ambient species such as  $H_2O$  and  $O_2$  can react and degrade BP by forming phosphorus oxides or oxoacids. For example, BP can react with ambient  $O_2$  to produce  $P_4O_{10}$  (also written as  $P_2O_5$ ), which, in turn, can readily react with ambient moisture to produce phosphoric acid due to hydrophilic nature of  $P_4O_{10}$ .

$$P_4 + 5O_2 \qquad \rightarrow \qquad P_4O_{10} \tag{4.1}$$

$$P_4O_{10} + 6H_2O \rightarrow 4H_3PO_4$$

(4.2)

As shown in Figure 4.3, O<sub>2</sub> plasma etching can remove the chemical degradation from the surface of the BP flakes, resulting in a smooth surface. The RMS surface roughness decreased from 3 nm for as-exfoliated case to 0.3 nm after the first etching. Therefore, in addition to thickness reduction, this O<sub>2</sub> plasma treatment can clean the surface of BP flake by removing the ambient degradations as well as the process induced organic residues during device fabrication. It should be mentioned that the cleaning effect is also observed for lower power, shorter duration etch (e.g. 75W, 30s) and not all as-exfoliated flakes have such high roughness.

Detailed AFM analysis of the top flake of Figure 4.2 is shown in Figure 4.4. The line scans after some of the etch steps are shown in Figure 4.4(a). The scan of the asexfoliated flake has numerous spikes which are removed by the initial etch. The flake has a smooth surface at an intermediate stage of  $4^{th}$  etch. After the  $8^{th}$  etch, flake thickness was reduced below 5 nm, however, surface roughness became significant. The temporal evolutions of flake height and surface roughness with each consecutive etch are shown in Figure 4.4(b) and 4.4(c), respectively. The height decreases in a monotonic manner with each etch step. The data point at t=15 minutes corresponds to the  $9^{th}$  etch where the flake became optically invisible. However, AFM scan shows presence of  $\sim 0.8$  nm flake with significant roughness and discontinuity. After the initial decrease for as-exfoliated flake, surface roughness increased steadily with each etching step, but the value remained below 0.75 nm till  $11^{th}$  minute ( $7^{th}$  etch). As mentioned before, it increased to  $\sim 1.5$  nm after the  $8^{th}$  etch. Careful calibration and lower plasma power with shorter duration of etch step should be employed for thickness scaling below 5 nm. For example, using 75W plasma power instead of 150W resulted in reduction of etch rate roughly by 50%.

Figure 4.4: AFM analysis for flake thinning process. (a) Line scan across the flake. Time in parenthesis is cumulative time of current and all previous etch steps. (b) Temporal evolution of flake height. (c) Temporal evolution of flake roughness. The straight lines serve as visual guides only.

Since the BP etching was carried out with  $O_2$  plasma in a RIE system, there can be both physical and chemical etching processes by  $O_2^+$  ions and O radicals, respectively. O radicals can readily react with phosphorus to form oxidized species.  $P_2O_5$  formation is likely due to abundance of oxygen and  $P_2O_5$  sublimes at relatively low temperature of  $\sim 360^{-0}$ C at atmospheric pressure. Therefore, the oxide layer is expected to have a