Copyright

by

Yilin Zhang

2014

# The Dissertation Committee for Yilin Zhang certifies that this is the approved version of the following dissertation:

## Interconnect Optimizations for Nanometer VLSI Design

| Committee:               |

|--------------------------|

|                          |

| David Z. Pan, Supervisor |

| Andreas Gerstlauer       |

| Andreas Gerstlauer       |

| Nur A. Touba             |

| Michael Orshansky        |

| Salim Chowdhury          |

### Interconnect Optimizations for Nanometer VLSI Design

by

Yilin Zhang, B.S.; M.S.E.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm August~2014}$

This dissertation is lovingly dedicated to my my mother Yanjun Huang and my father Shijin Zhang who constantly provide all their love and all they own to me in every single day of my life. It is also dedicated to friends who earnestly help me on my paper writing and problem solving during my PhD.

## Acknowledgments

I want to thank my adviser, Prof. David Z. Pan, first, for his guidance, understanding and support during my Ph.D. studies at the University of Texas at Austin. He could always find a clear path for me when I was confused or trapped in certain problem. It was him that made me understand that staying with big picture was way more important than optimizing some sub-problems. Also, he had great understanding about my situations and feelings outside research/study. He provided me long enough time to spend with my families when my families and me preferred that. He also very kindly asked about my families when he knew that my father was not in a good health condition. Retrospectively, I was so lucky to meet Prof. Pan during his visit in my college, Peking University, when I was considering to apply for PhD. It was a correct decision to join UTDA and finished my PhD under the supervision of Prof. Pan.

I would like to thank the current and former UTDA members for all great days we spent together no matter for research discussions or ball sporting together. They are Ashutosh Chakraborty, Kun Yuan, Anurag Kumar, Ou He, Katrina Lu, Jae-Seok Yang, Xiaoqing Xu, Shuojing Wang, Jerrica Gao, Yibo Lin, Duo Ding, Jiwoo Pak, Bei Yu, Subhendu Roy, Yongchan (James) Ban, Wooyoung Jang, Samuel Ward, Wen Zhang, Yang Li, Boyang Zhang, Yen-

Hung Lin, Joydeep Mitra, Jiaojiao Ou, Abhishek Bhaduri and Che-Lun Hsu. From their self-giving help, I learned lots of helpful skills, such as how to properly arrange everything to boost overall efficiency, how to devote yourself on one project for days and nights, etc. Also, the time we played tennis, Pingpong or basketball together really make us good friends and I would miss every moment we spent together.

I am also deeply thankful to Salim Chowdhury and Zhuo Li who were my mentors during my interns at Oracle and IBM, respectively. Basically I started my PhD project during the cooperation between UTDA and Oracle. Dr. Chowdhury always had a lot of creative ideas so we can work on together. We keep exchange our ideas during my whole PhD and honorably he accepted my invitation to be one of my committee members. I would also like to thank other co-workers during my intern at Oracle: Rajendran Panda, Akshay Sharma, Duo Ding, Kevin Grant, Yong Li, Boyang Zhang, Zhen Liu, et al. Dr. Li was my mentor when I spent six months doing intern at IBM. His amazing working efficiency and problem solving ability was one of great lessons I learned at IBM. I deeply thank him for many interesting projects he provided me. I would deeply thank to my colleagues in IBM. They are Yuhan Zhou, Chuck Alpert, Tiago Reimann, Ying (Nancy) Zhou, Yaoguang Zhou, Cliff Sze, Gi-Joon Nam, Natarajan Viswanathan, Myung-Chul Kim, et al.

My sincere thanks also go to my three other Ph.D. committee members, Prof. Nur A. Touba, Prof. Michael Orshansky and Prof. Andreas Gerstlauer. Thank you for bring out various questions during my Ph.D. proposal exam which inspired me to explore more interesting problems that I could not find by myself.

Last but not least, I would like to thank my parents. They always give me maximum understanding when I studied PhD in another country and could not well perform my responsibility as a son to take care of them when they are growing old. I love you.

Interconnect Optimizations for Nanometer VLSI Design

Publication No.

Yilin Zhang, Ph.D.

The University of Texas at Austin, 2014

Supervisor: David Z. Pan

As the semiconductor technology scales into deeper sub-micron do-

main, billions of transistors can be used on a single system-on-chip (SOC)

makes interconnection optimization more important roughly for two reasons.

First, congestion, power, timing in routing and buffering requirements make

interconnection optimization more and more challenging. Second, gate delay

getting shorter while the RC delay gets longer due to scaling.

Study of interconnection construction and optimization algorithms in

real industry flows and designs ends up with interesting findings. One used to

be overlooked but very important and practical problem is how to utilize over-

the-block routing resources intelligently. Routing over large IP blocks needs

special attention as there is almost no way to insert buffers inside hard IP

blocks, which can lead to unsolvable slew/timing violations. In current design

flows we have seen, the routing resources over the IP blocks were either dealt

as routing blockages leading to a significant waste, or simply treated in the

viii

same way as outside-the-block routing resources, which would violate the slew constraints and thus fail buffering.

To handle that, this work proposes a novel buffering-aware over-the-block rectilinear Steiner minimum tree (BOB-RSMT) algorithm which helps reclaim the "wasted" over-the-block routing resources while meeting user-specified slew constraints. Proposed algorithm incrementally and efficiently migrates initial tree structures with buffering-awareness to meet slew constraints while minimizing wire-length.

Moreover, due to the fact that timing optimization is important for the VLSI design, in this work, timing-driven over-the-block rectilinear Steiner tree (TOB-RST) is also studied to optimize critical paths. This proposed TOB-RST algorithm can be used in routing or post-routing stage to provide high-quality topologies to help close timing.

Then a follow-up problem emerges: how to accomplish the whole routing with over-the-block routing resources used properly. Utilizing over-the-block routing resources could dramatically improve the routing solution, yet require special attention, since the slew, affected by different RC on different metal layers, must be constrained by buffering and is easily violated. Moreover, even of all nets are slew-legalized, the routing solution could still suffer from heavy congestion problem. A new global router, BOB-Router, is to developed solve the over-the-block global routing problem through minimizing overflows, wire-length and via count simultaneously without violating slew constraints. Based on my completed works, BOB-RSMT and BOB-Router tremendously

improve the overall routing and buffering quality.

Experimental results show that proposed over-the-block rectilinear Steiner tree construction and routing completely satisfies the slew constraints and significantly outperforms the obstacle-avoiding rectilinear Steiner tree construction and routing in terms of wire-length, via count and overflows.

## **Table of Contents**

| Ackno   | wledg  | ments                                                                                | v        |

|---------|--------|--------------------------------------------------------------------------------------|----------|

| Abstra  | act    |                                                                                      | vii      |

| List of | Table  | es                                                                                   | xiii     |

| List of | Figu   | res                                                                                  | xiv      |

| Chapt   | er 1.  | Introduction                                                                         | 1        |

| 1.1     | Chall  | enges in Interconnection Optimization                                                | 1        |

| 1.2     | How    | Interconnection Optimization Works                                                   | 4        |

| 1.3     | Critic | eal Problems in Interconnection Optimization                                         | 9        |

| 1.4     | Contr  | ributions                                                                            | 13       |

| 1.5     | Organ  | nization of the Dissertation                                                         | 14       |

| Chapt   | er 2.  | Buffering-Aware RSMT Construction for Reclaiming Over-the-IP-Block Routing Resources | ı-<br>16 |

| 2.1     | Intro  | duction                                                                              | 16       |

| 2.2     | Probl  | em Formulation                                                                       | 20       |

|         | 2.2.1  | What is BOB-RSMT?                                                                    | 20       |

|         | 2.2.2  | Basic Ideas and Optimization Primitives                                              | 21       |

| 2.3     | BOB-   | RSMT Algorithms                                                                      | 27       |

|         | 2.3.1  | Generating Possible Point Set                                                        | 28       |

|         | 2.3.2  | Refinement of Possible Region Set                                                    | 30       |

|         | 2.3.3  | Primitive Choice Based on a Fast ILP                                                 | 31       |

|         | 2.3.4  | Block-aware Maze Routing Algorithm                                                   | 34       |

|         | 2.3.5  | Min-cost Slew Mode Buffer Insertion                                                  | 36       |

| 2.4     | Expe   | rimental Results                                                                     | 37       |

| 2.5     |        | narv                                                                                 | 40       |

| Chapt      | er 3.  | Timing-Driven, Over-the-Block RST Construction                                      | 44  |

|------------|--------|-------------------------------------------------------------------------------------|-----|

| 3.1        | Intro  | duction                                                                             | 44  |

| 3.2        | Notat  | tions and Problem Formulation                                                       | 49  |

| 3.3        | Timir  | ng-driven Over-the-block RST                                                        | 52  |

|            | 3.3.1  | Initial Tree Generation with Pre-Buffering                                          | 53  |

|            | 3.3.2  | Buffering-Aware Over-the-Block Routing                                              | 57  |

|            | 3.3.3  | Timing-driven Buffer-location-based Tuning                                          | 60  |

|            |        | 3.3.3.1 Slew Margin                                                                 | 60  |

|            |        | 3.3.3.2 Buffer-location-based Tuning                                                | 62  |

|            |        | 3.3.3.3 Algorithms                                                                  | 66  |

| 3.4        | Exper  | rimental Results                                                                    | 66  |

|            | 3.4.1  | Effectiveness of Pre-Buffering                                                      | 68  |

|            | 3.4.2  | Over-the-Block RST                                                                  | 69  |

|            | 3.4.3  | Post-buffering Topology Tuning                                                      | 69  |

| 3.5        | Sumn   | nary                                                                                | 71  |

| Chapter 4. |        | Buffering-Aware Global Router with Over-the-Block<br>Routing Resources Optimization |     |

| 4.1        | Intro  | duction                                                                             | 72  |

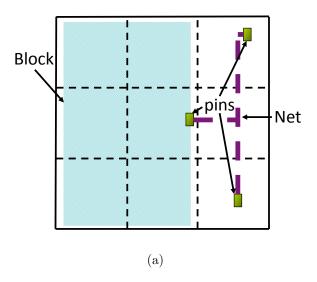

| 4.2        |        | minaries                                                                            | 75  |

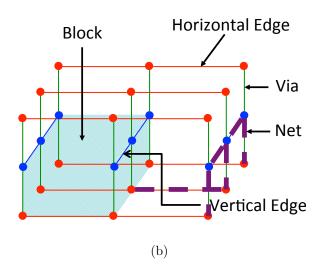

|            | 4.2.1  | Basic Over-the-block Concepts                                                       | 75  |

|            | 4.2.2  | Problem Formulation                                                                 | 77  |

| 4.3        | BOB-   | -Router Algorithms                                                                  | 77  |

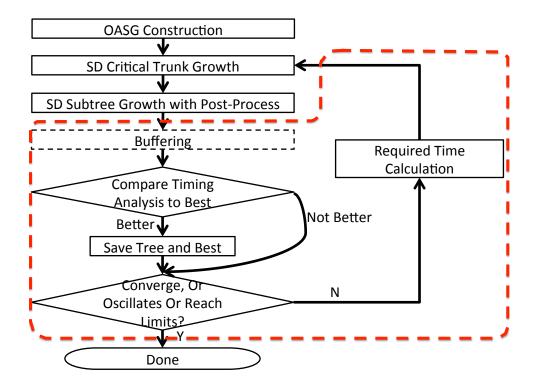

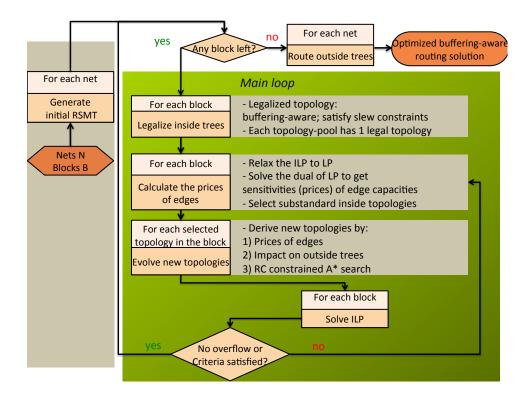

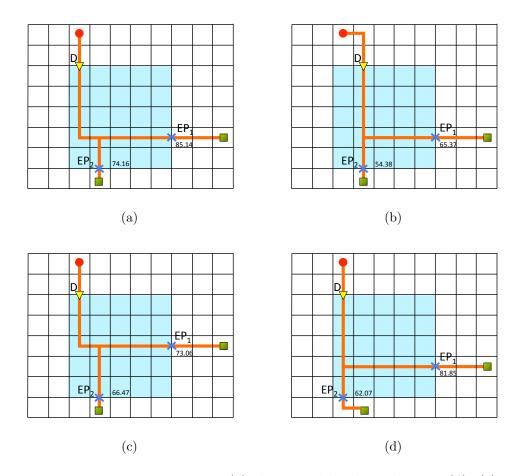

|            | 4.3.1  | Generate Legal Initial Topologies                                                   | 79  |

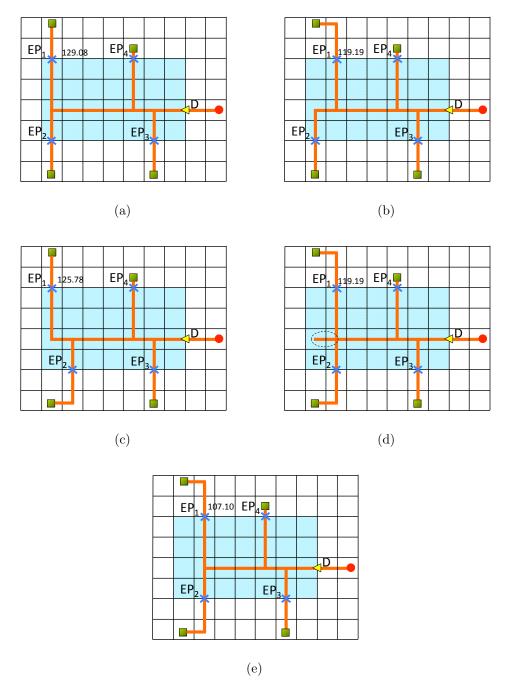

|            | 4.3.2  | Evolve More Legal Congestion-Aware Min-Cost Topologies                              | 81  |

|            | 4.3.3  | Outside-tree Routing                                                                | 93  |

| 4.4        |        | rimental Results                                                                    | 93  |

|            |        | nary                                                                                | 99  |

| Chapt      | er 5.  | Conclusion                                                                          | 100 |

| Bibliog    | graphy | y                                                                                   | 104 |

| Vita       |        |                                                                                     | 112 |

## List of Tables

| 2.1 | Notation of variables                                     | 24 |

|-----|-----------------------------------------------------------|----|

| 2.2 | Notation of variables in our formulation                  | 33 |

| 2.3 | CPU runtime                                               | 41 |

| 2.4 | Extra buffering cost comparison                           | 42 |

| 2.5 | Comparisons between our proposed BOB-RSMT and OA-RSMT     | 43 |

|     | Notation of variables in our formulation                  |    |

| 4.1 | Slew distribution of inside trees                         | 93 |

| 4.2 | Comparisons between our proposed BOB-Router and OA-Router | 94 |

## List of Figures

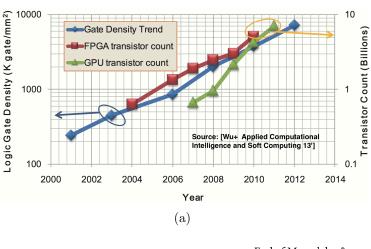

| 1.1 | (a) Transistor count and gate density continues to increase. [49] (b) Moores Law history, future, limited factors, and Nanotechnology-enhance factors for Moores Law and compared with Dow Jones industrial average in the same period of time (1971—20 [50] | 012).<br>2 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

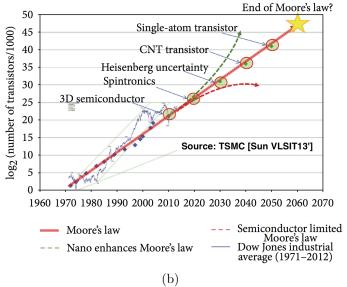

| 1.2 | A simplified VLSI design and physical design flow                                                                                                                                                                                                            | 3          |

| 1.3 | Interconnect RC delay v.s. gate delay                                                                                                                                                                                                                        | 4          |

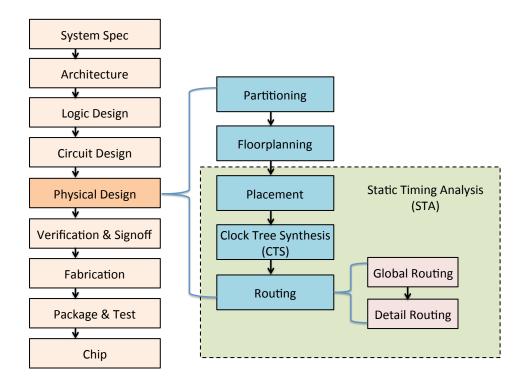

| 1.4 | RSMT on hanan grid with black dots as pins                                                                                                                                                                                                                   | 6          |

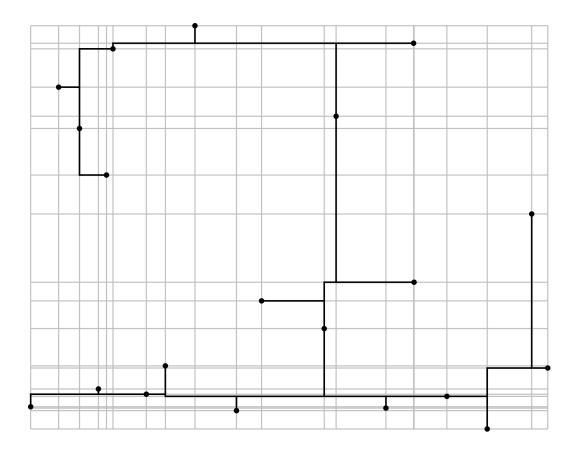

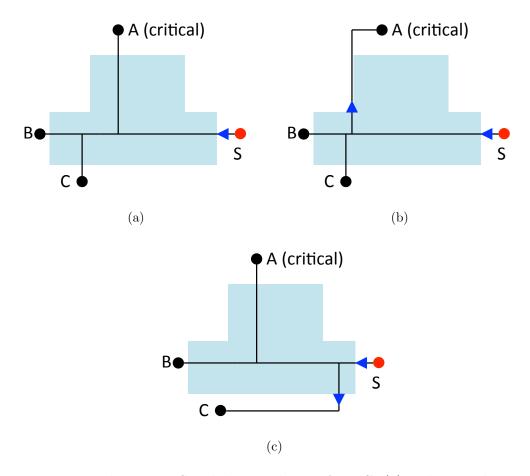

| 1.5 | (a) RSMT topology. (b) Rectilinear Steiner tree with better source-to-critical-sink delay but worse wire-length. (c) Topology with the best source-to-critical-sink delay but worst wire-                                                                    | <b>-</b>   |

| 1.0 | length                                                                                                                                                                                                                                                       | 7          |

| 1.6 | One example of OA-RSMT [37]                                                                                                                                                                                                                                  | 9          |

| 2.1 | A motivational example compares [28] and our proposed BOB-RSMT, which saves wire-length and buffers                                                                                                                                                          | 18         |

| 2.2 | V moves to right in (b) compared to (a). This parallel sliding is providing slew improvement for escaping points $U$ and $V$ .                                                                                                                               | 22         |

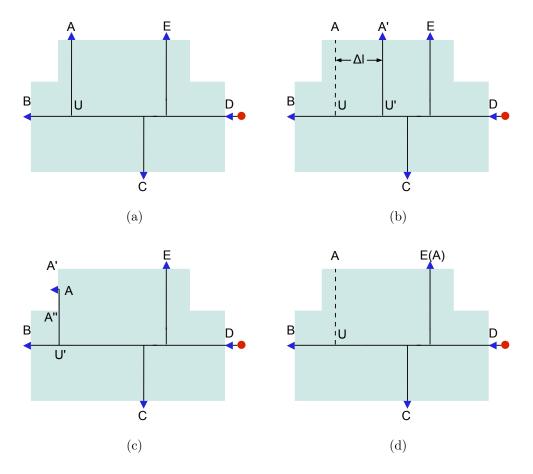

| 2.3 | An example shows slew reduction from three primitives. (b) shows escaping point $A$ slides to $A'$ parallelly to improve slew on $A$ and $B$ . (c) shows the vertical sliding of $A$ from $A'$ to $A''$ . (d) shows EP merging of escaping point $A$ to $E$  | 25         |

| 2.4 | (a) is an inside tree with driver at $D$ . It shows all possible points for $E$ . (b) exhibits the refined possible point set for $E$                                                                                                                        | 29         |

| 2.5 | Restricted length, over-the-block maze routing find a shortest path to reconnect pin A                                                                                                                                                                       | 35         |

| 3.1 | (a) estimates only sink $E$ is critical. (b) groups sink $E$ and $D$ as critical cluster                                                                                                                                                                     | 46         |

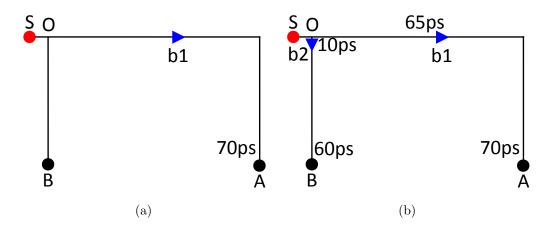

| 3.2 | (a) is an OA-RSMT with root $S$ and two sinks $A, B$ . (b) uses part of the over-the-block routing resources                                                                                                                                                 | 47         |

| 3.3 | (a) is a buffered RST with root $S$ and two sinks $A, B$ . (b) exhibits the tuned topology and new buffering                                                                                                                                                 | 48         |

| 3.4 | Flow of initial tree generation                                                                                                                                                                                                                                       | 54 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5 | (a) is the initial critical trunk based tree with root S and sinks A,B,C,D. (b) reconstructs the tree according to the pre-buffering and timing information from (a). The tree topology converges in (c)                                                              | 55 |

| 3.6 | The root is $S$ and three sinks are $A, B, C$ . (a) is the initial timing-driven RST with slew violations. (b) fixes the slew violations with minimum wire-length penalty. (c) fixes the slew violations and considers the delay on critical path                     | 61 |

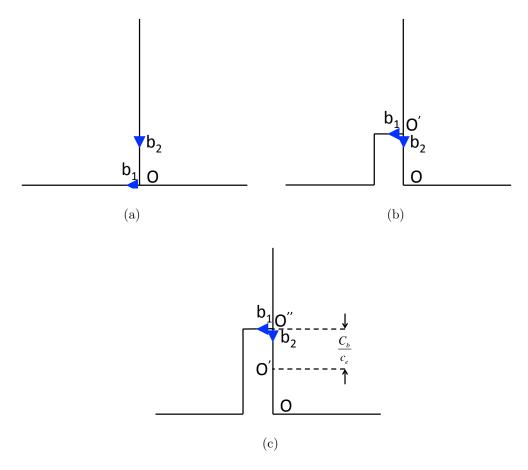

| 3.7 | (a) bottom-up buffer solutions before merge at Steiner node $O$ . (b) slew margin after propagation through Steiner node $O$ .                                                                                                                                        | 62 |

| 3.8 | (a) depicts the pattern of slew margin. (b) shows buffer-location-based tuning if the input capacitance of buffers is negligible. (c) illustrates buffer-location-based tuning without neglecting the input capacitance of buffers                                    | 64 |

| 4.1 | 3D grid-graph $G$ of three metal layers with each one divided into $3*3$ global routing bins                                                                                                                                                                          | 76 |

| 4.2 | Overall flow of BOB-Router                                                                                                                                                                                                                                            | 78 |

| 4.3 | Best move selection (a) shows an illegal inside tree. (b), (c) and (d) exhibit and evaluate the best single-unit move from the driver, $EP_1$ and $EP_2$ respectively.                                                                                                | 80 |

| 4.4 | Slew calculation method in BOB-RSMT and BOB-RSMT-m. (a) shows an illegal inside tree. (b), (c) and (d) exhibit and evaluate the best single-unit move from the driver, $EP_1$ and $EP_2$ respectively                                                                 | 82 |

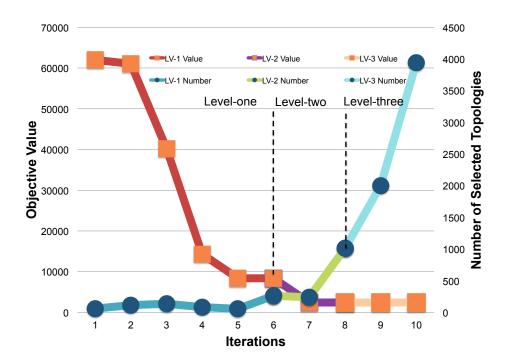

| 4.5 | Progression of objective value and number of selected "to-be-<br>evolved" topologies over optimization rounds for one block on<br>ADAPTEC1                                                                                                                            | 89 |

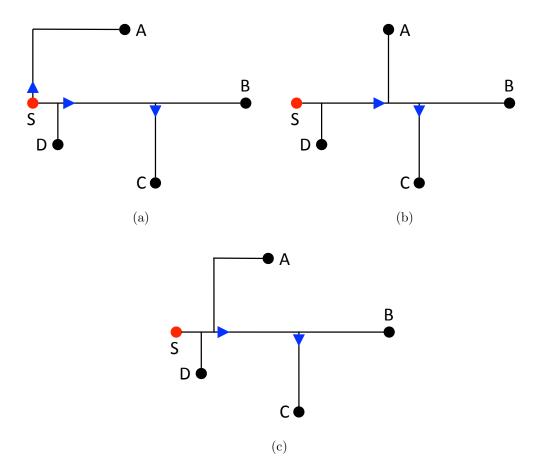

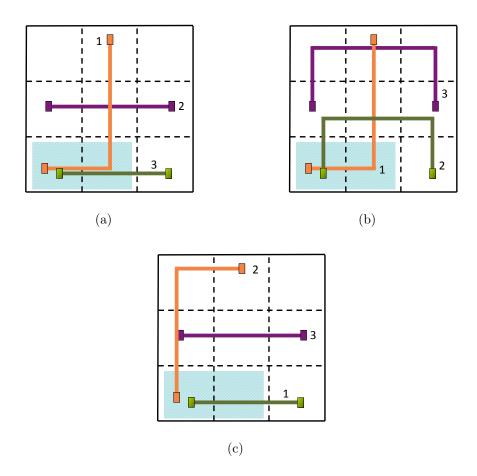

| 4.6 | Impact of net ordering: (a) has overflows in shade area by sequencing orange, purple, green net. (b) has a different ordering of orange, green, purple but with detour of green and purple nets. (c) has the no overflow and detour by ordering green, orange, purple | 92 |

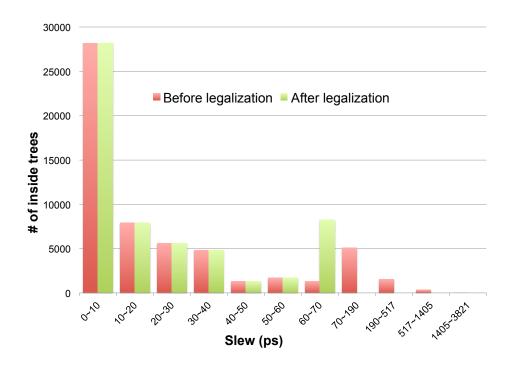

| 4.7 | Slew distribution of all inside trees in adpatec1 initially and finally. Each y coordinates number of inside trees with slew in the slot between current and previous x                                                                                               | 96 |

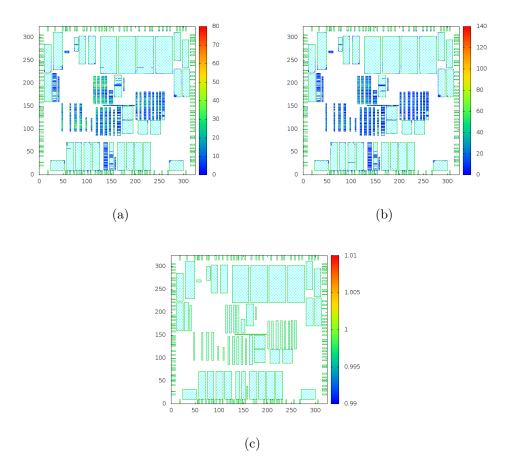

| 4.8 | Over-the-block overflow analysis of a) before EP-movement-based legalization, b) after EP-movement-based legalization but before evolving new topologies c) after evolving new topologies and selecting new topology for each inside tree                             | 97 |

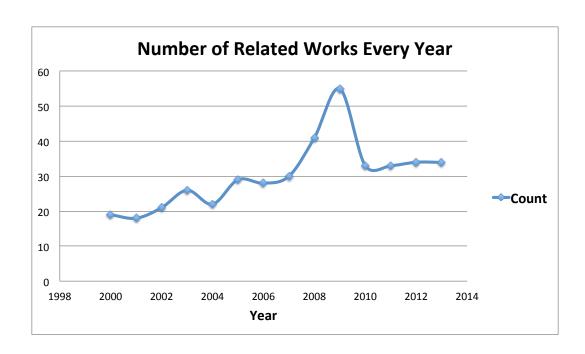

| 5.1 | Number of routing related works which contains "VLSI routing" |     |

|-----|---------------------------------------------------------------|-----|

|     | or "global routing" in title                                  | 101 |

## Chapter 1

#### Introduction

#### 1.1 Challenges in Interconnection Optimization

Due to technology scaling, the number of transistors on a single systemon-chip (SOC) is expanding dramatically. According to ITRS [3], the combination of 3D device architecture and low power device will usher the (Third)

Era of Scaling. New device, such as spin wave device (SWD) is able to convert

input voltage signals into the spin waves, compute with spin waves and convert

the output spin waves into the voltage signals. Materials, such as III-V and

Ge can further improve device performance with higher mobility. Stacking

multiple layers of transistors continually compacts more transistors per unit

chip area. In brief, by these novel inventions, semiconductor technology will

keep in scaling continually which puts more gates in a chip and increases cell

density (Fig. 1.1). Thus, the emerging challenge is: modern VLSI designs

with hundred billions of gates will turn out to be extremely complicated to

design, which in turn places more demands on computer aided design (CAD),

especially physical design.

Physical design is the stage which turns RTL code into GDSII before fabrication. Physical design consists of partitioning, floorplanning, placement,

Figure 1.1: (a) Transistor count and gate density continues to increase. [49] (b) Moores Law history, future, limited factors, and Nano-technology-enhance factors for Moores Law and compared with Dow Jones industrial average in the same period of time (1971—2012). [50]

CTS, routing, etc (Fig. 1.2). This dissertation will focus on interconnection optimization which includes routing, in particular global routing, buffering,

Figure 1.2: A simplified VLSI design and physical design flow.

tree construction, together with static timing analysis (STA). Interconnection optimization plays an important role in the physical design flow. It will automatically generate and optimize topologies for all nets in modern VLSI design with both performance and power considerations. With technology scaling, interconnection optimization is becoming more challenging for two reasons:

1. The portion of RC interconnection delay in the overall delay is dramatically growing due to increasing RC interconnection delay and decreasing

Figure 1.3: Interconnect RC delay v.s. gate delay.

gate delay as CMOS scaling (Fig. 1.3 [54]).

2. Interconnection optimization becomes more challenging as increasing total wire-length and cell density amplifying the congestion and routability problem.

#### 1.2 How Interconnection Optimization Works

After placement is done, all functional blocks and gates are fixed with location but not wiring between logic gates. As above mentioned, the process of planning all wires is interconnection optimization which becomes more and more challenging and crucial nowadays.

Routing, particularly global routing, is the main part of the intercon-

nection planning process. As shown in Fig. 1.2, routing consists of two parts: global routing followed by detail routing. This division separates this extremely complex problem into two relatively easier sub-problems. Global routing is performed on a coarse-grain grid, which depicts the rough shape of each net. With coarse-grain grid, it provides smaller solution space, which stands for relatively less runtime for this NP-complete problem [33]. On the other hand, detail routing is based on the global routing solution with a fine-grain grid. Detail routing solves legalization issues with exact routes. Because detail routing is to find the exact routes based on global routing, the quality of final routes is primarily depend on the global routing solution. Therefore, a powerful global routing needs to find route for each net with wire-length, routability and timing co-optimization.

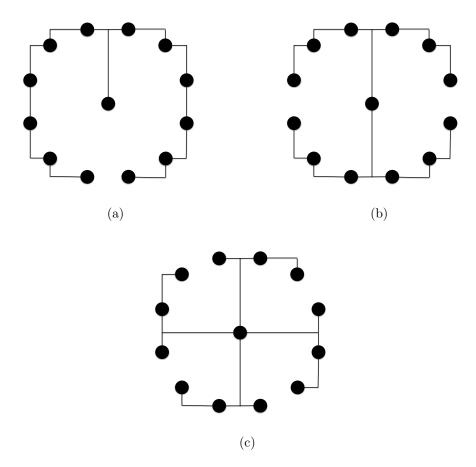

Other components in interconnection optimization is actually surrounding routing process. Rectilinear Steiner minimum tree (RSMT) construction is one fundamental physical design problem to achieve routing and buffering quality. RSMT is to connect all pins in a net in horizontal or vertical way. Fig. 1.4 is one example of RSMT connecting twenty pins. During routing, every net among all hundred billions nets requires RSMT construction or incremental RSMT re-construction. This classical problem has long been proved as NP-complete [41] and many works have been performed including recent breakthrough, e.g. the well-known FLUTE [18].

Because RSMT is only targeting at minimize total wire-length, which is not enough for high performance VLSI design. Timing driven RSMT (TD-

Figure 1.4: RSMT on hanan grid with black dots as pins.

RSMT), instead, forges better trade-off on timing and wire-length. With scaling, interconnection delay has become the dominant factor in determining circuit speed, contributing up to  $50\% \sim 70\%$  of the clock cycle in high performance circuit [19]. Since STA is performed during placement and routing stages, it is common that critical paths information is available during current RST construction process. With these criticality information, TD-RSMT will trade wire-length for shorter delay on critical paths. In Fig. 1.5, it shows

Figure 1.5: (a) RSMT topology. (b) Rectilinear Steiner tree with better source-to-critical-sink delay but worse wire-length. (c) Topology with the best source-to-critical-sink delay but worst wire-length.

the trade-off of wire-length and delay to sinks (assume all sinks are critical). RSMT will construct the net as Fig. 1.5(a) which consumes the least wire-length, yet delay to certain sinks is very long. On the other hand, if sacrificing some wire-length, a new topology as in Fig. 1.5(b) is generated with better source-to-critical-sink delay but more wire-length. To be extremely on delay

optimization, topology in Fig. 1.5(c) is the worst at wire-length but the best at timing optimization.

After RSMT construction, buffering will be performed over each tree to linearize the interconnection delay on long interconnections and shield branch-capacitance. Buffers can re-strengthen signals as well as reduce delays. Due to dominance of interconnection delay, the critical length, i.e. minimum distance beyond which inserting an optimal-sized buffer makes the interconnect delay smaller, is decreasing, which requires more and more buffers inserted in a chip. It is reported that in 32–nm technology, it reaches an alarming point that 70% of cells are buffers [48]. Besides, it is reported that in reality, slew mode buffering is more predominant than timing mode buffering [28, 44]. Only a fraction (roughly  $5\% \sim 10\%$ ) of nets needs to be buffered for delay optimization while for the remaining (roughly  $90\% \sim 95\%$ ) are sufficient with slew mode buffering algorithm is crucial during interconnection optimization.

In slew mode buffering, slew needs to be calculated over and over. Moreover, slew calculation is repeatedly performed in STA, clock tree synthesis, routing and sizing locally or globally. Because of these reason, this dissertation adopts a simple but effective slew calculation model, i.e. PERI [34] model, for slew calculation. It shows the error of PERI is within 1% [34], which is indistinguishable from what is obtained using SPICE simulation.

Figure 1.6: One example of OA-RSMT [37].

## 1.3 Critical Problems in Interconnection Optimization

Because of extensively using IP-blocks to shorten turn around time, SOC designs nowadays are packed with IP blocks or macros. Since it is forbidden to insert any buffer on those pre-designed IP blocks or macros, traditional RSMT algorithm will result in impractical topology which is unfeasible for buffering. Although there are studies of the so-called buffer planning [22] or suggestions to even put unconnected buffers inside IP blocks [7], in practice, most IP blocks still do not have pre-placed "idle" buffers. RSMT construction avoiding these blockages is the most simple and straight way to handle that. It is studied and well known as the OA-RSMT problem. OA-RSMT problem has been studied actively in the last few years (e.g., [6, 30, 35, 36]). Early approaches [35, 36] only deal with rectangular blockages, while a most recent study [30] can tackle rectilinear blockages without dissecting rectilinear blockages into rectangular ones. This approach can eliminate the unfeasible solutions which put wires and buffers between adjoining blocks. However, all these OA-RSMT algorithms simply treat IP blocks as routing blockages, which would significantly waste routing resources over these IP blocks and cause more congestion issues. Fig. 1.6 illustrates an example of OR-RSMT.

Indeed, most IP blocks such as SRAMs only use certain lower metal layers. There are still considerable amount of routing resources available at higher metal layers over these IP blocks, even if we take into consideration the resources reserved for power/ground and clock routing. If we simply treat the IP blocks as routing obstacles, these over-the-block routing resources will be "wasted", which leads to more routing demand elsewhere.

In order to use "wasted" routing resources while still enable feasible buffering, this dissertation studies a new class of buffering-aware over-theblock rectilinear Steiner minimum tree (BOB-RSMT) problem. This dissertation develops an effective algorithm which tries to intelligently reclaim the "wasted", over-the-IP-block routing resources by previous approaches while ensuring slew constraints for high quality buffering. Proposed algorithm incrementally updates the initial RSMT structure obtained from FLUTE [18] to satisfy slew constraints while minimizing wire-length (FLUTE is chosen to be the initial RSMT generator because its low runtime and high quality). A restricted length, over-the-block maze routing algorithm is developed to reconnect any part of BOB-RSMT which is dissected during the optimization process.

RSMT and related extensions produce good results regarding wire-length minimization, which contributes to routability and power optimization. However, there are certain amount of nets which are critical nets. These critical nets are eager for timing optimization other than power and wire-length. Since straight paths will give less delay compared with detoured paths, it is necessary to place timing critical nets over-the-block than avoiding-the-block. Furthermore, using over-the-block routing resources could unburden the outside-the-block congestion which in turn decreases power and delay. This dissertation proposes a timing-Driven, over-the-block rectilinear Steiner tree (TOB-RST) construction algorithm with pre-buffering and slew constraints in consideration. TOB-RST intelligently utilizes over-the-block routing resources, and the resulted tree is buffering-feasible and slew-violation-free.

With the algorithm of building over-the-block RSMT, the whole global

routing problem considering over-the-block routing resources is the next emergent problem to solve. The CEDA-sponsored ISPD Global Routing Contests [4] and [5] attract attention from dozens of academic and industrial participants. Inspired by the competitions, many high-performance global routers are published.

However, due to guidance from two ISPD Global Routing Contests are similar, most published modern routers are aiming at the same problem: minimizing wire-length and via count in addition to alleviating congestion. However, the global routing problem has never been touched upon to not only consider wire-length, vias and overflows, but also properly use over-the-block routing resources. Studying this new problem is essential as to shorten the design cycle and improve the chip quality. If over-the-block routing resources are treated the same as that for out-the-block, long nets over the block will fail buffering, leading to additional manual work; whereas over-the-block routing resources are totally avoided, less remaining routing resources will significantly deteriorate the quality of the routing solution.

This dissertation studies a new class of buffering-aware over-the-block global router (BOB-ROUTER) which tries to intelligently reclaim the "wasted" over-the-IP-block routing resources while minimizing overflows, wire-length and via count as in "basic" routers. The generated topologies are aware of slew constraints which guarantees feasible buffering.

#### 1.4 Contributions

This dissertation has the following major contributions:

- This is the first work that proposes a practical formulation of buffering-aware over-the-block RSMT. Quality of the Steiner tree and feasible buffering are ensured as considering slew constraints with wire-length simultaneously. Our algorithm is able to integrate with a buffering tool to generate a low buffering cost BOB-RSMT without violating maximum slew constraint, which can be used in floorplanning, placement and routing stages. An incremental approach of fixing slew violation one by one is used to satisfy slew constraints on over-the-block part of BOB-RSMT, followed by a restricted length, over-the-block maze routing algorithm which reconnects any dissected part of BOB-RSMT during the optimization process.

- It is first time a comprehensive timing-driven RST is studied which includes: (1) pre-buffering algorithm pre-characterizes the tree topology and buffer distribution to provide accurate timing information for final TD-RST construction, (2) proposed TOB-RSMT reclaims the wasted over-the-block routing resources while meeting user-specified timing (slack and slew) constraints, and (3) before fixing topology, a topology-tuning is performed based on location of buffers to improve timing without increasing buffering cost.

• For the first time, a router tries to solve the over-the-block global routing problem through minimizing overflows, wire-length and via count simultaneously without violating slew constraints. First, an integer linear programming (ILP) formulation is used to characterize the object (wire-length and via) and constraints (overflow and slew). Second, the ILP formulation is relaxed into a LP formulation. Third, solving the Lagrangian relaxation of the LP formulation provides the price of each edge in the 3D routing model. Last, a RC-constrained A\* search is applied to help explore new buffering-aware topologies on all metal layers.

#### 1.5 Organization of the Dissertation

The rest of the dissertation is organized as follows. Chapter 2 formalizes a practical and new problem in rectilinear Steiner construction: BOB-RSMT. It demonstrates the importance of buffering-aware over-the-block RSMT and lack of that in previous works. Chapter 3 presents a solution for timing-driven pre-buffering rectilinear Steiner tree with over-the-block consideration. It illustrates the trade-off of timing and power for critical nets and non-critical nets. Chapter 3 also exhibits a post-tree-construction tuning algorithm which can further improves timing without more buffering cost. Chapter 4 characterizes a new global routing problem which considers over-the-block routing tracks as well as slew constraints in additional to traditional routing problem. It outlines the relevant prior work in global routing first. Then it describes the importance of over-the-block router followed by a new problem formulation. Next.

Chapter 4 utilizes the physical meaning of Lagrangian multipliers to calculate the real value of each edge in the 3D-routing framework. Finally, it introduces how to use multi-level topology selection algorithm and A\* search to discover new topologies. Chapter 5 summarizes the dissertation, and discusses topics for future research.

## Chapter 2

## Buffering-Aware RSMT Construction for Reclaiming Over-the-IP-Block Routing Resources

#### 2.1 Introduction

As the semiconductor technology scales into deeper sub-micron domain, trillions of transistors and nets can be designed on a single system-on-chip (SOC). Routing becomes more and more challenging because of congestion, power, timing and buffering requirements. Rectilinear Steiner minimum tree (RSMT) construction is a fundamental physical design problem to achieve routing and buffering quality. This classical problem has long been proved as NP-complete [41] and many works have been performed including recent breakthrough, e.g. [18].

Because of extensively using IP-blocks to shorten turn around time, SOC designs nowadays are packed with IP blocks or macros. RSMT construction avoiding these blockages is well known as the OA-RSMT problem. OA-RSMT problem has been studied actively in the last few years (e.g., [6,30,35,36]). Early approaches [35,36] only deal with rectangular blockages, while a most recent study [30] can tackle rectilinear blockages without

dissecting rectilinear blockages into rectangular ones. This approach can eliminate the unfeasible solutions which put wires and buffers between adjoining blocks. However, all these OA-RSMT algorithms simply treat IP blocks as routing blockages, which would significantly waste routing resources over these IP blocks and cause more congestion issues.

In practice, most IP blocks such as SRAMs only use certain lower metal layers. Even if we take into consideration the resources reserved for power/ground and clock routing, there are still considerable amount of routing resources available at higher metal layers over these IP blocks. It leads to over-the-block routing resources waste if we simply treat the IP blocks as routing obstacles, which results in more routing demand elsewhere.

Besides blockage avoidance, other layout constraints are considered in [10, 11, 27, 28, 43, 57]. [10, 27, 43, 57] take timing, buffering, etc., into consideration in their tree construction. But slew constraint is not fully touched upon. It is reported that in reality, slew mode buffering is more predominant than timing mode buffering [28, 44]. Only a fraction (roughly  $5\% \sim 10\%$ ) of nets needs to be buffered for delay optimization while for the remaining (roughly  $90\% \sim 95\%$ ) are sufficient with slew mode buffering to meet the slew constraints. [11] extends the work in [10] with slew in consideration. However, the slew constraints are translated as length constraints, which may not guarantee meeting strict slew tolerances. [28] considers slew mode buffering and adopts the blockage avoidance algorithm in [8, 26] to benefit slew. But this approach either puts a Steiner node stationary in block or completely moves it

out of block. This might bring unnecessary wiring detours and high buffering cost.

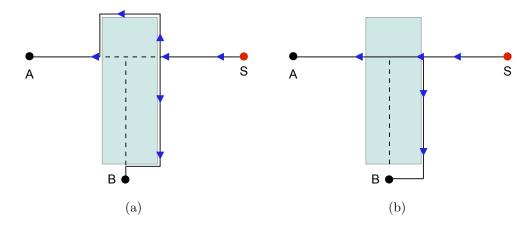

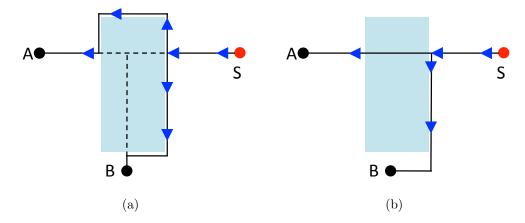

The blockage avoidance approach in [28] is shown by a 3-pin net example in Fig. 2.1(a). S is the source and A, B are the sinks; moving the Steiner node to right leads to the minimum-cost solution. Fig. 2.1(b) shows the same net if BOB-RSMT is adopted. In this case, BOB-RSMT saves two buffers as well as some detour wire-length because it changes the structure of inside tree more efficiently. Buffer-aware tree construction has advantage over methods of tree construction which are independent of buffering.

Figure 2.1: A motivational example compares [28] and our proposed BOB-RSMT, which saves wire-length and buffers.

In this chapter, we propose to study a new class of BOB-RSMT problem and develop an effective algorithm which tries to intelligently reclaim the "wasted", over-the-IP-block routing resources by previous approaches while ensuring slew constraints for high quality buffering. Our algorithm incrementally updates the initial RSMT structure obtained from FLUTE [18] to satisfy slew constraints while minimizing wire-length (FLUTE is chosen to be the initial RSMT generator because its low runtime and high quality). A restricted length, over-the-block maze routing algorithm is developed to reconnect any part of BOB-RSMT which is dissected during the optimization process. This chapter has the following major contributions:

- 1. This is the first work targeting this kind of BOB-RSMT problem. Our algorithm is able to integrate with a buffering tool to generate a low buffering cost BOB-RSMT without violating maximum slew constraint, which can be used in floorplanning, placement and routing stages. An incremental approach of fixing slew violation one by one is used to satisfy slew constraints on over-the-block part of BOB-RSMT.

- 2. Wire-length outside blocks of our BOB-RSMT is remarkably less comparing with that in other algorithms which are not utilizing over-the-block routing resources. This will result in better timing, less power consumption and alleviate routing congestion. The total wire-length, which includes the inside wire-length as well, is also shorter than the results from OA-RSMT algorithms.

- 3. We formulate the incremental slew improvement problem into an integer linear programming (ILP) problem, which can be solved very fast as the number of variables are small.

4. A block-aware maze router is proposed to reconnect any part of BOB-RSMT dissected during the tree structure optimization.

Our incremental approach of tree structures optimization will be presented in Section 2.2, which includes five subsections. Section 2.3.1 discusses about how to find possible point set. Section 2.3.2 gives a method of shrinking search space. Section 2.3.3 formulates and solves the problem. Section 2.3.4 introduces a block-aware maze router to reconnect any dissected part of the tree. Section 2.3.5 describes a buffer insertion algorithm. Experimental results will be shown in Section 2.4, followed by summary in Section 2.5.

#### 2.2 Problem Formulation

#### 2.2.1 What is BOB-RSMT?

BOB-RSMT which utilizes the routing resource over the IP-blocks to improve wire-length and congestion. In a two-dimensional routing region, we are given a net with a set of pins  $P = \{p_1, p_2, \ldots, p_n\}$ . Let  $B = \{b_1, b_2, \ldots, b_m\}$  be a set of non-overlapping rectilinear blocks in the 2-dimensional space. For  $\forall p_r \in P$ ,  $p_r$  is not inside the 2-dimensional space occupied by B. Any area with high-density placed logic cells is not allowed for buffering is also taken as buffering blockage into B.

Our algorithm constructs BOB-RSMT to connect all the pins in P. BOB-RSMT might intersect with blocks in B, which confine a set of trees  $T = \{T_1, T_2, \dots, T_l\}$  inside blocks. We call trees in T inside trees. The outside-the-block part of BOB-RSMT is defined as  $T_0$ . For each inside tree  $T_i \in T$ , the leaf nodes of  $T_i$  are on the boundaries of a block. Among all leaf nodes, one must be driving the signal and others are receiving. We name these leaf nodes which receive signals escaping points (EP), and the set of escaping points for  $T_i$  is  $EP^i = \{EP_1^i, EP_2^i, \dots, EP_{|EP^i|}^i\}$ , in which  $|EP^i|$  is the number of escaping points in  $EP^i$ . We denote the driver by  $D^i$ .

### 2.2.2 Basic Ideas and Optimization Primitives

For any inside tree  $T_i \in T$ , the worst slew part would occur at escaping points because no buffer is allowed to be inserted over the block. The best that a buffering tool can do to carry signal over the block to escaping points is to put the strongest buffer at  $D^i$  and a bunch of smallest buffers at  $EP^i$  to shield downstream capacitance. If for any  $j, slew_j^i$  is still worse than  $slew_{spec}^i$ , then the slew from  $D^i$  to  $EP^i_j$  violates maximum slew constraint, which means that no buffering solution can be generated anyway. Further, because we want to leave more margin for buffering tool at critical timing path and buffer placement aspects, we use a middle size hypothetical buffer at  $D^i$  and middle size hypothetical buffers at  $EP^i$  to judge if thus the escaping points have slew violation. Using middle size hypothetical buffers instead of two extreme sizes will weaken the capability of utilizing more over-the-block routing resources, but the former will be a more practical assumption and leads to less buffering cost because more solutions can propagate through this inside tree. If any escaping point  $EP_j^i$  driven by a hypothetical buffer has  $slew_j^i$  worse than  $slew_{spec}^i$ , then this  $EP_j^i$  is called illegal escaping point. Any inside tree with at least one illegal escaping point is an illegal inside tree.

In order to legalize any illegal inside tree, we will change positions of its escaping points as well as inside Steiner nodes. We move escaping points closer to the driver and then update the positions of corresponding Steiner nodes to improve slew. Fig. 2.2(a) is a three-pin net with source S and sinks A and B. Fig. 2.2(b) is the updated tree after a parallel sliding of escaping point V. Comparing Fig. 2.2(b) to Fig. 2.2(a), the downstream capacitance from W is closer to driver point due to the parallel sliding of V. The less capacitance burden to the driver reduces the slew on both escaping points U and V.

Figure 2.2: V moves to right in (b) compared to (a). This parallel sliding is providing slew improvement for escaping points U and V.

We adopt the following PERI model for slew calculation at the escaping points [34]:

$$S(v_j) = \sqrt{S(v_i)^2 + S_{step}(v_i, v_j)^2}$$

(1)

$S(v_j)$  is slew at any node  $v_j$ , which is the root-mean square of the *step slew* from  $v_i$  to  $v_j$  and *output slew* at node  $v_i$ . The experimental results in [34] shows the error of PERI is within 1%, which is indistinguishable from what is obtained using SPICE simulation. For simplicity we use Bakoglu's metric [12] for step slew calculation:

$$S_{step}(v_i, v_j) = \alpha * Elmore(v_i, v_j), \alpha = ln9$$

(2)

The combination of Bakoglu's metric and the PERI model is shown to have error within 4% [34]. It is, in general, accurate enough for RSMT construction purpose.

We propose three slew optimization primitives including parallel sliding, perpendicular sliding and EP merging to improve the slew. The proposed primitives could guide illegal inside trees to migrate into legal ones with minimum wire-length increase. The analysis demonstrates that the capability of using these three primitives can fix slew violations under any  $slew_{spec}$ .

We first analyze parallel sliding which performs sliding to a new position on one of the block boundaries. As the escaping point sliding on the boundary, if its first upstream Steiner node ancestor can also slide to keep the wire segment between escaping point and the ancestor Steiner node in translation, then this sliding on the boundary is called parallel sliding. The requirement of a meaningful parallel sliding is that the sliding should shorten the length of path from the escaping point to  $D^i$ , i.e., sliding the escaping point closer to the driver.

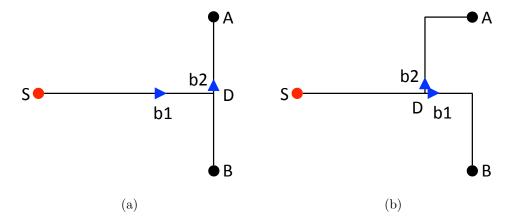

The example in Fig. 2.3(a) provides an inside tree with the driver D and escaping points A, B, C, E. Fig. 2.3(b) shows that escaping point A performs a parallel sliding by a distance of  $\Delta l$  to new position A'. There will be a reduction of step slew on escaping point A and B. We adopt the following notations in Table 2.1 to calculate the slew improvement of parallel sliding in this example. The step slew reduction on A and B from Bakoglu's metric model will be:

$$\delta_A = -\alpha * r\Delta l(C_t(U) + 0.5 * c\Delta l)$$

$$\delta_B = -\alpha * r * \Delta l * (C_b + c * l(A, U))$$

The output slew of the driver D remains unchanged since the total downstream capacitance of the inside tree is the same. Then we can use (3.3) to calculate the corresponding slew change on escaping point A and B. The changes in slew of escaping point C and E are both zero because U is not on the path from these two escaping points to the driver D.

Table 2.1: Notation of variables

| r        | unit length wire resistance on chosen layer          |

|----------|------------------------------------------------------|

| c        | unit length wire capacitance on chosen layer         |

| $R_b$    | chosen buffer output resistance                      |

| $C_b$    | chosen buffer input capacitance                      |

| l(U,V)   | length of edges between node $U$ and $V$             |

| $C_t(V)$ | total capacitance of the sub-tree rooted at node $V$ |

|          | down to the nearest downstream buffer,               |

|          | including the buffer input capacitance               |

With parallel sliding we can decrease slew at escaping points, but we

Figure 2.3: An example shows slew reduction from three primitives. (b) shows escaping point A slides to A' parallelly to improve slew on A and B. (c) shows the vertical sliding of A from A' to A''. (d) shows EP merging of escaping point A to E.

may have wire-length penalty because the position change of escaping points may need some additional wire connection from outside-the-block sub-tree. In the example shown in Fig. 2.3(a) to Fig. 2.3(b), escaping point A moves a distance of  $\Delta l$  to A' by a parallel sliding. The penalty of wire-length is at most  $\Delta l$  because the outside connection to A' can go through A along the edge

from A to A' with  $\Delta l$  more wire-length and there is no change in wire-length of inside tree.

Besides parallel sliding, we perform perpendicular sliding on edges which are not considered as parallel sliding edges. In Fig. 2.3(c), if A is sliding on the segment between A' to A'', the wire-length penalty will be zero during the whole sliding process because slide of A from A' to A'' is just slipping wire from inside block to outside. It is observed that as A reaches A'', all escaping points will have the largest slew improvement due to the least downstream capacitance from U'. The calculation of slew reduction is similar as of parallel sliding.

Complementary to parallel sliding and perpendicular sliding, EP merging removes one escaping point and all edges from this escaping point up to the first Steiner point ancestor in the inside tree. This will also bring down the slew of all escaping points based on the fact that this escaping point and the upstreaming edges from it to next Steiner point in the inside tree will be removed. The above process will reduce the total capacitance burden of the driver and hence improve slew for all escaping points.

In tree  $T_i$ , if EP merging joins one  $EP_i$  with another  $EP_j$ , the outside connection to  $EP_i$  will be reconnected to  $EP_j$  or other closer part of BOB-RSMT by a restricted length, over-the-block maze routing algorithm, which will be introduced in Section 2.3.4.

Considering the EP merging of escaping point A to E in Fig. 2.3(a)

## **Algorithm 1** The overall BOB-RSMT Algorithm

Require: Initial inside trees T, Slew required for the net:  $slew_{spec}$

Ensure: BOB-RSMT

- 1: for each  $T_t$  do

- 2: Sort  $EP^t$  in descending order of slew

- 3: while  $slew_1^t > slew_{spec}$  do

- 4: Build possible point set for all unfixed EP in  $EP^t$

- 5: Formulate the problem by a ILP

- 6: Solve the ILP and update  $T_t$

- 7: Remove  $EP_1^t$  from  $EP^t$

- 8: end while

- 9: end for

- 10: return BOB-RSMT

and Fig. 2.3(d), the wire-length penalty will be at most the distance between A and E because the outside connection to A can go through original position of A and then along the edge to E as shown in Fig. 2.3(d). Actually due to the existence of tree outside this block, reconnecting to the outside part might have less wire-length penalty. But here, we take the previous conservative estimate as the wire-length penalty because it is guaranteed to be achieved. The calculation of slew reduction is similar.

# 2.3 BOB-RSMT Algorithms

To construct a legal BOB-RSMT, we first generate an initial RSMT by using FLUTE-3.1, and then we apply primitives to all illegal inside trees to fix the slew of them. Finally a proposed restricted length, over-the-block maze routing algorithm is used to reconnect all these parts to form the final BOB-RSMT. The approach is described in Algorithm 1.

For each  $T_t \in T$  as an illegal inside tree, three primitives are applied to decrease slew on illegal escaping points until  $T_t$  becomes a legal inside tree. The procedure starts from calculating slew of each  $EP_i^t$ . From the calculated result, we first sort  $EP^t$  in descending order of their slew violations as line 2 of Algorithm 1. Then we choose the first illegal escaping point,  $EP_1^t$ , which should have worst slew violation based on the sorting. To improve slew for  $EP_1^t$ , each escaping point from  $\{EP_1^t, EP_2^t, \dots EP_{|EP^t|}^t\}$  might slide to a different position by taking a combination of primitives discussed in section 2.2.2. Taking these optimization primitives guarantees  $slew_1^t$  to be within slew requirement. Because in the extreme situation where maximum slew constraint is zero  $EP_1^t$  can still become legal escaping point by merging one escaping point to another until only the driver is left. This slew fixing procedure is elaborated through line 4 to 6 of Algorithm 1.

After  $slew_1^t$  has decreased below the required slew,  $EP_1^t$  is fixed at the current position and removed from  $EP_t$  as in line 7. Next iteration will start from the rest of  $EP^t$ . The current iteration will not degrade the result of previous iterations as we will remove solution space from current solution space if it degrades slew of fixed escaping points. This solution space elimination happens rarely because moving one escaping point closer to driver usually does not degrade slew on other points. This slew improvement method will keep being applied on  $EP_1^t$  at each iteration until all  $EP^t$  are fixed.

Figure 2.4: (a) is an inside tree with driver at D. It shows all possible points for E. (b) exhibits the refined possible point set for E.

### 2.3.1 Generating Possible Point Set

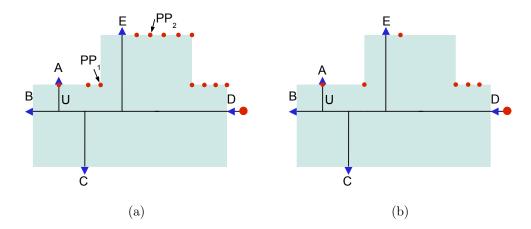

At every iteration we try to improve the  $slew_1^t$  of inside tree  $T_t \in T, t \in \{1, 2, \ldots, l\}$ . One important step in that is to generate possible point set for each non-fixed escaping points. Possible point set is a set of all possible points of one non-fixed escaping point. Each possible point in the set is a point on a boundary edge where escaping point might end up. For any non-fixed  $EP_i^t \in \{EP^t\}$ , the  $j^{th}$  possible point associated with  $EP_i^t$  is denoted as  $PP_{ij}$ .  $PP_{ij}$  is stored in a 3-tuple format  $\{E_{ij}, B_{ij}, W_{ij}\}$ .  $E_{ij}$  and  $B_{ij}$  denote the step slew at  $EP_1^t$  and output slew reduction of the driver if  $EP_i$  moves to  $PP_{ij}$ .  $W_{ij}$  is the corresponding estimated wire-length penalty. The possible point set associating with  $EP_i^t$  in the current iteration is denoted as  $PPS_i^t$ .  $PPS_i^t = \{PP_{i1}^t, PP_{i2}^t, \ldots, PP_{ir}^t\}$ , where r is the number of possible points inside.

For each  $EP_i^t$  in current iteration, we generate the possible point for EP merging first. Assume the target escaping point for  $EP_i^t$  to merge with is  $EP_j^t$ . The estimated wire-length penalty is the outside-the-block distance from  $EP_i^t$  to  $EP_j^t$ . Thus for EP merging, we always choose the  $EP_j^t$  with minimum outside-the-block distance from  $EP_i^t$ . The slew reduction and the estimated wire-length penalty of this choice will be added to the  $PPS_i^t$  as the 3-tuple  $\{E_{ij}, B_{ij}, W_{ij}\}$ . For example in Fig.2.4(a), where  $EP_1^t$  is B and  $EP_i^t$  is E, the EP merging point for E is escaping point A.

Secondly, we consider the sliding for  $EP_i^t$ . We first search all edges on  $block_t$  for sliding by the criteria discussed in Section2.2.2. The  $block_t$  here refers to the block confining  $T_t$ . Then for each parallel sliding edge, we chop it at a number of points. Moving  $EP_i^t$  to any one of these points can improve slew on  $EP_1^t$ . For each perpendicular sliding edge, we pick the possible point at one end of it, as discussed in Section2.2.2. Each chop point is a possible point, which will be added into possible point set. We set distance between two chop points to be a fixed value depending on the scale of the chip. For example in Fig.2.4(b), D is the driver and A, B, C, E are escaping points. The possible point set for E are shown with red color dots.

## 2.3.2 Refinement of Possible Region Set

For any escaping point  $EP_i^t$ , after collecting  $PPS_i^t$ , we will do a refinement on  $\forall PP_{ij} \in PPS_i^t$  to reduce the potential solution space. The refinement is based on Pareto efficiency [13].

The refined possible point set should form a Pareto frontier in the sense of estimated wire-length penalty and slew reduction (both output slew reduction at the driver and step slew reduction at  $EP_1^t$ ), which is restricting attention to the set of choices that either has less estimated wire-length penalty or more slew reduction. After applying refinement on Fig.2.4(a), the possible points turn into Fig.2.4(b). One example of a pruned possible point in Fig.2.4(a) is:  $PP_2$  is pruned by  $PP_1$  as the latter has less estimated wire-length penalty and more slew improvement.

#### 2.3.3 Primitive Choice Based on a Fast ILP

In order to construct the inside tree under the slew constraint with minimum wire-length as target,  $\forall EP_i^t \in EP^t$  we need to decide which possible point to choose. We use an incremental way to update positions of all escaping points at each iteration. In each iteration, in order to meet the slew constraint for the worst violated escaping point, all escaping points in  $EP^t$  will move and the whole inside tree will be updated. Only through moving all  $EP_i^t \in EP^t$  at the same time can we attain an optimal solution with minimum estimated wirelength penalty. This stems from the reason that  $\forall PPS_i^t, i \in \{1, 2, ..., |EP_i^t|\}$  has a Pareto frontier to choose one point from. The choice depends on what choices are made at other Pareto frontiers because the total slew reduction summed up from all these choices has to diminish the slew violation of  $EP_1^t$ .

The new slew has to satisfy the slew constraints,

$$\sqrt{(S_{step1}^t + \sum_{i=1}^{|EP_i^t|} E_i^t)^2 + (S^t(D^t) + \sum_{i=1}^{|EP_i^t|} B_i^t)^2} < slew_{spec}^t$$

The simultaneous step slew reduction is same with calculating one by one, and the simultaneous output slew reduction is close enough to be represented by the summation of individuals.

This simultaneous selection problem is exact knapsack problem: Given a set of possible points, each with a slew improvement and a wire-length penalty, determine possible point to move to so that the total slew improvement is more than or equal to a given limit and the total wire-length penalty is as small as possible [2]. We use maximum number of possible points on one edge to limit the maximum number of candidates from one EP. Then the total number of candidates for inside-tree t is O(n) where n is the number of EPs. Moreover, the number of EPs on one block for each net equals to the number of interactions between one topology and one block. Since this decision problem is NP-complete and the problem size for each block is O(n), we can apply ILP to solve it. The simultaneous point choice problem can be formulated in an optimization problem as follows (notation in Table 2.2):

Table 2.2: Notation of variables in our formulation

| $X_{ij}$   | binary variable denoting the choice of $PPS_{ij}^t$ ,                     |

|------------|---------------------------------------------------------------------------|

|            | $X_{ij} = 1$ if it is chosen, otherwise $X_{ij} = 0$                      |

| $E_{ij}$   | step slew reduction at $EP_1^t$ if $EP_i^t$ moves to $PPS_{ij}$           |

| $B_{ij}$   | output slew reduction on $D^t$ if $EP_i^t$ moves to $PPS_{ij}$            |

| $W_{ij}$   | estimated wire-length penalty of $EP_1^t$ if $EP_i^t$ moves to $PPS_{ij}$ |

| $Y_{rsij}$ | binary variable equals to one only if $X_{rs} = 1$ and $X_{ij} = 1$       |

$$\min \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} X_{ij} W_{ij}$$

(3)

s.t.

$$(S_{step1}^t + \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} X_{ij} E_{ij}^t)^2 +$$

$$(S^{t}(D^{t}) + \sum_{i=1}^{|EP^{t}|} \sum_{j=1}^{|PPS_{i}^{t}|} X_{ij} B_{ij}^{t})^{2} \le slew_{spec}^{t}^{2}$$

(3a)

$$\sum_{j=1}^{|PPS_i^t|} X_{ij} = 1 \qquad \forall i \in \{1, 2, \dots, |EP^t|\}$$

(3b)

The objective function (5) is to minimize the total estimated wirelength penalty. Constraint (3a) restricts that the total slew reduction on  $EP_1^t$  has to be able to pull  $slew_1^t$  down below requirement. Constraint (3b) is used to limit only one position chosen for each escaping point.

This formulation is a non-linear integer programming formulation (NLIP).

We expand the step slew part in constraint (3a) as:

$$\begin{split} S_{step1}^{t}^{2} + 2S_{step1}^{t} \sum_{i=1}^{|EP^{t}|} \sum_{j=1}^{|PPS_{i}^{t}|} (X_{ij}^{t})(E_{ij}^{t}) + \\ \sum_{r=1}^{|EP^{t}|} \sum_{s=1}^{|PPS_{i}^{t}|} \sum_{i=1}^{|EP^{t}|} \sum_{j=1}^{|PPS_{i}^{t}|} X_{rs}^{t} E_{rs}^{t} X_{ij}^{t} E_{ij}^{t} \end{split}$$

We observe that the only quadratic item is  $X_{rs}^t X_{ij}^t$ . We can substitute this item for a new binary variable  $Y_{rsij}$ . We constrain  $Y_{rsij}$  such that  $Y_{rsij}$  always behaves same as  $X_{rs}^t X_{ij}^t$ . The constraint needed is (for output slew part, it is similar):

$$Y_{rsij} \le X_{rs}^t \qquad \forall r, s, i, j \in \{1, 2, \dots, |EP^t|\}$$

(3c)

$$Y_{rsij} \le X_{ij}^t \qquad \forall r, s, i, j \in \{1, 2, \dots, |EP^t|\}$$

(3d)

$$Y_{rsij} > = X_{rs}^t + X_{ij}^t - 1 \ \forall r, s, i, j \in \{1, 2, \dots, |EP^t|\}$$

(3e)

By adding constraint  $(3c) \sim (3e)$  to (5), we turn the NLIP problem into integer linear programming formulation (ILP), which can be solved by solver Gurobi Optimizer [1] quickly. The formulation of ILP is shown as follows:

$$\begin{aligned} & \text{min.} \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} X_{ij} W_{ij} \\ & \text{s.t.} S_{step1}^t ^2 + S^t (D^t)^2 + 2 S_{step1}^t \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} (X_{ij}^t) (E_{ij}^t) + \\ & 2 S^t (D^t) \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} (X_{ij}^t) (B_{ij}^t) + \\ & \sum_{r=1}^{|EP^t|} \sum_{s=1}^{|PPS_i^t|} \sum_{i=1}^{|EP^t|} \sum_{j=1}^{|PPS_i^t|} (B_{rs}^t B_{ij}^t + E_{rs}^t E_{ij}^t) Y_{rsij} <= slew_{spec}^t \\ & \sum_{j=1}^{|PPS_i^t|} X_{ij} = 1 & \forall i \in \{1, 2, \dots, |EP^t|\} \\ & Y_{rsij} <= X_{rs}^t & \forall r, s, i, j \in \{1, 2, \dots, |EP^t|\} \\ & Y_{rsij} >= X_{rs}^t + X_{ij}^t - 1 \ \forall r, s, i, j \in \{1, 2, \dots, |EP^t|\} \end{aligned}$$

Due to the number of choices for each escaping point is limited by the number of possible sliding edges and their length, the total number of variables in our formulation is very limited. The ILP solver can get the solution very fast.

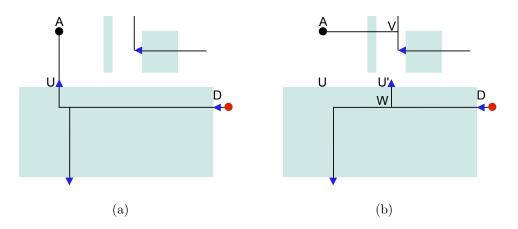

#### 2.3.4 Block-aware Maze Routing Algorithm

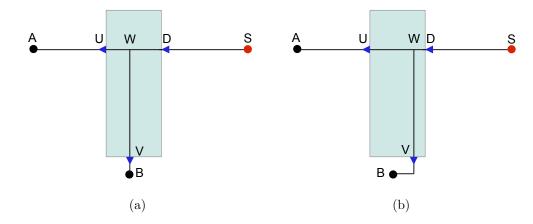

After final positions of all escaping points are fixed, a restricted length, over-the-block maze routing will be applied. This maze routing features ability of routing over-the-blockage. The maximum length it can route over the block is decided by the distance a middle size buffer could drive itself over the block without slew problem. This restricted length, over-the-block maze

router requires less wire-length comparing with normal maze router because of its ability to route over the block. In Fig. 2.5(a), U is an escaping point and A is a sink of the tree. Escaping point U slides to U' to legalize the inside tree. The restricted length, over-the-block maze is applied to reconnect A, and it will choose connection from A to V instead of from A to U' because of shorter wire-length, resulting in Fig. 2.5(b). Wire segment U' to W will be removed if no other part connects to U'.

Figure 2.5: Restricted length, over-the-block maze routing find a shortest path to reconnect pin A

The implementation of block-aware maze routing is based on the normal maze routing. But its multiple points to multiple points search is from all points of the tree rooted at the current escaping point to  $T_0$  or an escaping point of any inside tree. Furthermore, the length of the over-the-block path is checked every step in the search to make slew safe. The details of the algorithm are skipped here due to page limit.

#### 2.3.5 Min-cost Slew Mode Buffer Insertion

After BOB-RSMT is fully constructed, we insert buffers in a free-location way, which allows buffers at any unblocked space. Comparing with fixed-location buffer insertion algorithm, free-location buffering can freely choose position for buffering, which will result in lower buffer cost. We assume the input slew of each buffer is fixed at the slew constraint. Free-location buffering with fixed input slew will give a shorter runtime but conservative result [28]. It uses a dynamic programming framework to propagate a set solutions from bottom up to the source of the net. Each solution is characterized as a triple (C, W, S), where C stands for downstream capacitance, W denotes the total cost of the solution, and S is the worst downstream accumulated step slew degradation calculated from (3.4). Consider to propagate a solution from a node  $v_j$  to its parent  $v_i$  through edge  $e = (v_i, v_j)$ . One solution  $\gamma_j$  at node  $v_j$  propagates to  $v_i$  to become a solution  $\gamma_i$  as  $C(\gamma_i) = C(\gamma_j) + C_e, W(\gamma_i) = W(\gamma_j), S(\gamma_i) = S(\gamma_j) + S_{step}(v_i, v_j)$ .

In addition to unbuffered propagation, a buffer can be placed at  $v_i$  to generate a buffered solution. If a buffer is placed, the buffered solution at  $v_i$  is becoming  $C(\gamma_{i,buf}) = C_b, W(\gamma_{i,buf}) = W(\gamma_i) + W_b, S(\gamma_{i,buf}) = 0$ .

When two sets of solutions propagated by both left and right children reach a branching node, these two set of solutions are merged. The merge is performed on each solution in left child with each solution in right child. Assume  $\gamma_l$  is one solution from left side and  $\gamma_r$  is one solution from right side to be merged. The merged solution  $\gamma_p$  will have  $C(\gamma_p) = C(\gamma_l) + C(\gamma_l), W(\gamma_p) =$

$$W(\gamma_l) + W(\gamma_r), S(\gamma_p) = \max\{S(\gamma_l), S(\gamma_r)\}.$$

It is beneficial to prune useless solution at each node. As two solutions  $\gamma_{i_1}$  and  $\gamma_{i_2}$  are at same node,  $\gamma_{i_1}$  dominates  $\gamma_{i_2}$  only if  $C(\gamma_{i_1}) <= C(\gamma_{i_2}), W(\gamma_{i_1}) <= W(\gamma_{i_2}), S(\gamma_{i_1}) <= S(\gamma_{i_2}).$

# 2.4 Experimental Results

We have implemented our algorithm in the C++ programming language. The experiments are conducted on an Intel Core 3.0GHz Linux machine with 32GB memory. We choose Gurobi Optimizer 4.60 as our solver for the integer linear programming.

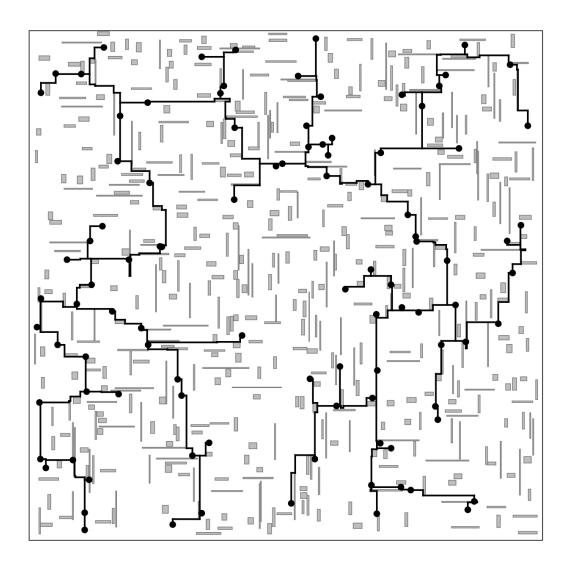

RT1-RT5 and RC01-RC11 are benchmarks in our experiments. IND1-IND5 used in [6,30] are not used in our experiments, because they require routing/buffering between adjoining blocks, which might be unfeasible for real designs. RT1-RT5 are randomly generated circuits used in [37]. RC01-RC11 are test cases used in [24]. Because these benchmarks are widely different in scale and do not carry timing and physical information, we first apply predetermined resistance and capacitance to all of them. We use different resistance and capacitance for horizontal and vertical wires respectively. If a congestion map is considered, we can assign each wire segment to a proper layer by pruning possible points in congestion.

For each benchmark, after FLUTE-3.1 finishes generating inside trees, we collect slew on every escaping point for all inside trees. The range of value of collected slew is  $[slew_{min}, slew_{max}]$ . Then we test each benchmark under three slew constraints:

- 1. 20\% slew:  $slew_{min} + 20\%(slew_{max} slew_{min})$

- 2. 50% slew:  $slew_{min} + 50\%(slew_{max} slew_{min})$

- 3. 80% slew:  $slew_{min} + 80\%(slew_{max} slew_{min})$ .

These three tests of each benchmark can test the performance of our algorithm under tight, medium and loose slew constraints, respectively.

Table 2.5 compares the performance of our algorithm with some recently published OA-RSMT algorithms. Columns 4, 5, 6 list the over-the-block wire-length, outside-the-block wire-length and total wire-length of our algorithm under 20% slew constraint. Columns 7 to 12 are for same types of wire-length under 50% and 80% slew constraints. The row at bottom illustrates the average performance from all benchmarks listed above. We normalize the performance in such a way that the total wire-length of FLUTE-3.1 is 100. The outside-the-block wire-length from Huang [30] is 14.27% more than our BOB-RSMT algorithm under 20% slew constraint and 17.29% under 80% slew constraint. The free over-the-block routing resources reclaimed by BOB-RSMT are between 10% to 12% of the total wire-length. Even for the total wire-length, since BOB-RSMT can intelligently use over-the-block wires, it can reduce about 5% of total wire-length compared with [30] and [6]. The runtime of our proposed algorithm BOB-RSMT is divided into two parts:

solving ILP and block-aware maze routing, which are listed in the columns 2, 3, 6, 7, 10, 11 in Table 2.3. Our runtime is much shorter than both reported in [30] and [6].

Table 2.4 carries out the buffering results on FLUTE, approach in [28] and BOB-RSMT. For simplicity we only use one type of buffer, and total buffering cost is the number of buffers used. From the table we have minimum buffering cost associated with 20%, 50%, 80% slew constraint respectively for all benchmarks. We use buffering on FLUTE as the baseline for our comparison. Buffering on FLUTE is performed without considering any block in the two-dimensional routing region. We implement the approach in [28] and the results are in columns 3, 8, 13 in the Table 2.4. The penalty parameter  $\alpha$  for over-the-block routing wires in [8, 28] is set between 10 to 100, which increases if no solution can propagate to the source. Columns 5, 10, 15 in the Table 2.4 are the minimum buffering costs from BOB-RSMT. Columns after the buffering cost are the percentages of extra buffers used to overcome blocks by that approach. As we can see, buffering on BOB-RSMT only uses around 3% more buffers than FLUTE to propagate through blocks, while the approach in [28] uses more than 20%. The CPU runtime comparison between buffering on BOB-RSMT and the approach in [28] is in Table 2.3. Columns 5, 9, 13 illustrate the runtime for buffering on BOB-RSMT under three slew constraints while columns 4, 8, 12 are for approach in [28]. Buffering on BOB-RSMT is much faster because during the buffering stage, the tree structure of BOB-RSMT has no need to be changed to meet slew constraint, but in contrast [28] needs to find LeastBlockedPath([8,26]) during every step.

# 2.5 Summary

In this chapter, we study an important new class of RSMT problems, i.e., buffering-aware over-the-IP-block rectilinear Steiner minimum tree. We propose an effective and efficient algorithm which can reclaim the over-the-IP-block routing resources and is beneficial to buffering. With our proposed approach, we can reduce the outside-the-block wire-length for more than 14% and use about 19% less buffer cost than the approach in [28] to ensure slew correct RSMT with blocks. Our proposed algorithm BOB-RSMT can be used in both pre-routing and global routing stage to provide high quality routing solutions. One example is to pre-route certain persistent critical signals in large complex chips, such as a microprocessor, using higher metal layers. Since this is the first work of this kind, we expect more follow-up works to push the state-of-the-art of BOB-RSMT, which is crucial for large SOC designs with many IP-blocks.

Table 2.3: CPU runtime

|                                 |           |              |           |    |      |         | $CP \cap (s)$ |           |      |         |           |           |

|---------------------------------|-----------|--------------|-----------|----|------|---------|---------------|-----------|------|---------|-----------|-----------|

| 20% slew                        | 20% slew  | 20% slew     |           |    |      |         | 50% slew      |           |      |         | 80% slew  |           |

| maze   C-SB   BOB-RSM7          | C-SB      | Е            | BOB-RS    | MT |      | maze    | C-SB          | BOB-RSMT  |      | maze    | C-SB      | BOB-RSMT  |

| ILP routing buffering buffering | buffering |              | buffering |    | ILP  | routing | buffering     | buffering | ILP  | routing | buffering | buffering |

| 0.1                             | 270.09    |              | 0.03      |    | 0    | 0.04    | 281.62        | 0.02      | 0    | 0.04    | 285.03    | 0.01      |

|                                 |           | 1041.83 0.03 | 0.03      |    | 0    | 0.04    | 1056.27       | 0.07      | 0.01 | 0.1     | 1059.6    | 0.04      |

| 0.13                            | 905.05    | _            | 0.26      |    | 0    | 0.02    | 1023.39       | 0.19      | 0    | 0.07    | 1041.01   | 0.15      |

| 0.25 2859.06 (                  | 2859.06   | _            | 0.64      |    | 0    | 0.02    | 2880.2        | 0.47      | 0    | 0.07    | 2896.48   | 0.43      |

|                                 | > 7200    |              | 1.25      |    | 0.01 | 1.43    | > 7200        | 1.03      | 0.01 | 0.35    | > 7200    | 1.03      |

| 0.01                            |           | 0.05 0       | 0         |    | 0    | 0.01    | 0.05          | 0         | 0    | 0       | 0.05      | 0         |

| 0.45                            | 0.45      |              | 0.01      |    | 0    | 0       | 0.53          | 0         | 0    | 0.01    | 0.63      | 0         |

| 0.02 0.50                       | 0.50      |              | 0.01      |    | 0    | 0.03    | 0.66          | 0.01      | 0    | 0.01    | 0.63      | 0.01      |

| 0.04 2.72                       | 2.72      |              | 0.01      |    | 0    | 0.01    | 2.40          | 0.01      | 0.02 | 0       | 2.40      | 0.01      |

| 0.01 4.44                       | 4.44      |              | 0.02      |    | 0.01 | 0.01    | 4.44          | 0.02      | 0.01 | 0.01    | 4.50      | 0.02      |

| 0.91 1652.4                     | 1652.4    |              | 0.2       |    | 0.01 | 80.0    | 1643.11       | 0.12      | 0    | 0.09    | 1634.05   | 0.13      |

| > 7200                          | > 7200    |              | 0.36      |    | 0.02 | 1.51    | > 7200        | 0.29      | 0    | 0.56    | > 7200    | 0.24      |

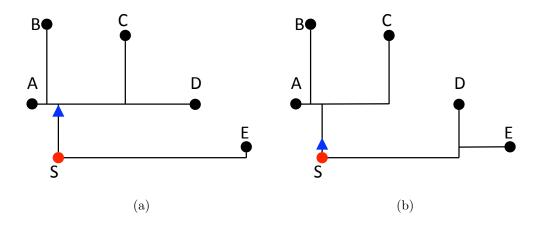

| 2.24 > 7200                     | > 7200    |              | 0.05      |    | 0.01 | 92.0    | > 7200        | 0.56      | 0.01 | 0.26    | > 7200    | 0.55      |