Copyright

by

Reena Panda

2017

# The Dissertation Committee for Reena Panda certifies that this is the approved version of the following dissertation:

# **Accurate Modeling of Core and Memory Locality for Proxy Generation Targeting Emerging Applications and Architectures**

| Committee:               |   |

|--------------------------|---|

|                          |   |

| Lizy K. John, Supervisor |   |

| Earl E. Swartzlander Jr. | _ |

| Sarfraz Khurshid         | _ |

| Andreas Gerstlauer       |   |

| Karthik Ganesan          | _ |

# **Accurate Modeling of Core and Memory Locality for Proxy Generation Targeting Emerging Applications and Architectures**

by

## Reena Panda

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2017

Dedicated to my husband Prateek,

my parents

and

my sister

## **Acknowledgments**

I would like to thank my advisor, Dr. Lizy Kurian John, for her advice, support and guidance. Dr. John had a great influence on the overall direction of this research and the content of this dissertation. Without her guidance over the years, this work would not have been possible. I am grateful to her for making my research experience a memorable one.

I would also like to thank my committee members, Professor Andreas Gerstlauer for his helpful comments and feedback in improving many research papers that I submitted as a graduate student; Professor Sarfraz Khurshid for his support and encouragement in my most difficult time in graduate school; Professor Earl Swartzlander for his kindness and useful suggestions during the course of this work; and Dr. Karthik Ganesan for providing me valuable feedback to improve this dissertation. Special thanks to Prof. Paul Gratz for introducing me to the field of computer architecture research and motivating me to pursue a Ph.D.

Thanks to Melanie, Melody, Barry and other administrative assistants who worked in the ECE department in the past years.

I also thank my fellow group members at the Laboratory for Computer Architecture (LCA). I enjoyed my collaborations with Dr. Xinnian Zheng, Chris Erb, Michael Lebeane, Jiajun Wang, Wooseok Lee, Dr. Jee Ho Ryoo, Shuang Song and Qinzhe Wu on various research projects. Their research ideas, their knowledge in

many diverse disciplines, willingness to listen and comment in many talks and discussions, and friendly help were much appreciated. I also enjoyed great discussions with Mochamad Asri and Kisore Punniyamurthy regarding research and otherwise.

I want to dedicate this dissertation to my father (bapa). Bapa has taught me the value of hard work and perseverance. He is and will always be my first teacher. I would like to thank my mother for her unconditional love, support and encouragement all through my life. She is my biggest strength. I would also like to thank my sister for being there with me through every good and bad phase of life and always motivating me to keep trying. I am eternally grateful to my family for everything. I would also like to thank my in-laws for being very supportive and encouraging throughout my graduate studies.

This dissertation would not be complete without giving credit to my husband and best friend, Prateek Srivastava. His unwavering support, constant motivation and enthusiasm has kept me going through the difficult years of graduate school. He took active interest in my research, helped me refine and shape ideas, proofread my papers, and gave feedback on my presentations. This is not something I could have accomplished alone.

Lastly, I would like to thank god for blessing me with this opportunity and giving me the strength to reach this point.

**Accurate Modeling of Core and Memory Locality for Proxy Generation Targeting Emerging Applications and Architectures**

Publication No.

Reena Panda, Ph.D.

The University of Texas at Austin, 2017

Supervisor: Lizy K. John

Designing optimal computer systems for improved performance and energy efficiency requires architects and designers to have a deep understanding of the enduser workloads. However, many end-users (e.g., large corporations, banks, defense organizations, national labs, etc.) are apprehensive to share their applications with designers due to the confidential nature of software code and data. In addition, emerging applications pose significant challenges to early design space exploration due to their long-running nature and the highly complex nature of their software stack that can not be supported on many early performance models.

The above challenges can be overcome by using a proxy benchmark. A miniaturized proxy benchmark can be used as a substitute of the original workload to perform early computer performance evaluation. The process of generating a proxy benchmark consists of extracting a set of key statistics to summarize the behavior of end-user applications through profiling and using the collected statistics

vii

to synthesize a representative proxy benchmark. Using such proxy benchmarks can help designers to understand the behavior of end-user's workloads in a reasonable time without the users having to disclose sensitive information about their workloads.

Prior proxy benchmarking schemes leverage micro-architecture independent metrics, derived from detailed simulation tools, to generate proxy benchmarks. However, many emerging workloads do not work reliably with many profiling or simulation tools, in which case it becomes impossible to apply prior proxy generation techniques to generate proxy benchmarks for such complex applications. Furthermore, these techniques model instruction pipeline-level locality in great detail, but abstract out memory locality modeling using simple stride-based models. This results in poor cloning accuracy especially for emerging applications, which have larger memory footprints and complex access patterns. A few detailed cache and memory locality modeling techniques have also been proposed in literature. However, these techniques either model limited locality metrics and suffer from poor cloning accuracy or are fairly accurate, but at the expense of significant metadata overhead. Finally, none of the prior proxy benchmarking techniques model both core and memory locality with high accuracy. As a result, they are not useful for studying system-level performance behavior. Keeping the above key limitations and shortcomings of prior work in mind, this dissertation presents several techniques that expand the frontiers of workload proxy benchmarking, thereby enabling computer designers to gain a better and faster understanding of end-user application behavior without compromising the privileged nature of software or data.

This dissertation first presents a core-level proxy benchmark generation methodology that leverages performance metrics derived from hardware performance counter measurements to create miniature proxy benchmarks targeting emerging big-data applications. The presented performance counter based characterization and associated extrapolation into generic parameters for proxy generation enables faster analysis (runs almost at native hardware speeds, unlike prior workload cloning proposals) and proxy generation for emerging applications that do not work with simulators or profiling tools. The generated proxy benchmarks are representative of the performance of the real-world big-data applications, including operating system and run-time effects, and yet converge to results quickly without needing any complex software stack support.

Next, to improve upon the accuracy and efficiency of prior memory proxy benchmarking techniques, this dissertation presents a novel memory locality modeling technique that leverages localized pattern detection to create miniature memory proxy benchmarks. The presented technique models memory reference locality by decomposing an application's memory accesses into a set of independent streams (localized by using address region based localization property), tracking fine-grained patterns within the localized streams and, finally, chaining or interleaving accesses from different localized memory streams to create an ordered proxy memory access sequence. This dissertation further extends the workload cloning approach to Graphics Processing Units (GPUs) and presents a novel proxy generation methodology to model the inherent memory access locality of GPU applications, while also accounting for the GPU's parallel execution model. The generated

memory proxy benchmarks help to enable fast and efficient design space exploration of futuristic memory hierarchies.

Finally, this dissertation presents a novel technique to integrate accurate core and memory locality models to create system-level proxy benchmarks targeting emerging applications. This is a new capability that can facilitate efficient overall system (core, cache and memory subsystem) design-space exploration. This dissertation further presents a novel methodology that exploits the synthetic benchmark generation framework to create hypothetical workloads with performance behavior that does not currently exist. Such proxies can be generated to cover anticipated code trends and can represent futuristic workloads before the workloads even exist.

# **Table of Contents**

| Ackno   | wledgm   | ents                                                                         | V   |

|---------|----------|------------------------------------------------------------------------------|-----|

| Abstra  | ct       |                                                                              | vii |

| List of | Tables   |                                                                              | XV  |

| List of | Figures  |                                                                              | xvi |

| Chapte  | er 1. II | ntroduction                                                                  | 1   |

| 1.1     | Proble   | m Description                                                                | 4   |

|         | 1.1.1    | Limitations of Prior Research Work                                           | 7   |

| 1.2     | Overv    | iew of Proposed Research                                                     | 12  |

|         | 1.2.1    | Core-level Proxy Generation using Performance Counter Based Characterization | 12  |

|         | 1.2.2    | Memory Locality Modeling using Hierarchical Pattern Detection                | 13  |

|         | 1.2.3    | System-level Proxy Benchmark Synthesis                                       | 15  |

|         | 1.2.4    | Synthetic Workloads to Cover Workload Performance Spectrum                   | 16  |

| 1.3     | Thesis   | Statement                                                                    | 17  |

| 1.4     | Thesis   | Contributions                                                                | 17  |

| 1.5     |          | Organization                                                                 | 20  |

| Chapte  | er 2. R  | telated Work                                                                 | 22  |

| 2.1     | Schem    | es for Modeling Cache and Memory Performance                                 | 22  |

| 2.2     | Schem    | es for Modeling Core-level Performance                                       | 26  |

| 2.3     | Techni   | ques for Modeling GPU Workload Performance                                   | 27  |

| 2.4     | Other    | Techniques for Reducing Simulation Time                                      | 28  |

| Chapte | r 3. N | <b>Methodology</b>                                                                                                 | 30 |

|--------|--------|--------------------------------------------------------------------------------------------------------------------|----|

| 3.1    | Detail | s of Profiling and Simulation Infrastructure                                                                       | 31 |

|        | 3.1.1  | Profiling and Measurement Infrastructure on Real Machines .                                                        | 31 |

|        | 3.1.2  | Simulation Infrastructure                                                                                          | 32 |

|        |        | 3.1.2.1 System Performance Simulation                                                                              | 32 |

|        |        | 3.1.2.2 Memory Timing Simulation                                                                                   | 32 |

|        |        | 3.1.2.3 Cache Hierarchy Simulation                                                                                 | 33 |

|        |        | 3.1.2.4 GPU Performance Simulation                                                                                 | 34 |

| 3.2    | Workl  | oad Description                                                                                                    | 35 |

|        | 3.2.1  | Databases                                                                                                          | 35 |

|        |        | 3.2.1.1 Cassandra                                                                                                  | 35 |

|        |        | 3.2.1.2 MongoDB                                                                                                    | 35 |

|        |        | 3.2.1.3 MySQL                                                                                                      | 36 |

|        | 3.2.2  | Data-serving Benchmarks                                                                                            | 36 |

|        | 3.2.3  | Data-analytics Benchmarks                                                                                          | 37 |

|        | 3.2.4  | SPEC CPU2006 and SPEC CPU2017 Benchmarks                                                                           | 37 |

|        | 3.2.5  | Other Benchmarks                                                                                                   | 39 |

|        | 3.2.6  | GPU Benchmarks                                                                                                     | 39 |

| Chapte | r 4. P | PerfProx: Core-level Proxy Benchmarks for Emerging Work-<br>loads using Performance Counter Based Characterization | 41 |

| 4.1    | PerfPi | ox's Methodology                                                                                                   | 42 |

|        | 4.1.1  | Workload Characterization using Performance Counters                                                               | 43 |

|        | 4.1.2  | Synthetic Proxy Benchmark Generation                                                                               | 50 |

|        | 4.1.3  | Discussion                                                                                                         | 52 |

| 4.2    | Evalua | ation                                                                                                              | 53 |

|        | 4.2.1  | Experimental Setup                                                                                                 | 54 |

|        | 4.2.2  | Results and Analysis                                                                                               | 55 |

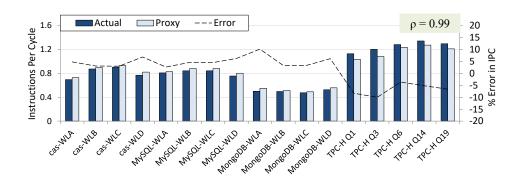

|        |        | 4.2.2.1 Performance Validation of Proxy Benchmarks                                                                 | 55 |

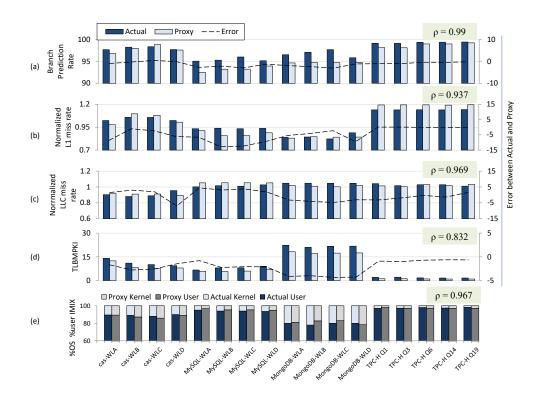

|        |        | 4.2.2.2 Proxy Cross-platform Validation                                                                            | 58 |

|        |        | 4.2.2.3 Proxy performance sensitivity analysis on different cache/TLB configurations                               | 60 |

|        |        | 4.2.2.4 Energy-efficiency Analysis                                                                                 | 63 |

|        | 4.2.3  | Comparison with standard benchmarking suites                                                 | 64  |

|--------|--------|----------------------------------------------------------------------------------------------|-----|

|        |        | 4.2.3.1 Degree of Miniaturization                                                            | 65  |

| 4.3    | Sumn   | nary                                                                                         | 66  |

| Chapte | r 5. ] | HALO: A Hierarchical Memory Access Locality Modeling Technique For Memory System Exploration | 67  |

| 5.1    | HALO   | O's Methodology                                                                              | 70  |

|        | 5.1.1  | Region Localization                                                                          | 71  |

|        | 5.1.2  | Intra-region Stride Locality Tracking                                                        | 72  |

|        | 5.1.3  | Inter-region Reuse Locality                                                                  |     |

|        | 5.1.4  | Proxy Generation Algorithm                                                                   | 78  |

|        | 5.1.5  | Execution Phase Consideration                                                                | 81  |

|        | 5.1.6  | Multi-programmed Workload Performance                                                        | 82  |

| 5.2    | Evalu  | ation                                                                                        | 82  |

|        | 5.2.1  | Experimental Setup                                                                           | 82  |

|        | 5.2.2  | Results and Analysis                                                                         | 84  |

|        | 5.2.3  | Sensitivity Studies                                                                          | 94  |

| 5.3    | Sumn   | nary                                                                                         | 95  |

| Chapte | r 6. ( | G-MAP: Statistical Pattern Based Modeling of GPU Memory                                      |     |

| _      |        | Access Streams                                                                               | 97  |

| 6.1    | GPU :  | Background                                                                                   | 98  |

| 6.2    | G-MA   | AP's Methodology                                                                             | 100 |

|        | 6.2.1  | Dynamic Memory Execution Profile                                                             | 102 |

|        | 6.2.2  | Inter-thread Memory Access Locality                                                          | 103 |

|        | 6.2.3  | Intra-thread Memory Access Locality                                                          | 104 |

|        | 6.2.4  | Control-flow Divergence                                                                      | 107 |

|        | 6.2.5  | Scheduling Policy                                                                            | 107 |

|        | 6.2.6  | Proxy Generation and Modeling                                                                | 108 |

| 6.3    | Evalu  | ation                                                                                        | 111 |

|        | 6.3.1  | Experimental Setup                                                                           | 111 |

|        | 6.3.2  | Results and Analysis                                                                         | 112 |

| 64     | Sumn   | 19rv                                                                                         | 117 |

| Chapter 7. CAMP: Accurate Modeling of Core and Memory Locality for |         |                                                                                                    |            |

|--------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------|------------|

| - 1                                                                | G 4 3 5 | Proxy Generation of Big-data Applications                                                          | 119        |

| 7.1                                                                |         | P's Methodology                                                                                    |            |

|                                                                    | 7.1.1   | Workload Profiling                                                                                 |            |

|                                                                    |         | 7.1.1.1 Instruction Locality Parameters                                                            |            |

|                                                                    |         | 7.1.1.2 Memory Locality Parameters                                                                 |            |

|                                                                    | 7.1.2   | Proxy Generation and Modeling                                                                      | 130        |

| 7.2                                                                | Evalua  | ation                                                                                              | 134        |

|                                                                    | 7.2.1   | Experimental Setup                                                                                 | 134        |

|                                                                    | 7.2.2   | Results and Analysis                                                                               | 135        |

| 7.3                                                                | Summ    | nary                                                                                               | 141        |

|                                                                    |         |                                                                                                    |            |

| Chapte                                                             | r 8. S  | ynthetic Workload Generation using Proxy Generator Fram work to Densely Cover Performance Spectrum | ie-<br>143 |

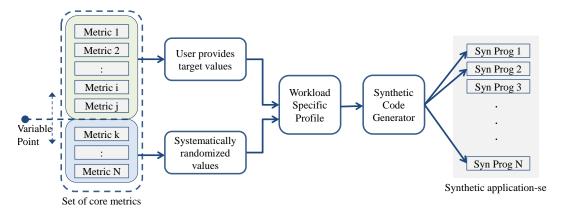

| 8.1                                                                | Genes   | sys's Methodology                                                                                  |            |

|                                                                    | 8.1.1   | Instruction-level Characteristics                                                                  |            |

|                                                                    | 8.1.2   | Control-flow Characteristics                                                                       |            |

|                                                                    | 8.1.3   | Memory-level Characteristics                                                                       |            |

|                                                                    | 8.1.4   | Genesys's Workload Generation Methodology                                                          |            |

| 8.2                                                                | Evalua  | ation                                                                                              |            |

|                                                                    | 8.2.1   | Experimental Setup                                                                                 |            |

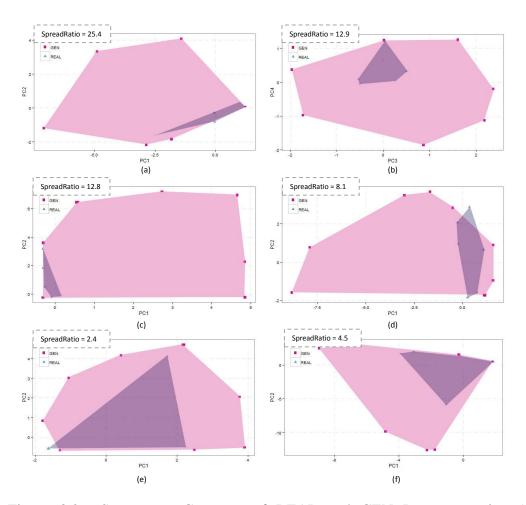

|                                                                    |         | Results: State-space Coverage                                                                      |            |

| 8.3                                                                |         | nary                                                                                               |            |

|                                                                    |         | ,                                                                                                  |            |

| Chapte                                                             | r 9. (  | Conclusion and Future Work                                                                         | 159        |

| 9.1                                                                | Summ    | nary                                                                                               | 160        |

| 9.2                                                                | Future  | e Work                                                                                             | 163        |

| Bibliog                                                            | raphy   |                                                                                                    | 165        |

| Vita                                                               |         |                                                                                                    | 180        |

# **List of Tables**

| 1.1 | of Cache and TLB Miss-rates                                            |

|-----|------------------------------------------------------------------------|

| 3.1 | Yahoo! Cloud Serving Benchmark (YCSB) Core Workloads 37                |

| 3.2 | TPC-H Benchmark Description                                            |

| 4.1 | PerfProx's Workload-specific Profile                                   |

| 4.2 | Systems used for Evaluating PerfProx's Cloning Accuracy 54             |

| 5.1 | Profiled Statistics for HALO Proxy Generation                          |

| 5.2 | HALO's Profiled System Configuration                                   |

| 6.1 | GPGPU Application Memory Access Patterns                               |

| 6.2 | Profiled System Configuration used for Collecting G-MAP Profiles . 111 |

| 7.1 | CAMP's Profiled Statistics                                             |

| 7.2 | Profiled System Configuration used for Collecting CAMP Profiles . 134  |

| 8.1 | Genesys' Workload Metrics                                              |

| 8.2 | Hardware Performance Features Used to Compare REAL and GEN Programs    |

# **List of Figures**

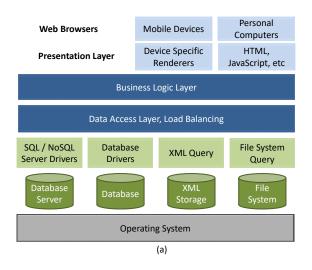

| 1.1 | Software Stack of a Typical Web-serving Engine                                                                             | 5  |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

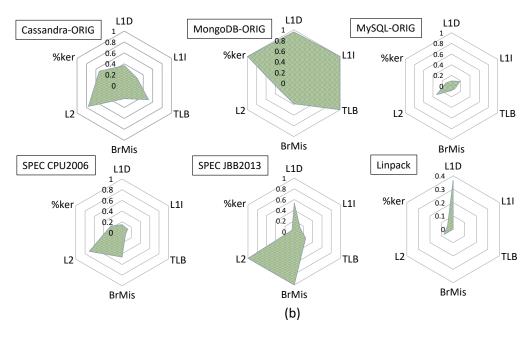

| 1.2 | Kiviat Plots Comparing Performance of Emerging Big-data Applications with Standard Benchmarks                              | 6  |

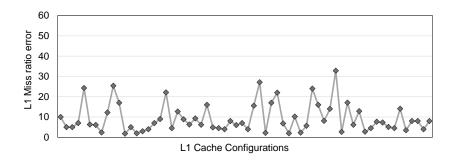

| 1.3 | L1 Miss-ratio Cloning Error of SDS Proxies for Various L1 Cache Configurations                                             | 9  |

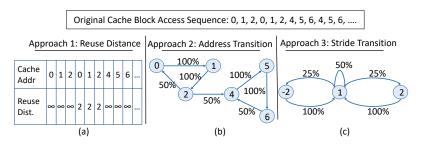

| 2.1 | Common Memory Access Locality Modeling Approaches                                                                          | 24 |

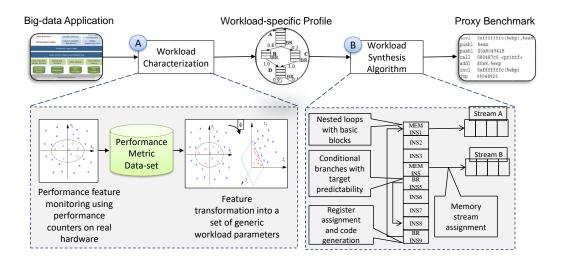

| 4.1 | PerfProx's Proxy Generation Methodology                                                                                    | 42 |

| 4.2 | IPC of Real Databases and Proxy Applications on System-A                                                                   | 56 |

| 4.3 | Comparison of Performance Features of Original and Proxy Applications on System-A. Error % on the Right-side Axis          | 57 |

| 4.4 | Proxies from System-A Validated on System-B: (a) IPC, (b) L2 MPKI, (c) LLC MPKI, (d) Branch Prediction Rate                | 59 |

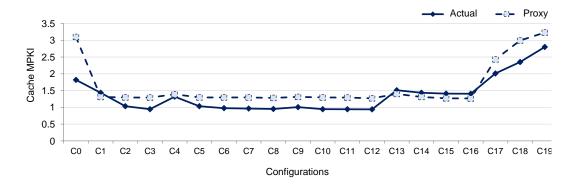

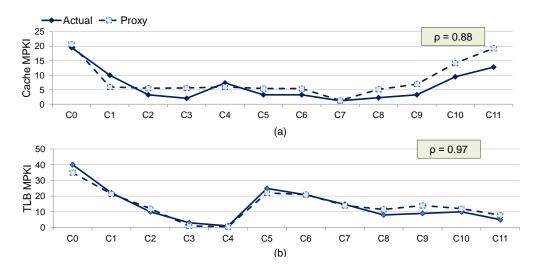

| 4.5 | Performance Sensitivity of Data-analytics (TPC-H Q19) Proxy to Different Cache Configurations                              | 61 |

| 4.6 | Sensitivity of Data-serving Proxy Performance to Different Cache and TLB Configurations                                    | 62 |

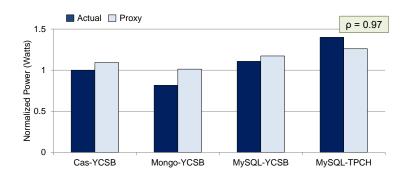

| 4.7 | Comparing Power Consumption of Proxy versus Actual Applications                                                            | 63 |

| 4.8 | Kiviat Diagrams Comparing Performance of Original Database Applications, Proxy Benchmarks and a Set of Standard Benchmarks | 65 |

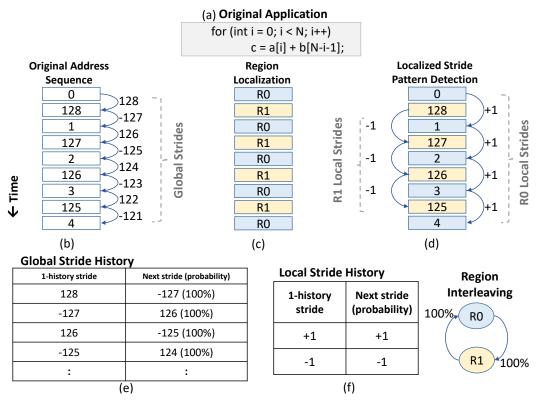

| 5.1 | Global versus Local Memory Access Pattern Tracking                                                                         | 69 |

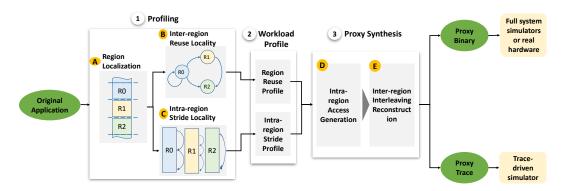

| 5.2 | HALO's Memory Locality Cloning Methodology                                                                                 | 71 |

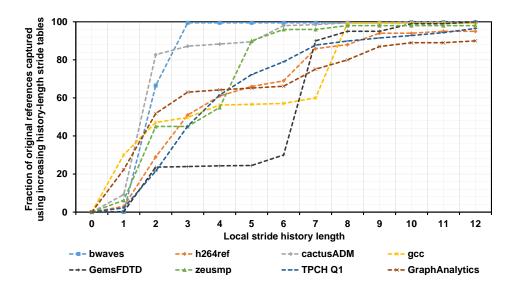

| 5.3 | Fraction of Original Reference Patterns Captured Using Increasing History-length Based Stride Tables.                      | 73 |

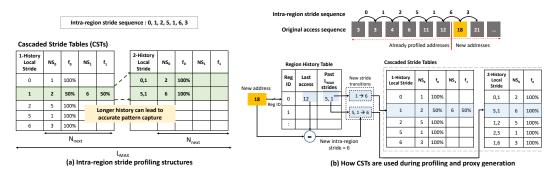

| 5.4 | Intra-region Locality Profiling using Cascaded Stride Tables (CSTs).                                                       | 74 |

| 5.5 | Inter-region Reuse Locality (Π Metric) Tracking                                                                            | 77 |

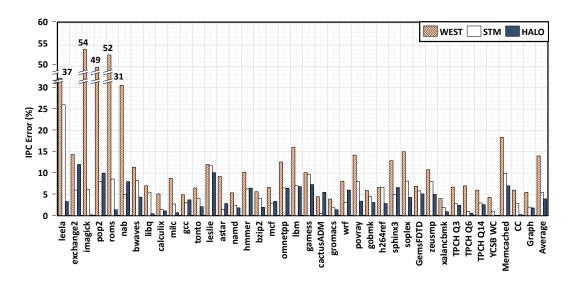

| 5.6 | Instructions per Cycle Error of WEST, STM and HALO Proxies versus the Original Applications                                | 85 |

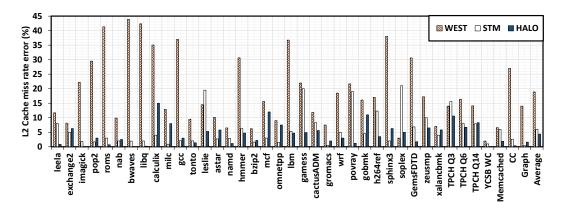

| 5.7 | L2 Miss-rate Errors of WEST, STM & HALO Proxies across L2 Cache and Prefetcher Configurations.                             | 86 |

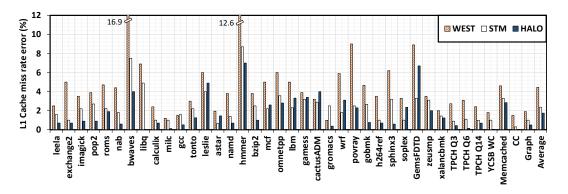

| 5.8  | L1 Miss-rate Errors of WEST, STM and HALO Proxies across L1 Cache and Prefetcher Configurations.               | 88  |

|------|----------------------------------------------------------------------------------------------------------------|-----|

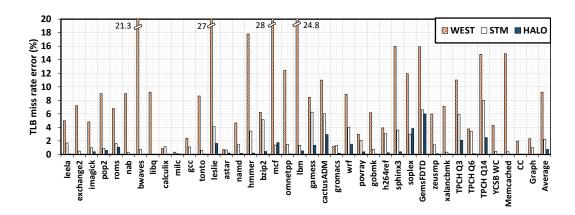

| 5.9  | TLB Miss-rate Errors of WEST, STM and HALO Proxies across Different TLB & Page-size Configurations.            | 90  |

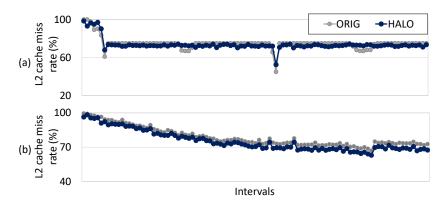

| 5.10 | Example Showing Phase-level Cache Performance Modeling for (a) GemsFDTD and (b) Graph Analytics                | 91  |

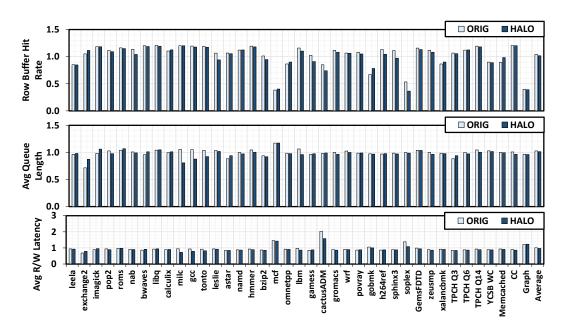

| 5.11 | Comparing DRAM Performance of HALO and Original Applications across Different DRAM Configurations              | 92  |

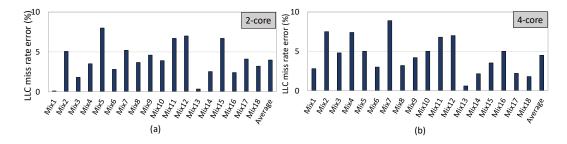

| 5.12 | Multi-programmed Performance Error of HALO Proxies for (a) 2-core and (b) 4-core Workload Mixes                | 93  |

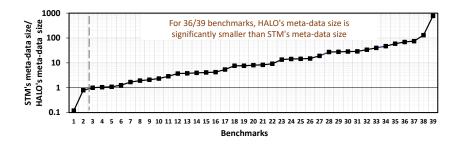

| 5.13 | Meta-data Size of HALO versus STM (Note Y-axis in Log-scale)                                                   | 94  |

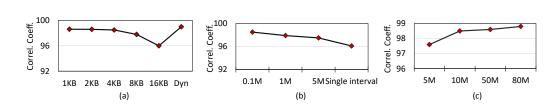

| 5.14 | Impact of Changing the (a) Region Size, (b) Profiling Interval Period, (c) Trace Length on Profiling Accuracy. | 96  |

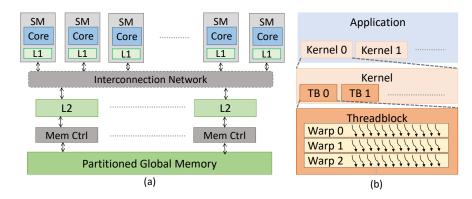

| 6.1  | (a) GPGPU Architecture (b) GPU Application Model                                                               | 99  |

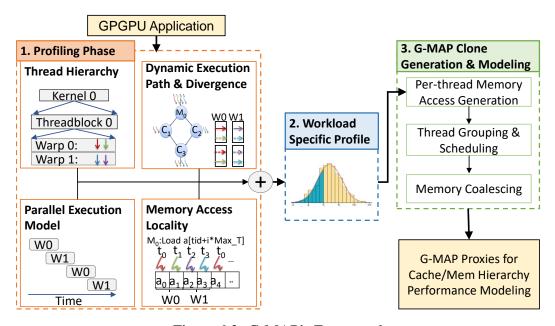

| 6.2  | G-MAP's Framework                                                                                              | 00  |

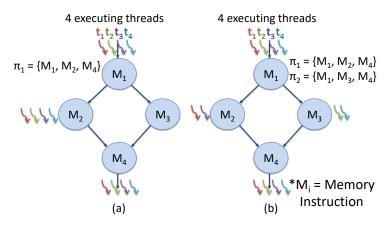

| 6.3  | Dynamic Memory Execution Profile Capture (a) Without and (b) With Control-flow Divergence                      | .02 |

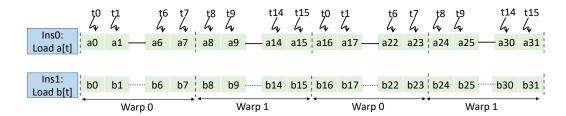

| 6.4  | Example Showing Intra-thread and Inter-thread Strides with Two Warps Adding Elements of Two Arrays             | .03 |

| 6.5  | Reuse Distance Computation Example                                                                             | 06  |

| 6.6  | Evaluating Cache, Prefetcher and Scheduling Policy Configurations using G-MAP Proxies: Error in Miss-rates     | .14 |

| 6.7  | DRAM Performance Evaluation using G-MAP Proxies                                                                | 16  |

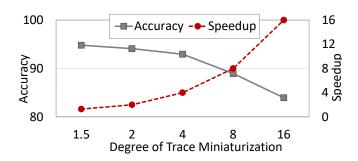

| 6.8  | Impact of Trace Miniaturization                                                                                | 17  |

| 7.1  | CAMP's Profiling and Proxy Generation Framework                                                                | 21  |

| 7.2  | Dependency Distance Computation Example                                                                        | 25  |

| 7.3  | STM-based Memory Locality Profiling                                                                            | 28  |

| 7.4  | Profiling for Write-back Requests                                                                              | 29  |

| 7.5  | DynInst Format                                                                                                 | 33  |

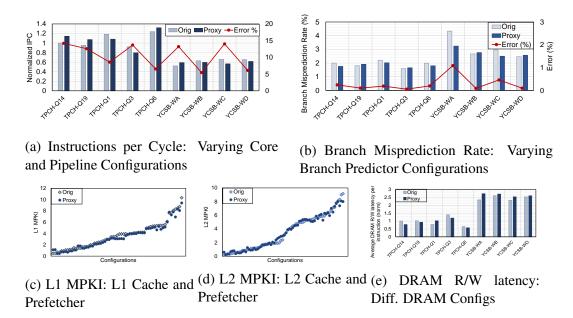

| 7.6  | Evaluating Core, Branch Predictor, Cache, Prefetcher and DRAM Configurations using CAMP Proxies                | .36 |

| 7.7  | Comparing L1 Miss-ratio Cloning Error Between CAMP and SDS Proxies for Various L1 Cache Configurations         | .39 |

| 7.8  | IPC Cloning Accuracy of CAMP versus SDS proxies                                                                | 39  |

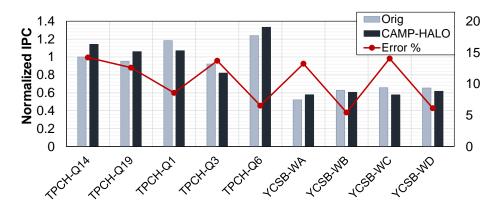

| 7.9 | IPC Cloning Accuracy of CAMP-HALO proxies versus Original Workloads                                                                                                                                                                    |   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 8.1 | Genesys's Overall Methodology and Framework                                                                                                                                                                                            |   |

| 8.2 | Example Synthetic Code Snippet                                                                                                                                                                                                         |   |

| 8.3 | State-space Coverage of REAL and GEN Programs using (a) Cache/memor Behavior - PC1 vs PC2 (b) Cache/memory Behavior - PC3 vs PC4 (c) TLB Behavior (d) Instruction-level Behavior (e) Control-flow Behavior (f) Overall Characteristics | • |

|     | Benavior (1) Overall Unaracieristics                                                                                                                                                                                                   |   |

## **Chapter 1**

## Introduction

Computer system design and research heavily relies on software simulation techniques to measure the performance of design alternatives and evaluate different design trade-offs. A processor simulator typically applies a workload and/or its input data-set to a model of the target processor's architecture and simulates the execution of individual instructions of the workload on the processor model, while recording its effect on various components of the underlying architecture.

Processor simulation tools range from microarchitectural-level performance simulators (e.g., Gem5 [13], Marssx86 [77]) to detailed register-transfer-level (RTL) models. RTL simulators simulate a very precise model of a processor that are sufficiently detailed to be manufactured. Modeling at such detailed abstraction levels ensures higher simulation accuracy, but it comes at the expense of significantly slow simulation speeds. On the other hand, performance simulators are generally higher-level and more versatile, and they can estimate program performance and statistics (e.g., number of branch mispredictions, various types of cache misses, TLB misses) with reasonably good accuracy at higher simulation speeds. Performance simulators can be further categorized into execution-driven simulators that execute a complete program binary (with or without an input data-set) on a performance

model and trace-driven simulators that execute a trace containing partial information about individual instructions and addresses. Different types of performance simulation models have been developed for solving different research and design problems, each model with its own simulation speed and accuracy trade-offs. Such models play a key role in performing design space exploration, evaluating new architectural ideas and identifying the performance bottlenecks of various designs by enabling architects to simulate representative target workloads.

The choice of workloads to simulate on a processor model depends on the class of applications that the architecture targets or the different features of the architecture that the designer wants to stress using the applications. Identifying the right set of workloads to simulate on a performance model is a very challenging problem. Small hand-written micro-kernels can be used to represent commonlyused algorithms in real-world applications, but such micro-benchmarks are often not comprehensive enough to be representative of the real target applications. A set of standard benchmarks are typically used for performing computer design space exploration. For example, Standard Performance Evaluation Corporation (SPEC) creates the popular SPEC CPU benchmarks (e.g., SPEC CPU2000 [92], SPEC CPU2006 [93], SPEC CPU2017 [94]), which represent the most commonly used general-purpose CPU applications and are widely used by computer architecture researchers and designers. The growth in complexity and popularity of datamanagement applications, fueled by the big-data revolution, has led to creation of a number of big-data benchmark suites such as the Cloudsuite [26], BigDataBench [31], Yahoo! Cloud Serving (YCSB) [18] and TPC-H [100] benchmarks. More

recently, graphics processing units (GPUs) have emerged as a popular computation platform for applications beyond graphics. Programmers exploit these massively parallel architectures in diverse domains (e.g., linear algebra and bio-informatics). This has led to several general-purpose GPU benchmark suite offerings such as Rodinia [17], Parboil [96], etc. Given the growing diversity and complexity of the applications that are run on modern-day systems, it is important to evaluate the architectural implications and performance/power efficiency of future computer designs when targeting such emerging applications and architectures.

Unfortunately, detailed performance evaluation and benchmarking of computer systems is a very challenging task. The growing complexity of modern workloads and computer systems pose even bigger challenges. For example, the slow speed of simulation models, the long-running nature of workloads, the complexity of software stacks of emerging workloads and confidentiality concerns regarding sharing end-user applications/data significantly limit the efficiency of early design space exploration studies. This dissertation focuses on developing techniques that can address the above challenges and help computer designers to have a better understanding of end-user workloads. The techniques rely on proxy benchmarking, i.e., replicating the performance behavior of end-user applications using miniaturized proxy benchmarks. The proxy benchmarks do not have complex software stack dependencies and can be used for computer design space exploration without compromising the privileged nature of software, while significantly reducing the simulation times. The presented proxy benchmarking techniques can improve the early design space exploration efficiency of emerging applications and architectures.

## 1.1 Problem Description

Data handling and management has become an integral component of all businesses, big or small. Every major industrial sector, be it health-care, scientificcomputing, retail, telecommunication or social networking generates large amounts of data every day. This has led to an unprecedented increase in the demand for efficient data handling systems and applications. While traditional data management systems were based on structured-query language (SQL) based relational databases, a new group of databases popularly known as NoSQL databases have recently emerged as competitive alternatives owing to their flexibility and scalability properties [37, 27, 18, 14]. Recent years have thus, seen a big surge in several such emerging application domains e.g., database applications, machine learning, business analytics etc. Big-data processing needs also challenge the capabilities of traditional computing systems to process the large amounts of data efficiently in terms of both performance and power. Thus, computer designers need to re-evaluate their design principles to target such emerging applications [26, 31, 67, 70]. However, it is very challenging to study the performance and power behavior of complex emerging applications by running them on early performance models. The following paragraphs summarize the key challenges and considerations affecting early design-space exploration efficiency.

The first challenge is that it is very difficult (and often impossible) to run many emerging applications on detailed performance models owing to the complex application software stacks and significantly long run times of such applications. Figure 1.1 shows the software stack of a typical web-serving engine, consisting of

Figure 1.1: Software Stack of a Typical Web-serving Engine

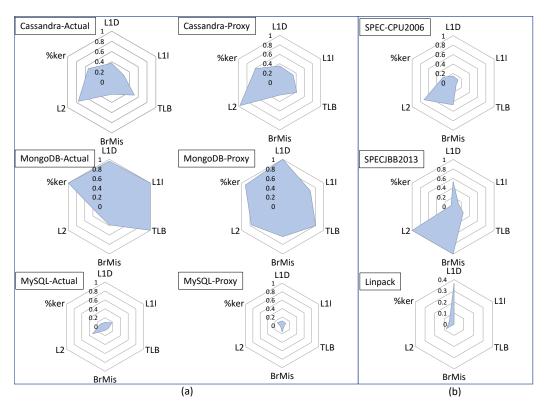

layers of complicated software levels interacting together to form the backbone of the engine. Running similar applications requires handling the complex software layers, back-end databases, third-party libraries, etc., which are quite challenging to support on most early performance models. Typically, a set of standard benchmarks [93, 92, 95, 100, 99] are used for performing computer performance evaluation. Benchmarks such as SPEC CPU2006 [93] and Linpack [36] are comparatively simpler targets for performance evaluation and are widely used by the computer architecture research community. Figure 1.2 compares the performance correlation between three emerging database applications (YCSB benchmarks running with Cassandra [16] and MongoDB [56] databases and TPC-H benchmarks running with MySQL [58] database) with three widely popular benchmark suites (SPEC CPU2006 [93], SPECjbb2013 [95] and Linpack [36]) across six key performance metrics: L1 data cache (L1D) misses per kilo instructions (MPKI), L1 instruction cache MPKI (L1I), last-level cache (LLC) MPKI and translation look-aside buffer

Figure 1.2: Kiviat Plots Comparing Performance of Emerging Big-data Applications with Standard Benchmarks

(TLB) MPKI, fraction of kernel instructions executed (%Ker) and branch misprediction rate (BrMis). The plots clearly illustrate that significant diversity exists in the performance and bottlenecks of the emerging applications and standard benchmarks [70, 67, 104]. On the other hand, the recently proposed big-data benchmarks (e.g., Cloudsuite and BigDataBench) suffer from a problem similar to those of the real-world applications; they rely on the ability of early performance models to support complex software stacks with back-end databases.

The next challenge affecting design space exploration is that simulation speeds are orders of magnitude slower than native execution. This severely limits the efficiency of extensive design space exploration studies. To complicate matters

further, most emerging applications have significantly long run times. For example, the average dynamic instruction counts of the YCSB benchmarks (with back-end Cassandra database) and the SPEC CPU2017 benchmarks are in the range of tens of trillions of instructions. Simulating even one such benchmark for a single design point can easily take anywhere between several days to several weeks to finish. Evaluating the entire design search space of a single architecture, on multiple benchmarks, will require up to thousands of simulation hours. That is equivalent to several months or even years of simulation on a single processor. Simulating large-scale processors running such complex applications is well beyond the capabilities of even the fastest and fanciest simulators, even on today's fast machines.

Finally, it is difficult to get access to many end-user applications due to confidentiality concerns regarding sharing software code or data. For example, such software may include weapons simulation, proprietary market trading algorithms, trade secrets or other sensitive data. Thus, on one hand, designers need in-depth insights into end-user workload behavior, and on the other hand, end users cannot reveal any significant information about their code to the designers due to the proprietary or confidential nature of their software/data.

#### 1.1.1 Limitations of Prior Research Work

A lot of research has been done to address the above challenges affecting efficient design space exploration of future computer designs. Benchmark sampling techniques such as simulation points [87] and SMARTS [108] have been proposed to reduce simulation time requirements of a benchmark. Such techniques analyze

phase-level redundancies within a single workload's execution and identify workload sub-sections to represent the overall execution behavior of the entire workload. By doing so, these techniques can address the long simulation time problem. However, they still suffer from the challenge of supporting complex application software-stacks on early performance models and they do not address the issue of proprietary end-user applications. Also, they rely on the capability of simulators to fast-forward execution until the interval of interest. Other techniques such as benchmark subsetting [79] have been proposed to identify a subset of benchmarks from a benchmark suite that can represent the performance behavior of all the benchmarks within the suite. However, the subset results are still whole programs and are still too big, complex and proprietary to be directly used with performance models.

A promising alternative to address the above challenges is proxy benchmarking. Proxy benchmarking is the process of extracting statistics that summarize the behavior of the end-user workloads through profiling and then using the statistics to synthesize a miniaturized representation of the proprietary workloads (called a "proxy" or "clone"). The proxy workloads can be used as miniaturized substitutes of the original workloads to perform early computer system performance evaluation, helping designers to understand the behavior of users' workloads in a reasonable time and without the users having to disclose sensitive information about the original workload.

Prior proxy generation proposals [42, 29, 43] utilize an extensive set of micro-architecture independent metrics that are derived from detailed functional simulators or profilers to synthesize the proxy benchmarks. Unfortunately, such

metrics are often very difficult to extract for many emerging applications that can not be supported on early simulation models or profilers. For example, several big-data workloads (e.g., Java-based Cassandra) do not work reliably with many detailed simulation models (e.g., gem5) or profiling tools (e.g., Pin [54], Valgrind). In such cases, it becomes impossible to apply prior proxy benchmark generation techniques to generate proxy benchmarks for such emerging applications.

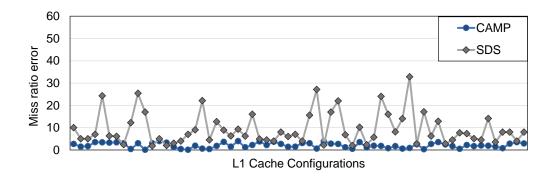

Furthermore, prior proxy generation techniques capture core-level locality metrics in detail, but abstract out memory locality modeling using very simple dominant stride-based models. As a result, these schemes suffer poor cloning accuracy in replicating performance behavior of applications with complex memory access patterns. For example, Figure 1.3 shows the L1 miss rate cloning error of proxies generated using the single dominant stride (SDS) approach (the most commonly used statistic in literature for modeling memory locality patterns in proxies), for a set of data-serving (YCSB) and data-analytics (TPC-H) benchmarks run against a back-end MySQL database. Figure 1.3's x-axis corresponds to different L1 cache

Figure 1.3: L1 Miss-ratio Cloning Error of SDS Proxies for Various L1 Cache Configurations.

configurations, where the cache size and associativity is varied between 16-64KB and 2-8 ways, respectively. It can be observed that the SDS proxies show significant errors in replicating the miss ratio versus the original applications (measured as the absolute difference in miss ratios) at several data points, reaching as high as 33% cloning error. This shows that the SDS approach is not suitable for modeling complex memory access patterns of big-data applications. Most big-data applications are highly data-intensive and their overall system-level performance is significantly impacted by the performance of the cache and memory hierarchy [26, 67]. As a result, prior performance cloning techniques are not very accurate at studying the overall performance of emerging big-data applications.

Several detailed cache and memory cloning techniques [7, 5] have also been proposed in the literature. WEST [7] models temporal locality of applications using per cache-set LRU stack distance distributions based on a baseline cache hierarchy. However, WEST does not model spatial locality behavior, making it inadequate for evaluating microarchitectural structures that exploit spatial locality e.g., prefetchers or the memory system (see Table 1.1 for the cloning error of WEST proxies for over 7000 different prefetcher-enabled last-level cache and TLB configurations across 39 big-data and SPEC CPU benchmarks). Spatio-temporal memory (STM) [5] cloning technique overcomes this limitation and models spatial locality by cap-

Table 1.1: Error between WEST Proxies and Original Applications in terms of Cache and TLB Miss-rates.

|               | LLC miss rates | TLB miss rates |

|---------------|----------------|----------------|

| Average Error | 19% (avg)      | 9.3% (avg)     |

| Maximum Error | 44% (max)      | 22% (max)      |

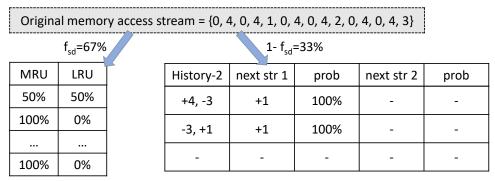

turing global stride-based correlations in the memory reference stream. However, the global stride transitions of many benchmarks cannot be captured even by using a stride history depth as long as ~80-100 [5]. Thus, STM has to maintain long histories in order to capture the dominant global stride transitions, which results in significantly higher meta-data storage overhead. Limiting the stride history depth can reduce storage overhead, but at the expense of significantly poor cloning accuracy. For example, limiting the history length to 40 causes STM proxies to experience up to 24% and 32% error in replicating the TLB miss rate and memory footprint of many big-data applications. Thus, the state-of-the-art memory behavior cloning proposals either model limited locality metrics (e.g., WEST) and suffer from poor cloning accuracy or are fairly accurate, but at the expense of significant meta-data overhead. Additionally, none of these techniques are suitable for modeling the memory access behavior of emerging architectures such as GPUs.

Finally, the above prior proxy generation techniques either model the instruction pipeline-level locality or the memory access locality in detail. However, none of them jointly model both core and memory reference behavior with high accuracy. As a result, they are not suitable for studying system-level performance of emerging applications. This dissertation explores techniques and methods that expand the frontiers of workload proxy benchmark synthesis through more accurate and efficient modeling of core and memory locality behavior of emerging applications and architectures. The proposed techniques can help computer designers to have a better and faster understanding of end-user workload behavior without compromising the privileged nature of software or data.

## 1.2 Overview of Proposed Research

# 1.2.1 Core-level Proxy Generation using Performance Counter Based Characterization

While prior system-level proxy benchmarking proposals [11, 43, 29] utilize micro-architecture independent metrics derived from detailed functional simulators for proxy generation, such metrics are often very difficult to generate for many emerging applications. However, it is possible to characterize these workloads based on performance counters. To enable proxy benchmark synthesis for complex, emerging applications that do not work with many simulation models or profiling tools, this dissertation first presents a core-level proxy benchmark synthesis methodology, PerfProx [69, 71], which leverages performance metrics derived from hardware performance counter measurements to create miniature system-level proxy benchmarks. First, the key drivers of big-data application performance (larger code footprints, operating system effects, and other run-time effects, etc.) are identified. Such effects are often not highly significant in traditional desktop or generalpurpose applications and thus, are not modeled by prior workload cloning proposals. Then, PerfProx captures the identified performance metrics using hardware performance counters and stochastically models them to create miniaturized proxy benchmarks. The proxy benchmarks replicate the performance behavior of realworld cloud applications, including operating system and run time effects, and yet converge quickly without needing any complex software stack support. Several bigdata workloads do not work reliably with many profiling tools, thus performancecounter based characterization and associated extrapolation into generic parameters for the code generator enables fast (runs almost at native hardware speeds, unlike prior workload cloning proposals) and efficient proxy generation for such benchmarks with reasonable accuracy.

#### 1.2.2 Memory Locality Modeling using Hierarchical Pattern Detection

Prior state-of-the-art memory locality modeling proposals [5] create memory proxies by extracting patterns within the global stream of memory references. However, the global memory access streams of applications are shaped by a number of different factors - data-dependent control-flow, high-level algorithms that access different data-structures in the program, data-structure access interleaving, memory layout of data-structures determined by the compiler/runtime and the machine's execution model (out-of-order versus in-order execution, memory address reordering, etc.). As a result, distilling the inherent patterns in the global memory access streams into a small set of statistics is very challenging.

This dissertation argues that memory access locality can be more accurately and succinctly captured by learning patterns at a localized granularity for many applications. With localization, memory addresses are ideally grouped according to some inherent property of programs and data accesses (e.g., code-based, address-region based, time-based), which make the resulting localized streams more predictable. For example, code-based localization exploits the fact that different memory instructions or PCs perform different functions versus other memory instructions, which get executed around the same time. This dissertation presents a novel class of memory proxy generation techniques [74] that exploit pattern detection and modeling at localized granularity to accurately replicate application cache and

memory behavior of different applications.

The first memory access locality modeling technique (HALO) exploits addressregion localization based pattern tracking to create miniature memory access proxies. HALO discovers patterns by first decomposing an application's memory accesses into a set of independent streams that are constrained to a smaller region of memory and then capturing fine-grained access patterns within localized regions using repeating stride transitions. This allows the representation of complex workloads through the composition of a set of smaller and simpler building blocks. Additionally, different programs have different locality behavior. HALO exploits this observation to achieve higher meta-data storage efficiency by capturing multi-level stride transitions, which are tailored to an application's locality patterns. However, modeling locality within individual streams alone is not sufficient to recreate the original application's memory behavior. There must be a mechanism to combine accesses from these decomposed streams to synthesize an ordered proxy sequence. HALO models this by tracking how accesses to the localized streams are interleaved with respect to each other by using coarse-grained temporal locality tracking. By accurately modeling the spatial locality, temporal locality and memory footprint of application, HALO proxies can replicate the cache and memory performance of applications even with complex memory access patterns.

However, this approach is not sufficient to model the cache and memory access behavior of emerging architectures such as GPUs. GPUs leverage large amounts of parallel hardware combined with light-weight context switching among thousands of threads to hide the impact of long memory latencies. To model the

memory locality of GPU applications, it is important to model the effects of thread-level parallelism on the cache and memory hierarchy. This dissertation extends workload cloning techniques to GPUs and presents G-MAP [76], a novel method-ology and framework to statistically model the inherent memory access locality and parallelism of GPU applications to create miniaturized GPU memory proxies. G-MAP exploits code-based correlations to model cache and memory locality behavior of GPU applications, while also accounting for GPU's parallel execution model.

### 1.2.3 System-level Proxy Benchmark Synthesis

Finally, the above techniques (and the prior work in proxy generation) can accurately model either the compute-instruction behavior or the memory access behavior. However, none of the prior cloning studies accurately model the joint performance of both core and memory subsystems and their complex interactions. In reality, the processor core configuration and the application together determine processor core performance, which in turn affects the timing of requests received in the memory system. At the same time, memory performance has a feedback loop with processor performance, which in turn affects the timing of other memory requests and, the overall performance of the application. As a result, the prior workload cloning proposals can not be used for studying overall system-level application performance. However, it would be useful to have easy-to-use and representative benchmarks to study overall system-level performance of emerging applications.

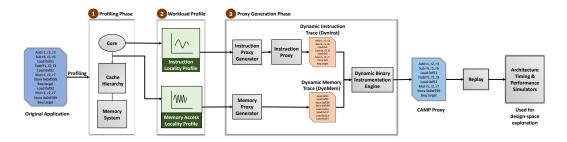

This dissertation presents a novel system-level proxy generation and model-

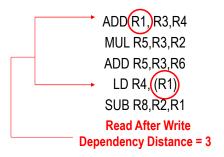

ing methodology (CAMP) that accurately models both core performance and memory locality to create miniature proxy benchmarks [73]. To model the processor core performance, the proposed technique captures and models dependencies between instructions (instruction-level parallelism), instruction types, control-flow behavior, etc. An improved memory locality profiling approach is added that accurately captures both the spatial and temporal locality of applications. However, most big-data applications typically do not have a single dominant stride/offset based access pattern. Thus, it is quite difficult to control the different dynamic execution instances of the low-level, static load/store instructions in the proxy benchmark to reproduce the complex memory access patterns of the original applications using synthetic data-structure accesses in the proxy code. To overcome this challenge, this dissertation introduces a novel proxy modeling and replay methodology that integrates the core and memory locality models to create accurate system-level proxy benchmarks.

#### 1.2.4 Synthetic Workloads to Cover Workload Performance Spectrum

Traditionally machines for tomorrow are built using benchmarks of today, which are workloads of yesterday. It is desirable to have benchmarks that model futuristic workloads so that future systems can be designed and tuned to work well for such workloads. This dissertation proposes a synthetic benchmark generation methodology, Genesys that systematically tweaks the program characteristics, used as an input to the proxy generation framework, to produce new hypothetical workloads with performance behavior that does not currently exist. Also, the set of programs included in a standard benchmark suite is limited and the benchmarks of-

ten fill only certain data-points in the workload spectrum (most of the spectrum is not represented). Genesys proxies can be generated to cover anticipated code trends and can represent futuristic workloads before the workloads even exist.

#### 1.3 Thesis Statement

Hierarchically capturing both spatial and temporal locality in the application memory streams using inter-region and intra-region access patterns improves the accuracy of modeling memory access behavior of complex emerging applications. Accurately capturing memory access locality and modeling other important features (e.g., system activity) creates more accurate and representative proxy benchmarks. Execution-related metrics can be used for generating proxies of emerging applications, which do not work with conventional profiling tools.

#### 1.4 Thesis Contributions

This dissertation makes several contributions to accurate memory locality and core performance modeling of emerging applications and architectures. The key contributions of this dissertation are summarized as follows.

- To simplify benchmarking of big-data data-serving and data-analytics workloads on early performance models, this dissertation propose to generate miniature, representative proxy benchmarks that do not need any complex software-stack or back-end database support.

- This dissertation presents a core-level proxy benchmark generation method-

ology, which enables fast and efficient proxy generation for emerging big-data applications using performance metrics derived primarily from hardware performance counters. The proxy benchmarks are representative of the performance of the emerging, real-world applications and yet converge to results quickly and do not need any complex software stack support. The presented approach is evaluated using three modern, real-world SQL and NoSQL databases (Cassandra, MongoDB and MySQL) running the data-serving and data-analytics applications on different hardware platforms and with different cache/TLB configurations. The proxy benchmarks closely mimic the performance of the original database applications, while significantly reducing the instruction counts.

• To enable fast and efficient design space exploration of futuristic memory hierarchies, this dissertation next proposes a hierarchical memory access locality modeling technique that identifies patterns in the original memory reference stream by isolating the global memory references into several localized streams and further zooming into each local stream capturing multigranularity spatial locality patterns. The interleaving degree between localized stream accesses is modeled by leveraging coarse-grained reuse locality patterns. The presented technique is evaluated using over 20,000 different memory system configurations and it achieves over 98.3%, 95.6%, 99.3% and 96% accuracy in performance behavior of replicating prefetcher-enabled L1 & L2 caches, TLB and DRAM performance, respectively. It also outperforms the state-of-the-art memory cloning schemes, WEST and STM, while

using  $\sim$ 39X less meta-data storage than STM.

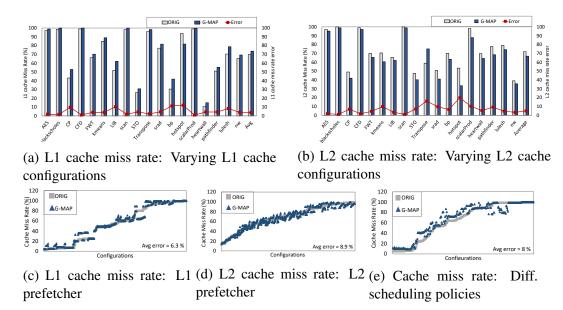

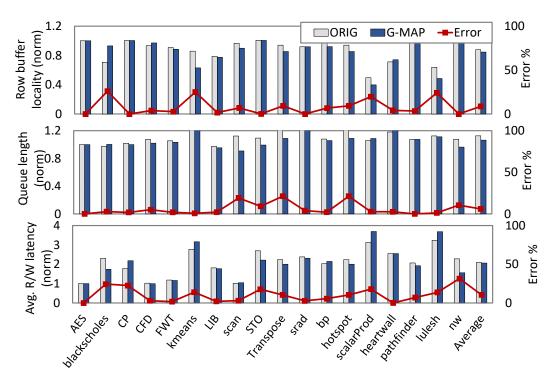

- To enable efficient GPU memory system exploration, this dissertation presents a novel methodology and framework that statistically models the GPU memory access stream locality by exploiting the synergy in code-localized access patterns (within and across threads) to create miniature memory access proxies. To account for the parallel execution model of GPUs, a fine-grained, coordinated scheduling policy is also adopted to ensure appropriate parallelism at the thread-level and cache/memory-level. Extensive evaluation using 18 benchmarks from Rodinia [17], CUDA SDK [62] and Ispass09 [6] benchmark suites shows that the presented technique can mimic the performance of the original GPU workloads with over 90% accuracy across over 5000 L1-cache, L2-cache, prefetcher and DRAM memory configurations.

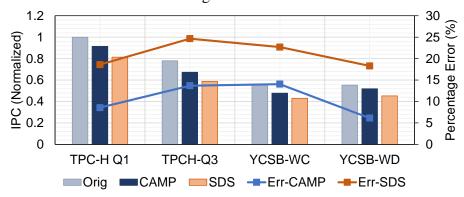

- The next proposal focuses on synthesizing accurate and representative system-level proxy benchmarks for emerging applications, by modeling both coreperformance and memory locality accurately along with modeling the feed-back loop between the core and memory performance. Core performance is modeled by capturing metrics such as instruction-level parallelism, control-flow behavior, etc. An improved memory locality profiling approach is added that captures both the spatial and temporal locality of applications. Finally, a novel proxy generation and replay methodology is introduced that integrates the core and memory locality models together to create accurate system-level proxy benchmarks. Using extensive evaluation on a set of big-data database

applications, it is demonstrated that the proxies can mimic the original application's overall performance behavior fairly accurately with an average cloning error of 11%. This is a new capability that can enable accurate overall system (core and memory subsystem) design exploration.

• Finally, this dissertation proposes a technique to exploit the synthetic workload generator framework to produce hypothetical workloads before the workloads even exist in order to densely cover the workload performance spectrum. It achieves this by systematically tweaking statistics used as an input to the synthetic workload generator in a systematic manner to produce new hypothetical workloads with performance behavior that does not currently exist.

# 1.5 Thesis Organization

This dissertation is organized as follows. Chapter 2 provides background about prior proxy benchmark generation and other simulation time reduction techniques. Chapter 3 presents the evaluation framework used in this dissertation and explains the set of benchmarks that were used. Chapter 4 presents details of the proxy generation framework that exploits performance-counter based characterization to generate miniature proxy benchmarks for big-data applications. Chapter 5 presents the hierarchical memory locality modeling approach for generating miniature proxy benchmarks targeting CPU applications. Chapter 6 extends the hierarchical memory locality modeling approach for GPU architectures while adding accountability of GPU's parallel execution model. Chapter 7 presents a unique

methodology to combine an accurate memory locality modeling framework with core behavior modeling methodology to create proxy benchmarks which model both core & memory behavior as well as the feedback loop between the two. Chapter 8 presents a methodology to create hypothetical benchmarks by systematically tweaking the workload statistics used as inputs to the proxy generation framework. Chapter 9 concludes this dissertation with a summary of the contributions of the dissertation and suggestions for future research opportunities.

# Chapter 2

## **Related Work**

This chapter provides an overview of the state-of-the-art research underlying this dissertation. Broadly, the prior workload cloning proposals can be categorized into techniques that capture detailed cache and memory level behavior of applications and techniques that model detailed core-level performance behavior. The following sections first discuss the respective proxy benchmarking proposals and then highlight a few other simulation time reduction techniques.

# 2.1 Schemes for Modeling Cache and Memory Performance

The memory reference stream of an application is affected by several factors: high-level algorithms that access different data-structures in the program, memory layout of data-structures determined by the compiler or runtime, program's unique control-flow, machine's execution model (out-of-order versus in-order execution, memory address reordering). As a result, distilling the inherent locality patterns in the memory access streams into a small set of statistics is a very challenging problem. A common approach to capture memory behavior is to start from a model of reference locality. The principle of locality asserts that, whenever a memory address is referenced, the address itself (temporal locality) or addresses

near it (spatial locality) are likely to be referenced again soon [90]. Most prior workload cloning approaches exploit some form of these two kinds of locality to model memory access patterns.

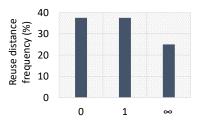

Reuse distance is an effective model of temporal locality [55, 64, 20, 7, 107]. It is calculated as the number of unique elements accessed between successive accesses to the same element. Figure 2.1a shows an example of reuse distance computation for the sequence of accesses shown in the figure at cacheline granularity (∞ represents access to a new cacheline). The captured reuse distance distribution can be used to synthesize a trace clone (e.g., {7, 12, 1, 7, 12, 1, 32, 0, 100, 32, 0, 100 ...}), which has the same reuse behavior. However, the synthesized trace sequence does not model the spatial locality behavior of the original sequence and cannot be used for evaluating prefetchers, DRAM, memory footprint. Another approach to model memory access locality is to capture spatial/temporal locality patterns using address or stride transition graphs. An address transition graph records every unique memory address as a node, and each edge connects an address to its successors (see Figure 2.1b). We can observe that while some cache-blocks have a single follower (e.g., 0), others have multiple followers (e.g., 2). The transitions recorded in the graph can be followed to generate a proxy trace. However, the space requirement for saving this graph is often prohibitive. Using stride transition graphs allows us to capture similar patterns in a more compact form (see Figure 2.1c). Nonetheless, longer stride history length correlations need to be exploited for achieving higher accuracy, which makes the storage requirements for capturing global stride transitions also significant.

Figure 2.1: Common Memory Access Locality Modeling Approaches

WEST [7] is a state-of-the-art data cache performance cloning framework. Based on a baseline L1/L2 cache hierarchy configuration, WEST captures temporal locality patterns using per cache-set LRU stack distance distribution for every level of the profiled cache hierarchy. Each cache-set's stack distance distribution captures the percentage of memory references to the corresponding LRU stack position. WEST also tracks other statistics such as access distribution across different sets, per-set read-write distribution to every stack position. To generate a memory proxy, WEST stochastically samples the stack distance statistics and generates accesses to the chosen cache sets and ways one-by-one. However, WEST's statistics are tightly tied to the profiled cache configuration. Thus, significant deviation between the profiled and test configurations (e.g., cacheline size) leads to poor cloning accuracy. Furthermore, WEST does not model spatial locality patterns, and thus WEST proxies are inadequate to study effects of microarchitectural structures that exploit spatial locality (e.g., prefetchers [68, 45, 91]). Finally, the meta-data overhead of capturing WEST's statistics is proportional to the size of profiled cache hierarchy. Although it is manageable for L1/L2 caches (relatively smaller size), the overhead is high for typically-sized last-level or DRAM caches.

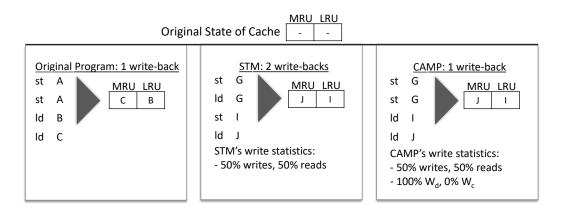

Spatio-Temporal Memory (STM) [5] is another state-of-the-art workload cloning proposal that captures an application's spatial and temporal locality behavior to create memory proxies. STM tracks temporal locality using per cache-set LRU stack distance distribution of a baseline L1 cache (like WEST). For the references that miss in the profiled L1 cache, STM captures their spatial locality patterns by learning global stride transitions (strides following a history of past M strides) in a global stride history table. Since STM captures stride transitions over the global memory sequence, it has to maintain long stride histories to accurately capture dominant patterns. Past research has shown that a history length of as long as  $\sim 100$  is insufficient to capture the access locality of many SPEC CPU2006 benchmarks (e.g., h264ref, wrf, etc.) [5]. Maintaining long history based stride tables significantly increases STM's meta-data storage overhead, which is a key limitation of STM in terms of portability. Limiting the history length can reduce the meta-data overhead, but it increases aliasing in the stride history table resulting in poor cloning accuracy. Furthermore, STM's reliance on a per-set LRU stack distance profile for capturing tight temporal locality patterns causes performance inaccuracies when the target L1 configurations differ from the baseline assumption.

Bell et al. [11], Joshi et al. [43] and Ganesan et al. [29] create workload clones by modeling instruction-level behavior, while modeling memory patterns using a single dominant stride for every load and store instruction. Because of this simplified assumption, these approaches suffer from poor cloning accuracy, especially when modeling complex access patterns of emerging big-data workloads. MEMST [8] clones DRAM performance by modeling statistics such as bank con-

flict behavior, row buffer hit ratio, etc. and is tightly tied to the profiled DRAM parameters. Metoo [106] generates workload clones by replicating memory traffic timing behavior, but the memory addresses are based on WEST's methodology.

While the above approaches model performance of some elements of the memory hierarchy, the proposed cloning techniques are the first to capture enough spatial and temporal features to model the performance of multi-level caches, prefetchers, TLB and main memory. Also, the state-of-the-art techniques can model memory access locality of CPU applications, but no such solutions exist for cloning GPU memory access patterns. This dissertation also proposes a novel framework to model memory access locality of GPU applications.

# 2.2 Schemes for Modeling Core-level Performance

Oskin et al. [65] and Eeckhout et al. [22] introduced the idea of statistical simulation. The approach used in statistical simulation is to generate a short synthetic trace from a statistical profile of workload attributes such as basic-block distribution, branch misprediction rate, data/instruction cache miss rates, instruction mix, dependency distance and then simulate the synthetic trace using a statistical simulator. Eeckhout et al. [23] improved statistical simulation by profiling workload attributes at a basic block granularity using statistical flow graphs. Bell et al. [11] improved upon the statistical framework proposed by Eeckhout et al. [22] by profiling applications at runtime and extracting several execution-related metrics to automatically create proxy workloads. Joshi et al. [43, 42] and Ganesan et al. [29] cloned proprietary applications into synthetic proxies for single core systems by ex-

tracting micro-architecture independent attributes only. Ganesan et al. [30] added support for generating proxy workloads for multi-threaded applications.

Prior synthetic generator proposals leverage detailed micro-architectural simulators to perform detailed workload characterization. Also, most prior workload cloning studies have focused on general-purpose applications like SPEC CPU2000 [92], SPEC CPU2006 [93] or embedded benchmarks like Implantbench [40]. However, many emerging applications cannot be reliably run and profiled on detailed micro-architectural simulators till completion. Techniques presented in this dissertation enable fast and accurate proxy generation for such complex, emerging workloads by monitoring their complete execution characteristics (with complex software stacks) on real systems using hardware performance counters.

## 2.3 Techniques for Modeling GPU Workload Performance

Early design space exploration of GPU architectures is traditionally done using detailed, cycle-accurate simulators [6, 80]. Although accurate, simulator speeds are often very slow, which limits efficiency of extensive design space exploration. A few researchers have also proposed analytical models to estimate GPU cache performance. To model L1 cache miss rate, Tang et al. [97] applied reuse distance theory on a single thread-block on a single core by arguing that there is limited reuse across different thread-blocks. Nugteren et al. [61] proposed another GPU L1 cache model. They collected per-warp memory traces and emulated inter-warp parallelism using round-robin scheduling policy before applying an extended reuse distance model (considering cache latencies, MSHRs, etc.). Although such models

are fast, their scope is limited to L1 cache performance modeling. In contrast, this dissertation presents a novel performance cloning framework (G-MAP) that can allow extensive exploration of different levels of the GPU memory hierarchy. Other GPU analytical modeling proposals [35, 89] focus on core performance, while using simple abstractions to model memory performance.

Yu et al. [109] proposed a GPU application cloning technique by replicating the instruction mix, control-flow, divergence behavior. Deniz et al. [19] proposed another GPU benchmark synthesis framework by replicating GPU application features such as the instruction throughput, compute resource utilization. Both these studies focus primarily on mimicking instruction-level characteristics, while they capture memory access patterns using abstract and simple models.

# 2.4 Other Techniques for Reducing Simulation Time