# **DISCLAIMER:**

This document does not meet the current format guidelines of the Graduate School at The University of Texas at Austin.

It has been published for informational use only.

Copyright by Qiu Zhao 2014 The Dissertation Committee for Qiu Zhao Certifies that this is the approved version of the following dissertation:

## THERMO-MECHANICAL STRESS MEASUREMENT AND ANALYSIS IN THREE DIMENSIONAL INTERCONNECT STRUCTURES

**Committee:**

Paul S. Ho, Supervisor

Alexander A. Demkov

Li Shi

Maxim Tsoi

John Keto

## THERMO-MECHANICAL STRESS MEASUREMENT AND ANALYSIS IN THREE DIMENSIONAL INTERCONNECT STRUCTURES

by

Qiu Zhao, B.S.;M.A.

## Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements

for the Degree of

## **Doctor of Philosophy**

The University of Texas at Austin December 2014

## Dedication

To my beloved parents and my wife, Xinshan

## Acknowledgements

I would like to express my sincere gratitude to my research advisor, Prof. Paul S. Ho, for his advice, guidance, and endless support for my research in the Laboratory for Interconnect and Packaging. His keen insight and commitment to research has and will continue to inspire me in my professional endeavors. I have to extend my heartfelt thanks to Dr. Rui Huang for his wisdom, guidance in the past a few years. He has been a source of inspiration and encouragement.

I am indebted to Dr. Jang-hi Im who has helped me in many aspects of my research and life. This work would not have been accomplished without his guidance and encouragement.

The work described herein would not have been possible without the support of my friends and colleagues. Special thanks go to Dr. Suk-Kyu Ryu. He has extended my vision to the world of mechanics and has helped me on the simulation work.

Finally, I'd like to deeply appreciate my parents, Liyan Wang and Guochao Zhao, for their boundless love and support throughout my education. I am also grateful to my wife, Xinshan Lu, from the bottom of my heart for her love, trust, understanding, and support.

## THERMO-MECHANICAL STRESS MEASUREMENT AND ANALYSIS IN THREE DIMENSIONAL INTERCONNECT STRUCTURES

Qiu Zhao, Ph. D

The University of Texas at Austin, 2014

Supervisor: Paul S. Ho

Three-dimensional (3-D) integration is effective to overcome the wiring limit imposed on device density and performance with continued scaling. The application of TSV (Through-Silicon Via) is essential for 3D IC integration. TSVs are embedded into the silicon substrate to form vertical, electrical connections between stacked IC chips. However, due to the large CTE mismatch between Silicon and Copper, thermal stresses are induced by various thermal histories from the device processing, and they have caused serious concerns regarding the thermal-mechanical reliability.

Firstly, a semi-analytic approach is introduced to understand stress distributions in TSV structures. This is followed by application of finite element analysis for more accurate prediction of stress behavior according to the real geometry of the sample. The conventional Raman method is used to measure the linear combination of in-plane stress components near silicon top surface Secondly, the limitation of conventional Raman method is discussed: only certain linear combination of in-plane stress, instead of separate value for each stress components, can be obtained. Two different kinds of innovative Raman measurements have been developed and employed to study the normal stress components separately. Both of them take advantages of different laser polarization profiles to resolve the normal stress components separately based on experimental data. The top-down Raman measurements utilize so called "high NA effect" to obtain additional information, and can resolve all 3 normal stress components. Independent bending beam experiments are used to validate the results from cross-section Raman measurement on the same sample. The correlation between top-down Raman measurement and cross-section Raman measurement are investigated as well.

Lastly, as a typical example of 3D IC package, a stack-die memory package is presented. Finite element analysis combined with cross-section Raman measurement and high resolution moiré interferometry were employed to investigate the thermalmechanical reliability and chip-package interaction of the stack-die memory structure.

## **Table of Contents**

| List of Tables xi                                                                                               |

|-----------------------------------------------------------------------------------------------------------------|

| List of Figures xii                                                                                             |

| Chapter 1 Introduction                                                                                          |

| 1.1 Background and motivation1                                                                                  |

| 1.1.1 Conventional interconnects and packaging methods1                                                         |

| 1.1.2 Cu/low-k interconnect2                                                                                    |

| 1.2 3-D integration with through-silicon Vias (TSVs)                                                            |

| 1.2.1 Process flow for TSV fabrication6                                                                         |

| 1.2.2 Reliability concerns in TSV structure7                                                                    |

| 1.3 Scope of this thesis9                                                                                       |

| Chapter 2 Near-Surface stress measurement with conventional raman measurement                                   |

| 2.1 Underlying theory of Raman spectroscopy11                                                                   |

| 2.2 Effect of stress on the Raman modes of Silicon                                                              |

| 2.3 Experimental descriptions                                                                                   |

| 2.4 Analysis of near-surface stresses17                                                                         |

| 2.5 Comparison between Raman and FEA results                                                                    |

| 2.6 Residual stress in oxide                                                                                    |

| 2.7 Characterization of via stress field interaction                                                            |

| 2.8 Summary                                                                                                     |

| Chapter 3 Extension of micro-Raman spectroscopy for full-component<br>stress characterization of TSV structures |

| 3.1 Top-down Raman measurement for full stress components determination                                         |

| 3.1.1 Secular equation in sample coordinates system                                                             |

| 3.1.2 Raman measurements with high numerical aperture (NA)<br>Configuration                                     |

| 3.1.3 Laser power, accumulation time optimization37                                                             |

| 3.1.4 Experimental design and results                                                                           |

| 3.1.5 Analysis and validation                                                                                            | 42 |

|--------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 Cross-section Raman measurements                                                                                     | 45 |

| 3.2.1 Secular equation for cross section Raman measurements                                                              | 45 |

| 3.2.2 Experimental samples and sample preparation                                                                        | 48 |

| 3.2.3 Experimental results, FEA simulations and analysis                                                                 | 50 |

| 3.3 Bending beam experiments                                                                                             | 55 |

| 3.4 Correlation between Raman measurement using high NA effect<br>and cross-section Raman measurement                    | 59 |

| 3.5 Summary                                                                                                              | 60 |

| Chapter 4 Thermo-mechanical reliability of stack-die memory package                                                      | 62 |

| 4.1 Introduction                                                                                                         | 62 |

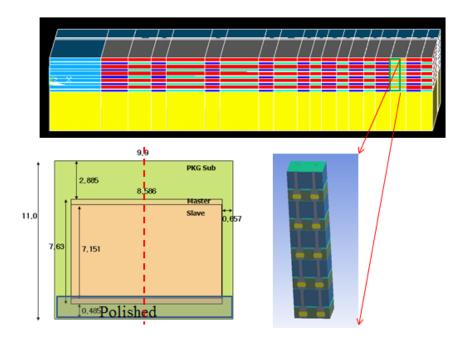

| 4.2 Test structures                                                                                                      | 62 |

| 4.3 Finite element method for Stack-die memory structures                                                                | 64 |

| 4.3.1 Secular equation for cross section Raman measurements                                                              | 64 |

| 4.3.2 Modeling of stack-die memory structure                                                                             | 71 |

| 4.4 Package level deformation                                                                                            | 73 |

| 4.5 Impact of CPI on stress/strain distribution around TSV                                                               | 74 |

| 4.6 Characterization of thermo-mechanical behavior of stack-die memory package with high resolution moiré interferometry | •  |

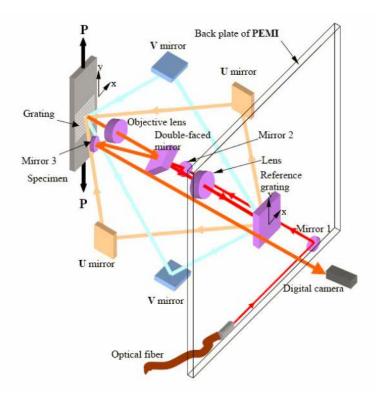

| 4.6.1 Regular moiré interferometry                                                                                       | 78 |

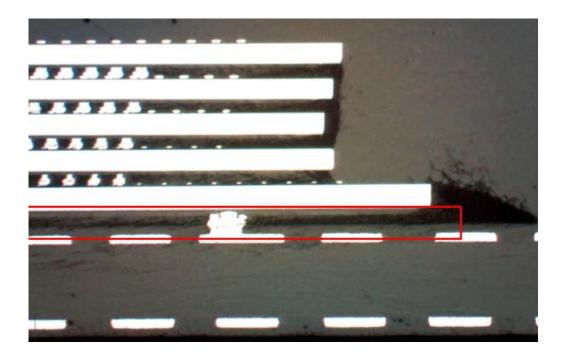

| 4.6.2 Sample preparation and measurement                                                                                 | 79 |

| 4.6.3 Results and discussion                                                                                             | 81 |

| 4.6.4 High resolution moire interferemetry                                                                               | 81 |

| 4.7 Summary                                                                                                              | 86 |

| Chapter 5 Conclusion and Outlook                                                                                         | 87 |

| 5.1 Conclusion                                                                                                           | 87 |

| 5.2 Outlook                                                                                                              | 89 |

| Appendix  | Sub-modeling Technique | .91 |

|-----------|------------------------|-----|

| Reference |                        | .97 |

| Vita      | 1                      | .02 |

## List of Tables

| Table 2.1:Polarization selection rules for back scattering from a (001) surface           |

|-------------------------------------------------------------------------------------------|

|                                                                                           |

| Table 2.2:         Thermomechanical properties used in finite element analysis            |

| Table 3.1:         Intensity for different Raman peaks under given polarization           |

| configuration                                                                             |

| Table 3.2:         Intensity for different Raman peaks vs. Polarization (Cross-Section    |

| Raman)47                                                                                  |

| Table 3.3:         Raman peak shift vs. stress distribution under different polarization  |

|                                                                                           |

| Table 4.1:    Material property used for FEA simulation                                   |

| Table 4.2:         Material property used in FEM for stack-die memory structure        73 |

## List of Figures

| Figure 1.1: | Illustration of a flip-chip packaging1                                                           |

|-------------|--------------------------------------------------------------------------------------------------|

| Figure 1.2: | Scaling effect on RC delay in interconnects                                                      |

| Figure 1.3: | Gate and interconnect delay versus feature size [3]4                                             |

| Figure 1.4: | Schematic diagrams showing the difference between 2-D and 3-D                                    |

|             | interconnects: (a) 2-D SiP integration; (b) SOC integration; (c) 3-D                             |

|             | integration. [11]5                                                                               |

| Figure 1.5: | Illustrations of Cu interconnect with TSV in 3-D stack die memory                                |

|             | [Source: Matrix Semiconductor Inc.]                                                              |

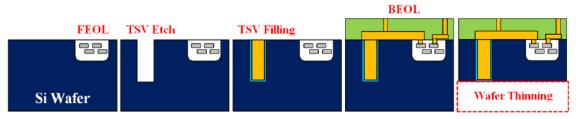

| Figure 1.6: | Via-middle process for TSV structures [16]7                                                      |

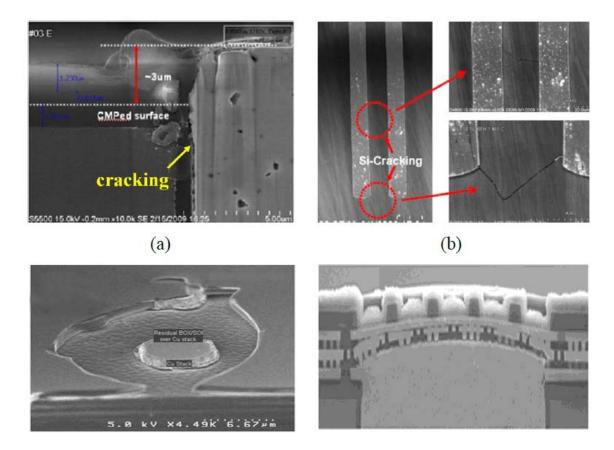

| Figure 1.7: | Mechanical issues in TSV structures [Source: Samsung [17]]:                                      |

|             | (a) Interfacial delamination; (b) Silicon Cracking; (c) Via extrusion                            |

|             | (Pop-up)9                                                                                        |

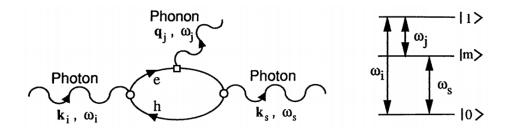

| Figure 2.1: | Feynman diagram and related energy levels for a first-order Stokes                               |

|             | scattering process [25]13                                                                        |

| Figure 2.2: | Picture of Renishaw inVia Raman system17                                                         |

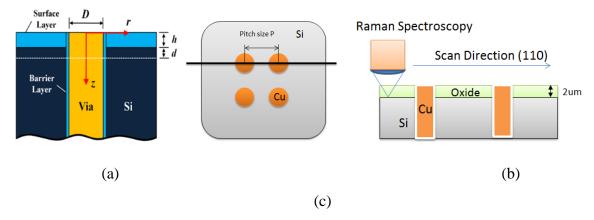

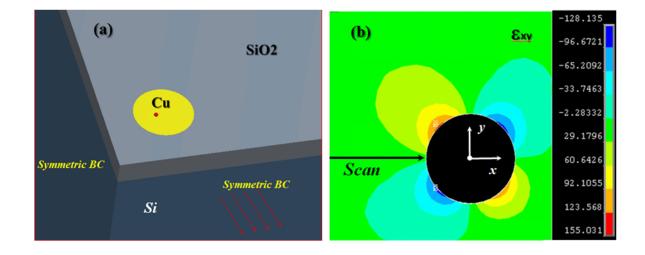

| Figure 2.3: | Schematic of (a) fully filled TSV structure near the wafer                                       |

|             | surface; (b) top view of a 2 by 2 TSV array; (c) illustration of                                 |

|             | Raman scan path illustration17                                                                   |

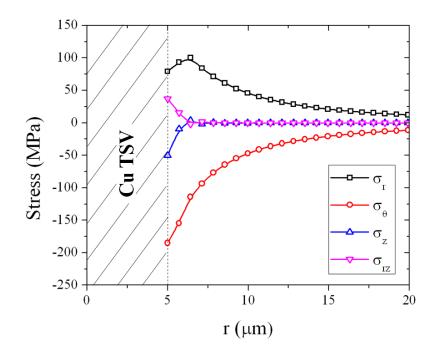

| Figure 2.4: | Near-surface stresses around an isolated TSV without oxide layer                                 |

|             | predicted by the semi-analytical solution ( $\Delta T = -100^{\circ}C$ , $D = 10 \mu\text{m}$ ). |

|             | (a) Stress components at $z = 0.2 \ \mu m$ ; (b) Sum of the in-plane normal                      |

|             | stresses at different depths[28]20                                                               |

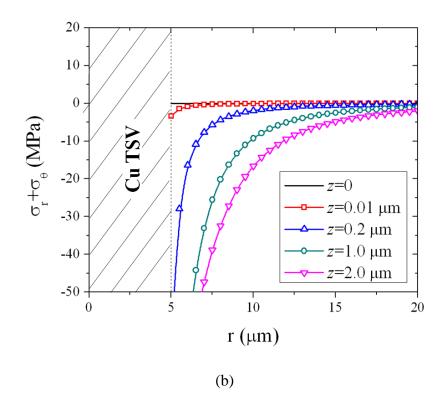

| Figure 2.5: | Distributions of the stress sum $(\sigma_r + \sigma_\theta)$ near the wafer surface $(z =$ |

|-------------|--------------------------------------------------------------------------------------------|

|             | 0.3 $\mu$ m) for (a) an isotropic Si model and (b) an anisotropic (001) Si                 |

|             | wafer. [28]                                                                                |

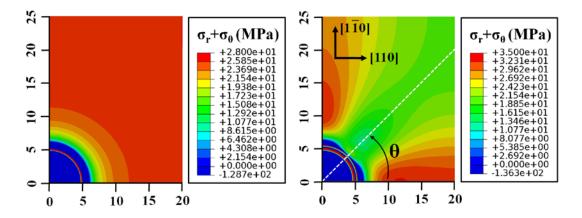

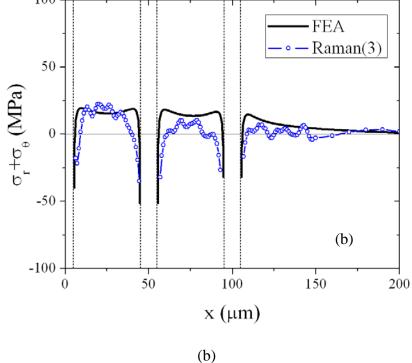

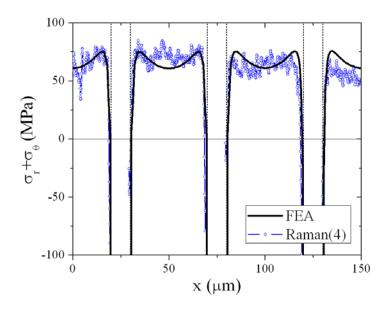

- Figure 2.6: (a) Measured Raman intensity and frequency for a TSV specimen with the surface oxide layer polished off. (b) Comparison of the nearsurface stress distribution between Raman measurements and finite element analysis. Vertical dash lines indicate the Cu/Si interfaces..23

- Figure 2.8: (a) Raman peak shift around two adjacent TSV w/o copper; (b)Comparison of Raman peak shift between experimental data in (a) and FEA at z=0.2um with different residual stress in oxide layer....25

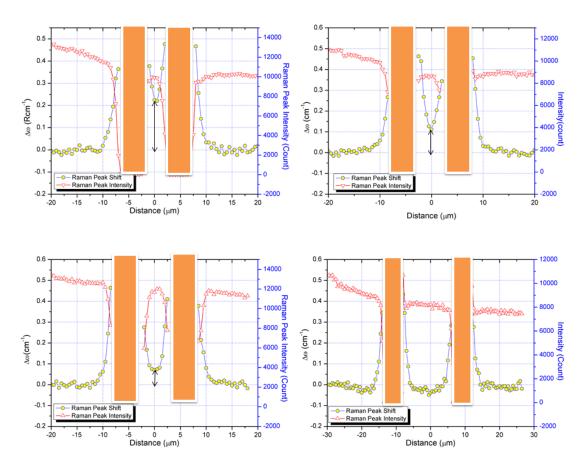

- Figure 2.9: Raman peak shift and Intensity with D= 5um and pitch size of (a) P=9um; (b) P=11um; (c) P=12um; (d) P=20um......27

| Figure 3.5   | (a) Illustration of scan path along [110] for the 2x2 TSV arrays and |

|--------------|----------------------------------------------------------------------|

|              | Raman peak shifts results along scan path for (b) sample A and (c)   |

|              | sample B41                                                           |

| Figure 3.6:  | (a) Modeling of a quarter structure and (b) in-plane shear stress    |

|              | distribution in Si around TSV for 2 by 2 TSV arrays                  |

| Figure 3.7:  | Comparison between experimental determined stress distribution and   |

|              | prediction of FEA simulation (a) Sample A annealed at 200C for 2     |

|              | hours (Thermal load of -80C is used in FEA model) (b) Sample B       |

|              | annealed at 300C for 2 hours (Thermal load of -280C is used in FEA   |

|              | model)                                                               |

| Figure 3.8:  | Illustration of the Geometry of Sample 1 and Sample 249              |

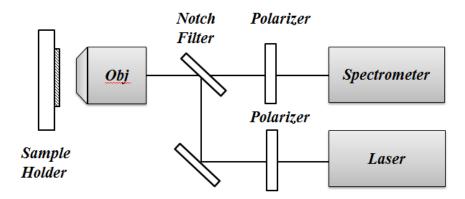

| Figure 3.9:  | Schematic of experimental set-up for Raman spectroscopy50            |

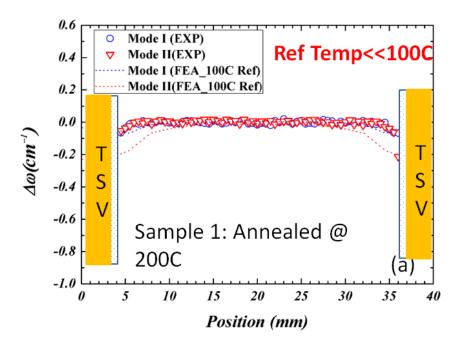

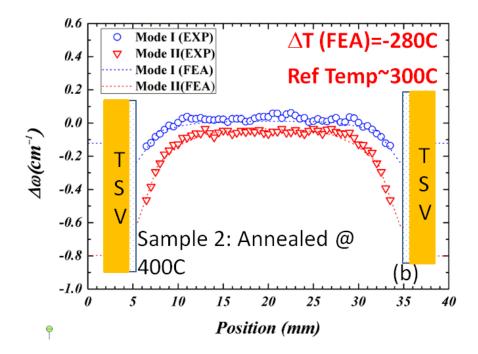

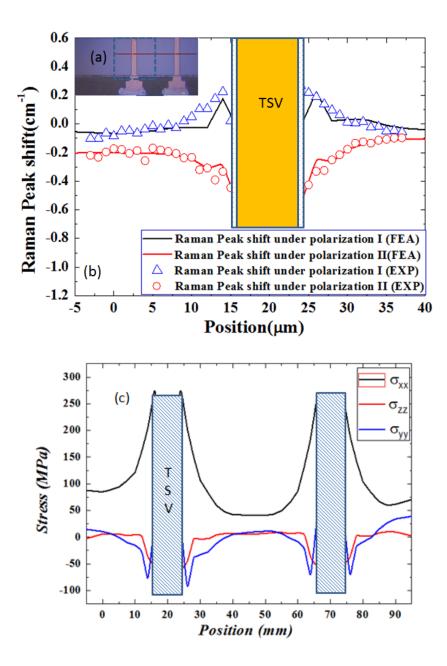

| Figure 3.10: | Raman peak shift along the scan path for (a) Sample 1 (Annealed at   |

|              | 200C) (b) Sample2 (annealed at 400C). The experimental data are      |

|              | plotted by blue circle (Raman Peak shift under polarization 1) and   |

|              | red triangle (Raman peak shift under polarization 2), and the FEA    |

|              | simulated Raman peak shift are plotted as dotted line. RT=20C52      |

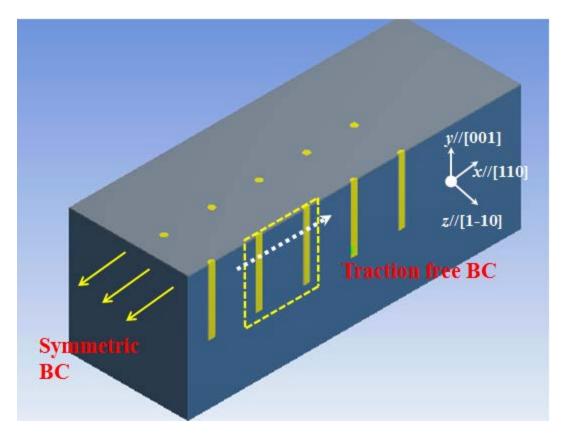

| Figure 3.11: | Visual illustration of the 3D FEA model                              |

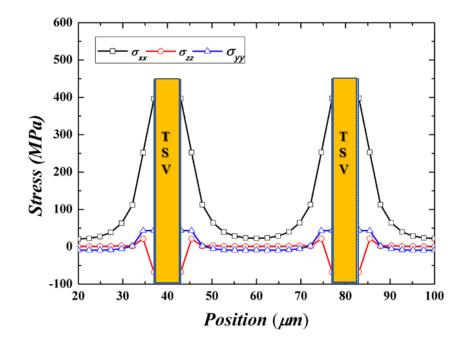

| Figure 3.12: | Normal stress distribution for Sample 2 on cross-section at $5\mu m$ |

|              | under TSV top surface                                                |

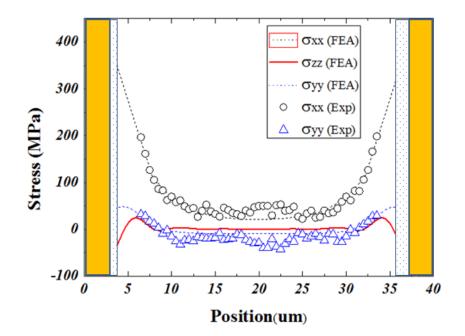

| Figure 3.13: | Comparison of the in-plane stresses distribution between Raman       |

|              | measurements and finite element analysis (FEA)55                     |

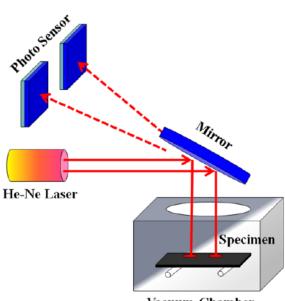

| Figure 3.14: | Illustration of the bending beam system. [Taken from [37]]57         |

| Figure 3.15: | Spatial relationships for the curvature calculation of specimen57    |

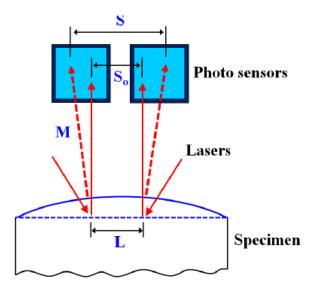

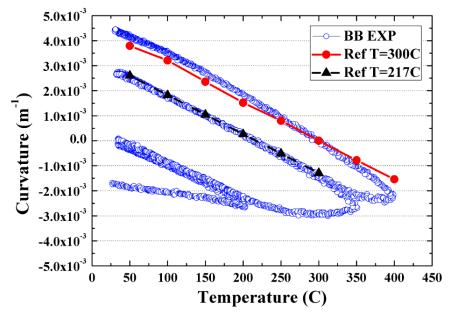

Figure 3.16: Bending beam measurement for sample 1 and sample 2 in section 3.2

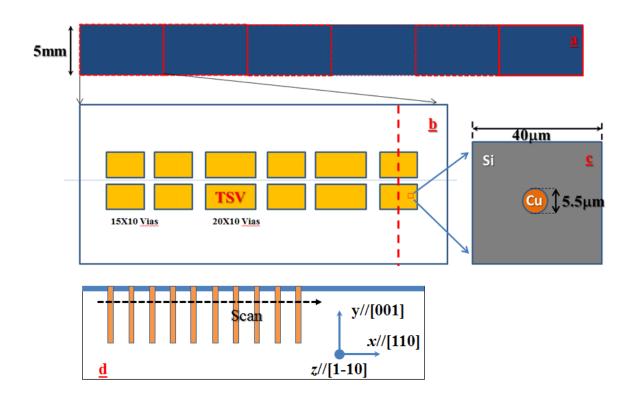

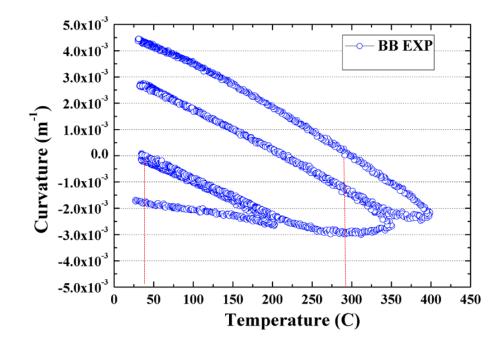

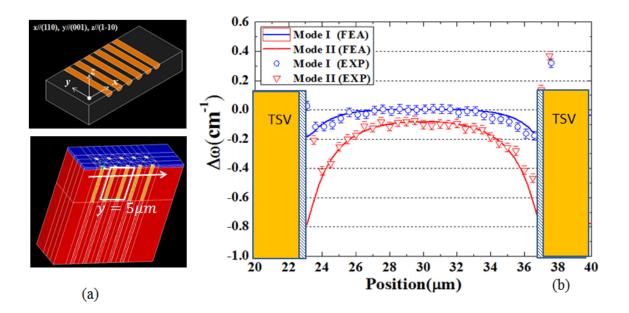

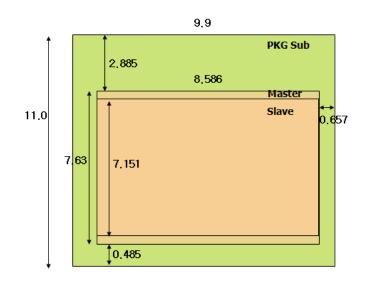

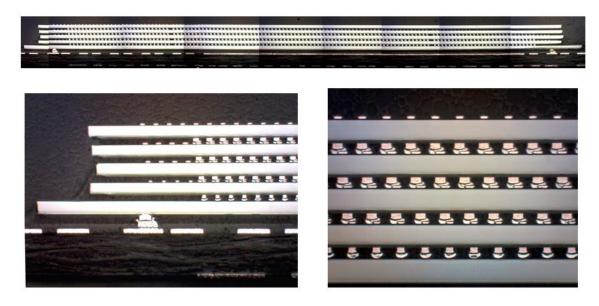

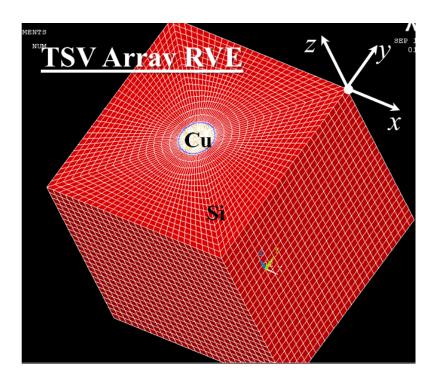

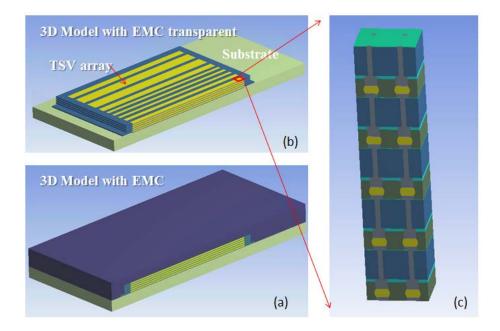

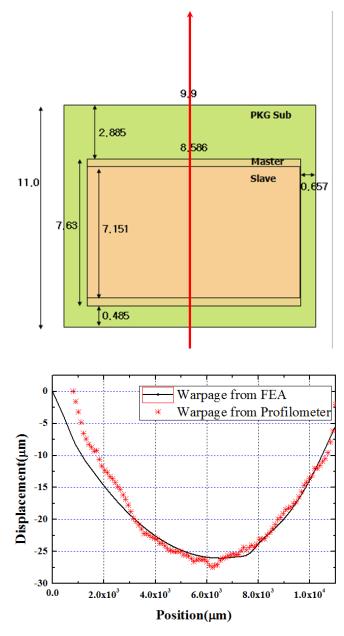

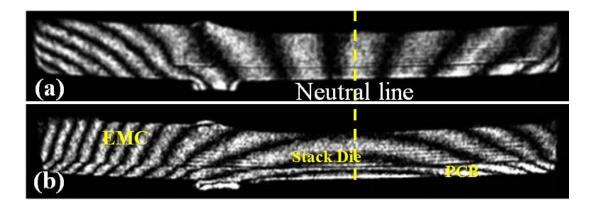

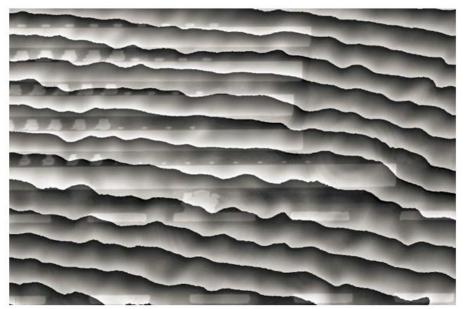

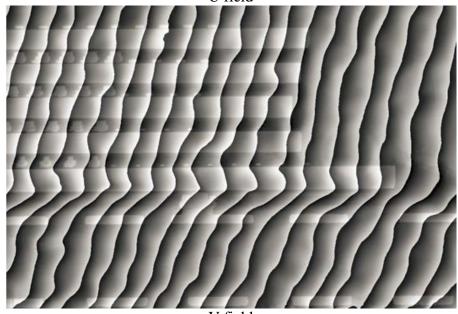

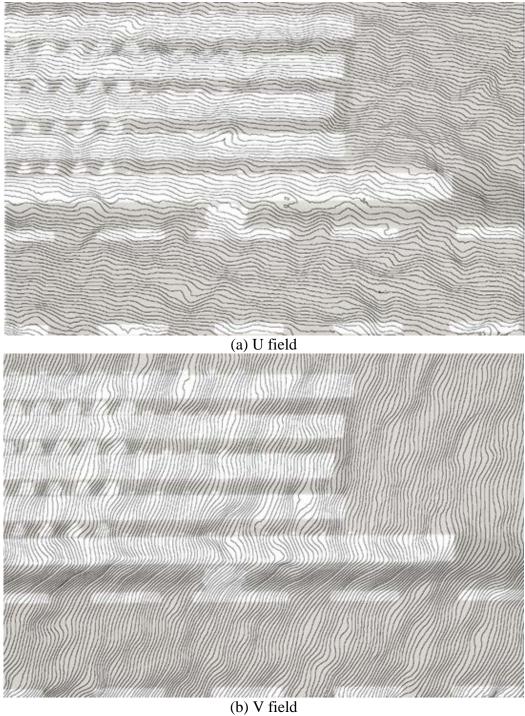

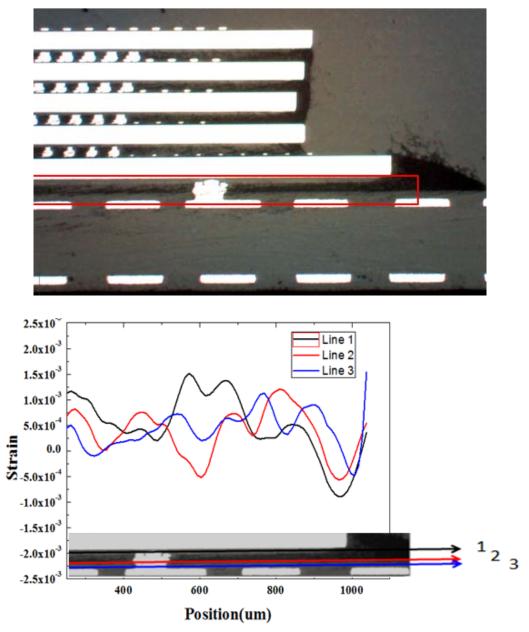

Figure 3.17: (a) Illustration of cross-section of region of measurement of sample B, x axis is along [110], y axis is along [001], and z axis is along [1-10] (b) Comparison of cross-section Raman measurement on sample B and FEA simulation results, a thermal load of -280C was Figure 4.1: Illustration diagram for stack-die memory structure (from top), units: Figure 4.3: A representative volume element for a TSV array with x axis along [110], y axis along [1-10], z axis along [001].....67 Figure 4.4: (a) FEM model for one quarter of the BB sample, the TSV arrays are replaced by equivalent composite material with effective moduli. (b) Out of plane displacement of top surface under a thermal load of Figure 4.5: Comparison of beam curvature obtained from BB experiment (hollow circle) and FEM simulation with effective moduli method (solid circle and solid triangle). .....70 Figure 4.6: (a) A half section FEM Model of stack die structure with symmetric boundary condition. (b) Same FEM model with EMC made transparent to show detailed structure under EMC. (c) TSV and Figure 4.7: Comparison of FEA and profilometer results of thermal deformation

| Figure 4.8: | Illustration | of  | sample   | preparation   | and   | locations | of | Cross-section |

|-------------|--------------|-----|----------|---------------|-------|-----------|----|---------------|

|             | Raman mea    | sur | ements i | n a die stack | struc | ture      |    | 75            |

- Figure 4.10: Optical system of moiré interferometer (Taken from [45]).....79

- Figure 4.11: Optical image of sample cross-section ......80

- Figure 4.12: Modified PEMI for moiré test (taken from [45])......81

| Figure 4.14: | Phase maps for stack-die memory package                   | .83 |

|--------------|-----------------------------------------------------------|-----|

| Figure 4.15: | Phase maps of stack-die memory package with 8X resolution | .84 |

Figure 4.16: Shear strain distribution in the region of interest......85

## **Chapter 1 Introduction**

### 1.1 Background and motivation

### **1.1.1 Conventional interconnects and packaging methods**

In the manufacture of modern computer chips, the process flow can be divided into two steps: Front-End-of-the-Line (FEOL) process and Back-End-of-the-Line (BEOL) process. In the FEOL process, individual devices, such as transistors which amplify and switch electronic signals, are patterned and fabricated on the surface of a silicon wafer. Subsequently, in the BEOL process, insulating layers (dielectrics) and metal lines are deposited and fabricated to interconnect the devices on the wafer.

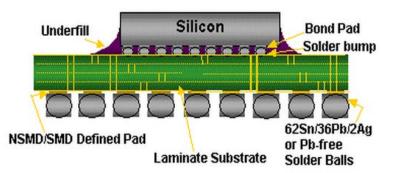

Chips are then integrated into chip package (or semiconductor device assembly) through several methods, such as the mature technology involving series of steps including die attach, wire bonding, and IC encapsulation and an advanced technology with flip chip packaging, etc. Particularly, in the flip chip packaging method, the silicon chip is flipped face down and electrically connected to the substrate through an area array of solder bumps. Fig 1.1

## FCPBGA Cross Section

Fig. 1.1 Illustration of a flip-chip packaging [Source: Freescale website]

The flip chip method offers several advantages, such as smaller packaging size, large I/O density, and higher performance and reliability, and it is widely used as the current packaging technology.

### 1.1.2 Cu/low-k interconnect

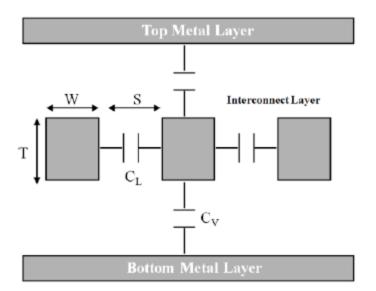

The proposal of doubling the number of transistors on an IC chip every 24 months by Gordon Moore in 1965 (also called Moore's law) has been the most powerful driver for the advancement of the microelectronics industry in the past 46 years. This law emphasized lithography scaling and integration (in 2D) of all functions on a single chip, perhaps through system-on-chip (SoC). [1] The challenges are mainly due to the interconnect delays, also known as Resistive-capacitive (RC) delay, which can be expressed by the following formula [2]

$$RC = 2\rho\kappa\varepsilon_0 \left(\frac{4L^2}{P^2} + \frac{L^2}{T^2}\right)$$

[1.1]

where P = W + S is the pitch size between the neighboring interconnects, L is the line length, W is the interconnect line width, T is the height of the interconnects,  $\rho$  is the resistivity of the interconnect materials,  $\kappa$  is the dielectric constant of the dielectric materials between the interconnect lines, and  $\varepsilon_0$  is the vacuum permittivity. A scaling effect on the RC delay is illustrated in Figure 1.2.

Fig. 1.2 Scaling effect on RC delay in interconnects

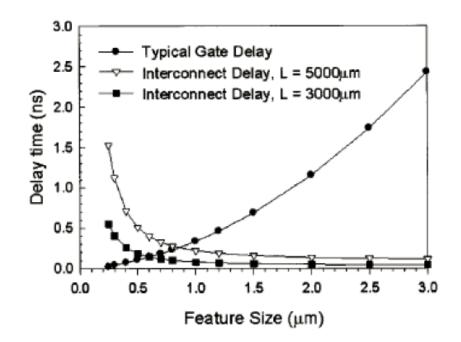

As shown in Figure 1.3, with the scaling of the gate length, gate oxide thickness, and junction depth, the corresponding scaling of interconnects will cause an increase in RC delay of interconnect. [3] This can limit the overall performance of the chip and cause serious challenges for future development of higher performance chips.

### **1.2 3-D integration with through-silicon Vias (TSVs)**

3-D integration, where several classes of IC chips are stacked in the vertical direction, appears to be an effective way to overcome the wiring limitation imposed on chip performance, device density and power consumption beyond the current technology. [4] [5] [6] The 3-D integration can achieve a high circuit density and performance through a heterogeneous integration of multiple IC chips. The application of through-silicon via (TSV) is essential for 3D silicon integration and 3D IC integration [7] [8] [9]TSVs are processed either through the IC chips or in the silicon interposer to form vertical, electrical connections between stacked IC chips

Fig. 1.3 Gate and interconnect delay versus feature size [3]

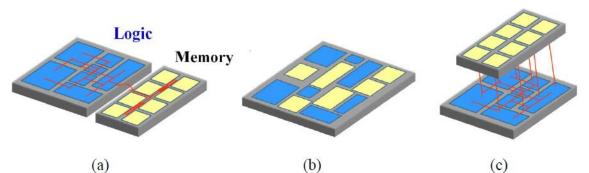

Major advantages of 3D integration include: (a) better electrical performance; (b) lower power consumption; (c) higher device density and smaller packaging form factor. [10] The benefits (a) and (b) can be interpreted from a conceptual illustration, as shown in Fig. 1.4. In Fig. 1.4(a), a logic chip and memory chip are connected by current 2-D interconnects. Wires that connect between chips can be as long as the lateral dimension of chips, i.e. a length of a centimeter scale. The relatively long transmission route could result in a signal delay that degrades the electrical performance. This is also known as the memory latency. In Figure 1.4(c), two IC chips are connected vertically using 3-D interconnects with TSVs. The wiring distance between two chips, if properly designed, can be as short as the vertical dimension between the chips, which is usually in the micron scale. Consequently, 3-D infrastructures can significantly reduce the memory latency and hence improve the chip performance.

**Fig. 1.4** Schematic diagrams showing the difference between 2-D and 3-D interconnects: (a) 2-D SiP integration; (b) SOC integration; (c) 3-D integration. [11]

The other benefit of 3-D integration is to increase the device density while to reduce the package form factor. An example of interconnects of Matrix 3D memory is illustrated in Figure 1.5. By stacking chips together, the device density in the unit area is increased by 4 times equivalently. In the meanwhile, by wafer-thinning, the total package thickness won't increase or even decrease. Therefore, 3-D integrated memory has a tremendous potential for mobile communication devices since it enables massive data storage in a more limited space

Fig. 1.5 Illustrations of Cu interconnect with TSV in 3-D stack die memory [Source: Matrix Semiconductor Inc.]

#### **1.2.1 Process flow for TSV fabrication**

The fabrication of TSVs involves three key processes [12] [13] [14] [15]: 1) via hole etching, 2) TSV filling by electroplating, and 3) Si wafer thinning and wafer bonding/deboning. Depending on when the TSV processing is done in the interconnect fabrication, the terms such as via first, via middle, and via last have evolved. Currently, the via-middle process is the most popular, and it is described in more detail below.

### Via middle process

Fig 1.6 schematically illustrates the via-middle process, which is performed in between the FEOL and the BEOL fabrication process. A typical via-middle process to fabricate TSVs with a diameter of 10um and a depth of 50um in the Si substrate is described as the following. First, lithography is done to pattern via openings across the wafer. Second, Deep reactive-ion etching DRIE is used to create via holes of desired dimensions. This is then followed by deposition of oxide liner on the via side walls. The oxide layer reduces capacitance and improves electrical isolation between the TSVs and the silicon substrate. To prevent diffusion of Cu into Si substrate, a thin barrier layer (50nm usually) of Ta/TaN or Ti/TiN is deposited after the oxide layer. Third, a thin Cu seed layer is first deposited on the barrier layer and then the vias are filled by the electroplating process. A subsequent annealing step could be applied to stabilize the Cu grain structures and relax the residual stresses. Fourth, CMP is conducted to remove the Cu overburden, Ta/TaN layers and oxide liner. The fabrication of TSV structure is followed by the BEOL process in which interconnects are made and bonding pads are patterned. Finally, the Si substrate is thinned down to the optimized TSV height to expose the bottom of the TSV for the following BEOL process.

Fig. 1.6 Via-middle process for TSV structures [16]

#### **1.2.2 Reliability concerns in TSV structure**

As there are two side of a coin, when taking advantage of 3-D integration, the reliability concerns has been raised due to the introduction of TSV into the package. Due to the CTE mismatch between the Cu and silicon, thermal stresses are introduced during processing and thermal cycling of the TSV structures. [16].The thermal stress can cause interfacial delamination, cracking of Si, and mobility degradation of stress-sensitive devices.

Protrusion, also called pop-up, of TSV during the thermal treatment is another frequently observed failure mode for TSV.(Fig. 1.7a) The protrusion of TSV can cause further mechanical failures, such as cracking or lifting of the dielectric layers built up over TSVs. (Fig 1.7b, Fig. 1.7c) [17]The via pop-up phenomenon is considered to be combined results of several different mechanisms, such as microstructure evolution of copper in TSV, the boundary diffusion of Cu along the liner oxide, etc. Among all those factors, the thermal stress induced by the CTE mismatch is still considered to be the most important part, which will cause Cu to be deformed plastically.

To understand the failure mechanisms in the TSV structures, it is essential to experimentally characterize the induced stresses and material behaviors under thermomechanical conditions equivalent to TSV fabrication.

**Fig. 1.7** Mechanical issues in TSV structures [Source: Samsung [17]]: (a) Interfacial delamination; (b) Silicon Cracking; (c) Via extrusion (Pop-up)

### 1.3 Scope of this thesis

In this thesis, analytic and numerical approaches are applied, along with experimental measurements to study thermal mechanical reliability issues in TSV for 3-D integration. Thermal stresses of TSV structures are analyzed. Raman spectroscopy is chosen to be the main method for experiment. [18] [19] [20] [21] [22] A comprehensive understanding is established for the thermo-mechanical stress and reliability of TSV structures. This thesis is organized as follows.

As an introduction, Chapter 1 presents a brief review of background and motivation for this work. This chapter covered the conventional interconnect and packaging scheme as well as the current challenge related to the interconnect. As an effective solution to overcome the challenges, the advantages of 3D integration are introduced and the via-middle fabrication processes are described.

In chapter 2, a brief review of Raman spectroscopy is presented as well as the physics behind it, and then the Raman spectroscopy is employed to measures a certain combination of the near-surface stresses for periodic TSV arrays. The results are compared with semi-analytic solution as well as finite element analysis (FEA) to gain comprehensive understanding of the stress distribution. Moreover, the effect of residual stress in both side wall and top oxide layer and interaction of stress field from an adjacent via are evaluate experimentally.

In chapter 3, two innovative Raman techniques for stress measurement are presented and employed to the TSV structure for the stresses characterization. First, by introducing the so called "High numerical aperture" effect, additional information is obtained under a proper polarization configuration. Based on this method, all the normal stress components can be obtained from the experimental data. Second, Raman measurement on the axial cross-section of the TSV structure is presented. By controlling the polarization of the scattering light, two different Raman peak shift trends can be observed on the same scan location. With proper assumption based on FEA simulation, in-plane stress components can be determined on the cross-section of TSV from experimental data. These Raman results are verified by independent bending beam experiments in the last part of this chapter

Chapter 4 focuses on the thermal reliability characterization on the stack-die memory structure. Various experimental methods such as Moiré interferometry and profilometer are applied to characterize the package level deformation, and cross-section Raman measurements are applied to characterize the local strain distribution around TSV. An effective module method

is developed based on finite element analysis (FEA) for evaluating the package level thermal mechanical behavior. Combing with the sub-modeling technique, the local strain field near TSV is obtained by FEA. Experimental and simulation results are compared and analyzed.

In conclusion, Chapter 5 summarizes the results from the present study and suggests potential directions for the future work.

## Chapter 2 Near-Surface Stress Measurement with Conventional Raman Spectroscopy

### 2.1 Underlying Theory of Raman spectroscopy

For short, Raman scattering or the Raman effect is the inelastic scattering of a photon due to photon-phonon interactions. It was first discovered by C. V. Raman and K. S. Krishnan in liquids [23], and by G. Landsberg and L. I. Mandelstam in crystals [24]. Different formularization are used to explain the mechanism of Raman scattering [25] [26] [27], and here the approach presented in [25] is followed. The collective lattice vibration can be described by means of phonon:

$$Q_j = A_j \exp[\pm(q_j \cdot r - \omega_j t)]$$

$$\tag{2.1}$$

For each possible vibration j,  $q_j$  represents the wave vector and  $\omega_j$  represents the frequency.  $Q_j$  is the normal coordinate of the vibration and  $A_j$  is a constant. When monochromatic light of frequency  $\omega_i$  is incident on a crystal in a direction **k**<sub>i</sub>, the associated electric field **E** will induce at position **r** an electric moment **P**, which is related to **E** through

$$P = \varepsilon_0 \boldsymbol{\chi} \cdot E_0 \exp[i(k_i \cdot r - \omega_i t)]$$

[2.2]

where,  $\chi$  is the susceptibility tensor, which describes the response of the crystal to the electric field [25].  $\chi$  is a function of lattice vibration, and can be expanded in Taylor series with respect to the normal coordinate of the vibration Qj:

$$\chi = \chi_0 + \left(\frac{\partial \chi}{\partial Q_j}\right)_0 Q_j + \left(\frac{\partial \chi}{\partial Q_j \partial Q_k}\right)_0 Q_j Q_k + \cdots$$

[2.3]

The first term in equation [2.3] corresponds to elastic scattering of photon, which is also known as Rayleigh scattering. The second and third term give rise to the first order and second order Raman scattering respectively. Higher order terms in equation [2.3] are ignored. Substituting equation [2.3] into [2.2] yields:

$$P = \varepsilon_0 \chi_0 \cdot E_0 \exp[i(k_i \cdot r - \omega_i t)] + \varepsilon_0 E_0(\frac{\partial \chi}{\partial Q_j})_0 A_j \exp\left[-i(\omega_i \pm \omega_j)t\right] \exp[i(k_i \pm q_j) \cdot r)$$

[2.4]

If  $(\frac{\partial \chi}{\partial Q_j})_0$  is non-zero, besides the Rayleigh scattering light, the scattering light with frequency of  $\omega_i + \omega_j$  and  $\omega_i - \omega_j$  will be observed as well, which corresponds to anti-Stokes and Stokes Raman scattering, respectively. The intensity of the scattering light is given by

$$I = C \sum_{j} \left| e_{i} \cdot R_{j} \cdot e_{s} \right|^{2}$$

$$[2.5]$$

Where C is a constant and  $R_j$  is the Raman tensor of the phonon j. The  $R_j$  are second-rank tensors and coordinate system dependent. For silicon, under coordinate system x//[100], y//[010] and z//[001], the Raman tensor is in the form of:

$$\boldsymbol{R_1} = \begin{pmatrix} 0 & 0 & 0 \\ 0 & 0 & d \\ 0 & d & 0 \end{pmatrix}, \quad \boldsymbol{R_2} = \frac{1}{\sqrt{2}} \begin{pmatrix} 0 & 0 & d \\ 0 & 0 & 0 \\ d & 0 & 0 \end{pmatrix}, \quad \boldsymbol{R_3} = \begin{pmatrix} 0 & d & 0 \\ d & 0 & 0 \\ 0 & 0 & 0 \end{pmatrix}$$

[2.6]

By combining equation [2.5] and [2.6], the polarization selection rule for back scattering from a (001) surface can be determined as shown in Table 2.1

|         | Visible              |                  |       |       |

|---------|----------------------|------------------|-------|-------|

| $e_{i}$ | es                   | $\overline{R_x}$ | $R_y$ | $R_z$ |

| Back so | cattering from (001) |                  |       |       |

| (100)   | (100)                |                  |       |       |

| (100)   | (010)                |                  |       | Х     |

| (1-10)  | (1-10)               |                  |       | Х     |

| (110)   | (1-10)               | —                | —     |       |

**Table 2.1** Polarization selection rules for back scattering from a (001) surface [25]

According to Table 2.1, for back scattering from a (001) surface, only one longitudinal mode (corresponds to Rz) can be observed.

From a quantum physical point of view, Raman scattering involves the destruction of a photon with frequency  $\omega_j$ , incident from a light source, and the creation of a photon with frequency  $\omega_s$ . Fig. 2.1 shows a typical Feynman diagram and the related energy levels for a first order Stokes scattering process [25], and the detailed calculation for the scattering cross-section is discussed in detail in [27].

**Figure 2.1** Feynman diagram and related energy levels for a first-order Stokes scattering process [25]

#### 2.2 Effect of Stress on the Raman Modes of Silicon

One of the first papers addressing theoretically the effect of stress on the Raman modes was that by Ganesan *et al* [28]. The famous secular equation is introduced to describe the relation between presented strain and frequency of Raman scattering [28] [29]. Under the crystal coordinate system x // [100], y //[010] and z// [001], secular equation is in the form of

$$\begin{vmatrix} p\varepsilon_{11} + q(\varepsilon_{22} + \varepsilon_{33}) & 2r\varepsilon_{12} & 2r\varepsilon_{13} \\ 2r\varepsilon_{12} & p\varepsilon_{22} + q(\varepsilon_{33} + \varepsilon_{11}) & 2r\varepsilon_{23} \\ 2r\varepsilon_{13} & 2r\varepsilon_{23} & p\varepsilon_{33} + q(\varepsilon_{11} + \varepsilon_{22}) \end{vmatrix} - \lambda \mathbf{I} = \mathbf{0}$$

[2.7]

Here p, q and r are the material constants, the so-called phonon deformation potentials. The difference between the Raman frequency of each mode in the presence of stress, and in the absence of stress,  $\omega_0$ , can be calculated from the eigenvalues  $\lambda_i$ :

$$\lambda_j = \omega_j^2 - \omega_{j0}^2 \text{ or } \Delta \omega_j = \omega_j - \omega_{j0} \approx \frac{\lambda_j}{2\omega_{j0}}$$

[2.8]

In principle, with known strain distribution in silicon, all three Raman modes (two transverse optical modes and one longitudinal optical mode) can be solved by combining equation [2.7] and [2.8]. Those Raman peaks are usually indistinguishably close, so generally, the Raman measured is the weighted average of all 3 modes:

$$\Delta \omega = \frac{I_1 \Delta \omega_1 + I_2 \Delta \omega_2 + I_3 \Delta \omega_3}{I_1 + I_2 + I_3}$$

[2.9]

However, based on the selection rules in Table 2.1, only longitudinal Raman mode ( $\Delta \omega_3$ ) is visible for back scattering from (100) surface. Now consider a specific example, the stress is assumed to be biaxial on (001) Si surface:

$$\varepsilon_{xz} = \varepsilon_{yz} = 0, \sigma_{zz} = 0$$

[2.10]

Substitute [2.10] to secular equation [2.7], combined with [2.8], the only visible Raman mode can be calculated:

$$\Delta\omega_3 \approx \frac{\lambda_3}{2\omega_0} = \frac{p\varepsilon_{zz} + q(\varepsilon_{xx} + \varepsilon_{yy})}{2\omega_0}$$

[2.11]

With Hook's law, the relation between Raman peak shift and in-plane stress can be obtained:

$$\Delta\omega_{3} \approx \frac{\lambda_{3}}{2\omega_{0}} = \frac{pS_{12} + q(S_{11} + S_{12})}{2\omega_{0}} (\sigma_{xx} + \sigma_{yy})$$

[2.12]

Using

$$S_{11} = 7.68 \times 10^{-12} Pa^{-1}$$

$$S_{12} = -2.14 \times 10^{-12} Pa^{-1}$$

$$S_{44} = 12.7 \times 10^{-12} Pa^{-1}$$

,  $p = -1.43\omega_0^2$ ,  $q = -1.89\omega_0^2$  and  $r = -0.59\omega_0^2$  [29], from equation [2.12],

$$\sigma_{xx} + \sigma_{yy}(\text{MPa}) = -470\Delta\omega_3(cm^{-1})$$

[2.13]

[2.13] is under the crystal coordinate system, it can be easily converted to the equation under polar coordinate system as the sum of in-plane stresses is invariant during coordinate transformation. Thus, in polar coordinate system:

$$\sigma_r + \sigma_{\theta}(\text{MPa}) = -470\Delta\omega_3(cm^{-1})$$

[2.14]

From this it follows that compressive uniaxial or biaxial stress will result in an increase of the Raman frequency (positive $\Delta\omega_3$ ), while tensile stress will cause a decrease (negative $\Delta\omega_3$ ).

### 2.3. Experimental Descriptions

A Renishaw inVia system (Fig. 2.2) was used for the Raman measurements, equipped with 532nm laser and a focused laser spot size of about 0.8  $\mu$ m by a 100x objective (NA = 0.85). Two types of TSV samples are investigated in this chapter. The Sample 1 consists of a large periodic TSV arrays. The diameter of the TSV is 10um with 50um pitch in the x direction and 40um pitch in the y direction. The depth of the TSV is 55um. The surface of silicon is coved by a thin layer (~0.2um) of oxide. The sample 2 consists of a periodic 2 by 2 arrays of Cu vias of diameter (D) of 5.5 $\mu$ m with a 9~20  $\mu$ m pitch size. The surface of Si is covered by an oxide layer of about 2 $\mu$ m thickness (*h*). In addition, an oxide barrier layer of about 0.25  $\mu$ m thick was deposited at the via/Si interface. The general structures of the TSV are similar as illustrated in Figs. 2.3 (a), (b), and (c), which show the scanning profile along (110) direction on 100 wafer across two adjacent vias. With Eq. [2.13], the sum of the two principal stresses in Si can be deduced directly from the Raman shift, which is a volume average over the region defined by the area of the focused laser spot and the penetration depth.

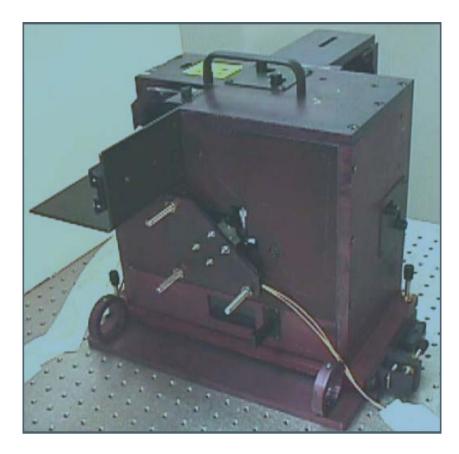

Fig. 2.2 Picture of Renishaw inVia Raman system

**Fig. 2.3** Schematic of (a) fully filled TSV structure near the wafer surface; (b) top view of a 2 by 2 TSV array; (c) illustration of Raman scan path illustration

## 2.4 Analysis of Near-surface Stresses

An approximate analytical solution for the stress field induced by coefficient of thermal expansion (CTE) mismatch between Copper and Silicon around a circular TSV embedded in a Si

wafer was obtained by S. Ryu [30]. Using the 3D analytical solution, the sum of the in-plane stresses is studied in comparison with the Raman measurements. The sum of the radial and circumferential stresses in the TSV structures is obtained as

$$\sigma_r + \sigma_\theta = \frac{-E\varepsilon_T}{2\pi(1-\nu)} \int_0^{\frac{D}{2}} \int_0^{2\pi} \left(\frac{3z^3}{R^5} - \frac{2(1+\nu)z}{R^3}\right) \rho \, d\rho \, d\theta$$

[2.15]

It is found that, while the stress sum is identically zero both at the wafer surface (z = 0) and far away from the surface ( $z \rightarrow \infty$ ), it varies with the depth (z) in the near-surface region as shown in Fig. 2.4(b). The stress sum is negative everywhere for z > 0 and r > D/2, The magnitude decays monotonically as r increases and diminishes to zero far away from the via. Since the two stress components have opposite signs as shown in Fig. 2.4(a), the magnitude of their sum in Fig. 2.4(b) is relatively small. Near the wafer surface ( $z < 2 \mu m$ ), the magnitude of the stress sum increases with increasing depth. This suggests that the Raman signal depends on the laser penetration depth and a typical penetration depth may be determined for the Raman measurement. On the other hand, while the stress magnitude is increasingly high approaching the Si/TSV interface, the Raman signal becomes noisy due to the reduction in the Raman intensity. Thus, the Raman data very close to the interface must be interpreted with caution.

(a)

**Fig. 2.4** Near-surface stresses around an isolated TSV without oxide layer predicted by the semianalytical solution ( $\Delta T = -100^{\circ}C$ ,  $D = 10 \,\mu$ m). (a) Stress components at  $z = 0.2 \,\mu$ m; (b) Sum of the in-plane normal stresses at different depths. [30]

Although the semi-analytical solution is a powerful tool to understand the qualitative stress distribution around TSV, the major assumptions made to simplify the results, will result in discrepancy of the stress distribution from the real case. Numerical analysis-based finite element method is utilized to gain better understanding of the stress distribution near the TSV structures. Two major assumptions are lifted in our numerical model: First, different materials in the TSV structure-the Cu via and the oxide-are considered with their elastic moduli to be taken as linear elastic and isotropic, 110GPa and 70GPa, respectively. The detailed property used in the model is listed in Table 2.2. The thin Ta layer, 0.2um thick, has negligible effect on the stress state in Si, thus ignored in the finite element analysis (FEA) for stresses. Second, the elastic anisotropy of Si is taken into account using the anisotropic elastic constants for Si crystal with a cubic symmetry. A 3-D FEA model consists of three different materials (Cu, Oxide, and Si) is used to simulate the periodic TSV array used for the Raman measurements. By symmetry, only a quarter of TSV array structure is modeled. To further reduce the computation time, the wafer thickness is taken to be 500  $\mu$ m in the FEA model instead of 700  $\mu$ m in the real specimen, while the TSV depth is still 55 µm. The top surface is traction free, and the out-of-plane displacement (z-direction) at the bottom surface is set to be zero. With such boundary conditions, increasing the wafer thickness has negligible effect on the near-surface stress distribution. Linear 3-D solid elements (Solid 185) in the ANSYS software are used, with a fine mesh near the surface (element size =  $0.1 \mu m$  in the thickness direction and  $0.2 \mu m$  in the lateral direction) and an increasingly coarse mesh away from the surface and TSV.

| Material | CTE<br>(ppm/°C) | Young's Modulus<br>(GPa) | Poisson's ratio |

|----------|-----------------|--------------------------|-----------------|

| Cu       | 17              | 110                      | 0.35            |

| Si       | 2.3             | 130                      | 0.28            |

| Oxide    | 0.55            | 72                       | 0.16            |

**Table 2.2** Thermomechanical properties used in finite element analysis

The contours of the in-plane stress sum are calculated at the depth  $z = 0.3 \mu m$ . As the stress components in out-plane direction are ignored, the summation of in-plane stress should be invariant among different coordinates system. In previous study, the summation is calculation in polar coordinates system, and the results are shown in Fig. 2.5, the summation  $\sigma_r + \sigma_{\theta}$  is the same as  $\sigma_{xx} + \sigma_{yy}$  in Cartesian coordinates. Using the anisotropic elastic property for the (001) silicon, the stress distribution as shown in Fig. 2.5b exhibits a four-fold symmetry, reflecting the cubical symmetry of silicon crystal.

Figure 2.5 Distributions of the stress sum  $(\sigma_r + \sigma_{\theta})$  near the wafer surface  $(z = 0.2 \ \mu\text{m})$  for (a) an isotropic Si model and (b) an anisotropic (001) Si wafer. [30]

#### 2.5 Comparison between Raman and FEA Results

Using Eq. [2.13], the measured Raman frequencies can be converted to the stress sum. To determine the reference frequency,  $\omega_0$ , the Raman scans were not only performed between the vias but also extended to the bare silicon surface far away from the vias, where the stress sum is expect to be zero. As shown in Fig. 2.6a, the average Raman frequency obtained from the farfield measurement gives the reference frequency. For this measurement, the surface oxide layer on the TSV sample was mechanically polished, and the sample was subsequently subject to an annealing step at 200C for 2 hours. All the Raman measurements were conducted after cooling down to the room temperature. In Fig. 2.6b, the measured Raman frequencies are converted to stress summation by Eq. [2.11], to compare with the stresses obtained from the FEA model. For the FEA model, the materials (Si, Cu and Oxide) were assumed to be linear elastic. As a result, the stress magnitude from the FEA model depended linearly on the temperature change, from a reference temperature at which the stress is zero. In a separate study using the bending beam technique, the reference temperature for the TSV specimen was determined to be around 100C, and thus  $\Delta T = -70 \ ^{o}C$  [31] for the Raman measurements at room temperature. With  $\Delta T = -70 \ ^{o}C$  the results from the FEA model are in reasonable agreement with the Raman data as shown in Fig 2.6(b). It is noted that the stress magnitude is relatively low in this case, which makes the Raman measurement difficult due to the relatively large noise-to-signal ratio.

**Fig. 2.6** (a) Measured Raman intensity and frequency for a TSV specimen with the surface oxide layer polished off. (b) Comparison of the near-surface stress distribution between Raman measurements and finite element analysis. Vertical dash lines indicate the Cu/Si interfaces.

Additional Raman measurements were performed for the TSV samples annealed at 300C for 1 hour. In Fig. 2.7, the stresses from the Raman measurements were compared to the FEA results with $\Delta T = -270C$ . It was assumed that the annealing at 300C relaxed the stresses in the TSV specimen and thus raised the reference temperature for the induced thermal stresses upon cooling down to the room temperature. Compared to Fig. 2.6, the stress magnitude in Si has increased and fitting to the FEA results improved due to the higher reference temperature. This is consistent with the bending beam measurement reported in the literature [31]

**Fig 2.7** Comparison of the near-surface stress distribution between Raman measurements and finite element analysis, for a TSV specimen annealed at 300°C for 1hr.

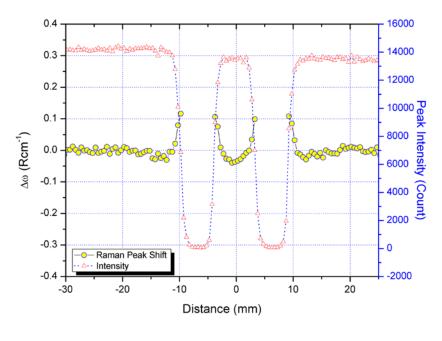

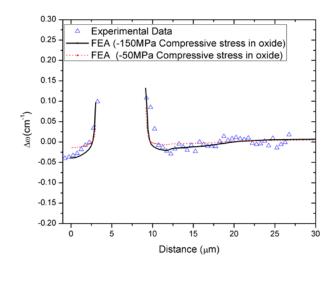

#### 2.6 Residual Stress in Oxide

During the study, for sample 1, comparison of the near-surface stress distribution between FEA and Raman measurements on TSV samples having top oxide layer showed a minor discrepancy. One possible explanation for the discrepancy could be the residual stress level within the top and side wall oxide layer. For detailed study of the oxide layer effect, sample 2 is chosen as its top oxide layer is significantly higher than sample 1. A 2 by 2 TSV array on sample 2 was prepared by dipping into nitric acid to etch off copper in the TSVs, and then Raman spectroscopy was performed at room temperature (Fig. 2.8 (b)). Various residual stress levels are assumed in FEA model for comparative fitting with the experimental data. As shown in Fig. 2.8 (a), FEA with an assumption of 150MPa residual compressive stress in the oxide layer gives a better agreement with the experimental data than the assumption of 50MPa compressive stress gives. Similar level of compressive stress state in oxide thin film has been reported previously by the beam curvature technique. [31]

(a)

(b)

**Figure 2.8** (a) Raman peak shift around two adjacent TSV w/o copper; (b) Comparison of Raman peak shift between experimental data in (a) and FEA at z=0.2um with different residual stress in oxide layer

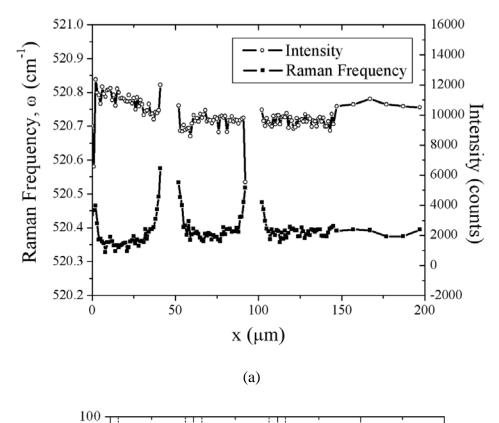

### 2.7 Characterization of Via Stress Field Interaction

Thermal stresses induced in the TSV structures can affect the device performance by degrading the carrier mobility. Keep-out zone (KOZ) has been brought out as a reference for industry design. The effects due to stress interactions in a TSV array on the KOZ were investigated theoretically. The effect of stress interaction was found to depend on the ratio of pitch to diameter of the TSV array. To evaluate the stress interaction experimentally, 2 X 2 TSV arrays were annealed at 300C for 12 hours to assure full stress relaxation in copper, and then cooled down to room temperature. As shown in Figs. 2.9 (a), (b), and (c), the minima of the Raman shift between the two TSVs is non-zero, and decreases with the increase of pitch size between the two vias. This is due to the stress field interactions between the two adjacent vias. In Fig. 2.9 (d), the interaction between the two adjacent vias diminishes to nearly zero and the two adjacent vias could be considered to be isolated from each other. From the comparison among

Figures 2.9(a) through 2.9(d), it can be concluded that, for a -280C thermal load, a pitch to diameter ratio of 4 could be considered the distance where the stress interaction between the two TSVs does not exist any longer.

**Fig. 2.9** Raman peak shift and Intensity with D= 5um and pitch size of (a) P=9um; (b) P=11um; (c) P=12um; (d) P=20um

# 2.8 Summary

A brief introduction to the Raman spectroscopy and the physics behind it is given. The Micro-Raman spectroscopy has been employed to study the thermal mechanical behaviors of TSV structures. The local distribution of near-surface stress in Si has been measured, in comparison with stress analysis of the TSV structure based on a semi-analytic approach and finite element analysis. The effect of residual stress in surface oxide layer and the interaction of stress field of neighboring TSV are evaluated experimentally.

### **Chapter 3 High Numerical Aperture Effect and Raman Measurements**

In Chapter 2, it was shown how to provide high-resolution scans of the stress distribution in Si near the TSV. However, stress mapping using the conventional Raman technique has serious limitations since it is unable to measure all the lattice vibration modes described in the Raman theory. For example, for TSVs embedded in a (001) wafer, the only measurable polarization of vibration is the longitudinal optical phonon mode along (001) [32]. Even for this vibration mode, only the sum of the in-plane normal stress components can be deduced [33]. The in-plane normal stress components near TSV surface, however, are about equal in magnitude but opposite in sign [33, 34]. Thus not only the stress components cannot be separately determined, but the magnitude of the Raman signal (for sum of the stresses) is generally quite small. This seriously limits the accuracy and usefulness of the conventional Raman technique. Finite element analysis (FEA) is commonly used to calculate the individual stress components and the results are correlated to the micro-Raman measurement. The FEA simulation has considerable uncertainties by itself and requires careful validation of the assumptions made on the material properties and the constitutive relation, e.g. elastic or elasticplastic used in the analysis.

In this chapter, two Raman techniques, top-down and cross-section of TSV structures, were first developed to measure the normal stress components separately. Different polarization conditions and so-called "high numerical aperture (NA)" effect were utilized in the experiments to observe the different Raman modes in order to deduce additional information for the stresses. Then an independent bending beam experiment was carried out to validate the cross-section Raman measurement. In the last part, the correlation between two different Raman measurement methods was discussed.

### 3.1 Top-down Raman Measurement for Full Stress Components Determination

## 3.1.1 Secular Equation in Sample Coordinates System

Following the discussion in Chapter 2, the following secular equation is deduced with respect to the sample system, where x/[110], y/[1-10], and z/[001]:.

$$\begin{vmatrix} A-\lambda & (p-q)\epsilon_{12}' & 2r\epsilon_{13}' \\ (p-q)\epsilon_{12}' & B-\lambda & 2r\epsilon_{23}' \\ 2r\epsilon_{13}' & 2r\epsilon_{23}' & C-\lambda \end{vmatrix} = 0$$

, where

$$A = p'\epsilon'_{11} + q'(\epsilon'_{22} + \epsilon'_{33})$$

$$B = q'\epsilon'_{11} + p'\epsilon'_{22} + q\epsilon'_{33}$$

$$C = p\epsilon'_{33} + q(\epsilon'_{11} + \epsilon'_{22})$$

$$p' = \frac{p+q}{2} + r, \quad q' = \frac{p+q}{2} - r$$

[3.1]

To obtain a general solution for the secular equation is non-trivial with the presence of all six strain tensor elements. However, the out of plane shear components ( $\epsilon'_{13}$ ,  $\epsilon'_{23}$ ) are usually small because of the zero traction near the surface, and the in-plane shear components ( $\epsilon'_{12}$ ) can also be ignored at certain location for specific structure. In this simplified case the secular matrix is diagonal and the eigenvalues can be directly obtained as:

$$\lambda'_1 = p'\epsilon'_{11} + q'\epsilon'_{22} + q\epsilon'_{33},$$

$\lambda'_2 = q'\epsilon'_{11} + p'\epsilon'_{22} + q\epsilon'_{33},$

$$\lambda'_{3} = q\epsilon'_{11} + q\epsilon'_{22} + p\epsilon'_{33}.$$

[3.2]

If  $\lambda'_1, \lambda'_2, and \lambda'_3$  can be determined in an experiment, three independent strains (and corresponding stress components) could be determined. However, for the conventional Raman measurement only  $\lambda'_3$  is visible due to the limitation of polarization directions of scattered light. [7]

## 3.1.2 Raman Measurements with High Numerical Aperture (NA) Configuration:

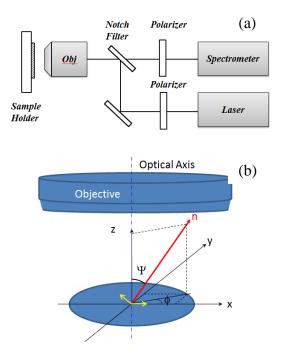

It is possible to take advantage of high numerical apertures objective for Raman measurements in directions other than the z direction on a micrometric scale. Such an experimental set up is schematically described in Fig. 3.1.

Fig. 3.1 (a) Experimental set-up and (b) illustration of optical path for high numerical aperture effect

Following E. Bonera [34], a geometrical optical model is used to describe the scattering process. Although the electric field across the focal volume is not constant due to the physical

nature of light, it is dominant in one direction and the effect from other polarized directions can be ignored. With the sample volume being considered point-like, the scattering light is not influenced by the presence of interface or optical constant inhomogeneity.

In the analysis, the sample coordinates are taken to be x/[110], y/[1-10], z/[001], where z is along the optical axis as shown in Fig. 3.1(b).

The incident light is polarized. As an example, the electric field is assumed to be along [100] direction:

$$\boldsymbol{e}_{i} = \left(\frac{1}{\sqrt{2}}\boldsymbol{e}_{x} + \frac{1}{\sqrt{2}}\boldsymbol{e}_{y}\right)$$

[3.3]

Following the geometrical optic model, if the polarization direction of incident and scattered beams are set to be parallel to each other, the scattered polarization measured for this configuration can be written as

$$\boldsymbol{e}_{s}(\boldsymbol{n}) = \frac{1}{\sqrt{|\boldsymbol{n} \times (\boldsymbol{e}_{z} \times \boldsymbol{e}_{i})|^{2}}} \big( \boldsymbol{n} \times (\boldsymbol{e}_{z} \times \boldsymbol{e}_{i}) \big)$$

$n = \sin \Psi \cos \phi \ e_x + \sin \psi \sin \phi \ e_y + \cos \psi \ e_z$

Thus

$$\boldsymbol{e}_{s}(\boldsymbol{n}) = \frac{1}{N} (\cos\psi \, \boldsymbol{e}_{x} + \cos\psi \, \boldsymbol{e}_{y} - \sin\psi(\cos\phi + \sin\phi) \, \boldsymbol{e}_{z}$$

[3.4]

where

$$N = \sqrt{2\cos^2\psi + \sin^2\psi(\cos\phi + \sin\phi)^2}$$

[3.5]

Considering an excitation with frequency  $\omega_i$ , the measured intensity:

$$I_k(\hbar\omega) = C \int |\boldsymbol{e}'_s(\boldsymbol{n}) \cdot \boldsymbol{R}_k \cdot \boldsymbol{e}_i|^2 d\Omega, k = 1,2,3$$

where C is a constant in the form of:

$$C = \frac{\omega_i^4}{(4\pi\varepsilon)^2 c^4} E_i^2 L_k(\hbar\omega)$$

[3.6]

$L_k$  is the Lorentzian line shape centered in the phonon energy, and  $R_k$  is the Raman tensor of the vibrational mode k (k=1, 2, 3), and is calculated under the sample coordinate system as following:

$$\boldsymbol{R}_{1} = \frac{1}{\sqrt{2}} \begin{pmatrix} 0 & 0 & d \\ 0 & 0 & d \\ d & d & 0 \end{pmatrix}, \quad \boldsymbol{R}_{2} = \frac{1}{\sqrt{2}} \begin{pmatrix} 0 & 0 & d \\ 0 & 0 & -d \\ d & -d & 0 \end{pmatrix}, \quad \boldsymbol{R}_{3} = \begin{pmatrix} d & 0 & 0 \\ 0 & -d & 0 \\ 0 & 0 & 0 \end{pmatrix}$$

[3.7]

Under this condition, the following equation can be derived:

$$I_1 = C \int_0^{\Theta} \int_0^{2\pi} \left(\frac{\sqrt{2}}{N} dsin\psi(\cos\phi + \sin\phi)\right)^2 \sin\psi \, d\phi d\psi = 0.7035 d^2C$$

$$I_2 = I_3 = 0 [3.8]$$

Similarly, the measured intensity for a different vibration mode under different polarization configurations has been calculated and listed in the Table 3.1. Table 3.1 shows that by selecting a certain set of polarization configurations, Mode 1 and Mode 2 can be measured separately from Mode 3.

| $e_i$ (Silicon crystal)                                                                                         | <i>I</i> <sub>1</sub> | <i>I</i> <sub>2</sub> | I <sub>3</sub> |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------|

| $\frac{1}{\sqrt{2}}\boldsymbol{e}_{\boldsymbol{x}} + \frac{1}{\sqrt{2}}\boldsymbol{e}_{\boldsymbol{y}} \ (010)$ | 0.7035                | 0                     | 0              |

| $\frac{1}{\sqrt{2}}e_x - \frac{1}{\sqrt{2}}e_y$ (100)                                                           | 0                     | 0.7035                | 0              |

| <i>e<sub>x</sub></i> (110)                                                                                      | 0.3442                | 0.3442                | 2.2529         |

**Table 3.1** Intensity for different Raman peaks under given polarization configuration

Combining with the eigenvalue solution from the secular equation, it would be possible to determine the stress components separately.

To validate the theory, the following polarization configuration was applied: The incident polarizer and scattering polarizer were parallel, and the incident light was polarized along (010) silicon crystal direction. This specific polarization configuration was chosen because the high numerical aperture effect is a secondary effect, so the signals from this effect will be low compared to that from the conventional Raman measurements (mode 3). Under this polarization configuration, from equation [3.3], the mode 3 is invisible even if there is high numerical aperture effect. In this case, the mode 3 signals will not overwhelm the signals from High NA effect, making it possible to observe other Raman modes.

Different objective lenses were applied to change the numerical aperture during the experiment. In this study, a RENISHAW InVia Raman Microscope system equipped with 532nm wavelength laser is used for the Raman measurements. A 3000 l/mm grating was installed to achieve a high resolution of the Raman peak position. The penetration depth of the 532nm laser is around 0.3µm under the Si surface.

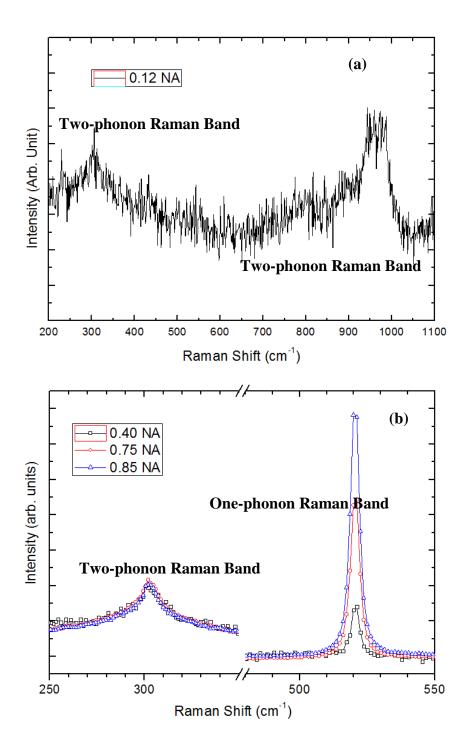

Fig. 3.2(a) shows the Raman spectrum of stress-free Si (100) wafer measured with 5X (NA=0.12) objective lens, 532nm laser and 10mW power. As the conventional Raman measurement predicted in Table 2.1, the one-phonon band is forbidden and can't be observed in the spectra. As the numerical aperture increases, the "forbidden band" appears in the Raman spectra as shown in Fig. 3.2(b). The spectra are normalized to two-phonon Raman band at 300 cm<sup>-1</sup> involving two TA phonons, as the two-phonon Raman band intensity is not sensitive to the NA.

Figure 3.2(c) shows the calculated one-phonon Raman band peak intensity vs. NA. Here, the intensity is normalized by the intensity at NA=0.85 (solid line). The ratio of intensity between NA=0.75 and NA=0.85 is experimentally determined at different laser power.

**Fig. 3.2** (a) Raman Spectrum for bare 100 wafers measured with 5X objective Lens. (b) Raman spectra measured for bare 100 wafer with 20X (NA =0.40), 50X (NA=0.75), 100X (NA=0.85) (c) "forbidden band" intensity as a function of numerical aperture (NA)

#### 3.1.3 Laser power and Accumulation Time Optimization

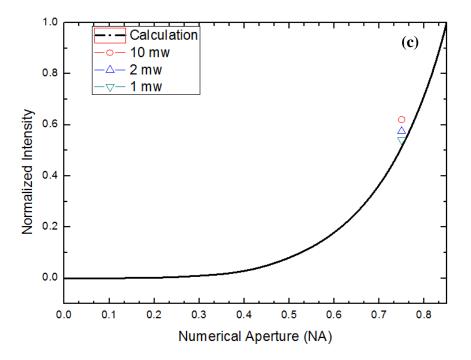

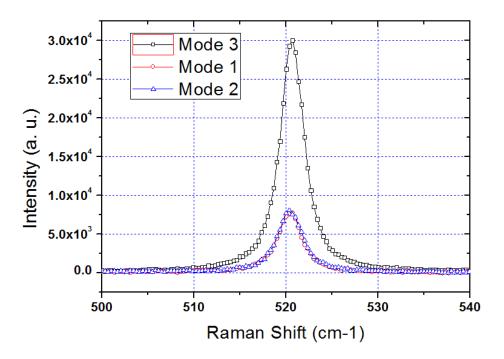

Although mode 1 and mode 2 are observable with high numerical aperture, the signals are weak compared to mode 3. Fig. 3.3 shows a typical silicon Raman peak of [100] stress-free Si wafer for mode 1, 2 and 3. The peak position of three modes should be the same in the absence of stress. Although the accumulation time for mode 1 and 2 was doubled compared to mode 3, the intensity of mode 1 and 2 were still much lower than that of mode 3. Lower intensity may cause high noise background and introduce a larger system error.

Fig. 3.3 Spectrum of different Raman modes in experiment

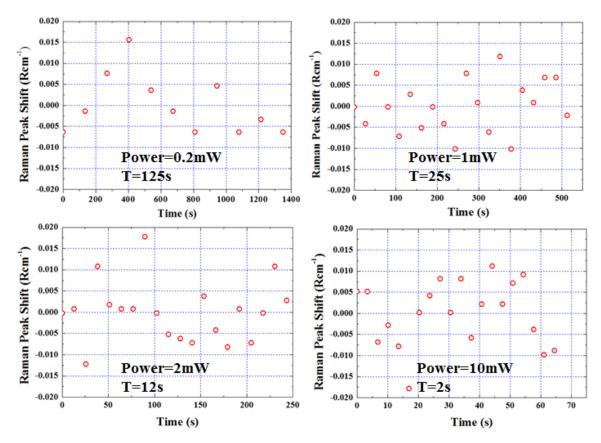

To determine the optimized laser power and accumulation time, and to evaluate the system error for the measurement of mode 1&2, a series of experiments with different laser power and accumulation times were carried out at the same location on a stress free bare wafer. In this case, mode 1 and mode 2 should be degenerated. An example of the results is shown in Fig. 3.4, where the product of laser power and accumulation time was kept constant. As the reference frequency at the same location of silicon wafer should be a constant, the fluctuation in the measurement results should represent the system error. The overall fluctuation increased slightly as the laser power of 1mw showd more stable trend for the first several points; what's more, it showed a lower overall fluctuation ( $\pm 0.015$ cm<sup>-1</sup>). Another concern during the measurement is the local heating due to scanning for an extended time. If the wafer is heated by laser, the Raman peak will shift to the negative side, however, no clear

trend was observed for the laser power of 1mw after 500sec exposure. Based on the consideration above, the laser power of 1mw was chosen as the optimized laser power condition to be applied in the experiments.

Fig. 3.4 Peak Position fluctuation vs. laser power

#### **3.1.4 Experimental Design and Results**

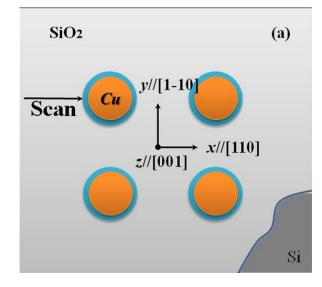

Top-down Raman measurement was applied for a full characterization of the nearsurface stress components. Samples used were [001] silicon wafers with blind TSV arrays embedded on top, and the top surface of Si was covered by a layer of 2  $\mu$ m thick oxide. The diameter of TSV was 5 um, and the depth 55um. Among different TSV arrays, 2 by 2 TSV arrays with a pitch of 10  $\mu$ m were selected for the measurement. Two sets of samples with the same structures were annealed at 200C (Sample A) and 300C (Sample B) in vacuum chamber with 100mtorr with forming gas for 2 hours, respectively, to build up different residual stress levels. The scan path was on the top surface along [110] direction as illustrated in Fig. 3.5(a).

Three specific polarization configurations (as shown in Table 3.1) were chosen to perform Raman measurements on the designed TSV structure. The trends of three different Raman peak shifts were observed corresponding to three different modes mentioned in the theory section, as illustrated in Fig. 3.5(b) Sample A and (c) Sample B. Mode 1, 2 and 3 correspond to the polarization conditions listed in Table 3.1. Mode 3 is the Raman peak shift usually measured in the conventional Raman measurement, and the appearance of mode 1 and mode 2 provide additional information that could be used to deduce the magnitude of all three normal stress components. The experimental results for sample A and B presented a similar trend but different magnitude, which implied that stress/strain distribution was same in sign but higher residual thermal stress was built up in Sample B due to the higher annealing temperature. Detailed stress distribution will be presented with the assistance of FEA simulation.

40

Fig. 3.5 (a) Illustration of scan path along [110] for the 2x2 TSV arrays and Raman peak shifts results along scan path for (b) sample A and (c) sample B

#### **3.1.5** Analysis and Validation

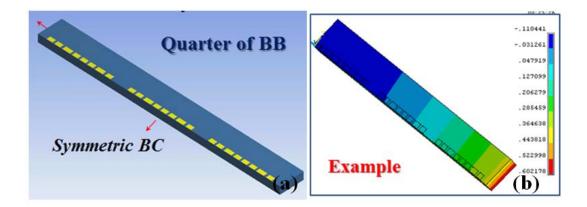

FEA simulation was carried out for better understanding of the near surface stress distribution of the samples. As shown in Figure 3.6(a), only one quarter of the 2 by 2 TSV array structure was chosen with symmetric boundary conditions on the edges. Following the discussion in Chapter 2, the same assumptions and material properties were used. The calculated in-plane shear stress distribution is presented in Fig. 3.6(b).

Fig. 3.6 (a) Modeling of a quarter structure and (b) in-plane shear stress distribution in Si around TSV for 2 by 2 TSV arrays

As demonstrated in the FEA simulations along the scan line shown by the arrow in Fig. 3.6(b), the in-plane shear stress was small and can be ignored. Thus equation [3.2] can be applied to the measurements.

For Raman measurements, the Raman signal is in fact an average of Raman Peak shift of different modes weighted by peak intensity. The peak intensity for separate mode under the specific polarization was determined as shown in Table 3.1. Thus the relation among all stress components and measured Raman signal can be written as:

$$\begin{aligned} \Delta\omega_1 &= -2.30\sigma_{xx} - 0.38\sigma_{yy} - 1.93\sigma_{zz} \\ \Delta\omega_2 &= -0.38\sigma_{xx} - 2.30\sigma_{yy} - 1.93\sigma_{zz} \\ \Delta\omega_3 &= -1.93\sigma_{xx} - 1.93\sigma_{yy} - 0.75\sigma_{zz} \end{aligned}$$

$$[3.9]$$

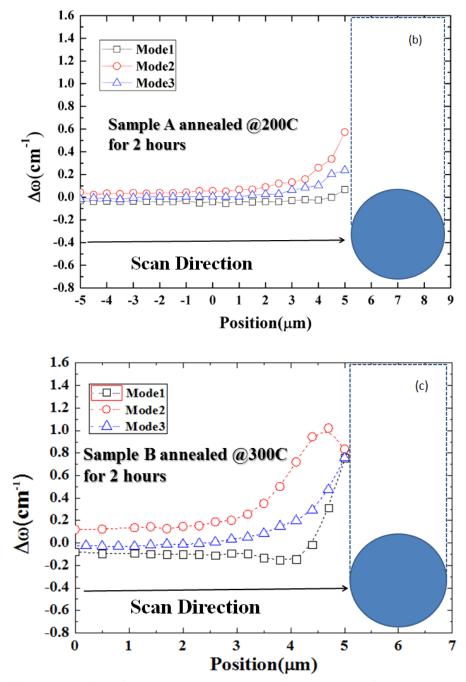

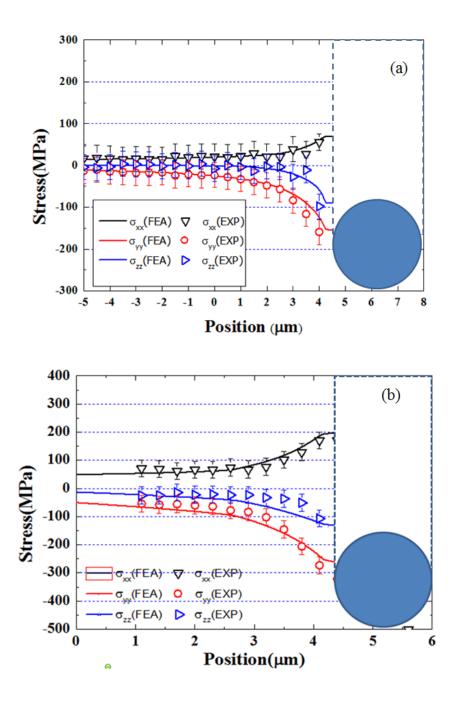

Three normal stress components were calculated by simultaneously solving the three equations resulted from three different Raman measurements. The normal stress components determined by experimental data were plotted in Fig. 3.7 as discrete symbols. With the optimized condition, the accuracy of Raman spectroscopy varied from  $\pm 0.015$ cm<sup>-1</sup> for Mode 3 to  $\pm 0.03$ cm<sup>-1</sup> for Mode 1 and 2, corresponding to 20~30MPa errors in the measured stresses.

Different stress-free temperatures (Reference temperatures) were chosen in the FEA model to fit the experiment results for sample A and sample B. For sample A, a stress free temperature of 100C (-80C thermal load) was chosen, and for sample B, a reference temperature of 300C (-280C thermal load) was chosen. The comparison between FEA simulation and experiment results are plotted in Fig. 3.7. The results showed a reasonable agreement with each other within the range of measurement error. Comparison between the residual stress build up in sample A and B indicated that the stress relaxation mechanisms were stronger (grain growth, creep, surface diffusion. etc.) at 300C. For sample B, a thorough stress relaxation occurred within 2 hours at 300C, which caused a high residual stress built up when cooled down to room temperature. However, for sample A, the stresses were only partially released during the thermal annealing at 200C, which caused a stress free temperature to be lower than 200C.

**Fig. 3.7** Comparison between experimental determined stress distribution and prediction of FEA simulation (a) Sample A annealed at 200C for 2 hours (Thermal load of -80C is used in FEA model) (b) Sample B annealed at 300C for 2 hours (Thermal load of -280C is used in FEA model)

#### 3.2 Cross-section Raman Measurements

As most of 3D TSV structures are fabricated in the (100) wafer, and the vias arrange along [110] directions, the cross-section Raman measurements are different from the top-down Raman measurements. Usually the cross-section is along [110] directions. More Raman modes are enabled, and according to the polarization configuration, different Raman peak shift can be observed. If the shear stress components are ignored, each Raman peak shifts are related to the linear combination of the normal stress components. And with reasonable assumptions, each in-plane stress component can be solved based on the Raman experimental data within the scope of current study.

### 3.2.1 Secular equation for cross section Raman measurements

To investigate the possible visible Raman modes, the secular equations are revisited. The cross-section measurement can be considered equivalently to a Raman measurement on (110) wafers. The secular equation will be discussed in the following Cartesian coordinate system: the x-axis is along the [110] direction, y-axis is along [001] and z axe is along [1-10]. By similar transformation as in section 3.1, the secular equation will be in the following form:

$$\begin{vmatrix} p'\epsilon_{11}' + q\epsilon_{22}' + q'\epsilon_{33}' - \lambda & 2r\epsilon_{12}' & (p-q)\epsilon_{13}' \\ 2r\epsilon_{12}' & q(\epsilon_{11}' + \epsilon_{33}') + p\epsilon_{22}' - \lambda & 2r\epsilon_{23}' \\ (p-q)\epsilon_{13}' & 2r\epsilon_{23}' & q'\epsilon_{11}' + q\epsilon_{22}' + p'\epsilon_{33}' - \lambda \end{vmatrix} = 0$$

where

$n \perp a$

$$p' = \frac{p+q}{2} + r$$

$$q' = \frac{p+q}{2} - r$$

[3.10]

where p, q, and r are called Raman phonon deformation tensor, which are constants for Silicon. Again, specifically for the scope of the current measurement, the shear components don't contribute too much to the observable Raman peak shift (as will be shown in the later FEA simulation). By ignoring all the shear components in the above secular equation, the solution can be easily obtained as:

$$\lambda_{1} = p'\epsilon_{11}' + q\epsilon_{22}' + q'\epsilon_{33}'$$

$$\lambda_{2} = q\epsilon_{11}' + p'\epsilon_{22}' + q\epsilon_{33}'$$

$$\lambda_{3} = q'\epsilon_{11}' + q\epsilon_{22}' + p'\epsilon_{33}'$$

[3.11]

For each eigenvalue,  $\Delta \omega = \omega - \omega_0 = \frac{\lambda}{2\omega_0}$ , where  $\omega_0$  is the Raman peak position for stress free silicon. Combining the solution with Hook's law, the relation between the Raman shifts and the stress distribution on cross-sectional silicon surface can be determined.

$$\Delta \omega_{1} = -2.31\sigma_{xx} - 1.93\sigma_{yy} - 0.38\sigma_{zz}$$

$$\Delta \omega_{2} = -1.93\sigma_{xx} - 0.76\sigma_{yy} - 1.93\sigma_{zz}$$

$$\Delta \omega_{3} = -0.38\sigma_{xx} - 1.93\sigma_{yy} - 2.31\sigma_{zz}$$

[3.12]

The intensity of different Raman modes can be determined by equation [3.6], The Raman tensor under the new coordinates system is:

$$R_{1} = \frac{1}{\sqrt{2}} \begin{bmatrix} 0 & d & 0 \\ d & 0 & -d \\ 0 & -d & 0 \end{bmatrix}, \qquad R_{2} = \frac{1}{\sqrt{2}} \begin{bmatrix} 0 & d & 0 \\ d & 0 & d \\ 0 & d & 0 \end{bmatrix}, \qquad R_{3} = \begin{bmatrix} d & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & -d \end{bmatrix}$$

[3.13]

Due to the surface roughness introduced by the sample preparation, the scattering light collected from the high numerical aperture effect was not enough to provide additional information in this kind of measurement. Although different Raman modes cannot be separated out, additional information could still be obtained by altering the polarization configuration during the measurement.

Table 3.2 shows an example of normalized intensity for different Raman modes under the specific polarization conditions. Under polarization configuration in row 1, the Raman peak shift observed was from the contribution of longitudinal mode (LO), but under the polarization configuration in row 2, only a mixture of two TO modes could be observed. According to the calculation, the ratio of those two TO modes was 1:1.

**Table 3.2** Intensity for different Raman peaks vs. Polarization (Cross-Section Raman)

| e <sub>i</sub>               | <i>e</i> <sub>s</sub>         | I <sub>1</sub> | <i>I</i> <sub>2</sub> | I <sub>3</sub> |

|------------------------------|-------------------------------|----------------|-----------------------|----------------|

| <i>e<sub>x</sub></i> Si(110) | <i>e<sub>x</sub></i> Si(110)  | 0              | 0                     | 1              |

| <i>e<sub>x</sub></i> Si(110) | <i>e</i> <sub>y</sub> Si(001) | 0.5            | 0.5                   | 0              |

Based on the calculated intensities of different modes, the relation between the stress distribution and the observed Raman peak shifts could be expressed as shown in Table 3.3.

Table 3.3 Raman peak shift vs. stress distribution under different polarization

| e <sub>i</sub>               | es                            | $\Delta \omega = \sum_{i} I_{i} \omega_{i}$                            |

|------------------------------|-------------------------------|------------------------------------------------------------------------|

| <i>e<sub>x</sub></i> Si(110) | <i>e<sub>x</sub></i> Si(110)  | $\Delta \omega = -0.38\sigma_{xx} - 1.93\sigma_{yy} - 2.31\sigma_{zz}$ |

| <i>e<sub>x</sub></i> Si(110) | <i>e</i> <sub>y</sub> Si(001) | $\Delta \omega = -2.12\sigma_{xx} - 1.35\sigma_{yy} - 1.16\sigma_{zz}$ |

Usually, the out of plane stress components for the cross-sectional sample were small enough to be ignored (as will be shown in FEA in section 3.2.3). With this assumption, the two in-plane stress components can be determined from the experimental Raman data under different polarization configuration.

#### **3.2.2 Experimental samples and Sample preparation**

In order to compare with experimental results from the bending beam method (will be discussed in section 3.3), another set of silicon beams with blind TSV arrays were selected for the cross-section Raman measurements. The geometry of the sample is illustrated in Fig. 3.8. The blind TSVs were embedded in (100) wafers, and aligned along the [110] direction, with diameters of 5.5µm and depth of 55µm. The pitch of TSV array was 40µm. Samples were covered by a thin layer of oxide with a thickness of 0.3µm. Sample 1 and 2 with the same structure were placed in a vacuum chamber with 100mtorr forming gas to avoid oxidation. The sample 1 were heated up slowly with a rate of 2°C/min to a maximum temperature of 200C and slowly cooled down to the room temperature. Sample 2 experienced 3 thermal cycles: RT $\rightarrow$  200°C  $\rightarrow$  350°C $\rightarrow$  RT $\rightarrow$  400C $\rightarrow$ RT with the same heating ramp rate of 2°C/min. The purpose of such thermal treatment was to carry out another independent experiment named "bending beam" for validation, the details will be discussed in the next section.

Fig. 3.8 Illustration of the Geometry of Sample 1 and Sample 2