Copyright

by

Bailey Anderson Yin

2015

# The Dissertation Committee for Bailey Anderson Yin Certifies that this is the approved version of the following dissertation:

# Fabrication of Silicon Nanowires with Controlled Nano-scale Shapes Using Wet Anisotropic Etching

**Committee:**

SV Sreenivasan, Supervisor

Sanjay K Banerjee

Roger T Bonnecaze

Michael A Cullinan

Wei Li

# Fabrication of Silicon Nanowires with Controlled Nano-scale Shapes Using Wet Anisotropic Etching

by

Bailey Anderson Yin, B.S.M.E.; M.S.E.

### Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### **Doctor of Philosophy**

The University of Texas at Austin August 2015

# Dedication

I dedicate this dissertation to my new niece, Buttercup.

#### Acknowledgements

I would like to thank Dr. S. V. Sreenivasan for introducing me to the world of nano-precision and for having patience with me for the last several years. I would also like to thank the other members of the High Throughput Nano-manufacturing (HTPN) lab especially Anshuman Cherala for his help fabricating the diamond template, Akhila Mallavarapu for her help with fabricating and measuring the ultra-capacitors, Austin Lane for his help with the sublimation process, Dr. Marlon Menezes (Molecular Imprints) for his help with the potassium hydroxide work, Dr. Vik Singh (Molecular Imprints) for his advice on process design, and Dr. Shrawan Singhal for his general advice and help with editing this document. I would also like to thank the cleanroom staff at the Microelectronics Research building at Pickle Research Campus especially Ricardo Garcia for his technical expertise. I would also like to thank the NASCENT Center for my funding as well as for the knowledge and lab resources. Lastly, I would like to thank my family, housemates, and friends for their support and encouragement.

# Fabrication of Silicon Nanowires with Controlled Nano-scale Shapes Using Wet Anisotropic Etching

Bailey Anderson Yin, PhD The University of Texas at Austin, 2015

Supervisor: SV Sreenivasan

Silicon nanowires can enable important applications in energy and healthcare such as biochemical sensors, thermoelectric devices, and ultra-capacitors. In the energy sector, for example, as the need for more efficient energy storage continues to grow for enabling applications such as electric vehicles, high energy storage density capacitors are being explored as a potential replacement to traditional batteries that lack fast charge/discharge rates as well as have shorter life cycles. Silicon nanowire based ultracapacitors offer increased energy storage density by increasing the surface area per unit projected area of the electrode, thereby allowing more surface "charge" to reside. The motivation behind this dissertation is the study of low-cost techniques for fabrication of high aspect ratio silicon nanowires with controlled geometry with an exemplar application in ultra-capacitors.

Controlled transfer of high aspect ratio, nano-scale features into functional device layers requires anisotropic etch techniques. Dry reactive ion etch techniques are commonly used since most solution-based wet etch processes lack anisotropic pattern transfer capability. However, in silicon, anisotropic wet etch processes are available for the fabrication of nano-scale features, but have some constraints in the range of geometry of patterns that they can address. While this lack of geometric and material versatility precludes the use of these processes in applications like integrated circuits, they can be potentially realized for fabricating nanoscale pillars. This dissertation explores the geometric limitations of such inexpensive wet anisotropic etching processes and develops additional methods and geometries for fabrication of controlled nano-scale, high aspect ratio features. Jet and Flash Imprint Lithography (J-FIL<sup>TM</sup>) has been used as the preferred pre-etch patterning process as it enables patterning of sub-50 nm high density features with versatile geometries over large areas. Exemplary anisotropic wet etch processes studied include Crystalline Orientation Dependent Etch (CODE) using potassium hydroxide (KOH) etching of silicon and Metal Assisted Chemical Etching (MACE) using gold as a catalyst to etch silicon.

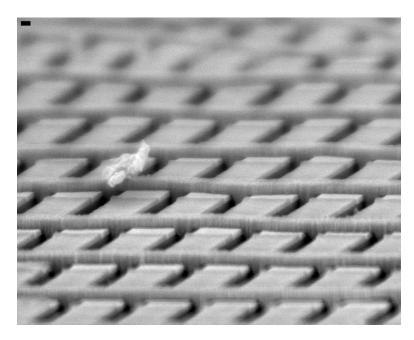

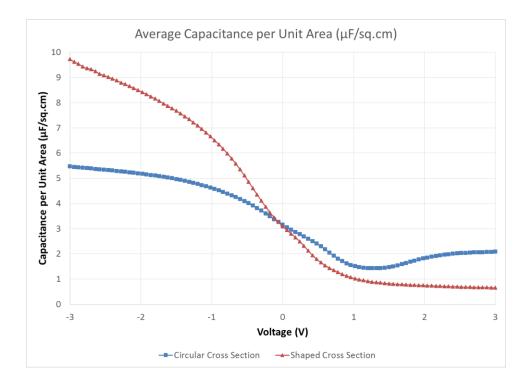

Experiments with CODE indicate that the geometric limitations of the etch process prevent the fabrication of high aspect ratio nanowires without adding a prohibitive number of steps to protect the pillar geometry. On the other hand, MACE offers a relatively simple process for fabricating high aspect ratio pillars with unique cross sections, and has thus been pursued to fabricate fully functional electrostatic capacitors featuring both circular and diamond-shaped nano-pillar electrodes. The capacitance of the diamond-shaped nano-pillar capacitor has been shown to be  $\sim$ 77.9% larger than that of the circular cross section due to the increase in surface area per unit projected area. This increase in capacitance approximately matches the increase calculated using analytical models. Thus, this dissertation provides a framework for the ability to create unique sharp cornered nanowires that can be explored further for a wider variety of cross sections.

## **Table of Contents**

| List of Tables                                                                    | xi  |

|-----------------------------------------------------------------------------------|-----|

| List of Figures                                                                   | xii |

| Chapter 1: Introduction                                                           | 1   |

| 1.1 Motivation                                                                    | 2   |

| 1.2 Nano-patterning Processes                                                     | 3   |

| 1.3 Wet Anisotropic Etching                                                       | 4   |

| 1.3.1 <u>Crystallographic Orientation Dependent Etching</u> (CODE)                | 5   |

| 1.3.1.1 Etching Mechanism of KOH                                                  | 6   |

| 1.3.1.2 CODE of Si using KOH                                                      | 7   |

| 1.3.2 <u>Metal Assisted Chemical Etching (MACE)</u>                               | 10  |

| 1.3.2.1 MACE Mechanism for c-Si                                                   | 11  |

| 1.3.3 CODE and MACE Comparison                                                    | 12  |

| 1.4 Proposed Nano-fabrication processes                                           | 15  |

| 1.4.1 iCODE Process                                                               | 15  |

| 1.4.2 iMACE Process                                                               | 16  |

| 1.5 Research and Structure of the Dissertation                                    | 17  |

| Chapter 2: Imprint-enabled Crystallographic Orientation Dependent Etching (iCODE) | 18  |

| 2.1 Preliminary Experiments                                                       | 18  |

| 2.1.1 Dots (convex hard mask)                                                     | 19  |

| 2.1.2 Lines                                                                       | 21  |

| 2.1.3 Rhombus with Sides Aligned to vertical (111) planes                         | 24  |

| 2.2 Problem Fundamentals                                                          | 28  |

| 2.2.1 Alignment                                                                   | 28  |

| 2.2.2 Convex Corner Undercutting – Edge Parasitics                                | 31  |

| 2.2.2.1 Corner Compensation to Overcome Undercutting                              | 32  |

| 2.2.2.2 Edge Protection to Overcome Undercutting                                  | 35  |

| 2.2.3 Non-vertical Etch Stop Planes                                               | 39  |

| 2.2.3.1 Methods of Overcoming the Etch Depth Restriction                                   |       |

|--------------------------------------------------------------------------------------------|-------|

| Concave Features                                                                           |       |

| 2.3 Conclusions                                                                            | 45    |

| Chapter 3: Imprint-enabled Metal Assisted Chemical Etching (iMACE)                         | 47    |

| 3.1 Preliminary Experiments                                                                | 47    |

| 3.2 Problem Fundamentals                                                                   | 51    |

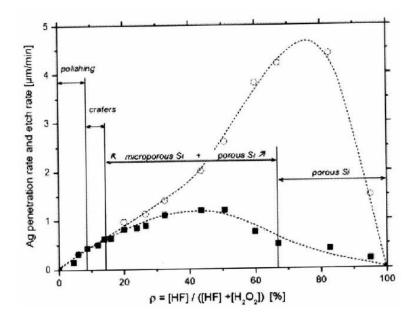

| 3.2.1 Etch Solution Composition                                                            | 51    |

| 3.2.1.1 Microporous Silicon                                                                | 52    |

| 3.2.1.2 Preferential Etch Direction (Porous Silicon)                                       | 52    |

| 3.2.2 Metal Catalyst Geometry                                                              | 54    |

| 3.2.2.1 3D Etch Motion                                                                     | 54    |

| 3.2.2.2 Catalyst Mechanical Stability                                                      | 58    |

| 3.3 Conclusions                                                                            | 60    |

| Chapter 4: Fabrication of Silicon Nanowires with High Surface Area per U<br>Projected Area |       |

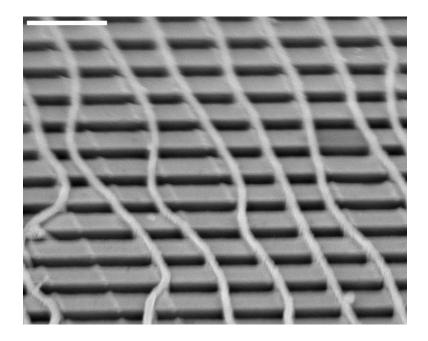

| 4.1 Patterning Gold Mesh for MACE Process                                                  | 61    |

| 4.1.1 Wet Etch of Gold                                                                     | 62    |

| 4.1.2 Dry Etch of Gold                                                                     | 64    |

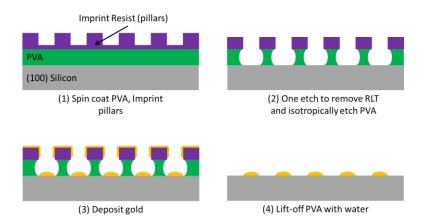

| 4.1.3 Bi-layer Lift-off Process                                                            | 66    |

| 4.1.4 Reverse Tone Bi-layer Lift-off Process                                               | 68    |

| 4.1.5 Simplified Bi-layer Lift-off Process                                                 | 72    |

| 4.2 Increasing Surface Area per Unit Projected Area Through High A<br>Ratio Features       | -     |

| 4.2.1 Forces Responsible for Collapsing Pillars                                            | 77    |

| 4.2.2 Forces Responsible for Keeping Collapsed Nanowires Adl<br>Together                   |       |

| 4.2.3 Mitigating Feature Collapse Induced by Capillary Forces of Drying                    | -     |

| 4.2.3.1 Evaporation Drying with Low Surface Tension Flu                                    | ids82 |

| 4.2.3.2 Critical Point Drying (CPD)                                                        | 83    |

| 4.2.3.3 Sublimation                                                                        | 84    |

| 4.2.3.4 Silanization85                                                                                                        | 5 |

|-------------------------------------------------------------------------------------------------------------------------------|---|

| 4.3 Increasing Surface Area per Unit Projected Area Through Unique Featur<br>Geometry                                         |   |

| 4.3.1 Other Unique Cross Section Geometries                                                                                   | 5 |

| 4.4 Using Ultra-capacitors to Validate the Increase in Surface Area per Unit<br>Projected Area due to Unique Feature Geometry |   |

| 4.4.1 Ultra-capacitor Background87                                                                                            | 7 |

| 4.4.2 Capacitor Fabrication                                                                                                   | l |

| 4.4.3 Comparison of Capacitance for Circular and Diamond Cross Sec<br>Geometry                                                |   |

| 4.4.3.1 Analytical Calculations                                                                                               | 2 |

| 4.4.3.2 Experimental Results                                                                                                  | 3 |

| Chapter 5: Conclusions and Future Work                                                                                        | 5 |

| 5.1 Conclusions                                                                                                               | 5 |

| 5.2 Future Work                                                                                                               | ) |

| Appendix: Details for Nanowire Fabrication using the Simplified Bi-layer Lift-off<br>Process                                  |   |

| References                                                                                                                    | 2 |

## List of Tables

| Table 1-1: Comparison of Anisotropic Wet Etchants                                   |  |

|-------------------------------------------------------------------------------------|--|

| Table 1-2: General comparison of CODE and MACE.    13                               |  |

| Table 1-3: Comparison between CODE and MACE of mask features (details in            |  |

| Chapter 2 and Chapter 3)14                                                          |  |

| Table 2-1: Purpose and results of etching of the preliminary experiment mask        |  |

| geometries19                                                                        |  |

| Table 4-1: Calculated capacitances per unit projected area for circular and diamond |  |

| cross section nanowire based capacitors                                             |  |

| Table 4-2: Results of experimental data collected of circular cross section versus  |  |

| diamond cross section capacitors                                                    |  |

# List of Figures

| Figure 1-1: Diagram showing isotropic versus anisotropic etching                                                 |

|------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Examples of miller indices                                                                           |

| Figure 1-3: Anisotropically etched features in (100) Si wafers                                                   |

| Figure 1-4: Anisotropically etched features in (110) Si wafers9                                                  |

| Figure 1-5: Hydrogen terminated bonds are the dangling bonds10                                                   |

| Figure 1-6: Back bonds and dangling bonds are denoted for a surface atom A on the                                |

| surface represented by the green plane10                                                                         |

| Figure 1-7: Schematic of MACE reactions                                                                          |

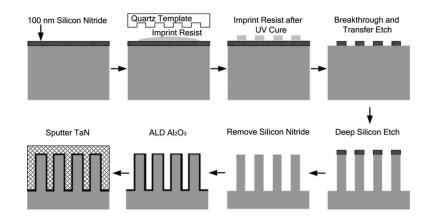

| Figure 1-8: Process flow for J-FIL <sup>™</sup> 15                                                               |

| Figure 1-9: Example process flow for imprint bilayer lift-off process17                                          |

| Figure 2-1: Radial pattern of $\sim$ 230 nm dots in Si <sub>3</sub> N <sub>4</sub> hard mask on Si. Scale bar is |

| 1 μm20                                                                                                           |

| Figure 2-2: SEM image showing the undercutting of the hard mask. Scale bar is                                    |

| 100 nm                                                                                                           |

| Figure 2-3: Pyramid features (hillocks) remaining just after the hard mask detached.                             |

| Scale bar is 100 nm                                                                                              |

| Figure 2-4: Well aligned gratings with minimal undercutting. Interface between Si                                |

| and $SiO_2$ marked with a dashed line. Scale bar is 100 nm22                                                     |

| Figure 2-5: Etched gratings with slight misalignment showing more undercutting of                                |

| the hard mask. Scale bar is 100 nm23                                                                             |

| Figure 2-6: High aspect ratio trenches. Scale bar is 1 µm                                                        |

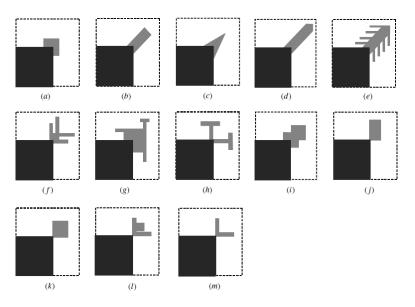

| Figure 2-7: Process flow for rhombus shape mask double patterning. (a) (110) Si      |  |  |

|--------------------------------------------------------------------------------------|--|--|

| wafer (b) SiO2 hard mask growth (c) Gratings patterned and etched into               |  |  |

| hard mask (d) Planarization with polymer (e) Gratings rotated by                     |  |  |

| 109.47° patterned and etched into hard mask25                                        |  |  |

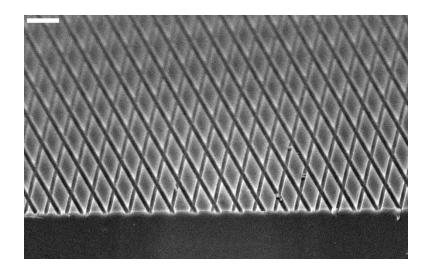

| Figure 2-8: Top-down SEM image of the double patterned hard mask. Scale bar is       |  |  |

| 1 μm26                                                                               |  |  |

| Figure 2-9: Visible undercutting of mask after 20 sec KOH etch. Scale bar is 100 nm. |  |  |

|                                                                                      |  |  |

| Figure 2-10: Undercutting of mask after 20 sec KOH etch with hard mask removed.      |  |  |

| Scale bar is 100 nm                                                                  |  |  |

| Figure 2-11: Top-down view of undercutting from KOH etching with the hard mask       |  |  |

| removed. The dashed lines are the (111) planes where the etch process                |  |  |

| was thought to stop. The four arrows show how the corners etch. Scale                |  |  |

| was mought to stop. The four arrows show now the conners etch. Searc                 |  |  |

| bar is 100 nm                                                                        |  |  |

|                                                                                      |  |  |

| bar is 100 nm27                                                                      |  |  |

| bar is 100 nm                                                                        |  |  |

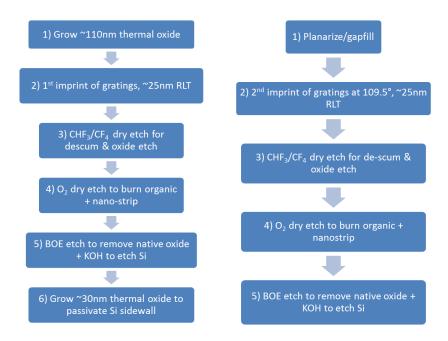

| Figure 2-19: | Examples of convex corner compensation designs                                                    | 34    |

|--------------|---------------------------------------------------------------------------------------------------|-------|

| Figure 2-20: | Process flow for edge protection using two sequential sets of imprin                              | ıt,   |

|              | dry etch, and KOH wet etch steps                                                                  | 35    |

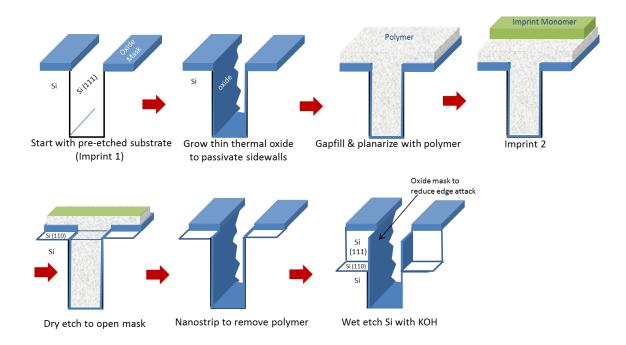

| Figure 2-21: | : Graphic depicting the new process flow starting after the initial set of                        | of    |

|              | gratings were etched into silicon                                                                 | 36    |

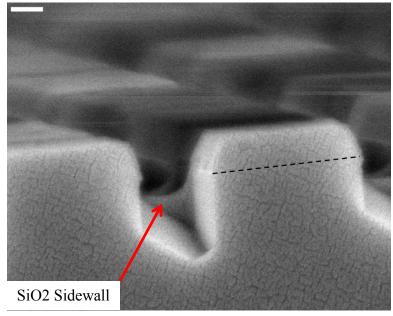

| Figure 2-22: | SEM image of the features after the second set of gratings are etche                              | d but |

|              | before the SiO2 hard mask and side wall have been removed. Interfa                                | ace   |

|              | between Si and $SiO_2$ marked with a dashed line. Scale bar is 100 nm                             | n.37  |

| Figure 2-23: | Features created by KOH etching using two imprint and two etch st                                 | eps   |

|              | after a buffered oxide etch (BOE) to remove oxides. Scale bar is 10                               | 0 nm. |

|              |                                                                                                   | 38    |

| Figure 2-24: | Features created by KOH etching using two imprint and two etch st                                 | eps   |

|              | after a buffered oxide etch (BOE) to remove oxides. Scale bar is 10                               | 0 nm. |

|              |                                                                                                   | 38    |

| Figure 2-25: | A SEM photo and schematic of the final shape of etched pits in (100                               | 0)-   |

|              | silicon                                                                                           | 39    |

| Figure 2-26: | Etched features are defined by four vetical (111) planes and two slo                              | ped   |

|              | (111) planes shown.                                                                               | 40    |

| Figure 2-27: | Graphic of the dependence of max etch depth on mask size                                          | 1     |

| Figure 2-28: | : SEM image of etched trenches shows the non-vertical (111) planes                                |       |

|              | restricting etch depth near their line ends. Scale bar is 1 $\mu$ m                               | 1     |

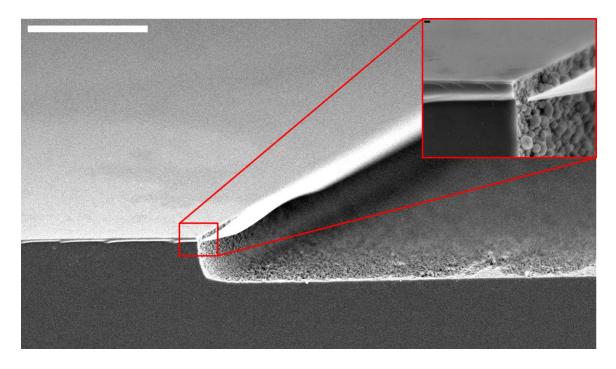

| Figure 2-29: | : Collapsed SiO <sub>2</sub> sidewall after ultra-sonication. Scale bar is 1 $\mu$ m <sup>4</sup> | 12    |

| Figure 2-30: | : Collapsed SiO <sub>2</sub> sidewall after ultra-sonication. Scale bar is 100 nm.                | 43    |

| Figure 2-31: New process flow starting after planarization and imprint utilizing           |  |  |

|--------------------------------------------------------------------------------------------|--|--|

| silicon containing resist to act as a mask for an organic etch to                          |  |  |

| selectively remove the SiO <sub>2</sub> sidewall44                                         |  |  |

| Figure 2-32: Delamination of silicon containing resist features. Scale bar is 100 nm.      |  |  |

|                                                                                            |  |  |

| Figure 2-33: Delamination of silicon containing resist features. Scale bar is 1 $\mu$ m.45 |  |  |

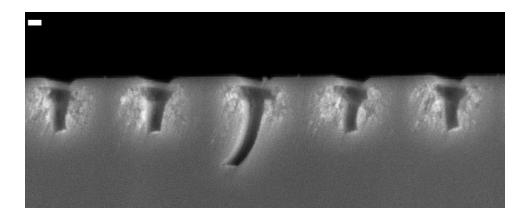

| Figure 3-1: Attempt at etching gratings using a silver iMACE process. Silver               |  |  |

| nucleation present on the sidewalls shown in inset. Scale bar is 10 $\mu$ m.               |  |  |

|                                                                                            |  |  |

| Figure 3-2: Gold MACE of gratings where the etch process switches from vertical to         |  |  |

| the [100] direction. Microporous silicon present on the sidewalls at the                   |  |  |

| top of the trenches. Scale bar is 100 nm                                                   |  |  |

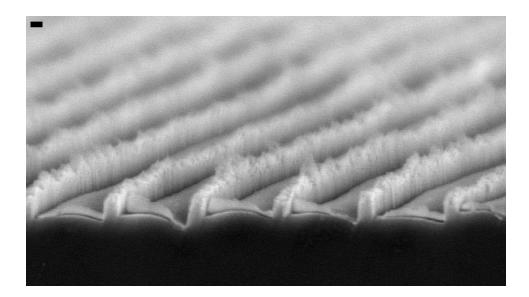

| Figure 3-3: SEM image of wider trenches etched with iMACE for 40 sec. Gold                 |  |  |

| delamination visible at the bottom of trench due to cleaving. Scale bar is                 |  |  |

| 100 nm                                                                                     |  |  |

| Figure 3-4: SEM image of wider trenches etched with iMACE for 80 sec. Gold                 |  |  |

| delamination visible at the bottom of trench due to cleaving. Scale bar is                 |  |  |

| 100 nm                                                                                     |  |  |

| Figure 3-5: Etch regimes for MACE. Open circles: penetration rate of Ag                    |  |  |

| nanoparticles. Filled squares: HF-H <sub>2</sub> O <sub>2</sub> etch rate                  |  |  |

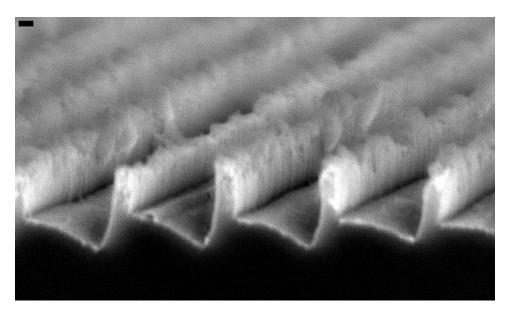

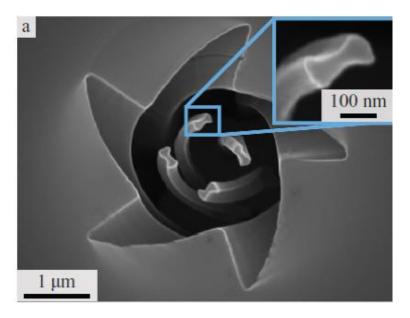

| Figure 3-6: Silicon etched from multiple sides using MACE                                  |  |  |

| Figure 3-7: A spiral fabricated by the in-plane rotation of a square catalyst with         |  |  |

| asymmetric extrusions                                                                      |  |  |

| Figure 3-8: A spiral fabricated by the in-plane rotation of a star catalyst with           |  |  |

| asymmetric extrusions                                                                      |  |  |

| Figure 3-9: SEM image of initial nano-particle catalyst (a), top-down view (b) and             |

|------------------------------------------------------------------------------------------------|

| cross section view (c) after the MACE process                                                  |

| Figure 3-10: Diagram depicting the change in etch width from a bending catalyst. <sup>72</sup> |

|                                                                                                |

| Figure 3-11: Diffusion of MACE reactants and products from edges to the center of              |

| the catalyst                                                                                   |

| Figure 3-12: Diffusion of MACE reactants and products through a porous catalyst.               |

|                                                                                                |

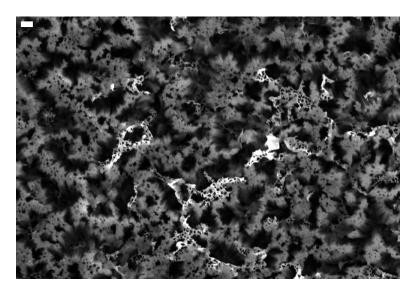

| Figure 4-1: Over etched gold mesh showing non-continuous metal catalyst. Scale bar             |

| is 200 nm63                                                                                    |

| Figure 4-2: Result of MACE using the over etched gold mesh. Scale bar is 1 $\mu$ m.63          |

| Figure 4-3: Gold mesh fabricated using an inductively coupled plasma (ICP) etch.               |

| Scale bar is 200 nm                                                                            |

| Figure 4-4: Irregular pillars etched using MACE after dry etching of gold to form a            |

| continuous mesh. Scale bar is 100 nm                                                           |

| Figure 4-5: Irregular pillars etched using MACE after dry etching of gold to form a            |

| continuous mesh. Feature clumping can be seen. Scale bar is 1 $\mu$ m.65                       |

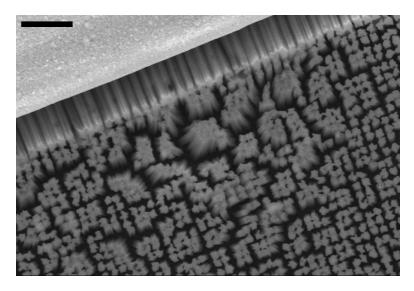

| Figure 4-6: Cross section SEM of 1.7 $\mu$ m tall irregular pillars etched using MACE          |

| after dry etching of gold. Scale bar is 1 µm66                                                 |

| Figure 4-7: Process flow of bi-layer lift-off using a template that prints holes in the        |

| resist67                                                                                       |

| Figure 4-8: Silspin <sup>™</sup> pillars before Ti/Au deposition. Scale bar is 200 nm67        |

| Figure 4-9: Gold catalyst mesh fabricated using bi-layer lift-off process. Scale bar is        |

| 200 nm                                                                                         |

| Figure 4-10: Nanowires fabricated using gold mesh fabricated using bi-layer lift-off          |

|-----------------------------------------------------------------------------------------------|

| process. Scale bar is 200 nm                                                                  |

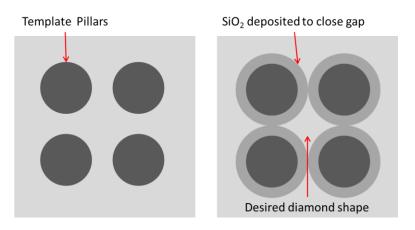

| Figure 4-11: Diamond shape created by ALD deposition on template with circular                |

| nanoscale pillars                                                                             |

| Figure 4-12: Reverse tone bi-layer lift-off process with resist pillars instead of holes.     |

|                                                                                               |

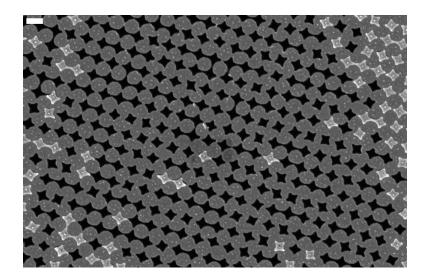

| Figure 4-13: Gold mesh with diamond patterns. Defects include connected diamonds,             |

| rotated diamonds, and incomplete lift-off. Scale bar is 200 nm71                              |

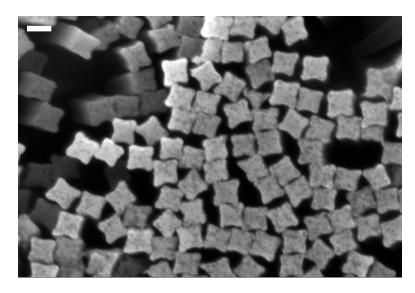

| Figure 4-14: Diamond pillars created by gold mesh. Scale bar is 100 nm                        |

| Figure 4-15: Diamond pillars with defects resulting from imperfect catalyst mesh.             |

| Scale bar is 200 nm                                                                           |

| Figure 4-16: Simplified bi-layer lift-off process where SiO <sub>2</sub> hard mask is removed |

| and the selectivity between the imprint resist and PVA only needs one                         |

| polymer etch to create a sufficient overhang for the gold deposition.73                       |

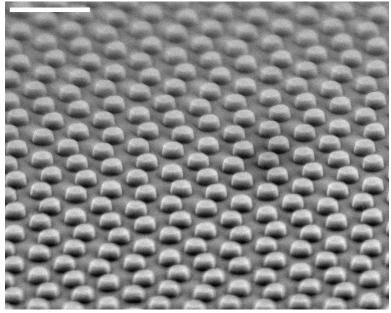

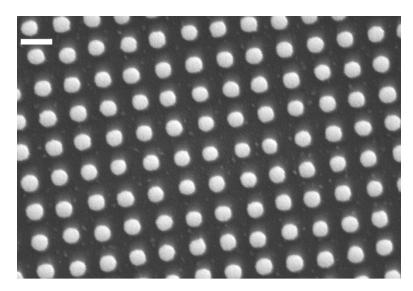

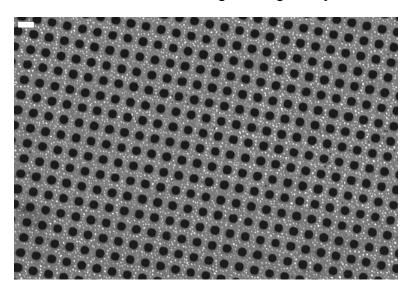

| Figure 4-17: Gold mesh with circular holes created using simplified process. Scale            |

| bar is 200 nm                                                                                 |

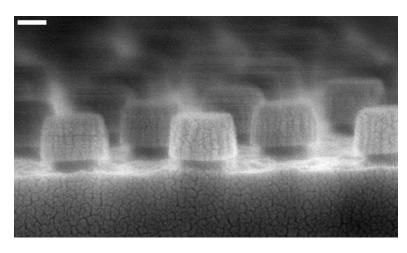

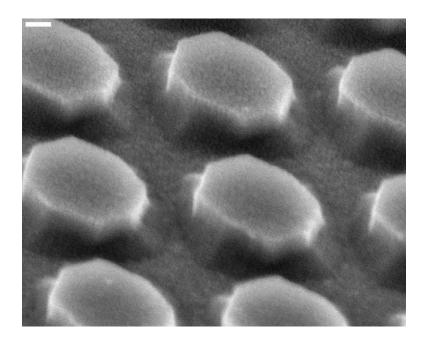

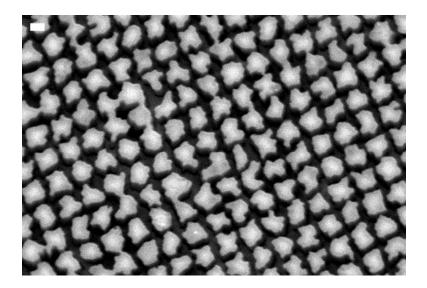

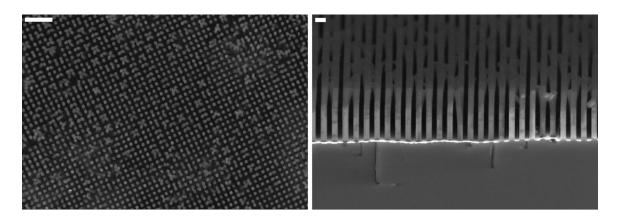

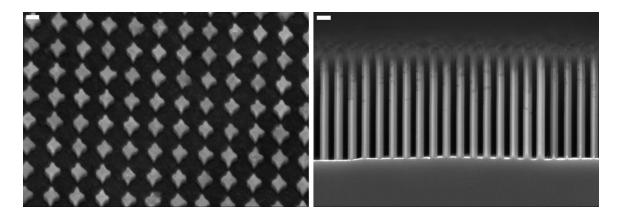

| Figure 4-18: (Left) Top down SEM of pillars etched using simplified circular mesh.            |

| Scale bar is 1 $\mu$ m. (Right) Cross section SEM of pillars etched using                     |

| simplified circular mesh. Scale bar is 200 nm                                                 |

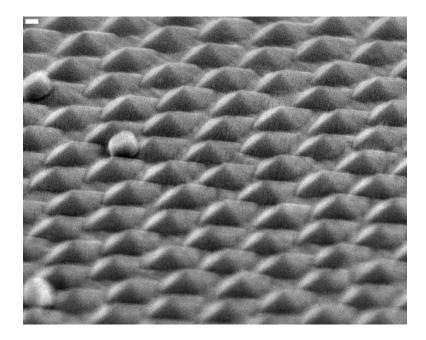

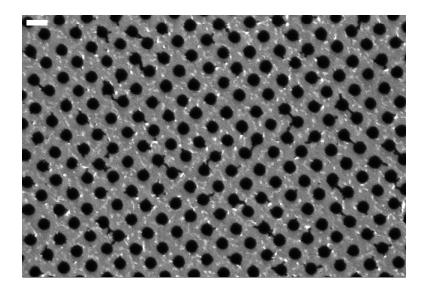

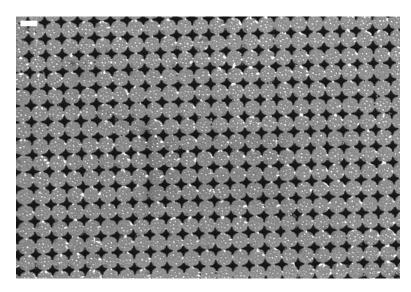

| Figure 4-19: Gold mesh with diamond holes created using simplified process. Scale             |

| bar is 200 nm                                                                                 |

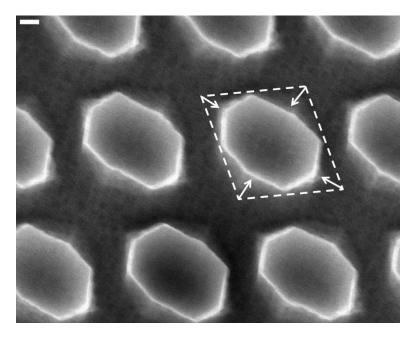

| Figure 4-20: (Left) Top down SEM of pillars etched using simplified diamond mesh.             |

| Scale bar is 100 nm. (Right) Cross section SEM of pillars etched using                        |

| simplified diamond mesh. Scale bar is 200 nm                                                  |

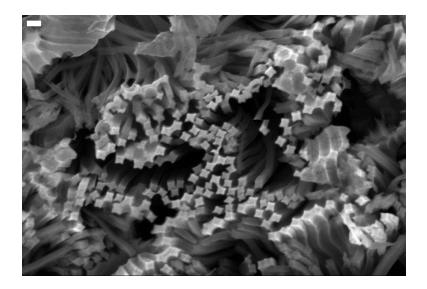

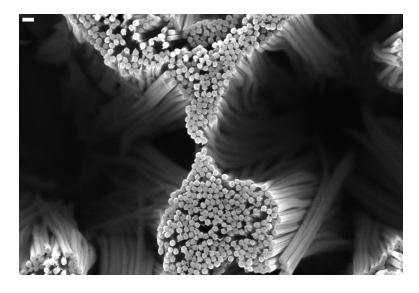

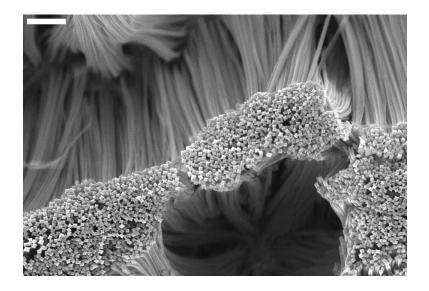

| Figure 4-21: Cross section of collapsed irregular pillars. Scale bar is 1 µm76                |

| Figure 4-22: | 2: Top down view of collapsed circular pillars. Scale bar is 200 nm76   |     |

|--------------|-------------------------------------------------------------------------|-----|

| Figure 4-23: | 3: Top down view of collapsed diamond pillars. Scale bar is 1 $\mu$ m77 |     |

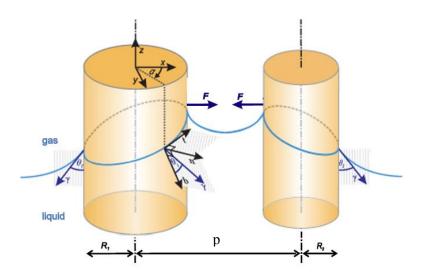

| Figure 4-24: | Boundary conditions used to calculate the meniscus profile for two      |     |

|              | cylinders7                                                              | 9   |

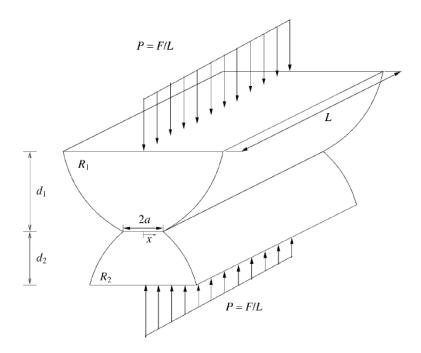

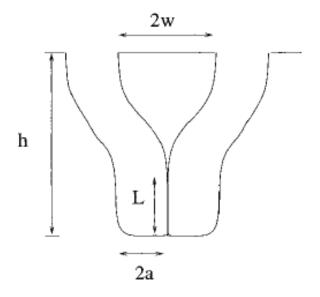

| Figure 4-25: | Contact width for two deforming cylinders                               | 1   |

| Figure 4-26: | Bending due to contact of two pillars                                   | 1   |

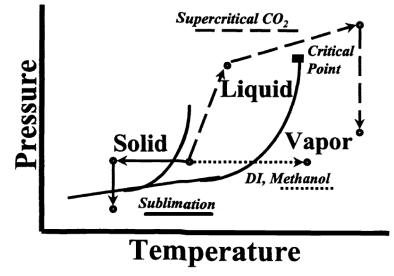

| Figure 4-27: | Three drying methods displayed on a phase diagram                       | 2   |

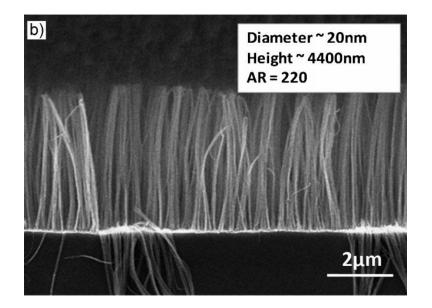

| Figure 4-28: | Nano-wires with aspect ratio of 220 using CPD patterned with            |     |

|              | nanosphere lithography                                                  | 4   |

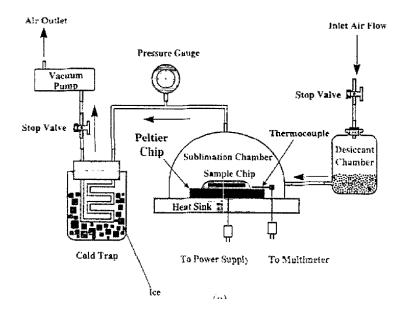

| Figure 4-29: | Sublimation apparatus used to lower temperature then lower pressur      | e   |

|              | inside the chamber                                                      | 5   |

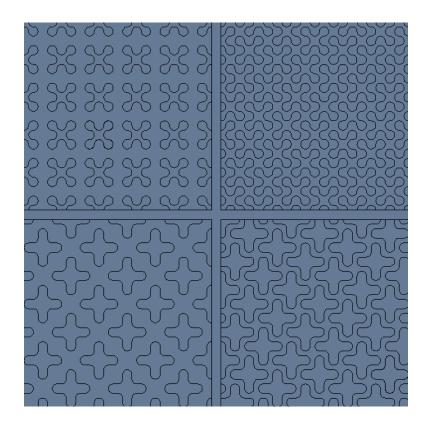

| Figure 4-36: | CAD drawing of potential high perimeter, high stiffness geometries      | for |

|              | nanowires                                                               | 7   |

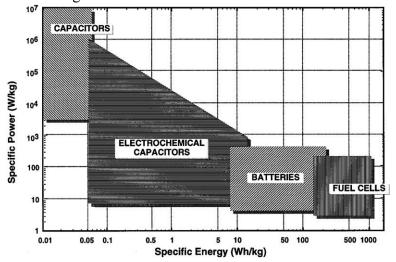

| Figure 4-30: | Plot showing the role of ultra-capacitors (electrochemical capacitors   | in  |

|              | image) in combining the positive features of both batteries and         |     |

|              | traditional capacitors                                                  | 8   |

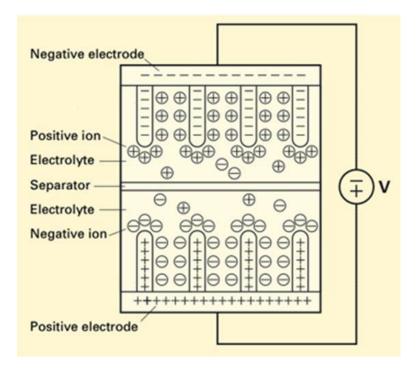

| Figure 4-31: | Schematic of an ultra-capacitor with nanowires which create more        |     |

|              | surface area                                                            | 0   |

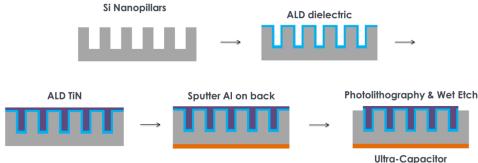

| Figure 4-32: | Process flow to fabricate metal-insulator-silicon nano-capacitors wit   | h   |

|              | nanowires9                                                              | 0   |

| Figure 4-33: | Process flow to fabricate an ultra-capacitor from nanowires9            | 1   |

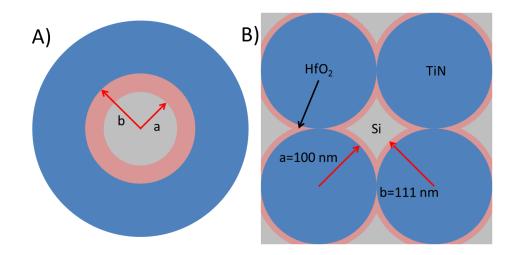

| Figure 4-34: | A) Circular cross section capacitor where a is the radius of the inner  |     |

|              | electrode and b is the radius of the outer electrode. B) Diamond cros   | s   |

|              | · · · · · · · · · · · · · · · · · · ·                                   |     |

#### **Chapter 1: Introduction**

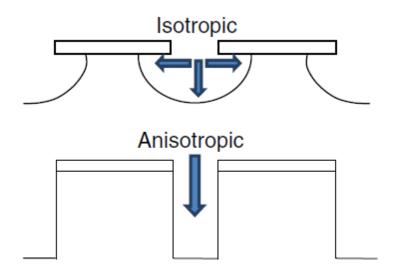

Anisotropic etch techniques are used for controlled transfer of nano-scale features into a thin film or a bulk substrate. Isotropic etchants, which include most liquid etchants, are not feasible for high aspect ratio pattern transfer needed in nanofabrication since isotropic etching leads to non-vertical lateral etching that can undercut the etch mask. This results in loss of feature definition (sharp corners) and critical dimensions  $(CDs)^{1,2}$ . A diagram depicting the difference between isotropic and anisotropic etching is shown in Figure 1-1. Dry plasma etching processes are used for many applications because of their ability to etch anisotropically. However, such processes require expensive vacuum equipment as well as a variety of consumable gases that may be difficult to facilitate<sup>1,3</sup>. In crystalline silicon, anisotropic wet etch processes are available at the nano-scale. These processes combine the inexpensive nature of wet chemical etching and the controlled anisotropic nature found in dry etching. However, in addition to being limited to crystalline silicon, they are constrained in the complexity of geometry of patterns that they can address<sup>1</sup>. For these reasons, these processes cannot be used in applications like fabrication of integrated circuits which need features of different geometries on the same die, and also need etching of metals, and amorphous dielectrics. The core of this research will explore such inexpensive wet anisotropic etching processes for controlled fabrication of nano-scale features in applications that do not possess the geometry and material complexity found in typical semiconductor manufacturing.

Figure 1-1: Diagram showing isotropic versus anisotropic etching.<sup>4</sup>

#### **1.1 MOTIVATION**

The cost of a unit process step depends on the throughput, tool capital cost as well as the cost of consumables. Dry plasma-based etching can be quite expensive, as its throughput is limited in addition to the need for complex vacuum tooling and gas mixtures<sup>1,3</sup>. On the other hand wet processes are relatively inexpensive because wafers can potentially be processed in batches without the need for complex tools. The challenge with using wet etchants for anisotropic etching, however, is that there are unique geometric constraints that make fabricating arbitrary features difficult, as will be seen in Chapter 2 and Chapter 3. If these constraints can be overcome, wet etch techniques like crystallographic orientation dependent etching (CODE) and metal assisted chemical etching (MACE) can inexpensively provide high degrees of anisotropy, comparable to plasma-based etching<sup>1,5</sup>. The main motivation for this study is to reduce fabrication costs by leveraging controlled patterning of feature geometry so as to use wet etching instead of dry etching processes for transferring the pattern onto a crystalline substrate specifically fabrication of high aspect ratio nanowires. There are many applications that

require high aspect ratio nano-scale features such as thermoelectrics<sup>6</sup>, biochemical sensors<sup>7</sup>, and electronic devices<sup>8,9</sup>, and ultra-capacitors<sup>10-12</sup>. This investigation has been conducted in the context of an exemplar application: high storage energy density ultra-capacitors which can potentially benefit from these high aspect ratio nanowires.

#### **1.2 NANO-PATTERNING PROCESSES**

There are three main categories of nanopatterning processes: (i) top-down which uses a mask or a template to pattern a sacrificial layer on a substrate, (ii) bottom-up which is the preferential growth and assembly of molecules to create a pattern, and (iii) a combination of the first two where a pattern defined by a top-down process helps direct the assembly of molecules in a bottom-up process<sup>13</sup>.

Photolithography is a photon based top-down patterning technique that has been the mainstay of the semiconductor industry but it is limited by diffraction. Overcoming diffraction limits requires the use of expensive processes like double patterning to obtain a resolution better than ~45 nm<sup>13,14</sup>. The next generation of photolithography is extreme ultraviolet but several technical challenges still need to be overcome to make it a viable option<sup>13-15</sup>. Electron-beam lithography can achieve high resolutions but at the price of very low throughput<sup>16</sup>.

Imprint lithography is a class of mechanical top-down patterning techniques that has demonstrated sub-10 nm resolution<sup>17</sup>. Thermal nano-imprint lithography, and UV nano-imprint lithography are the two primary techniques that fall under the gamut of imprint lithography. Specifically, this work uses Jet-and-Flash Imprint Lithography, which is a variant of UV nanoimprint lithography as the preferred patterning step.<sup>13,18</sup>

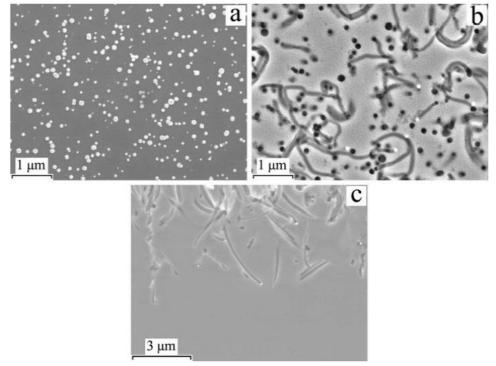

Bottom-up patterning techniques rely on nanoscale phase separation and subsequent self-assembly of a solution to create the desired nanoscale periodic structures.

Block co-polymer solutions, inorganic nano-particle and polystyrene nanosphere dispersions are most commonly used<sup>16</sup>. These solutions can be dispensed on the substrate using techniques such as spin-coating. When the solvent that suspends the solution evaporates, nanophase separation occurs, creating a pattern of nanodomains. In block co-polymer patterning, one of the blocks can be selectively removed, leaving behind the desired pattern. Likewise, self-assembled nano-particles can be sintered to give a pattern, and polystyrene nano-spheres can self-assemble into a periodic pattern that can be used as a mask for subsequent pattern transfer. These techniques can only result in periodic regular patterns and also have trouble with long-range order. Currently, research is being done to mitigate the problems with long-range order by using top-down techniques to create lower resolution features that can guide bottom-up self-assembly.<sup>16,19,20</sup>

#### **1.3 WET ANISOTROPIC ETCHING**

The three primary types of wet anisotropic etching techniques being used today include (i) crystallographic orientation dependent etching (CODE), (ii) electrochemical etching, and (iii) metal assisted chemical etching (MACE)<sup>3,21-23</sup>. CODE and MACE will be the focus of this study because electrochemical etching has a limit to the possible feature size it can produce due to the effect of the space charge region (SCR). The size of the SCR is dependent on the resistivity of the Si wafer. Wafers with resistivity less than 0.02 ohm-cm are needed to fabricate features less than 50 nm. These wafers need to be highly doped to obtain the required resistivity which limits the potential applications.<sup>24,25</sup> For instance, highly doped silicon has surface traps that reduce conductivity and the surface atoms are highly reactive to the electrolyte which reduces electrochemical stability for capacitors that use liquid electrolytes<sup>26</sup>.

#### 1.3.1 Crystallographic Orientation Dependent Etching (CODE)

Crystallographic orientation dependent etching (CODE) is an anisotropic etching technique of crystalline silicon where the etch rate changes based on the crystallographic orientation of the surface exposed to the etch solution. The benefits of crystallographic orientation dependent etching is that very smooth sidewalls and sharp corners can be fabricated compared to the other methods of anisotropic wet etching<sup>1,27</sup>. Unfortunately, the shape and orientation of the features being etched are constrained due to the dependence on the crystallographic planes. This process has been used for applications in MEMS and etching through wafer vias<sup>28-30</sup>. Table 1-1 lists some common CODE techniques. From Table 1-1, it is evident that Potassium hydroxide (KOH) has a high anisotropic ratio etch rate and is also relatively more benign to handle. Hence, KOH has been used as the preferred etchant for Si.

Table 1-1: Comparison of Anisotropic Wet Etchants.

| Etchant             | Pros                                        | Cons                                     |

|---------------------|---------------------------------------------|------------------------------------------|

| Ethylenediamine     | Anisotropic                                 | highly toxic and requires                |

| Pyrocatechol (EDP)  |                                             | special handling <sup>1,23</sup>         |

| Hydrazine           | Anisotropic                                 | highly toxic, potentially                |

|                     |                                             | explosive, and requires                  |

|                     |                                             | special handling <sup>1,23,31</sup>      |

| Potassium Hydroxide | Anisotropic, high etch rate,                | not compatible with CMOS                 |

| (KOH)               | high anisotropic ratio, and                 | (mobile K+ ion                           |

|                     | non-organic (easier to                      | contamination) <sup>1,23</sup>           |

|                     | dispose of than TMAH) <sup>23</sup>         |                                          |

|                     | excellent uniformity and                    |                                          |

|                     | reproducibility <sup>32</sup>               |                                          |

| Tetramethylammonium | anisotropic, compatible                     | more expensive to dispose                |

| Hydroxide (TMAH)    | with CMOS, and highly                       | of organic solutions than                |

|                     | selective to SiO <sub>2</sub> <sup>23</sup> | non-organic, low etch rate,              |

|                     |                                             | low anisotropic ratio <sup>1,23,31</sup> |

#### 1.3.1.1 Etching Mechanism of KOH

KOH is an alkaline etchant that is described by several slightly different etching mechanisms, three of which are given in Equations 1.1-1.3. Equation 1.1 and Equation 1.3 are very similar but Equation 1.1 doesn't show the hydroxide ion even though it is needed to catalyze the reaction and keep the product soluble<sup>23,33</sup>. All the reactions produce gaseous hydrogen which can affect surface roughness by acting like a local mask if it adheres to the silicon surface. Isopropanol (IPA) can be added to the etching solution

to increase the wettability of the etchant and keep the hydrogen bubbles from sticking to the surface<sup>31</sup>. Another method of reducing the effect of hydrogen bubbles is to agitate the solution through ultra-sonication<sup>34</sup>.

$$Si + 4H_2O \to Si(OH)_4 + 2H_2$$

(1.1)

$$Si + 20H^{-} + 2H_20 \rightarrow SiO_2(0H)_2^{2^{-}} + 2H_2$$

(1.2)

$$Si + 20H^{-} + 2H_2O \rightarrow Si(OH_4)^{-} + H_2(g)$$

(1.3)

#### 1.3.1.2 CODE of Si using KOH

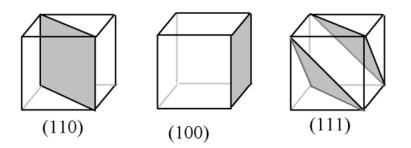

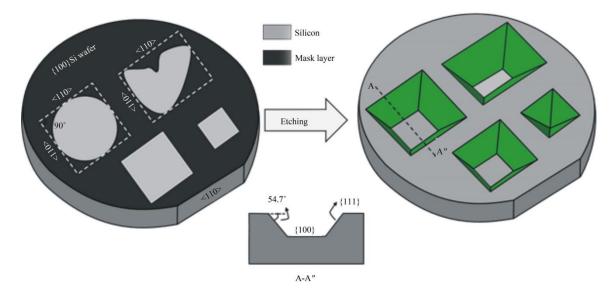

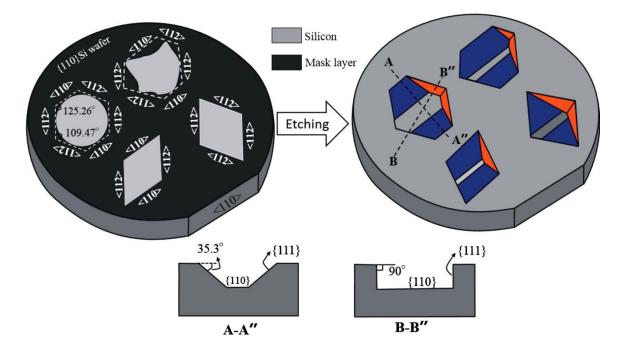

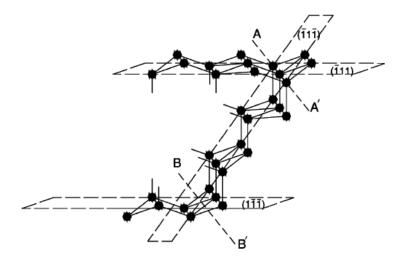

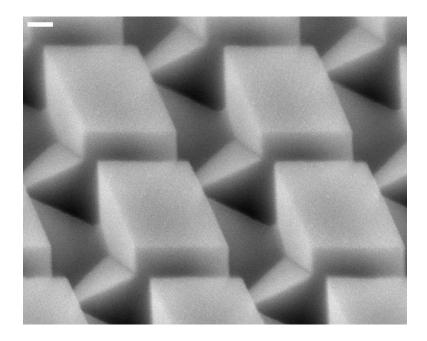

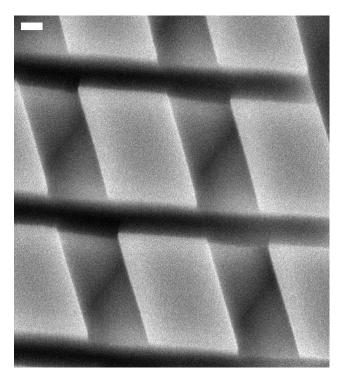

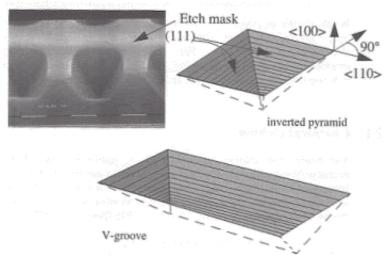

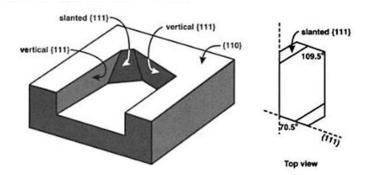

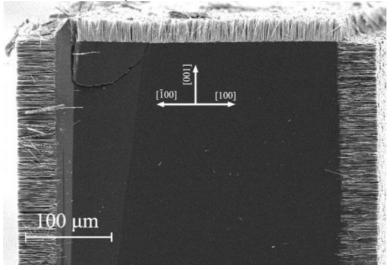

KOH etches single crystalline silicon at different rates depending on the exposed surface's crystallographic orientation. Miller indices are used to denote different planes and directions of crystalline silicon<sup>\*</sup>. Figure 1-2 shows examples of the three main planes considered when talking about the anisotropic etching of silicon. Etch anisotropy is defined as the ratio of the lateral etch amount and the etch depth. This value has been found to vary significantly in the literature since it is based on experimental setup and the composition of the etch solution<sup>5,35-37</sup>. A typical anisotropic ratio is reported to be  $r_{(110)}$ :  $r_{(100)}$ :  $r_{(111)} \cong 600$ : 300: 1 where *r* is the etch rate for the given plane<sup>5</sup>. The (111) slow etching planes define the sidewalls of concave features etched into Si. Examples include rectangular/square grooves that are created in (100) silicon with edges aligned to the [110] directions as shown in Figure 1-3; and hexagonal/rhombus cavities with the two sets of vertical (111) planes aligned to the [112] direction and one set of (111) planes aligned to the [110] directions as shown in Figure 1-4 for (110) silicon wafers. (Pal, P. 2013)

<sup>\*</sup> Parentheses are placed around the inverse of the intercepts of a given plane. For example, (110) means that the x and y axes are intersected at 1/1 where 1 is the normalized length of a side of the cubic and the plane is parallel to the z axis since  $1/\infty=0$ .

Figure 1-2: Examples of miller indices<sup>†</sup>

Figure 1-3: Anisotropically etched features in (100) Si wafers.<sup>38</sup>

<sup>&</sup>lt;sup>†</sup> modified from http://upload.wikimedia.org/wikipedia/commons/f/f5/Indices\_miller\_plan\_exemple\_cube.png

Figure 1-4: Anisotropically etched features in (110) Si wafers.<sup>38</sup>

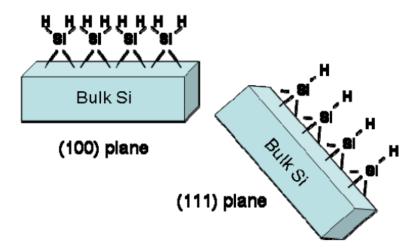

The primary explanation for the dependence of etch rates on crystallographic orientation is the number of back bonds and the density of dangling bonds for a given perfect crystallographic surface. Each back bond attached to a given atom of Si has to be broken for that atom to be etched away. This requires more energy compared to the removal of dangling bonds. The probability that a given atom will be removed decreases with an increase in energy needed to break all the bonds. A (111) surface has three back bonds and only one sparsely placed dangling bond while a (100) surface has two back bonds and two dangling bonds and a (110) surface has only one back bond with one dangling bond that are more closely packed.<sup>23,39,40</sup> Figure 1-5 and Figure 1-6 show the back bonds and dangling bonds for silicon atoms on the three major crystallographic orientations.

Figure 1-5: Hydrogen terminated bonds are the dangling bonds.<sup>40</sup>

Figure 1-6: Back bonds and dangling bonds are denoted for a surface atom A on the surface represented by the green plane<sup>‡</sup>

#### 1.3.2 Metal Assisted Chemical Etching (MACE)

Metal assisted chemical etching (MACE) is an anisotropic wet etch technique that has been shown to be able to fabricate high aspect ratio features in c-Si, a-Si, and GaAs.<sup>3,41-47</sup>

<sup>&</sup>lt;sup>‡</sup> <u>http://www.fujitsu.com/img/PR/2008/20081216-01al.jpg</u>

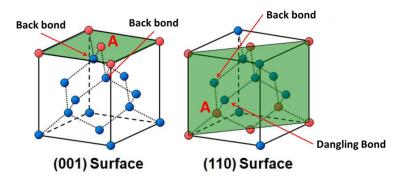

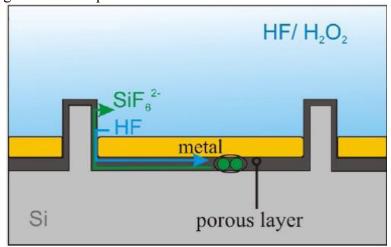

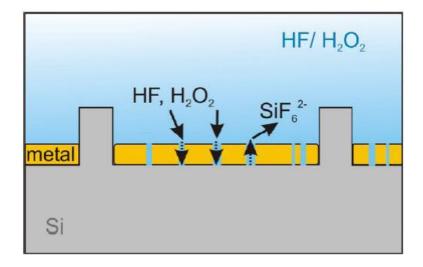

#### 1.3.2.1 MACE Mechanism for c-Si

The etch mechanism occurs when silicon with a patterned noble metal layer (commonly Ag, Au, and Pt) is submerged in a solution containing water, an oxidant (most commonly hydrogen peroxide -  $H_2O_2$ ), and hydrofluoric acid (HF). The noble metal acts as a catalyst for the reduction of the  $H_2O_2$  (cathode reaction), thereby creating positively charged electron holes. These holes are then injected through the metal to the metal-silicon interface thereby oxidizing the silicon underneath the metal (anode reaction). The oxidized silicon is dissolved by the HF that diffuses from the sides of the metal catalyst and the soluble products diffuse away. This redox reaction can also produce hydrogen gas. There is some dispute about the actual reactions at the metal-silicon interface but most researchers agree that Equation 1.4 is the overall redox reaction shown in Figure 1-7. The variable n = 2 to 4 is determined by the ratio of oxidant to HF which determines the etch regime that occurs. The differences between regimes will be discussed in Section 3.2.1. The metal catalyst then fills in the hole created by the dissolved silicon and the process repeats.<sup>3,45,47-49</sup>

$$Si + \frac{n}{2}H_2O_2 + 6HF \to H_2SiF_6 + nH_2O + \frac{4-n}{2}H_2\uparrow$$

(1.4)

Figure 1-7: Schematic of MACE reactions.<sup>3</sup>

#### **1.3.3 CODE and MACE Comparison**

Given that both CODE and MACE can enable highly anisotropic wet etching, it is instructive to compare the two processes with respect to their pros and cons, and the specific geometries that they can address. These have been summarized in Table 1-2 and Table 1-3 respectively. The details captured in Table 1-3 have been discussed later in Sections 2.1-2.2 and Sections 3.1-3.2.

Table 1-2: General comparison of CODE and MACE.

| Etch Technique | Advantages                  | Disadvantages                |

|----------------|-----------------------------|------------------------------|

| CODE           | Smooth side walls, sharp    | (111) etch stop planes       |

|                | edges possible              | restrict final feature shape |

|                |                             | to rectangular for (100)     |

|                |                             | wafers and rhombuses and     |

|                |                             | hexagons for (110) wafers    |

| MACE           | More arbitrary feature      | Noble metal left at the      |

|                | geometries possible, etched | bottom of etched feature,    |

|                | patterns defined by the     | rougher sidewalls            |

|                | geometry of the catalyst    |                              |

|                | during the etch process     |                              |

| Pattern of Hard             | CODE                                                                                                                                                                                                            | MACE                                                                                                                                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mask or Catalyst<br>Dots    | Mask lift-off due to<br>undercutting and loss of<br>features                                                                                                                                                    | Catalyst can wander from uneven<br>forces (3D motion) <sup>50-52</sup> , can prefer to<br>etch along [100] direction depending<br>on solution composition                                                             |

| Layer with<br>openings/Mesh | Non-vertical stop planes<br>prevent high aspect ratio<br>etching, inverted pyramids,<br>hexagon with four vertical<br>sidewalls and two non-<br>vertical that meet in the<br>middle                             | Deep pillars can be fabricated, mesh<br>prevents lateral motion of individual<br>parts of the catalyst                                                                                                                |

| Lines                       | Depth of lines depends on<br>the length of the lines,<br>increase in width depends<br>on misalignment to the<br>vertical (111) planes for<br>(110) wafers, long inverted<br>pyramids etched for (100)<br>wafers | Etch direction of flat lines depends on<br>solution composition and wafer<br>orientation, if metal nano-rods are<br>used as catalyst then the rods can<br>return to surface (not just downward<br>etch) <sup>50</sup> |

# Table 1-3: Comparison between CODE and MACE of mask features (details in Chapter 2 and Chapter 3).

#### **1.4 PROPOSED NANO-FABRICATION PROCESSES**

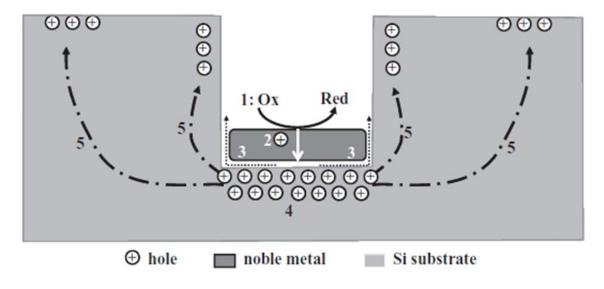

Jet and Flash Imprint Lithography (J-FIL<sup>™</sup>), a UV nano-imprint lithography process developed at The University of Texas at Austin and Molecular Imprints, has been used as the preferred pre-etch patterning process as it enables patterning of sub-50 nm high density features with different geometries over large areas. The basic imprint process is shown in Figure 1-8.

Figure 1-8: Process flow for J-FIL<sup>TM<sup>53</sup></sup>

#### 1.4.1 iCODE Process

Imprint-enabled <u>C</u>rystallographic <u>O</u>rientation <u>D</u>ependent <u>E</u>tching (iCODE) uses J-FIL<sup>TM</sup> to pattern the hard mask that has been used to perform CODE on (110) silicon. For this, the imprint template needs to be accurately aligned with the correct crystallographic planes to enable <111> plane sidewalls, and hence, get deep, vertically etched features. The two most common hard mask materials for KOH etching are silicon dioxide (SiO<sub>2</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>). SiO<sub>2</sub> is thermally grown and a low pressure chemical vapor deposition (LPCVD) furnace is used to deposit Si<sub>3</sub>N<sub>4</sub>. The etch selectivity of Si/SiO<sub>2</sub> in a KOH solution varies with the solution concentration and temperature but is nominally 500, whereas Si<sub>3</sub>N<sub>4</sub> can be considered to be not attacked by KOH<sup>1</sup>. Once the hard mask is patterned, the sample is submerged in a heated solution of KOH and deionized (DI) water.

#### **1.4.2 iMACE Process**

Imprint-enabled Metal Assisted Chemical Etching (iCODE) uses J-FIL<sup>TM</sup> to pattern the metal catalyst used to perform MACE on (100) silicon. There are two main methods to pattern the metal catalyst before it is used in the MACE process. The first method consists of transferring a resist pattern into a thin noble metal film such as Ag, Au, and Pt (gold was used in this project) via etching or ion milling. Imprint lithography is used to define the resist pattern after the film is vacuum deposited on the Si wafer. Then, a descum process is used to remove the residual layer<sup>54</sup> and expose the underlying Au film for etching. The gold film can be etched by either an iodine based solution (Gold Etchant TFA)<sup>55</sup> or an argon (Ar) and chlorine (Cl) plasma<sup>56,57</sup>. Finally, the resist is stripped and the sample is submerged in a solution of DI water, hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>), and hydrogen fluoride (HF) at room temperature for MACE.

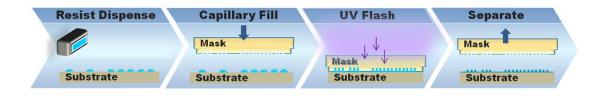

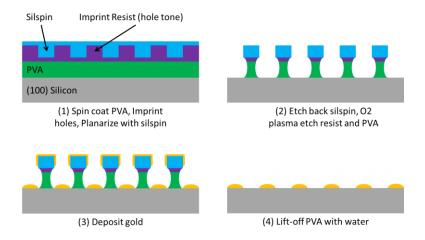

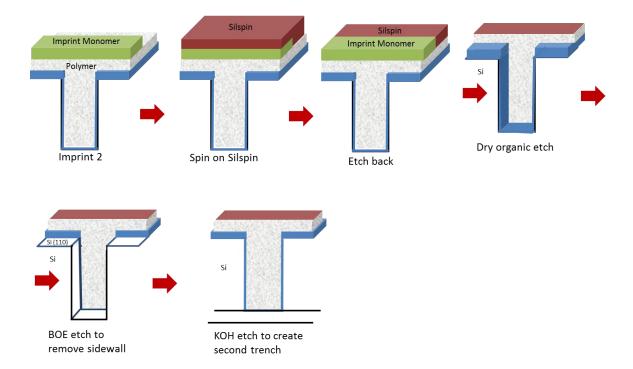

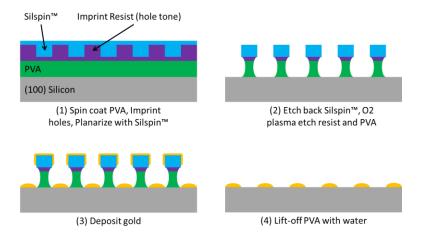

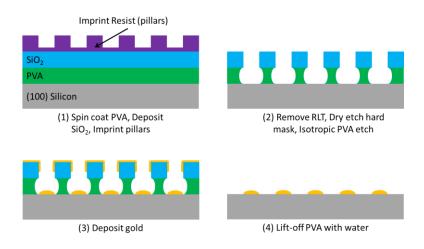

The second method to pattern the metal catalyst is a bilayer lift-off based process. Figure 1-9 shows an example of a bilayer lift-off process. A silicon wafer is first coated with polyvinyl alcohol (PVA). A resist pattern with holes is imprinted on top of the PVA and then the wafer is planarized with a proprietary silicon containing resist called Silspin<sup>™</sup> manufactured by Molecular Imprints. The Silspin<sup>™</sup> is etched back in a dry etch process following which an O<sub>2</sub> is used to preferentially etch the organic material (imprint resist and PVA) and oxidize the Silspin<sup>™</sup> into SiO<sub>2</sub> which does not get removed. The O<sub>2</sub> plasma also etches the organic material isotropically so as to create a bowed sidewall profile. Metal is then deposited using e-beam evaporation, but does not become a continuous film because of the bowed sidewall profile. Finally, the PVA is dissolved in water leaving behind the patterned metal with the same tone as the imprint.

Figure 1-9: Example process flow for imprint bilayer lift-off process.

#### **1.5 RESEARCH AND STRUCTURE OF THE DISSERTATION**

This dissertation is organized such that the second and third chapters detail the two processes used in this study. Chapter 2 details the advantages and limitations of iCODE and Chapter 3 details the advantages and limitations of iMACE. Chapter 4 discusses patterning of gold for the iMACE process and the exemplar application enabled by iMACE: Increase the energy storage density of ultra-capacitors by increasing the surface area per unit projected area of the electrodes with silicon pillars fabricated using iMACE. Finally, Chapter 5 summarizes the intellectual merit and future work.

# Chapter 2: <u>Imprint-enabled Crystallographic Orientation Dependent</u> <u>Etching (iCODE)</u>

Imprint-enabled <u>Crystallographic</u> <u>Orientation</u> <u>Dependent</u> <u>Etching</u> (iCODE) is a process where J-FIL<sup>TM</sup> is leveraged to pattern sub-50nm hard mask features for the CODE process, which is an anisotropic etch technique where monocrystalline silicon is etched at different rates based on the exposed surface's crystal orientation (see Section 1.3.1.2). This process has been explored to enable inexpensive etching of high aspect ratio nanowires in Si.

#### **2.1 PRELIMINARY EXPERIMENTS**

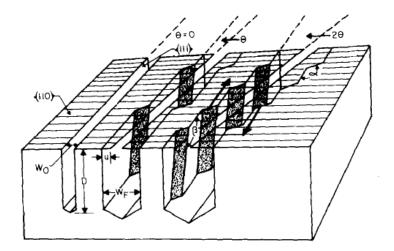

Preliminary experiments were performed to explore the geometric constraints of the iCODE process by using different initial template patterns. All iCODE experiments were performed on (110) Si wafers because this orientation of Si wafers has four vertical (111) etch stop planes, as discussed previously in Section 1.3.1.2, that can be used to fabricate high aspect ratio features. Table 2-1 summarizes the purpose and results of the preliminary experiments. These have been detailed further in the following sections.

| Mask               | Purpose                                | Result                      |

|--------------------|----------------------------------------|-----------------------------|

| Geometries         |                                        |                             |

| Dots (250 nm       | Test whether the vertical etch stop    | Undercutting leads to the   |

| diameter circles   | planes would automatically create      | hard mask detaching,        |

| in radial pattern) | rhombus shaped pillars without need    | hillock formation, and      |

|                    | for alignment to the vertical (111)    | finally feature loss        |

|                    | planes                                 |                             |

| Gratings           | Test optical/manual alignment and      | Optical/manual alignment is |

| (500 nm Lines      | achievable anisotropy                  | precise enough for the CDs  |

| and 150 nm         |                                        | used in the preliminary and |

| Spaces)            |                                        | proof of concept            |

|                    |                                        | experiments                 |

| Rhombuses          | Same test as the dots but with sides   | Undercutting leads to the   |

| (Intersection of   | that are aligned to the vertical (111) | hard mask detaching,        |

| rotated gratings)  | planes                                 | hillock formation, and      |

|                    |                                        | finally feature loss        |

Table 2-1: Purpose and results of etching of the preliminary experiment mask geometries.

#### 2.1.1 Dots (convex hard mask)

As a preliminary experiment to test whether the vertical etch stop planes would automatically create rhombus shaped pillars, dots were used as the pattern geometry of choice. Figure 2-1 is an SEM image of the dot pattern after it was transferred into the  $Si_3N_4$  hard mask. The features are ~250 nm wide and ~120 nm high dots in a radial pattern with a pitch of 380 nm to 1.8 µm. Subsequent 5 sec anisotropic wet etching led to the hard mask being undercut, as shown in Figure 2-2, and eventually resulting in the

hard mask being completely removed. Short pyramids, shown in Figure 2-3, were revealed just after the hard mask detached from the Si after a 10 sec etch. The experiment showed that the anisotropic etch does not automatically stop at the vertical (111) planes which will be discussed in Section 2.2.2.

Figure 2-1: Radial pattern of ~230 nm dots in  $Si_3N_4$  hard mask on Si. Scale bar is 1  $\mu$ m.

Figure 2-2: SEM image showing the undercutting of the hard mask. Scale bar is 100 nm.

Figure 2-3: Pyramid features (hillocks) remaining just after the hard mask detached. Scale bar is 100 nm.

## 2.1.2 Lines

The iCODE process was used on a lines and spaces pattern to test the anisotropy of the process, test the precision of an optical/manual alignment scheme, and observe how misalignment to the vertical (111) planes affects the final feature dimensions. An optical/manual alignment procedure was used because the available imprint tool does not have the equipment necessary for automatic theta alignment. The alignment is done iteratively using the following steps:

- 1) The wafer is loaded onto the wafer chuck and the chuck is moved under the imprint template,

- The angle between the sides of the die on the template and the wafer flat is observed using a camera mounted above the transparent template,

- 3) The chuck is moved back to the load/unload position and the wafer is unloaded,

- 4) The wafer is rotated by hand,

5) Steps 1) - 4) are repeated until the best visual alignment is reached.

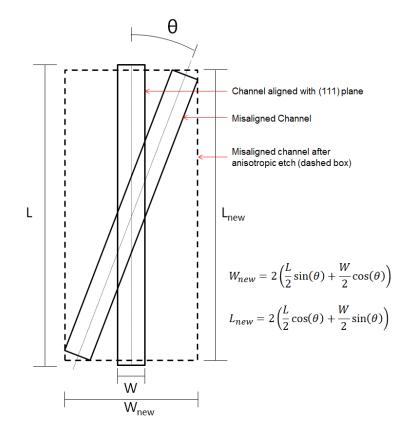

Figure 2-4 shows a SEM image of gratings that were etched using a hard mask with the features well aligned to the vertical (111) etch stop planes. A misalignment of less than  $0.5^{\circ}$  was measured between the imprint and a cleaved side using an optical microscope. With increasing misalignment, greater undercutting of the mask occurs, as can be seen in Figure 2-5. Here, the initial alignment of the gratings was worse than the previous set of gratings as can be seen by the ~37 nm mask undercutting for a similar etch time.

Figure 2-4: Well aligned gratings with minimal undercutting. Interface between Si and SiO<sub>2</sub> marked with a dashed line. Scale bar is 100 nm.

Figure 2-5: Etched gratings with slight misalignment showing more undercutting of the hard mask. Scale bar is 100 nm.

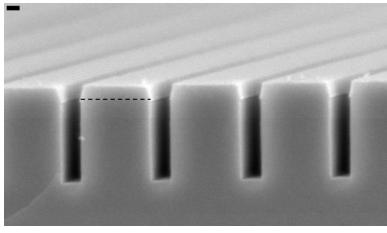

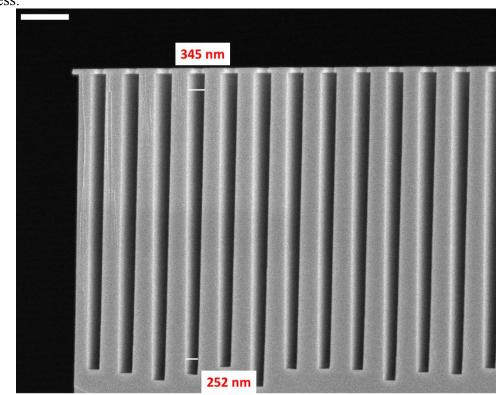

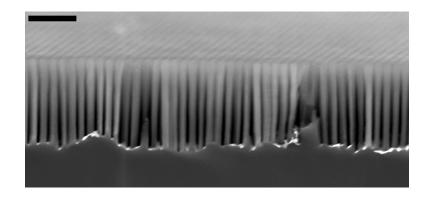

The anisotropy of iCODE was also tested by observing the changes in dimension after increasing the etch time. Figure 2-6 is a SEM image of the same gratings that were shown previously in Figure 2-5 but were etched for 15 min instead of 90 sec. The sidewalls are no longer vertical as can be seen by the change in trench width from  $\sim$ 313 nm at the top to  $\sim$ 252 nm at the bottom. The taper is most likely due to the different compositions of the etch solution along the gratings vertical direction. This difference in composition is hypothesized to be because of restricted transport of the reactants and products to the bottom of the trenches. The hard mask is also undercut by  $\sim$ 70 nm and the etch depth is  $\sim$ 6.5 µm. This equals an anisotropy of  $\sim$ 93 which is not as high as has been reported in literature<sup>5,35-37</sup>. The anisotropy can be affected by many factors such as solution composition, flow of etch solution, geometry of features, and alignment to the (111) planes. These parameters will also influence the uniformity of the etch process as well as surface roughness<sup>58,59</sup>. These parameters were not optimized since these

experiments were preliminary and were done to observe the parasitics in the iCODE process.

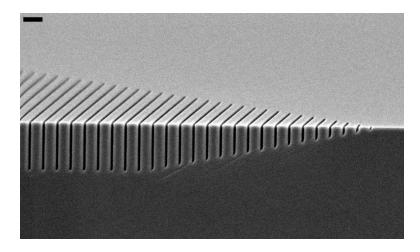

Figure 2-6: High aspect ratio trenches. Scale bar is 1 µm.

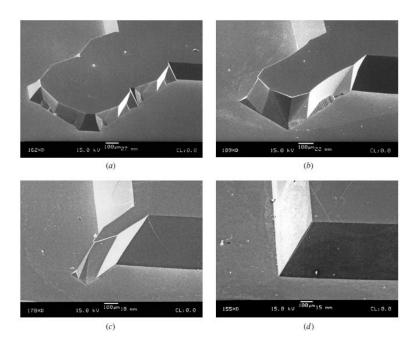

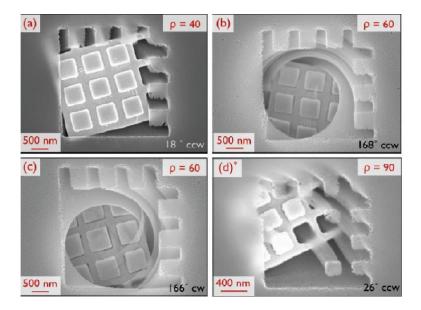

### 2.1.3 Rhombus with Sides Aligned to vertical (111) planes

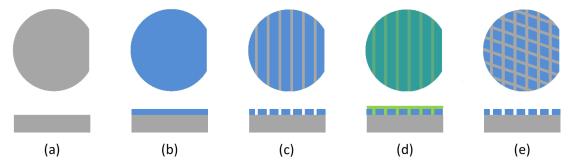

The results from attempting to create pillars from a dot pattern show that severe undercutting occurs, leading to the removal of the hard mask. A second set of experiments were performed to observe the results of changing the pattern to have a convex geometry where the sides are aligned to the vertical (111) planes. These planes form a rhombus with angles of 109.47° and 70.53°. Since such a geometry was not readily available on a template, the patterning was done in a two-step process, with each step involving the patterning of a lines and spaces template as given in Section 2.1.2. Figure 2-7 is a simplified process flow of the process for patterning the hard mask in the

form of rhombus. First, a SiO<sub>2</sub> hard mask was patterned with a grating pattern of 150nm lines and 500nm spaces that was aligned to one family of vertical (111) planes using the optical/manual method of alignment discussed in Section 2.1.2. The alignment was done with optical/manual alignment procedure. Then, a descum etch (O<sub>2</sub> and Ar) was used to remove the residual layer and then a SiO<sub>2</sub> dry etch (Ar, CHF<sub>3</sub>, and CF<sub>4</sub>) was used to transfer the pattern into the hard mask. The hard mask was patterned again but with the gratings aligned to the second family of vertical (111) planes.

Figure 2-7: Process flow for rhombus shape mask double patterning. (a) (110) Si wafer(b) SiO2 hard mask growth (c) Gratings patterned and etched into hard mask(d) Planarization with polymer (e) Gratings rotated by 109.47° patterned and etched into hard mask.

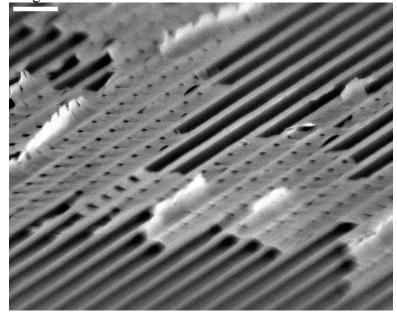

The wafer was etched in a KOH solution after the  $SiO_2$  hard mask was fully patterned. Figure 2-8 shows the resultant mask after double patterning gratings aligned to both the families of (111) planes. Figure 2-9, Figure 2-10, and Figure 2-11 show that there was severe undercutting of the corner of the rhombuses after 20sec KOH etch instead of etching vertically, which eventually lead to lift-off of the hard mask just like the experiments with the dots. The crossing of (111) planes did not help with creating pillars with slow etching sides as expected. The reasons for this will be discussed in Section 2.2.2. The dashed lines in Figure 2-11 show the vertical (111) planes where the mask sides ended and the etch process was expected to stop.

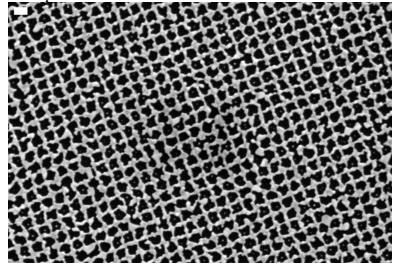

Figure 2-8: Top-down SEM image of the double patterned hard mask. Scale bar is 1  $\mu$ m.

Figure 2-9: Visible undercutting of mask after 20 sec KOH etch. Scale bar is 100 nm.

Figure 2-10: Undercutting of mask after 20 sec KOH etch with hard mask removed. Scale bar is 100 nm.

Figure 2-11: Top-down view of undercutting from KOH etching with the hard mask removed. The dashed lines are the (111) planes where the etch process was thought to stop. The four arrows show how the corners etch. Scale bar is 100 nm.

#### **2.2 PROBLEM FUNDAMENTALS**

As described in the previous section, the preliminary experiments show that there are several constraints on the CODE process that limits the ability to etch arbitrary feature geometries. These constraints include undercutting of the mask that occurs at the corners during KOH etching even when the sidewalls are aligned to the (111) etch stop planes, and the change in etch rate and undercutting due to misalignment with the (111) planes. A third etch depth constraint is exemplified with the experiments that were carried out to overcome the convex edge etching.

#### 2.2.1 Alignment

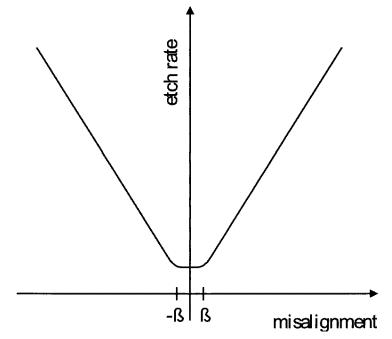

Alignment of the feature sides with respect to the (111) planes determines the amount of undercutting of the mask that occurs and the initial lateral etch rate. The anisotropy of an etch is determined by the amount of undercutting or the ratio of the lateral etch amount and the etch depth. Misalignment of the mask with respect to the (111) planes leads to higher initial etch rates until the etching planes self-align to the (111) planes. Figure 2-12 shows how the lateral etch rate changes with respect to the angle between the masked features and the (111) planes. This phenomenon is explained with ledges where one face of the ledge is the (111) plane. The ledges etch along the (111) plane since the other face of the ledge will be a faster etching plane. The density of the ledges decreases as the orientation of the widening feature rotates to be more aligned to the (111) plane. In Figure 2-13, the left trench is perfectly aligned so there is almost no lateral etching compared to the depth. The middle trench is slightly misaligned so some of the (111) planes are cut revealing faster etch planes which start etching along the (111) plane. The right trench is misaligned by twice as much as the middle and there are twice as many ledges per length which means the etch rate is twice as high. Figure 2-14 shows

the change in feature dimension due to misalignment of gratings from the vertical (111) planes.<sup>60</sup>

Figure 2-12: Lateral etch rate versus misalignment.<sup>37</sup>

Figure 2-13: Misalignment of trenches etched in (110) silicon showing ledges, final width, and etch direction.<sup>60</sup>

Figure 2-14: Change in trench dimensions due to misalignment.

There are two main components to reducing misalignment. First, the amount of misalignment between the (111) planes and the template features needs to be measured. Nominally, the major flat of (110) silicon wafers are aligned to the (111) planes but the flat can have an alignment error of  $0.5^{\circ}$  to  $5^{\circ}$  depending on the grade of the wafer. This amount of error is unacceptable for applications on the nanoscale so other methods are needed to precisely determine the (111) plane orientation<sup>36,37,61</sup>. Second, the lithography tool needs to have a theta stage to be able to rotate the wafer and align the template features to the (111) plane. While the actuation of the wafer can be done with commercial theta stages, the main difficulty lies in accurately determining the true (111) planes. Commercial theta stages can be found with theta resolutions as high as 0.00004 degrees

which is well beyond the current sensing resolution which can be as high as 0.01 degrees<sup>61</sup>§.

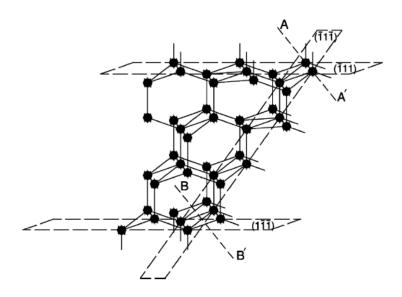

#### 2.2.2 Convex Corner Undercutting - Edge Parasitics

The preliminary experiments done in Section 2.1.3 show that convex edges etch away even when their sides are aligned to (111) etch stop planes. This has to do with the structure of the Si atoms at the convex and concave edges created by the intersection of two (111) planes. Figure 2-15 shows the structure of the 70.53° convex edge at AA' and the 109.47° convex edge at BB'. The edge atoms along AA' each have two dangling bonds and two back bonds like the (100) plane so they etch faster than the (111) plane and lateral etch occurs which undercuts any mask. The two sets of atoms beside BB' each have one dangling bond but they are closer together than the (111) which means there is a higher density of dangling bonds similar to the (110) plane. On the other hand the atoms of the concave edges, shown in Figure 2-16, have zero dangling bonds so are very stable compared to any plane.<sup>39</sup> The stability of concave edges versus the instability of convex edges is summed up by Batterman when he stated, "On a concave surface, the plane at a relative minimum in etch rate versus orientation will limit, while on a convex surface the converse will hold."<sup>62</sup>

<sup>&</sup>lt;u>https://www.newport.com/Motorized-Rotation-Stage-Selection-Guide/140222/1033/content.aspx</u> viewed on June 15, 2015

Figure 2-15: Convex edges created by (111) planes.<sup>39</sup>

Figure 2-16: Concave edges created by (111) planes.<sup>39</sup>

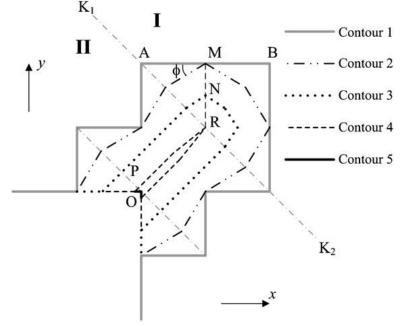

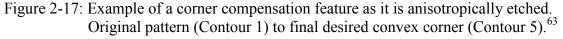

## 2.2.2.1 Corner Compensation to Overcome Undercutting

The main method developed to mitigate the undercutting due to mask geometries with convex corners is called corner compensation<sup>63-65</sup>. This method uses knowledge of the etch rates of different planes to design mask geometries with extra protrusions on the convex corners that result in the desired shape after a timed anisotropic etch for a given

depth. Figure 2-17 shows an example of a corner compensation feature and Figure 2-18 shows SEM images of the feature at different etch times. The compensation feature shrinks as the initial pattern is anisotropically etched since the convex corners are equivalent to fast etch planes.

The two drawbacks of this method are: (i) the etch process has to be timed, and (ii) the size of the compensation feature is dependent on the desired depth. The process window can be as small as a few seconds depending on the sharpness requirements needed for the edge since overetching leads to flattening of the corner and underetching results with part of the compensation feature remaining on the edge. The etch time is determined by the etch rate and the desired depth which dictates how large the feature needs to be. A large compensation feature means that the spacing between desired features has to be large as well, thus reducing feature density. Many different potential geometries have been developed to mitigate these drawbacks as shown in Figure 2-19.

Figure 2-18: SEM images of the corner compensation feature shown in Figure 2-16 at different etch times.<sup>63</sup>

Figure 2-19: Examples of convex corner compensation designs.<sup>64</sup>

#### 2.2.2.2 Edge Protection to Overcome Undercutting

Instead of relying on a timed etch to fabricate sharp convex edges, an alternative technique relies on the edge being protected with a hard mask to create an etch stop. After the  $SiO_2$  hard mask is patterned with the first set of gratings aligned to the vertical-(111) planes, the silicon is KOH etched to the desired depth of the pillars. The Si was etched only 650nm for the preliminary experiments. A thin  $SiO_2$  is grown on the sides of the etched trench to provide protection during the second etch. The wafer is planarized with a polymer so the second set of gratings can be patterned along the second family of vertical (111) planes. The etch process is repeated to create the other sides of the pillars. The new process flow is shown in Figure 2-20 and Figure 2-21.

Imprint 1, Dry Etch 1, Wet Etch 1 Imprint 2, Dry Etch 2, Wet Etch 2

Figure 2-20: Process flow for edge protection using two sequential sets of imprint, dry etch, and KOH wet etch steps.

Figure 2-21: Graphic depicting the new process flow starting after the initial set of gratings were etched into silicon.

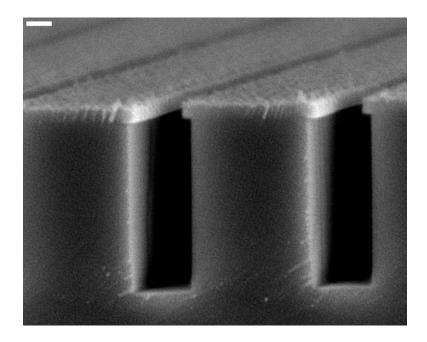

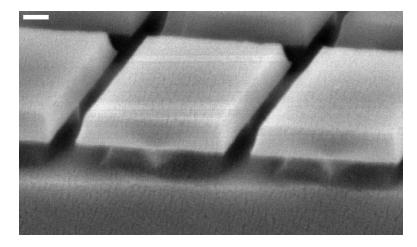

Figure 2-22, Figure 2-23, and Figure 2-24 are taken at the end of the edge protection process flow. Figure 2-22 shows the features after the second set of gratings have been etched with iCODE but before the SiO<sub>2</sub> hard mask and sidewalls have been removed. The SiO<sub>2</sub> sidewall was able to keep the vertical edges from being etched away but also kept the second etch from progressing below the point where the sidewall protected the non-vertical (111) plane. As mentioned in Section 1.3.1.2, the non-vertical (111) plane is at an angle of 54.7° from the vertical (111) plane. The SiO<sub>2</sub> sidewalls divided the second set of gratings into many pits. The problem with etching pits is described in the Section 2.2.3. The etch was deeper than it would have been if the top of the SiO<sub>2</sub> sidewall had not been slightly etched during the pattern transfer into the hard mask. This masked the non-vertical (111) planes starting ~50nm below the surface and

exposed the top of the Si pattern. Figure 2-23 and Figure 2-24 show the features with the oxide removed.

Figure 2-22: SEM image of the features after the second set of gratings are etched but before the SiO2 hard mask and side wall have been removed. Interface between Si and SiO<sub>2</sub> marked with a dashed line. Scale bar is 100 nm.

Figure 2-23: Features created by KOH etching using two imprint and two etch steps after a buffered oxide etch (BOE) to remove oxides. Scale bar is 100 nm.

Figure 2-24: Features created by KOH etching using two imprint and two etch steps after a buffered oxide etch (BOE) to remove oxides. Scale bar is 100 nm.

#### 2.2.3 Non-vertical Etch Stop Planes

The second etch step in the previous section highlighted the etch depth constraint imposed by the non-vertical (111) planes. Concave features etched into Si wafers with CODE tend to become certain concave shapes bounded by (111) slow etching planes depending on the surface orientation. A pit etched into a (100) silicon wafer, will tend to become an inverted pyramid or v-groove with sides aligned to <110> direction. The (111) surfaces are at 54.74° angle with the (100) surface. Figure 2-25 shows an example of anisotropic etch of a concave feature into a (100) wafer.

Figure 2-25: A SEM photo and schematic of the final shape of etched pits in (100)silicon.<sup>23</sup>

Etching into (110) silicon wafers will produce hexagons with two of the opposing sides sloping downwards since four of the (111) planes intersect the (110) surface at a right angle and two with a 35.26° angle. The vertical planes intersect each other at a 109.47° angle. Figure 2-26 shows the shape of a feature etched with CODE in a (110) wafer. This project will focus on (110) silicon wafers because the vertical (111) planes can be used to create features with smooth, vertical sidewalls whereas (100) wafers will always have sloped walls that converge and prevent deep etching.

Figure 2-26: Etched features are defined by four vetical (111) planes and two sloped (111) planes shown. (Modified from <sup>66</sup>)

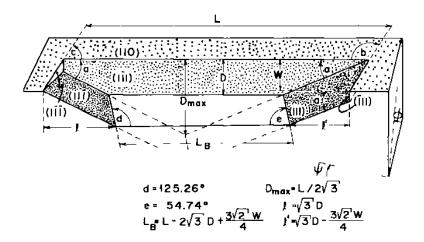

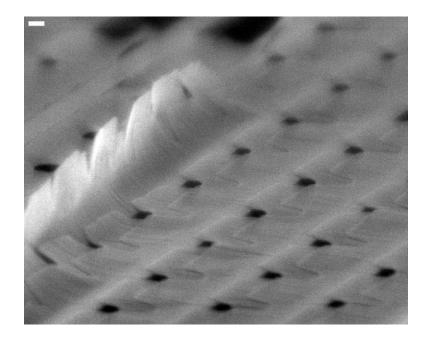

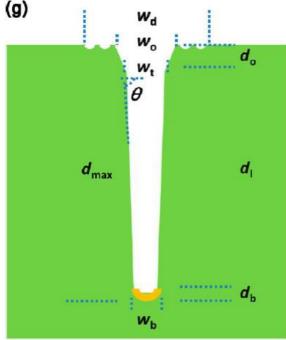

Figure 2-27 shows the angle and distance relationships for a pit etched in a (110) wafer.  $D_{max}$  is the maximum etch depth which is limited by the intersection of the non-vertical (111) planes that are protected by the mask. Long trenches that are aligned to the vertical (111) planes can be deeply etched because the non-vertical (111) planes start far apart at the ends of the line on the surface of the wafer. Adding the SiO<sub>2</sub> sidewalls to protect the convex edge reduces the distance between the non-vertical (111) planes to the same length as the width of the trench. The max etch depth is approximately 144nm because the sidewalls are ~500 nm apart and the non-vertical (111) planes intersect the surface at a 35.26 degree angle. If the SiO<sub>2</sub> sidewall could be selectively removed, then the second etch would be similar to etching a second set of trenches and the potential depth would be the same as the first set of trenches. Figure 2-28 shows the change in etch depth due to the non-vertical (111) planes that were protected by the SiO<sub>2</sub> hard mask at the end of the trenches.

Figure 2-27: Graphic of the dependence of max etch depth on mask size.<sup>67</sup>

Figure 2-28: SEM image of etched trenches shows the non-vertical (111) planes restricting etch depth near their line ends. Scale bar is 1 μm.

### 2.2.3.1 Methods of Overcoming the Etch Depth Restriction for Concave Features