Copyright

by

Dylan Conrad Pfeifer

2013

# The Dissertation Committee for Dylan Conrad Pfeifer Certifies that this is the approved version of the following dissertation:

# Parallel and Distributed Cyber-Physical System Simulation

**Committee:**

Jonathan Valvano, Co-Supervisor

Andreas Gerstlauer, Co-Supervisor

Derek Chiou

Ranjit Gharpurey

Gian Gerosa

# Parallel and Distributed Cyber-Physical System Simulation

by

# Dylan Conrad Pfeifer, B.A.; B.S. Math; M.S.E.

# Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

# **Doctor of Philosophy**

The University of Texas at Austin December 2013

# Dedication

To my parents, Walt and Jeri Pfeifer.

### Acknowledgements

This work concludes a journey that has required the faith and support of many participants. Acknowledgement first goes to my research supervisor, Jonathan Valvano, who took me on as a Ph.D. student and proposed a course of research in the hybrid simulation of hardware and software systems, which evolved into the rich study of parallel and distributed simulation. Next, my co-supervisor, Andreas Gerstlauer, and committee members Derek Chiou, Gian Gerosa, and Ranjit Gharpurey deepened the work with supportive and consistent challenges during the course of research and discovery. Jonathan and Andreas provided substantial direction as well guiding the conference and journal publications resulting from the work.

While attending conferences and presenting papers during the research, I had great opportunities to meet recognized researchers in the field of parallel and distributed simulation, particularly Edward Lee of U.C. Berkeley, Richard Fujimoto of Georgia Tech, and David Jefferson of Lawrence Livermore National Laboratory. I also had the fortune to meet Christoph Grimm of SystemC-AMS development, Rishiyur Nikhil of Bluespec, Inc., who encouraged me to give a faculty talk at the University of Manchester, and Jim Garside of the University of Manchester, who was kind enough to facilitate the talk. These were great experiences, and these research leaders were kind to me and attentive to my ideas and questions.

Grateful acknowledgement is due to Intel Corporation, which allowed me to pursue Ph.D. research while also working as an Intel employee through the years 2009-2013. My managers, Sanjoy Mondal, Pankaj Kukkal, Nick Samra, and Haytham Samarchi were supportive during critical times of the work and committed to seeing me reach the final phases of the degree. Family and friends have provided unflagging support, particularly my parents, brother, and grandmother, as they have in everything I have endeavored. The doctoral tradition established by my grandfather and continued through my mother and aunt helped me feel I could complete the journey, and my grandmother provided superior wisdom from many years of faculty roles. My father helped grow my imagination skills at a young age with discussions about the sciences, and my paternal grandmother started teaching me very early. The indefatigable support of my mother and father through the journey to doctorate can only be compared to the divine.

In that direction, I must acknowledge a faith in and gratitude towards a higher power, which created this universe with sufficient complexity that Ph.D. degrees may continue to be earned by students for some time to come. The acknowledgement of this creator is the beginning of knowledge. We are granted a partnership, such that if we try, we are met with wonders.

# Parallel and Distributed Cyber-Physical System Simulation

Dylan Conrad Pfeifer, Ph.D.

The University of Texas at Austin, 2013

Supervisors: Jonathan Valvano and Andreas Gerstlauer

The traditions of real-time and embedded system engineering have evolved into a new field of cyber-physical systems (CPSs). The increase in complexity of CPS components and the multi-domain engineering composition of CPSs challenge the current best practices in design and simulation. To address the challenges of CPS simulation, this work introduces a simulator coordination method drawing from strengths of the field of parallel and distributed simulation (PADS), yet offering benefits aimed towards the challenges of coordinating CPS engineering design simulators. The method offers the novel concept of Interpolated Event data types applied to Kahn Process Networks in order to provide simulator coordination. This can enable conservative and optimistic coordination of multiple heterogeneous and homogeneous simulators, but provide important benefits for CPS simulation, such as the opportunity to reduce functional requirements for simulator interfacing compared to existing solutions. The method is analyzed in theoretical properties and instantiated in software tools SimConnect and SimTalk. Finally, an experimental study applies the method and tools to accelerate Spice circuit simulation with tradeoffs in speed versus accuracy, and demonstrates the coordination of three heterogeneous simulators for a CPS simulation with increasing model refinement and realism.

# **Table of Contents**

| List of Tablesxi                                                  | i |  |

|-------------------------------------------------------------------|---|--|

| List of Figures                                                   | i |  |

| List of Illustrationsxv                                           | V |  |

| CHAPTER ONE. INTRODUCTION                                         | 1 |  |

| 1.1 Challenges of Cyber-Physical System Simulation                | 2 |  |

| 1.2 Leading Coordination Solutions and Limits with CPS Simulation | 5 |  |

| 1.2.1 The IEEE 1516 High Level Architecture (HLA)                 | 6 |  |

| 1.2.2 The Discrete Event System Specification (DEVS)              | 7 |  |

| 1.2.3 Other Significant Solutions                                 | 8 |  |

| 1.3 Thesis Statement: The KPN-IE Method for PADS10                | 0 |  |

| 1.4 Original Contributions                                        | 0 |  |

| 1.4.1 Original Contributions to the Field of PADS10               | 0 |  |

| 1.4.2 Original Contributions through Enabling Technologies1       | 1 |  |

| 1.4.3 SimConnect and SimTalk Features                             | 1 |  |

| 1.5 Overview of the KPN-IE Method for CPS PADS                    | 2 |  |

| 1.5.1 The Interfacing Approach                                    | 2 |  |

| 1.5.2 The Dataflow Approach                                       | 3 |  |

| 1.5.3 Simplified Interfacing                                      | 3 |  |

| 1.5.4 Simplified Messaging14                                      | 4 |  |

| 1.5.5 Analysis14                                                  | 4 |  |

| 1.5.6 Non-exclusivity1                                            | 5 |  |

| 1.6 Organization of Thesis                                        |   |  |

| CHAPTER TWO. THEORY OF MODELING AND SIMULATION 18                 |   |  |

| 2.1 Modeling                                                      | 0 |  |

| 2.1.1 State Transition Systems                                    | 0 |  |

| 2.1.2       | Timed Models                                              | 21 |

|-------------|-----------------------------------------------------------|----|

| 2.1.3       | Time Driven Models                                        | 22 |

| 2.1.4       | Event Driven Models                                       | 22 |

| 2.1.5       | Errors in Modeling                                        | 24 |

| 2.2 Simula  | tion                                                      | 25 |

| 2.2.1       | Accounting for Time in Digital Simulation                 | 26 |

| 2.2.2       | Simulating Timed, Event Driven Models                     | 27 |

|             | Equivocating Time Driven and Event Driven Models          | 27 |

|             | Discrete Time, Discrete Event Simulation                  | 28 |

|             | Logical Processes                                         | 29 |

|             | The DEVS Formalism                                        | 29 |

|             | Subtleties between LP and DEVS                            | 30 |

| 2.2.3       | Distributed, Parallel, Timed, Discrete Event Models       | 31 |

|             | The Challenges of Distribution and Parallelism            | 32 |

|             | Coupling Error                                            | 34 |

| 2.2.4       | Methods of Parallel and Distributed, Timed Discrete Event |    |

|             | Simulation                                                | 34 |

|             | Definitions                                               | 34 |

|             | Conservative Simulation                                   |    |

|             | Optimistic Simulation                                     | 37 |

| 2.3 Chapter | r Summary                                                 | 39 |

| CHAPTER     | <b>THREE. INTERPOLATED EVENTS AND PORTS</b>               | 40 |

| 3.1 Interpo | plated Events                                             | 40 |

| 3.1.1       | Definition and Properties                                 | 40 |

| 3.1.2       | Operations on Interpolated Events                         | 41 |

| 3.2 Interpo | plated Event Ports                                        | 43 |

| 3.2.1       | Interpolated Event Output Ports                           | 43 |

| 3.2.2       | Interpolated Event Input Ports                            | 46 |

| 3.3 A Simula   | tion Time Cost Function with IEs and IE Ports          | 48  |

|----------------|--------------------------------------------------------|-----|

| 3.4 Error and  | Accuracy with IEs and IE Ports                         | 60  |

| 3.5 Chapter S  | ummary                                                 | 68  |

| CHAPTER FO     | UR. KAHN PROCESS NETWORKS AND INTERPOLATED EVENTS      | 69  |

| 4.1 Kahn Pro   | cess Networks                                          | 69  |

| 4.2 Dynamics   | s of Kahn Process Networks and Interpolated Events     | 71  |

| 4.2.1 Ka       | ahn Process Networks and Simulator Coordination        | 71  |

|                | The Simulator IE Port Servicing Sequence               | 71  |

|                | A Conservative Coordination Example                    | 73  |

|                | The KPN-IE Connection Servicing Sequence               | 83  |

| 4.2.2 Pr       | operties of KPN and IE Servicing                       | 84  |

| 4.3 An Optim   | istic Coordination Algorithm with the KPN-IE Method    | 86  |

| 4.4 A Combin   | ned Conservative and Optimistic Coordination Algorithm |     |

| with the F     | KPN-IE Method                                          | 89  |

| 4.5 Chapter S  | ummary                                                 | 91  |

| CHAPTER FIV    | E. SIMCONNECT AND SIMTALK IMPLEMENTATION               | 92  |

| 5.1 The KPN    | -IE Method with SimConnect and SimTalk                 | 92  |

| 5.2 SimConn    | ect                                                    | 95  |

| 5.3 SimTalk.   |                                                        | 96  |

| 5.4 Dynamic    | Resolution                                             | 98  |

| 5.5 Distributi | on, Synchronization, and CPS Simulators                | 99  |

| 5.6 Software   | Metric Comparisons with HLA                            | 103 |

| 5.6.1 Sc       | ource Code Comparisons                                 | 103 |

| 5.6.2 A        | pplication Layer Messaging Comparisons                 | 106 |

| 5.7 Chapter Summary                                            | 109 |

|----------------------------------------------------------------|-----|

| CHAPTER SIX. EXPERIMENTS AND RESULTS                           | 111 |

| 6.1 Homogeneous Coordination                                   | 111 |

| 6.1.1 Distributed Spice Coordination                           | 111 |

| 6.1.2 Distributed Spice Summary and Conclusions                |     |

| 6.2 Heterogeneous Coordination                                 |     |

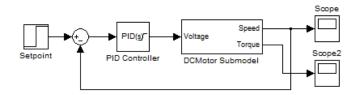

| 6.2.1 Distributed PID/PWM Software-based Motor Control         | 121 |

| 6.2.2 Heterogeneous Simulation Summary and Conclusions         |     |

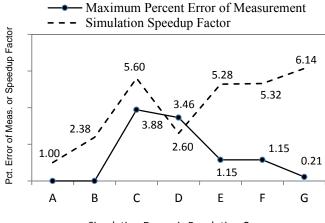

| 6.3 Dynamic Resolution in Heterogeneous Coordination           | 140 |

| 6.4 Chapter Summary                                            | 147 |

| CHAPTER SEVEN. THESIS SUMMARY AND FUTURE WORK                  | 149 |

| 7.1 Benefits of the KPN-IE Method, Implementation, and Results | 149 |

| 7.2 Opportunities                                              |     |

| BIBLIOGRAPHY                                                   | 155 |

# List of Tables

| Table 1. | SimConnect/SimTalk code sizes and development costs  | .104 |

|----------|------------------------------------------------------|------|

| Table 2. | Open source HLA code metrics                         | .105 |

| Table 3. | DC motor model parameters                            | .122 |

| Table 4. | Simulation times, configurations and message traffic | .139 |

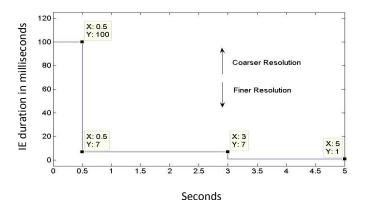

| Table 5. | Dynamic resolution case times and counters           | .146 |

| Table 6. | Simulation times, configurations and traffic legend  | .146 |

# List of Figures

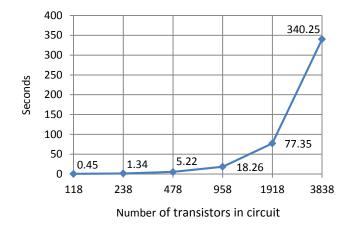

| Figure 1. | Ngspice transient analysis time for $1.5 \ \mu s$ of simulation time as |      |

|-----------|-------------------------------------------------------------------------|------|

|           | counter width increases                                                 | .115 |

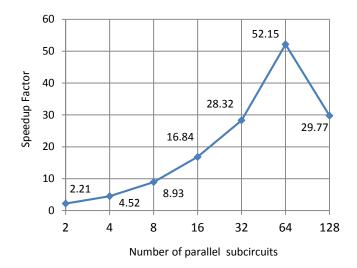

| Figure 2. | Speedup at 10 ns IE resolution                                          | .117 |

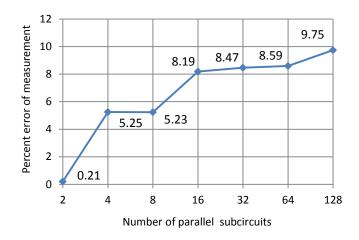

| Figure 3. | Percent error of measurement at 10 ns IE resolution                     | .118 |

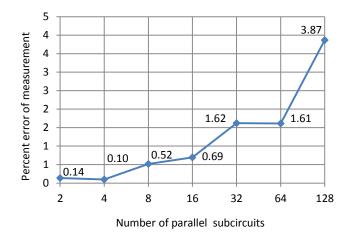

| Figure 4. | Percent error of measurement at 2 ns IE resolution                      | .119 |

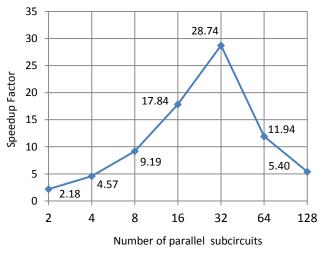

| Figure 5. | Speedup at 2 ns IE resolution                                           | .119 |

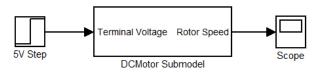

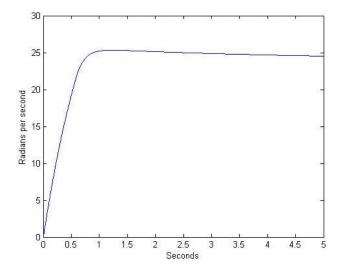

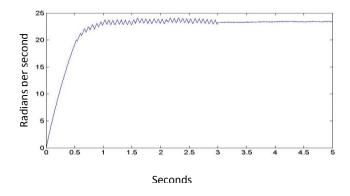

| Figure 6. | Model rotor speed versus time, open-loop transient response to a        |      |

|           | 5 Volt step function                                                    | .124 |

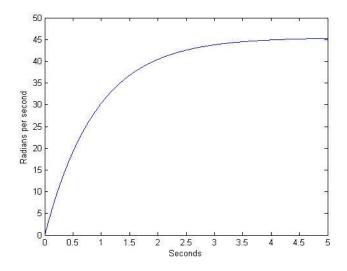

| Figure 7. | Model rotor speed versus time in Simulink continuous PID                |      |

|           | controller closed-loop transient response                               | .125 |

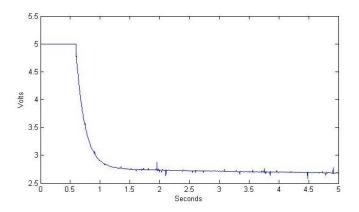

| Figure 8. | Model controller effort in Simulink continuous PID controller           |      |

|           | transient applied voltage                                               | .125 |

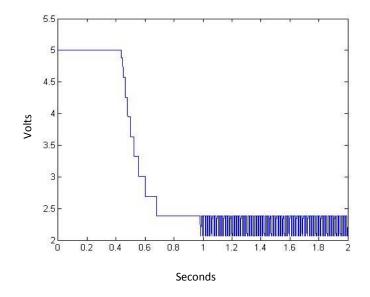

| Figure 9. | Quantized output controller effort in Simulink quantized PID            |      |

|           | controller applied voltage                                              | .127 |

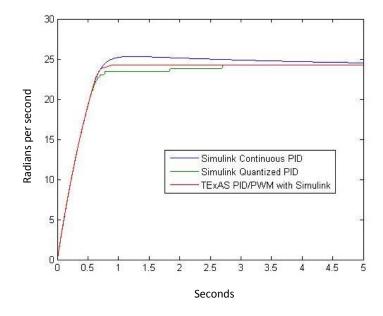

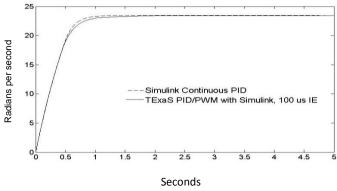

| Figure 10 | . Model output speed versus time with Simulink-only and                 |      |

|           | 2-simulator PID control model cases                                     | .129 |

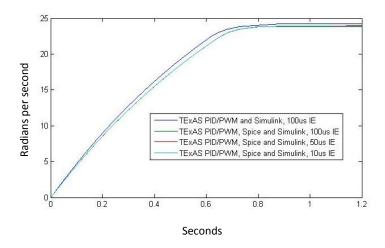

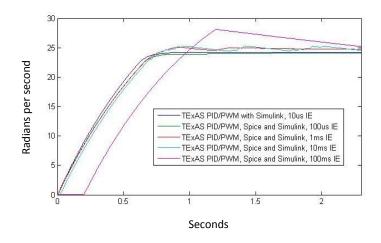

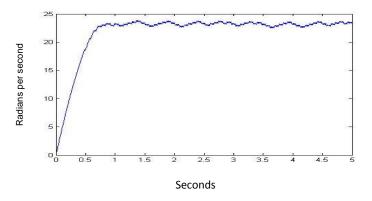

| Figure 11 | . Model speed versus time in 2 and 3-Simulator configurations           | .134 |

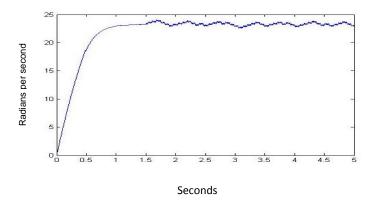

| Figure 12 | . Variation in model rotor output speed versus time as a function       |      |

|           | of IE resolution                                                        | .135 |

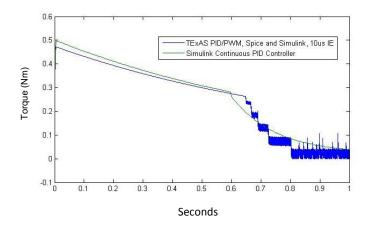

| Figure 13 | . Discrete versus continuous model controller effort, applied motor     |      |

|           | torque versus time in 1-simulator and 3-simulator cases                 | .137 |

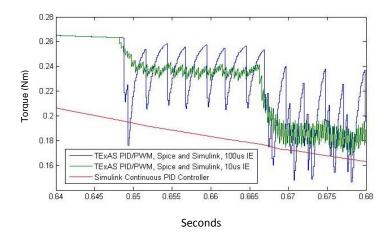

| Figure 14 | . Discrete versus continuous model controller effort, applied motor     |      |

|           | torque versus time in 1-simulator and two 3-simulator cases             | .138 |

| i iguite 15. | wooder output speed versus time with Simulink-Only and |     |

|--------------|--------------------------------------------------------|-----|

|              | 2-simulator PID control model cases                    | 140 |

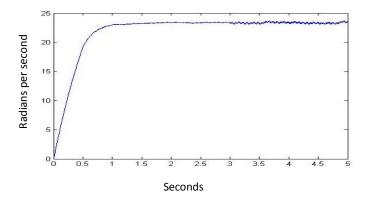

| Figure 16.   | Case C model output speed versus time                  | 141 |

| Figure 17.   | Case D model output speed versus time                  | 141 |

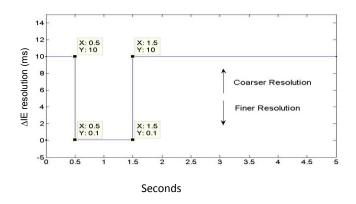

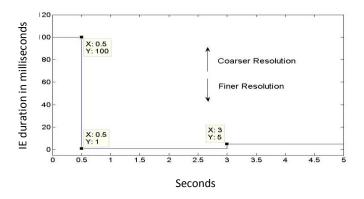

| Figure 18.   | Case D dynamic IE duration change                      | 142 |

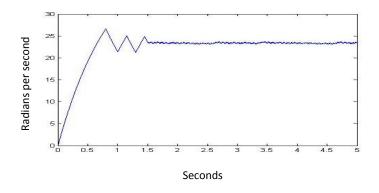

| Figure 19.   | Case E model output speed versus time                  | 142 |

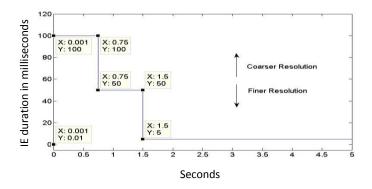

| Figure 20.   | Case E dynamic IE duration change                      | 143 |

| Figure 21.   | Case F model output speed versus time                  | 143 |

| Figure 22.   | Case F dynamic IE duration change                      | 144 |

| Figure 23.   | Case G model output speed versus time                  | 144 |

| Figure 24.   | Case G dynamic IE duration change                      | 145 |

| Figure 25.   | Speedup versus accuracy with dynamic resolution cases  | 146 |

# Figure 15. Model output speed versus time with Simulink-only and

# **List of Illustrations**

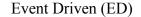

| Illustration 1. Quadrant based categories of timed state transition systems | .23 |

|-----------------------------------------------------------------------------|-----|

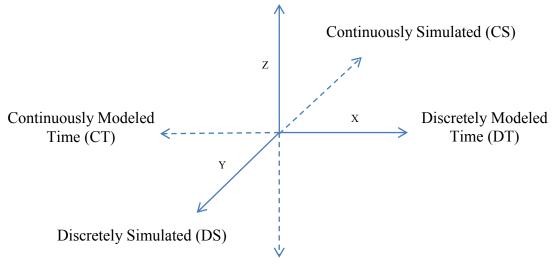

| Illustration 2. State elements of the Interpolated Event Output Port        | .44 |

| Illustration 3. Interpolated Event Output Port pseudo code example          | .45 |

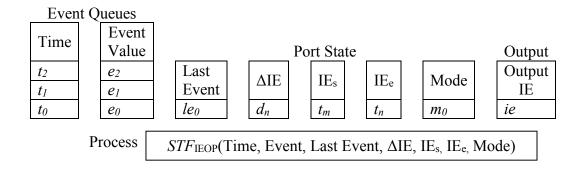

| Illustration 4. Interpolated Event Input Port state elements                | .46 |

| Illustration 5. Interpolated Event Input Port pseudo code example           | .47 |

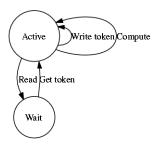

| Illustration 6. The Kahn Process Network node read, wait, and execute cycle | .71 |

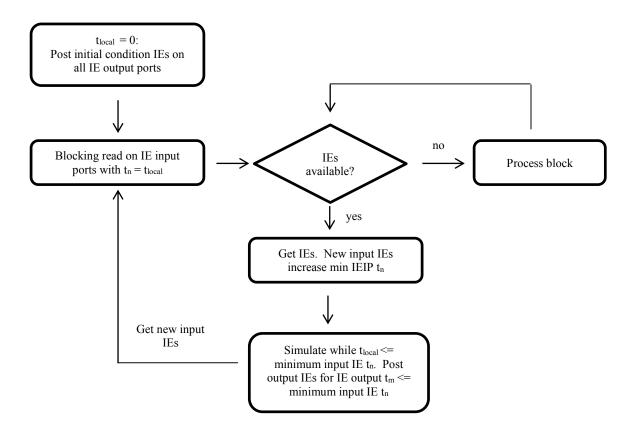

| Illustration 7. The simulator IE port servicing flowchart                   | .72 |

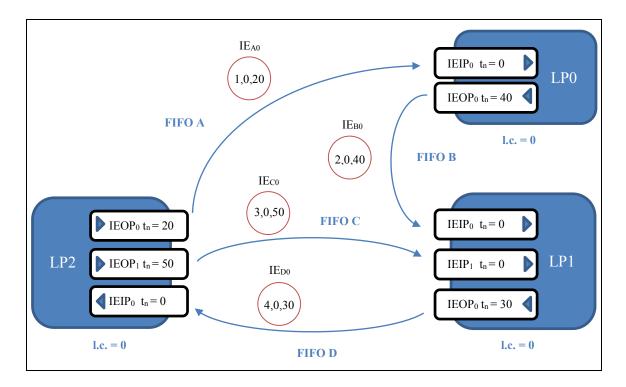

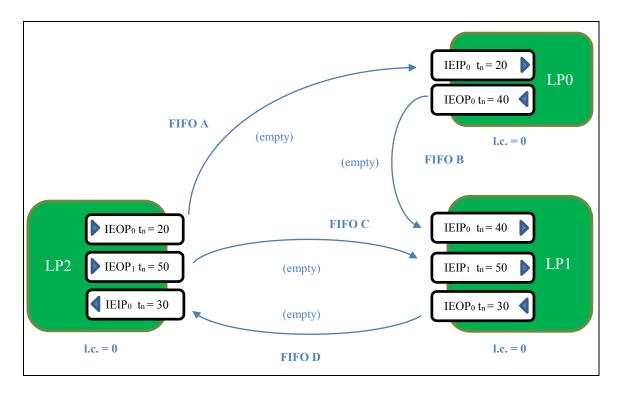

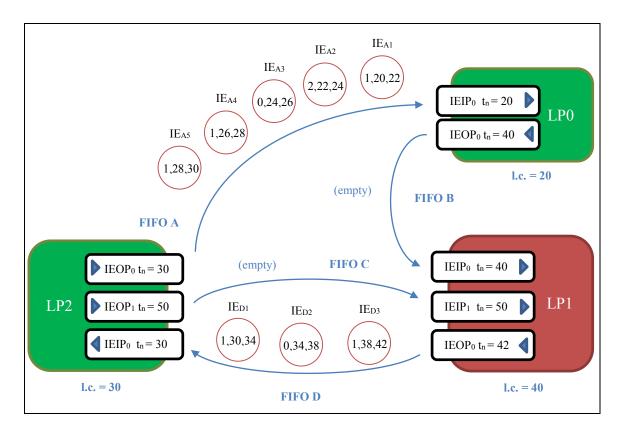

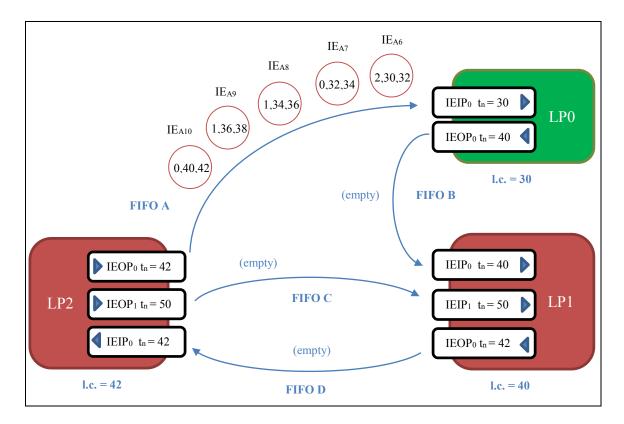

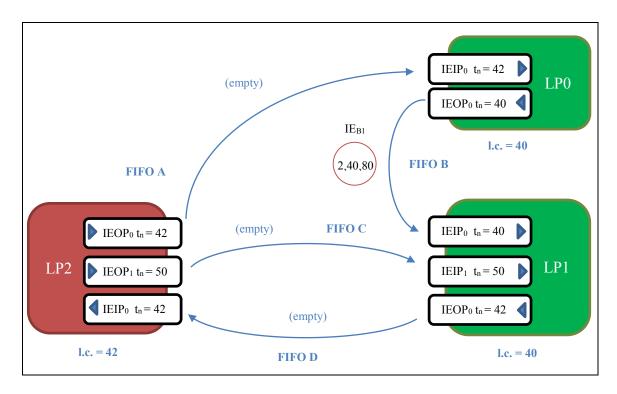

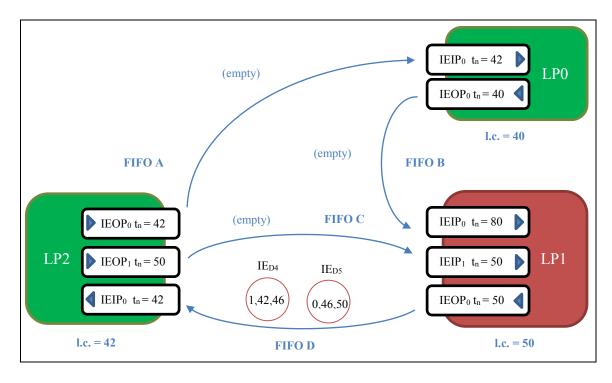

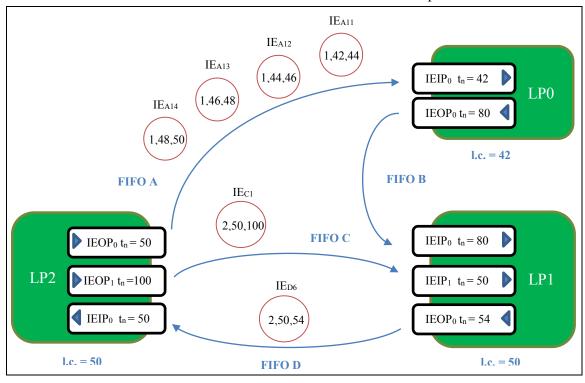

| Illustration 8. Conservative KPN-IE coordination example                    | .74 |

| Illustration 9. Conservative KPN-IE coordination example continued 1        | .75 |

| Illustration 10. Conservative KPN-IE coordination example continued 2       | .76 |

| Illustration 11. Conservative KPN-IE coordination example continued 3       | .77 |

| Illustration 12. Conservative KPN-IE coordination example continued 4       | .78 |

| Illustration 13. Conservative KPN-IE coordination example continued 5       | .79 |

| Illustration 14. Conservative KPN-IE coordination example continued 6       | .79 |

| Illustration 15. Conservative KPN-IE coordination example FIFO point of     |     |

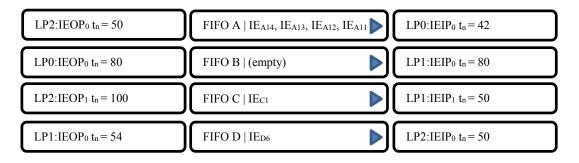

| view                                                                        | .80 |

| Illustration 16. Conservative KPN-IE coordination example port servicing    |     |

| point of view                                                               | .81 |

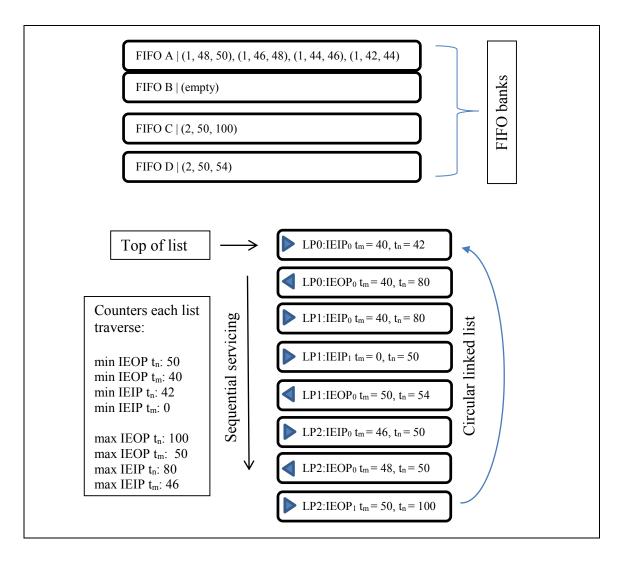

| Illustration 17. The KPN-IE backplane connection servicing flowchart        | .83 |

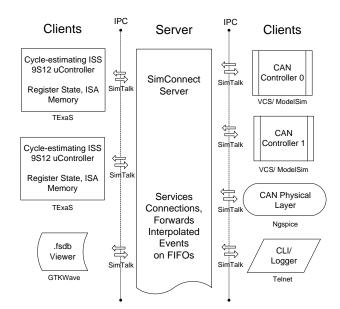

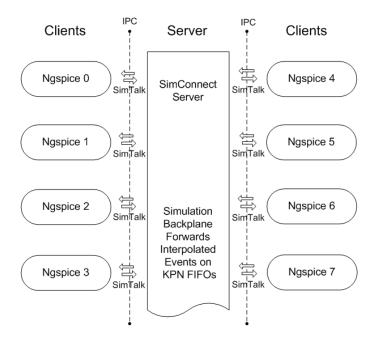

| Illustration 18. Heterogeneous client-server hierarchy and network          |     |

| distribution                                                                | .99 |

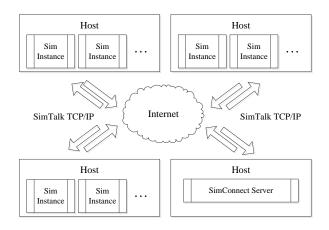

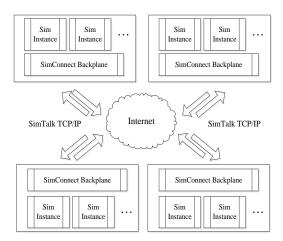

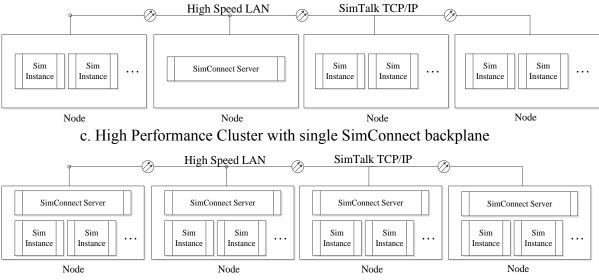

| Illustration 19. SimConnect/SimTalk client-server network distributions1    | .01 |

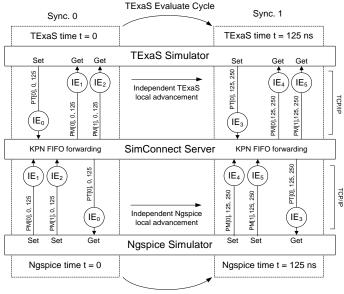

| Illustration 20. Conservative, predicted event synchronization1             | .02 |

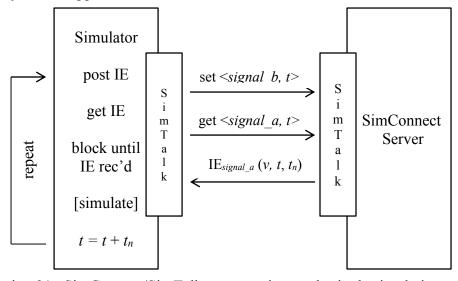

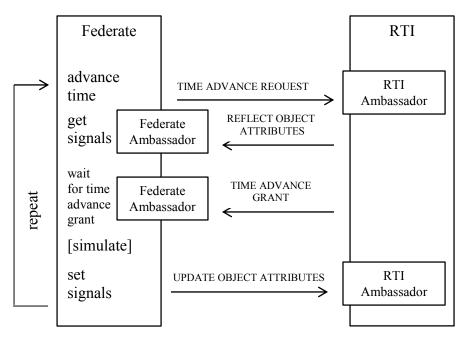

| Illustration 21. | SimConnect/SimTalk conservative mode single simulation      |     |

|------------------|-------------------------------------------------------------|-----|

|                  | cycle                                                       | 107 |

| Illustration 22. | Example conservative time driven federate-RTI simulation    |     |

|                  | cycle [74]                                                  | 109 |

| Illustration 23. | SimConnect/SimTalk relationship for distributed, parallel   |     |

|                  | Ngspice instances                                           | 113 |

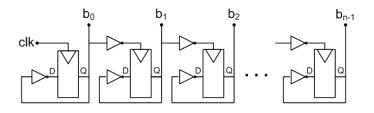

| Illustration 24. | <n>-bit asynchronous ripple counter</n>                     | 113 |

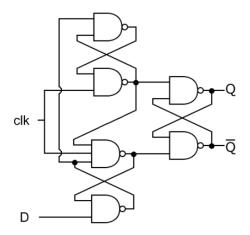

| Illustration 25. | Edge-triggered D flip-flop                                  | 114 |

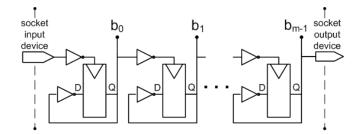

| Illustration 26. | Partitioned subcircuit with socket devices                  | 116 |

| Illustration 27. | 2 <sup>nd</sup> order DC motor model transfer function [18] | 122 |

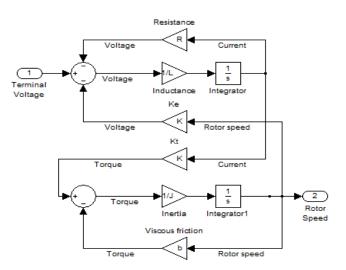

| Illustration 28. | Simulink DC motor electro-mechanical model                  | 123 |

| Illustration 29. | Simulink open-loop 5V step-function stimulus                | 124 |

| Illustration 30. | Simulink continuous PID controller                          | 125 |

| Illustration 31. | Simulink quantized PID controller                           | 126 |

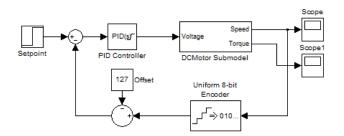

| Illustration 32. | 2-Simulator configuration                                   | 127 |

| Illustration 33. | Simulink DC motor model with SimTalk I/O interface          | 128 |

| Illustration 34. | 3-Simulator configuration                                   | 130 |

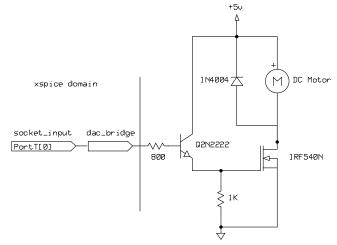

| Illustration 35. | Ngspice model for motor driver circuit                      | 131 |

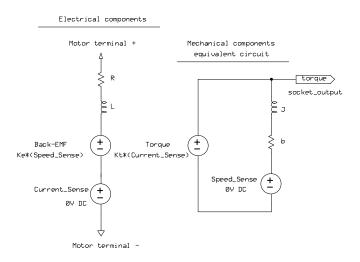

| Illustration 36. | Ngspice models for DC motor electrical and mechanical       |     |

|                  | components                                                  | 131 |

| Illustration 37. | Ngspice deck for motor and driver                           | 132 |

| Illustration 38. | Ngspice SimTalk devices 100 µs IE resolution                | 133 |

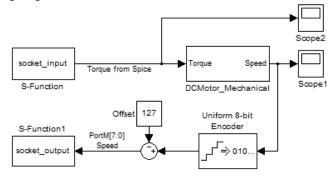

| Illustration 39. | Simulink co-simulation model with mechanical only DC        |     |

|                  | motor model                                                 | 133 |

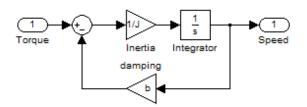

| Illustration 40. | Simulink mechanical only DC motor submodel                  | 134 |

## **CHAPTER ONE. INTRODUCTION**

Cyber-physical systems (CPSs), defined as systems that integrate computation and physical processes, are becoming increasingly important for their transformative potential. Inheriting the field of embedded systems, but offering more distribution, communication, and computation capabilities, CPSs suggest new engineering and scientific opportunities as the number computational elements per device grows while devices shrink in terms of power requirements, cost, and size. The transformative power of what CPSs may have to offer in terms of controlled, coupled computation and physical processes has the "potential to dwarf the 20th century IT revolution" by virtue of ubiquity and impact [1]. The impact reaches everything from medicine to civil engineering, energy, defense, transportation, and smart consumer homes and devices [2].

Heterogeneous by definition, cyber-physical systems challenge their constituent disciplines, including electrical and computer engineering, computer science, mechanical engineering, biomedical engineering, and the traditional sciences. By consequence of their multi-domain composition, CPSs also challenge the discipline of simulation. Simulation is useful for systems where constructing a physical prototype and verifying functionality through build and test iterations is costly or perhaps impossible. Even if physical prototyping is manageable, simulation may still benefit the engineering design cycle, particularly for the computational side of the system during phases of integrated circuit design and verification, software development, and board-level circuit design. CPSs involving many independent computational elements interacting with the physical environment through transducers and actuators may have emergent properties that may not be discovered until the system is constructed and tested with real world physical processes. It is desirable to discover some of these properties in simulation rather than reality, so that the software for the CPS is in an advanced state of functionality by the time the system is physically constructed. Therefore, simulation is beneficial not only to CPS behavioral discovery, but also to the best practices of CPS engineering. Robust, diverse, accurate, observable, and time-feasible simulation can enable adept and elegant CPS design.

### 1.1 Challenges of Cyber-Physical System Simulation

CPSs are composed of heterogeneous computation and physical processes [1]. At a system level, CPS simulation can require coordinating models of electrical hardware components (such digital processors, analog electronics, and mixed-signal applicationspecific integrated circuits), software components (real-time operating systems, softwarebased digital filters, software-based control, networking protocols), and physical models (such as transducers, dynamical systems, mechanical devices, and biological systems), each at potentially different levels of abstraction. These models may be simulated with continuous differential equation-based mathematical models of world physical processes, such as fluid dynamics or electromagnetics, and discrete based models for computational components. The challenge of mixing these components from different engineering and modeling domains for CPS simulation is called the "heterogeneous domain" challenge.

No single simulator or model of computation arguably spans the range of components that must be simulated by this challenge. For example, a cycle-estimating processor instruction set simulator may not be adequate for simulating an electrical network at the voltage and current level, but may be adequate for simulating the register and memory state of a processor for software development. A lumped element circuit simulator such as Spice [33], while popularly used for simulating circuits at the electrical level, may not be sufficient for simulating world-physical effects in CPSs that may need

to be modeled with space and time resolution, such as computational electromagnetics (CEM) or computational fluid dynamics (CFD). Finally, gate-level, clock-cycle accurate simulators supporting languages such as Verilog or VHDL can simulate large-scale VLSI circuits with gate-level resolution, but may not be sufficient for simulating high level software running over a virtual model for minutes of simulated software time.

Each of these domains, models, and simulation environments can be combined and coordinated to overcome some of their individual limitations. Mixes of simulators specializing in individual subsystems and modeling domains can increase the modeling range of simulation compared to a single simulator solution. Multiple simulator communication and coordination is both a benefit and challenge for system-level CPS simulation. The challenge arises as a consequence of model and model-of-computation diversity in CPSs, and as a consequence of simulation time cost. As the number of modeled components in a system increases, the time cost of simulation for some single simulators may increase exponentially. For some simulations, it may be possible to reduce the time cost of sequential simulation by partitioning the system among parallel, independent simulators, or leveraging algorithmic parallelism in the simulator where it exists. However, parallel simulation can introduce even more simulator communication and synchronization challenges.

Because software components (firmware, real-time operating systems, middleware, communication stacks, protocols, digital filters, and so on) are significant components of CPSs [4][5], simulation of software interacting with virtual models is another challenge to CPS simulation. Software is conventionally developed and modeled with a debugger running over a real, emulated, or virtual target such as a processor instruction set simulator. Debugging software over virtual processor targets that include extra-processor models (like interfacing electronics, discrete hardware, transducers, and physical processes) is a challenge to system-level CPS simulation. Software debugging requires the ability to insert breakpoints into the debugger, single-step the program counter, or stop the debugger in time to inspect the target processor state, such as registers and memory. This is the source level debugging requirement of CPS software simulation. Yet, a CPS includes more components interacting with the software than just the simulated processor state. So, source-level debugging of software at system-level CPS simulation requires the ability to stop and inspect the state of other simulated models running outside of the processor target model that are affected by the simulated software.

Also, a CPS may include not just one processor target and software stack, but many virtual processors such as with a multi-core system, sensor grid, or multi-node industrial automation network. To support source level software debugging, extraprocessor models must be able stop in time with each CPS software component being simulated and debugged, and then be able to resume without losing state or having state become altered by the pause and inspection. This is a distributed breakpoint problem across coordinated models, compared to single target breakpoints.

The software challenge of CPS simulation is further elaborated in [1] and [3]. Traditional embedded systems may couple computation with physical inputs through processor interrupts or cyclic polling. Testing software behavior to these inputs in simulation over a virtual processor model requires being able to pass extra-processor state into the processor model from a simulate peripheral in order to generate a simulated interrupt as it would occur in real hardware. For a CPS simulation, it is desired that these inputs actually come from simulated world physical process models acting through modeled transducers and peripherals. So, model coupling is a challenge because the

extra-processor models may be entirely different models of computation than the processor models. Therefore, just as CPSs challenge the scientific intersection of physical processes and computation interacting in real life, so also do they challenge the intersection of physical processes and computation modeled together in simulation.

### **1.2 Leading Coordination Solutions and Limits with CPS Simulation**

Each of these challenges places CPS simulation firmly in the field of parallel and distributed simulation (PADS) [6][7][8], but with new challenges of diverse model coordination. Since the parallel and distributed simulation (PADS) challenge has been well represented in the modeling and simulation literature over the past three decades, with fundamental results by [6][7][8], it is important to identify contributions that may also benefit distributed CPS simulation.

PADS methods fall into categories of conservative or optimistic simulator coordination, or a mix of both [30]. These can be implemented with conservative messaging schemes such as the Chandy/Misra/Bryant-style null messages for conservative coordination [7], the numerous lookahead-based schemes for conservative coordination inspired by the Chandy/Misra/Bryant solution [36], or optimistic coordination approaches inspired from the Jefferson Time Warp solution [65].

Two important solutions among PADS implementations that inherit strengths of these approaches are the United States Department of Defense originated "High Level Architecture" (HLA), which has become IEEE standard 1516 [19], and the set-theoretic Discrete Event System Specification (DEVS) formalism, originating from Bernard Ziegler [20], resulting in tools such as Oak Ridge National Lab's ADEVS suite [21].

### 1.2.1 THE IEEE 1516 HIGH LEVEL ARCHITECTURE (HLA)

HLA has shown particularly effective with large-scale, real-time, distributed military simulations with humans-in-the-loop (HIL) in the simulation federation. HLA's success in military simulation and training has earned it recognition as "the most influential standard in the field of distributed simulation" [22]. HLA is an architectural specification, and implementations offer simulator synchronization through the time management services of the Run-Time Infrastructure (RTI) specification of the architecture, which controls when time regulated federated simulators may advance in time [23]. Federates declare a Federation Object Model (FOM) of signals they will exchange and their attributes, and the HLA RTI supports techniques from the PADS literature for combined conservative and optimistic distributed simulation [23].

However, HLA has not yet been widely employed in engineering system design, embedded systems, or CPS system-level simulation to the definitive level of contribution it has provided for defense simulation and training. RTI software ambassadors for CPS components, for example, presently lack widespread instantiation among popular engineering software debuggers, logic simulation tools, and design automation tools. Yet, the potential for HLA as an embedded system and CPS simulation solution is recognized [27]. Also recognized is the outstanding effort to enable it by connecting tools such as VLSI electronic design automation tools into an HLA federation [24]. A shift of support for HLA RTI plugins among the major VLSI design vendors such as Cadence [25] and Synopsis [26] could signal a possible EDA industry migration to the solution. While Matlab/Simulink [21] now supports an HLA-Toolbox, and Matlab/Simulink is used as a numerical simulation federate in some reports [30], in CPS simulation we also desire to simulate numerous electronic components, such as ones widely supported by Spice models [31]. The authors in [27] state that their technique to transform Simulink models into an HLA federate merits improvement, supporting only fixed time step advancement, for example.

Therefore, for complexity challenges of integrating numerical system simulation, software debuggers, and VLSI design automation integration into RTI-enforced coordination, HLA as stand-out solution to system-level design and simulation coordination for CPS engineering is open to be demonstrated. However, it is clearly valuable to CPS simulation for the multitude of world effects by HLA-compliant simulators offered and its IEEE standardization [19]. Its primary drawback to CPS simulation is that many diverse simulators must be coordinated to achieve a broad reach for CPS modeling and simulation, and the HLA RTI interfacing approach demands very tight integration with simulator runtime kernels. The tight simulator-level interfacing required to coordinate a closed architecture simulator with an HLA RTI may be an important market and research time cost. For CPS simulation, we volunteer a solution with coordination fidelity (attention to time synchronization and causality) and an interface specified primarily in the model definition layer rather than simulation kernel layer. We also seek to impose fewer and more simple functional interfacing requirements on federated simulators.

### **1.2.2** The Discrete Event System Specification (DEVS)

The Discrete Event System Specification (DEVS), introduced in 1976 [20], focuses on model formalisms and formal algorithms to correctly simulate them, thereby separating as much as possible the art of modeling from the art of simulation. In this way a model can be verified to the degree it complies with a DEVS formalism, and a simulator can be verified to the degree executes a DEVS algorithm. The strength of DEVS is that it defines model interfacing channels for a variety of set theoretic models,

allowing for a general modeling specification with closure under model composition. When any DEVS conforming model is expressed in the DEVS notation, it can be coordinated with any other model in the DEVS system through DEVS model channels. ADEVS ("A Discrete Event System Simulator") [21] is a coordination solution in a set of open source C++ libraries that offers hybrid and distributed co-simulation for models conforming to the DEVS formalisms [20].

The primary limitation of DEVS for CPS PADS is that models must be expressed in a DEVS formalism to participate. For the range of models and devices we should like to include in a CPS simulation, such as the many circuit-level devices modeled in Spice simulators [31], we may not have market or research time to remodel the components of the CPS in DEVS. Rather, we should like to pick up a model as given, or where expertly simulated in the best environment, and interface that model and environment to other models and environments. We call this the "interfacing approach."

#### **1.2.3 OTHER SIGNIFICANT SOLUTIONS**

Other notable solutions include SimBus/Xyce [48], a parallel VHDL and parallel Spice solution from Sandia National Labs, backplane based solutions (examples of which are [12][13][14]), and 2- to 3-simulator special case coordinations, instances of which are numerous in the IEEE and ACM literature. However, these classes of solutions can require internal modification of the coordinated simulator kernels, which may not be allowed when interfacing proprietary, closed architecture simulators. While there are numerous examples in the space of special purpose 2- to 3-simulator coordination solutions, a solution is desired with the generality of a DEVS or HLA class solution.

Hybrid languages also offer hybrid modeling and simulation, the most flexible of which is arguably SystemC-AMS [47]. However, no single hybrid modeling

environment, such as SystemC-AMS, Verilog-AMS, or VHDL-AMS [34] is sufficient to cover the range of CPS simulation, by virtue of the number of models (sometimes proprietary) that a CPS system must simulate, and the potential localization of domain expertise in established simulators. Another honored solution is the Ptolemy system [35], from the University of California at Berkeley. The Ptolemy system has been recognized for real-time embedded system design [1][3][40].

We seek, however, an interfacing based approach to CPS PADS, rather than uniform modeling or uniform simulator approach, mainly because practitioners in CPS simulation may not be able to remodel all desired components in a uniform modeling or single simulation environment. It is also impracticable to assume domain expertise in every domain of the CPS simulation on the part of the modeler or simulation integrator. Therefore, we select the approach of collecting existing and upcoming tools from multiple engineering simulation domains that best model components and systems in their domain expertise, and interfacing them. We call the effort of synchronizing and providing communication between different simulators the effort of "simulator coordination" for this work. The method we introduce compared to the DEVS or HLA RTI based coordination approach is a *dataflow based* approach. We apply the properties of a well-defined dataflow formalism, the Kahn Process Network (KPN) [29], to ensure scheduling and synchronization properties of simulator coordination, and we innovate on the data tokens of the KPN with a type called Interpolated Events (IEs) to provide the required time and causal fidelity of a PADS solution. This approach may lessen functional burdens where simulators are interfaced compared to existing solutions, while still providing model and simulator-independent generality.

### **1.3 Thesis Statement: The KPN-IE Method for PADS**

The Kahn Process Network (KPN) and Interpolated Event (IE) method of parallel and distributed simulation (PADS) offers conservative and optimistic coordination for multiple concurrent, distributed, and heterogeneous closed architecture simulators and can reduce time managing functional requirements for the coordination backplane and connected simulators compared to existing PADS solutions. A protocol based on KPN and IE facilitating PADS may reduce the time advancement and application layer messaging traffic to the coordination backplane. Additionally, an implementation based on KPN and IE based protocols may reduce the functional interfacing requirements and optimistic support requirements for federated simulators compared to the existing solutions.

### **1.4 Original Contributions**

In this thesis, original contributions are offered to the field of parallel and distributed simulation from the KPN-IE method. The contributions are described in the following categories.

#### **1.4.1 ORIGINAL CONTRIBUTIONS TO THE FIELD OF PADS**

- The Interpolated Event (IE) data type, which when forwarded according to the rules of Kahn Process Networks (KPNs), enables PADS with adherence to the local causality constraint, without logical process scheduling requirements

- The Interpolated Event Input Port and Interpolated Event Output Port plugin specification, which offers a lightweight interface for models and simulators to be coordinated, and enables a PADS model-level interface for closed architecture simulators

• An optimistic time management algorithm using the KPN-IE formalism that can reduce simulator interfacing and messaging requirements compared to existing solutions

### **1.4.2 ORIGINAL CONTRIBUTIONS THROUGH ENABLING TECHNOLOGIES**

- A simulation message protocol, "SimTalk," realizing the method of IEs, which captures, independently, in a dataflow network, the synchronization information necessary to coordinate the simulation, conservatively or optimistically

- A simulation backplane, "SimConnect," realizing the KPN formalism, which, when paired with the SimTalk protocol, may not incur the functional management requirements of existing interfacing-based solutions, but can still enable conservative and optimistic coordination of connected simulators

- A method using SimConnect and SimTalk to coordinate multiple Spice simulators without internal modification of the Spice kernel, with tradeoffs in simulation speed versus accuracy

#### **1.4.3 SIMCONNECT AND SIMTALK FEATURES**

- A lightweight solution for PADS coordination targeting the needs of cyberphysical system simulation

- A means to conduct conservative simulation without null message traffic overhead

- A means to offer optimistic simulation but with no additional functional requirements for simulators other than the ability to save a 1-deep history of simulator state. Anti-message queues and other Time Warp style overheads [65] are not imposed on the simulators.

- Reduction in backplane functional requirements for coordination, because SimConnect (SC) is not required compute the global Lower Bound Time Stamp (LBTS) for conservative synchronization or the Global Virtual Time (GVT) for optimistic simulation. This information is captured in the IE data streams, and bounds on it can be monitored with tracking counters.

- A means for dynamic resolution in the distributed simulation that can be controlled by any participating simulator, observer, or the coordinating backplane

- Well-defined, expressible trade-off equations between the speed of simulation and accuracy in terms of IE primitives

- Mathematical analysis on IE signaling information through zero-order hold interpolated events

### **1.5 Overview of the KPN-IE Method for CPS PADS**

#### **1.5.1 THE INTERFACING APPROACH**

CPS simulation can benefit from an interfacing approach instead of a unified modeling approach or uniform simulation environment. The interfacing approach allows CPS simulation to benefit from established and specialized models and simulators with closed architecture. This can reduce the modeling burden on CPS researchers, because they may not have to port strong existing models into a new language, model of computation, or simulation environment. Rather, models and environments are interfaced through the Interpolated Event Input and Output Port specifications introduced in Chapter Three. By taking the interfacing approach, the modeling capability of the KPN-IE method may increase on the cardinality of the power set of the set of all simulators for which Interpolated Event Input and Output Ports have been implemented.

#### **1.5.2 THE DATAFLOW APPROACH**

The KPN-IE method moves some of the coordination challenges of PADS into the dynamics of a KPN dataflow system, so that the simulation may be characterized by the interconnection dataflow. The KPN-IE approach is an observable, mathematically well-defined, distributable, and scalable data-flow network formalism that provides, through interpolated event data tokens, the synchronization and communication requirements of parallel and distributed CPS simulations. The capture, replay, and visibility of CPS system traffic in IE token format is convenient to a host of powerful software tools for analysis. The simulation can be completely characterized and evaluated in terms of events in the dataflow network and streams of interpolated events, rather than internal simulator events.

By design, the KPN-IE method achieves coordination and simulator advancement strictly through the KPN dataflow network and IE format, freeing the simulator coordination backplane from specific simulator object management and internal simulator time management. This can simplify the effort of implementing coordination software for a simulator.

#### **1.5.3 SIMPLIFIED INTERFACING**

A challenge of HLA RTI interfacing is that the RTI interface can be tightly coupled to the simulator internal kernel and time advancement. Simulator time advancement is managed explicitly by the external controlling software agent, the RTI. Because a simulator software layer may be proprietary, or of sufficient complexity that interfacing to an HLA RTI implementation through RTI and Federate Ambassadors (software interfaces) exceeds the budget of a researcher or the simulation vendor, the Interpolated Event Input and Output Port specification attempts to reduce the burden of simulator interfacing. By requiring only a user-level, device-model software interface from the simulator and the ability to include OS-level libraries and compile OS-level system calls for tasking and network communication primitives, the IE port specification can be adept from a software engineering perspective. Most simulators offer a user-level, device-model software interface as a service, allowing users to monitor simulator signals and time, assign signals in time, and schedule events, but without exposing internal proprietary simulator time management software or intellectual property.

#### **1.5.4 SIMPLIFIED MESSAGING**

The KPN-IE method combines synchronization and communication in the IE token format, potentially reducing the messaging burden for conservative and optimistic coordination. With the HLA RTI, in addition to implementing callback functionality for signal update messages, the simulator must implement the Time Advance Request function or its sibling functions [74], which are separate messaging calls to the HLA backplane from the object attribute update functions. For a simulator time advance cycle, many signal update callbacks may be issued in addition to the time advance messaging requests. In KPN-IE method, only the IE token format is used for signal and time information, which may reduce the backplane messaging traffic at the application level. This traffic does not include the messaging costs of carrier technology, such as TCP/IP, or MPI, or the link and physical layers to the backplane.

#### **1.5.5** ANALYSIS

KPN-IE offers a means for mathematical analysis of communication streams, because IEs are formally zero-order hold (ZOH) interpolators for continuous signals. This interpolation, along with the IE port specification, enables closed-form analytical expressions for tradeoffs in simulation resolution versus speed, and simulation resolution versus accuracy for classes of model conditions. These expressions are constructed in Chapter Three.

Another important benefit of the IE token and port specification is that bounds on important conservative and optimistic coordination variables, namely the conservative Lower Bound Time Stamp (LBTS) and optimistic Global Virtual Time (GVT) values, automatically fall out of maintaining the KPN dataflow dynamics in the KPN-IE coordinating backplane. Additional messaging or simulator blocking is not imposed on the system to calculate these values, nor imposed on the coordinating backplane in a complex algorithm. The KPN backplane, therefore, is primarily a token router, focused on managing KPN and IE dynamics.

#### **1.5.6 NON-EXCLUSIVITY**

Lastly, KPN-IE method does not exclude participation in an HLA, or other hybrid simulation suite such as SystemC-AMS, Verilog-AMS, Ptolemy, or DEVS, if interfacing connectors such as SimTalk plugins are written for simulation suites that offer OS-level software interfaces. The goal of the IE port specification and SimTalk protocol is to be sufficiently light weight to interface to different environments with a short learning curve required from the simulation integration engineer.

### **1.6 Organization of Thesis**

The organization of this work is as follows. Chapter Two covers primary material and concepts prerequisite to a discussion of PADS dynamics achieved through KPN-IE. The theory of modeling and simulation within the needs of CPS simulation is presented with no prior assumption of knowledge upon the reader. Important concepts and definitions that have persisted in PADS theory, composing a language for researchers in the field, are presented in preparation for the original work of Chapters Three and Four. Terms such as state transition systems, modeling and simulation, conservative and optimistic coordination, logical processes, and timed, discrete event models are covered.

Chapter Three introduces the theoretical contributions to PADS provided by the KPN-IE method. Interpolated Events are introduced and defined, including operations on Interpolated Events, and the Interpolated Event Input and Output Port specification for allowing models to interface at the model-definition layer. Next, a simulation time cost function is constructed in terms of IEs and IE ports, leading to expressions for simulation speed versus IE resolution. Expressions for simulation error in terms of IE resolution are also constructed.

In Chapter Four, Kahn Process Networks are introduced, with elaboration of their formal properties, and the dynamics of Kahn Process Networks with Interpolated Event data tokens are covered. An example of conservative coordination with the KPN-IE method is given step by step. Next, the ability of the KPN network to yield bounded tracking of the important Lower Bound Time Stamp (LBTS) and Global Virtual Time (GVT) values for optimistic and conservative simulator coordination is described. An optimistic coordination algorithm is offered, which can reduce the anti-message queue maintenance burden on IE port-conforming models compared to existing leading Time Warp-inspired solutions [36][65]. Finally, a combined conservative and optimistic coordination scheme is offered based on the ability of the KPN to track bounds on LBTS and GVT in the IE token streams in the KPN FIFOs.

In Chapter Five, the software implementation of the KPN-IE method through original tools SimConnect and SimTalk is presented with examples of synchronization, dynamic resolution management, and example simulation configurations. The architecture of the SimConnect KPN backplane is discussed, and the SimTalk KPN-IE messaging protocol is discussed. In Chapter Six, results from application of the KPN-IE method through SimConnect and SimTalk tools are covered for homogenous (many identical simulator) and heterogeneous (many different simulator) systems. The application of the KPN-IE method for parallel Spice circuit simulation at the model expression level is presented, offering a means of Spice acceleration by the coordination of many independent Spice simulators. Next, application of the KPN-IE method to simulate a software-managed, microcontroller PID/PWM based DC motor controller is presented. Tradeoffs in simulation resolution versus speed and accuracy are explored for both systems in each experiment.

Finally, in Chapter Seven, primary conclusions of the thesis are re-summarized, and areas of future work are offered based on new opportunities the KPN-IE method may offer to CPS simulation. A bibliography of important references in the field of CPS PADS is presented including peer-reviewed conference and journal articles generated by this work.

### CHAPTER TWO. THEORY OF MODELING AND SIMULATION

This work concerns the theory and practice of engineering simulation for cyberphysical systems (CPSs). Simulation can be defined as the practice of building one system to discover the properties of another system. Simulation endeavors to reveal properties of a system desired to be observed without actually having to build the final system, but rather by building a *similar* system with *similarly* observable properties. Recommended fundamentals of simulation theory and practice are [20] and [36].

Several needs motivate the simulation of cyber-physical systems. First, during the engineering design cycle, repeated physical prototypes of the cyber-physical system may be expensive to build. For example, a system may contain new computational system-on-chip designs, which are costly to manufacture for each new production mask. A system may contain complex mechanical systems with high manufacturing costs or scarce materials. A system may contain complex software, the cost of which, due to writing and testing, can postpone timely delivery of the system. In simulation, however, these prototyping costs can be reduced by building and testing a *similar* system rather than repeated iterations of the physical one.

In the extreme, building the physical side of the CPS target system may not be possible. For example, it may be desired to know the transient dynamics of an early warning CPS system, such as a hurricane or earthquake warning system, but some physical parts of those systems (like hurricanes and earthquakes) are not possible to build. We must rather wait for those systems to occur and study them, with potential hazards. A similar *model*, however, might be constructed of those systems to provide insight into their behavior without the hazard of their physical reality. This model may

be tested with a model of the computational side of the CPS in the safety of a simulated world.

Other important motivations for CPS simulation are discovery, testing, and validation. For discovery, a model of a physical process may be so complex that emergent properties are not easy to predict. It may be beneficial to discover unstable, emergent properties of a system in simulation before they happen in physical reality. Additionally, some mathematical models of physical processes have no analytical, closed-form solution, but can only be simulated with numerical differentiation and integration [77] to observe their trajectories, or observed in real life.

For testing and validation, it is desired to know whether the system will function to a measure of confidence. Design flaws are desired to be identified before the system is constructed, particularly if resources only allow the system to be constructed once, or only allow the system to be exercised once (such as with some space probes). If a simulation exposes design flaws, there is a chance to eliminate them before the final system is built. In some CPS systems, such as biomedical devices [43], design flaws may be fatally dangerous. Simulation enables early testing of the system to eliminate design flaws so they are not present in the final system.

In each of these categories of need for simulation, a *model* of the system is created. The goal of model is to describe the system components and their behavior. A model is exercised in another system called a simulator. Therefore, modeling and simulation are distinct, but cooperating endeavors. A model and simulator may share a common underlying model of computation, which enables the simulator to correctly instantiate the model dynamics. This relationship is called a homeomorphism between the model and simulator [20], provided through the model of computation.

Modeling and simulation always encounter tradeoffs in detail and accuracy. A model may or may not be able to describe all of the system dynamics, and a simulator may or may not be able to instantiate all elements in the model and all element transitions specified in the model. Because of the limitations of models and simulators, errors can be introduced, which can be described as differences between a modeled or simulated property of a system and its composition and behavior in physical reality. These errors may be within a tolerance or critically misleading. The presence of error in each stage of the definition of modeling and simulation will be tracked as we introduce terms and concepts. We begin with a discussion of models.

# 2.1 Modeling

#### **2.1.1 STATE TRANSITION SYSTEMS**

Modeling concerns the representation of elements and dynamics of a system. A starting point for models that evolve in some manner is the *state transition system* [68]-[72]. A state transition system is a pair  $(S, \rightarrow)$  where S is a set of states and  $\rightarrow \subseteq S \times S$  is a binary relation over S of transitions. If  $p, q \in S$ , then  $(p, q) \in \rightarrow$  is notated as  $p \rightarrow q$  and indicates there is a transition from state p to state q. State transition systems are a bridge from the domain of mathematics, where they are subclasses of "abstract rewriting systems," [68] to the realm of engineering, where they are a superclass for finite automata, labeled transition systems, and discrete event systems [68].

A transition system can be defined as a collection or set of elements (things to observe), with each element having a set of properties, or "states," assigned to it. The cardinality of the set of states S of elements in the system can be infinite, even uncountable (isomorphic to the set of real numbers), but for this work it will be finite. Let the system model be a set of elements E, and for each element e, let there be a set  $S_e$

of properties the element could obtain at any instance of observation. That is for each element  $e \in E$ , at any point of observation, there is a state  $s \in S_e$  given to the element.  $S_e$  could be the set of integers, reals, complex numbers, the set of colors, letters in the Latin alphabet, or a simple binary set  $\{0, 1\}$ . Specification of  $S_e$  is open to the modeler.

The set of states for a state transition system (denoted *S*) is defined as the set of all states the elements in the system may obtain. That is, at any one point of observation, the system state is represented by the tuple  $\{s_0, s_1, ..., s_n\}$ , where  $s_i \in S_i$  is the state of element *i* in the system, for all elements *n* in the system, for all set of states  $S_i$  associated with each element. If the system is dynamic or state changing, it may occupy different points, each represented a state tuple  $\{s_i\}$ , at any point of observation. The state transition model, or the relation  $\rightarrow \subseteq S \times S$ , specifies how the system evolves from one state tuple to the next, giving the system behavior.

#### **2.1.2 TIMED MODELS**

Subclasses of state transition system models and how they are simulated are numerous [71], but for this work a primary classifier of systems will be the system element of time. A *timed* state transition system contains a model of time as an element of the system. For this work, timed models are models for which the state transition function is primarily a function of time, but may also be a function of time and also other state variables. For this work, no transition in a timed model is specified without the element of time associated with the transition. *Untimed models,* conversely, are not required to associate a time with every state transition. Untimed modes are a rich and important field in modeling research [35], but because this work concerns cyber-physical systems, which are engineered systems that transition in time, we are interested in timed models. The simulation of timed models may be time driven or event driven.

#### **2.1.3 TIME DRIVEN MODELS**

Time driven models have transitions with time as a primary stimulus of each system state transition. The simulation of time driven models involves choosing a point in the model time, inputting that time to the system, and evaluating the state transition function as a result of the input. The simulation then advances time to the next time point and repeats the process. The system may produce outputs during this cycle. Time driven models can be simulated discretely in a digital computer by capturing the system state in variables, choosing a start value t for time, and then evaluating the state transition function STF(t) for some finite subset of the discretely modeled time. Because the evaluation of STF(t) is countable and finite in a digital system, the simulation of the model can incur discretization errors. Digital simulation only proceeds through a finite subset of the system state has finitely discretized element state.

### 2.1.4 EVENT DRIVEN MODELS

Event driven models are static until "something happens," that is, an event occurs [36]. The model receives notice of the event, and the transition function evaluates the new state as a function of the event. Event driven models may be discretely or continuously defined, but, like time driven models, their simulation is discrete in digital simulators. A timed, event driven model (TEDM) is one for which time is an element of the system state, and evolution of the system is specified in terms of events, not in terms of the advancement of time. Each event is associated with a point in time, since the model is timed, but simulation of the model involves creating an event e, and then evaluating the state transition function STF(e) as a function of the received event e. Background for event driven models and timed models is excellent in [36].

We can construct a classifier of models based on their representation of time and how they are simulated, whether time driven or event driven. Illustration 1 offers a quadrant based classifier, where each quadrant represents a grouping of models. We can populate this classifier with examples from engineering simulation. Register transfer level (RTL) simulations are discretely simulated, discrete time, event driven models and simulations, with examples from Verilog and VHDL-based simulators occupying points in the +X, +Y, +Z quadrant. Simulations on analog computers occupy points in the -X, -Y plane. While simulation by analog components such as operational amplifiers may, in fact, still occupy discrete states in space and time (a topic beyond this work), we say that they are continuously simulated (CS) because time is not discretized in the analog computer in the manner it must be in a digital computer. Spice-based [31] circuit simulations can occupy the +Y, -X, -Z quadrant. Their models are expressed in continuous time differential equations, but their simulation is discretely conducted by algebraic difference equations in a digital machine.

Time Driven (TD)

Illustration 1. Quadrant based categories of timed state transition systems

We are primarily concerned in cyber-physical systems with **timed**, **discrete time**, **discrete event**, **event driven** models. These are models conveniently simulated by a digital computer. As timed models, time is an element of the system state, but the advancement of the model is specified in terms of how the system reacts to events. A time change in the system without an event associated with it may be a modeled as a null event, so event driven models can capture a time driven simulation model of computation. The field of timed, event driven, discrete time modeling and simulation is rich [36], and we will continue to introduce terms, but we must account for categories of error early in the discussion.

#### 2.1.5 ERRORS IN MODELING

The definition of modeling with state transition systems introduces errors as we depart from a physical reality. These are errors of representation. First, we may not know all the elements in the system, or the set of elements specified the model may be less than the set of all elements exercised in the simulator. This is the **error of simplification**. It can arise because we may not chose to study or model every element in the system, or because the simulator can only instantiate a subset of elements of the system model. Next is the **error of assignment**. This is the error that the set of states assigned to elements in the model to an element may or may not represent completely or exactly the set of physical states the element may obtain. The states of an element specified in the model may be a subset, or simplification, of the states it may obtain. For example, a switching element of a model may have a property state of {on, off}, or {0, 1}. However, its electrical signal level in the physical system might be a larger set (a subset of the real numbers assigned to model voltage, for example). So we have encountered an error of assignment by abstracting the element state.

Along with the state set of elements in the system, the state transition function may have representational error. The error of simplification implies that the state transition function may not be defined (or known) for all points in the system state. For example, we may say a state transition function is continuously defined if one of the elements of the system has a state set equivalent to  $R^{l}$ , the set of real numbers, and that the state transition function is surjective for that element. A state transition function may be discretely defined if all of the state sets for each element in the system are countable (equivalent to a subset of Z), or if the transition function is only defined for countable subsets of the system state. However, although a continuously defined transition function may be defined in closed form, when the model is exercised in a digital simulator, it becomes necessarily discrete. Therefore, we commit an error of simplification in the state transition simulation, because we cannot model all of the states specified in the system state set and transition function. It is sometimes necessary to simplify a model because the number of states and system elements increase simulation time costs when the model is simulated. It costs memory to store the model states, and it costs computation time to evaluate the state transition function. For some models these costs can increase nonlinearly as the number of elements in the system increases.

### 2.2 Simulation

The act of simulation is to realize the behavior of a model by instantiating elements of the model in simulator resources and executing the model transition function in a selected model of computation offered by the simulator. Executing the model of computation in the simulator takes a model through a state trajectory to observe simulated system properties. Simulation can be conducted with analog or digital computers, but this work concerns digital simulation. Separating the act of modeling and the act of simulating allows separating the acts of verification and validation of the model and simulator [20]. Examining the model might ask if the right model is made, or if the errors of representation are tolerable. The art of simulating might ask if we are simulating the model correctly to its formalism within a tolerance of error [20][75].

The act of digital simulation is to realize a model and its transition function in a computationally realizable algorithm in a digital machine. The element properties are mapped to computer variable primitives and the transition function is mapped to instructions that the computer may execute on those variables. The act of simulation incurs the error of discretization. The error of discretization applies to both elements and the state transition function because the element property sets must be mapped to finite machine precision (encountering round-off error), and the state transition function must be mapped to finite machine arithmetic (encountering round-off and truncation errors) [76][77].

### 2.2.1 ACCOUNTING FOR TIME IN DIGITAL SIMULATION

Two expressions of time are frequently given when accounting for time in a simulation. The time to execute the simulation, called wall clock time, or  $\Delta T_{wall}$ , is the observed time elapsed for a simulation to start and stop as the observer experiences time. The simulation time, or  $\Delta T_{sim}$ , is the time in the simulation that the model completes during a segment of wall clock time. In similar language, adopting the definitions of [36] physical time refers to time in the "real life" system being modeled. Simulation time is an "abstraction used by the simulation to model physical time" [36]. Simulation time is an element of the system state for timed models. Wall clock time refers to time during the execution of the simulated program, the time we experience as the simulation proceeds.

A timed, event driven model advances  $\Delta T_{sim}$  by processing events. We can construct a real-time ratio,  $\frac{\Delta T_{wall}}{\Delta T_{sim}}$ , which quantifies how "quickly" a simulation advances. If  $\Delta T_{wall} \gg \Delta T_{sim}$ , the simulation can be said to be "slow." If  $\frac{\Delta T_{wall}}{\Delta T_{sim}} = 1$ , the simulation is said to be running in real-time, or processing events and advancing as fast as the physical system would in "real life." If  $\Delta T_{wall} \ll \Delta T_{sim}$ , the simulation is said to run "as-fast-as-possible," meaning the system simulation advances much more quickly than the physical system would, processing events as quickly as it can. If  $\Delta T_{wall} \ll \Delta T_{sim}$ and real-time simulation is desired,  $\Delta T_{sim}$  can be scaled to match wall clock time by connecting the rate of event processing with a local real-time clock [36].

For cyber-physical system simulation and engineering simulation, it is most often the case that  $\Delta T_{wall} \gg \Delta T_{sim}$ , due to complexity of state or compute time to evaluate the state transition function. Additionally, for CPS simulation in engineering product design, it is most often "as-fast-as-possible" simulation, rather than scaled real-time simulation, which proceeds at the same rate as wall clock time. Also, CPS simulation experiences a challenge in the difference in frequency of circuit level events that must be modeled versus software-level events, which might occur several orders of magnitude less frequently. Yet, both of these resolutions must be simulated with correct causal interaction with circuit-level and physical effects to reliably observe the system as it would behave if constructed.

#### 2.2.2 SIMULATING TIMED, EVENT DRIVEN MODELS

#### Equivocating Time Driven and Event Driven Models

The simulation of time driven, discrete time models can be mapped to the simulation of event driven models if a change in simulation time is considered an event from the event driven viewpoint. In this mapping, the simulation chooses a countable,

finite subset of time (time points) to evaluate the state transition function, and then evaluates the system at those points. This is equivalent to making time an internal event queue, where the contents of the event queue are simulated time points when the simulation chooses to evaluate the state transition function STF(t). This mapping is important, because it can focus our view, without loss of generality, to event driven, discrete event simulation.

#### Discrete Time, Discrete Event Simulation

The timed, discrete event model (TDEM) is central to this work. Two prominent examples of TDEMs are "Logical Processes" [36] and the Discrete Event System Specification (DEVS) formalism [20]. We examine each in turn. First, we must define model inputs and outputs.

An input to a discrete event model is an event not generated internally by the model. An input is applied from sources "external" to the model. The input is applied through an input port, an abstract means to collect information into the model from sources not a part of the model set of elements.

An output is an event that can be generated as a function of the model's state and/or inputs. An output event may be fed back into the model through an input port for feedback. For these definitions, an output is considered to be an event that is sent "outside" of the model to another consumer.

A timed event, as described by [35], is a tuple (v, t), a value v and a tag t, taken from the product set  $V \ge T$ , where V is a set of values and T is a set of tags. Timed, event driven models advance in simulated time by processing timed events, whether generated internally in the model from its state transition function or supplied externally to the model through input ports.

### Logical Processes

The Logical Processes viewpoint, covered by Richard Fujimoto in [36], points to a legacy of insights and techniques that influenced the IEEE 1516 High Level Architecture (HLA) standard [19] for distributed simulation coordination. Logical processes are event-driven processes with the following elements and definitions.

**System state variables** are elements "describing the state of the system" [36]. These are precisely the system elements and their properties defined in state transition systems. An **event list** contains events that are to occur at a "time in the simulated future" of the system [36]. An event list is a list of timed events ordered on *T*, the set of tags representing modeled time. A **local clock** denotes "the instant on the simulation time axis at which the simulation now resides" [36].

The simulation cycle of the sequential, discrete event Logical Process can be expressed as follows. While the simulation is in progress, remove the smallest time stamped event from the event list. Set the simulation clock to the time stamp of this event. Then execute all event handlers in the application to process the event [36].

The transition function consists of the actions of all the event handlers in the system model. Executing the event handlers moves the system from one point state to another and may add more events (internal events) to the event queue in the process. The state transition function for the Logical Process is therefore a function of S (the system state), E (the set of possible events), and T (the set of local time points).

### The DEVS Formalism

The Discrete Event System (DEVS) formalism, attributed to Bernard Ziegler [20], is a set theoretic formal system. It attempts to classify and describe a model in terms of a DEVS set theoretic formalism, and then describe the concurrent simulation and composition of these models through formal interfaces. DEVS has a rich legacy dating to 1976 [20][21], and offers a means to separate the problems of verifying models and validating the correct simulation of models. The formalism has evolved in the PADS literature over the past three decades and is still actively researched [21][51][59][66].

### Subtleties between LP and DEVS

The original atomic DEVS and Logical Process models encounter the challenge of simultaneous events, described as "events with the same time stamps" [36]. If a model receives two events of different values, but each with the same time stamp, which event shall the model process first? It turns out the correctness of the model can depend on the order in which the model processes the two events. Both system descriptions have been adapted in definition to handle simultaneous events.

Simultaneous events raise a challenge regarding event causality based on time stamps alone. A strongly causal system is said to have outputs that are strictly a function of present and past state and previous inputs. A weakly causal system has outputs that are a function of present and past state and present inputs. When simulating cycles of weakly causal systems, the simulation may depend on the order that events are received, even if they have the same time stamp. The receive order of simultaneous events may then not be repeatable over some networks from one run of the simulation to the next. Methods, such as extra lower precision bits added to event time stamps to differentiate between simultaneous events are offered in [36] and [51]. Another approach is to let the receiver decide between simultaneous events based on an internal priority [36]. A unified approach to DEVS and Logical Processes, offered by Nutaro [51], adds measures for simultaneity and causality in cycles of weakly causal processes.

#### 2.2.3 DISTRIBUTED, PARALLEL, TIMED, DISCRETE EVENT MODELS

**Distributed** simulation means that the system simulation processes potentially run on spatially separate machines. Distributed simulation requires a means for processes to communicate events that they produce for each other. **Parallel** simulation means that the processes potentially execute concurrently. Parallel simulation requires a means to synchronize timed models so that processes receive and process timed events "when they are supposed to." That is, causality of events must be no different in parallel simulation compared to the causality of events in the same system simulated sequentially. Therefore, parallel and distributed simulation requires both communication and synchronization, terms this work combines together in the word "coordination."

Several needs motivate the creation and coordination of distributed and parallel TDEM process rather than sequential simulation of them over fast machines. First, the wall clock cost of simulating the state transition function STF(e) for event *e* may grow exponentially as the cardinality of *S*, the set of system states, increases for a model. This is an issue for models such electrical circuit models where the number of nodes or transistors in a system is large, as it is for VLSI systems. The reduction of STF(e) so that more elements of state may be simulated is a strong motivator for parallel and distributed simulation if STF(e) reduces for some domain over the set of parallel simulators.

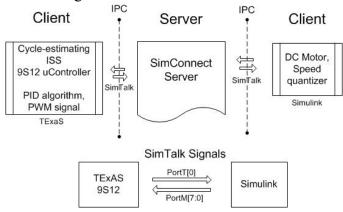

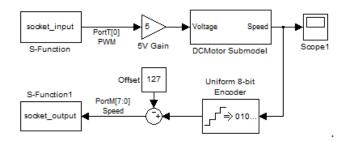

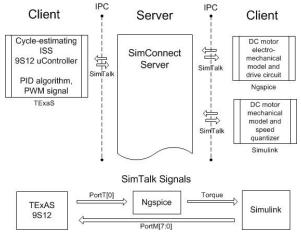

Another motivation is model complexity. The system state S may be of such complexity that domain experts must define elements and properties, but cannot define all of them. For this reason, a model may be partitioned into domain groupings. The simulation of those models may only be available on proprietary simulators or only in a limited number or difficult to write from scratch simulation packages. Modelers may wish to focus on some elements of S and not burden themselves with other elements of S.