Copyright by Gokhan Sayilar 2014 The Thesis Committee for Gokhan Sayilar Certifies that this is the approved version of the following thesis:

# Cryptoraptor: High Throughput Reconfigurable Cryptographic Processor for Symmetric Key Encryption and Cryptographic Hash Functions

APPROVED BY

SUPERVISING COMMITTEE:

Derek Chiou, Supervisor

Mohit Tiwari

# Cryptoraptor: High Throughput Reconfigurable Cryptographic Processor for Symmetric Key Encryption and Cryptographic Hash Functions

by

Gokhan Sayilar, B.S.

#### THESIS

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### MASTER OF SCIENCE IN ENGINEERING

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2014

To my family and many friends...

## Acknowledgments

A major research project like this is never the work of anyone alone. I would like to extend my appreciation especially to the following.

First and foremost I offer my sincerest gratitude to my supervisor, Dr. Derek Chiou, for his excellent guidance, caring, and patience. I would also like to thank him for being an open person to ideas, encouraging and helping me to shape my interest and ideas, and giving me the freedom to work in my own way. He's the funniest advisor and one of the smartest people I know.

Besides my advisor, I would like to thank to my second reader, Dr. Mohit Tiwari, for his advises and insightful comments.

I am also thankful to my friends in US, Turkey, and other parts of the World for being sources of laughter, joy, and support.

Last but not least, I would like to thank my parents and my brother for their continuous love and unconditional support in any decision that I make.

I also want to thank to Semiconductor Research Corporation and Freescale Semiconductor, Inc for their financial support which allowed me to undertake this research

For any errors or inadequacies that may remain in this work, of course, the responsibility is entirely my own.

# Cryptoraptor: High Throughput Reconfigurable Cryptographic Processor for Symmetric Key Encryption and Cryptographic Hash Functions

Gokhan Sayilar, M.S.E The University of Texas at Austin, 2014

Supervisor: Derek Chiou

In cryptographic processor design, the selection of functional primitives and connection structures between these primitives are extremely crucial to maximize throughput and flexibility. Hence, detailed analysis on the specifications and requirements of existing crypto-systems plays a crucial role in cryptographic processor design. This thesis provides the most comprehensive literature review that we are aware of on the widest range of existing cryptographic algorithms, their specifications, requirements, and hardware structures. In the light of this analysis, it also describes a high performance, low power, and highly flexible cryptographic processor, Cryptoraptor, that is designed to support both today's and tomorrow's encryption standards. To the best of our knowledge, the proposed cryptographic processor supports the widest range of cryptographic algorithms compared to other solutions in the literature and is the only crypto-specific processor targeting the future standards as well. Unlike previous work, we aim for maximum throughput for all known encryption standards, and to support future standards as well. Our 1GHz design achieves a peak throughput of 128Gbps for AES-128 which is competitive with ASIC designs and has 25X and 160X higher throughput per area than CPU and GPU solutions, respectively.

# Table of Contents

| Acknowledgments                                                                                            | V    |

|------------------------------------------------------------------------------------------------------------|------|

| Abstract                                                                                                   | vi   |

| List of Tables                                                                                             | xi   |

| List of Figures                                                                                            | xiii |

| Chapter 1. Introduction and Motivation                                                                     | 1    |

| 1.1 Introduction $\ldots$ | . 1  |

| 1.2 Our Contributions                                                                                      | . 4  |

| 1.3 Thesis Outline                                                                                         | . 5  |

| Chapter 2. Related Work                                                                                    | 7    |

| 2.1 Instruction Set Architecture Extensions                                                                | . 8  |

| 2.2 Algorithm Specific Hardware                                                                            | . 10 |

| 2.3 Domain Independent Configurable Processors                                                             | . 11 |

| 2.4 Configurable Cryptographic Processors                                                                  | . 13 |

| Chapter 3. Cryptographic Algorithm Analysis                                                                | 17   |

| 3.1 Existing Workload Characterizations                                                                    | . 17 |

| 3.2 Algorithm Selection                                                                                    | . 19 |

| 3.3 Analysis Methodology                                                                                   | . 23 |

| 3.4 Detailed Analysis                                                                                      | . 24 |

| 3.4.1 Operation Classes                                                                                    | . 24 |

| 3.4.2 Table Lookup Structure                                                                               | . 28 |

| 3.4.3 Bundled Operation Patterns                                                                           | . 31 |

| 3.4.4 Special Functional Units                                                                             | . 33 |

| 3.4.5 Processing Element Width                                                                             | . 37 |

|            | 3.4.6                                                           | Connection Structures                                                                                                                    | 39 |

|------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | 3.4.7                                                           | Storage Requirements                                                                                                                     | 41 |

| Chapter 4. |                                                                 | Cryptographic Algorithm Instrumentation 4                                                                                                | 43 |

| 4.1        | 4.1 Existing Binary Instrumentation of Cryptographic Algorithms |                                                                                                                                          |    |

| 4.2        | Instrumentation Methodology                                     |                                                                                                                                          |    |

| 4.3        | 4.3 Detailed Analysis                                           |                                                                                                                                          |    |

| Chapt      | er 5.                                                           | Cryptoraptor: Reconfigurable Cryptographic Pro-<br>cessor                                                                                | 51 |

| 5.1        | Desig                                                           | gn Methodology                                                                                                                           | 51 |

| 5.2        | Crypt                                                           | $toraptor \ldots \ldots$ | 53 |

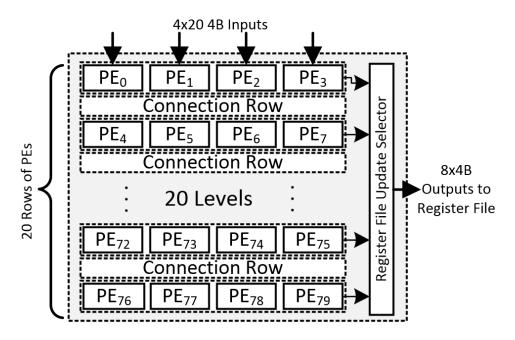

| 5.3        | Execu                                                           | ution Tile                                                                                                                               | 54 |

| 5.4        | Conn                                                            | ection Row                                                                                                                               | 56 |

| 5.5        |                                                                 |                                                                                                                                          |    |

| 5.6        | Proce                                                           | essing Element                                                                                                                           | 60 |

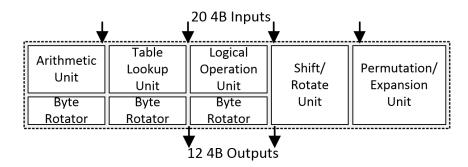

| 5.7        | Funct                                                           | tional Units                                                                                                                             | 64 |

|            | 5.7.1                                                           | Logical Operation Unit (LOU)                                                                                                             | 64 |

|            | 5.7.2                                                           | Table Lookup Unit (TLU)                                                                                                                  | 67 |

|            | 5.7.3                                                           | Arithmetic Unit (AU)                                                                                                                     | 69 |

|            | 5.7.4                                                           | Permutation/Expansion Unit (PEU)                                                                                                         | 71 |

|            | 5.7.5                                                           | Shifter/Rotator Unit (SRU)                                                                                                               | 72 |

| Chapt      | er 6.                                                           | Processor Analysis 7                                                                                                                     | 75 |

| 6.1        | Imple                                                           | $ementation \dots \dots$           | 75 |

| 6.2        | Timir                                                           | ng Analysis                                                                                                                              | 77 |

| 6.3        | Area                                                            | Analysis                                                                                                                                 | 79 |

| 6.4        |                                                                 |                                                                                                                                          | 82 |

| 6.5        |                                                                 |                                                                                                                                          | 86 |

| 6.6        | Resou                                                           | urce Utilization                                                                                                                         | 93 |

| 6.7        |                                                                 |                                                                                                                                          | 95 |

| 6.8        | Limit                                                           | $tations \ldots $               | 97 |

| Chapter 7.                | Cryptographic Algorithm Mapping                                                                                | 100 |

|---------------------------|----------------------------------------------------------------------------------------------------------------|-----|

| 7.1 Block                 | $\mathbf{x}$ Ciphers $\ldots$ | 103 |

| 7.1.1                     | Advanced Encryption Standard (AES)                                                                             | 104 |

| 7.1.2                     | Blowfish                                                                                                       | 107 |

| 7.1.3                     | Camellia                                                                                                       | 109 |

| 7.1.4                     | CAST-128                                                                                                       | 112 |

| 7.1.5                     | Data Encryption Standard (DES)                                                                                 | 115 |

| 7.1.6                     | GOST                                                                                                           | 118 |

| 7.1.7                     | Kasumi                                                                                                         | 119 |

| 7.1.8                     | Rivest Cipher 5 (RC5) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                           | 122 |

| 7.1.9                     | SEED                                                                                                           | 124 |

| 7.1.10                    | ) Twofish                                                                                                      | 126 |

| 7.2 Strea                 | m Ciphers $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                              | 129 |

| 7.2.1                     | Rivest Cipher 4 (RC4) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                           | 129 |

| 7.2.2                     | Phelix                                                                                                         | 131 |

| 7.3 Cryp                  | tographic Hash Functions                                                                                       | 133 |

| 7.3.1                     | Message Digest Algorithm-4 (MD4)                                                                               | 134 |

| 7.3.2                     | Message Digest Algorithm-5 (MD5)                                                                               | 136 |

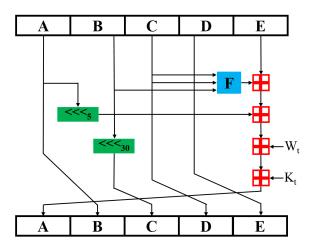

| 7.3.3                     | Secure Hash Algorithm-1 (SHA1)                                                                                 | 138 |

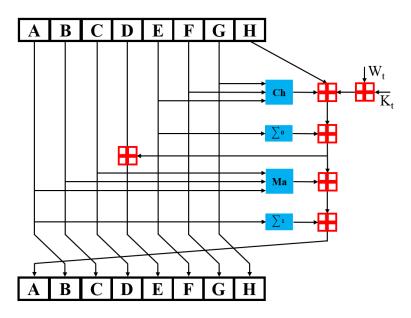

| 7.3.4                     | Secure Hash Algorithm-2 (SHA2)                                                                                 | 139 |

| Chapter 8. Future Work 14 |                                                                                                                |     |

| Chapter 9.                | Conclusion                                                                                                     | 145 |

| Appendices                |                                                                                                                | 147 |

| Appendix A                | . Detailed Operation Classes Usage                                                                             | 148 |

| Appendix E                | 8. Operation Clusters                                                                                          | 153 |

| Appendix C                | 2. Operation Bundles                                                                                           | 155 |

| Appendix I                | 0. Detailed Processing Element Width Usage                                                                     | 157 |

| Bibliograph               | У                                                                                                              | 159 |

# List of Tables

| 3.1  | The distribution number of parallel lookup operation in cryptographic algorithms             |

|------|----------------------------------------------------------------------------------------------|

| 3.2  | The distribution of XOR and SBOX patterns in cryptographic algorithms                        |

| 3.3  | The distribution of Shift/rotate and logic operation patterns in cryptographic algorithms    |

| 3.4  | The distribution of XOR and Arithmetic operation patterns in cryptographic algorithms        |

| 3.5  | The special functional unit requirements in cryptographic algorithms                         |

| 3.6  | The modular arithmetic base distribution in cryptographic al-<br>gorithms                    |

| 4.1  | Instruction Classes                                                                          |

| 4.2  | Instruction Class Frequencies                                                                |

| 4.3  | Operation Class Frequencies                                                                  |

| 4.4  | Distribution of Memory Accesses                                                              |

| 4.5  | Distribution of Data Read/Write Granularities                                                |

| 5.1  | The control structure of one PE connector                                                    |

| 5.2  | The input selection structure of PE connector (least significant 4 bits of 6 selection bits) |

| 5.3  | The input structure of PE                                                                    |

| 5.4  | The output structure of PE                                                                   |

| 5.5  | The control signal structure of PE                                                           |

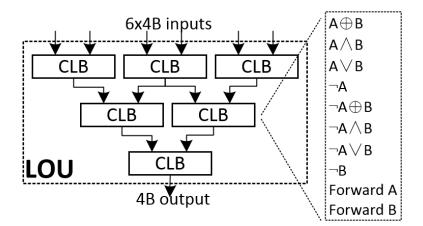

| 5.6  | The Configurable Logic Block functionality                                                   |

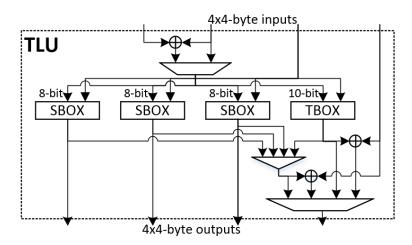

| 5.7  | The Table Lookup Unit functionality                                                          |

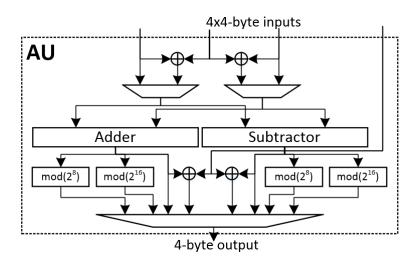

| 5.8  | The Arithmetic Unit functionality                                                            |

| 5.9  | The Bit Selector control structure                                                           |

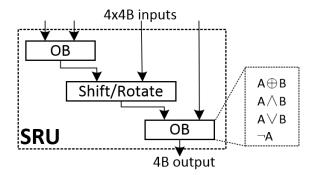

| 5.10 | The Shifter/Rotator Unit functionality                                                       |

| 5.11 | The Operation Block functionality                                       | 74  |

|------|-------------------------------------------------------------------------|-----|

| 6.1  | The cycle time of functional units in PE                                | 77  |

| 6.2  | The cycle time comparison of functional units with bundles              | 78  |

| 6.3  | The cycle time of sub-modules in Cryptoraptor                           | 79  |

| 6.4  | The area comparison between Design Compiler and CACTI .                 | 80  |

| 6.5  | The area of functional units in PE                                      | 80  |

| 6.6  | The area comparison of functional units with bundles $\ldots$ .         | 81  |

| 6.7  | The area of sub-modules in Cryptoraptor                                 | 81  |

| 6.8  | The power usage comparison for memory blocks                            | 82  |

| 6.9  | The power usage of functional units in PE $\ldots$                      | 83  |

| 6.10 | The power usage comparison of functional units with bundles .           | 84  |

| 6.11 | The power usage of modules in Cryptoraptor                              | 84  |

| 6.12 | Power usage comparison of GPPs                                          | 85  |

| 6.13 | AES Performance comparison of ASIC solutions                            | 88  |

| 6.14 | AES Performance comparison of FPGA solutions                            | 90  |

| 6.15 | AES Performance comparison of GPP solutions                             | 91  |

| 6.16 | Performance summary of algorithms on Cryptoraptor                       | 92  |

| 6.17 | Resource utilization summary of mapped algorithms on Cryptoraptor       | 94  |

| 6.18 | Resource utilization summary of mapped algorithms on Cryptoraptor       | 94  |

| 6.19 | The current coverage of cryptographic algorithms $\ldots \ldots \ldots$ | 96  |

| 7.1  | Algorithm summary and selection for mapping process                     | 101 |

| 7.2  | Instruction List                                                        | 102 |

| A.1  | The special functional unit requirements in cryptographic algorithms    | 148 |

| B.1  | Operation clusters and patterns                                         | 153 |

| C.1  | Operation patterns                                                      | 155 |

| D.1  | Operation width (PE way)                                                | 157 |

# List of Figures

| 2.1 | The distribution of energy dissipation in an in-order RISC processor [92]                    | 12  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 3.1 | The use of operation classes in cryptographic algorithm classes                              | 25  |

| 3.2 | The ratio of different table sizes used in cryptographic algorithms                          | 29  |

| 3.3 | The ratio of different table entry widths used in cryptographic algorithms                   | 30  |

| 3.4 | The distribution of logical operation patterns in cryptographic algorithms                   | 32  |

| 3.5 | The coverage ratio of algorithms that require modular arithmetic                             | 37  |

| 3.6 | The distribution of algorithms requires 1, 2, 4, 8 and 16-way processing elements            | 38  |

| 3.7 | The trend of connection structure among processing elements used for implementing algorithms | 40  |

| 4.1 | Instruction and Operation Class Distribution                                                 | 48  |

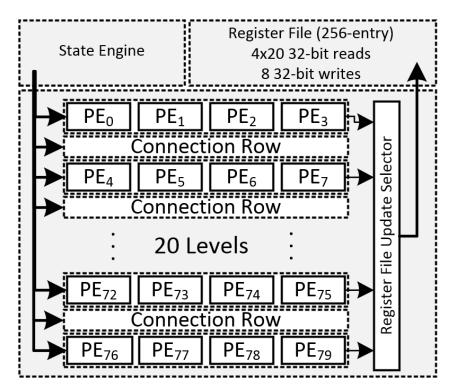

| 5.1 | The internal structure of Cryptoraptor                                                       | 53  |

| 5.2 | The high level structure of Execution Tile                                                   | 55  |

| 5.3 | High level unit structure of a Processing Element                                            | 60  |

| 5.4 | The internal structure of LOU                                                                | 65  |

| 5.5 | The internal structure of TLU                                                                | 67  |

| 5.6 | The internal structure of AU                                                                 | 69  |

| 5.7 | The internal structure of SRU                                                                | 73  |

| 6.1 | The utilization summary                                                                      | 95  |

| 6.2 | The distribution of supported and non-supported algorithms based on limitations              | 97  |

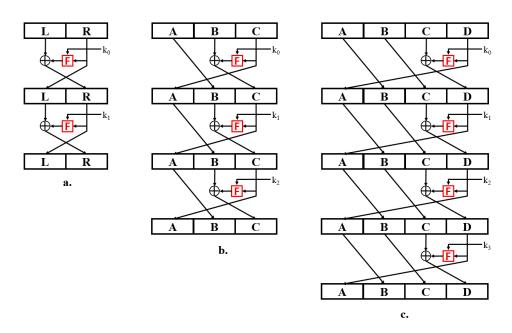

| 7.1 | The overall structure of Feistel network and its derivations                                 | 104 |

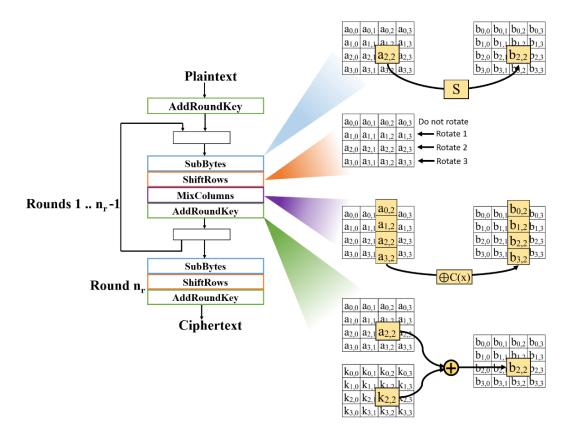

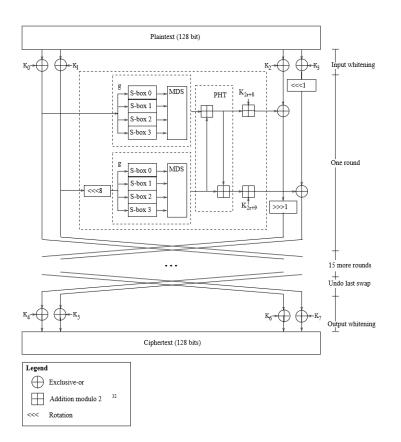

| 7.2 | The traditional structure of AES                                                             | 105 |

| 7.3  | The round function of Blowfish                                                            | 108 |

|------|-------------------------------------------------------------------------------------------|-----|

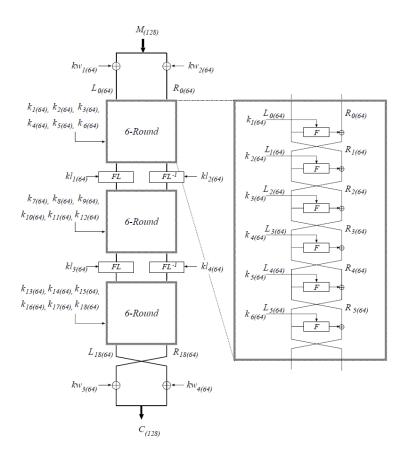

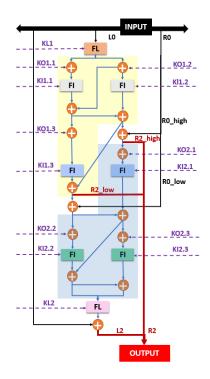

| 7.4  | The high level structure of Camellia                                                      | 110 |

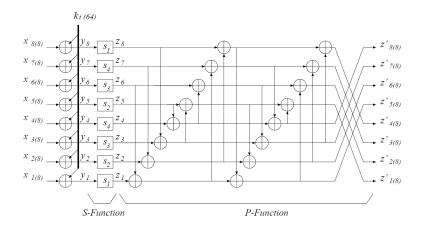

| 7.5  | The internal structure of one Camellia round                                              | 111 |

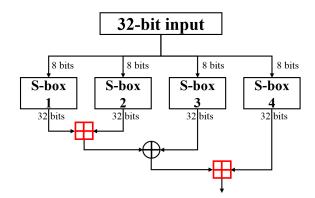

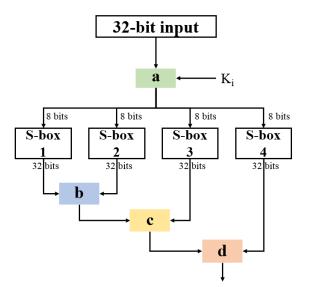

| 7.6  | The round function template for CAST-128                                                  | 113 |

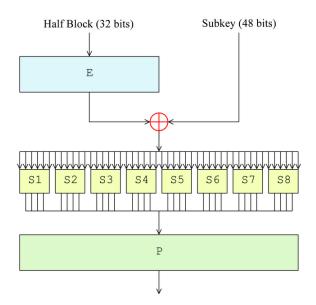

| 7.7  | The round function f of DES                                                               | 116 |

| 7.8  | The overall structure of GOST block cipher                                                | 118 |

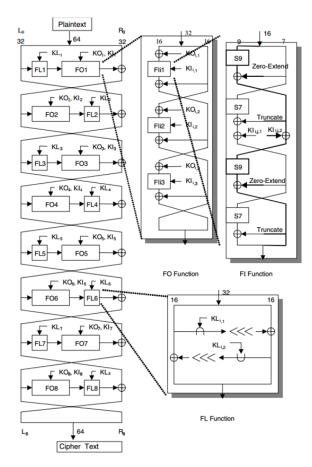

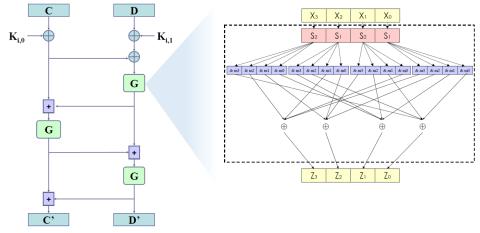

| 7.9  | The traditional structure of Kasumi                                                       | 120 |

| 7.10 | Merging one odd and one even round of Kasumi as one big<br>operation block                | 121 |

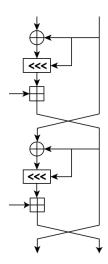

| 7.11 | Two half rounds (one round) of RC5 $\ldots$                                               | 123 |

| 7.12 | The round structure of SEED block cipher                                                  | 125 |

| 7.13 | The overall structure of Twofish block cipher                                             | 127 |

| 7.14 | One block of Phelix encryption                                                            | 132 |

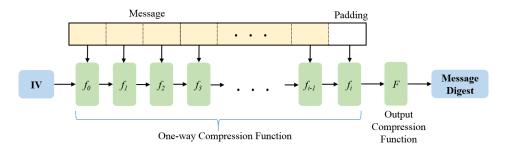

| 7.15 | The high level structure of the Merkle-Damgard construction .                             | 133 |

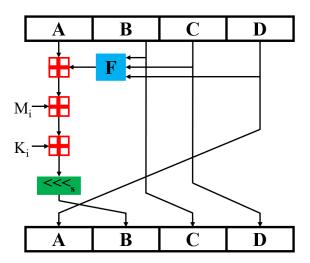

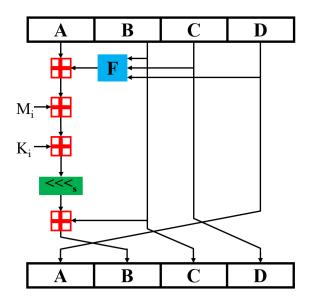

| 7.16 | The round structure of MD4 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 134 |

| 7.17 | The structure of one MD5 operation $\ldots \ldots \ldots \ldots \ldots \ldots$            | 136 |

| 7.18 | The round structure of SHA-1                                                              | 138 |

| 7.19 | The round structure of SHA-2                                                              | 140 |

## Chapter 1

## Introduction and Motivation

### 1.1 Introduction

As the demand for secure communication bandwidth is growing at an unprecedented pace, efficient and high throughput cryptographic processing becomes increasingly critical for overall system performance. Besides high performance computing, the flexibility also becomes an essential feature of cryptographic processors because of the numerous cryptographic algorithms and security standards. New cryptographic algorithms are continuously being developed, which makes existing hardware inadequate to satisfy new requirements. Thus, it becomes more desirable for cryptographic processors to support existing crypto-systems as well as having the potential to support future standards.

To be to cover all cryptography domain, one must understand the whole domain and existing requirements first. In current cryptography standards, there are three types of algorithms: (i) symmetric-key encryption and (ii) cryptographic hash functions, and (iii) public-key encryption.

a. Symmetric-key encryption: Symmetric-key encryption refers to a class of cryptography algorithms where a sequence of operations is repeatedly applied to the blocks of data using a single shared key to encrypt and decrypt. Since both parties have to share and use a single "secret" or "key" for encryption and decryption, symmetric-key encryption is also known as "shared key encryption" or "private key encryption". Symmetric-key encryption algorithms exist as block and stream ciphers. While block ciphers tend to be used for higher security, stream ciphers are known to be fast, secure enough, easier to implement, and requires less processing power. Advanced Encryption Standard (AES) [58], and Rivest Cipher 4 (RC4) [213] are often used examples of this algorithm class.

- b. Cryptographic hash functions: Cryptographic hash functions refer to a class of irreversible one-way functions that take an arbitrary length message and generate a fixed-size bit sequence, message digest. Cryptographic hash functions are widely used in the form of authentication such as digital signatures and message authentication codes. Secure Hash Algorithm-1 (SHA1) [74] and Secure Hash Algorithm-2 (SHA2) [74] are widely used examples of this class.

- c. Public-key encryption: Public-key encryption is a class of cryptography algorithms that requires a pair of keys; one public and one private for each user. The private key is always in the possession of the owner, while public key is sent along with the message or publicly available. Even though the public and private keys are entirely different, they are mathematically linked to each other as specified in the algorithm. Since

the keys are used for performing opposite operations, public-key encryption is also known as "asymmetric cryptography". The security of a public key encryption depends on the computational infeasibility of the algorithm which generally involves (i) computing the factors of a gigantic number (300 decimal digits or more) that is the product of two large prime numbers or (ii) exponentiation of a significantly large number over a significantly large another number in modulo p where p is a large prime. The widely known public-key encryption algorithms are Diffie-Hellman key exchange [98] and RSA [112].

While symmetric-key encryption algorithms and hash functions mostly rely on primitive logical and arithmetic operations that can be computed efficiently, modular exponentiation and modular multiplication are the most frequent operations in public-key encryption. Public-key encryption tends to be very slow and resource intensive. They require special hardware support for high performance since they have to deal with very large numbers (up to 2048 bits). Public-key encryption algorithms are relatively computationally expensive compared to the most, if not all, symmetric-key encryption algorithms and cryptographic hash functions; therefore, they are expensive in terms of time, area, and power.

In this project, our studies and the proposed cryptographic processor focus on symmetric-key encryption algorithms and cryptographic hash functions only since they rely on common structures and completely different computational primitives than public-key cryptography. Thus, public-key encryption is currently beyond the scope of this work.

### **1.2** Our Contributions

New cryptography standards and fast implementation of existing ones are continuously being developed. Implementations are ranging from applicationspecific integrated circuits (ASICs), which are fast but inflexible, to general purpose processor (GPP) based software, which are flexible, but slow. In this thesis, we address the problem of having highly flexible and yet high performance cryptographic processor.

To design a high performance configurable crypto processor, one must first understand which functionalities must be implemented by that processor in order to support current cryptographic algorithms while providing the capability of implementing future algorithms as required.

Our first contribution is the comprehensive literature review on cryptographic algorithms and the detailed analysis on the specifications and requirements of various crypto-systems. To the best of our knowledge, our algorithm analysis of 148 existing symmetric-key encryption algorithms and hash functions is the first and only work that provides comprehensive information about the algorithms and hardware structures that can efficiently implement them. During our study, we focused on the architectural structure of cryptographic algorithms to bridge the gap between hardware designers and cryptographic algorithm developers. Even though each algorithm has different structures and characteristics, we focused both on finding common patterns and characteristics, as well as the features that differ between algorithms. Unlike other research projects that focus on a limited set of currently popular algorithms, our analysis relies on a wide range of cryptographic algorithms.

As the second and main contribution, we propose a high performance and highly flexible cryptographic processor based on our analysis. It supports a wide range of existing ciphers and cryptographic hash functions and has high potential to support future algorithms. The proposed architecture with its reconfigurable substrate provides a high degree of flexibility even when implemented in an ASIC. Besides its flexibility, our design operating at 1GHzachieves a peak throughput of 128Gbps on CTR AES-128 encryption which is highly competitive with fully-optimized AES cores described in the literature.

Lastly, we provide a detailed timing, power, and area analysis on functional primitives of cryptographic algorithms and our processor. We believe that such analysis combined with our comprehensive literature survey on symmetric-key encryption algorithms and hash functions would help both cryptographic algorithm developers and hardware designers to evaluate design trade-offs during the design and implementation.

#### **1.3** Thesis Outline

The rest of this thesis is organized as follows. In chapter 2, we briefly describe related research projects and other solutions found in the literature. The chapter 3 and 4 present our detailed analysis on existing cryptographic

algorithms. The specifications and design rationales of our proposed cryptographic processor are given in chapter 5. In chapter 6, we provide detailed analysis of our processor in terms of performance, timing, area, power, and algorithm coverage. The chapter 7 provides brief description about a subset of algorithms and explains how these algorithms are mapped onto our processor. Finally, we discuss possible future research questions and extensions to the proposed processor in chapter 8 and 9.

## Chapter 2

## **Related Work**

Once a cryptographic algorithm is designed, it is relatively straightforward to implement that algorithm in software to run on a general purpose processor (GPP). Such an implementation, however, may not provide the desired performance at the desired power and computing resources. For example, encrypting 10Gb/s of data using an Intel processor with AES instructions today takes roughly one processing core, which may not be acceptable.

To drastically reduce or eliminate the processing overhead from the GPP, one could implement encryption algorithms in a hard-wired applicationspecific integrated circuit (ASIC). Doing so potentially offers the highest performance at the lowest power, but requires hardware design that is expensive and the final product is inflexible. If the ASIC does not support any of the currently used algorithms, it is worthless and would have to be replaced, at potentially great cost and effort. Even if a subset of the algorithms supported is not used, there is wasted silicon and the effort; therefore, the cost to build and deploy that ASIC may not be worthwhile. Moreover, changing standards and algorithms could make ASIC partially or entirely useless. Thus, the inflexibility of ASIC solutions is a significant negative. To eliminate the inflexibility, one could implement encryption algorithms in hardware structures in a field programmable gate array (FPGA) that can be reprogrammed at will. FP-GAs, however, are expensive and, at least currently, roughly the same level of difficulty to program as an ASIC (though much simpler to delay).

Another alternative is to design a special purpose programmable processor that is optimized to execute cryptographic algorithms. Due to their flexibility and high throughput, reconfigurable cryptographic processors are promising alternatives for the implementation of cryptographic algorithms. Therefore, developing a hardware architecture that provides efficient and high throughput implementations for crypto-systems has become increasingly important.

#### 2.1 Instruction Set Architecture Extensions

The first category that tries to achieve high throughput on cryptographic applications is ISA extensions (ISEs) which are new instructions introduced to support one or more cryptographic algorithms. Intel added six SSE instructions and hardware support in their new generation CPUs to speed up AES [4]. Even though the proposed pipeline and new instructions help to achieve high performance by having the round latency of six cycles for one stream in serial mode, they are useful to accelerate AES only. IBM and Oracle also introduced new cryptographic instructions and hardware support in their high-end processors. IBM provided a crypto engine in IBM PowerEN<sup>TM</sup> Processor Chip [40] to accelerate a predefined set of crypto-systems: AES, ARC4, DES, Kasumi, MD5, SHA-1, and SHA-2. Likewise, Oracle followed the same strategy in the Sparc T4 Chip [84] to support a similar set of algorithms: AES, DES, Kasumi, Camellia, MD5, SHA-1, and SHA-2. Both IBM and Oracle designs consist of algorithm-specific instructions and dedicated hardware units for each algorithm, which restricts their flexibility and prevents them from supporting other existing and future algorithms.

There are several research projects [25, 44, 67, 110, 129, 193, 221] that propose new instruction extensions to existing ISAs or hardware extensions to GPPs; however, they are also restricted. Even though Parallel Table Lookup [76] and Parallel Read instructions [130] are not intended to be algorithmspecific extensions, they are not useful for the algorithms that do not have table lookup operations and not enough to implement the full functionality of the algorithms that have table lookup operations. The ISE proposed by Grabher [89] accelerates a wider range of cryptographic algorithms compared to other ISE solutions. Nevertheless, it is also limited to a subset of cryptosystems, specifically the ones that operate on data in a bit-oriented manner rather than word-oriented.

Even though ISE proposals improve software performance of cryptographic algorithms, most of the added functionalities is limited to speeding up AES only or a limited subset of crypto-systems. However, more generic crypto-specific ISEs are desirable to support a wide range of algorithms and achieve higher throughput.

#### 2.2 Algorithm Specific Hardware

In addition to ISE solutions introduced in literature and commercial products, there are countless algorithm-specific hardware implementations for both ASIC and FPGA intended to achieve high throughput and better area and power efficiency.

Due to large development and manufacture cost of cell-based and full custom hardware, ASIC solutions become less attractive then FPGA-based solutions. FPGA-based designs also have a quicker time-to-market cycle than ASICs. Therefore, FPGA generally seems to be the ideal candidate for reconfigurable yet high-performance implementation of cryptography algorithms. FPGA-based designs often operate efficiently when highly pipelined. Most of the optimized hardware implementations of cryptographic algorithms use pipelined approaches with varying number of stages, where inner-round functions are duplicated. Doing so allows to achieve a higher maximum frequency, higher throughput, and more efficient use of hardware resources. There has been significant amount of work done in the area of high performance implementation of crypto-systems, specifically for AES [5, 31, 49, 70, 86, 87, 99, 100, 102, 107, 109, 132, 139, 151, 171, 181, 186, 187, 204, 212, 228]. Optimized hardware implementations have also been described for Camellia [60, 223], DES [144], Twofish [124], Blowfish [70], RC4 [78], SHA-1 and SHA-2 [48].

Although hardware solutions optimized for particular algorithms do not have the same objective as our work, they inspired us to design a more optimized processor and helped us to map algorithms onto our processor more effectively rather than following the traditional structures as described in their specifications.

### 2.3 Domain Independent Configurable Processors

Besides application and domain-specific reconfigurable computing solutions, there also exists research projects [126, 170] on domain independent configurable processors to lower design effort and eliminate hardware modifications when requirements change. The main purpose of such systems is to enable efficient high performance computing. Despite the fact that flexibility and ease of design are listed as the key benefits of these systems, the applicability of the proposed techniques has not been evaluated on more than one application or domain. The reconfigurability of such systems only allows the processor to integrate different hardware accelerators or configure different functional units in execute stage based on the input.

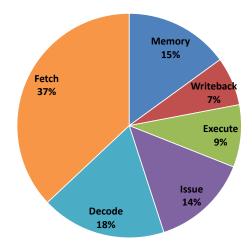

One serious drawback of the proposed techniques is that they rely on traditional instruction fetch and decode structures to make control decisions, which increases the complexity of hardware, requires more area, and consumes the majority of total energy used in the whole processor (Figure 2.1). In an in-order Reduced Instruction Set Computer (RISC), a large fraction of energy dissipation can be attributed to the instruction supply; 37% for fetching, 18% for decoding, and 14% for issuing an instruction [92]. With our processor architecture, we aim to increase energy efficiency by simplifying the front-end structure of a conventional processor. We use a compact finite state machine

Figure 2.1: The distribution of energy dissipation in an in-order RISC processor [92]

representation for control flow of algorithms to reduce the energy consumption and area requirements.

Our proposed architecture is not the first attempt to simplify the front end of the system. BERET [92] is an energy efficient general purpose coprocessor that can be configured to benefit a wide range of applications. The proposed approach maps users' application to predefined sub-graphs and partially eliminates "fetch-decode-issue" stages using trace cache for those sub-graphs.

Besides high power consumption and area requirements, generic reconfigurable processors generally fail to achieve very high throughput due to the lack of cryptographic algorithm-specific instructions, or they require recompilation process to adapt their internal structures for a specific algorithm. To the best of our knowledge, ProDFA [224] is the only domain independent runtime reconfigurable architecture that is evaluated on symmetrickey encryption algorithms and does not rely on traditional "fetch-decode-issue" structure. The proposed architecture consists of several reconfigurable processing units, memory units, and interconnects. Each sub-unit is self-controlled using a finite state machine. Even though overall architecture of ProDFA is domain independent, the functional units need to be recompiled for different application domains.

### 2.4 Configurable Cryptographic Processors

Even though there are various application-specific coprocessors and algorithm-specific hardware implementations, there are very limited attempts to build configurable cryptographic processors with generic modules suitable for a large set of cryptographic algorithms.

CRYPTONITE [43], a Very Long Instruction Word (VLIW) architecture, is a cryptographic processor that supports various encryption and hashing standards, e.g. AES, DES, MD5, and SHA-1. The proposed processor is a twocluster architecture where each bank consists of a crypto-specific arithmetic logic unit and dedicated memory structure with vector memory addressing mode optimized for table-based encryption functions. Even though the proposed vector memory addressing scheme provides flexibility on permutations and table lookup operations, only per-byte or smaller granularity operations are supported. CCProc [208] is a flexible cryptography co-processor for symmetric-key encryptions. The proposed coprocessor has its own instruction set tailored to symmetric-key encryption algorithms and an extended VLIW RISC-like datapath structure. The design was aimed to support a wide range of symmetrickey encryption algorithms, but only tested on AES round 2 finalists; Rijndael(AES), MARS, RC6, Serpent, and Twofish. Support for other ciphers and cryptographic hash functions has not been evaluated.

Multi-Core Crypto-Processor (MCCP) [90] is an FPGA-based reconfigurable and high throughput cryptographic processor to secure multi-channel and multi-standard communication systems. It is designed as loosely coupled multi-core system with its own crypto-specific ISA to provide a flexible and high performance cryptography solution. However, the proposed structure is designed to support only 128-bit block cipher algorithms. Thus, it fails to be generic for both symmetric-key encryptions and cryptographic hash functions.

Celator [77] is another cryptographic coprocessor that supports multiple block ciphers and cryptographic hash functions. The proposed architecture consists of 4x4 identical processing elements, each of which can be configured independently. A processing element is capable of performing XOR, AND, NOT, modular arithmetic, right shift, and one AES-specific operation; *xtime*. Even though proposed processor is designed for multi-algorithm support, it has not been evaluated on algorithms other than AES, DES, SHA-1, and SHA-2, and the processing element structure is not powerful enough to support a wide range of algorithms efficiently. Zodiac [93] is a Network Security Processor designed to provide high performance for network security protocols; IPsec and SSL. Even though it seems to be an application-specific processor, its architecture allows to perform different algorithms and applications; DES, 3DES, AES, RSA, ECC, SHA-1, pseudo random number generation, IPsec, and SSL. Like other alternatives, the main drawback of the proposed processor is that it is restricted to a predefined set of cryptographic applications due to having dedicated hardware for each algorithm.

Cryptographic (Optimized for Block Ciphers) Reconfigurable Architecture (COBRA) [66, 68] is a reconfigurable array structure for efficient block cipher implementations. The proposed architecture is designed after a detailed analysis of 41 block ciphers. However, the algorithm analysis is restricted to block ciphers that operate on plaintext with block sizes of 64 and 128 bits. Even though it aims to support wide range of block ciphers, it fails to efficiently support some most commonly known algorithms (i.e DES and IDEA); thus, it fails to be generic even for block ciphers. The main reasons of not being able to generic are (i) limited block size support, (ii) insufficient lookup table structure, (iii) insufficient bit-wise permutations, and (iv) fixed modulus in modular arithmetic units. While bitwise shifts and rotations are possible on COBRA, bit-wise permutations are extremely difficult to implement. The main difference between COBRA and other configurable cryptographic processors is that the datapath needs to be recompiled for each algorithm separately, resulting different clock frequency and area usage for each algorithm. However, our project focuses on designing a cryptographic processor with fixed hardware that can be reconfigurable for a wide range of existing cryptographic processor.

Besides research projects, there exists one commercial processor introduced by IBM, called IBM PCIe Cryptographic Coprocessor [103], which provides a high-security and high throughput cryptographic subsystem with specialized hardware to perform AES, DES, 3DES, RSA, SHA-1, and SHA-2. The coprocessor consists of secured sub-system modules which are controlled using sub-system control program and a cryptographic application programming interface (API).

The advantages of alternative solutions described above include better area, power and cost efficiencies, flexibility, algorithm upgradability, and higher performance. However, existing reconfigurable crypto-processors are still restricted to only a small set of symmetric-key encryption algorithms and hash functions, and are far from being generic for all existing and potential future algorithms. Moreover, the proposed solutions mostly rely on traditional instruction fetch and decode structures to make control decisions, which potentially results in high power and area consumptions.

## Chapter 3

## Cryptographic Algorithm Analysis

In this chapter, we describe our algorithm selection process and analysis methodology, and provide a detailed analysis on existing symmetric-key encryption algorithms and cryptographic hash functions.

### 3.1 Existing Workload Characterizations

Designing a flexible, high performance, and resource efficient solution for cryptographic applications requires a comprehensive literature review on existing symmetric-key encryption algorithms and hash functions. Besides detailed information on existing algorithms, such study also gives an insight about potential requirements and specifications of future cryptographic algorithms.

Even though there are numerous attempts to speed up cryptographic applications, there are only few studies [77, 206, 208, 224] that present analysis on functional and hardware structure of existing cryptographic algorithms. However, since they are only supportive parts of the presented work in these papers, these analyses only focus on a small set of cryptographic algorithms and only categorize the operation classes. Thus, they do not provide sufficiently detailed information about common hardware structures of existing crypto-systems to enable the design of high performance configurable crypto processor. On the other hand, there are some attempts [45, 47, 75] to study workload characteristics of a set of cryptographic algorithms and profile their software implementation. They give a good idea about the operations classes, their usage frequencies, and required instructions. However, they are also limited to a small set of algorithms, hence not sufficient enough to design a highly configurable cryptographic processor. With its analysis on 41 block ciphers, Elbirt [68] provides detailed information about their functional primitives and common hardware elements so far. However, the algorithm analysis is restricted to block ciphers that operate on plaintext with block sizes of 64 and 128 bits. Like other studies, it also does not present the relation between functional primitives, common patterns, and connection structures. Hence, it is far from providing a sufficiently detailed analysis.

To the best of our knowledge, our analysis on 148 existing cryptographic algorithms is the first and only work that provides a comprehensive analysis on symmetric-key encryption algorithms and cryptographic hash functions about their specifications, requirements, and hardware structures. During our analysis, we mostly focused on architectural structure cryptographic algorithms, where our aim is to bridge the gap between hardware designers and cryptographic algorithm developers. We believe that such a detailed literature survey will help both algorithm developers and researchers while designing new cryptographic algorithms and/or standards, and hardware architects to design flexible crypto-specific processors achieving high performance. Even though each algorithm has different structures and characteristics, we focused on finding general patterns, common characteristics, and the features that create diversity among algorithms. Unlike previous work, instead of focusing on algorithms and features that suit best to our needs, we provide a broader insight about cryptographic algorithms to enable users to pick their own algorithm list and configure their environments and hardware based on their needs.

#### 3.2 Algorithm Selection

We studied more than a hundred ciphers and hash functions from Lucifer[200] (1971) to present. Our algorithm selection process was solely based on mostly used security protocols such as IPsec, TLS/SSL, WTLS, SSH, S/MIME, and OpenPGP, and cryptographic libraries such as OpenSSL and GNU Crypto. However, common security protocols and libraries do not cover a wide range of algorithms. For that reason, we crawled the literature, patents as well as famous competitions for security standards organized by National Institute of Standards and Technology (NIST), New European Schemes for Signatures, Integrity and Encryption (NESSIE), eSTREAM, and European Network of Excellence in Cryptology (ECRYPT). We analyzed not only the winners but also all finalists and semi-finalists in these competitions. Finally, our algorithm analysis consists of 148 cryptographic algorithms including 96 block ciphers, 26 stream ciphers, and 26 cryptographic hash functions. **a.** Block ciphers: A block cipher is a deterministic method of encrypting text in a way that the algorithm is applied with user's secret key to fixed-length groups of bits at once as a block rather than to one bit at a time. They rely on a fixed secret key and an unvarying transformation defined by the algorithm. Many block ciphers are characterized as a Feistel network that divides the data block into two halves where one half operates upon the other half. Block ciphers play a crucial role in the design of cryptographic protocols and are widely used to encrypt large bulk data. Due to the significant number of block ciphers in the literature, they represent a huge portion of existing algorithms used in our study. Thus, they have a serious impact on the design of our processor as well.

The list of block ciphers that we used in our analysis is as follows;

- 3WAY [55]

- AES [58]

- Akelarre [6]

- Anubis [19]

- ARIA [123]

- BaseKing [51]

- Blowfish [188]

- Camellia [10]

- CAST-128 [2]

- CAST-256 [3]

- CIKS-1 [150]

- Cipherunicorn-A [182]

- Cipherunicorn-E [183]

- CLEFIA [196]

- CMEA [172]

- COCONUT98 [210]

- Crab [115]

- Cryptomeria/C2 [37]

- CRYPTON [131]

- CS-Cipher [201]

- DEAL [118]

- DES [1]

- DESX [117]

- DFC [82]

- E2 [207]

- FEAL [194]

- FEALNX [149]

- FEA-M [226]

- FOX [114]

- FROG [81]

- GOST [169]

- Grand Cru [154]

- Hasty Pudding cipher [190]

- Hierocrypt-3 [166]

- Hierocrypt-L1 [165]

- ICE [122]

- IDEA [125]

- Intel Cascade Cipher [39]

- KeeLoq [42]

- KHAZAD [20]

20

- Khufu and Khafre [30]

- KLEIN [85]

- KN-Cipher [162]

- Ladder-DES [174]

- LED [91]

- LOKI97 [41]

- LUCIFER [200]

- M6 [116]

- M8 [164]

- MacGuffin [32]

- Madryga [135]

- MAGENTA [108]

- MARS [46]

- MBAL [120]

- Mercy [50]

- MESH [155]

- Kasumi [140]

- MMB [54]

- MULTI2 [15]

- MultiSwap [192]

- New Data Seal [22]

- NewDES [191]

- Nimbus [134]

- Noekeon [57]

- NUSH [222]

- NXT [113]

- PRESENT [35]

- PRINCE [36]

- Q [142]

- RC2 [119]

- RC5 [178]

- RC6 [180]

- REDOC III [197]

- SAFER K-128 [137]

- SAFER K-64 [136]

- SAFER+ [138]

- SC2000 [195]

- SEED [128]

- Serpent [9]

- SHACAL [95]

- SHACAL-2 [143]

- Shark [173]

- Skipjack [159]

- SMS4 [61]

- Spectr-H64 [88]

- Square [56]

- SXAL [163]

- TEA [216]

- Threefish [72]

- Twofish [189]

- UES [96]

- Xenon [209]

- Xmx [152]

- XTEA [157]

- XXTEA [225]

- Zodiac [127]

- **b.** Stream Ciphers: A stream cipher is a deterministic method of encrypting text in which plaintext digits are combined with a pseudorandom cipher key stream. Unlike block ciphers, stream ciphers work on smaller chunks of data (usually one byte at a time), keep some sort of memory (called "state") while processing the plaintext, and use this state as an input on the next stages. Stream ciphers are often used for their speed and simplicity in applications where plaintext comes in quantities of unknowable length like a secure wireless connection.

The list of stream ciphers that we used in our analysis is as follows;

| • A5/1 [83]       | • MICKEY [17]  | • SEAL [184]   |

|-------------------|----------------|----------------|

| • A5/2 [168]      | • MUGI [214]   | • Sfinks [38]  |

| • Achterbahn [79] | • PANAMA [52]  | • SNOW [65]    |

| • DECIM [23]      | • Phelix [217] | • Trivium [59] |

| • FFCSR [11]      | • Py [29]      | • Turing [185] |

| • FISH [33]       | • Rabbit [34]  | • VEST [167]   |

| • GRAIN [97]      | • RC4 [213]    | • WAKE [215]   |

| • HC256 [218]     | • Salsa20 [24] |                |

| • ISAAC [111]     | • Scream [94]  | • Yamb [220]   |

|                   |                |                |

c. Cryptographic Hash Functions: Cryptographic hash functions processes an arbitrary finite length input message to a fixed length output referred to as the hash value. Any changes in message or data (even slight ones) potentially result in entirely different cryptographic hash value due to the avalanche effect that is intentionally designed in the algorithm. The desired security level for cryptographic hash functions is that it should be impossible (i) to find two messages with substantially similar digests, and (ii) to infer any useful information about the data using its digest. Secure hash functions serve data integrity, non-repudiation, and authenticity of the source in conjunction with the digital signature schemes. For that reason, an ideal cryptographic hash function should be injective. Besides cryptographic hash functions already in use, we also included finalists and semi-finalists proposals in recent SHA3 competition into our algorithm analysis to cover recent algorithms as well.

The list of cryptographic hash functions that we used in our analysis is as follows; • BLAKE [14]

- GOST [148]

- Groestl [80]

- HAS-160 [12]

- Haval [229]

- Hamsi [121]

- JH [219]

- Keccak [27]

- MD2 [177]

- MD4 [176]

- MD5 [175]

- MD6 [179]

- PANAMA [53]

- RadioGatÞn [26]

- RIPEMD [62]

- RIPEMD-160 [63]

- SHA-0 [160]

- SHA-1 [64]

- SHA-2 [74]

- SHAvite3 [28]

- SipHash [13]

- Skein [73]

- Snefru [146]

- SWIFFT [133]

- TIGER [8]

- Whirlpool [21]

#### 3.3 Analysis Methodology

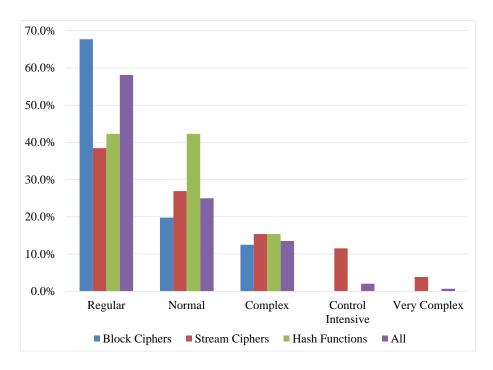

We studied specifications of each cryptographic algorithm and manually gathered detailed information about all aspects of these algorithms. During our studies, we mainly focused on analyzing table sizes, addressing schemes, operation classes, high-level sequence of operations, operation widths, and connection structures of the 148 algorithms. Even though each algorithm has different structures and characteristics, we focused on finding general patterns, common characteristics, and the features that create diversity among algorithms. The detailed results and discussions are presented in following sections.

Besides manual analysis of 148 cryptographic algorithms, we created a simple cryptography programming language and implemented a toolchain that takes an algorithm, optimizes its control and data flow, generates a dataflow graph, and cross compare of dataflows with other algorithms' dataflow graphs to extract common patterns and structures. Using our tools allowed us to extract pure data dependencies defined by the algorithm itself rather than tool-specific or language-specific optimizations that would arise if we started with a high-level language like C/C++. Due to the excessive amount of time required to implement and process the dataflow analysis of each algorithm, we limited our analysis to the most widely used algorithms in security protocols and cryptographic libraries. Our dataflow graph analysis included not only individual analysis for each algorithm but also cross comparisons of sub-graphs between algorithms' dataflow graphs.

### 3.4 Detailed Analysis

In this section, we provide a comprehensive analysis on each aspect of cryptographic algorithms' specifications and requirements. In following sections, we describe common operation classes in cryptographic algorithms, special requirements in these operation classes, relations between other operations, and some special needs of particular algorithms. Besides primitive operations used in cryptographic algorithms, we also give a detailed analysis on essential requirements for a good cryptographic processor such as parallel functional units, their connections, and storage requirements.

### 3.4.1 Operation Classes

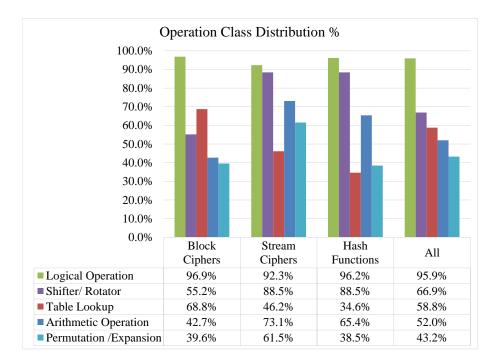

Our analysis suggested that primitive operations used in studied cryptographic algorithms can be clustered in 5 operation classes: (i) arithmetic, (ii) logical, (iii) table lookup, (iv) shift/rotate, and (v) permutation/expansion. The classes were determined based on which functional primitives are used most frequently. There exists a few algorithms that require special functional units; however, we didn't include them in common operation classes since they require special hardware and consideration and those algorithms are not widely used. We discuss special functional units in following sections separately. Primitive operations in each class can be summarized as follows;

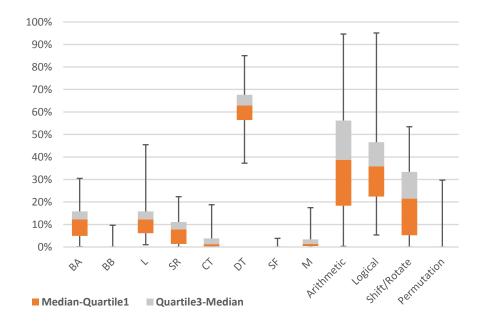

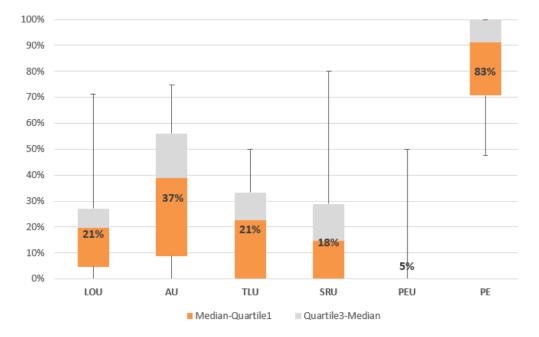

Figure 3.1: The use of operation classes in cryptographic algorithm classes

a. Arithmetic operation: The arithmetic operation class includes scalar addition and subtraction over varying lengths. Since floating point numbers and operations are not used in cryptographic algorithms, hardware support for floating point operations is not required. Even though arithmetic operations can be found in all cryptographic algorithm classes, they are mostly used in stream ciphers. While there is no division operation in cryptographic algorithms, the multiplication will be analyzed separately as a special operation in following sections.

- b. Logical operations: The logical operation class consists of bitwise primitive operations; XOR, AND, OR, and NOT. As shown in Figure 3.1 even though the usage frequency varies among algorithm classes, logical operations are the top most used functions in cryptographic algorithms. More than 95% use one or more logical operations in their datapath. In fact, cryptographic algorithms tend to perform a sequence of logical operations; however, we will present more detailed analysis on operation patterns in following sections. Even though any function can be represented as a sequence logical operations, the algorithms that do not require logical operations in their traditional implementations are KLEIN, MultiSwap, PRESENT, SWIFFT, RC4, and Turing.

- c. Table Lookup: The table lookup operation, also known as SBOX lookup, replaces runtime computation with a simpler array indexing operation. The table lookup operation is one of the most commonly used operations in block ciphers and provides non-linearity during the encryption process. There is a literature [101, 109, 151] that provides computational representations instead of table lookup operations to eliminate the use of memory, but we consider them to be table lookup operations. This

structure is not limited to explicit table lookup operations defined in algorithm specifications. Some functional operations like matrix multiplication with a constant matrix can also be implemented as table lookup operation using a precomputed table.

- d. Shift/Rotate: Variable amount shift and rotation in both direction are clustered in this class. Since shift and rotation operations enable changing the order of the bits in a reversible way, it is the second most commonly used operation class in all types of cryptographic algorithms.

- e. Permutation/Expansion: Permutation/Expansion class is responsible for any bit manipulation on up to 64-bit data. Since permutation and expansion operations require an excessive amount of control signals, they are not widely used. However, some portion of each algorithm class still rely on this operation class. Some permutations, especially byte-wise, can also be represented as a table lookup operation.

Our analysis on the use of each operation class in each crypto-system class as well as overall distributions is summarized in Figure 3.1. A detailed analysis on the use of functional units in cryptographic algorithms can be found in Appendix A. More detailed information about operation clusters is presented in Appendix B. Based on targeted cryptographic algorithm classes, the structure and amount of functional units can be changed while designing cryptographic processor.

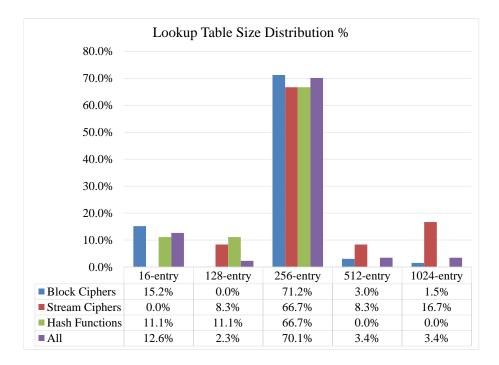

#### 3.4.2 Table Lookup Structure

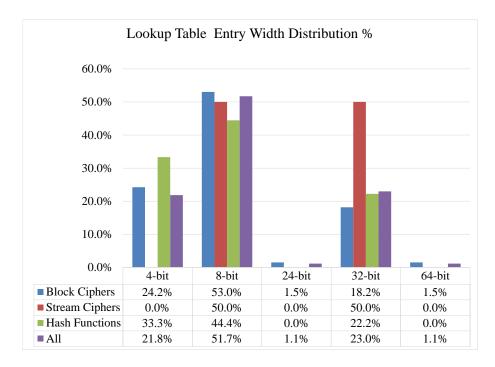

Since table lookup is one of the most common operations, we examined each aspect of the table structure of cryptographic algorithms in detail. We analyzed table sizes, entry widths, addressing schemes, number of different tables, and the number of parallel tables in each algorithm. With a table structure that is too wide, resources are wasted. Additional lookups are required for a table structure that is too narrow. Therefore, table size and entry wide are crucial elements in the design of cryptographic processor. Our studies show that table sizes and addressing schemes greatly vary among crypto-systems. The table sizes used in cryptographic algorithms vary from 16 to 1024 entries while the entry width starts from 4-bit and goes up to 64-bit. Figure 3.2 shows that more than 70 percent of the algorithms using table lookup consist of tables with 256-entry. However, an ideal generic cryptographic processor should support as many algorithms as possible. Thus, in the light of studied algorithms, table lookup unit structures should be mostly 256-entry tables with support for any table size up to 1024 entries.

The width of the table entry is another important consideration on lookup table structure, since unnecessarily large entry width may cause waste of resources while insufficient entry width may result in loss of performance. Figure 3.3 shows that 8-bit and 32-bit are the most common entry widths among the algorithms that use table lookup operation; 51.3% and 23.3% respectively.

Our algorithm analysis shows that even though there are some outlier

Figure 3.2: The ratio of different table sizes used in cryptographic algorithms

algorithms with different table sizes, the most common table structures are 256x32-bit and 256x8-bit. Since there is only one algorithm, KHAZAD [20], which stores 64-bit data in the table, a reasonable table entry size is 32-bit, since any table with 64-bit data entries can be divided into two parallel tables and outputs of both lookup operations can be combined.

Moreover, our algorithm analysis suggests that there are maximum of four parallel 1024-entry, eight parallel 512-entry, and sixteen parallel 256entry tables in any specific cryptographic algorithm. Therefore, the table lookup structure of reconfigurable cryptographic processor should ideally be capable of supporting the table size requirements of all existing algorithms

Figure 3.3: The ratio of different table entry widths used in cryptographic algorithms

for both the size of one table (4 KB), and the total size of parallel tables in algorithm (16 KB) as well as maximum number of parallel lookup operations (16 operations). Any structure that does not meet these requirements may cause lower performance even though they might save some other resources like area and power.

Table 3.1 shows the distribution of number of parallel lookup operations in cryptographic algorithms. Even though some of the the SHA-3 candidates such as Groestl, Hamsi, and JH use 128 and 256 parallel lookup operations in their bit-slice implementation, we do not include them as maximum number of parallel lookup operations.

|                | 1     | 2     | 4     | 8     | 16 +  |

|----------------|-------|-------|-------|-------|-------|

| Block Ciphers  | 3.0%  | 3.0%  | 22.7% | 43.9% | 27.3% |

| Stream Ciphers | 16.7% | 33.3% | 33.3% | 16.7% | 0.0%  |

| Hash Functions | 0.0%  | 0.0%  | 11.1% | 22.2% | 66.7% |

| All            | 4.6%  | 6.9%  | 23.0% | 37.9% | 27.6% |

Table 3.1: The distribution number of parallel lookup operation in cryptographic algorithms

### 3.4.3 Bundled Operation Patterns

Cryptographic algorithms process a sequence of operations on a fixsized block of data. Their fairly regular structures enable bundling commonly executed sequences of operations as a single big operation block. We studied the possibility of such bundles and examined the ratio of algorithms that use these bundles. The result of our study gave us better insight about general trends in cryptographic algorithms, enabling to design a better cryptographic processors.

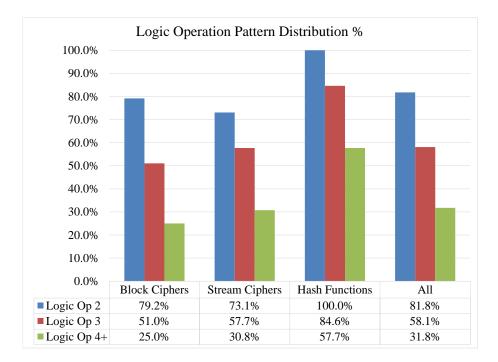

As we mentioned earlier, logical operators are the most commonly used operations, and cryptographic algorithms tend to perform a sequence of logical operations back to back. Our studies show that more than half of all cryptographic algorithms process three consecutive logical operations. As shown in Figure 3.4, 82.4% of the algorithms that we studied process two consecutive logical operations while 58.8% process three, and 57.7% of the cryptographic hash functions process four or more in a row.

Our algorithm and dataflow graph analysis suggest that in most of the cryptographic algorithms table lookup operations are preceded and/or followed

Figure 3.4: The distribution of logical operation patterns in cryptographic algorithms

by an XOR operation. Table 3.2 shows that XOR-SBOX, SBOX-XOR and XOR-SBOX-XOR operation bundles are processed in 69.0%, 71.4%, and 59.5% of the algorithms that have table lookup operations, respectively.

Besides the pattern of XOR and SBOX operations, we also analyzed the possibility of other bundles between other operation classes. The second most common relation between operation classes is the pattern of shift/rotate and logical operations. Table 3.3 summarizes that Logic-Shift/rotate, Shift/rotate-Logic, and Logic-Shift/rotate-Logic operation bundles are processed in 44.4%, 49.5%, and 34.3% of algorithms using shift/rotate operations, respectively.

|                | XOR-SBOX | SBOX-XOR | XOR-SBOX-<br>XOR |

|----------------|----------|----------|------------------|

| Block Ciphers  | 76.9%    | 76.9%    | 66.2%            |

| Stream Ciphers | 27.3%    | 36.4%    | 18.2%            |

| Hash Functions | 62.5%    | 75.0%    | 62.5%            |

| All            | 69.0%    | 71.4%    | 59.5%            |

Table 3.2: The distribution of XOR and SBOX patterns in cryptographic algorithms

Table 3.3: The distribution of Shift/rotate and logic operation patterns in cryptographic algorithms

|                | Logic Op<br>Shift/rotate | Shift/rotate -<br>Logic Op. | Logic Op<br>Shift/rotate -<br>Logic Op. |

|----------------|--------------------------|-----------------------------|-----------------------------------------|

| Block Ciphers  | 56.6%                    | 50.9%                       | 39.6%                                   |

| Stream Ciphers | 21.7%                    | 60.9%                       | 21.7%                                   |

| Hash Functions | 39.1%                    | 34.8%                       | 34.8%                                   |

| All            | 44.4%                    | 49.5%                       | 34.3%                                   |

Due to the significant amount of XOR and arithmetic operations in cryptographic algorithms, we analyzed the frequency of XOR and arithmetic operation patterns. Table 3.4 shows that XOR-Arithmetic, Arithmetic-XOR, and XOR-Arithmetic-XOR operation bundles are processed in 43.4%, 38.2%, and 35.5% of algorithms using arithmetic operations, respectively.

### 3.4.4 Special Functional Units

As mentioned above, there are some cryptographic algorithms that require special functional units to achieve higher performance or even to be supported. Even though some of those special functions can be realized by

|                | XOR -<br>Arithmetic<br>Op. | Arithmetic<br>Op XOR | XOR -<br>Arithmetic Op.<br>- XOR |

|----------------|----------------------------|----------------------|----------------------------------|

| Block Ciphers  | 51.2%                      | 46.3%                | 41.5%                            |

| Stream Ciphers | 15.8%                      | 10.5%                | 10.5%                            |

| Hash Functions | 56.3%                      | 50.0%                | 50.0%                            |

| All            | 43.4%                      | 38.2%                | 35.5%                            |

Table 3.4: The distribution of XOR and Arithmetic operation patterns in cryptographic algorithms

other operation classes or by a logical combination of those other operation classes, they may also require special logic or dedicated hardware. Our analysis shows that the most commonly required special operations are integer multiplication, byte-wise rotation, and modular arithmetic.

Table 3.5: The special functional unit requirements in cryptographic algorithms

|                | Byte Rotator | Multiplication | $\begin{array}{c} {\rm Modular} \\ {\rm Arithmetic} \end{array}$ |

|----------------|--------------|----------------|------------------------------------------------------------------|

| Block Ciphers  | 24.0%        | 13.5%          | 43.8%                                                            |

| Stream Ciphers | 19.2%        | 3.8%           | 73.1%                                                            |

| Hash Functions | 34.6%        | 11.5%          | 61.5%                                                            |

| All            | 25.0%        | 11.5%          | 52.0%                                                            |

Our studies indicate that only 11.5 percent of cryptographic algorithms that we analyzed use integer multiplication (Table 3.5). In fact, these 17 out of 148 crypto-systems are not common and not included in mostly used security protocols or cryptographic libraries. Therefore, dedicated multiplication hardware may or may not be a necessary component of cryptographic processor depending on target workload. The list of algorithm that explicitly requires multiplication is as follows;

Block Ciphers: Cipherunicorn-A [182], CLEFIA [196], DFC [82], FEA-M [226], IDEA [125], KN-cipher [162], MESH [155], MMB [54], MultiSwap [192], Nimbus [134], RC6 [180], SC2000 [195], and Xenon [209]

Stream Ciphers: Rabbit [34]

#### Hash Functions: PANAMA [53], SWIFFT [133], and TIGER [8]

As shown in Table 3.5, one-fourth of all algorithms use simple bytewise rotation on 32-bit data instead of a variable amount. Although byte-wise rotation is a part of the shift/rotate operation class, hardware implementation is less expensive and can be affordably combined with other classes. On the other hand, a shift/rotate unit working on varying granularities is not necessary since only 1% of all cryptographic algorithms require them, and any granularity can be easily implemented using permutation/expansion class.

Our algorithm analysis suggests that modular arithmetic is one of the most common special operation used in cryptographic algorithms, especially among stream ciphers. Theoretically, the simple form of modular arithmetic (addition, subtraction, and multiplication) is not a special function since it just allows the values always staying less than a fixed number, called base or modulus. As a general rule, we do not want the encryption process to have a big affect on the size of a message. Thus, modular arithmetic allows to keep the operation size within a chosen range. Since modular arithmetic is very well understood in terms of algorithms over various basic operations, it became the primary choice of operation for cryptographic algorithm developers and included in 52% of all cryptographic algorithms (Table 3.5).

Table 3.6: The modular arithmetic base distribution in cryptographic algorithms

|                | $mod(2^8)$ | $\mathbf{mod}(2^{16})$ | $mod(2^{32})$ | $mod(2^{64})$ | Others |

|----------------|------------|------------------------|---------------|---------------|--------|

| Block Ciphers  | 9.5%       | 2.4%                   | 73.8%         | 7.1%          | 7.1%   |

| Stream Ciphers | 26.3%      | 5.3%                   | 63.2%         | 0.0%          | 5.3%   |

| Hash Functions | 0.0%       | 0.0%                   | 93.8%         | 6.3%          | 0.0%   |

| All            | 11.7%      | 2.6%                   | 75.3%         | 5.2%          | 5.2%   |

Any crypto-system that uses modular arithmetic can be constructed in an analogous way with a group having certain properties under associated group of operations. Therefore, due to the choice of the base value, a significant portion of modular arithmetic operations can be implemented using existing operation classes or with a logical combination of them. Table 3.6 shows that 75.3 percent of modular arithmetic operations in studied cryptographic algorithms use  $2^{32}$  as the base value, while more than 90 percent of modular arithmetic operations can be realized using traditional integer arithmetic combined with an AND operation.

On the other hand, there are 5 different cryptographic algorithms that require special hardware or logic to be supported due to their unorthodox base choice for modular arithmetic; specifically  $2^{33}$  for KN-cipher [162],  $2^{32} - 1$

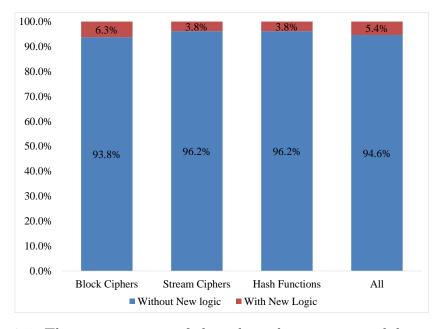

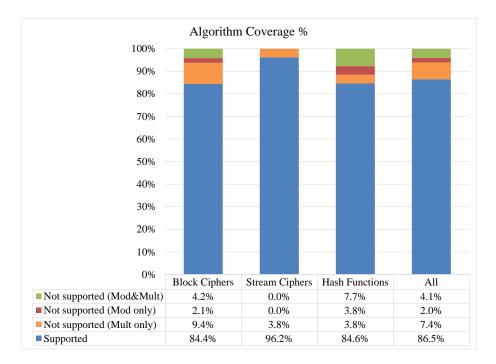

Figure 3.5: The coverage ratio of algorithms that require modular arithmetic

for MMB [54],  $2^{64} + 13$  for DFC [82], 17 for PANAMA [52], and  $2^{256}$  for GOST [148]. Therefore, 94.6 percent of all cryptographic algorithms that we analyzed can be implemented without requiring any complicated logic to combine existing operation classes while only small portion of each algorithm classes does require special consideration, specifically 6.3% of block ciphers, 3.8% of stream ciphers, and 3.8% of hash functions. (Figure 3.5). That is; the choice of target algorithms has a significant impact on designing special hardware for cryptography.

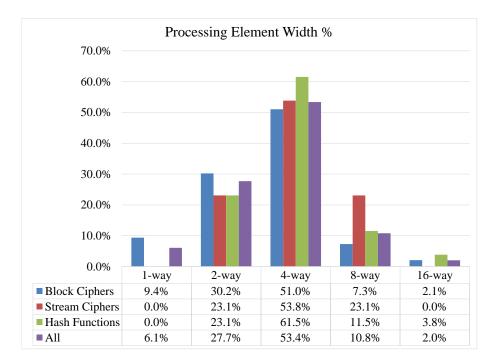

### 3.4.5 Processing Element Width