Copyright by Mahesh Prabhu 2014

# The Dissertation Committee for Mahesh Prabhu certifies that this is the approved version of the following dissertation:

# Scalable Algorithms for Software Based Self Test using Formal Methods

| Committee:                   |

|------------------------------|

|                              |

| Jacob A. Abraham, Supervisor |

| Jayanta Bhadra               |

| Andreas Gerstlauer           |

| David Z. Pan                 |

| Nur A. Touba                 |

# Scalable Algorithms for Software Based Self Test using Formal Methods

$\mathbf{b}\mathbf{y}$

Mahesh Prabhu, B.E., M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2014$

# Acknowledgments

I would like to thank my advisor Dr. Jacob Abraham for his valuable guidance and support. His novel ideas, intellectual discussions and expert comments at every stage have been the catalysts for this work.

I thank all my PhD committee members for giving me valuable inputs on my research and on this dissertation.

Sincere thanks to the students at CERC who were generously available to answer my questions and to direct me to right resources whenever needed. I would especially like to thank Gaurav, Sriram, Ameya, Shahrzad, EJ, Whitney and Junyoung.

Thanks to the CERC and ECE department staff members for their quick response in all the matters that needed their support. I thank Melanie, Debi and Andrew for answering all my questions patiently.

I thank my brother and my sister-in-law for their love and support throughout my PhD. Thanks to my parents for their selfless love and faith in me. Without their support and understanding this PhD would not have been possible. Last but not the least, I thank my loving wife, Shwetha, for standing by me through the most difficult of times. Scalable Algorithms for Software Based Self Test using

Formal Methods

Mahesh Prabhu, Ph.D.

The University of Texas at Austin, 2014

Supervisor: Jacob A. Abraham

Transistor scaling has kept up with Moore's law with a doubling of the

number of transistors on a chip. More logic on a chip means more opportu-

nities for manufacturing defects to slip in. This, in turn, has made processor

testing after manufacturing a significant challenge. At-speed functional test-

ing, being completely non-intrusive, has been seen as the ideal way of testing

chips. However for processor testing, generating instruction level tests for cov-

ering all faults is a challenge given the issue of scalability. Data-path faults

are relatively easier to control and observe compared to control-path faults. In

this research we present a novel method to generate instruction level tests for

hard to detect control-path faults in a processor. We initially map the gate

level stuck-at fault to the Register Transfer Level (RTL) and build an equiva-

lent faulty RTL model. The fault activation and propagation constraints are

captured using Control and Data Flow Graphs of the RTL as a Liner Tempo-

ral Logic (LTL) property. This LTL property is then negated and given to a

vi

Bounded Model Checker based on a Bit-Vector Satisfiability Module Theories (SMT) solver. From the counter-example to the property we can extract a sequence of instructions that activates the gate level fault and propagates the fault effect to one of the observable points in the design. Other than the user supplying instruction constraints, this approach is completely automatic and does not require any manual intervention.

Not all the design behaviors are required to generate a test for a fault. We use this insight to scale our previous methodology further. Underapproximations are design abstractions that only capture a subset of the original design behaviors. The use of RTL for test generation affords us two types of under-approximations: bit-width reduction and operator approximation. These are abstractions that perform reductions based on semantics of the RTL design. We also explore structural reductions of the RTL, called path based search, where we search through error propagation paths incrementally. This approach increases the size of the test generation problem step by step. In this way the SMT solver searches through the state space piecewise rather than doing the entire search at once. Experimental results show that our methods are robust and scalable for generating functional tests for hard to detect faults.

# **Table of Contents**

| Acknowledgments                                            | v    |

|------------------------------------------------------------|------|

| Abstract                                                   | vi   |

| uist of Tables                                             | xi   |

| dist of Figures                                            | xii  |

| Chapter 1. Testing: An introduction                        | 1    |

| 1.1 Fault models                                           | . 2  |

| 1.2 Fault observability and controllability                | . 3  |

| 1.3 Conventional testing techniques                        | . 5  |

| 1.3.1 Automatic test pattern generation (ATPG)             | . 5  |

| 1.3.2 Scan based design for testing (DFT)                  | . 6  |

| 1.3.3 Built-in self test (BIST)                            | . 7  |

| 1.3.4 Functional testing                                   | . 8  |

| 1.4 Software based self test (SBST)                        | . 11 |

| 1.5 Test generation using formal methods                   | . 12 |

| 1.6 Contributions                                          |      |

| 1.7 Outline                                                |      |

| Chapter 2. Software based self test: approaches and issues | 18   |

| 2.1 Functionality based test generation                    | . 18 |

| 2.2 Constraint extraction based approach                   | . 20 |

| 2.3 Pre-computed test mapping approach                     | . 22 |

| Chapter 3. |       | Formal Methods                                                                            | 25              |

|------------|-------|-------------------------------------------------------------------------------------------|-----------------|

| 3.1        | Intro | $\mathbf{oduction}$                                                                       | 25              |

| 3.2        | Mod   | el checking                                                                               | 26              |

|            | 3.2.1 | Unbounded vs bounded model checking                                                       | 26              |

|            | 3.2.2 | Properties                                                                                | 28              |

| Chapte     | er 4. | Functional Test Generation for Hard to Detect Stuck<br>At Faults using RTL Model Checking | -<br><b>2</b> 9 |

| 4.1        | Intro | $\mathbf{oduction}$                                                                       | 29              |

| 4.2        | Preli | minaries                                                                                  | 31              |

|            | 4.2.1 | Boolean difference                                                                        | 31              |

|            | 4.2.2 | Model Checking                                                                            | 32              |

| 4.3        | Appr  | roach                                                                                     | 34              |

|            | 4.3.1 | Capturing Gate level faults in RTL                                                        | 34              |

|            | 4.3.2 | Test Generation Using Model Checking                                                      | 38              |

| 4.4        | Obse  | ervability Property using CDFG                                                            | 41              |

|            | 4.4.1 | Structural Dependency Graph                                                               | 41              |

|            | 4.4.2 | Observability Property                                                                    | 43              |

|            | 4.4.3 | Structural Reduction                                                                      | 46              |

|            |       | 4.4.3.1 Reducing Duplicated Signals                                                       | 46              |

|            |       | 4.4.3.2 Bounded Cone of Influence Reduction                                               | 47              |

| 4.5        | Expe  | erimental Results                                                                         | 48              |

|            | 4.5.1 | OR1200 Processor                                                                          | 48              |

|            | 4.5.2 | Identifying Hard-to-detect Faults                                                         | 49              |

|            | 4.5.3 | Fault Conditions                                                                          | 52              |

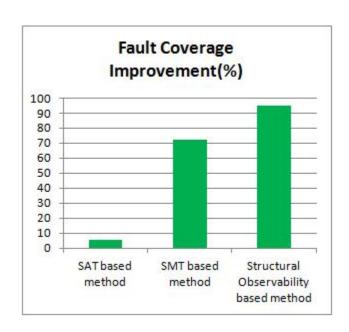

|            | 4.5.4 | SAT-based ATPG                                                                            | 53              |

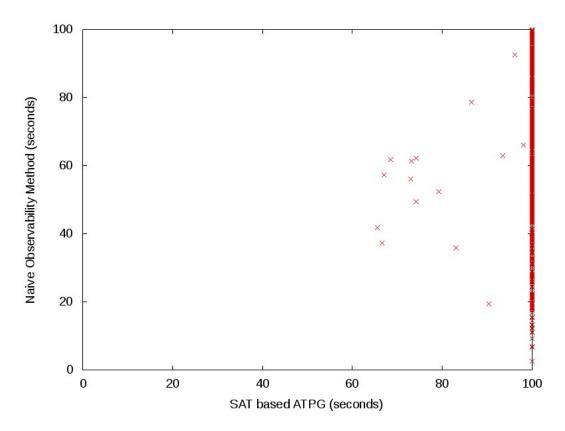

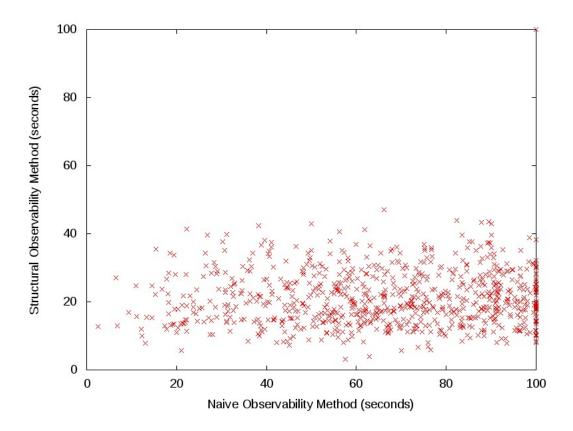

|            | 4.5.5 | The Naive Observability Method                                                            | 55              |

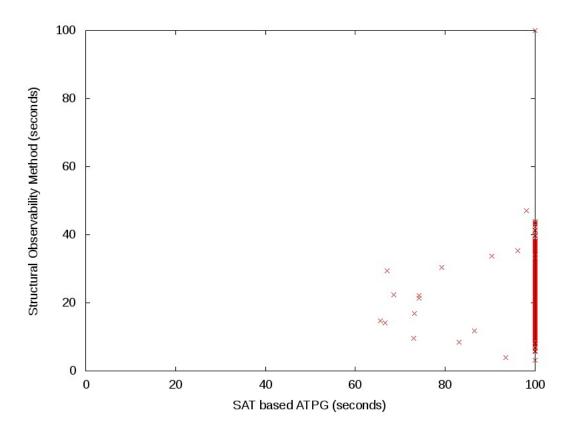

|            | 4.5.6 | The Structural Observability Method                                                       | 56              |

| 4.6        | Sumi  | marv                                                                                      | 61              |

| $\mathbf{Chapt}$ |        |                                        |     |

|------------------|--------|----------------------------------------|-----|

| ۳ 1              | т ,    | Test Generation                        | 64  |

| 5.1              |        | duction                                | 65  |

| 5.2              |        | er-approximation Techniques            | 67  |

|                  | 5.2.1  | Bit-width Reduction                    | 67  |

|                  |        | 5.2.1.1 Bit-width Encoding             | 68  |

|                  |        | 5.2.1.2 Motivating Example             | 69  |

|                  |        | 5.2.1.3 Refinement Strategies          | 71  |

|                  | 5.2.2  | Data-path Operator Approximation       | 74  |

|                  |        | 5.2.2.1 Motivating Example             | 74  |

| 5.3              | Expe   | rimental Results                       | 75  |

| 5.4              | Sumi   | mary                                   | 85  |

| Chapt            | er 6.  | Path Based Search for Test Generation  | 87  |

| 6.1              | Intro  | duction                                | 88  |

|                  | 6.1.1  | Background: Incremental Satisfiability | 88  |

| 6.2              | Path   | Search Heuristics                      | 89  |

|                  | 6.2.1  | Path Selection                         | 92  |

| 6.3              |        | erimental Results                      | 95  |

| 6.4              |        | mary                                   | 97  |

| Chapte           | er 7.  | Conclusion and Future Work             | 100 |

| 7.1              | RTL    | Based Test Generation                  | 100 |

| 7.2              |        | gn Abstractions                        | 101 |

| 7.3              | _      | r Applications of RTL Fault Injection  | 102 |

| Bibliog          | graphy | 7                                      | 104 |

| Vita             |        |                                        | 114 |

# List of Tables

| 4.1 | Commercial ATPG Coverage Results for OR1200 processor                                               |

|-----|-----------------------------------------------------------------------------------------------------|

| 4.2 | Example of SOP for fault condition in OR1200 processor fetch module                                 |

| 4.3 | Running Time and Coverage Results for SAT-based ATPG $$ .                                           |

| 4.4 | Running Time and Coverage Results for the naive observability method                                |

| 4.5 | Running Time and Coverage Results for structural observability method                               |

| 4.6 | Sample tests generated by structural observability method                                           |

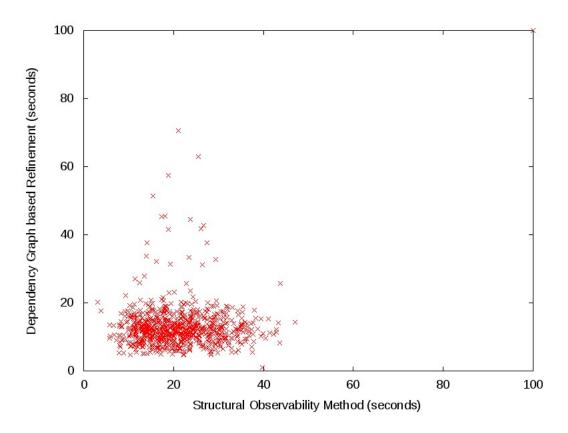

| 5.1 | Running Time for Bit-width reduction                                                                |

| 5.2 | Fault coverage results from structural observability method (no abstraction) for OR1200 processor   |

| 5.3 | Fault coverage results from dependency graph based refinement for OR1200 processor                  |

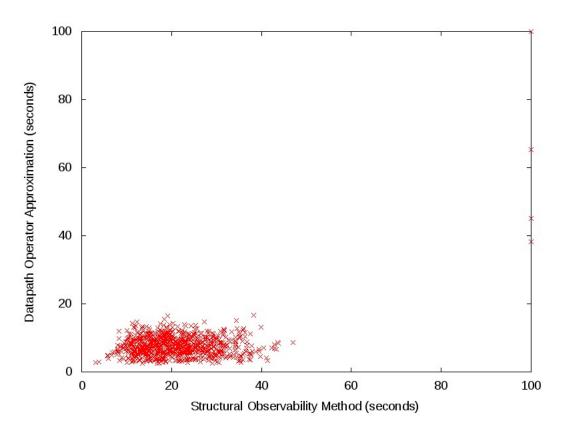

| 5.4 | Running Time for Operator Approximation                                                             |

| 5.5 | Fault coverage results for data-path operator approximation .                                       |

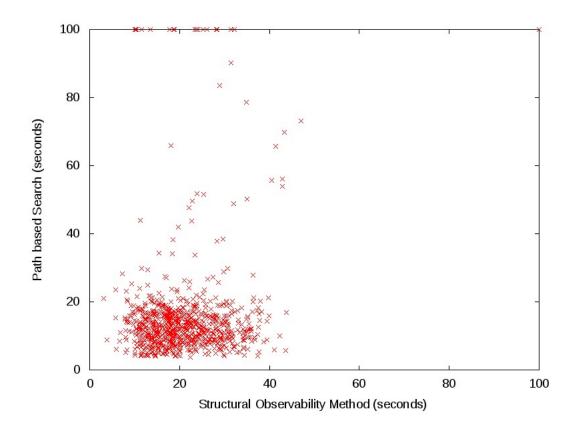

| 6.1 | Experimental results for structural observability method                                            |

| 6.2 | Experimental results for path based search method                                                   |

| 6.3 | Fault coverage results due to structural observability method (no abstraction) for OR1200 processor |

| 6.4 | Fault coverage results from path based search for OR1200 processor                                  |

# List of Figures

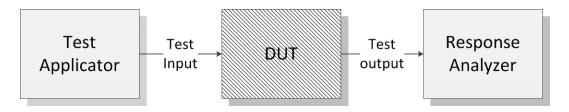

| 1.1  | Testing infrastructure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

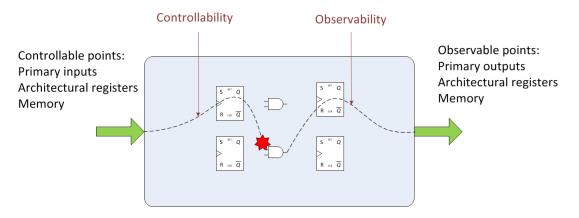

| 1.2  | Controllability and observability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4  |

| 1.3  | Traditional functional testing technique requiring at-speed ATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8  |

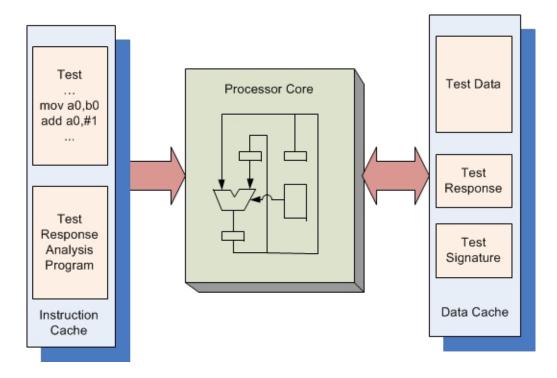

| 1.4  | Software based self test methodology, which can use slower ATE equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12 |

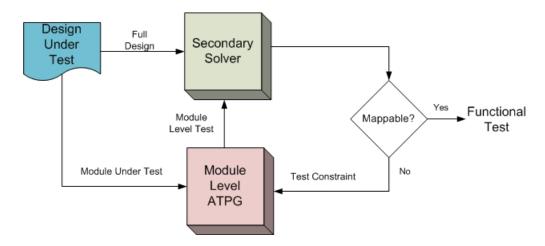

| 2.1  | Mapping based approach for software based self test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 |

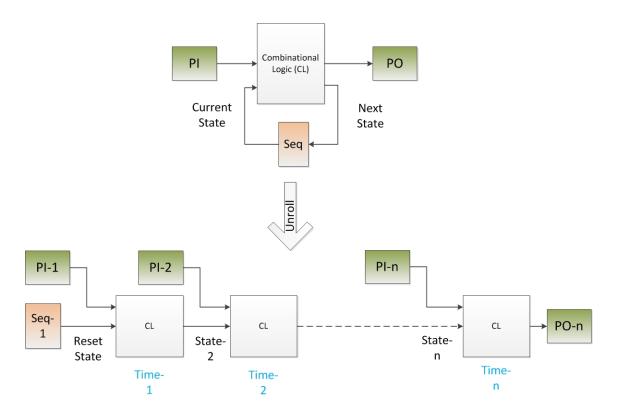

| 3.1  | Unrolling a DUT for a bound of n cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

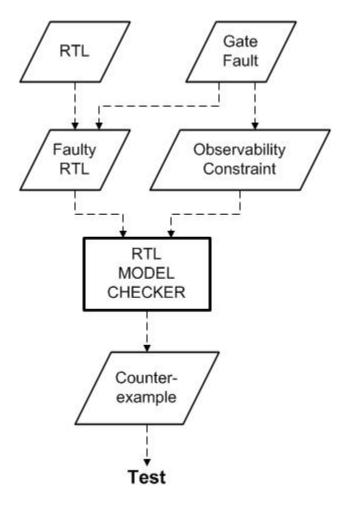

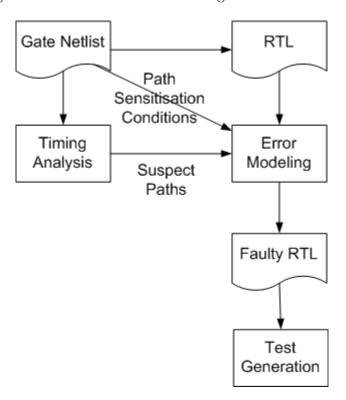

| 4.1  | RTL test generation methodology for gate level faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30 |

| 4.2  | Transitive Fan-in Illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

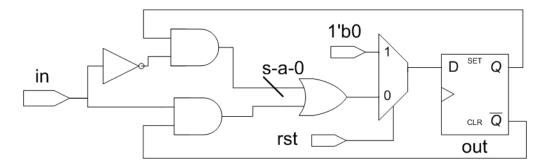

| 4.3  | Stuck-at Fault Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

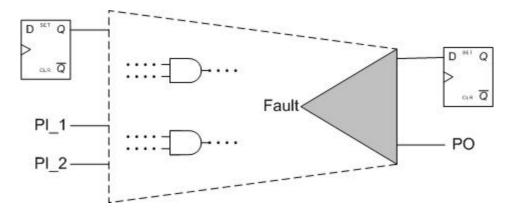

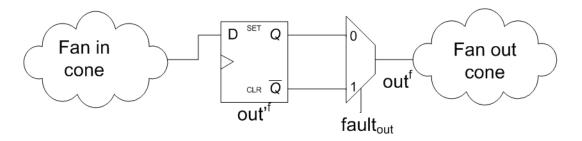

| 4.4  | Fault Injection Mux Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37 |

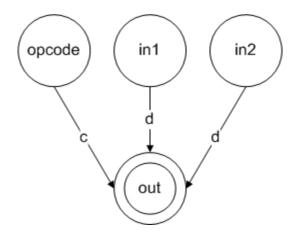

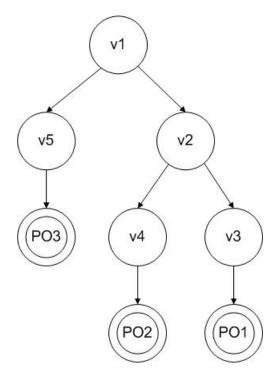

| 4.5  | Example of a control and data dependency graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42 |

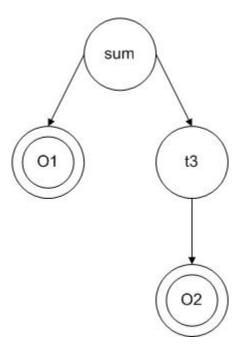

| 4.6  | Control and data dependency graph of verilog example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46 |

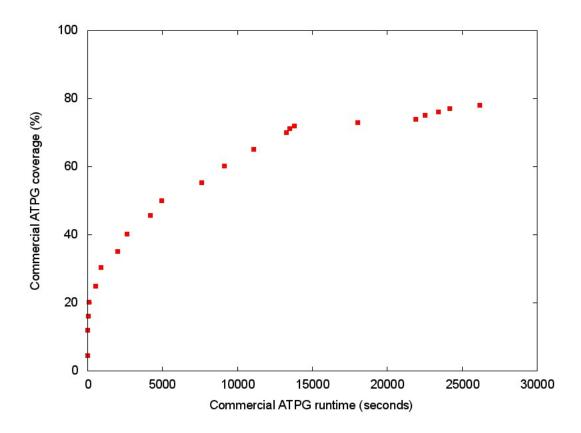

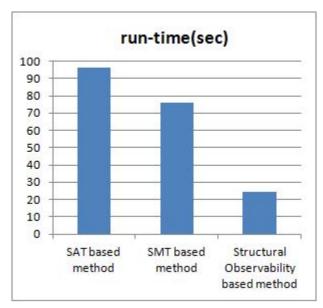

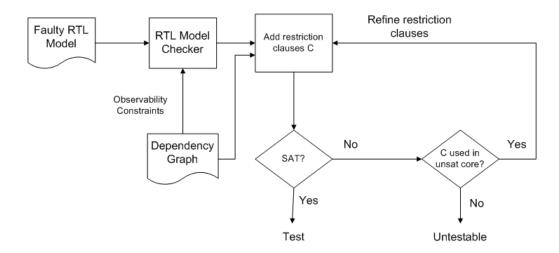

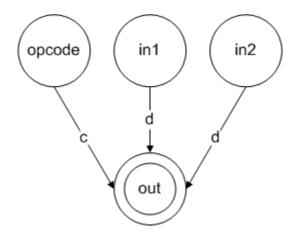

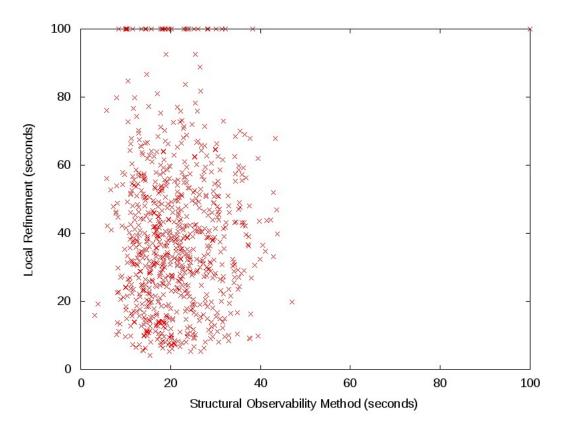

| 4.7  | Commercial ATPG tool results on OR1200 processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |