Copyright by

Jaehyun Ahn

2018

# The Dissertation Committee for Jaehyun Ahn Certifies that this is the approved version of the following dissertation:

**Optoelectronic Devices for Power Conservation and Generation**

**Committee:**

Sanjay Banerjee, Supervisor

Edward Yu

Leonard Frank Register

S.V Sreenivasan

Brian Korgel

# **Optoelectronic Devices for Power Conservation and Generation**

by

# Jaehyun Ahn

# Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

# **Doctor of Philosophy**

The University of Texas at Austin December 2018

# Dedication

To my beloved family and god

#### Acknowledgements

I would like to sincerely thank my supervisor, Professor Sanjay K. Banerjee during this incredible journey. His guidance, support, and patience has truly helped me to get back up from the endless failures in the cleanroom. I would like to acknowledge my committee members, Professor Edward Yu, Professor L. Frank Register, Professor S.V Sreenivasan and Professor Brian Korgel for their support. I would like to thank Jean L. Toll for taking care of everything (from receipts to visa documentations) during my time at MER.

I would like to thank all my friends, colleagues, group members, seniors, staff members during my Ph. D. Among them, I would like to especially commemorate Jongwook Sohn and his wife Soojin Lee. From the first day I landed in Austin, your kindness has been a priceless treasure to me. I would like to thank Dr. Taegon Kim from Samsung Electronics, and Leo Mathew, Dr. Rajesh Rao from Advanced Novel Devices for their technical discussion and support which has led to publications.

Lastly, I thank my mom, dad, and baby sis for their love. They are the pillars of my existence.

### **Optoelectronic Devices for Power Conservation and Generation**

Jaehyun Ahn, Ph.D.

The University of Texas at Austin, 2018

Supervisor: Sanjay K. Banerjee

Energy conservation and generation have become increasingly important in society. Here, we pursue novel transistor technologies based on three-dimensional (3D) FinFETs and two-dimensional (2D) materials to make low power, high speed transistors. We also develop quasi-2D silicon thin film solar cells for power generation.

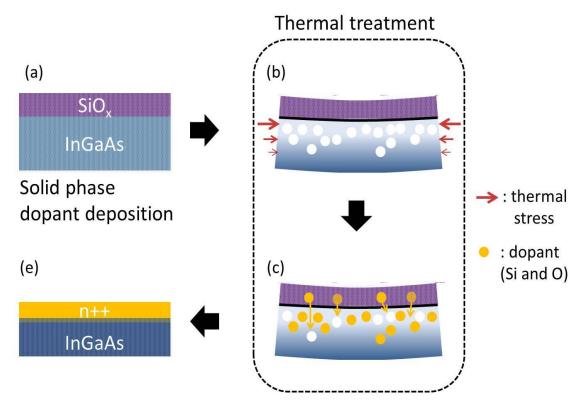

First, a novel approach of doping III-V semiconductors is presented. Oxygen rich silicon oxide (SiO<sub>x</sub>, where x > 2) is found to behave as a solid dopant source when deposited on InGaAs, followed by thermal annealing. Oxygen, when diffused into InGaAs, act as n-type dopants where the active carrier concentration reaches up to  $1.4 \times 10^{18}$  cm<sup>3</sup>. Besides the simple, CMOS compatible doping technique of solid source doping, another interesting factor is the dopant concentration can be altered by the deposited dopant thickness, which adds an additional control knob therefore allowing enhanced control over the doping process. Thermally induced compressive stress within InGaAs due to the difference in coefficient of thermal expansion (CTE) between InGaAs and SiO<sub>x</sub> is known to increase the number of vacancies within InGaAs therefore giving rise to active dopant concentration. This approach can be used to make high speed, low power transistors.

Second, study of thin indium metal contacts on InGaAs is presented. Unlike silicon, III-V compound semiconductors such as InGaAs decomposes around 450 °C which result in out-diffusion of indium and gallium and decrease in metal-InGaAs contact resistance. By adding a thin layer of indium between the metal-InGaAs interface, the out-diffusion of gallium was minimized.

Third, solar cells based on graphene-silicon (GS) heterojunction architecture are demonstrated on bendable crystalline silicon substrates. Flexible, thin silicon films are fabricated by using the thermal expansion difference between electroplated nickel and bulk silicon, which generates residual strain upon thermal cycling. By controlling the amount of thermal stress, silicon thicknesses between 8 and 35 µm are exfoliated through a kerf-less mechanical method. Together with multi-layer graphene (MLG) grown by chemical vapor deposition (CVD) and atomic layer deposition (ALD) of Al<sub>2</sub>O<sub>3</sub> as a silicon passivation layer, power conversion efficiencies (PCE) of 7.4 % were achieved on bendable silicon substrates.

Finally, Chapter 7 summarizes the all the chapters from this dissertation and some thoguhts for future work.

# **Table of Contents**

| List of Tab | oles    | Х                                                                   |

|-------------|---------|---------------------------------------------------------------------|

| List of Fig | ures    | Xi                                                                  |

| Chapter 1.  | Introdu | iction                                                              |

| 1.1.        | III-V   | Compound Semiconductors: InGaAs                                     |

|             | 1.1.1   | Challenges in Fin doping                                            |

| 1.2.        | AlG     | N/GaN Compound Semiconductor and 2DEG layer                         |

| 1.3.        | Two     | -Dimensional Materials                                              |

| 1.4.        | Kerf    | -less Exfoliation of Semiconductors                                 |

| 1.5.        | Orga    | nization of Dissertation                                            |

| -           |         | cale doping of compound semiconductors by solid phase<br>diffusion1 |

| 1.1.        | Intro   | duction1                                                            |

| 1.2.        | Samj    | ple Preparation12                                                   |

| 1.3.        | Resu    | Its and Discussion12                                                |

| 1.4.        | Conc    | elusion                                                             |

| -           |         | ontact Resistivity Indium Metal Contacts on InGaAs and GaAs tion2   |

| 3.1.        | Intr    | oduction2                                                           |

| 3.2.        | Exp     | perimental24                                                        |

| 3.3.        | Ker     | -less Exfoliation of GaAs                                           |

| 3.4.        | Cor     | nclusion                                                            |

| Chapter 4.  | Demor   | nstration of bendable GaN HEMT for RF applications                  |

| 4.1.        | Intr    | oduction                                                            |

| 4.2.        | Exf     | oliation of AlGaN/GaN 2DEG Layer on Silicon Substrate40             |

| 4.3.        | Der     | nonstration of AlGaN/GaN HEMT on Silicon Substrate42                |

|             | 4.3.1.  | Photomask Drawing for HEMT Structure42                              |

|             | 4.3.2.  | AlGaN/GaN Etch and Channel Definition44                             |

|             | 4.3.3.  | Specific contact resistivity of AlGaN/GaN layer48                   |

|            | 4.3.4. | I-V Characteristics of AlGaN/GaN HEMT49                                                               |   |

|------------|--------|-------------------------------------------------------------------------------------------------------|---|

| 4.4.       | Ker    | f-less exfoliation of non-planar, multi-layer architecture51                                          |   |

| Chapter 5. | -      | hene-Al <sub>2</sub> O <sub>3</sub> -Silicon Heterojunction Solar Cells on Flexible Silicon<br>trates | n |

| 5.1.       | Intro  | duction53                                                                                             |   |

| 5.2.       | Exp    | erimental54                                                                                           |   |

|            | 5.2.1. | Growing, doping, and transfer of multilayer graphene54                                                |   |

|            | 5.2.2. | Fabrication of thin silicon films with metal backing                                                  |   |

|            | 5.2.3. | Graphene-silicon (and graphene-insulator-silicon) SBSC fabrication                                    |   |

| 5.3.       | Res    | ults and discussion62                                                                                 |   |

|            | 5.3.1. | GS-SBSC                                                                                               |   |

|            | 5.3.2. | GIS cells with ALD Al <sub>2</sub> O <sub>3</sub> 65                                                  |   |

| 5.4.       | Con    | clusion69                                                                                             |   |

| -          | U      | rown h-BN for Photovoltaic and Electronic Device Applications                                         |   |

|            | •••••  |                                                                                                       |   |

| 6.1.       | Intr   | oduction71                                                                                            |   |

| 6.2.       | Exp    | erimental72                                                                                           |   |

|            | 6.2.1. | h-BN Growth and Characterization72                                                                    |   |

| 6.3.       | Pho    | tovoltaic application of CVD h-BN74                                                                   |   |

|            | 6.3.1. | Graphene/h-BN/c-Si Solar Cell Fabrication74                                                           |   |

|            | 6.3.2. | Results and Discussion74                                                                              |   |

| 6.4        | Elec   | tronic application of CVD h-BN78                                                                      |   |

|            | 6.4.1. | Graphene/h-BN FET78                                                                                   |   |

|            | 6.4.2. | Fabrication of Graphene/h-BN FET78                                                                    |   |

|            | 6.4.2. | Results and Discussion79                                                                              |   |

| Chapter 7. Conclusion and Future Work | 80 |

|---------------------------------------|----|

| Appendix                              | 84 |

| References                            | 87 |

| Vita                                  | 93 |

# List of Tables

| Table 2.1: | RBS measurement of $SiO_x$ deposited samples with different gas flow       |

|------------|----------------------------------------------------------------------------|

|            | rate14                                                                     |

| Table 6.1: | Open circuit voltage (Voc), short circuit current (Jsc), fill factor (FF), |

|            | power conversion efficiency (PCE) and cell area for graphene/h-            |

|            | BN/A12O3/exfoliate silicon (GBIS), graphene/h-BN/exfoliation silicon       |

|            | (GBS), graphene/Al2O3/exfoliated silicon(GIS), and                         |

|            | graphene/exfoliated silicon (GS) solar cells76                             |

# List of Figures

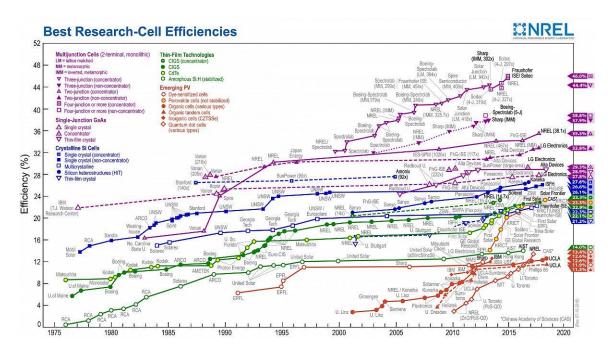

| Figure 1.1: | Best Research-Cell Efficiency graph by NREL1                             |

|-------------|--------------------------------------------------------------------------|

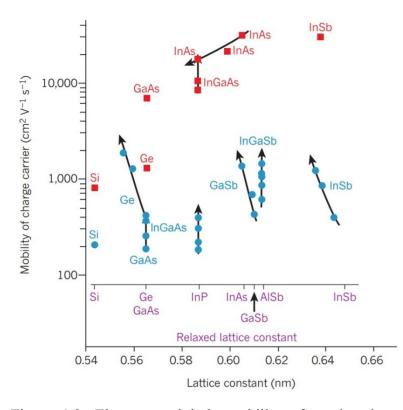

| Figure 1.2: | Electron and hole mobility of semiconductors including silicon,          |

|             | germanium and III-V compound semiconductors                              |

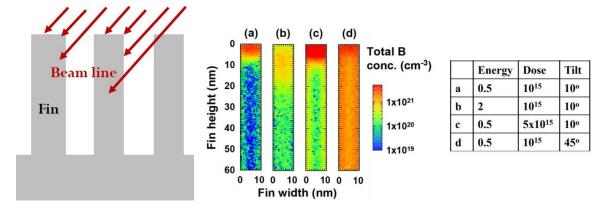

| Figure 1.3: | Left: Schematic of Fin structure with ion implantation beam line,        |

|             | Middle, Right: Simulation result of doping profile of silicon fin with   |

|             | different implant energy, dose and beam angle4                           |

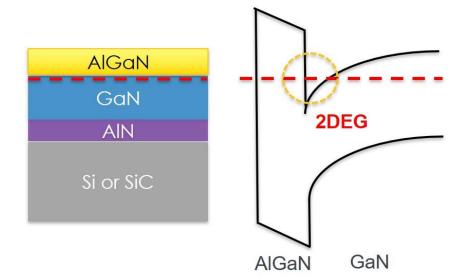

| Figure 1.4: | Schematic and band diagram of AlGaN/GaN 2DEG layer5                      |

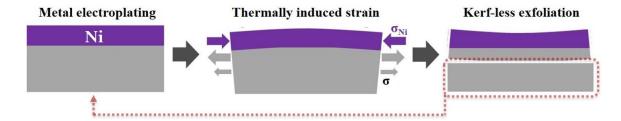

| Figure 1.5: | Schematic of kerf-less exfoliation process7                              |

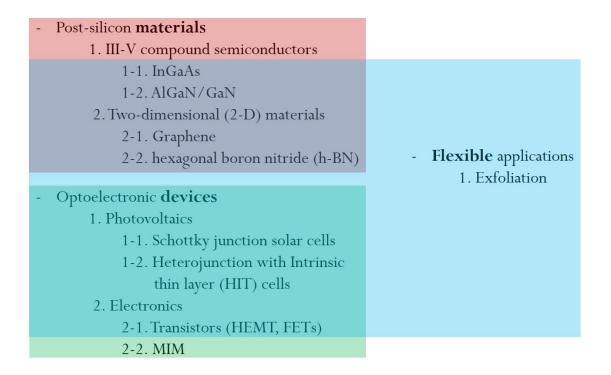

| Figure 1.6: | Graphic chart of this dissertation9                                      |

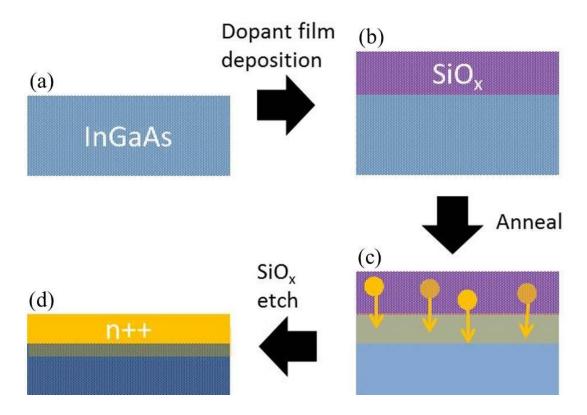

| Figure 2.1: | Schematic diagram of solid dopant based doping process12                 |

| Figure 2.2: | RBS measurement of $SiO_x$ deposited samples with differend gas flow     |

|             | rate13                                                                   |

| Figure 2.3: | I-V characteristics for InGaAs layer after SRSO and ORSO doping          |

|             | process. Inset shows the result from the untreated InGaAs as a reference |

|             | with a magnified scale15                                                 |

| Figure 2.4: | SIMS profile of (a) silicon and (b) oxygen for SRSO & ORSO treated       |

|             | 100 nm thick InGaAs samples16                                            |

| Figure 2.5: | (a) Sheet resistnace and active doping concentration of oxygen           |

|             | implanted InGaAs samples. (b) TOF-SIMS profile of oxygen implanted       |

|             | InGaAs sample17                                                          |

| Figure 2.6: | Illustration of vacancy formation and dopant diffusion in InGaAs .18     |

| Figure 3.1: | Electrical resisvity of various metal/Ga alloy and Gallium between 300   |

|             | and 500 (K) from literature survey                                       |

| Figure 3.2:  | Schematic of ideal/real case metal/InGaAs interface phenomenon and           |

|--------------|------------------------------------------------------------------------------|

|              | theoretical models for each case23                                           |

| Figure 3.3:  | AFM & Optical microscope image of indium contact after ultra-                |

|              | sonication24                                                                 |

| Figure 3.4:  | Schematic diagram and process flow of TLM fabrication25                      |

| Figure 3.5:  | Sheet and contact resistance of various TLM devices before and after         |

|              | annealing (10 mintue anneal)26                                               |

| Figure 3.6:  | TLM pad resistance as a function of pad spacing for various metal            |

|              | ohmic contacts on n-In53GaAs (30 nm)/InAlAs (130 nm)/InP with                |

|              | doping concentration of 3x10 <sup>19</sup> 26                                |

| Figure 3.7:  | Effect of indium thickness in indium (5, 10 nm)/Ti(30 nm) on InGaAs          |

|              | before and after annealing27                                                 |

| Figure 3.8:  | STEM image and EDS mapping of In, Ga, and As, elements. Brightness           |

|              | of the color is proportional to the counts of each element28                 |

| Figure 3.9:  | EDS of In (30 nm) before and after 400 °C anneal29                           |

| Figure 3.10: | SIMS profile of Ti (30 nm)/In (10 nm) on n-InGa <sub>53</sub> As30           |

| Figure 3.11: | HRXRD analysis of indium (30 nm) on n-InGa <sub>53</sub> As before and after |

|              | 300 °C and 400 °C anneal                                                     |

| Figure 3.12: | Schematic band diagram of In/ $In_{0.53}GaAs$ structure with (a) low (b)     |

|              | high temperature anneal. Diffusion depth may be ultra-shallow ( $10 \sim 30$ |

|              | Å)                                                                           |

| Figure 3.13: | HRTEM image of indium (30 nm)/InGaAs (a) before and (b) after 400            |

|              | °C annealing. Inter-mixing is oberserved at the interface                    |

| Figure 3.14: | Schematic diagrams of typical gate last MOSFETs fabrication. Indium          |

|              | and Mo were used and S/D contact metal                                       |

| Figure 3.15: | Summary of $V_g$ vs. I <sub>d</sub> characteristics in Gate late processed InGaAs  |

|--------------|------------------------------------------------------------------------------------|

|              | MOSFETs with indium (30 nm) or Mo (30 nm) source/drain contacts at                 |

|              | channel length of (a) L= 5 $\mu$ m, and (b) L= 10 $\mu$ m35                        |

| Figure 3.16: | Comparison of linear scaled drive current and transconductance                     |

|              | between In and Mo on InGaAs                                                        |

| Figure 3.17: | Source/drain contact resistance ( $R_{SD}$ ) & channel length offset ( $L_{off}$ ) |

|              | comparisons between (a) indium (30 nm) and (b) Mo (30 nm) on                       |

|              | InGaAs. R <sub>SD</sub> and L <sub>off</sub> were linearly extrapolated            |

| Figure 3.18: | Top: Photo image of after nickel electroplating and after exfoliation of           |

|              | GaAs. Bottom: Cross-sectional SEM image of exfoliated GaAs37                       |

| Figure 4.1:  | Exfoliation result of AlGaN/GaN 2DEG layer on silicon substrate and                |

|              | fabrication procedure of sample after exfoliation40                                |

| Figure 4.2:  | Top left: Image of AlGaN/GaN on bulk silicon. Right: Image of                      |

|              | AlGaN/GaN/c-Si on EVA sheet after exfoliation. Bottom : Hall                       |

|              | measurement result of bulk and exfoliated 2DEG layer41                             |

| Figure 4.3:  | L-edit image of final mask design as well as TLM and HEMT structure                |

|              |                                                                                    |

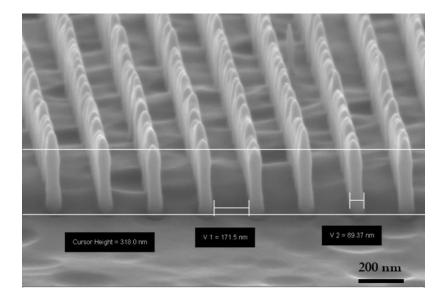

| Figure 4.4:  | Top: Cross sectional SEM image of AlGaN/GaN on silicon substrate                   |

|              | after 9 min etch at 100 W. Bottom: Cross sectional SEM image of                    |

|              | AlGaN/GaN on silicon substrate after nickel mask removal. AlGaN                    |

|              | surface is smooth after nickel etch45                                              |

| Figure 4.5:  | AFM scan of bare AlGaN/GaN before (top) process (average                           |

|              | roughness= 0.8 nm) after (bottom) ICP etch and nickel mask removal                 |

|              | (average roughness = 1.3 nm)46                                                     |

| Figure 4.6:  | Etch rate of GaN on Si and SiC using ICP etch                                      |

| Figure 4.7: | Specific contact resistivity of AlGaN/GaN layer for different |    |

|-------------|---------------------------------------------------------------|----|

|             | temperature and time by RTA                                   | 19 |

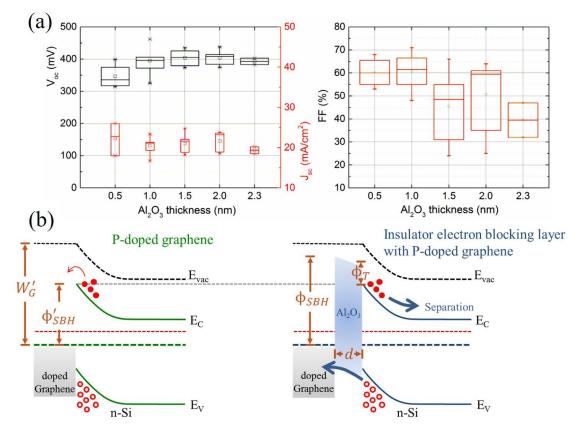

- Figure 5.3: (a) Schematic of GIS Solar cell fabrication process. For GS-SBSC, all is identical except excluding Al<sub>2</sub>O<sub>3</sub> layer deposition process. (b)

Photographic image of a completed GIS solar cell......60

| Figure 5.4: | (a) Qualitative energy band diagram of GS-SBSC with and without                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------|

|             | AuCl <sub>3</sub> doping. P-doped MLG creates a shift in potential resulting in                                 |

|             | improved cell performance. (b) J-V plot of un-doped MLG and pre-                                                |

|             | doped MLG with no interlayer oxide layer. (c) lnJ-V plot measured in                                            |

|             | dark with linear fit (solid lines) of the forward current for ideality factor                                   |

|             | and SBH extraction. (d) $dV/d(lnJ)$ -J plot for series resistance (R <sub>s</sub> )                             |

|             | extraction62                                                                                                    |

| Figure 5.5: | (a) $V_{OC}$ , $J_{SC}$ and FF versus $Al_2O_3$ thickness for GIS solar cells on                                |

|             | exfoliated silicon film. (b) Qualitative band diagram of GS cells with                                          |

|             | and without interlayer oxide                                                                                    |

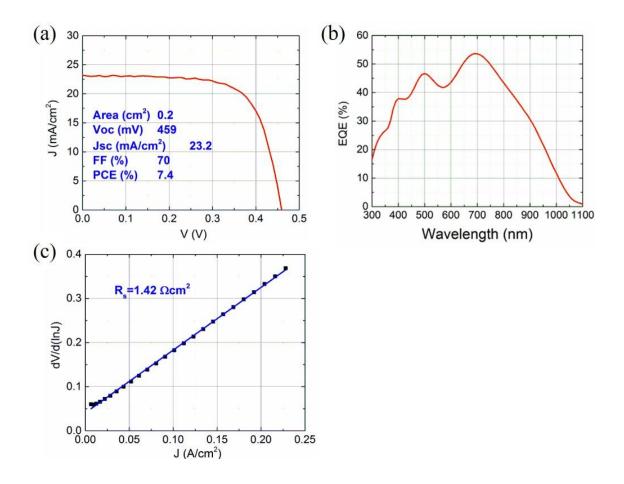

| Figure 5.6: | GIS cell performance (a) J-V and (b) EQE plots for optimized GIS                                                |

|             | device with 1 nm Al <sub>2</sub> O <sub>3</sub> insulator layer. (c) $n$ and R <sub>S</sub> extracted from dark |

|             | current in forward bias for the optimized GIS device68                                                          |

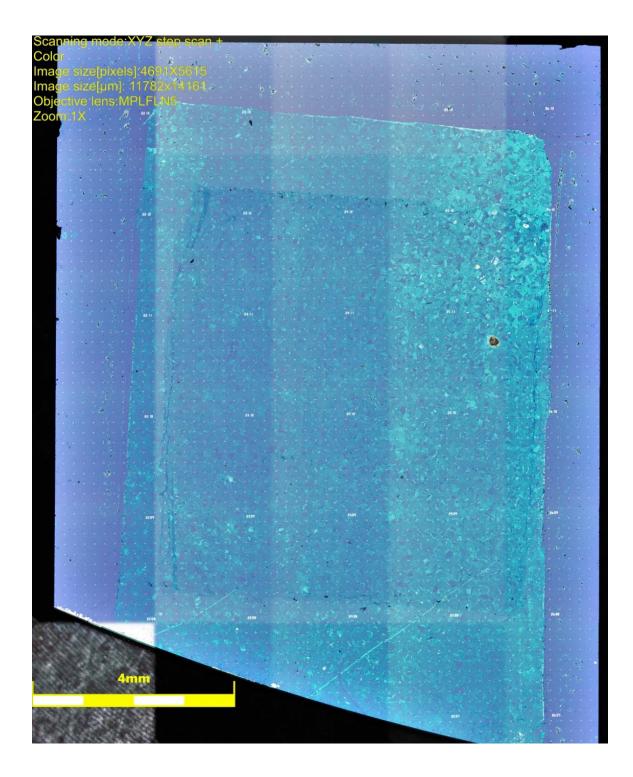

| Figure 6.1: | Laser optical image of CVD h-BN after transferring on to SiO <sub>2</sub> /Si                                   |

|             | substrate73                                                                                                     |

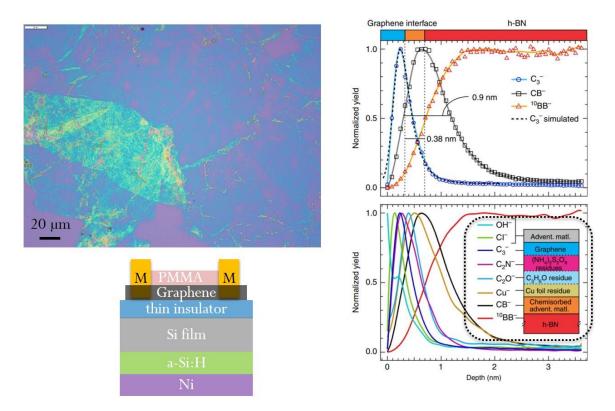

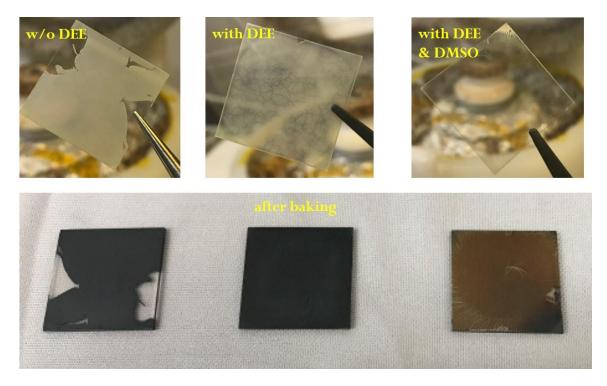

| Figure 6.2: | Top left: Optical image of CVD h-BN after wet transfer. Right: Vertical                                         |

|             | composition of transferred graphene/h-BN stack. Bottom left: Schematic                                          |

|             | of graphene/h-BN/silicon solar cell77                                                                           |

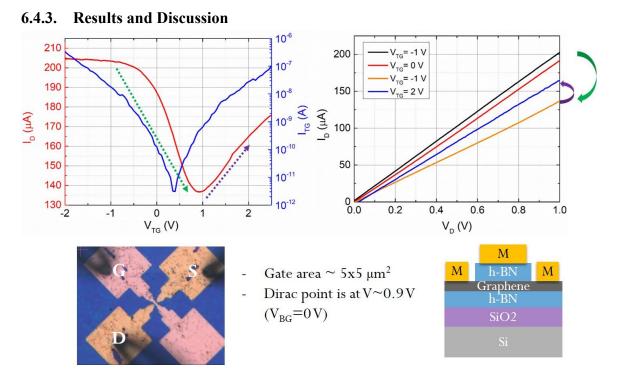

| Figure 6.3: | Top: $I_D/V_G$ and $I_D/V_G$ characteristic of graphene/h-BN FET. Bottom:                                       |

|             | Optical image and illustration of graphene/h-BN FET79                                                           |

| Figure 7.1: | Cross-sectional SEM image of InGAs fin                                                                          |

| Figure 7.2: | Difference in perovskite transparency by solvent engineering82                                                  |

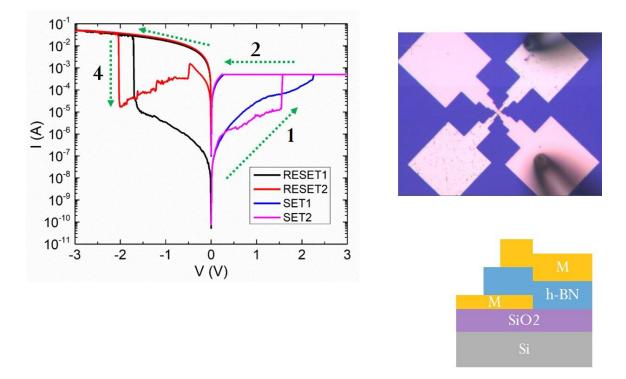

| Figure 7.3: | Resistive switching properties of thin h-BN grown by MOCVD83                                                    |

#### **Chapter 1.** Introduction

As of 2018, silicon is still the dominant material for both photovoltaic devices and electronic transistors. For integrated circuits, the leading semiconductor manufacturers such as Intel, Samsung and TSMC are fabricating transistors with a pitch of just 14 nanometers (nm) wide, which is less than 150 atoms. While advanced lithographic processes such as extreme ultraviolet lithography (EUVL) is making its debut, it is indeed no doubt that we are quickly running out of physical space for future scaling.

Figure 1.1. Best Research-Cell Efficiency graph by NREL [1]

As for silicon-based solar cells, according to reports from National Renewable Energy Laboratory (NREL), the power conversion efficiency (PCE) for silicon-based solar cells have shown an increase of less than 3 % during the last decade, which is shown in figure 1.1. [1]

For decades, extensive research has been made on finding alternative materials to replace silicon as well as new, innovative techniques to improve optoelectronic device performance.

In this dissertation, we investigate post-silicon candidate materials in various optoelectronic applications including field effect transistors (FETs), high electron mobility transistors (HEMT) and photovoltaics for efficient power conservation and generation.

1.1 III-V Compound Semiconductor: InGaAs

Figure 1.2. Electron and hole mobility of semiconductors including silicon, germanium and III-V compound semiconductors. [2]

InGaAs is a ternary III-V compound semiconductor which has been noticed as a potential replacement for silicon-based FETs due to its very high electron mobility ( $\mu_e$ ) compared to silicon. Figure 1.2. shows the mobility of various semiconductors and their lattice constants. [2] High mobility of InGaAs leads to high velocity which improves the performance of electronic devices. Also, high mobility compound semiconductors can reduce the device operating voltage without compromising the switching speed which can reduce the power dissipation or density as devices continue to scale down. [3]

#### 1.1.1 Challenges in Fin doping

Figure 1.3. Left: Schematic of Fin structure with ion implantation beam line, Middle, Right: Simulation result of doping profile of silicon fin with different implant energy, dose and beam angle. [4]

One of the key challenges for high quality transistors as it scales down is effectively doping the semiconductor to minimize parasitic resistances. Regarding semiconductor doping, ion implantation has been the dominant method of doping due to its precise controllability. However, as the scaling down continues, transistor architecture has shifted from a 2D planar structure to a tall, narrow 3D structure generally now referred to as "Fin". Unlike conventional planar structures, 3D structures such as Fin face challenges when doping with ion implantation. Due to it directionality, ion beams generate shadowing effects which result in non-uniform doping when doping an array of fins as illustrated in Figure 1.3. While studies have shown that tilting the beam angle can resolve doping uniformity for a single fin, the on-current (I<sub>on</sub>) for a single FinFET is too low for practical use which eventually requires an array of fins. [4]

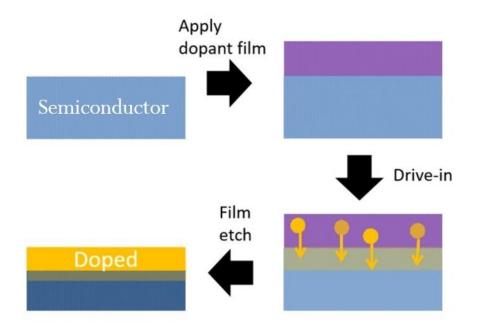

An alternative way of doping semiconductors is by diffusing the dopants through a thermal drive-in process which is illustrated in figure 1.4. While this method has been less

common compared to ion implantation, it has been reconsidered with various names such as 'solid source diffusion', 'spin-on-dopant' (SOD), 'monolayer doping' (MLD) and 'solid phase doping'.

Figure 1.4. Schematic diagram of semiconductor doping by thermal drive-in process.

#### 1.2 AlGaN/GaN Compound Semiconductor and 2DEG layer

Figure 1.5. Schematic and band diagram of AlGaN/GaN 2DEG layer.

GaN is binary III-V compound semiconductor with a wide band gap of 3.4 eV making it favorable for high power and frequency applications. While GaN was typically grown or deposited on silicon carbide (SiC), recently, it has been successfully grown on silicon, which triggered new interest in this semiconductor, due its compatibility with conventional CMOS processing and reduction in substrate cost.

A unique feature of this III-V semiconductor is that, it can form a two-dimensional electron gas (2DEG) when combined with other compound semiconductors such as AlGaN. Figure 1.5 illustrates the multi-layer III-V semiconductor structure to form such 2DEG and its band diagram. A buffer layer (AlN) is usually grown on top of bulk substrate followed by the GaN/AlGaN to form the 2DEG. This 2DEG is a layer of electrons which are free two travel parallel to the interface while simultaneously confined perpendicular to the sheet of electrons, making it quasi two-dimensional.

#### **1.3 Two-Dimensional Materials**

Graphene is a 2D material consisted of carbon atoms in a hexagonal lattice bonding structure. A monolayer of graphene is a zero band gap material with electron mobilities reaching over 100,000 cm<sup>2</sup>/V·s. Ever since the discovery of graphene by the famous 'scotch tape' method, extensive study on graphene along with other 2D materials have be conducted. [5]

Hexagonal boron nitride (h-BN) is another type 2D material in which boron and nitrogen atoms are bonded in a hexagonal array. While graphene is a semi-metal material, h-BN is a dielectric material with exceptional chemical stability, high mechanical flexibility, thermal conductivity and oxidation resistance gaining great interest. [6-7]

While exfoliated 2D materials generally show superior quality and device performance, its size limits from any practical applications. Thus, growing large area 2D materials by methods such as chemical vapor deposition (CVD) have also been extensive researched for various optoelectronic applications.

#### 1.4 Kerf-less Exfoliation of Semiconductors

Figure 1.6. Schematic of kerf-less exfoliation process.

Flexible optoelectronic devices have gained much interest from wearable devices to internet of things (IoT). Conventional bendable devices are made on flexible materials such as polymers, plastics or thin glass. For devices fabricated on semiconductor wafers, the common method is thinning down the silicon wafer through wet etching.

Recently, a mechanical exfoliation process of semiconductors which does not require semiconductor etch has been developed. [8] The process consists of depositing a metal layer (through electron beam evaporation and electroplating) on top of the semiconductor followed by a thermal cycling process. Thermally induced stress is created along the metal/semiconductor interface due to the thermal expansion mismatch between the two materials. When the amount of stress is properly controlled, the stress is kept within the interface. A crack is induced at the edge of the semiconductor wafer which results in the release of stress propagates along the semiconductor surface. By controlling the amount of stress, we can control the thickness of the exfoliated semiconductor thickness. Figure 1.6 illustrates the kerf-less exfoliation process. Some advantages of this technique are,

- This process can be applied to any semiconductors with the right exfoliation recipe.

- (2) The parent wafer can be re-used for fabrication or exfoliation.

- (3) The thickness of semiconductor film can be accurately controlled.

#### **1.5 Organization of Dissertation**

Figure 1.7. Graphic chart of this dissertation.

Figure 1.7 organizes the dissertation into three categories; materials, devices, and flexible applications. Materials are highlighted in red, devices in green and flexible applications of materials and devices are overlapped in blue.

This dissertation is consisted of 7 chapters, Chapter 2 and 3 covers InGaAs, which describes a new way of effectively doping the material as well as introducing a thin layer of indium between the InGaAs and metal contact pad to prevent the out-diffusion of indium during hot temperature processes.

GaN, which is another type of type of III-V compound semiconductor is described in chapter 4, focusing on exfoliation of AlGaN/GaN 2DEG and demonstration of HEMT devices.

Chapter 5, 6 covers 2D materials including graphene and h-BN and its application in bendable organic/inorganic solar cells, FETs and resistive switching applications.

Finally, Chapter 7 summarizes the work followed by future work regarding this dissertation.

### Chapter 2. Nanoscale Doping of Compound Semiconductors by Solid Phase Dopant Diffusion \*

#### **2.1.** INTRODUCTION

In the unceasing pursuit of scaling down semiconductor devices, high mobility compound semiconductors have gained great interest as future candidate materials beyond silicon [9-12]. To successfully develop devices in the post-silicon regime, effective doping of these compound semiconductors is essential. It is often more challenging to remove ion implantation-induced damage in compound semiconductors than in silicon due to incongruent evaporation during annealing, which leads to increased junction leakage and interferes with dopant activation [13-17]. In addition, there are challenges with ion implantation for doping of 3 dimensional (3-D) structures, such as fin field effect transistors (FinFETs), where shadowing effects of the ion beam result because ion implantation is a line-of-sight process. Such shadowing effects require changes in structure optimization for FinFETs, which, in turn, requires increases in process complexity, cost and time. To overcome these limitations, alternative doping strategies have been studied for compound semiconductors, such as monolayer doping (MLD), solid phase regrowth (SPR) and surface charge transfer doping [18-21].

In this chapter, we propose a novel method for solid phase doping of compound semiconductors, in this case InGaAs. With this method, we demonstrate that silicon or

<sup>\*</sup> This chapter is based on Reference: J. Ahn, H. Chou, D. Koh, T. Kim, A. Roy, J. Song, and S. K. Banerjee, Nanoscale doping of compound semiconductors by solid phase dopant diffusion. *Appl. Phys. Lett.*, **2016**, *108*, 122107. J.A., H.C. and T.K. designed the experiments (DOE), J.A. and D.K. carried out device fabrication, J.A, H.C, A.R, and J.S. conducted characterization of devices.

oxygen atoms from a deposited  $SiO_x$  layer on InGaAs can diffuse into InGaAs during postdeposition annealing, as illustrated in figure 2.1.

Figure 2.1: Schematic diagram of solid dopant based doping process.

#### 2.2. SAMPLE PREPARATION

The InGaAs samples were cleaned prior to deposition. The samples consist of GaAs (300 nm), InP (850 nm), InAlAs (300 nm) and  $In_{0.53}Ga_{0.47}As$  film (300 nm) grown on silicon substrates by molecular beam epitaxy (MBE). The deposition of SiO<sub>x</sub> films was carried out by plasma enhanced chemical vapor deposition (PECVD) at 285 °C and 900 mTorr with RF power of 30 W and various N<sub>2</sub>O/SiH<sub>4</sub> gas flow ratios [22]. The

samples were then annealed in a N<sub>2</sub> ambient for 10 minutes at 700 °C. The SiO<sub>x</sub> films were then etched off with HF and metal contacts (Mo/Ti/Au=20/40/100 nm) were immediately deposited on the InGaAs samples using electron beam evaporation patterned via metal shadow mask for electrical transport and Hall effect measurements.

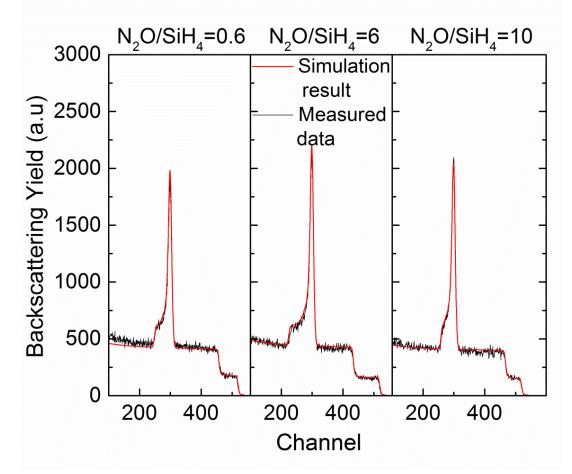

Figure 2.2: RBS measurement of SiO<sub>x</sub> deposited samples with different gas flow rate.

#### 2.3. Results and Discussion

Figure 2.2 shows the Rutherford backscattering spectrometry (RBS) analysis results for the various  $SiO_x$  films which were deposited on silicon substrates in parallel with the InGaAs films. RBS measurement was done with a NEC 6SDH-2 accelerator and ion

beam analysis system. In order to enhance the oxygen scattering cross-section,  $He^{2+}$  incident ions were used at an energy of 3.05 MeV. In addition, the RBS data was taken at a laboratory scattering angle of  $170^{0}$  with a detector of 14 keV nominal energy resolutions. These SiO<sub>x</sub> films used for characterization were deposited on silicon substrates that were put in the deposition chamber simultaneously with InGaAs film substrates. From the RBS measurements, we were able to determine the composition and thickness of each SiO<sub>x</sub> film. The RUMP code was used for quantitative analysis of the measured RBS spectra [23]. Table I summarizes the Si –to-O ratio for three different gas flow deposition conditions. Depending on the gas flow ratio, the deposited SiO<sub>x</sub> films resulted in silicon rich silicon oxide (SRSO, SiO<sub>x</sub>, x<2) or oxygen-rich silicon oxide (ORSO, SiO<sub>x</sub>, x>2) [24].

|                                         | Elemen  | nt ratio |

|-----------------------------------------|---------|----------|

| N <sub>2</sub> O/SiH <sub>4</sub> ratio | Silicon | Oxygen   |

| 0.6                                     | 1       | 0.6      |

| 6                                       | 1       | 6        |

| 10                                      | 1       | 10       |

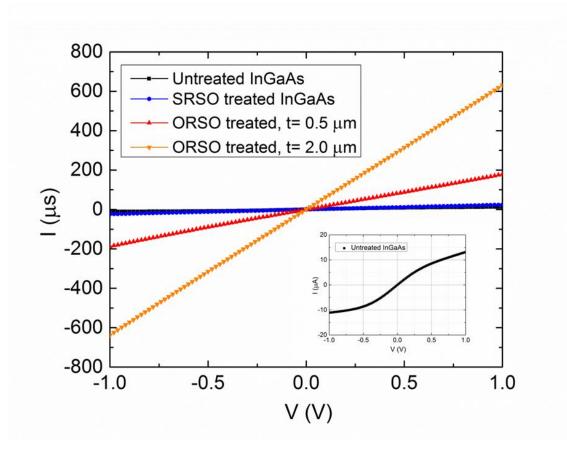

In order to verify the doping efficacy of our technique, current-voltage measurements were made for InGaAs samples doped by SRSO and by ORSO. Figure 2.3 shows the I-V characteristics in the InGaAs layer after SiO<sub>x</sub> film deposition, annealing and etch. A higher doping level was obtained with ORSO compared to SRSO.

Figure 2.3: I-V characteristics for InGaAs layer after SRSO and ORSO doping process. Inset shows the result from the untreated InGaAs as a reference with a magnified scale.

In addition, the current in InGaAs from the ORSO-deposited sample was two orders of magnitude higher in comparison to the SRSO-deposited sample, when the thickness of the ORSO and SRSO films were similar. When a thicker (2  $\mu$ m) ORSO film was deposited (compared to the thinner, 0.5  $\mu$ m, film), the current flow in the InGaAs layer was three times greater than in the current in the thinner ORSO film. These results indicate that oxygen in-diffusion is related to InGaAs doping.

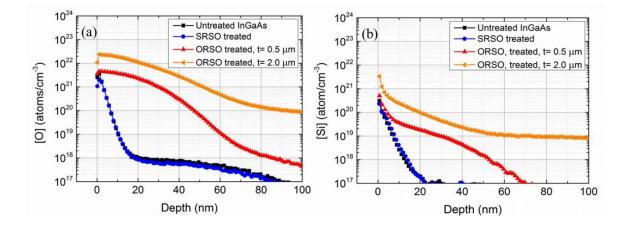

Figure 2.4: SIMS profile of (a) silicon and (b) oxygen for SRSO & ORSO treated 100 nm thick InGaAs samples.

Figure 2.4 shows the secondary ion mass spectrometry (SIMS) depth profiling results for the InGaAs layers after doping. The analysis shows that (1) more oxygen than silicon is incorporated in the InGaAs and (2) the oxygen concentration is further increased in the InGaAs layer with a thicker ORSO film. This is consistent with the findings from the I-V measurements. To confirm the role of oxygen inside InGaAs, ion implantation was conducted for comparison. 20 keV oxygen ions were implanted into InGaAs at three different doses (3x10<sup>13</sup>, 3x10<sup>14</sup> and 3x10<sup>15</sup> cm<sup>-2</sup>), giving an implant depth of 41 nm [25]. Following implantation, the samples were capped with 20 nm of Al<sub>2</sub>O<sub>3</sub> by atomic layer deposition (ALD) and annealed with the same conditions as the SiO<sub>x</sub> treated samples. A control InGaAs sample was deposited with Al<sub>2</sub>O<sub>3</sub>, annealed, and etched to remove Al<sub>2</sub>O<sub>3</sub>, and tested as a control to confirm that the Al<sub>2</sub>O<sub>3</sub> capping layer does not play any role in InGaAs doping.

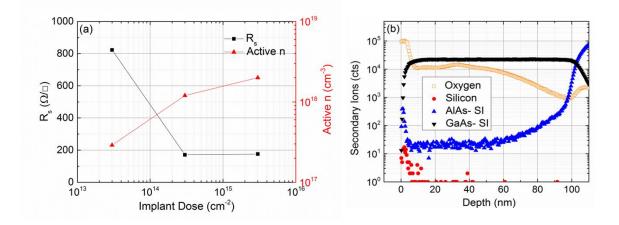

Figure 2.5: (a) Sheet resistance and active doping concentration of oxygen implanted InGaAs samples. (b) TOF-SIMS profile of oxygen implanted InGaAs sample.

Figure 2.5(a) shows that there is an increase in active dopant concentration in oxygen-implanted samples in proportion to oxygen dose, and a reduction in sheet resistance. To show that ion implantation did not otherwise alter the structure of the InGaAs sample, depth profiles of the oxygen-implanted InGaAs samples were taken with time-of-flight SIMS (TOF-SIMS) as shown in Figure 2.5 (b). The depth profiles show that no silicon or other out-diffusion of underlying layers occurred to impact the InGaAs film. This indicates that oxygen indeed appears to act as an n-type dopant at active dopant concentrations that have not been reported to date. The SIMS depth profile shows the dopant distribution with respect to depth, whereas the current-voltage measurement reflects an average dopant concentration. The InGaAs sample doped with thick ORSO film showed an active doping concentration of  $1.4 \times 10^{18}$  cm<sup>-3</sup>, which is comparable to other doping methods including ion implantation.

Figure 2.6: Illustration of vacancy formation and dopant diffusion into InGaAs.

It has been previously reported that an increase in compressive stress within a GaAs substrate can generate vacancies via enhanced gallium diffusion and arsenicantisite defects [26-27]. This extrinsic stress occurs because of the difference in the coefficient of thermal expansion (CTE) between SiO<sub>2</sub> ( $0.55 \times 10^{-6} \text{ K}^{-1}$ ) and GaAs ( $6.86 \times 10^{-6} \text{ K}^{-1}$ ). Similarly, vacancies can be formed due to the thermal stress between SiO<sub>x</sub> and InGaAs in the InGaAs substrate (figure 2.6(b)). In addition, the amount of vacancies generated within InGaAs is greater in the thicker ORSO ( $2 \mu m$ ) than in the thinner ORSO ( $0.5 \mu m$ ). This is because increasing the film thickness generates more stress, which leads to an enhancement of the vacancy formation phenomenon. This, in turn, increases the probability for dopants to diffuse into InGaAs (figure 2.6(c)). In addition to the conventional annealing temperature and time process parameters, our method provides an additional parameter available to control doping (i.e. solid source film thickness and stoichiometry). The high concentration of oxygen compared to silicon inside InGaAs can be understood by considering the diffusivity of each element, which is dictated by an Arrhenius relation. Oxygen has a lower activation energy for diffusion ( $E_A$ = 1.1 eV) compared to silicon ( $E_A$  =2.2~2.8 eV) in GaAs, an analogue of InGaAs [28]. In the case that oxygen has a lower energy barrier for diffusion into InGaAs, it allows a higher doping concentration at a given temperature.

Oxygen impurities in III-V semiconductors have typically been considered as contaminants that create energy levels near mid-gap [29-32]. However, oxygen has also been shown to increase the free carrier density in GaAs and InGaAs in some cases, presumably due to differences of the where the oxygen sits in the lattice and how it affects the bandstructure [32-34]. Although the fundamental mechanism of how oxygen acts as a dopant was not elucidated in our work, the use of ORSO demonstrates a new approach for effectively doping III-V compound semiconductors. It also points out a potential unintentional doping effect when applying silicon processes to compound semiconductors, such as for silicon dioxide-based device isolation. While this isolation method is effective for conventional silicon-based technology, unintended doping can occur for compound semiconductors during a similar process steps and can negatively affect device performance.

#### 2.4. Conclusion

In conclusion, we were able to demonstrate a simple technique for doping compound semiconductors through PECVD SiOx. As oxygen has a lower activation energy for diffusion, it diffuses more easily than silicon into InGaAs, leading to n-type doping. This solid phase doping method can be applied to other semiconductors by choosing appropriate films. Our method provides an alternative way to overcome one of the challenges of doping compound semiconductors, such as InGaAs.

# Chapter 3. Low Contract Resistivity Indium Metal Contacts on InGaAs and GaAs exfoliation

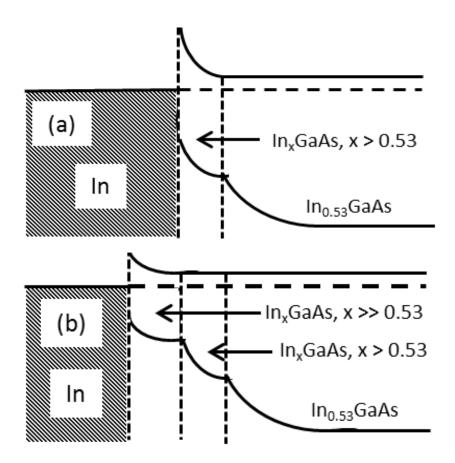

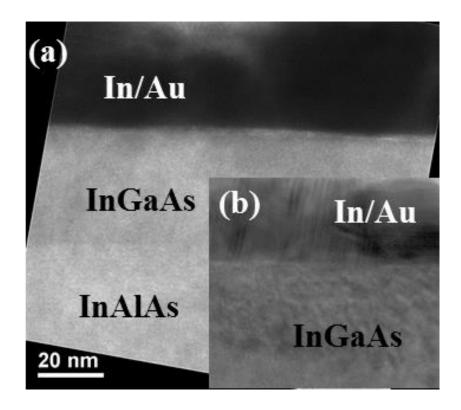

In this chapter, we studied the interfacial characteristics, electrical properties, and thermal stability of indium ohmic contacts on n-type In<sub>0.53</sub>GaAs. TEM, XRD, SIMS and EDS analysis show ultra-shallow diffusion of indium into In<sub>53</sub>GaAs layer after annealing and formation of higher indium concentrated thin In<sub>x</sub>GaAs (x > 0.53) phases at the indium/In<sub>53</sub>GaAs interface. Electrical measurements of TLM patterns and InGaAs MOSFETs show indium contacts ( $8 \times 10^{-7} \Omega \cdot cm^2$ ) are comparable to Mo ( $3.2 \times 10^{-6} \Omega \cdot cm^2$ ) based devices even after annealing temperatures of 400 °C. A thin layer of GaAs, an analogue of InGaAs, was successfully spalled using the kerf-less mechanical exfoliation technique.

#### **3.1. INTRODUCTION**

One major challenge in achieving high performance III-V MOSFETs is minimizing the parasitic resistance, including metal/semiconductor contact resistance.

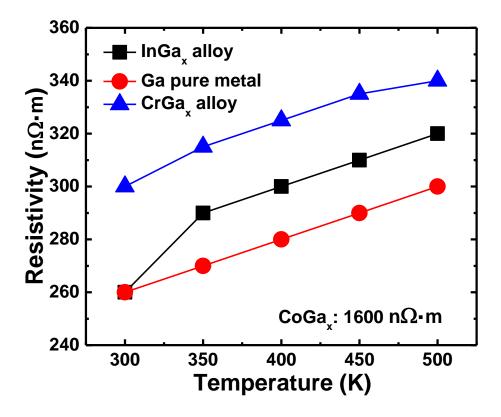

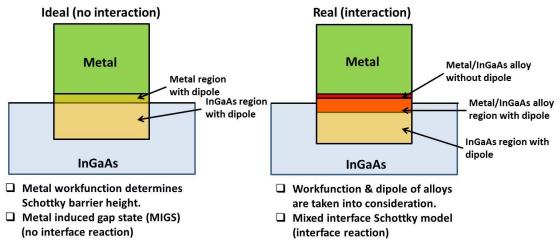

One cause of increased contact resistance for metal/InGaAs is the out-diffusion of gallium at elevated temperatures which form gallium-based alloys with high resistivity. [34] Therefore, low resistivity of metal/Ga alloy is needed. From literature survey, indium/Ga alloy have lower resistivity compared with other Ga based alloys and equal resistivity with Gallium which is plotted in Fig 3.1. [35] Fig 3.2 describes the ideal and practical models of metal/semiconductor interface characteristics. Applying inter-diffusion, strong chemical reactions and formation of new metallurgical compounds, the mixed interface Schottky model is considered for detailed understanding of metal-InGaAs interface. To achieve low contact resistivity based on the mixed interface Schottky model, low workfunction,

electronegativity and electrical resistivity are required. From these conditions, indium, (electronegativity: 1.78, workfunction: 4.12 eV, electrical resistivity: 83 n $\Omega$ ·m) is a suitable candidate.

Figure 3.1: Electrical resistivity of various metal/Ga alloy and Gallium between 300 and 500 (K) from literature survey.

Fig 3.2: Schematic of ideal/real case metal/InGaAs interface phenomenon and

theoretical models for each case.

# **3.2.** EXPERIMENTAL

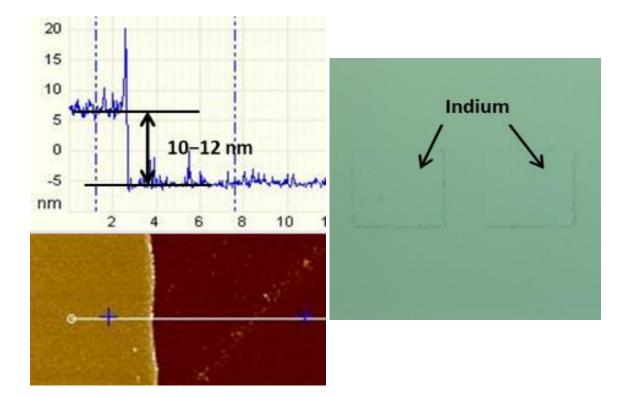

Figure 3.3: AFM & Optical microscope image of indium contact after ultrasonication.

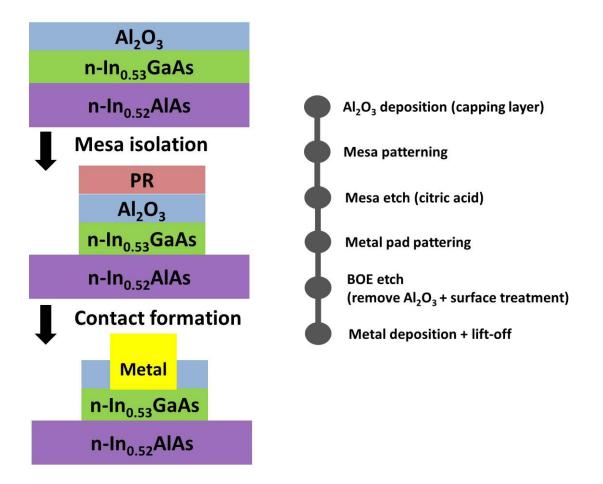

Figure 3.4: Schematic diagram and process flow of TLM fabrication.

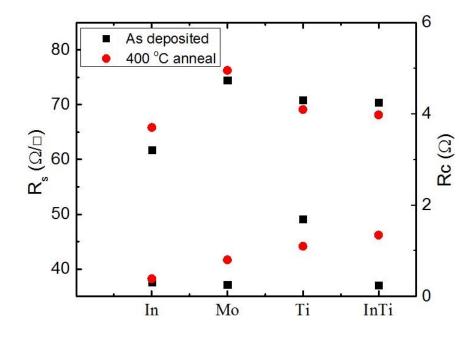

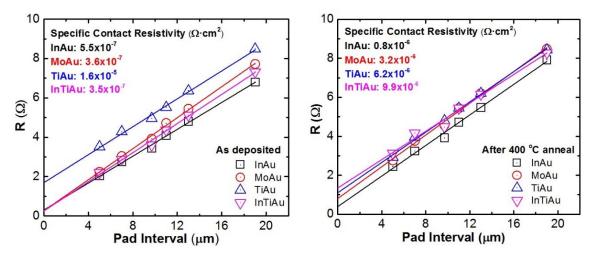

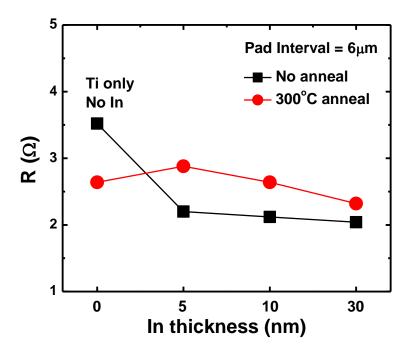

AFM and optical images in Fig. 3.3 show that  $10 \sim 12$  nm of indium remains intact after e-beam evaporation, followed by 10 min, ultra-sonication. Fig. 3.4 describes the schematic for TLM pattern fabrication. 30 nm thickness of gold is used as pad metal for probing the TLMs and MOSFETs. Indium contacts show good thermal stability of resistance, comparable with Mo and Ti, after 400°C annealing. (Fig. 5) In Fig. 3.6, indium contact shows lower specific contact resistivity ( $\rho_c$ ) than Mo after 400°C annealing. Optimization of surface treatment can further lower  $\rho_c$ . Indium contacts with various thicknesses do not show any significant degradation with Ti in Fig. 3.7.

Figure 3.5: Sheet and contact resistance for various TLM devices before and after annealing (10 minute anneal).

Figure 3.6: TLM pad resistance as a function of pad spacing for various metal ohmic contacts on n-In<sub>53</sub>GaAs (30 nm)/InAlAs (130 nm)/InP with doping concentration of  $3 \times 10^{19}$ .

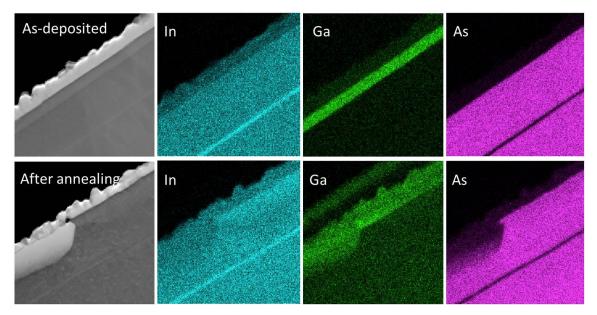

Fig. 3.8 shows STEM image and EDS mapping results of indium TLM devices before and after annealing. The color brightness is proportional to the number of counts during EDS mapping. From Fig 8, the interface of indium/InGaAs became uneven after annealing, which indicates the inter-mixing. And Ga is diffused out to the metal contact while arsenic shows distinct boundaries. The trench in TEM is the area of mesa etch, not any result of metal diffusion. Fig. 3.9 shows the EDS line scan result of the two samples, which further supports the increase of indium content after annealing. The color brightness of each image is proportional to the counts of each element.

Figure 3.7: Effect of indium thickness in indium (5, 10 nm)/Ti(30 nm) on InGaAs before and after annealing.

Figure 3.8: STEM image and EDS mapping of In, Ga, and As, elements. Brightness of the color is proportional to the counts of each element.

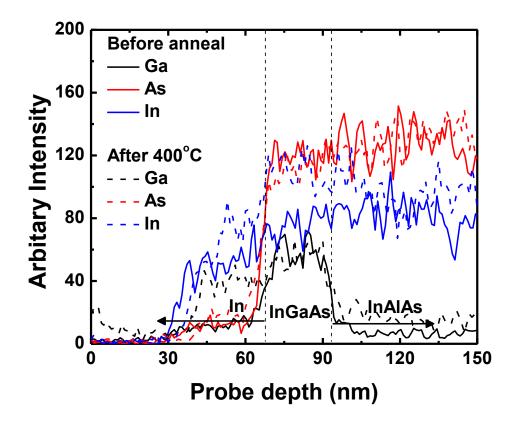

Figure 3.9: EDS of In (30 nm) before and after 400°C anneal.

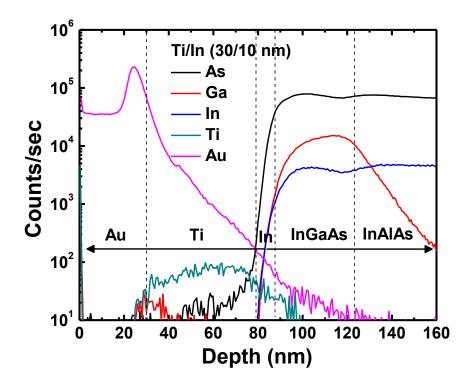

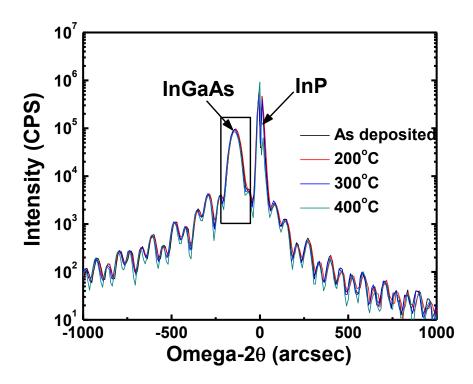

Fig 3.10 is SIMS analysis of Ti/indium on InGaAs. Indium/InGaAs boundary is not discernible, which may indicate the interfacial reaction of indium/InGaAs. HRXRD analysis of indium (30 nm) before and after 300, 400°C annealing (Fig. 3.11) show minute change of InGaAs signal (all InP signals are aligned), which indicates ultrashallow diffusion depth of the increased indium concentration on  $In_{0.53}GaAs$  after annealing. (The change of indium concentration was simulated using Bede RADS and shows that indium inside InGaAs increased from 53% to 60% with roughly 10 ~ 30 Å diffusion depth with limited fitting accuracy.) And indium diffusion was reported in which indium diffuses into GaAs with anneal [36]. Fig 3.12 illustrates the schematic band diagram of indium/In<sub>0.53</sub>GaAs structure before and after annealing, deduced from EDS analysis and literature.

Figure 3.10: SIMS profile of Ti (30 nm)/In (10nm) on n-In<sub>53</sub>GaAs.

Figure 3.11: HRXRD analysis of indium (30 nm) on n-In<sub>53</sub>GaAs before and after 300°C and 400°C anneal.

Figure 3.12: Schematic band diagram of In /  $In_{0.53}GaAs$  structure with (a) low (b) high temperature anneal. Diffusion depth may be ultra-shallow (10 ~ 30Å).

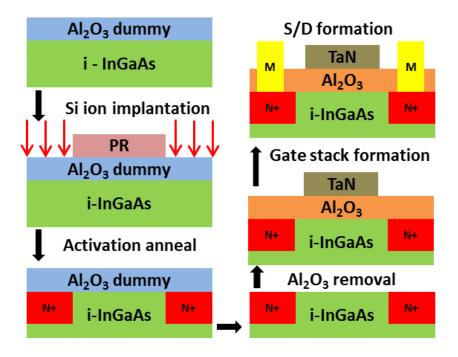

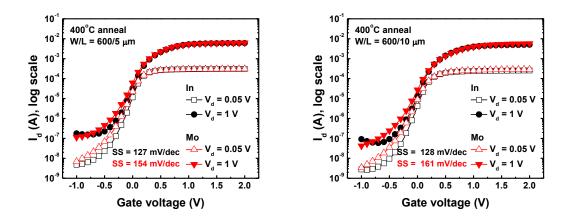

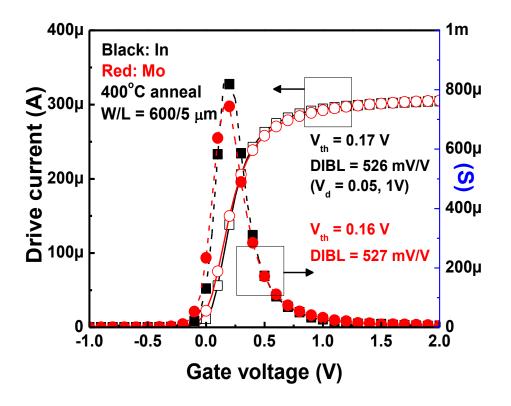

TEM analysis (Fig. 3.13) shows inter-mixing at the interface of indium/InGaAs before and after 400°C annealing. Fig 3.14 describes the fabrication process of gate-last MOSFET fabrication used in this study (Si ion implantation at 35 keV,  $5 \times 10^{14}$ /cm<sup>2</sup>, activation temperature at 700°C 10sec). Post deposition anneal (PDA) was conducted at temperature 400 °C to reduce the interface trap density (D<sub>it</sub>) of Al<sub>2</sub>O<sub>3</sub>. Fig. 3.15 is a summary of V<sub>g</sub> vs. I<sub>d</sub> characteristics in gate-last processed InGaAs MOSFETs with indium (30 nm)/Au (30 nm) or Mo (30 nm)/Au (30 nm) source/drain contacts at channel length of (a) L = 5 µm and (b) L = 10 µm. Indium contacts show similar drive current at

various channel lengths, compared with that of Mo, consistent with TLM results. Slightly higher subthreshold swing of Mo may be due to the change of surface morphology, caused by high energy transfer from Mo to InGaAs. Utilizing sputtering instead of e-beam evaporation may avoid this issue. V<sub>th</sub> and DIBL are also similar between indium and Mo contacts in Fig. 3.16. Source/drain contact resistance (R<sub>SD</sub>) and channel length offset (L<sub>off</sub>) for (a) indium and (b) Mo in Fig. 3.17 were linearly extrapolated from the results of Fig. 3.15. Indium and Mo contacts show the same R<sub>SD</sub>, but Mo clearly shows higher value of L<sub>off</sub>. Higher thermal energy required for Mo during e-beam evaporation may have impacted the lateral diffusion of Si dopants, compared with indium.

Figure 3.13: HRTEM image of indium (30 nm)/InGaAs (a) before and (b) after 400°C annealing. Inter-mixing is observed at the interface.

Figure 3.14: Schematic diagrams of typical gate last MOSFETs fabrication. Indium and Mo were used as S/D contact metal.

Figure 3.15: Summary of  $V_g$  vs.  $I_d$  characteristics in Gate last processed InGaAs MOSFETs with indium (30 nm) or Mo (30 nm) source/drain contacts at channel length of (a)  $L = 5 \mu m$  and (b)  $L = 10 \mu m$ .

Figure 3.16: Comparison of linear scaled drive current and transconductance between In and Mo on InGaAs.

Figure 3.17: Source/drain contact resistance  $(R_{SD})$  & channel length offset  $(L_{off})$  comparisons between (a) indium (30 nm) and (b) Mo (30 nm) on InGaAs.  $R_{SD}$  and  $L_{off}$  were linearly extrapolated.

#### **3.3. KERF-LESS EXFOLIATION OF GAAS**

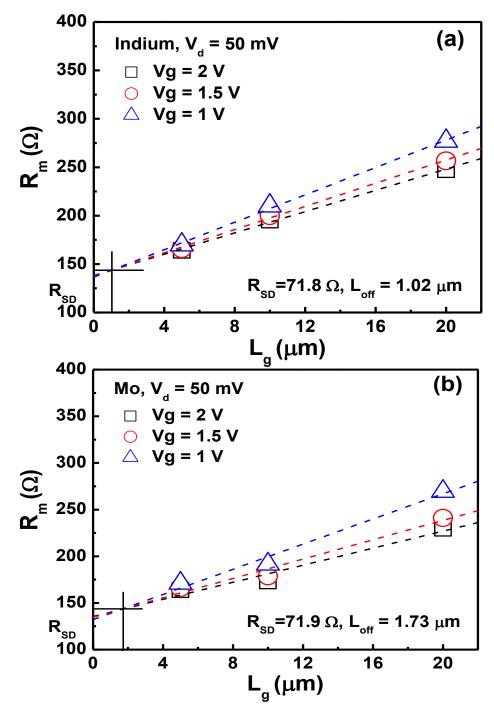

Figure 3.18: Top: Photo image of after nickel electroplating and after exfoliation of GaAs. Bottom: Cross-sectional SEM image of exfoliated GaAs.

Figure 3.18 shows the exfoliated result of GaAs sample. The exfoliation procedure is similar to the explanation in chapter 1. The nickel thickness and the thermal cycling condition were optimized to exfoliate GaAs which is an analogue of InGaAs. An interesting aspect of GaAs exfoliation is that the exfoliated surface showed a zig-zag shape regardless of the exfoliation recipe for successfully exfoliated samples. This represents that the zig zag surface is related to the material properties of GaAs. While the exfoliated surface may have limitations in applications due to it rough surface, utilizing the nickel contact side through pre-process before exfoliation followed by nickel removal can be applied for bendable electronic and photovoltaic devices. This method will be demonstrated in detail in the following chapter.

#### **3.4.** CONCLUSION

For the first time, we have studied the interface characteristics, electrical properties, and thermal stability of indium ohmic contacts on n-type In<sub>0.53</sub>GaAs. TEM, SIMS and EDS analysis show inter-mixing at the interface and the increase of indium content after annealing, resulting in the formation of ultra-shallow In<sub>x</sub>GaAs (x > 0.53) phases on In<sub>0.53</sub>GaAs which may contribute to the lower specific contact resistivity of indium (8 × 10<sup>-7</sup>  $\Omega \cdot cm^2$ ), comparable with Mo contacts (3.2 × 10<sup>-6</sup>  $\Omega \cdot cm^2$ ). Gate-last process MOSFET data show similar drive current, R<sub>sd</sub> and lower L<sub>off</sub> making indium contact a potential candidate for high performance InGaAs FET devices. Finally, kerf-less exfoliation of GaAs was successfully demonstrated.

# Chapter 4. Demonstration of Bendable AlGaN/GaN 2DEG layer on silicon and HEMT fabrication

## 4.1. INTRODUCTION

AlGaN/GaN based III-V semiconducting heterostructures have brought great interest due to their unique properties of two-dimensional electron gas (2DEG) at the interface. At this interface, the electron movement is confined in one dimension and free from impurity scattering. This allows such III-V materials to fabricate high electron mobility transistors (HEMTs) which is suitable for applications in high-power and highfrequency electronic devices used in various fields such as wireless communications, light emitting devices (LEDs), and photodetectors.

In this chapter, kerf-less mechanical exfoliation of AlGaN/GaN 2DEG layer grown on silicon substrate is conducted. Experimental results show that the high mobility layer is maintained after exfoliation. Next, demonstrations of fabricating AlGaN/GaN HEMTs is presented. Finally, comparison of exfoliating multi-layer structures to single layer are discussed.

## 4.2. EXFOLIATION OF ALGAN/GAN 2DEG LAYER ON SILICON SUBSTRATE

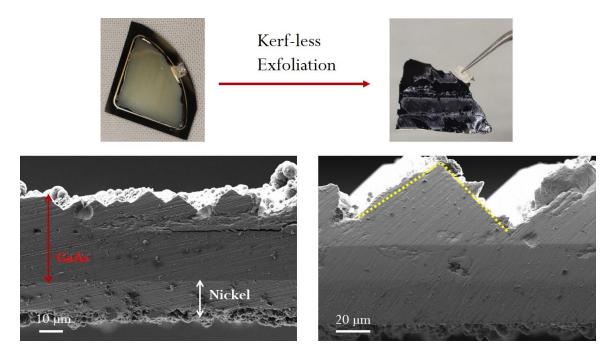

Figure 4.1. Exfoliation result of AlGaN/GaN 2DEG layer on silicon substrate and fabrication procedure of sample after exfoliation.

AlGaN/GaN 2DEG layer is grown on <111> silicon substrate. The growth starts off with growing 50 nm of AlN layer on top of silicon. This layer is referred to as the nucleation layer; this layer is to mitigate stress as well as to avoid cracking of the top AlGaN/GaN layer. [37] Next, 1.7 um of GaN and 25 nm of AlGaN is grown to create the 2DEG layer. The exfoliation process of AlGaN/GaN on silicon substrate is similar to GaAs which was explained in chapter 3.4. After exfoliation, the Ni/Ti/AlGaN/GaN/Si foil was

cut and patched to an ethylene-vinyl acetate (EVA) sheet. Detailed process after exfoliation as well as exfoliated result is shown in figure 4.1.

To check if the 2DEG layer was affected during the exfoliation process, hall measurement was conducted on both bulk and exfoliated sample.

|                                                                | Bulk<br>sample          | Exfoliated sample       |

|----------------------------------------------------------------|-------------------------|-------------------------|

| Sheet resistance $(R_s, \Omega/\Box)$                          | 469                     | 1056                    |

| Sheet<br>Concentration<br>(n <sub>s</sub> , cm <sup>-2</sup> ) | 0.98 x 10 <sup>13</sup> | 0.97 x 10 <sup>13</sup> |

| Hall mobility<br>(μ, cm²/V·s)                                  | 1353                    | 608                     |

Figure 4.2. Top left: Image of AlGaN/GaN on bulk silicon. Right: Image of AlGaN/GaN/c-Si on EVA sheet after exfoliation. Bottom: Hall measurement result of bulk and exfoliated 2DEG layer.

Fig 4.2 shows the bulk and exfoliated AlGaN/GaN on silicon samples and their hall measurement results. The same sheet concentration implies that the 2DEG was not affected even after exfoliation. The high sheet resistance on exfoliated samples could be due to higher contact resistance between the AlGaN and metal pad.

## 4.3. Demonstration of AlGaN/GaN HEMT on Silicon Substrate

#### 4.3.1. Photomask drawing for HEMT structure

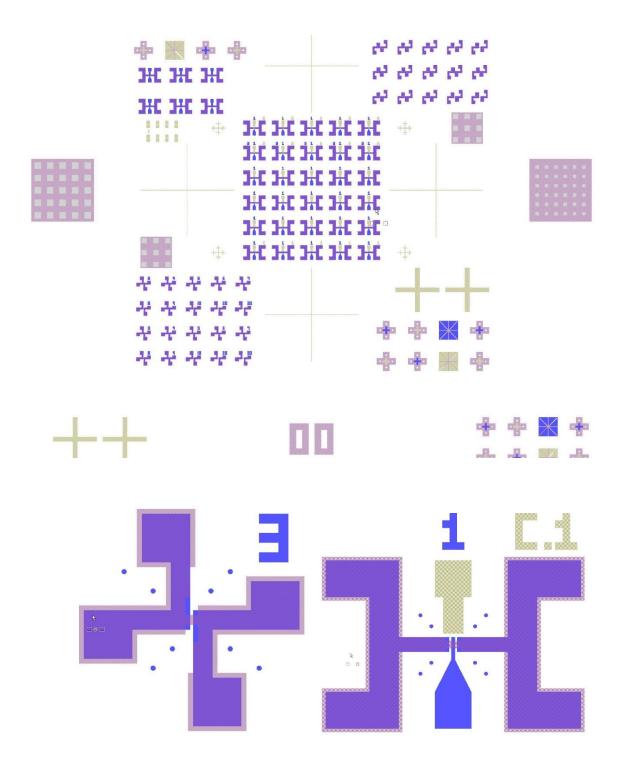

To fabricate AlGaN/GaN HEMT, a series of photomasks were first drawn using Ledit program which is shown in Fig 4.3. A number of features that were considered during drawing list as follows.

- (1) Structures such as HEMT, TLM, Hall measurement, SOLT (for RF testing) were included in the photomask.

- (2) Source/drain pads were drawn to accommodate both 100 & 150 um pitch probes for RF measurement.

- (3) Alignment marks were drawn to accommodate MA6, MJB4, Raith & Jeol lithography tools inside cleanroom.

- (4) Gate length variations of 0.3 um to 5 um were inserted to investigate gate length effect as well as to consider future potential mask use with only photolithography.

Figure 4.3. L-edit image of final mask design as well as TLM and HEMT structure.

#### 4.3.2. AlGaN/GaN etch and channel definition

To fabricate AlGaN/GaN HEMT, we start off by defining the 2DEG channel layer. This process requires lithography and etch of AlGaN/GaN layer. After cleaning the AlGaN surface with acetone and IPA, a thin layer of SiO<sub>2</sub> (PECVD, 27 nm) is deposited. This SiO<sub>2</sub> layer serves as a barrier so that the AlGaN surface does not come in direct contact with the photoresist as well as a barrier for nickel etchant. Next, photolithography of channel pattern followed by nickel deposition (200 nm, e-beam evaporation) and lift-off (overnight in acetone) is conducted. Before etching AlGaN/GaN, the sample is dipped in BOE for 20 secs to remove the SiO<sub>2</sub> layer. AlGaN/GaN layer is etched using the Oxford ICP. The ICP etch recipe for GaN is 2 sccm of BCl<sub>3</sub>, 20 sccm of Cl<sub>2</sub>, 20 °C tested at 50 W & 100 W respectively.

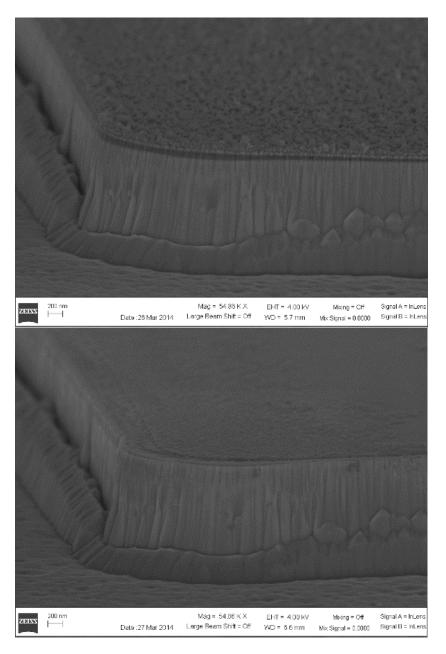

Figure 4.4. Top: Cross sectional SEM image of AlGaN/GaN on silicon substrate after 9 min etch at 100 W. Bottom: Cross sectional SEM image of AlGaN/GaN on silicon substrate after nickel mask removal. AlGaN surface is smooth after nickel etch

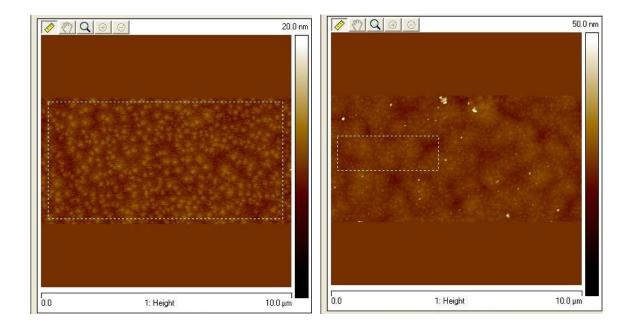

Figure 4.5. AFM scan of bare AlGaN/GaN before(left) process (average roughness= 0.8 nm) after (right) ICP etch and nickel mask removal (average roughness = 1.3 nm)

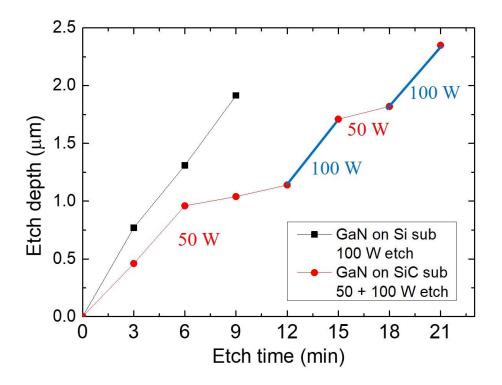

Figure 4.6. Etch rate of GaN on Si and SiC using ICP etch.

GaN etch rate was defined by measuring the etched thickness using the profilometer. Fig 4.6 shows the etch rate of GaN for 50 W and 100 W conditions. Since the thickness of GaN is 1.7 um, 9 min etch at 100 W was enough to fully etch GaN and thus prevent any parasitic current path. After etching, nickel is removed by dipping sample in nickel etchant followed by BOE to remove SiO<sub>2</sub>. Fig 4.4 and 4.5 shows the crosssectional SEM image of etched AlGaN/GaN layer before and after nickel removal as well as the AlGaN surface roughness measured by AFM.

#### 4.3.3. Specific Contact Resistivity of AlGaN/GaN layer

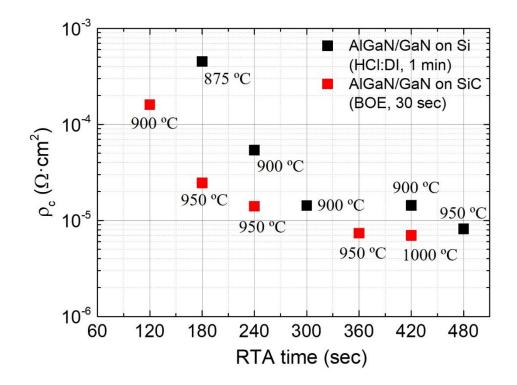

To fabricate AlGaN/GaN HEMT, achieving high quality ohmic contact, at the source and drain region is required. To achieve such low resistance, Ti/Al metallization method is generally performed. [38-40] This method involves depositing Ti/Al on AlGaN surface followed by high temperature annealing, which results in an alloy form of Ti/Al and AlGaN/GaN showing low resistance. To minimize the oxidation of Al during the annealing step, metals such as Ni, Ti, Pt and Mo are overlaid on top of Ti/Al. [41-47]. To measure the contact resistivity of etched AlGaN/GaN layer, a TLM structure is fabricated by defining contacts with different channel length. Photolithography followed by metal lift-off of with Ti/Al/Ni/Au = 20/100/40/100 nm was conducted. To achieve ohmic contact, TLM sample was annealed in a rapid thermal annealing (RTA) system starting from 800 °C for 60 secs in N<sub>2</sub> ambient. Fig. 4.7 plots the specific contact resistivity values after annealing at different temperatures and time. Results show that ohmic contact is achieved after annealing at 900 °C. To further reduce the contact resistance for high quality HEMT, extracting the specific contact resistivity at higher temperatures were conducted. Fig 4.7 shows the specific contact resistivity of AlGaN/GaN layer on both silicon and silicon carbide after annealing beyond 900 °C. Both samples showed resistivity decrease over a magnitude when annealing time and temperature was increased and reached as low as  $8 \times 10^{-1}$  $^{6}$  ohm cm<sup>2</sup>.

Figure 4.7. Specific contact resistivity of AlGaN/GaN layer for different temperature and time by RTA.

# 4.3.4. I-V Characteristics of AlGaN/GaN HEMT

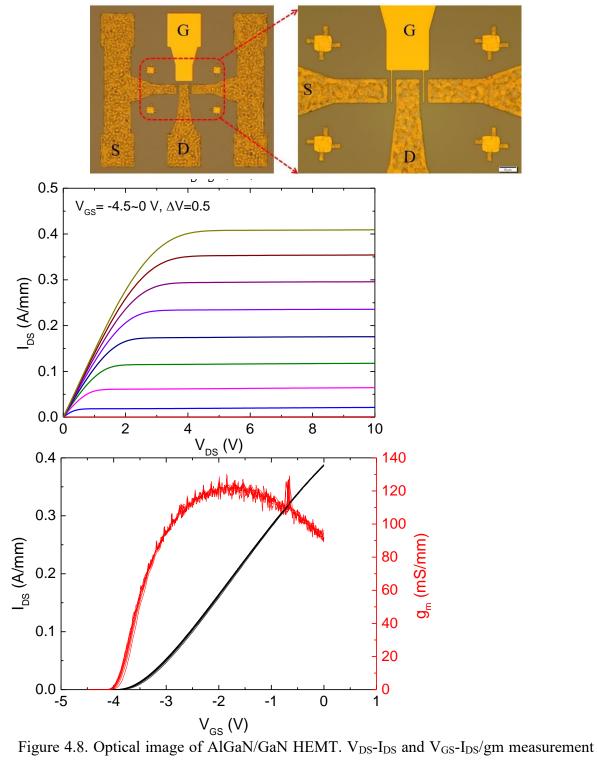

After channel definition and ohmic contact of formation, the gate pattern was defined using photolithography and e-beam lithography for gate lengths smaller than 3  $\mu$ m. Gate metal of Ni/Au= 50/100 nm was deposited using e-beam evaporator and lift-off using Remover PG for e-beam lithography. Fig 4.8 shows the final device with its I-V characteristic results.

Figure 4.8. Optical image of AlGaN/GaN HEMT.  $V_{DS}$ - $I_{DS}$  and  $V_{GS}$ - $I_{DS}$ /gm measurement result.

AlGaN/GaN HEMT shows the following measurement parameters;

- Pinch-off Voltage= -4 V

- Maximum current density= 409 mA/mm at  $V_{GS}$ = 9.5 V (Saturates after

- $V_{GS} = 5 V$ )

- On-resistance=  $\sim 500 \ \Omega \cdot \text{mm} (V_{GS} = 0 \text{V})$

- On-off ratio  $\sim 10^7$

- Peak extrinsic  $g_m$ = 122 mS/mm at  $V_{GS}$  = -1.65V

# 4.4. Kerf-less exfoliation of non-planar, multi-layer architecture

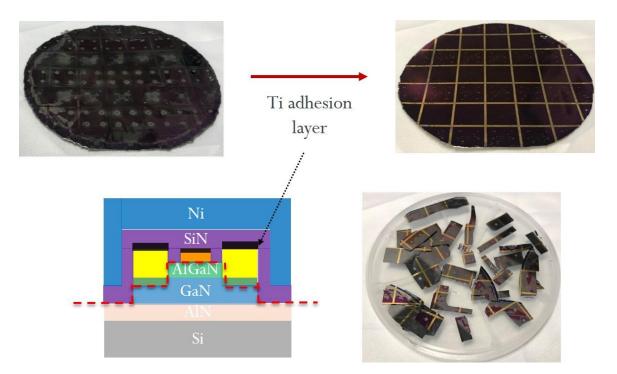

Figure 4.9. Top: Optical image of exfoliated AlGaN/GaN HEMT with and without additional Ti adhesion layer. Bottom left: Schematic of final structure before exfoliation. Dotted line represents exfoliated path. Bottom right: Parent silicon wafer after exfoliation.

Once the demonstration of AlGaN/GaN HEMT on bulk silicon was successful, exfoliation of the electronic devices was conducted. After fabricating the HEMT structures on silicon substrate, Si<sub>3</sub>N<sub>4</sub> was deposited using PECVD followed by Ti/Ni seed layer. The Si<sub>3</sub>N<sub>4</sub> layer is needed to protect the HEMT from subsequent nickel etchant after exfoliation. Fig 4.9 shows the exfoliation result of AlGaN/GaN HEMT devices on silicon substrate. Unlike the planar structure case, the exfoliation mainly occurred between the Si<sub>3</sub>N<sub>4</sub> and electroplated Ni interface. This can be explained by the adhesion difference between each interface. When a Ti adhesion layer was inserted between the HEMT metal contacts and the Si<sub>3</sub>N<sub>4</sub> layer, the exfoliation occurred between the HEMT metal contacts and the AlGaN interface which is illustrated as the dotted line in figure 4.9.

While exfoliation of HEMT structure on silicon was conducted at various conditions including change in electroplated nickel thickness, thermal cycling condition and initial cracking, the exfoliation did not occur within the silicon substrate.

Another difference between the planar structure in chapter 4.2 is that the bulk, parent wafer cracks into small pieces shown in figure 4.9. (bottom right image) This did not occur for the planar architecture samples which implies that the thermally induced stress distribution for the multi-layer structure is different and complex.

# Chapter 5. Graphene-Al<sub>2</sub>O<sub>3</sub>-Silicon Heterojunction Solar Cells on Flexible Silicon Substrates \*

#### 5.1. INTRODUCTION

Two-dimensional materials have been studied extensively since the seminal work with graphene in 2004 [48-51]. The appeal of this class of materials arises from their unique electronic, optical, and physical properties. For example, graphene has remarkable mechanical properties and flexibility [52], it is optically transparent (absorbing less than 3% of incident light per layer) [53], and it is highly conductive electrically and thermally [54]. One application for graphene which has garnered early attention is its use as a transparent conducting film [55-56]. For many applications, the current market standard transparent conductor is indium tin oxide (ITO) and graphene can provide unique advantages over ITO, namely mechanical flexibility, and lower cost with earth abundant materials [57]. As a transparent conductor, graphene can advance energy generation in solar cell applications. To this end, graphene has been used to form a heterojunction with semiconductors such as silicon and GaAs, resulting in graphene semiconductor-Schottky barrier solar cells (GS-SBSC) [58-59]. While early work gave efficiencies of less than 2 % in power conversion efficiency (PCE), researchers have boosted the efficiencies of these GS-SBSC up to 15.6 % by various techniques such as graphene doping, insertion of a thin insulator between the graphene and silicon, anti-reflective coating, and semiconductor and backside passivation [60-65].

<sup>\*</sup> This chapter is based on Reference : J. Ahn, H. Chou, and S.K. Banerjee Graphene-Al<sub>2</sub>O<sub>3</sub>-Silicon Heterojunction Solar Cells on Flexible Silicon Substrates *Journal of Applied Physics*, **2017**, *121*, 163105. J.A. and H.C. contributed equally to this work.

Thin solar cells possess the advantage of reducing the material cost as well as potentially increasing the PCE [66]. Additionally, thin solar cells can be made flexible, which opens a whole new range of applications such as wearable devices [67-68]. Utilizing the inherent flexibility of graphene, GS-SBSC fabricated on thinned Si body have been demonstrated with efficiencies up to 8.4% [69-70]. These flexible GS-SBSC are fabricated on bendable silicon films which are produced by wet etching a bulk Si wafer.

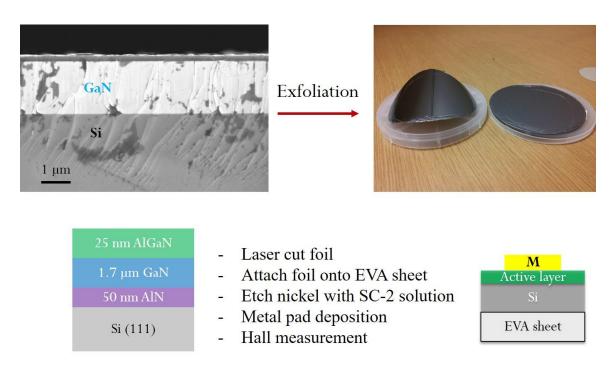

In this chapter, we demonstrate GS-SBSC on bendable, thin silicon foils obtained by a kerf-less mechanical exfoliation technique. The exfoliation process does not require the strong etchants of the other processes and the "parent" wafer can be subsequently used to generate additional thin silicon films, and both aspects bolster the effort of reducing material cost. We also study the effects of an Al<sub>2</sub>O<sub>3</sub> interlayer between the exfoliated silicon and doped graphene, giving a graphene-insulator-silicon (GIS) solar cell. This thin insulator layer, deposited by atomic layer deposition (ALD), increases the overall performance of the device by preventing recombination and increasing charge carrier lifetime.

#### 5.2. EXPERIMENTAL

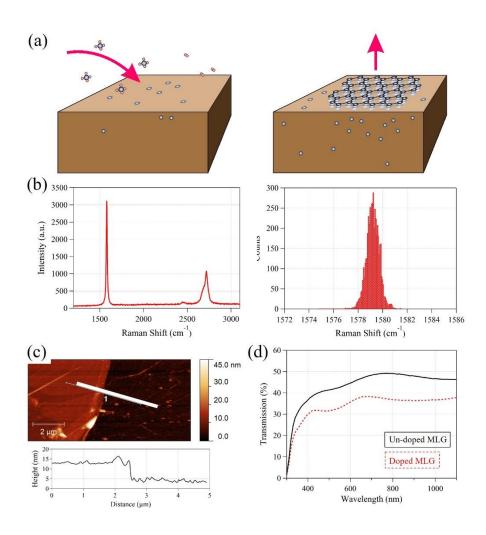

#### 5.2.1. Growing, doping, and transfer of multilayer graphene

Multi-layer graphene (MLG) was grown by chemical vapor deposition (CVD) on Cu-Ni alloy foils in a low-pressure system. A single layer of graphene can be grown in a self-limiting process on pure copper due to the low solubility of carbon in copper [71-72]. Although other reports have shown high performance using single layer graphene (SLG), it has also been shown that MLG enhances the solar cell performance. [64, 73-74]

Therefore, in thes devices, we incorporate MLG. By growing on a Cu-Ni alloy instead, the solubility of carbon is increased and MLG can be formed by precipitating carbon out (in the form of graphene) during cooling, as has been shown previously [75-76]. The dissolution and precipitation process is shown schematically in Figure 5.1 (a). Methane was flowed at 3 sccm and carried by hydrogen gas flowed at 10 sccm to the foil substrate at held at 1050° C. After the high temperature growth, the chamber was cooled also under 3 sccm flow of methane and 10 sccm flow of hydrogen. After growth and graphene transfer as described below, the MLG film is characterized by confocal Raman spectroscopy (Renishaw inVia, 532 nm wavelength laser) and atomic force microscopy (AFM), which is shown in Figure 4.1 (b) and (c). The Raman characterization gives a spectrum consistent for MLG and a narrow distribution for the G band position [77-78]. The AFM scan at the edge of a MLG film shows a step height of  $\sim 10$  nm, which corresponds to 27 – 29 layers of graphene. After synthesis, the MLG is charge-transfer doped p-type by spin coating a 10mM solution of AuCl<sub>3</sub> in nitromethane at 2000rpm for 1 minute [79-80]. The doping effect is verified by measuring the sheet resistance and optical transmission, as shown in Figure 4 (d). The AuCl<sub>3</sub> dopant does adversely impact the transmission of the MLG layer, and there is a trade-off between loss in transmission due to more graphene layers and doping, and a boost in conductivity. After the doping process, the CVD graphene is transferred using a PMMA-assisted wet etching method [81].

55

Figure 5.1: (a) Illustration of graphene growth. Methane decomposes on the catalytic surface of the Cu-Ni alloy and carbon dissolves into the substrate at high temperature. On slow cooling, the carbon precipitates out of the Cu-Ni alloy in the form of MLG. (b) Raman spectrum of MLG after transfer onto SiO<sub>2</sub>/Si substrate showing a highly crystalline film and a histogram of the G peak position over a scanned area of 40 x 30  $\mu$ m MLG showing that the film is uniform in quality. (c) AFM scan of the edge of a transferred MLG showing the thickness to be ~ 10 nm. (d) Transmission of un-doped and pre-doped MLG over a broad light spectrum.

A PMMA film is spin coated onto the graphene at 2000rpm and baked for 1 min. at 90° C. The PMMA-graphene stack is floated on 0.5 M ammonia persulfate solution to etch away the Cu-Ni alloy substrate. The PMMA-graphene is then rinsed in deionized water to remove any etchant or byproducts from the Cu-Ni removal process. The PMMAgraphene is lifted from the water directly by the target substrate, the silicon foil. The doping was done prior to the for reasons discussed below.

As we show below, the tradeoff favors utilizing MLG (as opposed to single layer graphene, SLG) and doping it. Doping the graphene (with AuCl<sub>3</sub>) reduces the graphene sheet resistance which is measured by van der Pauw method. Un-doped and pre-doped MLG were transferred onto SiO<sub>2</sub>/Si bulk substrate followed by metal contact formation using silver paste for measurement. Sheet resistances of 448 and 11  $\Omega/\Box$  were obtained for un-doped and doped MLG, respectively, with an encapsulating layer of PMMA on top.

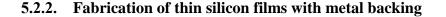

Figure 5.2: (a) Schematic of silicon exfoliation process by deposition of metal layer, thermal cycling, and exfoliation. (b) Scanning electron microscope (SEM) cross-section image of a thin exfoliated silicon layer. Inset: Photographic image of an exfoliated 4-inch Si wafer. (c) Experimental result of silicon film thickness relationship with thermal cycling temperature

Figure 5.2 illustrates the kerf-less exfoliation process based on spalling and resulting exfoliated silicon film on metal foil. Bulk silicon wafers (n-type, <100>, 1 ~ 5  $\Omega \cdot cm$ ) were covered with a dual-layer of hydrogenated amorphous silicon ( $\alpha$ -Si:H) using remote plasma chemical vapor deposition (RPCVD). 5 nm, intrinsic  $\alpha$ -Si:H was deposited on the front side to passivate the surface, and 7 nm, n<sup>+</sup> doped  $\alpha$ -Si:H was deposited on the back side to achieve ohmic contact with backside metal [82]. Chromium (10 nm) and Nickel (100 nm) were sequentially deposited onto the back surface by electron beam evaporation as a seed layer for electroplating 50 ~ 55 µm of Ni onto the

metal seed layer with current density fixed to 30 A/cm<sup>2</sup>. At this step, the backside of the GS-SBSC device was complete and the kerf-less exfoliation process was done [83-84]. Exfoliation was initiated with a crack at the edge of the wafer after the thermal annealing process and followed by controlled spalling. The exfoliated silicon thickness was controlled by the thermal cycling process (270 °C ~ 310 °C, 10 min.) which thermally induced stress at the metal/silicon interface due to the difference in coefficient of thermal expansion (CTE) in the different materials. Silicon thicknesses down to 8  $\mu$ m can be successfully exfoliated with surface RMS roughness less than 2 nm. Other parameters such as metal thickness, annealing time, current density during electroplating and mechanical exfoliation condition can further control the silicon thickness [85]. Solar cells fabricated by this method reduce the material cost through re-use of the parent wafer for subsequent exfoliation. This method is also beneficial with respect to handling issues and preventing cracks in thin silicon films because of the mechanical support provided by the electroplated Ni layer.

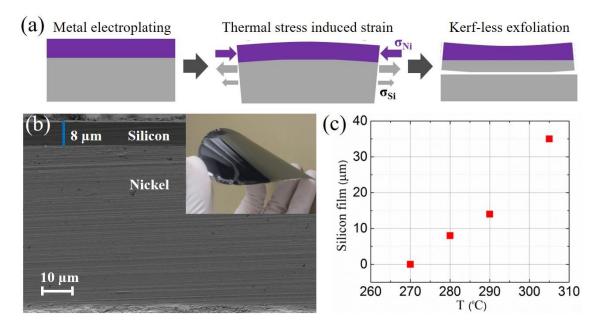

#### 5.2.3. Graphene-silicon (and graphene-insulator-silicon) SBSC fabrication

The exfoliated silicon film with Ni metal backing foil was first sonicated in acetone and iso-propyl alcohol (IPA), followed by RCA clean. An SC-1 clean removes silicon particles from the exfoliation process. Silicon films with thicknesses of 35 μm were used to maximize absorption, while maintaining the flexibility of the film. Immediately before any subsequent process, the native oxide was removed from the silicon surface in diluted HF. In the case where an interlayer oxide was inserted (GIS cells), Al<sub>2</sub>O<sub>3</sub> was deposited by atomic layer deposition in a Cambridge nanotech Fiji F200 ALD system, using tri-methyl aluminum (TMA) and water precursors at 200 °C. To fabricate the GS-SBSC device (or GIS cell), MLG was transferred using the method described above onto the silicon surface (without an intervening Al<sub>2</sub>O<sub>3</sub> layer) and then allowed to dry in ambient. The sample was then heated up to 110 °C for 10 min. to improve graphene/substrate adhesion. To further aid adhesion and remove wrinkles in the MLG, an additional application of PMMA was made on top of the PMMA-graphene [86-87]. The PMMA was spin coated at 3000rpm for 1 min. and then baked at 90 °C for 1 min. It has been previously reported that removing the PMMA after graphene transfer can degrade the graphene quality [69]. To effectively dope the graphene while retaining the graphene quality, the graphene is pre-doped prior to PMMA coating.

Silver paste was directly applied onto the PMMA/AuCl<sub>3</sub>/graphene to form top contact of the graphene. Acetone solvent within the silver paste dissolved the PMMA allowing direct contact between silver paste and graphene. All remaining areas were covered with black tape to ensure precise measurements. The active area of the solar cells is  $0.17 \sim 0.37$  cm<sup>2</sup>. Figure 5.3 illustrates the GS-/GIS- SBSC device fabrication and includes a photograph of a completed GIS cell.

Figure 5.3: (a) Schematic of GIS Solar cell fabrication process. For GS-SBSC, all is identical except excluding Al<sub>2</sub>O<sub>3</sub> layer deposition process. (b) Photographic image of a completed GIS solar cell.

# 5.3. Results and discussion

# 5.3.1. GS-SBSC.

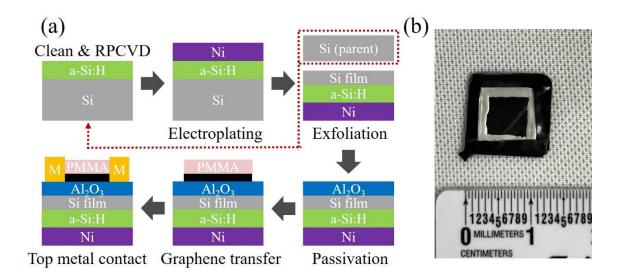

Figure 5.4: (a) Qualitative energy band diagram of GS-SBSC with and without AuCl<sub>3</sub> doping. P-doped MLG creates a shift in potential resulting

in improved cell performance. (b) J-V plot of un-doped MLG and predoped MLG with no interlayer oxide layer. (c) lnJ-V plot measured in dark with linear fit (solid lines) of the forward current for ideality factor and SBH extraction. (d) dV/d(lnJ)-J plot for series resistance (R<sub>S</sub>) extraction.

Figure 5.4 (b) shows the current density-voltage (J-V) characteristics of un-doped and pre-doped heterojunction GS-SBSC on thin exfoliated silicon films. GS-SBSC were measured using an ABET solar simulator (Model: Sun 2000) and were calibrated using a reference solar cell (ABET model #15150) prior to measurement. Results show that doping the graphene increases open circuit voltage (Voc) from 209 to 299 mV, fill factor (FF) from 43 to 53 % and improving the PCE from 1.8 to 3.0 %. The increase in performance after doping can be explained by analyzing the GS-SBSC dark I-V graph and band diagram. Figure 5.4 (a) illustrates the band diagram for un-doped and p-type doped graphene on n-type silicon. According to the Schottky-Mott rule of Schottky barrier formation, the Schottky barrier height (SBH,  $\phi_{SBH}$ ) between MLG and thin silicon film is described based on the work function of the MLG (W<sub>G</sub>) and the electron affinity of the silicon ( $\chi$ ),  $\phi_{SBH} \sim W_G - \chi$ . Doping the MLG with AuCl<sub>3</sub> is known to shift the MLG work function ( $\phi^*_{SBH}$ ) [56] and can be extracted from the equation

$$J_s = A^* T^2 \exp(\frac{-\phi_{SBH}}{kT}) \tag{1}$$

where  $J_S$  is the saturation current extrapolated at V = 0 from the linear portion of the forward current (solid lines in figure 2.4 (c), un-doped  $J_S = 8.9 \ \mu A/cm^2$ , doped  $J_S =$ 1.14  $\mu A/cm^2$ ), A\* is the Richardson constant (~ 112 A/cm<sup>2</sup>·K<sup>2</sup> for n-Si), *T* is the absolute temperature, q is the electron charge and k is the Boltzmann constant. The SBH for undoped and doped GS-SBSC was found to be 0.71 and 0.77 eV, respectively.

The change in saturation current results in a change of  $V_{OC}$  given by the following relation,

$$V_{oc} = \frac{nkT}{q} \ln(\frac{J_{ph}}{J_s})$$

<sup>(2)</sup>

where *n* is the ideality factor of the graphene/silicon interface, and  $J_{ph}$  is the lightinduced photocurrent density of the solar cell [88]. The ideality factor can be extracted by fitting the device response in the dark, giving *n* of 1.5 and 1.8, respectively, and shown in Figure 5.4 (c). Following the above equation, an increase in *n* and decrease in  $J_S$  leads to an increase in  $V_{OC}$  for doped MLG solar cells. The drop in short circuit current ( $J_{SC}$ ) can be explained due to the decrease in transmitted photons after doping. There is a loss in transmission through the MLG due to AuCl<sub>3</sub> charge-transfer doping, which results in a decrease of light reaching the silicon absorber as shown in Figure 5.1 (d).

The increase in FF is due to the reduction in series resistance (R<sub>S</sub>) after graphene doping. The R<sub>S</sub> for un-doped and doped GS-SBSC are extracted using the slope of the dV/d(lnJ) plot, which is shown in Figure 5.4 (d). The R<sub>S</sub> is shown to decrease from 11.75 to 4.08  $\Omega$ ·cm<sup>2</sup> for doped GS-SBSC cells. Since FF is strongly related to R<sub>S</sub>, the decrease in R<sub>S</sub> gives the increase in FF. Overall, the GS-SBSC is improved from 1.8 % PCE to 3.0 % PCE upon doping with 10 mM AuCl<sub>3</sub> in nitromethane.

#### 5.3.2. GIS cells with ALD Al<sub>2</sub>O<sub>3</sub>