Copyright

by

Tianhao Zheng

2018

# The Dissertation Committee for Tianhao Zheng certifies that this is the approved version of the following dissertation:

## Efficient Fine-grained Virtual Memory

| Committee:              |

|-------------------------|

|                         |

| Mattan Erez, Supervisor |

|                         |

| Vijay Janapa Reddi      |

|                         |

| Calvin Lin              |

| G: D.                   |

| Simon Peter             |

| Mohit Tiwari            |

## Efficient Fine-grained Virtual Memory

by

## Tianhao Zheng

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2018$

## Acknowledgments

My Ph.D. journey would not have been possible without tremendous supports and guidance from my advisor, Mattan Erez. He was smart, knowledgable, hard-working and the most important, open-minded and willing to help all the way through my PhD career. Instead of assigning a direction to me, he inspired me to grow my own research interest from the beginning of the Ph.D. program. I shall always remember the days I started with little experience, making numerous mistakes on various ideas and experiments. He was always patient and supportive, happy to spend time on my questions no matter how trivial they are.

I thank Vijay Janapa Reddi, Mohit Tiwari, Calvin Lin, Simon Peter for serving on my dissertation committee and providing me valuable comments on this dissertation.

I would like to thank David Nellans, Arslan Zulfiqar, Mark Stephenson and Stephen W. Keckler at Nvidia Research for the opportunity to collaborate with them. I learned a lot about GPU memory systems while I was interning with them.

I am glad to get to know many other graduate students during my PhD. Specifically, I would like to thank Jaeyoung Park, Dong Wan Kim, and Haishan Zhu for the collaborations with them. Their knowledge and experience expended my expertise and helped me to develop many research ideas.

I would also like to acknowledge the old members of LPH group: Min Kyu Jeong, Mike Sullivan, Evgeni Krimer, Minsoo Rhu, Ikhwan Lee, Jungrae Kim for selflessly sharing their experience and knowledge with me.

I also thank all the other members of our research group: Song Zhang, Jinsuk Chung, Seong-Lyong Gong, Kyushick Lee, Esha Choukse, Derong Liu, Nick Kelly, Benjamin Cho, Sangkug Lym, Yongkee Kwon, Chun-Kai Chang, Majid Jalili, and Wenqi Yin. And I am grateful for the friendship with many others: Yuhao Zhu, Jingwen Leng, Yazhou Zu, Wenzhi Cui, Matt Halpern, Zhuoran Zhao, Shuang Song, Qinzhe Wu, Hangchen Yu, Pei Yan. It has been much fun having coffee and pizza together and spend days and nights on projects.

Finally, I cannot express enough my gratitude to my parents, Zhenhong Zheng and Yanru Tang for their unconditional love. I would like to appreciate my girlfriend, Yawen He for the adventures we took together.

Tianhao Zheng

April 2018, Austin, TX

#### Efficient Fine-grained Virtual Memory

Publication No.

Tianhao Zheng, Ph.D.

The University of Texas at Austin, 2018

Supervisor: Mattan Erez

Virtual memory in modern computer systems provides a single abstraction of the memory hierarchy. By hiding fragmentation and overlays of physical memory, virtual memory frees applications from managing physical memory and improves programmability. However, virtual memory often introduces noticeable overhead. State-of-the-art systems use a paged virtual memory that maps virtual addresses to physical addresses in page granularity (typically 4 KiB). This mapping is stored as a page table. Before accessing physically addressed memory, the page table is accessed to translate virtual addresses to physical addresses. Research shows that the overhead of accessing the page table can even exceed the execution time for some important applications. In addition, this fine-grained mapping changes the access patterns between virtual and physical address spaces, introducing difficulties to many architecture techniques, such as caches and prefecthers.

vii

In this dissertation, I propose architecture mechanisms to reduce the overhead of accessing and managing fine-grained virtual memory without compromising existing benefits. There are three main contributions in this dissertation.

First, I investigate the impact of address translation on cache. I examine the restriction of virtually indexed, physically tagged (VIPT) caches with fine-grained paging and conclude that this restriction may lead to sub-optimal cache designs. I introduce a novel cache strategy, speculatively indexed, physically tagged (SIPT) to enable flexible cache indexing under fine-grained page mapping. SIPT speculates on the value of a few more index bits (1 - 3 in our experiments) to access the cache speculatively before translation, and then verify that the physical tag matches after translation. Utilizing the fact that a simple relation generally exists between virtual and physical addresses, because memory allocators often exhibit contiguity, I also propose low-cost mechanisms to predict and correct potential mis-speculations.

Next, I focus on reducing the overhead of address translation for finegrained virtual memory. I propose a novel architecture mechanism, Embedded Page Translation Information (EMPTI), to provide general fine-grained page translation information on top of coarse-grained virtual memory.

EMPTI does so by speculating that a virtual address is mapped to a pre-determined physical location and then verifying the translation with a very-low-cost access to metadata embedded with data. Coarse-grained virtual memory mechanisms (e.g., segmentation) are used to suggest the predetermined physical location for each virtual page. Overall, EMPTI achieves the benefits of low overhead translation while keeping the flexibility and programmability of fine-grained paging.

Finally, I improve the efficiency of metadata caching based on the fact that memory mapping contiguity generally exists beyond a page boundary. In state-of-the-art architectures, caches treat PTEs (page table entries) as regular data. Although this is simple and straightforward, it fails to maximize the storage efficiency of metadata. Each page in the contiguously mapped region costs a full 8-byte PTE. However, the delta between virtual addresses and physical addresses remain the same and most metadata are identical. I propose a novel microarchitectural mechanism that expands the effective PTE storage in the last-level-cache (LLC) and reduces the number of page-walk accesses that miss the LLC.

## **Table of Contents**

| Ackno   | wledg | ments                                       | $\mathbf{v}$ |

|---------|-------|---------------------------------------------|--------------|

| Abstra  | act   |                                             | vii          |

| List of | Table | es                                          | xiii         |

| List of | Figu  | res                                         | xiv          |

| Chapt   | er 1. | Introduction                                | 1            |

| 1.1     | The C | Cost of Fine-Grained Paged Virtual Memory   | . 1          |

| 1.2     | The I | Real Implications of Fine Granularity       | . 3          |

| 1.3     | Thesi | s Statement                                 | . 4          |

| 1.4     | Contr | ributions                                   | . 4          |

| 1.5     | Disse | rtation Organization                        | . 6          |

| Chapt   | er 2. | Background and Terminology                  | 8            |

| 2.1     | Fine- | Grained Virtual Memory                      | . 8          |

|         | 2.1.1 | Translation Lookaside Buffers               | . 9          |

|         | 2.1.2 | Memory-Management Unit (MMU) Caches         | . 10         |

| 2.2     | Coars | se-Grained Virtual Memory                   | . 11         |

|         | 2.2.1 | Direct Segments                             | . 11         |

|         | 2.2.2 | Coarse-Grained Pages                        | . 12         |

|         | 2.2.3 | Redundant Memory Mappings                   | . 13         |

| 2.3     | L1 Ca | ache Indexing                               |              |

|         | 2.3.1 | Virtually Indexed, Virtually Tagged Caches  |              |

|         | 2.3.2 | Virtually Indexed, Physically Tagged Caches |              |

| Chapte                                                       | er 3.  | Problem Statement and Motivation                              | 17         |

|--------------------------------------------------------------|--------|---------------------------------------------------------------|------------|

| 3.1                                                          | VIPT   | Cache Design Space with Fine-Grained Page Mapping .           | 17         |

| 3.1.1 Challenge I: Enabling Effective Cache Indexing         |        | Challenge I: Enabling Effective Cache Indexing                | 20         |

| 3.2 Deficiency of Address Translation in Fine-grained Paging |        | ency of Address Translation in Fine-grained Paging            | 20         |

| v                                                            |        | Challenge II: Page Walk Latency                               | 21         |

| 3.3 The Absence of Fine-Grained Metadata in Coa              |        | Absence of Fine-Grained Metadata in Coarse-grained Vir-Memory | 22         |

|                                                              | 3.3.1  | Challenge III: Coupled Translation and Metadata               | 23         |

| 3.4                                                          | Metac  | data in the Data Cache Hierarchy                              | 24         |

| 3.5                                                          | Redu   | ndancy in Metadata                                            | 24         |

|                                                              | 3.5.1  | Challenge IV: Efficient Metadata Caching                      | 25         |

| Chapt                                                        | er 4.  | Flexible L1 Caches with Fine-grained Paging                   | 27         |

| 4.1                                                          | Specu  | llatively Indexed, Physically Tagged Caches                   | 27         |

|                                                              |        | 4.1.0.1 Speculation Accuracy                                  | 29         |

|                                                              | 4.1.1  | Naive SIPT Performance                                        | 29         |

| 4.2                                                          | Predic | cting and Bypassing Misspeculations                           | 32         |

| 4.3                                                          | Partia | al Index Prediction                                           | 36         |

|                                                              | 4.3.1  | Combined Speculation Bypass and Index-Bit Value Prediction    | 39         |

|                                                              | 4.3.2  | Multicore Evaluation                                          | 42         |

| 4.4                                                          | Furth  | er Discussion                                                 | 4          |

|                                                              | 4.4.1  | Way Prediction                                                | 4          |

|                                                              | 4.4.2  | The Predictability of Partial Index Bits                      | 4          |

|                                                              | 4.4.3  | Implications for Instruction Schedulers                       | 49         |

| Chapt                                                        | er 5.  | Low-overhead Translation with<br>Fine-grained Metadata        | <b>5</b> . |

| 5.1                                                          | Embe   | edded Page Translation Information                            | 5          |

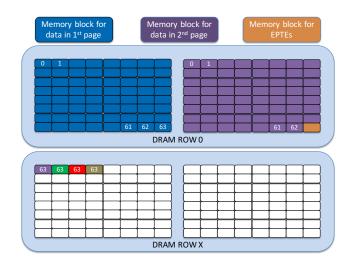

|                                                              | 5.1.1  | EPTE Storage                                                  | 56         |

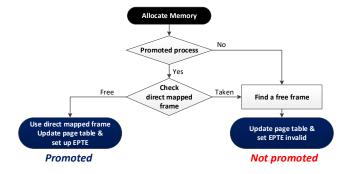

|                                                              | 5.1.2  | Software Support                                              | 60         |

| 5.2                                                          | Evalu  | ation Methodology                                             | 6          |

|                                                              |        | Performance Model                                             | 6          |

| 5.3                                                          | Evalu  | ation Results                                                 | 69         |

|        | 5.3.1  | Energy Impact                             | 72  |

|--------|--------|-------------------------------------------|-----|

| 5.4    | Futur  | e Work                                    | 73  |

| Chapte | er 6.  | Efficient Metadata Caching                | 74  |

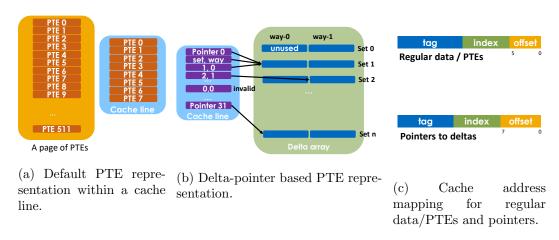

| 6.1    | Motiv  | vation                                    | 74  |

|        | 6.1.1  | PTEs in the Data Cache                    | 75  |

|        | 6.1.2  | Contiguity of Address Mapping             | 77  |

| 6.2    | Delta  | Caching                                   | 78  |

|        | 6.2.1  | The Delta Array                           | 79  |

|        | 6.2.2  | Delta Caching Hierarchy                   | 82  |

|        | 6.2.3  | Delta Caching and Page Table Updates      | 82  |

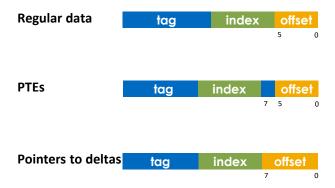

| 6.3    | Dual   | PTE/Delta Caching                         | 83  |

|        | 6.3.1  | Address Mapping for Dual Caching          | 85  |

|        | 6.3.2  | Mode Selection                            | 85  |

| 6.4    | Evalu  | ation Methodology                         | 86  |

|        | 6.4.1  | Page-Walk Memory Access Costs             | 87  |

|        | 6.4.2  | Comparing System Performance              | 88  |

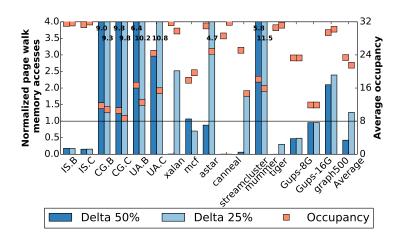

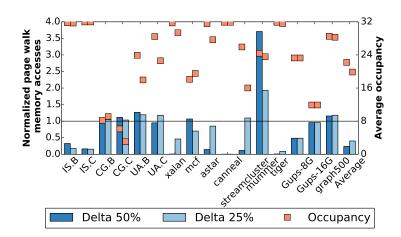

| 6.5    | Evalu  | ation Results                             | 89  |

| 6.6    | Furth  | er Discussion                             | 93  |

|        | 6.6.1  | CoLT (Coalesced Large-Reach TLBs)         | 93  |

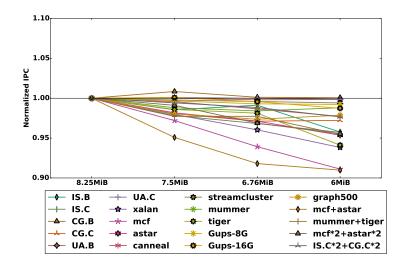

|        | 6.6.2  | Impact of LLC Capacity Reduction          | 97  |

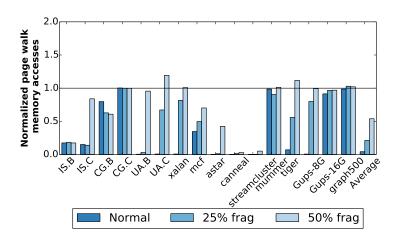

|        | 6.6.3  | Sensitivity Study to Memory Fragmentation | 97  |

| 6.7    | Relate | ed Work                                   | 98  |

| Chapte | er 7.  | Conclusion                                | 105 |

| 7.1    | Futur  | e Work                                    | 106 |

| Appen  | dices  |                                           | 108 |

| Index  |        |                                           | 125 |

| Vita   |        |                                           | 126 |

## List of Tables

| 3.1 | L1 cache configurations                                                                                                                                                                         | 18  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Simulated system configurations                                                                                                                                                                 | 31  |

| 4.2 | Multi-programmed workloads                                                                                                                                                                      | 43  |

| 5.1 | Number of mmap, munmap, and mprotect calls                                                                                                                                                      | 64  |

| 5.2 | System configuration                                                                                                                                                                            | 65  |

| 5.3 | Application parameters                                                                                                                                                                          | 66  |

| 5.4 | Performance model and measured parameters. The $4\mathrm{K/THP}$ notation indicates that two parameters are measured – once when running with $4\mathrm{KiB}$ pages and a second time with THP  | 67  |

| 6.1 | Benchmark parameters                                                                                                                                                                            | 76  |

| 6.2 | Cache configurations, # of sets * # of ways                                                                                                                                                     | 87  |

| 6.3 | Performance model and measured parameters. The $4\mathrm{K/THP}$ notation indicates that two parameters are measured – once when running with $4\mathrm{KiB}$ pages and a second time with THP. | 89  |

| 6.4 | Comparison of delta caching with prior schemes for reducing translation overhead                                                                                                                | 102 |

# List of Figures

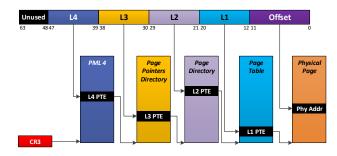

| 2.1 | 4-level page walk in x86 architecture                                                                                                                                         | 9  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | A x86 page table entry                                                                                                                                                        | 9  |

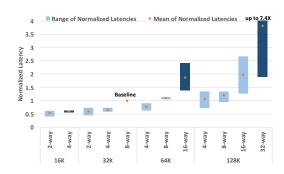

| 3.1 | L1 cache latency relative to 32KiB 8-way baseline                                                                                                                             | 18 |

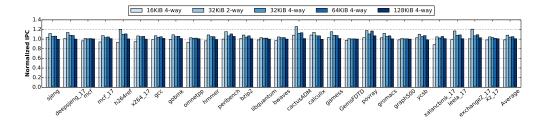

| 3.2 | IPC with various L1 cache configurations for an OOO core, normalized to the baseline L1                                                                                       | 19 |

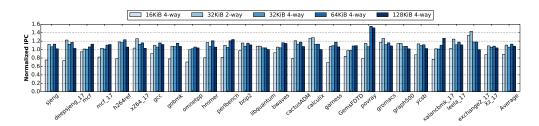

| 3.3 | IPC with various L1 cache configurations for an in-order core, normalized to the baseline L1                                                                                  | 19 |

| 3.4 | Natural address mapping contiguity                                                                                                                                            | 25 |

| 4.1 | SIPT cache access when speculated index is unchanged (left) and changed (right)                                                                                               | 28 |

| 4.2 | Fraction of correct speculations vs. the number of index bits that must be predicted                                                                                          | 30 |

| 4.3 | IPC and additional L1 accesses with a naive SIPT 32KiB/2-way/2-cycle cache for an OOO core normalized to the baseline L1                                                      | 31 |

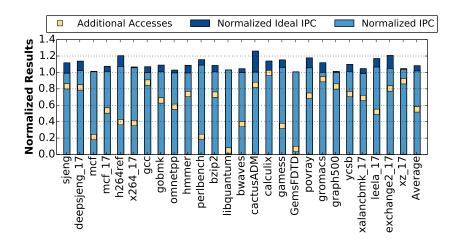

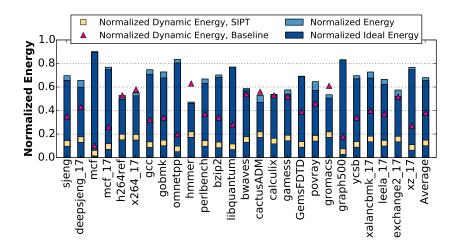

| 4.4 | Cache hierarchy energy of naive SIPT 32KiB/2-way/2-cycle for an OOO core normalized to baseline                                                                               | 32 |

| 4.5 | Perceptron-based predictor                                                                                                                                                    | 34 |

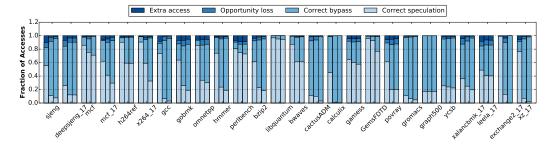

| 4.6 | Break down of prediction results into the four possible outcomes; each group of 3 bars represents 1, 2, and 3 speculative index bits (from left to right, respectively)       | 35 |

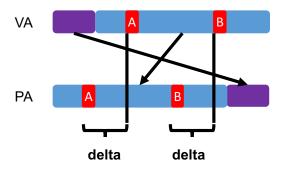

| 4.7 | Deltas between virtual and physical addresses are constant within a single large block                                                                                        | 37 |

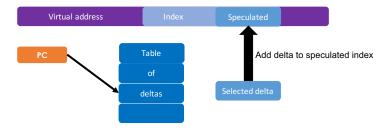

| 4.8 | The index delta buffer predicts the delta between the speculative virtual address bits and corresponding physical address bits                                                | 38 |

| 4.9 | Prediction accuracy of the combined predictor when attempting to predict 1, 2, and 3 speculative index bits (the left, middle, and right bar within each group, respectively) | 39 |

| 4.10 | IPC and additional L1 accesses with a 32KiB/2-way/2-cycle SIPT cache with IDB for an OOO core normalized to the baseline L1                                                                                                                                        | 41 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.11 | Cache hierarchy energy with a 32KiB/2-way/2-cycle SIPT+IDB for an OOO core normalized baseline                                                                                                                                                                     | 42 |

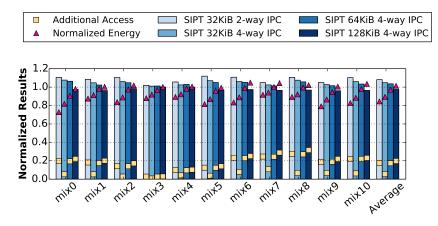

| 4.12 | IPC, extra L1 accesses, and cache hierarchy energy of SIPT with IDB for an OOO quad core; IPC and energy normalized to the baseline L1 cache                                                                                                                       | 44 |

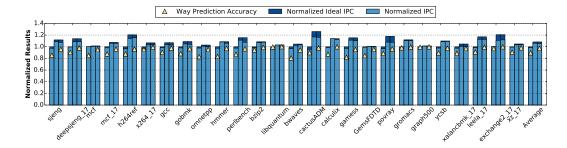

| 4.13 | IPC normalized to the baseline L1 and way prediction accuracy. Each group from left to right: baseline L1 with way prediction, 32KiB/2-way/2-cycle SIPT with IDB, and 32KiB/2-way/2-cycle SIPT with both IDB and way prediction                                    | 45 |

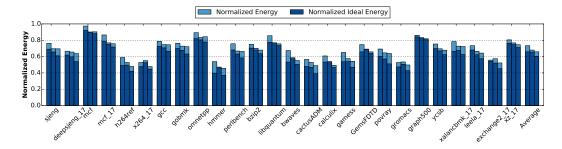

| 4.14 | Cache hierarchy energy normalized to the baseline L1. Each group from left to right: baseline L1 with way prediction, 32KiB/2-way/2-cycle SIPT with IDB, and 32KiB/2-way/2-cycle SIPT with both IDB way prediction                                                 | 45 |

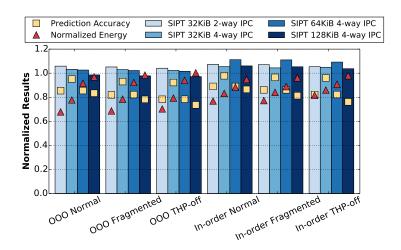

| 4.15 | IPC, cache hierarchy energy, and prediction accuracy on OOO and in-order core with various operating conditions; IPC and energy normalized to the baseline L1                                                                                                      | 50 |

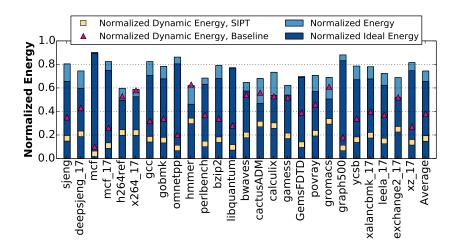

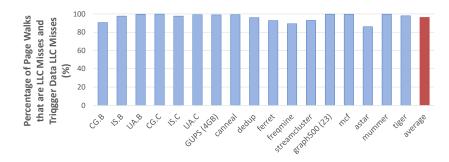

| 5.1  | Percentage of page walks that are last-level-cache (LLC) misses which also trigger data LLC misses. Results are for a simulated quad-core system with a 64-entry L1 TLB per core, a shared 1024-entry second level TLB, an 8MiB unified LLC, and 8GiB main memory. | 52 |

| 5.2  | Page walk and data access served by a single memory access with EMPTI. The light and dark portions of a memory block represent the embedded PTE (EPTE) and data portions, respectively                                                                             | 53 |

| 5.3  | Embedded Page Table Entry (EPTE)                                                                                                                                                                                                                                   | 54 |

| 5.4  | Direct mapped conflict rate with various memory capacities (footprint/memory)                                                                                                                                                                                      | 55 |

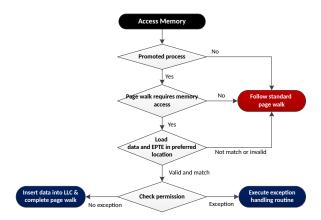

| 5.5  | Application memory access with Embedded Page Translation Information                                                                                                                                                                                               | 56 |

| 5.6  | Storing EPTE with ECC redundancy                                                                                                                                                                                                                                   | 58 |

| 5.7  | Visual representation of mapping data and EPTE storage to DRAM rows.                                                                                                                                                                                               | 60 |

| 5.8  | Workflow for memory allocation                                                                                                                                                                                                                                     | 62 |

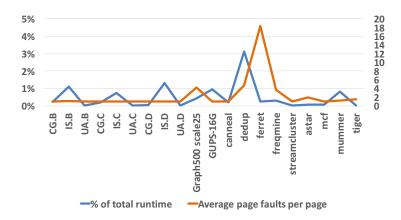

| 5.9  | Percentage of total run time and average page faults per allo-<br>cated page                                                                                                                                                                                       | 64 |

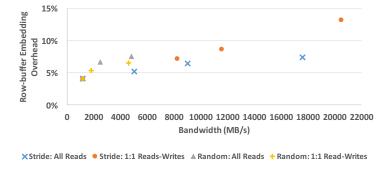

| 5.10 | Row-buffer embedding overhead                                                                                                | 68  |

|------|------------------------------------------------------------------------------------------------------------------------------|-----|

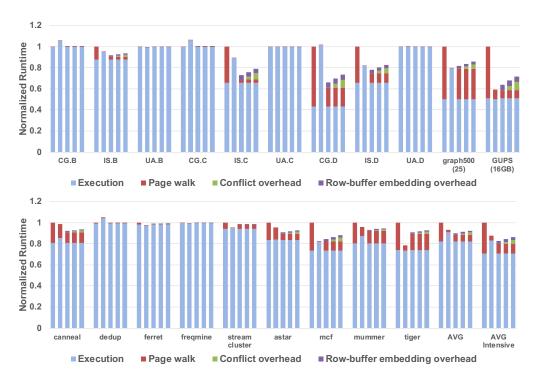

| 5.11 | Performance of 4KiB pages, THP, Embedded Page Translation Information with $0\%$ , $5\%$ , $10\%$ conflicts (left to right)  | 70  |

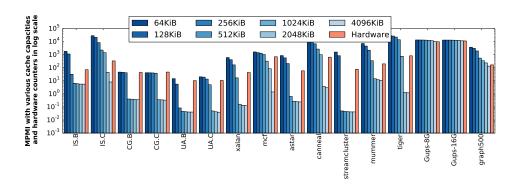

| 6.1  | MPMI (misses per million instructions) of page walks with various cache capacities and hardware counters                     | 76  |

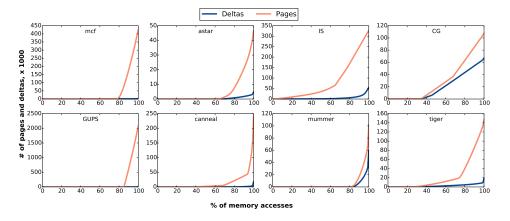

| 6.2  | Number of pages and deltas over memory accesses                                                                              | 77  |

| 6.3  | Delta Caching overview                                                                                                       | 79  |

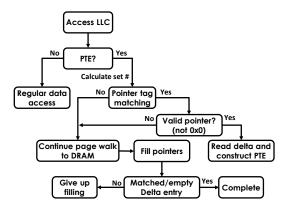

| 6.4  | Flow of cache accessing                                                                                                      | 80  |

|      |                                                                                                                              | 81  |

| 6.5  | A delta array entry                                                                                                          | _   |

| 6.6  | Address mapping for dual caching                                                                                             | 86  |

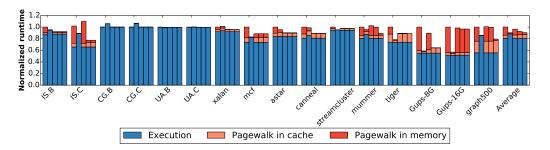

| 6.7  | Normalized page walk-memory accesses with delta caching                                                                      | 91  |

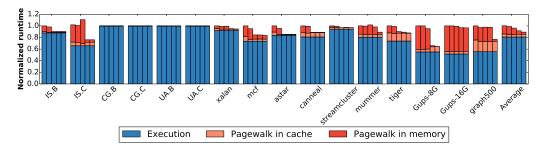

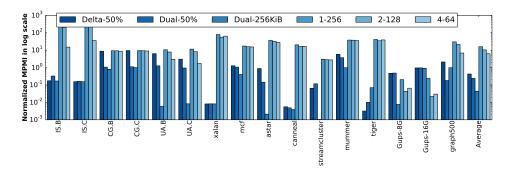

| 6.8  | Normalized page walk-memory accesses with dual caching                                                                       | 92  |

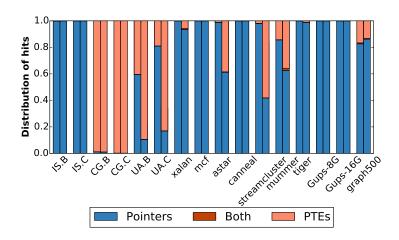

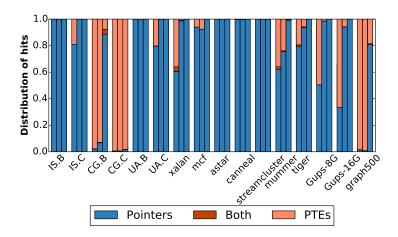

| 6.9  | Distribution of hits with dual caching                                                                                       | 93  |

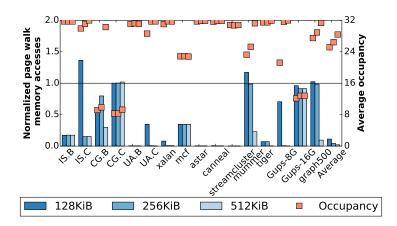

| 6.10 | Normalized page walk memory accesses with fixed sized delta array                                                            | 94  |

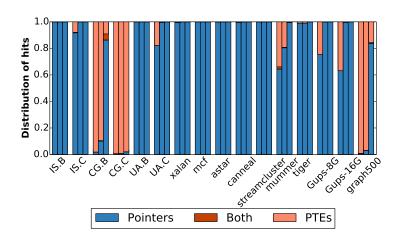

| 6.11 | The distribution of hits (left to right: 128KiB, 256KiB, 512KiB)                                                             | 95  |

| 6.12 | The distribution of run time (left to right: 4KiB Baseline, THP, Dual caching with 128KiB, 256KiB, 512KiB delta array)       | 95  |

| 6.13 | The distribution of run time (left to right: 4KiB Baseline, CoLT only, CoLT + Dual caching with 128KiB, 256KiB, 512KiB delta | 06  |

| 0.14 | array                                                                                                                        | 96  |

|      | The distribution of hits (left to right: 128KiB, 256KiB, 512KiB)                                                             | 96  |

| 6.15 | Impact of LLC capacity reduction                                                                                             | 98  |

| 6.16 | Normalized page walk-memory accesses with different fragmentation levels                                                     | 99  |

| 6 17 | Normalized page walk memory accesses                                                                                         | 103 |

## Chapter 1

### Introduction

Virtual memory has been introduced to computer systems for efficiency, programmability, and security. It creates a contiguous address space for each process, such that programmers are not required to deal with fragmentation or overlays of physical memory explicitly. In addition, virtual memory enables fine granularity memory mapping. In state-of-the-art systems, this mapping is usually achieved with 4 KiB pages. By mapping virtual memory to physical memory with such fine-grained pages, non-contiguous physical memory can be efficiently utilized to satisfy contiguous virtual memory allocations. Virtual memory also provides various metadata, including access permissions, page attributes, and access information, which are necessary for correct and efficient system operation. In fact many additional uses of metadata such as tracking access counts [59] and monitoring memory accesses [85] have been proposed.

## 1.1 The Cost of Fine-Grained Paged Virtual Memory

Everything comes at a cost. State-of-the-art virtual memory cannot provide all features mentioned above while keeping the overhead low. Three major issues with current virtual memory systems are summarized below:

- (1) The fine-grained virtual to physical mapping may change access patterns between virtual and physical address spaces. This indirection brings difficulties to many architecture techniques. For example, virtually indexed, physically tagged (VIPT) caches can only be indexed with partial addresses within a page boundary. For physical address based prefetching mechanisms, crossing page boundaries can be harmful [23]. These either directly hurt performance, or constrain trade-off options, leading to sub-optimal designs.

- (2) Main memory and most caches are physically addressed. Before accessing them, address translations must be performed. In standard 4 KiB paged virtual memory, the memory mapping is stored in page tables with each entry containing the translation information and other metadata for a page. To reduce page table storage, radix tree structures are employed in most architectures, including x86 [41] and ARM [6]. Each translation is obtained by a page walk with multiple sequential memory look-ups. Mechanisms such as translation lookaside buffers (TLBs) and memory-management unit (MMU) caches are used to accelerate this look-up process. But these on-chip structures cannot be scaled up efficiently. For page walk intensive workloads, up to 83.1% of execution time may be spend on page walks in a processor with a 2-level TLB and MMU caches [9].

- (3) Metadata caching is critical. While dedicated buffering structures, such as TLB and MMU caches, are used for better performance, the total capacity is constrained by limited on-chip storage. Caching metadata in the regular data cache hierarchy also plays an important role in reducing the la-

tency of address translation [64, 72]. Current caching schemes for metadata that simply treat metadata as regular data fail to maximize storage efficiency. The redundancy of page-grained metadata has been investigated by Basu et al. [9] who find that the per-page permissions are identical for vast majority of pages. Prior research [89, 70] also suggests that the contiguity of address mapping generally exists beyond a page boundary. Therefore, the mapping of many pages in the same contiguously-mapped region can be represented with a single delta between virtual addresses and physical addresses and a single set of permissions.

## 1.2 The Real Implications of Fine Granularity

Enormous effort has been spent on reducing the cost of fine-grained virtual memory, mainly in two directions. The first is to strictly keep fine-grained virtual memory and focus on improving microarchitectural support, such as introducing larger and more efficient TLBs and MMU caches. The second direction completely gives up on fine granularity and employs a coarser granularity, exchanging flexibility, compatibility, programability, and fine-grained metadata for lower overhead. Instead of going to either extreme, I identify better tradeoffs between fine and coarse granularity memory management. As an example, previous work [70] and my experiments (Figure 6.2) show that memory mapping is frequently contiguous across page boundaries, even with the standard 4KiB paged virtual memory. Maintaining fine-grained mapping within a contiguously-mapped region is not necessary, yet it wastes storage

space and incurs runtime overhead. At the same time, coarser memory mapping granularity can be carefully used within the contiguously-mapped region without hurting the flexibility of fine-grained memory mapping. In this dissertation, I explore a pay-as-you-go approach for supporting fine-grained pages. Compatibility-wise, I do not compromise the ability to use fine-grained paging. Programmers are always free from porting source code. Performance-wise, I propose various schemes to remove the unnecessary overhead, utilize the "free" contiguity mentioned above, and make sure the cost of fine-grained virtual memory is paid only when necessary.

#### 1.3 Thesis Statement

Current fine-grained paged virtual memory provides appealing features with significant overhead, e.g., long translation latency and changed access patterns. Future virtual memory systems can reduce this overhead and approach the overhead of coarse-grained paging without compromising programmability, efficiency, and metadata.

#### 1.4 Contributions

The goal of my dissertation is to enable efficient fine-grained paged virtual memory mechanisms that resolve the issues mentioned above, without compromising existing benefits. To achieve this goal, I develop user-transparent, low-overhead architecture mechanisms on top of existing, standard computer systems that improve system efficiency while maintaining back-

ward compatibility. In the first part of this dissertation I analyze issues in existing state-of-the-art systems, and evaluate their impact. In the second part of the dissertation, I propose various novel architecture mechanisms to address these issues, quantitatively evaluate the effectiveness of proposed mechanisms, and compare with prior work. To summarize the main contributions of my dissertation:

- I examine the restriction of virtually indexed, physically tagged (VIPT) caches with fine-grained paging and conclude that this restriction may lead to suboptimal cache designs. I introduce a novel cache strategy, speculatively indexed, physically tagged (SIPT) to enable flexible cache indexing under fine-grained page mappings. SIPT speculates on the value of a few more index bits (1 3 in our experiments) to access the cache speculatively before translation and then verify the physical tag match after translation. Utilizing the fact that a simple relation generally exists between virtual and physical addresses, because memory allocators often exhibit contiguity, I also propose low-cost mechanisms to predict and correct potential mis-speculations.

- I propose a novel architecture mechanism, Embedded Page Translation Information (EMPTI), to provide general fine-grained page translation information on top of coarse-grained virtual memory. EMPTI does so by speculating that a virtual address is mapped to a pre-determined physical location and then verifying the translation with a very-low-cost

access to metadata that is embedded with the data. Coarse-grained virtual memory mechanisms (e.g. segmentation) are used to suggest the pre-determined physical location for each virtual page. Overall, EMPTI achieves the benefits of low overhead translation while keeping the flexibility and programmability of fine-grained paging.

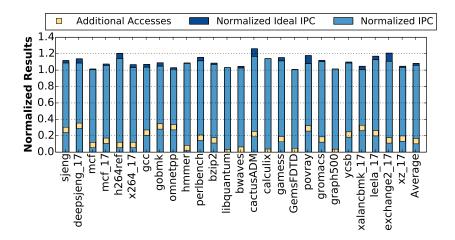

• I revisited prior research on address mapping contiguity and redundancy of per-page permissions, and propose Delta Caching to achieve more efficient, yet flexible metadata caching. Delta caching provides up to 4× higher storage density than when 4KiB page table entries are stored as data, and does not compromise mapping flexibility and fine-grained metadata. By converting DRAM accesses incurred during page walks into LLC hits, delta caching removes a substantial fraction of page walk overhead, when combined with existing techniques, Delta Caching outperforms THP.

## 1.5 Dissertation Organization

The rest of this dissertation is organized as follows: Chapter 2 provides background on virtual memory and clarifies terminologies; Chapter 3 discusses challenges this dissertation tries to address; Chapter 4 revisits design constrains in virtually indexed, physically tagged (VIPT) caches. I propose speculatively indexed, physically tagged (SIPT) caches to remove these constrains. I evaluate the benefit in terms of both performance and energy. Chapter 5 focus on reducing the cost of virtual to physical translation. I present and

evaluate Embedded Page Translation Information (EMPTI). With EMPTI, low translation overhead and fine-grained paging can be achieved at the same time. Chapter 6 address the inefficiency of current metadata storage in the data cache hierarchy by introducing Delta Caching. Chapter 7 concludes this dissertation.

## Chapter 2

## Background and Terminology

## 2.1 Fine-Grained Virtual Memory

The standard 4 KiB paged virtual memory has evolved into the dominant memory management scheme. Its strength is that virtual pages are a single abstraction for all memory-management needs and their fine-grained nature and flexible mapping enable numerous optimizations and system functions. Page-based virtual memory works by having applications only use virtual addresses, which are then mapped to physical addresses via an OS-maintained page table. Because of increasing memory capacities, current systems utilize a multi-level hierarchical page table structure. As an example, current 64-bit x86 processors from Intel [41] and AMD [1] use a 4-level page table.

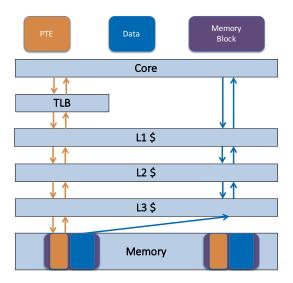

Before accessing data, a memory operation must translate the virtual address into a physical one, requiring a page walk with up to 4 memory accesses for address translation, on top of the memory access for the data (Figure 2.1). For each level, the corresponding entry can be located by adding an offset from part of the virtual address to the base address from a pre-defined register (CR3 in x86) or the result of last level. By repeating this look-up 4 times, an L1 Page Table Entry (PTE, Figure 2.2) from the hierarchical page table is

Figure 2.1: 4-level page walk in x86 architecture

Figure 2.2: A x86 page table entry

loaded to the MMU. The MMU then decodes the PTE, and uses the upper bits of the page base address or physical frame number (PFN) to locate the physical base address of the page. The metadata in the permission bits are also checked. With the PFN and offset bits within the virtual address, the actual data can then be located and accessed in physical memory.

#### 2.1.1 Translation Lookaside Buffers

To overcome the latency of indirection, translation lookaside buffers (TLBs) are used [29]. By caching address mapping information in a dedicated hardware buffer, TLBs eliminate the overhead of fetching paging information from memory in most cases. However, some applications have poor spatial locality and exhibit frequent TLB misses, which significantly impairs application performance as memory is repeatedly accessed to perform translations [57, 9].

Various techniques have been proposed to improve the efficiency of

TLBs. TLB clustering [69] enlarge the reach of a TLB by storing mapping of contiguous pages as one TLB entry. Prefetching is another technique that has been proposed for improving TLB hit rate and shows benefits for some applications [44, 55, 76]. However, the effectiveness of these techniques is limited by their ability to identify access patterns, which proves challenging for applications that make irregular memory accesses.

An early alternative to TLBs is the use of *inverted page tables* [16]. Instead of caching translations on chip, inverted page tables act as a large in-memory cache of translations. Part of the virtual address is used directly, or after hashing, as a physical address into the inverted page table, and on a hit, the inverted page table returns a tag to verify whether the translation information is valid for the virtual address that queried it. Inverted page tables decrease, but do not eliminate, the number of memory accesses required to fill a TLB entry.

#### 2.1.2 Memory-Management Unit (MMU) Caches

Another approach is to utilize the hierarchical page structure to increase coverage by caching page directory entries (L2 PTEs, L3 PTEs, and L4 PTEs in Figure 2.1) in a dedicated MMU cache [8, 12, 41, 11]. This approach increases translation caching coverage effectively for some applications, but still suffers from memory accesses for page table levels that are closer to the leaves of the page table radix tree.

### 2.2 Coarse-Grained Virtual Memory

The standard 4 KiB paged virtual memory provides appealing features such as flexible address mapping and fine-grained metadata. However, address translation in such a fine granularity can still be very costly even with state-of-the-art processors with a 2-level TLB and MMU caches [9]. In contrast, another solution is to coarsen the granularity of address mapping. Although various schemes have been previously proposed or implemented, in general, there are three approaches to employ coarser granularity. One big issue with all these schemes is compatibility with many existing system features and optimizations.

#### 2.2.1 Direct Segments

Direct segments [18, 20, 9] use range-based translation, in which large contiguous virtual regions are mapped to contiguous physical ones. Regions and segments make translation simple and practically eliminate all translation overhead. However, the absence of fine granularity protection and mapping does place limitation on system management and application characteristics. This can significantly limit their applicability. Developers need to find memory allocations that can be safely managed by direct segments. Source code modification is also required to opt-in or opt-out of direct segments explicitly. And, there is significant porting effort of libraries. This deficiency can be addressed by increasing the number of regions and thus more closely approaching the flexibility of fine-grained pages only when necessary. However, when the num-

ber of regions grow, the same issues as TLB coverage and TLB misses arise. Segments have been popular in the past for specialized high-performance and embedded systems, but have lost popularity to ubiquitous standardized paging schemes or have been combined with paging [73, 74].

#### 2.2.2 Coarse-Grained Pages

Superpages [82, 81, 63] and hugepages [14, 53, 5] enlarge the standard translation granularity to improve the effectiveness of the TLB and reduce translation overhead. By enlarging the granularity of address mapping and management, the coverage of the TLB can be increased. However, larger page sizes increase the working set size [83], rely on large contiguous memory regions, and fail to provide fine granularity protection. Holes between small non-continuous regions can lead to wasted memory. A single 4KiB dirty page can cause the write back of the whole mostly clean large page in current hardware implementations [5, 14]. Even for applications with suitable memory behavior, it is challenging to use coarse-grained pages because the optimal page size depends on the application, system, and dynamic characteristics of the inputs. Note that academic research on superpages addresses some of these limitations, but not all [82, 81]. For example, in NUMA systems, large pages may lead to performance loss due to load imbalance and poor locality, which might entirely offset the benefits from fewer page walks [27]. In addition, forming coarser pages requires management in the OS and adds overhead that can be significant. This is apparent with the THP mechanism of Linux for which I measure significant management costs with some benchmarks (e.g., 24% for IS.C and 10% for mcf), and the active effort to improve OS support [52].

#### 2.2.3 Redundant Memory Mappings

Redundant Memory Mappings (RMM) [46] maintain both region-based translation information and fine-grained pages for the same addresses to improve performance while maintaining compatibility when fine-grained pages are a necessity. The TLB reach is increased with a range TLB and the regular TLB can take care of any non-contiguous spaces. However, the fine granularity metadata is not available in a range TLB and extra OS-management effort is required. For example, the OS may be required to allocate consecutive physical pages to consecutive virtual pages eagerly at allocation time and set accessed and dirty bits at allocation time, instead of relying on hardware to maintain this information dynamically, increasing overhead and potentially significantly coarsening the granularity of writing data out of memory. The OS must also maintain and apply policies for breaking regions and coalescing pages.

## 2.3 L1 Cache Indexing

Due to its critical impact on performance, much effort has been invested to improve L1 performance. The L1 presents challenging tradeoffs between hit rate and access latency. Access latency includes the virtual memory address translation latency (TLB lookup), tag array access and matching, and the data access itself. In order to push latency down, all three components should ideally overlap. Tag and data accesses are overlapped by accessing all ways simultaneously and delivering only tag-matching data (with a switch or multiplexer). Overlapping those two accesses with address translation is more challenging because an access can not start before the address is known. The simplest cache design indeed performs translation before L1 access begins. This design is called a *physically-indexed physically-tagged* (PIPT) cache because virtual addresses (VAs) are not used at all in the L1. While simple, the translation overhead is not hidden and access latency is often considered too high. Current designs solve the latency problem and enable access and translation overlap in one of two ways.

#### 2.3.1 Virtually Indexed, Virtually Tagged Caches

The first solution is to translate virtual addresses (VAs) after the L1 is filled, thus accessing the cache purely with VAs. This design is known as virtually-indexed virtually-tagged (VIVT) and eliminates the translation latency for accessing the cache. However, relying purely on VAs for most memory accesses (as most are L1 hits) presents significant complications for cache management and coherence because software maps multiple VAs to the same physical address (synonyms) and may also map the same virtual address to multiple physical addresses across different address spaces (homonyms). Prior work has developed solutions, but the design is more complicated than

the VIPT alternative, described below [48, 30].

#### 2.3.2 Virtually Indexed, Physically Tagged Caches

The second solution relies only on the offset bits of the VA for computing L1 array locations; the offset bits are not translated and can hence be used at the same time translation proceeds. Before data is delivered, the tag is compared to the fully translated physical address (PA). This design is called virtually-indexed physically-tagged (VIPT). Virtually indexed, physically tagged (VIPT) caches are more appealing and popular among all three variants (PIPT, VIVT and VIPT) because they combine the strong correctness and simple coherence guarantees of PIPT caches with practically zero-latency translation. All addresses have the full physical address available through the tags for correctness and coherence. At the same time, the latency of translation can be fully hidden by accessing the cache arrays in parallel with only the page offset bits that are never modified by address translation. However, the important tradeoff made is the constraints on cache parameters. Specifically, each set is limited in capacity to a single virtual memory page. Therefore, the cache capacity is coupled with its associativity: capacity = #ways  $\times$  4KiB, assuming common 4KiB page granularity. For example, many current processors have 32KiB 8-way set-associative caches [10, 15, 19]. While high associativity reduces the conflict miss rate it also adds latency, which is potentially a suboptimal design point when compared to a larger lower-associativity cache. Furthermore, L1 cache access energy is also coupled with associativity because all ways are typically accessed in parallel to reduce latency.

## Chapter 3

### **Problem Statement and Motivation**

# 3.1 VIPT Cache Design Space with Fine-Grained Page Mapping

With a conventional virtually indexed, physically tagged (VIPT) data L1 cache, the cache associativity is inflated in order to provide sufficient capacity while meeting the VIPT indexing constraint. For example, Intel Haswell processors, have a 32KiB 8-way set-associative L1 data cache with 4-cycle access latency. This constraint in VIPT caches design may lead to suboptimal configurations.

I explore the capacity and associativity design space with Cacti 6.5 [62], and use the Haswell L1 cache configuration as the baseline. I simulate L1 caches with the configurations and parameters summarized in Table 3.1 and present the latency of the different configurations relative to the baseline in Figure 3.1. For each capacity and associativity, I sweep the number of read ports and the number of banks and show the range and mean of relative latencies for each configuration. The baseline for each bank/port configuration is always 32KiB with 8 ways.

While both capacity and associativity affect latency, associativity has

| Technology      | 32 nm                        |

|-----------------|------------------------------|

| Cache line size | 64 Bytes                     |

| Capacity        | 16 KiB, 32 KiB,              |

|                 | 64 KiB, 128 KiB              |

| Associativity   | 2-way, 4-way, 8-way,         |

|                 | 16-way, 32-way               |

| Access mode     | Parallel data and tag access |

| Ports           | 1 or 2 for read,             |

|                 | 1 for write                  |

| Banks           | 1, 2 or 4 banks              |

Table 3.1: L1 cache configurations.

Figure 3.1: L1 cache latency relative to 32KiB 8-way baseline.

the greater impact. This is especially the case when increasing associativity from 4 to 8 ways. For example, we can reduce the latency of a 32KiB cache to 2 cycles by reducing its associativity to 2 ways. However, this configuration is not possible with VIPT and 4KiB pages because it needs 13 index bits, one more than the 12 offset bits of the page. Configurations that are not feasible for VIPT are shaded light blue while those that are feasible are shaded dark blue. Unfortunately, perhaps the most desirable configurations are currently infeasible.

The next question is what impact these tradeoffs have on application performance. I run applications from SPEC CPU 2006 [35] suite and SPEC CPU INT 2017 [80] with reference inputs. In addition to the large-memory footprint applications of SPEC INT 2017 (>8GiB for many), I also evaluate large-memory big-data applications: graph500 (graph processing) [32] and DBx1000 with the ycsb workload (database) [87], each configured to use more than 4GiB of memory. For each application I collect 500 million instructions at a SimPoint [79]. While different applications exhibit different characteristics,

Figure 3.2: IPC with various L1 cache configurations for an OOO core, normalized to the baseline L1.

Figure 3.3: IPC with various L1 cache configurations for an in-order core, normalized to the baseline L1.

both big-data applications and the large-footprint SPEC 2017 applications are not outliers w.r.t. SPEC CPU 2006 applications.

I simulate both an OOO core with a 3-level cache hierarchy and an in-order core with a 2-level cache hierarchy. Based on the results shown in Figure 3.1, four desirable configurations are selected. The detailed parameters are listed in Table 4.1 of Chapter 4. Note that these configurations are not feasible due to the VIPT cache-indexing constrains.

In conclusion, relaxing the indexing constrains in a VIPT cache and enabling larger capacity and/or lower latency can be very beneficial. However, it is correct only if the extended bits also remain the same after address translation. Handling these extra index bits and guaranteeing the correctness properly is challenging.

#### 3.1.1 Challenge I: Enabling Effective Cache Indexing

I propose speculatively indexed, physically tagged caches, where every cache access starts with speculatively accessing the L1, assuming that all necessary index bits will remain the same after translation. Then correctness is validated after address translation, which is done in parallel to tag matching with the VA. If the speculation succeeds, the data can be served as fast as a VIPT cache. If it fails, another access with index bits from the newly translated physical address will be issued, and in this case SIPT works in the same way as a PIPT cache. Obviously, the speculation efficiency is critical to SIPT. I propose to use a light-weighted predictor to improve speculation accuracy. Ideally, the predictor identify accesses with unchanged index bits, continues speculation with them, and furthermore, predicts the correct index bits in the PA for those accesses in which index bits are changed by translation.

# 3.2 Deficiency of Address Translation in Fine-grained Paging

When a translation misses in the TLBs, a page walk is required to complete translation. As illustrated in Figure 2.1, the page walk in hierarchical page tables requires multiple memory accesses. These memory accesses increase the pressure on the memory sub-system. For example, with x86 4-level page tables, one data access may require 5 memory accesses in the worst

case. In addition, most caches and main memory are physically addressed, the translation must be completely finished before issuing the memory access for data. The page walk latency is on the critical path of these data accesses. It should be noticed that previous work suggests page walks typically hit in the data cache hierarchy [45]. However, because of the large gap in the latency of main memory and the caches, even the few page-walk requests that miss the caches have significant overhead [24].

#### 3.2.1 Challenge II: Page Walk Latency

The first challenge addressed in this dissertation is the long latency of page walks. Many techniques have been proposed to improve the TLB hit rate by prefetching or coalescing TLBs [44, 55, 76, 69], but they all rely on certain access pattern of applications. Various MMU cache schemes [8, 12, 11] are used to enlarge the coverage of partial translations if a TLB miss occurs. However, even a perfect MMU cache may still suffer from the numerous accesses to the last level of the page walk. Both TLBs and MMU caches are on-chip structures and scaling them to match the growing of memory capacity is impossible. Even with large, multi-level TLBs to reduce the frequency of page walks and MMU caches to reduce the number of memory accesses per page walk, the page walk overhead can still exceed execution itself [9]. Reducing the latency of page walks, especially when a page walk access misses the last-level data cache is critical. As an orthogonal solution to reduce address translation overhead, I propose Embedded Page Translation Information (EMPTI)

to embed translation information and other metadata with data. Thus, the data access and address translation can be done with only one memory access and the latency of the page walk can be avoided. However, this simple idea has one big flaw: even if we have data and translation information co-located and they can be accessed with one access, we still need to know the location first. I propose to resolve this issue by utilizing coarse-grained virtual memory schemes and employ EMPTI on top of them.

# 3.3 The Absence of Fine-Grained Metadata in Coarsegrained Virtual Memory

Coarse-grained virtual memory schemes such as direct segments, huge pages, and RMM can effectively reduce address translation overhead. By enlarging the granularity of address mapping, the address space can be managed with minimal amount of translation information. However, coarsening the granularity of translation sacrifices the fine-grained metadata that is available with fine-grained pages. Not having this metadata can be problematic. For instance, many libraries need to be ported if changing the page size and protection and clean/dirty status may incur large overheads when not fine enough. Even as previous work [9, 46] claims that many memory regions do not require fine-grained metadata, they rely on developers to modify code and give directives for opt-in and opt-out coarse-grained virtual memory. These directives have to be precise and absolutely correct. In addition, coarse-grained translation requires address coalescing. Because the coarse-grained mapping admits

no exceptions in a single contiguous region, any conflicts need to be resolved by employing smaller regions. In summary, I conclude that the absence of finegrained metadata in coarse-grained virtual memory reduces programmability and flexibility, introducing significant challenges in many contexts.

#### 3.3.1 Challenge III: Coupled Translation and Metadata

The second challenge addressed in this proposal is coupling translation and metadata. Conventionally, translation information and metadata are managed in the same structure and maintained in the same granularity. This legacy unnecessarily limits our design space and introduces the dilemma that we wish to utilize coarse-grained translation for speed but desire the programmability and flexibility benefits of fine-grained metadata. I propose to separate the granularity of address mapping and metadata management in a novel way that maintains the full richness of current metadata at fine-grained page granularity while achieving efficient translation. Specifically, a coarsegrained virtual memory (e.g. direct segments) will be used to manage address translation, but this translation is treated as a speculative hint. When accessing memory translation information in EMPTI will be checked to validate the speculation. If speculation fails, the conventional page walk will be employed to ensure the correctness. With EMPTI, metadata are always maintained in fine granularity and the per fine-grained page translation information enables gaps in mostly contiguous regions.

## 3.4 Metadata in the Data Cache Hierarchy

The overhead of page-table based virtual memory address translation and metadata access continues to be a significant challenge [9]. I observe that while translation-specific caching structures (e.g., TLBs and page-walk caches [8]) are very important, the regular data cache hierarchy also plays an important role in reducing the latency of address translation [64, 72]. My study in Chapter 6 shows that PTEs can take substantial LLC capacity. On an Intel Core i5-4590 processor with 32GiB main memory, PTEs take up to 4MiB out of the 6MiB LLC.

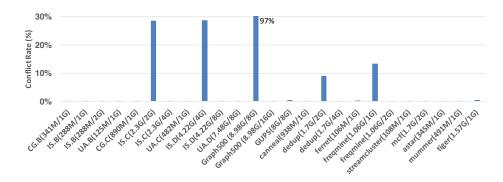

## 3.5 Redundancy in Metadata

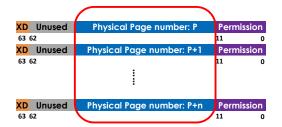

Previous work suggests two types of redundancy in metadata. First, it is not necessary to keep a copy of permissions for every page because the vast majority of pages (more than 99%) use the same permissions (readable and writable) [9]. In addition, the physical address takes the largest space in a PTE (Figure 3.4a), while previous work [70] suggests that the OS naturally assigns contiguous physical pages to contiguous virtual pages (Figure 3.4b). Thus, all pages in the same contiguously-mapped region share the same delta between virtual addresses and physical addresses. By storing one delta for a contiguously-mapped region instead of physical addresses for all pages, significant cache space can be saved and more pages can be cached with the same capacity.

(a) Page table entries in a contiguously-mapped region (x86).

(b) Virtual to physical address mappings with cross page contiguity.

Figure 3.4: Natural address mapping contiguity.

#### 3.5.1 Challenge IV: Efficient Metadata Caching

Metadata are usually small-sized supporting data to serve various functionality of the system. Yet, metadata can take a substantial fraction of cache capacity in state-of-the-art processors. At the same time, the highly redundant nature of metadata indicates opportunities for more efficient representation and storage. I propose to use Delta Caching for better caching efficiency of page tables. Delta caching modifies the PTE by replacing the physical frame number with the delta between virtual address and physical address. All pages in the same contiguously-mapped region can be represented with it. For each page, instead of storing a full 8B PTE, a 2B pointer to a separate delta array

is stored. Because this pointer (2-byte in our design) is much shorter than 8-byte PTE, the overall cache efficiency increases.

# Chapter 4

## Flexible L1 Caches with Fine-grained Paging

As discussed in Chapter 3, relaxing index restrictions expands the design space of L1 caches and enables more trade-offs. In this chapter, we focus on how to make these appealing cache configurations feasible. <sup>1</sup>

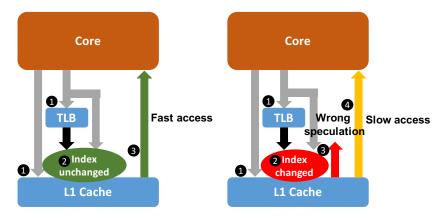

## 4.1 Speculatively Indexed, Physically Tagged Caches

We proposed speculatively indexed, physically tagged (SIPT) caches to handle the situation that cache indexing bits beyond the page boundary may change during address translation. The simplest variant of SIPT always speculatively accesses the cache assuming that all necessary index bits will remain the same after translation, including those beyond the page granularity. SIPT, Like VIPT, performs address translation in parallel to accessing the cache arrays (Step 1 in Figure 4.1). For performance, all ways are accessed together so that overall latency can be reduced. After address translation, all cache tags read in Step 1 are compared with the physical addresses to

<sup>&</sup>lt;sup>1</sup>This chapter is based on a published work [89], T. Zheng, H. Zhu and M. Erez, "SIPT: Speculatively Indexed, Physically Tagged Caches," 2018 IEEE International Symposium on High Performance Computer Architecture (HPCA), Vienna, 2018, pp. 118-130. I proposed and evaluated the main ideas and collaborated with H. Zhu and M. Erez to accomplish this work.

select the correct cache line. At the same time, SIPT compares those index bits that were speculated with their values after address translation (Step 2 in Figure 4.1). If all speculated bits indeed are the same the "fast" access completes (Step 3). If any of the speculated bits do not match, the cache request must be repeated with the correct index bits from the PA (Step 4), slowing down the access. Fast accesses are as fast as a VIPT cache, or faster if the relaxed design constraints enable a lower-latency configuration. A slow access, on the other hand, only issues after address translation like a PIPT cache. In addition every slow access wastes energy and contends for the L1 cache port. Note that there are no coherence implications because only the L1 cache is accessed speculatively and no action (other than another access) is taken on a misprediction (tag mismatch).

Figure 4.1: SIPT cache access when speculated index is unchanged (left) and changed (right).

#### 4.1.0.1 Speculation Accuracy

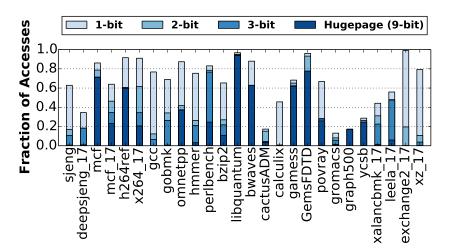

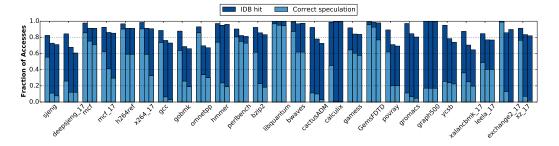

Figure 4.2 shows the percentage of memory accesses that are speculated correctly, depending on how many speculative index bits are required. Each component of each stacked bar in the figure represents fast accesses for the number of bits required and all other accesses are slow. The most strict scenario, hugepage includes only those accesses from huge pages (for which 21 address bits are guaranteed not to change).<sup>2</sup> While some applications (e.g., libquantum and zeusmp) have most accesses targeting transparently mapped huge pages, many others have the vast majority of accesses to normal 4KiB pages. Those applications with a low correct speculation rate are likely to suffer performance degradation with SIPT compared to the VIPT baseline.

Reasonable L1 configurations, however, do not use 2MiB sets  $(2^{21})$  and only require 1-3 index bits beyond the page granularity. In these scenarios, the correct prediction rate is much higher overall. If only a single speculative index bit is needed (e.g., for a 32KiB 4-way L1), all but two applications (gromacs and CactusADM) have majority fast accesses.

#### 4.1.1 Naive SIPT Performance

To evaluate the performance of this naive version of SIPT, which always speculates, we evaluate different SIPT configurations with the detailed

<sup>&</sup>lt;sup>2</sup>We run Linux 3.12 with transparent hugepage management turned on and collected our traces on a system that is regularly used and which had an uptime of weeks. In the dissertation, we will include results with a fragmenter form Ingens [52] running in the background to mimic an extremely fragmented system.

Figure 4.2: Fraction of correct speculations vs. the number of index bits that must be predicted.

parameters shown in Table 4.1, and compare to the baseline L1. We focus on OOO core and only show the results for the 32KiB 2-way SIPT configuration (with 2 extra index bits), which performs the best as an ideal cache in an OOO processor. Figure 4.3 summarizes the results and shows the IPC normalized to the baseline, and compares with the ideal cache. The figure also shows relative extra accesses due to misspeculation  $\left(\frac{\text{accesses}_{SIPT}}{\text{accesses}_{baseline}} - 1\right)$ .

SIPT caches with lower associativity and shorter latency achieve IPC improvement in many applications; e.g., h264ref, and perlbench, exhibit 7.3% and 8.9% IPC speedup. However, because speculative bits are used, naive SIPT suffers a high misspeculations rate. For example, in some applications, e.g., calculix and gromacs, less than 5% speculations succeed with 2 extra index bits. When misspeculations happen, SIPT generates slow accesses.

Similarly in Figure 4.4, we show the relative energy  $\left(\frac{E_{\text{SIPT}}}{E_{\text{baseline}}}\right)$  of the

|      | In-Order processor with                                  |         | Out-of-Order processor with  |              |

|------|----------------------------------------------------------|---------|------------------------------|--------------|

|      | 2-level cache hierarchy                                  |         | 3-level cache hierarchy      |              |

| Core | 2-wide, in-order                                         |         | 6-wide issue, OOO            |              |

|      | $3.0~\mathrm{Ghz}$                                       |         | 192-ROB, 3.0 GHz             |              |

| TLB  | L1: 64-entry, 4KiB pages; 32-entry, 2 MiB pages, 2-cycle |         |                              | ges, 2-cycle |

|      | L2: 1024-entry unified, 7-cycle                          |         |                              |              |

| L1   | Configuration                                            | Latency | Energy per access            | Static power |

|      | 32KiB 8-way VIPT                                         | 4-cycle | 0.38 nJ                      | 46 mW        |

|      | 32KiB 2-way SIPT                                         | 2-cycle | 0.1 nJ                       | 24 mW        |

|      | 32KiB 4-way SIPT                                         | 3-cycle | 0.185 nJ                     | 30 mW        |

|      | 64KiB 4-way SIPT                                         | 3-cycle | 0.27 nJ                      | 51 mW        |

|      | 128KiB 4-way SIPT                                        |         | 0.29 nJ                      | 69 mW        |

|      | Slow access in SIPT starts right after TLB access        |         |                              |              |

| L2   | None                                                     |         | 256 KiB, 8-way, 12-cycle,    |              |

|      |                                                          |         | private, 0.13 nJ per access, |              |

|      |                                                          |         | 102 mW static power          |              |

| LLC  | 1 MiB, 16-way, 20-cycle,                                 |         | 2 MiB 16-way, 25-cycle,      |              |

|      | shared, 0.29 nJ per access,                              |         | shared, 0.35 nJ per access,  |              |

|      | 532 mW static power                                      |         | 578 mW static power          |              |

| DRAM | 8-bank, 4-channel, DDR3, 16 GiB total                    |         |                              |              |

| Note | LLC size increase proportional to                        |         |                              |              |

|      | core count for multi-core evaluation.                    |         |                              |              |

Table 4.1: Simulated system configurations

Figure 4.3: IPC and additional L1 accesses with a naive SIPT 32 KiB/2-way/2-cycle cache for an OOO core normalized to the baseline L1.

whole cache hierarchy and also compare with the ideal cache. Some applications such as libquantum and GemsFDTD exhibit energy savings close to ideal. However, many other applications exhibit significant gaps between naive

Figure 4.4: Cache hierarchy energy of naive SIPT 32KiB/2-way/2-cycle for an OOO core normalized to baseline.

SIPT and ideal. On average, naive SIPT reduces total cache energy to 74.4%, which is 8.5% worse than ideal. We also show the relative dynamic energy  $\left(\frac{E_{\rm dynamic}}{E_{\rm baseline\_total}}\right)$  for both SIPT and baseline. SIPT reduces dynamic energy significantly.

Overall, due to a high misspeculation rate, the naive SIPT is far from ideal. We now aim to both reduce extra L1 accesses and increase the number of fast accesses.

## 4.2 Predicting and Bypassing Misspeculations

In this section we evaluate a light-weight predictor that determines whether a fast access is likely to succeed, and speculation should proceed, or whether cache access should wait until after translation. Our goal is to make a speculate/no-speculate binary decision and we take inspiration from the rich

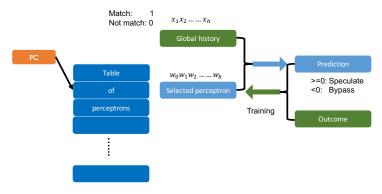

literature on branch direction prediction. Specifically, because we seek a light-weight predictor that can be used during instruction fetch, we evaluate a small Perceptron predictor [43].

We base our Perceptron predictor design (Figure 4.5) directly on the smallest global-history configuration proposed by Jimenez and Lin [43]. We add a global history register  $x_1x_2...x_h$  that tracks the last h speculation outcomes as ones and zeros (fast access success or extra cache access failure). The predictor itself has 64 entries each being a perceptron of h + 1 weights  $w_0w_1...w_h$ . We use the memory operation program counter (PC) to index the 64-entry predictor table. Because we only use the PC, the prediction can be overlapped with other pipeline stages.

Perceptron calculates a prediction (y) by performing a dot product of the history and the weights of a specific entry in the table plus a learned bias:  $y = w_0 + [x_1x_2...x_h] \cdot [w_1...w_h]$ . If y is positive, we predict the index will not change and will continue with a fast access using the speculative index. If y is negative we bypass speculation and wait for the physical address before accessing the cache. Other than the smaller number of entries, all details, training algorithm, and other parameters precisely follow those of Jimenez and Lin [43] and we do not describe them.

We estimate the overhead of this perceptron predictor at just 624B of storage and a small amount of logic (6b weights, 13 weights per perceptron, 64 perceptrons). We model perceptrons as RAM with Cacti [36] (Table 3.1). The dynamic energy for reading a perceptron is only 0.34% of a baseline L1

cache access. The static power is only 0.0007% of the baseline L1 cache. Song et al. [34] suggest a 32-bit integer addition consumes  $\frac{1}{10}$  the energy of reading 32 bits from a register file. Since  $x_1x_2...x_h$  are ones and zeros,  $y = w_0 + [x_1x_2...x_h] \cdot [w_1...w_h]$  is essentially adding h+1 (13 in our implementation) 6-bit integers and therefore estimated to consume less energy than reading the perceptron. Training consumes similar energy. This predictor introduces no extra latency and only negligible area and energy overheads.

Figure 4.5: Perceptron-based predictor.

We evaluate the predictor by considering four possible outcomes. If the speculated bits are unchanged by translation and the predictor decides to speculate, we call it *correct speculation*. If the speculated bits are changed by translation and the predictor decides to bypass, we call it *correct bypass*. If the speculated bits are unchanged by translation but the predictor chooses bypass, an opportunity for a fast access was squandered, we call this *opportunity loss*. Finally, if the speculated bits are changed by translation and the predictor chooses to speculate, an extra access is generated, we call this *extra access*.

Figure 4.6: Break down of prediction results into the four possible outcomes; each group of 3 bars represents 1, 2, and 3 speculative index bits (from left to right, respectively).

This simple perceptron predictor achieves more than 90% accuracy in all applications; in fact most applications have far fewer than 5% extra L1 accesses and negligible opportunity loss (Figure 4.6). We also evaluated the sensitivity of the predictor parameters such as increasing the number of perceptrons and increasing the history length. Our experiments did not show strong sensitivity to these parameters, most likely because the prediction rate is already high. Note that we do not warm up the predictor and the results include all mispredictions. We also evaluated the sensitivity of the predictor parameters such as increasing the number of perceptrons and increasing the history length. Our experiments did not show strong sensitivity to these parameters, most likely because the prediction rate is already high. We do not warm up the predictor and the results include all mispredictions. We also evaluated various counter-based predictors, but their average accuracy is only  $\sim 85\%$  and not consistent across applications. We omit the results for brevity and because the perceptron already has low overhead.

#### 4.3 Partial Index Prediction

Intuitively, if the speculation bypass predictor is so accurate at predicting whether speculative indexing can proceed, perhaps it can be extended to predict the actual post-translation index value. Consider an SIPT design that requires a single speculative index bit. In this case, if the bypass predictor predicts to bypass, it is in effect indicating that the speculative bit is most likely not remaining the same. Therefore, flipping the bit in these cases will lead to the correct post-translation index. Because the prediction accuracy is so high, few extra accesses are added by this technique.

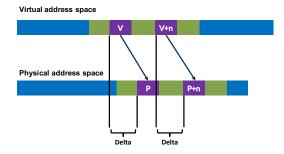

When there are multiple speculative tag bits, we need to predict their exact values, which is generally hard because with 3 speculative bits, it is likely that they may take any of 8 possible values. This requires a complex predictor or resulting many misspeculations. However, in the context of SIPT, predicting values is doable because of spatial locality in memory address mapping. Prior work [47, 9] establishes that memory addresses are usually mapped in coarsegrained blocks even without considering huge pages. And Pham et al. [70, 69] suggests the spatial contiguity between the virtual page numbers and physical page numbers.

Linux manages free pages using the buddy algorithm. Free pages are grouped into  $1, 2, 4, \dots 1024$  contiguous page frames and page groups of each size are then stored in linked lists. This scheme keeps the overhead of tracking free pages low.

Consider the scenario in which a user program allocates a large number of pages. This is common behavior when programs set up data structures during their initialization. The number of pages at fine-grained groups is unlikely to satisfy such requests. As a result, the buddy algorithm has to break large groups to satisfy bursts of memory allocation requests, which can lead to a significant amount of contiguous physical pages being mapped to a contiguous virtual address space. Other allocators, such as slab and eager paging [47], maintain contiguity explicitly. OS features such as Hugepages and page coloring also increase the occurrence of contiguously mapped memory blocks; page coloring tries to maintain the same low-order address bits between the VA and PA to maximize usage of the LLC.

Figure 4.7: Deltas between virtual and physical addresses are constant within a single large block.

The fact that large contiguous blocks exist aids with predicting speculative index bits. For all addresses in one contiguous range (A and B for example in Figure 4.7), the delta between a virtual address and its corresponding physical address is the same. Software may even optimize for SIPT,

though prediction rates are already high.

Figure 4.8: The index delta buffer predicts the delta between the speculative virtual address bits and corresponding physical address bits.