Copyright

by

Robert John Ascott

2014

# The Dissertation Committee for Robert John Ascott Certifies that this is the approved version of the following dissertation:

### **JAVAFLOW: A JAVA DATAFLOW MACHINE**

**Committee:**

Earl E. Swartzlander Jr., Supervisor

Anthony P. Ambler

Derek Chiou

Lizy K. John

Keshav K. Pingali

### JAVAFLOW: A JAVA DATAFLOW MACHINE

by

Robert John Ascott, BS; MSEE

### Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### **Doctor of Philosophy**

The University of Texas at Austin December, 2014

### Dedication

To my wife Virginia, David (1985-2009) and to Colin, Mason, Sofia, Cian, Quentin, and Laurelin whose world of technology will be far different than today.

### Acknowledgements

Sincere thanks to Professor Earl Swartzlander Jr. for his encouragement, patience, and continuously positive attitude which made this research enjoyable and productive. Also thanks to the myriad of technical and fellowship groups which maintained and expanded my mental, physical, and spiritual fitness over the past several years.

#### JAVAFLOW: A JAVA DATAFLOW MACHINE

Robert John Ascott, PhD

The University of Texas at Austin, 2014

Supervisor: Earl E. Swartzlander Jr.

The JavaFlow, a Java DataFlow Machine is a machine design concept implementing a Java Virtual Machine aimed at addressing technology roadmap issues along with the ability to effectively utilize and manage very large numbers of processing cores. Specific design challenges addressed include: design complexity through a common set of repeatable structures; low power by featuring unused circuits and ability to power off sections of the chip; clock propagation and wire limits by using locality to bring data to processing elements and a Globally Asynchronous Locally Synchronous (GALS) design; and reliability by allowing portions of the design to be bypassed in case of failures.

A Data Flow Architecture is used with multiple heterogeneous networks to connect processing elements capable of executing a single Java ByteCode instruction. Whole methods are cached in this DataFlow fabric, and the networks plus distributed intelligence are used for their management and execution. A mesh network is used for the DataFlow transfers; two ordered networks are used for management and control flow mapping; and multiple high speed rings are used to access the storage subsystem and a controlling General Purpose Processor (GPP). Analysis of benchmarks demonstrates the potential for this design concept. The design process was initiated by analyzing SPEC JVM benchmarks which identified a small number methods contributing to a significant percentage of the overall ByteCode operations. Additional analysis established static instruction mixes to prioritize the types of processing elements used in the DataFlow Fabric.

The overall objective of the machine is to provide multi-threading performance for Java Methods deployed to this DataFlow fabric. With advances in technology it is envisioned that from 1,000 to 10,000 cores/instructions could be deployed and managed using this structure. This size of DataFlow fabric would allow all the key methods from the SPEC benchmarks to be resident.

A baseline configuration is defined with a compressed dataflow structure and then compared to multiple configurations of instruction assignments and clock relationships. Using a series of methods from the SPEC benchmark running independently, IPC (Instructions per Cycle) performance of the sparsely populated heterogeneous structure is 40% of the baseline. The average ratio of instructions to required nodes is 3.5. Innovative solutions to the loading and management of Java methods along with the translation from control flow to DataFlow structure are demonstrated.

### **Table of Contents**

| List of Tables                              | xi  |

|---------------------------------------------|-----|

| List of Figures                             | xiv |

| Chapter 1: Introduction                     | 1   |

| Section 1.1 - Computing Challenges          | 1   |

| Section 1.2 - Hardware Background           | 3   |

| Section 1.3 - Software Background           | 4   |

| Chapter 2: JavaFlow Problem Statement       | 8   |

| Section 2.1 - Summary                       | 8   |

| Section 2.2 - Included Topics               | 8   |

| Section 2.3 - Excluded Topics               | 9   |

| Chapter 3: Related Work                     | 10  |

| Section 3.1 - Related Work Summary          | 10  |

| Section 3.2 - General Purpose Processors    | 10  |

| Section 3.3 - Compilation Techniques        | 12  |

| Section 3.4 - Special Purpose Java Machines | 14  |

| Section 3.5 - Dataflow Machines             | 18  |

| History and concepts:                       | 18  |

| Monsoon, Manchester                         | 23  |

| TRIPS                                       | 24  |

| WaveScalar                                  | 27  |

| Section 3.6 - JAVA                          | 29  |

| Section 3.7 – Summary                       | 36  |

| Chapter 4: JavaFlow Overview                | 37  |

| Section 4.1 - Overview                      | 37  |

| Section 4.2 - Instruction Nodes             | 41  |

| Section 4.3 - Limitations                   | 45  |

| Chapter 5: Benchmarks                                  | 46  |

|--------------------------------------------------------|-----|

| Section 5.1 - Overview                                 | 46  |

| Section 5.2 - Dynamic Mix Methodology and Results      | 48  |

| Section 5.3 - Static Mix Methodology and Results       | 55  |

| Section 5.4 - DataFlow and ControlFlow Analysis        | 58  |

| Section 5.5 - Summary                                  | 60  |

| Chapter 6: JavaFlow Detailed Description               | 63  |

| Section 6.1 - Functional Units                         | 63  |

| Serial Network                                         | 65  |

| DataFlow Fabric (Mesh Network)                         | 70  |

| Memory – General Purpose Processor Interface           | 72  |

| Section 6.2 - DataFlow Fabric Management               | 73  |

| Loading a Method                                       | 73  |

| DataFlow Address Resolution                            | 78  |

| Initialization and Execution Start                     | 84  |

| Management and Cleanup                                 | 85  |

| Section 6.3 - Method Execution                         | 86  |

| Instruction Group – Arithmetic/Logical/Move Operations | 87  |

| Instruction Group – Register Operations                | 89  |

| Local Read Instructions                                | 89  |

| Local Writes                                           | 90  |

| Local Increment                                        | 90  |

| Instruction Group – Storage Operations                 | 91  |

| Instruction Group – Service Operations                 | 92  |

| Instruction Group – Control Flow Operations            | 93  |

| Instruction Group – Special Instructions               | 96  |

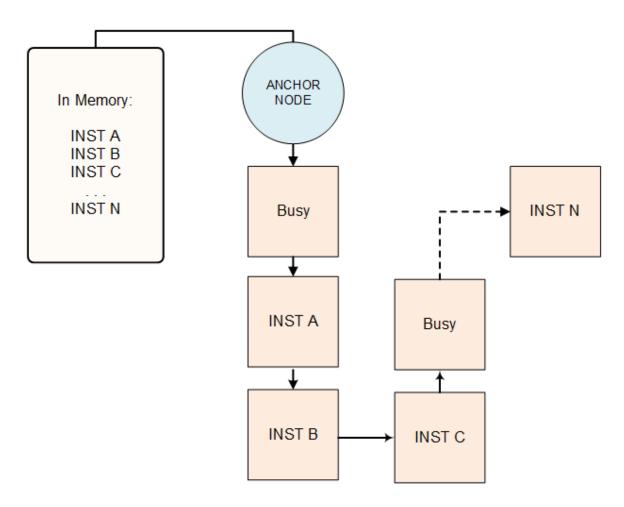

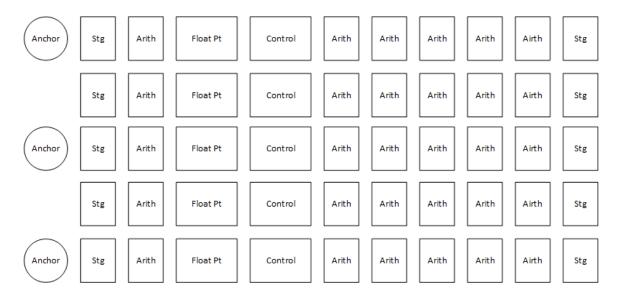

| Anchor Node                                            | 96  |

| Exceptions                                             | 97  |

| Section 6.4 - Enhancements                             | 98  |

| Section 6.5 - Summary                                  | 100 |

| Chapter 7: Results                           | 101 |

|----------------------------------------------|-----|

| Section 7.1 - Results Overview               |     |

| Section 7.2 - DataFlow Analysis              |     |

| Section 7.3 - Performance Analysis           |     |

| Measurement Strategy                         |     |

| Baseline configuration                       |     |

| Measurements                                 |     |

| Configurations                               | 107 |

| Method Execution                             | 109 |

| Filters on methods                           | 109 |

| Simulation Structure                         | 110 |

| Detailed Assumptions                         | 112 |

| Measurements                                 | 117 |

| Coverage                                     | 117 |

| Instructions per Cycle and Figure of Merit   | 119 |

| Parallelism                                  |     |

| Measurements vs Top 4 Spec Benchmark Methods |     |

| Chapter 8: Conclusions                       | 127 |

| Appendices                                   | 129 |

| Appendix A - ByteCode Instructions           |     |

| Appendix B - Data from top 90% Methods       | 140 |

| Appendix C - Sample analysis from one method | 145 |

| Appendix D - Benchmark Descriptions          | 151 |

| Glossary                                     | 154 |

| References                                   |     |

### List of Tables

| Table 1 Method Utilization in SPEC Benchmarks          | 50  |

|--------------------------------------------------------|-----|

| Table 2 Dynamic Instruction Mix of 90% Methods         | 51  |

| Table 3 SpecJvm2008 - Top 4 Methods                    | 53  |

| Table 4 SpecJvm98 - Top 4 Methods                      | 54  |

| Table 5 Impact of Quick Instructions                   | 55  |

| Table 6 Static Mix Analysis                            | 57  |

| Table 7 Benchmark DataFlow and Control Flow Analysis   | 60  |

| Table 8 Analysis Summary                               | 61  |

| Table 9 General Data Flow Analysis – Filter 1          | 102 |

| Table 10 DataFlow FanOut and Arc Analysis - Filter 1   | 103 |

| Table 11 DataFlow Resolution Queue Analysis – Filter 1 | 104 |

| Table 12 DataFlow Merge Analysis - Filter 1            | 104 |

| Table 13 DataFlow Jump Forward Analysis - Filter 1     | 105 |

| Table 14 DataFlow Jump Backward Analysis - Filter 1    | 105 |

| Table 15 Benchmark Configurations                      | 108 |

| Table 16 Filters on Methods                            | 110 |

| Table 17 Execution Cycles per Instruction              | 113 |

| Table 18 Execution Coverage – All Methods              | 117 |

| Table 19 Ratio of Instructions to Max Node             | 118 |

| Table 20 Heterogeneous Addressing Detail – Filter 1    | 119 |

| Table 21 Raw IPC Data - All Methods                    |     |

| Table 22 Figure of Merit – Filter All                  |     |

| Table 23 Correlations with FM Hetero2 – Filter All     | 121 |

| Table 24 All Data - Filter 1                             | 122 |

|----------------------------------------------------------|-----|

| Table 25 All Data - Filter 2                             | 122 |

| Table 26 Parallelism - All Methods                       | 123 |

| Table 27 Figure of Merit on Top 4 SpecJvm2008 Benchmarks | 125 |

| Table 28 Figure of Merit on Top 4 SpecJvm98 Benchmarks   | 126 |

| Table 29 ByteCode Floating Point Conversion Instructions | 130 |

| Table 30 ByteCode Arithmetic/Integer Instructions        | 131 |

| Table 31 ByteCode Arithmetic/Move Instructions           | 132 |

| Table 32 ByteCode Floating Point Arithmetic Instructions | 133 |

| Table 33 ByteCode Control Flow Instructions              | 134 |

| Table 34 ByteCode Call Instructions                      | 134 |

| Table 35 ByteCode Return Instructions                    | 135 |

| Table 36 ByteCode Memory Constant Instructions           | 135 |

| Table 37 ByteCode Memory Read Instructions               | 135 |

| Table 38 ByteCode Memory Write Instructions              | 136 |

| Table 39 ByteCode Local Read Instructions                | 137 |

| Table 40 ByteCode Local Write Instructions               | 138 |

| Table 41 ByteCode Special Instructions                   | 139 |

| Table 42 Top 90% methods - part 1                        | 141 |

| Table 43 Top 90% methods - part 2                        | 142 |

| Table 44 Top 90% methods - part 3                        | 143 |

| Table 45 Top 90% methods - part 4                        | 144 |

| Table 46 SpecJvm98 Benchmarks                            | 151 |

| Table 47 SpecJvm2008 Benchmarks Included                 | 152 |

| Table 48 SpecJvm2008 Benchmarks Excluded                 | 153 |

## List of Figures

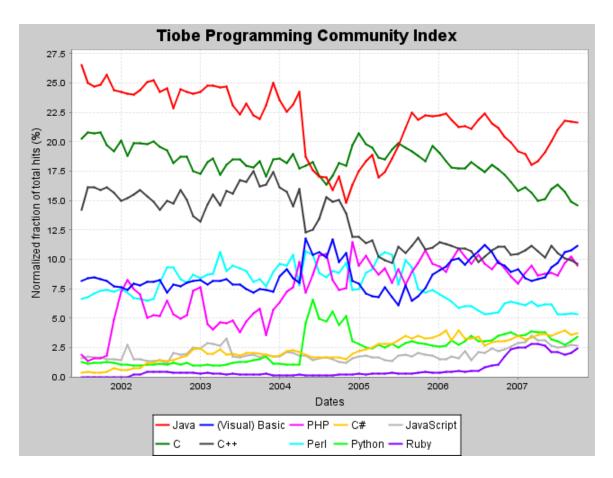

| Figure 1 Tiobe Programming Community Index [2]       | 5  |

|------------------------------------------------------|----|

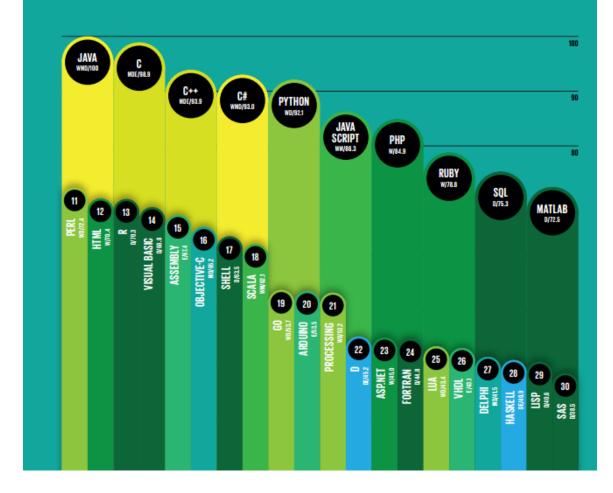

| Figure 2 IEEE Spectrum 2014 Language Ranking [3]     | 6  |

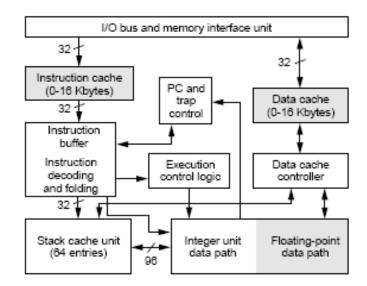

| Figure 3 Pico Java Configuration [14]                | 15 |

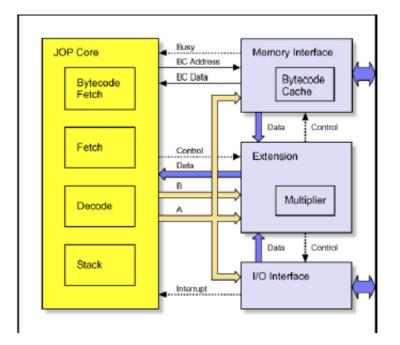

| Figure 4 JOP Machine Structure [15]                  | 15 |

| Figure 5 An Elementary DataFlow Program [30]         | 20 |

| Figure 6 TRIPS Machine Organization [41]             | 24 |

| Figure 7 WaveScalar Processing Element [46]          | 28 |

| Figure 8 JavaFlow DataTypes                          | 30 |

| Figure 9 Invalid Stack Example                       | 32 |

| Figure 10 Java Memory Organization                   | 35 |

| Figure 11 Machine Architecture Layers                |    |

| Figure 12 JavaFlow System Diagram                    | 40 |

| Figure 13 Instruction Data Unit Resources            | 42 |

| Figure 14 JavaFlow Network Commands                  | 64 |

| Figure 15 JavaFlow DataTypes                         | 65 |

| Figure 16 Serial Message Structure                   | 66 |

| Figure 17 Serial Network Interface                   | 69 |

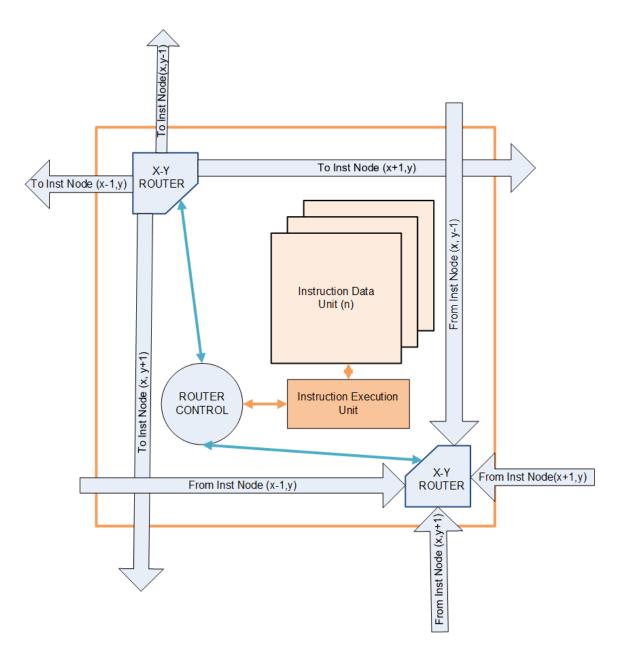

| Figure 18 JavaFlow Mesh Network                      | 71 |

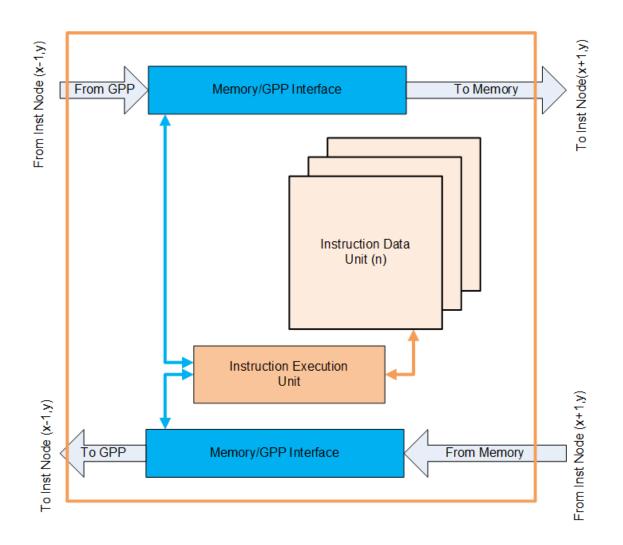

| Figure 19 Memory-General Purpose Processor Interface | 73 |

| Figure 20 Loading a Method                           | 77 |

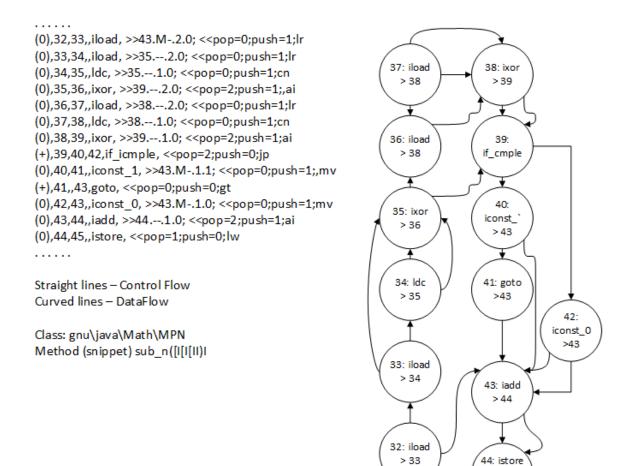

| Figure 21 Simple Address Resolution Example          | 80 |

| Figure 22 DataFlow Address Resolution                | 83 |

| Figure 23 Token Bundle                               | 87 |

| Figure 24 Simulator Class Structure             | .111 |

|-------------------------------------------------|------|

| Figure 25 Network Transit Times                 | .114 |

| Figure 26 Heterogeneous DataFlow Configuration  | .116 |

| Figure 27 Sample Analysis for nextDouble()      | .145 |

| Figure 28 Method code from JAVAP – nextDouble() | .146 |

| Figure 29 DataFlow code - nextDouble()          | .147 |

| Figure 30 DataFlow Analysis - nextDouble()      | .148 |

| Figure 31 Simulation results - nextDouble()     | .150 |

### **Chapter 1: Introduction**

#### **SECTION 1.1 - COMPUTING CHALLENGES**

JavaFlow, a Java DataFlow Machine employs high levels of both innovation and invention to address a series of computing challenges being faced by those attempting to implement modern computing platforms. The challenges addressed in this project include:

- Design complexity and associated design resource requirements

- Power consumption and cooling constraints

- Limited performance of wires across the chip

- Reliability in large system on chip implementations

- Management of software in multi-core structures

Innovation is achieved through the integration of a series of currently trending technologies:

- Virtually unlimited number of circuits on a chip

- Advanced on chip networks

- Dataflow architectures

- Java Virtual Machine Specification

Inventions are applied to the concepts of a DataFlow machine which allow the dynamic loading of a Java ByteCode method and execution of this procedural language structure within the dataflow framework. The two key inventions in this design are:

- The use of a self-organizing system to dynamically load and perform address resolution of Java methods.

- Additions to a traditional DataFlow machine to allow whole procedural Java methods to be resident in a DataFlow fabric and execute with high

performance and power efficiency exploiting higher levels of locality than in other computing structures.

In his book "The Smart Swarm" [1] Peter Miller described behavior of leaderless groups achieving great results. Examples included bees, geese, ants all of whose populations achieve a series of common goals without centralized leadership. These techniques are applied to the distribution of a Java ByteCode method into a DataFlow fabric in order to prepare for computation. The assignment of specific instructions to specific locations is not made centrally, but rather developed as the program is deployed throughout the network of DataFlow processing elements.

DataFlow machines exploit locality for working variables, but traditionally have had difficulty implementing loops and registers for communications across basic blocks. Dynamic DataFlow machines have used extensive hardware to both handle this looping and achieve high levels of parallel execution of loops. The JavaFlow machine demonstrates low cost structures to effectively deploy local registers locally to the processing elements and to implement both forward and loopback branches without adding traditional Dataflow switch/merge/predication functions.

The machine utilizes a minimalist approach to the design of the processing elements in the DataFlow fabric so that the maximum number of nodes can be realized on a chip. By utilizing the DataFlow fabric itself to load and resolve producer/consumer addresses, constraints on the instruction set encoding can be relieved with data expansion in the processing elements. One example of this is fan out from one producer to a number of consumer nodes.

#### SECTION 1.2 - HARDWARE BACKGROUND

Price and performance have been the two factors used to measure the effectiveness of computing systems since they were first created. While these two factors have at times been combined into a single metric, the largest change in the measurement of effectiveness has come in the components that make up these factors. In the early days of computing the system cost was primarily associated with financial cost of the materials used to implement the hardware of the computer. Similarly, the performance was initially measured as the frequency of the clocking circuit that drove the hardware machine. Even in the early years the cost of development was a consideration in the overall price of the system, and system clock speeds needed adjustments to account for instruction set differences.

In later years the components of these factors have changed dramatically. Cost measurements now start with area of a semiconductor chip and include the cost of the design. However; the increasing cost of complexity, verification, and testing plays an increasing factor in the overall ability to implement a processor design. The power dissipation from a traditional design on a modern semiconductor chip may yield a design that is either not feasible due to cooling or requiring significant cost in cooling technology.

With the differences in performance of components such as memory, circuitry, and I/O; clock speed-up on traditional micro-architectures has not led to comparable system performance increases. This is where advances in architecture and micro-architecture have combined with technology speed-up to improve system performance. Specifically, areas such as cache memory, pipelining, and parallel execution of some instructions have provided most of the system performance gains over the past 10 years.

Details of these various hardware alternatives are described in Chapter 3: Related Work.

#### SECTION 1.3 - SOFTWARE BACKGROUND

The original programming model was coding in either machine or assembly language to achieve the optimal performance for a specific application. The very high development costs of this machine level programming strategy has led to a plethora of high level languages over the past 50 years. All of these languages were aimed at increasing the productivity of the programmer while not sacrificing too much performance versus the hand coded assembly/machine language.

The Java language became popular in the late 1990's and its popularity remains today. Tiobe BV [2] has attempted to measure 'popularity' of programming languages by applying metrics to web search results. While this does not necessarily demonstrate the business usage of these languages, it does offer one measure of 'popularity.' Figure 1 demonstrates this 'popularity' measurement with Java shown as the top graph. The second most 'popular' language is C with the recent cluster of C++, Visual Basic, and PHP showing in third place.

Figure 1 Tiobe Programming Community Index [2]

A more recent review of programming languages was published in July, 2014 [3] and again, Java is the achieved the highest ranking as shown in Figure 2. This latest ranking used metrics from 10 sources including IEEE, Xplore, GitHub, and Google to attempt to quantify the popularity of languages.

Working with computational journalist Nick Diakopoulos, IEEE Spectrum has weighted and combined 12 metrics from 10 sources (including IEEE Xplore, Google, and GitHub) to rank the most popular programming languages. If you don't agree with our weighting, want to see more languages, or are interested in what's dominant in a specific subsector, such as mobile, go to our online interactive version. There you can adjust the weight of each metric and create your own custom ranking. — STEPHEN CASS KEY | W-Web | M-Mobile D-Desktop and Enterprise E-Embedded

Scores are normalized so that the top-ranked language's score is set to 100.

Figure 2 IEEE Spectrum 2014 Language Ranking [3]

THE TOP 10

PROGRAMMING

14 RANKING

ANGUAGES

Java is one of the later languages aimed at standardizing the complex world of programming. Despite advocates of alternative languages, the Java language has achieved some level of standardization. This is due the definition of the "Java Virtual Machine" (JVM) [4, 5] which has become ubiquitous on all modern computing platforms. There are multiple computing scenarios where Java is utilized:

One scenario is the internet and a computing model which distributes software over the network to a remote computer/browser for a specific computing assignment. The JVM represents an intermediate, machine level architecture which has been implemented on almost all current hardware platforms for the execution of downloaded programs over the network. Key attributes of this JVM are that programs cannot negatively affect the computing platform, and a series of processes are in place to insure the integrity of the distribution of these programs. With these two factors in place, the scope of computing platforms for which the JVM can be effective expands to include cell phones and the ever increasing set of small computing machines which previously may have been considered 'hard coded' by their original designers.

At the other end of the application spectrum, Java is a major component of Enterprise Computing Systems. The programmer productivity from levels of abstraction and software reuse is key to this popularity. The JavaFlow machine with its focus on managing large numbers of cores is more likely targeted towards this application area than the more cost sensitive personal device marketplace.

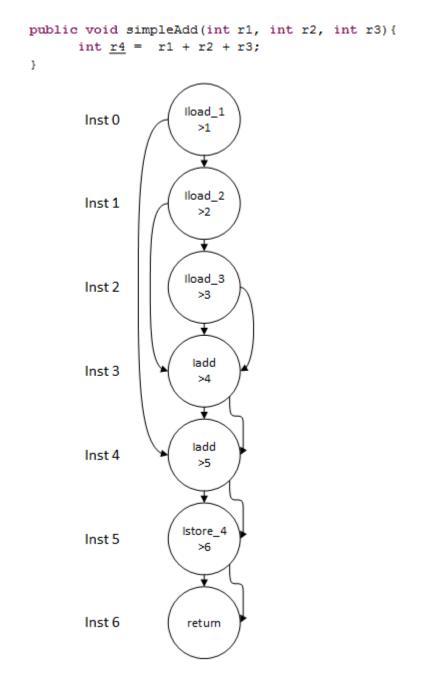

The JVM is a stack based architecture whose instructions are called *ByteCodes*. Each instruction contains a single byte operation code and a variable number of operands. Due to the stack nature of this architecture, instruction level parallelism has been difficult to obtain.

7

#### **Chapter 2: JavaFlow Problem Statement**

#### SECTION 2.1 - SUMMARY

This section offers a brief statement of the problem addressed in this research and a summary of the solution. The following section describes the related work, and the last section presents details of the proposed solution. Chapter 1: Introduction introduced a series of problems being addressed by computer architects.

The specific problem addressed in this research is focused on the general problems identified in Chapter 1 in the context of a Java Virtual Machine executing ByteCode instructions. The specific direction of this solution is the definition and analysis of a Java Dataflow machine. This machine combines the basic concepts of DataFlow machines along with recent developments in this field to implement a hardware ByteCode execution subsystem.

The overall goal is to use a minimalist approach to implement a JVM while implementing complete methods inside a DataFlow Fabric. This will address performance issues of traditional ByteCode approaches and exploit the advantages of a DataFlow machine which can capitalize on the data locality of the Java ByteCode program.

An additional goal of this machine is the automation of the loading and management of the DataFlow Fabric to relieve the operational systems from these tasks. With the number of cores anticipated to grow to between 1,000 and 10,000, the importance of this automation task will expand in the future.

#### SECTION 2.2 - INCLUDED TOPICS

The research effort includes the analysis of comparable hardware and software solutions and the analysis of SPEC benchmarks to gain understanding of the dynamic and

static behavior of key Java Methods. The DataFlow machine is described and the ability to load/unload/manage/execute ByteCode instructions is demonstrated. A baseline machine configuration is identified and comparisons to a series of DataFlow configurations is made against the baseline. Instructions per Cycle, DataFlow node utilization, and method DataFlow parameters are measured.

Discussion is provided for handling of all instructions and special cases such as exceptions are addressed. The management of the Java Method Area and Heap is discussed and ways of performing garbage collection is addressed.

#### **SECTION 2.3 - EXCLUDED TOPICS**

As described in the Proposal for this Dissertation, a series of items are not included in the scope of this research:

- Detailed logic design of DataFlow Nodes

- Semiconductor analysis of power management techniques

- Specific bus widths and implementations

- Complete JVM implementation and hence the ability to completely execute benchmarks on this proposed machine.

- Detailed implementation of Heap management including Garbage Collection

- ClassLoader implementations

- Memory subsystem details

- General purpose processor details

#### **Chapter 3: Related Work**

#### SECTION 3.1 - RELATED WORK SUMMARY

Other than the original paper [6], there is no specific previous work on a Java DataFlow Machine. As JAVA has become increasingly popular over a wide range of applications, there are existing architecture structures that successfully implement the JVM. Just as JavaFlow is a combination of hardware and software, most existing solutions have both components. Most solutions employ a combination of:

- General purpose processors

- Compilation techniques

- Special purpose hardware

In addition selected DataFlow machines and other tiled architectures are described.

#### **SECTION 3.2 - GENERAL PURPOSE PROCESSORS**

Most implementations of Java Virtual Machines are done with a general purpose processor using various compilation techniques. Modern processors have evolved through many stages:

- Simple single instruction execution

- Pipelined instruction execution

- SuperScalar (multiple instruction issue)

- Multi-core systems

Each stage of this evolution was aimed at both advancing performance, and only at the last step has minimizing power consumption and design effort become significant concerns Modern processors have mostly stabilized on the x86 or ARM ISA (Instruction Set Architecture) and have focused on technology and micro-architecture enhancements to achieve system performance improvements.

SuperScalar is the term applied to micro-architectures that have multiple instructions being issued simultaneously. Sometimes SuperScalar implies out of order execution and deep pipelines. Another key component of the performance gain is in the area of branch prediction. As stated earlier, cache memories are critical to the overall system performance.

A problem with superscalar implementations [7] is that the control logic necessary to support the out-of-order execution is: complex; power consuming; and can be distributed across the entire chip. The complexity translates into increased development cost with its associated risk of design failure. Wiring is becoming a limiting factor as propagation times across the chip have become an increasing percentage of a processor's clock cycle. An additional observation from the effect of the current design strategy is that less than 10% of a modern processor chip is dedicated to arithmetic execution vs. 90% utilized for complex control functions and storage [7]. This 10% utilization and with global wiring delays not scaling as technology scales [8], future designs are focusing on compartmentalizing functions on the chip and optimizing power consumption.

Current approaches to achieve more performance using current technology include focusing on coarser level parallelism. Examples of this include multiple processing cores on a single chip. A key advantage to this structure is that design costs can be reduced through the re-use of existing SuperScalar designs. A further advantage is that whole cores can be powered off when work load decreases, which could result in significant power savings. The challenge in these systems is that typical desktop applications do not present much parallelism. Extracting parallelism to utilize the increased computing power is another very complicated challenge. Note that for server implementations multiple cores or Sun's Niagara [9] advanced Simultaneous Multi-Threading (SMT) structure represent solutions to highly parallel workloads.

With current multi-core designs at 10-100 cores, JavaFlow's simple Instruction Node should provide at least an order of magnitude increase in the total number of Instruction Nodes available to be applied to an application.

While multi-core designs do provide savings in design complexity due the repetition of a single core design, the challenges are in the effective usage and management of these many cores. Since most applications are not designed with parallelism in mind, the partitioning of a single application into multiple threads running on multiple cores is complex, and has been the subject of much research. In addition to the effective execution on multiple cores, the management of these applications is also complex. JavaFlow attempts to address these challenges by allowing a single application to consume a variable number of cores and for the deployment of the program to these cores to be managed by the DataFlow fabric.

#### **SECTION 3.3 - COMPILATION TECHNIQUES**

Current Java virtual machines utilize a combination of compiler techniques. All Java programs are initially compiled to the Java ByteCode architecture which offers a series of security and program distribution advantages over other languages.

The simplest way to implement the JVM is on a general purpose processor that first loads the compiled ByteCode class and then interprets the instructions as required to execute the defined method. Modern systems use heuristics to identify methods which are executed repeatedly. Then advanced compilation technology is employed to optimize the execution. This is called Just-In-Time compilation (JIT). Obviously these compilers are specific to the target machine architecture. Finally several specific JVM hardware implementations have been created with the objective of further improving the cost/performance of Java byte code execution.

Even with a JIT compiler, the interpretation of ByteCodes initially remains a key component of most JVM's. Nicolaescu and Veidenbaum [10] analysis of the SpecJVM98 benchmarks showed the compiler performed at between 1.75 and 13.9 times as fast as a baseline interpreter. One of the performance challenges of interpreters is the use of program switch structures to decode ByteCode instructions and the effect on branch prediction in modern SuperScalar processors. Casey, Ertl, Wien, and Gregg [11] showed that branch prediction using BTB (Branch Target Buffers) mispredict 81% to 98% of the indirect branches in switch dispatch interpreters, and 57%-63% in an alternative structure. Their work attempts to further optimize this performance. The JavaFlow machine with its control flow to data flow translation system described in Chapters 4 and 6 does not utilize branch prediction hardware and therefore optimizes this aspect of the JVM in an alternative manner.

In addition to compiler techniques to execute the Java Virtual Machine, it should be noted that a significant aspect of the overall performance of Java programs comes in the Garbage Collection strategy. Note that one of the many advantages of the Java language is that memory management is not a user function, but rather delegated to the JVM. This function is outside the scope of this dissertation, but is mentioned for completeness.

One example of this Garbage Collection strategy has been demonstrated by Azul, Inc. [12]. Azul originally developed a hardware JVM but recently have focused primarily on the Garbage Collection. In enterprise Java applications, where the overall memory usage is beyond the benchmarks used in this analysis, the effectiveness of the Garbage Collection becomes an increasing factor in overall performance.

#### **SECTION 3.4 - SPECIAL PURPOSE JAVA MACHINES**

Traditionally a Java Virtual Machine (JVM) [4] is either interpreted or compiled 'just in time' (JIT) on a general purpose processor. However over the past years, several hardware designs have been proposed to implement the JVM and from these designs several key characteristics of the JavaFlow machine can be found.

In general, these machines are aimed at the low cost/power application space, although some employ special hardware for application specific optimization.

The earliest design was the JEM1 [13] processor developed by Rockwell. Its instruction set was modeled after the JVM ByteCode definitions and used traps to execute more complex ByteCodes.

Another early design was Sun's PicoJava [14]. This machine implemented the Java stack in hardware and introduced the concept of 'instruction folding.' This reduces the number of ByteCode instructions executed by optimizing movements of operands from the local storage to the top of the stack. A configuration diagram of PicoJava is shown in Figure 3

Schoeberl defined the Java Optimized Processor (JOP) [15] and reviewed six additional designs targeted towards embedded systems [16]. The JOP dataflow is shown in Figure 4 [15]. While Java optimization is performed, the machine is a traditional von Neuman architecture.

Figure 3 Pico Java Configuration [14]

Figure 4 JOP Machine Structure [15]

The Molen FemtoJava Engine [17] expanded on a traditional Java hardware core to perform application specific functions outside of the main Java execution unit.

Radhakrishnan defined further optimizations to the folding algorithm of PicoJava and also defined 'Hard\_Int' [18, 19] which optimized ByteCode execution by performing folding offline and by combining instructions into hardware macros.

Other efforts continued to seek optimizations on the execution of ByteCodes by eliminating, re-ordering, and translating ByteCode instructions [20-22].

In [23] Wang and Yuen demonstrated instruction level parallelism by using data flow concepts to tag JVM stack operands to realize both folding and out of order execution in a VLIW structure.

In [24] Vijaykrishnam, Ranganathan and Gadekarla extended the focus of the hardware implementation to include support for the object-oriented aspects of the Java programs. In addition to folding techniques implemented elsewhere, this machine used new cache constructs to assist the access of both fields and methods of Java objects.

Although not a specific Java machine, a recent multicore offering is relevant to see the potential for a machine like JavaFlow. Adapteva, Inc. released its Epiphany 64 core processing chip [25] where a general purpose processor is used in conjunction with a tiled fabric of processors. Each node has a full processing capability and the mesh network implements a single memory address space accessible by all cores. An interesting aspect of this design was part of a conversation with the company president which indicated the entire design was completed in a relatively short period of time by a very small design team. This design was released to the Global Foundry's semiconductor facility and sample parts with 16 or 64 cores are available. This architecture is claimed to scale to 4096 cores which is the magnitude envisioned for the JavaFlow machine.

Another special purpose hardware solution entering the Java space has been defined by the Heterogeneous Systems Architecture Foundation [26]. This system architecture utilizes the combination of a set of general purpose processing cores combined with a Graphics Processing Unit which contains potentially thousands of cores. The GPU cores execute in a SIMD (Single Instruction, Multiple Data) configuration where an extreme level of parallelism is available for tasks that can be partitioned to exploit this system. The target application for these systems, as contained in their name is the processing of graphic images for high performance display rendering. Recent research has been targeted in exploiting this high level of parallel processing capability towards parallel applications. In addition to the limitations of the SIMD structure, traditional GPU's require the transfer of data between local memories and the shared main memory of the general purpose processing cores.

The HSA architecture overcomes a significant limitation of traditional GPU's by allowing each processor to directly access the large memory space of the general purpose processor cores. This capability combined with the structures supported in the latest release of Java (Java 8 [27]) which explicitly identifies parallelism through Lambda expressions allows performance enhancements of specific parallel applications through the execution on HSA GPU systems. This work is part of the Sumatra Project of the OpenJDK foundation [28]. These systems are aimed explicitly at improving the performance of highly parallel applications rather than the general applications targeted by the JavaFlow machine.

An additional demonstration of hardware enablement can be found in IBM's TrueNorth "neuromorphic chip" [29]. While not aimed at Java processing, it demonstrates the "unlimited number of circuits" referenced in the Introduction. This 2014 chip claims 5.4 billion transistors, 4096 "neurosynaptic" cores, 1 million programmable neurons, and 256 million programmable synapses. They also claim a system of 16 chips. A key aspect of this design is the power density claim of 20mW per square centimeter; or 70 mW for the chip.

#### **SECTION 3.5 - DATAFLOW MACHINES**

#### **History and concepts:**

In 1975 Dennis [30] proposed a computing architecture as an alternative to the traditional von Neumann model. The term applied to this architecture was a 'DataFlow Machine' because it was structured according to the dataflow graph of the underlying computing algorithm. Conceptually this structure could employ significantly more circuits for arithmetic and logical operations versus control. Practically, however; this was not the focus of early dataflow implementations due to the overall scarcity of circuitry. Modern technology has reopened the door for the implementation of DataFlow machines where much of the complex control circuitry could be turned into additional arithmetic and logical operators with less global control requirements.

There has been recent work in the area of DataFlow machines. Some key problems with the earlier designs, such as memory ordering have been overcome by the modern machines enabling them to be considered for modern general purpose computing problems.

A key reason for an interest in a tiled DataFlow machine versus a SuperScalar alternative is that the DataFlow machines exploits 'data locality' in the program. For example a tiled DataFlow machine can capitalize on the physical relationship between instructions that produce data and those instructions that consume the same data. SuperScalar machines through general purpose register renaming ignore this relationship and consume significant circuitry and power to allow parallelism and out-of-order execution.

In addition to the work of Dennis, another reference to this technology is available from an earlier Thesis and follow-on publication by D. A. Adams at Stanford in 1968 [3133]. Adams was focusing on ways to improve parallel processing and proposed the use of the dataflow graph of the program to sequence instructions. Also, Rumbaugh [34] proposed an early DataFlow machine.

These initial machines were all based on the dataflow graph of a program, but differed in number of tokens that could be present on each dataflow graph edge, on whether execution could begin before all tokens were present, and in the definition of the control nodes in the dataflow graph.

The concept of this machine is to move from the traditional von Neumann computer definition where each instruction is executed in an order specified by a program counter to a machine executing operations in an order based on the availability of data. By basing execution on the availability of data, the expectation is increased performance; and with availability of more hardware, increased parallelism.

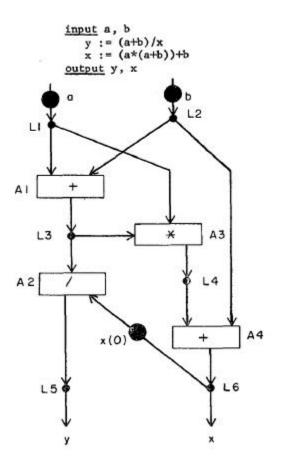

DataFlow machines execute according to the data flow graph of a program. Each node of the dataflow graph represents an operation in the program, and the arcs represent paths that data travels between operators. In the pure sense of a DataFlow machine, there is no concept of a program counter or program control. Each operator obeys 'dataflow firing rules' which are defined as having all operands present at its input terminals. All DataFlow machines reviewed so far have nodes with 1 or 2 data operands as inputs and 1 or more nodes as outputs. Terminology used in these structures is 'producer-consumer' where each node consumes data, and then produces a result which is subsequently consumed by another node in the dataflow graph. Figure 5 from Dennis [30] shows a dataflow representation of a simple program. Note that links L1 and L2 are initially enabled. L1 and L2 are links that are 'fired' and make copies of data available to downstream consumers. Operation A1 can 'fire' first. When A1 produces its result, A3 can 'fire.' Subsequently A4 can 'fire' which produces the final result 'x.' Finally this

result is sent to A2 which can then 'fire' to produce the final result 'y.' This example showed the firing rules and some parallelism that can be achieved. No conditional operations are shown in this example.

Figure 5 An Elementary DataFlow Program [30]

One of the first challenges of a DataFlow machine is implementation of program control in this data only environment. One of the techniques utilized is predication which translates control dependencies into data dependencies. Different DataFlow designs use different variants to realize this predication. Examples include PHI and inverse-PHI instructions. These have also been called T-Gate, F-Gate, and Switch instructions. The PHI instruction consumes either of the two operands and passes to the producer side of the node based on a third predication value passed in the dataflow graph. The inverse PHI instruction directs one of the operands to either of two consuming nodes based on a similar Boolean signal. There are many variants on the implementation of predication in DataFlow machines. The WaveScalar machine implements both functions but designates the inverse-PHI function as a Steer instruction [35].

TRIPS uses a different form of predication called "Dataflow Predication" [36] where each instruction has extra bits to identify whether a third predicate operand is required before 'firing' can occur.

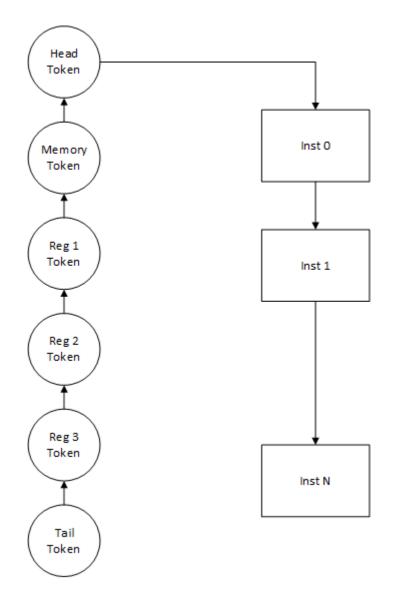

Beck, Johnson, and Pingali [37] demonstrated the "Access Token" to order memory references in a DataFlow Machine. This structure is used as the MEMORY\_TOKEN in the JavaFlow machine, and additional serial tokens are defined in Chapter 6 forming a key aspect of JavaFlow.

Early examples of DataFlow machines were created with technology constraints limiting the number of functional units available to implement the DataFlow graph. Original proposals [38] called for only a single functional unit with the DataFlow 'nodes' saved in an array whose execution order was determined by the DataFlow firing rules. There were several problems with these designs that precluded a practical solution.

First the single functional unit precluded any level of instruction level parallelism, but did allow increased occupancy of the processor. This was consistent with most modern processors in the 1970's where a single functional unit (arithmetic and logical unit) was commonplace. Second, the logic of early DataFlow machines to determine the firing rules consisted of a large associative array to match the availability of an operand from one operation to the requirements of other operands. These arrays were not only expensive but inserted delay into the overall processing pipeline. Another differentiating characteristic of DataFlow machines is how multiple values of a variable are handled. This is key to loop structures and high levels of parallelism. A Static DataFlow machine allows only one variable to be present on any arc in the control flow graph. While this avoids the problem of multiple values in loop iterations; potential parallelism is lost. The alternative is to add a tag to each token (variable) to distinguish values in different iterations of a loop. This "dynamic tagged token" approach is utilized in the initial MIT machine [38] and also in WaveScalar [35].

One aspect of early DataFlow machines was the challenge/opportunity regarding the ordering of memory operations. With a traditional von Neumann architecture, the program counter implies an order to the memory operations. On the other hand, a DataFlow machine following only DataFlow firing rules might create an unexpected ordering of memory load and stores. The solution to this challenge has been the topic of much research over the years and two solution areas have emerged. The initial focus of DataFlow machines was in the use of Functional Languages [39]. These languages offered parallelism, but were significantly different from traditional languages and they have not seen widespread use among programmers. A characteristic of the memory used in these languages is that after initialization, it can only be written once so that read-after-write data hazards are eliminated.

Recent DataFlow implementations have imposed an ordering on memory operations so that traditional imperative languages can be executed. WaveScalar, TRIPS, and the JavaFlow machine all employ memory ordering which may preclude some parallelism to insure program integrity.

#### Monsoon, Manchester

Early research and resulting implementations of DataFlow machines focused both functional languages and maximizing the parallelism while deploying a relatively small number of processing units. These implementations were targeted for large scale scientific processing. Each implementation required extensive matching logic for a significant number of tokens which would then be dispatched to the execution unit(s). Each implementation used dynamic tagging of the operands.

The Manchester machine [40] demonstrated parallelism on programs written in the single assignment language SISAL. Tokens are carried in data packets around a pipeline ring structure where a matching unit looks for pairs of tokens that can be sent to an execution unit. The Manchester machine has a microcode controlled pipeline while the Monsoon machine is implemented exclusively in hardware.

The original MIT architecture was called TTDA (Tagged Token DataFlow Architecture) and was followed by the ETS (Explicit Token Store) architecture [38]. This latter architecture formed the basis for the Monsoon implementation. These machines exploited the functional language Id [39]. The TTDA architecture had the same challenges as the Manchester machine where the matching of the dynamically generated tokens was very expensive in both logic and cycle time. The ETS/Monsoon extended the architecture to replace the matching functions with an explicit location where the first argument to a binary instruction is saved and presence bits set to non-empty. Upon the arrival of the second argument, the presence bits for the location are read indicating that the first argument has arrived. Then the first argument is read and the instruction is fired. The presence bits are then reset to empty.

## TRIPS

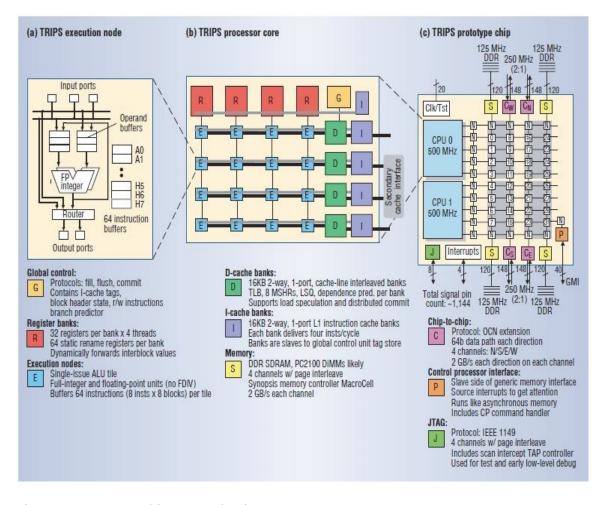

The TRIPS project at the University of Texas [41, 42] is focused on "EDGE" Explicit Data Graph Execution. The project is a combination of a static DataFlow machine with a program counter to maintain control flow. Because of this approach towards the execution of a traditional program structure, this machine is the closest comparison to the JavaFlow design. A system diagram of the TRIPS machine is shown in Figure 6.

Figure 6 TRIPS Machine Organization [41]

This processor breaks down the control graph of a program into 'hyperblocks' which can contain up to 128 instructions. The DataFlow fabric consists of 16 Processing Elements (PEs) and the instructions of the hyperblocks are distributed across the PEs. Each PE contains up to 64 instructions which are addressable as consumer nodes from producer and predicating instructions. This combination shows that up to 1024 instructions can be dispatched or 'in flight' during program execution, although at most 16 could be executing in parallel. Each of these processing elements follows the DataFlow firing rules with predication having been included in the compiled code to implement branching. Hyperblocks are defined as blocks of code where no loops are allowed.

The key to the execution of programs is that inter-block communications is handled primarily through the register banks which eases the pressure on memory references. The intra-block data communications is handled with the DataFlow producer-consumer transfers using the edges of the dataflow graph. A further key to execution is the 'block atomic' execution of each hyperblock. A hyperblock is a segment of code that executes atomically where there is a single entry point, possibly multiple exit points, and no internal looping. Once a hyperblock is initiated, the system can deterministically know when it is complete independent of the path taken through the block. Each hyperblock is allowed to make 32 register reads and writes and the completion of the block is defined by the completion of all register writes.

A critical factor in the successful implementation of TRIPS is the compiler [43]. Since the hyperblock size is 128 instructions and most program blocks are significantly smaller, the compiler is responsible for loop unrolling to fill the instruction space. Furthermore, the compiler is responsible for address assignment to minimize the distance between producer and consumer nodes and the proper handling of all register reads and writes. A challenge for the instruction set of the TRIPS is that limiting the instruction width to 32 bits allows only 2 possible consumers for the data that is produced at a processing element. This limitation requires the insertion of move or fan-out instructions that takes a single data element and moves it to two additional consumers.

TRIPS implements a memory ordering scheme similar to WaveScalar which insures proper handling of data dependencies. TRIPS utilizes a series of on chip networks optimized to handle the producer-consumer operand transfers; the instruction loading; register read/write; and access to the L2 data cache.

The TRIPS machine was implemented using standard cell 130 nanometer technology. Analysis of the implementation showed mixed results when compared to other SuperScalar machines. [44] The largest challenge in the analysis was to normalize the technology and design resources when attempting to compare this project with commercial processors. Code benchmarks were analyzed compared to an Alpha architecture to measure instructions executed, parallelism, storage accessed, and instructions per cycle using both compiled and hand optimized code.

The conclusion of the analysis was that the EDGE execution structure offered no clear advantage over a traditional architecture nor advantage over a modern technology implementation. Several areas were cited as weakness areas which have been incorporated into the design of the JavaFlow machine. The following issues were reported: [44]

- The fan-out limitation of two consumer addresses caused 20% of the instruction count to be the special move instructions which was larger than expected.

- The hyperblock size had issues of both oversized block headers and many NOPs required to fill the block. This consumed storage but not processing.

Variable sized blocks and block headers would save significant storage and

resulting instruction fetches. This requirement also place significant pressure on the compiler to maximize the block sizes.

Since the blocks did not allow looping, branch prediction was key to optimizing the instruction fetches. This added complexity and misspredictions added execution time to the results.

In summary, the analysis concluded that TRIPS could sustain 10 IPC showing a three-fold cycle count speedup over an Intel Core 2 process with hand optimized kernels. However with compiled benchmarks the cycle counts were not competitive. While technology improvements may show improved results, the change of ISA to this new structure is unlikely to change desktop systems. However, this architecture may apply to systems where high performance and low power are both required such as mobile and data center applications.

## WaveScalar

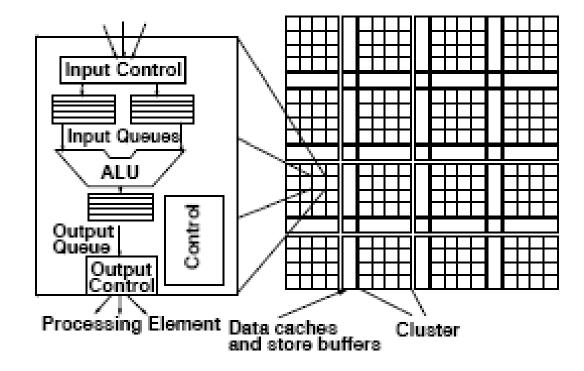

WaveScalar represents another recent DataFlow architecture and implementation and has solved several problems of historical machines. This processor, developed at the University of Washington [7, 35, 45] exploits advanced semiconductor technology to implement a true DataFlow machine with processing elements across a single chip. Processing Elements (PEs) are combined into domains and clusters to support different routing protocols over increasing distances. This fabric of PEs is called the WaveCache.

The simplest DataFlow machine would allocate a single instruction to a PE, WaveScalar assigns 64 instructions to each PE. The goal in the assignment for producerconsumer instructions to be close to each other to avoid network delays while not in the same PE to allow parallelism. A single cluster WaveScalar implementation contains 32 PEs and can store 2048 instructions. A four cluster machine would contain 128 PEs and 8192 instructions. An example of the WaveScalar configuration is shown in Figure 7.

Figure 7 WaveScalar Processing Element [46]

Each Domain consisting of 8 PEs has a section of a banked L1 data cache, store buffers, and a floating point unit. On the periphery of the chip is an L2 cache. Cache coherency is maintained using a MSEI protocol.

The machine was targeted to execute the Alpha instruction set which is then translated to the native DataFlow instruction set. Performance is measured in equivalent Alpha instructions per second.

WaveScalar introduced the concept of 'Waves' which are segments of a program's control flow graph and the ordering of memory operations within waves. This key element

allows the WaveScalar machine to execute traditional languages compiled to the Alpha ISA.

The 'Wave Cache' also supports the transition of unused instructions from the PE's to the memory to make room for required executions. WaveScalar implements a 'Dynamic DataFlow Machine' similar to the original machines previously described. This structure allows multiple instances of loops to be executing concurrently which is key to increases in levels of parallelism. The challenge with this architecture is the increase in design complexity and circuit count to handle the dynamic allocation of machine resources to implement the parallel loop execution.

## SECTION 3.6 - JAVA

The JAVA programming language and its associated Java Virtual Machine has some characteristics that invite implementation on a machine like JavaFlow. The Java Virtual Machine is described in an original edition [4] and then updated for Java 8 [47].

While the stack-based architecture has some limitations, there are several characteristics that can be exploited to optimize performance. All local variables and working registers are part of the stack. All accesses to this stack are explicitly addressed by 'ByteCode' instructions. This means that at instruction decode time, all stack addresses are available, and optimizations can be performed.

The Java Language is strongly typed, which means all data is identified according to one of the language types as shown in Figure 8. This removes any ambiguity regarding how to handle specific data elements. The following is a list of specific characteristics of the Java Virtual Machine which key to the success of the JavaFlow machine:

```

public enum DataType {

BYTE,

SHORT,

INT,

LONG,

CHAR,

FLOAT,

DOUBLE,

REFERENCE,

RETURN_ADDRESS

}

```

Figure 8 JavaFlow DataTypes

- The JAVAC compiler provided by Oracle is traditionally used to create the architecturally defined Java Class Files which are eventually loaded into the Java Virtual Machine.

- Java Byte Code programs have the maximum number of local registers utilized and the maximum number of stack elements defined at compile time. This allows the JavaFlow machine to know if a program would extend beyond the register/stack capacity in the DataFlow Fabric.

- Although not optimized, the JAVAC compiler utilizes the stack for communications inside a basic block of code and uses local registers for communications between blocks and other methods.

- 4. Part of the JVM definition is that every instruction must have the same stack configuration from any entry point. An example of this restriction is in the case of a control flow merge. If instructions A and B have instruction C as their next instruction, then the numbers and types of elements of the stack

after the execution of both instructions A and B must be identical. Figure 9 provides an example of this where a ByteCode program starts with a single 'value' on the stack. The example shows only a forward branch, but this situation can become more complicated in the case of back branches or loops.

- 5. Local Storage addressing is never indirect. All register accesses are specified as absolute values as either part of the opcode or part of the operand. No calculations are allowed which simplifies the interface between the Serial Network and the Mesh Network during Local Register operations.

- Java programs are organized into Classes and each Class is compiled into a data structure called a ClassFile. Each ClassFile has several components including:

- a. Constant Pool. The Constant Pool is the collection of all constants used by the Class along with definitions/references to all components of the Class such as the Fields and Methods.

- Methods. A Method of a Java Class is the actual program consisting of a list of ByteCode instructions. A Java Class may have many Methods and all are contained in the ClassFile.

- c. Additional debugging information and tools to assist in the development and execution of the Class.

| Label Instruction<br>Start: |                     | Comment                 | Stack<br>value1 |

|-----------------------------|---------------------|-------------------------|-----------------|

|                             | ifeq, X             | if value1==0, jump to X | <b></b>         |

|                             | iconst_1            | push integer 1 on stack | 1               |

|                             | iconst_2            | push integer 2 on stack | 1, 2            |

|                             | iconst_3<br>goto, Y | push integer 3 on stack | 1, 2, 3         |

| X:                          | iconst_4            | push integer 4 on stack | 4               |

|                             | iconst_5            | push integer 5 on stack | 4, 5            |

| Y                           | iadd                | add 2 stack elements    | invalid stack   |

Example of Invalid Stack. A ByteCode program starts with a single 'value' on the stack. The first instruction jumps to label X if the value is 0. Starting at label X, the next two instructions push integer constants onto the stack. If the value is not zero, then the next three instructions are executed which push integer constants onto the stack, and then jumps to label Y. Note that eventually both paths of the program arrive at location Y. However, since the stack is different for each entry point, this program is an invalid ByteCode program.

Figure 9 Invalid Stack Example

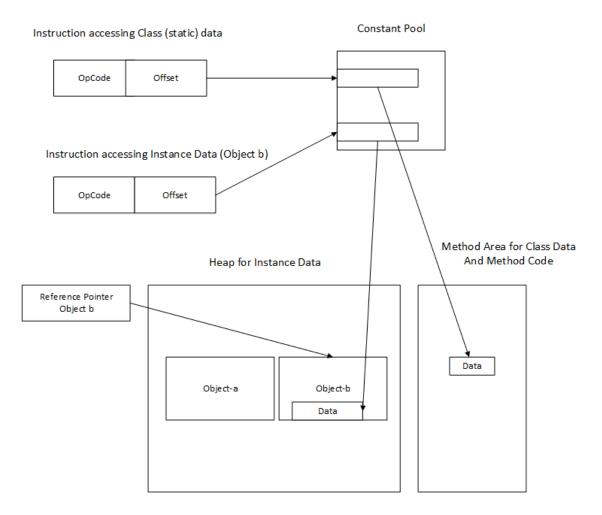

Two key elements of the Java language are the use of abstraction via object oriented programming and the use of automatic memory management provided by the Java Virtual Machine. The allocation and management of memory in a Java system is not architected by the Java machine specification, but rather is left up to specific implementation decisions. Venners [5] described several options for managing both the Method Area and the Heap. Tradeoffs in terms of performance and optimized garbage collection are necessary in order to realize an optimized system. The translation process from the symbolic references included in Java Class files to the actual pointers to data is complex and offers both opportunities and challenges to the JavaFlow machine configuration. The affected instructions include memory 'get,' 'put,' and 'invokes' for both static and instance references. The ByteCode instruction definitions [4, 47] call for the operand of these instructions to point to an offset in the Class 'Constant Pool' where another pointer into the Class data or the Object instance data is found. The translation from the symbolic reference to this offset can be done by the Linkage process before the method is loaded into the machine or when the data is first accessed, although the details of this process are machine dependent. Once the actual pointer is found, interpreter systems change the opcode by prefacing the code with a '\_Quick' modifier to avoid the architected indirection to access the Class or Instance data. This latter approach is the basis for the simulation and performance analysis data reported in Chapter 7. Vijaykrishnan [24] describes this process for both gets and calls in a Java hardware machine which does not have the level of distributed processing capability of JavaFlow.

However; each of the 3 steps to the address resolution process offers potential opportunities for overall performance improvement with associated expense in circuitry. The opportunities involve the utilization of the Instruction Nodes with memory access instructions to resolve these addresses in parallel. The cost is the additional logic required in each node.

• The Class File with symbolic references requires the linking of these references with other Classes that are already loaded or will be loaded. While doing this in the Fabric could offer offload of the General Purpose Processor, the initial judgment is that this function requires visibility to the entire state of the Java Machine and is best left to the GPP. Also, sending the symbolic references to the individual Instruction Nodes would require network traffic and storage in the nodes.

• A more interesting option is to include the architected offset into the Constant Pool as the operand of storage operands and then utilize the Instruction Nodes to resolve these to actual memory pointers by accessing this Class Constant Pool data. While the linking process would still need to resolve all references to other classes, each memory access Instruction Node would be able to find and save the pointer into the Heap or Class area either at load time or memory operation execution time. Note that accesses to static fields are made directly into the Class data area of the Method area, while accesses to objects are first referenced by an object reference variable passed via local registers or the stack.

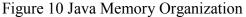

Figure 10 shows an example of the Constant Pool, Method Area and Heap in a Java memory system. Note that since constants including memory reference information are part of the Constant Pool which is loaded prior to execution, the JavaFlow machine can perform unordered parallel accesses to gather constants for upcoming instruction execution. The Method Area is used to house the actual code in interpreted systems and the Class variables. The Heap is used to house object instantiations of Classes and is clearly subject to Garbage Collection during execution.

Two example instruction are shown accessing Class and Instance data. For Class data, the instruction contains an offset into the Constant Pool where an offset is found into the Method or Class data area. For instance data, a similar lookup is performed into the Constant Pool, however the offset is with respect to the instance data on the heap which is found by an address reference pointer. Note that to ease access in the current method, any non-static method has its local register 0 containing the reference to the method's instance area on the heap.

Since this research began, Java has realized is version 8 release. Throughout all Java releases, the JVM has remained very constant, and so far this holds for Java 8. The new JVM does provide support for a new type of dynamic method invocation which can be exploited by other languages, the strongly typed Java language still does not allow such structures.

For reference a complete list of the Java ByteCode instructions is provided in Appendix A. The instructions are categorized by group whose processing functions are similar. For each instruction, the contents of the JVM Stack before and after execution is described along with the 'Pop' and 'Push' counts. These counts are the number of stack elements removed and replaced for each instruction.

## SECTION 3.7 – SUMMARY

This chapter reviewed a broad spectrum of the technologies available for the execution of Java programs. General Purpose Processors represent a significant area of computer architecture research, and therefore were addressed as they face challenges in technology scaling in the future. Compilation techniques which are the current way Java programs are primarily executed would be limited by the scaling issues facing General Purpose Processors. Special purpose Java machines demonstrated techniques to optimize the execution of ByteCode instruction streams which is key to JavaFlow and its proposed enhancements. DataFlow machines were originally conceived to realize high levels of instruction parallelism and often exploit alternative programming languages. This architecture forms the basis for the JavaFlow machine and modifications in both structure and objective are key to the success of the design. Finally the Java language offers a combination of complexity through its abstractions and also the opportunity for the JavaFlow machine to achieve optimizations due to its distributed processing capabilities.

# **Chapter 4: JavaFlow Overview**

## **SECTION 4.1 - OVERVIEW**

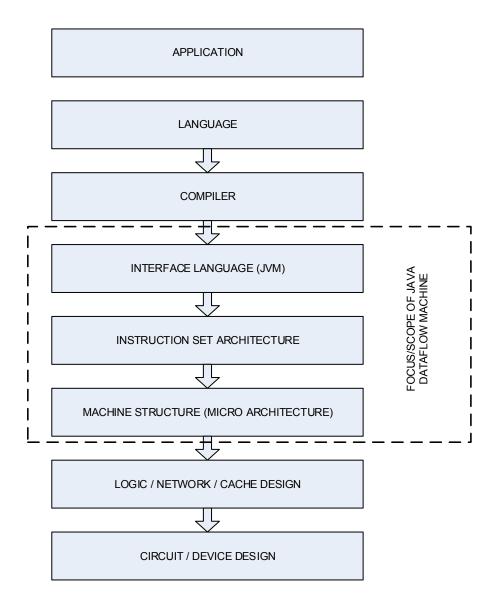

Before presenting a system diagram and associated descriptions, Figure 11 describes the overall process of translating a computing problem (application) to the circuitry which ultimately implements the solution. The focus/scope of this system includes the interface language, instruction set architecture, and machine structure. In this system, this intermediate language is the Java Virtual Machine (JVM). Similarly, the logic design, network implementation, and cache structures which are critical to the performance of any computing system are not the focus of this research.

Figure 11 Machine Architecture Layers

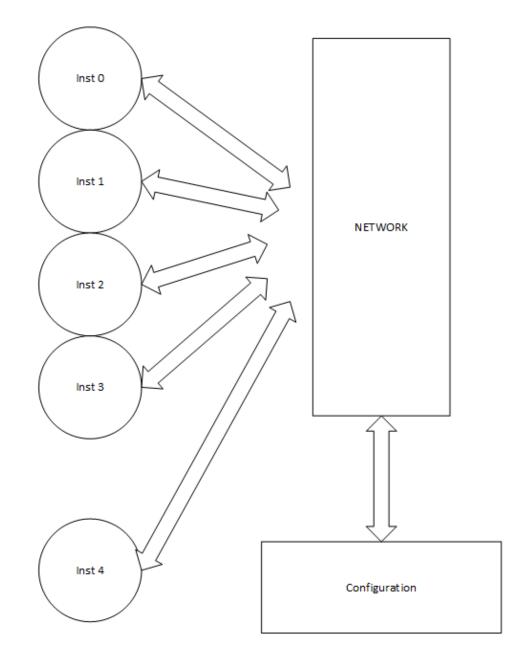

Chapter 3 provided a basic description of several DataFlow machines in addition to specific similar machine structures. In addition some key characteristics of the Java Virtual Machine have been described. Chapter 5 provides an analysis of Java Benchmarks demonstrating the characteristics of two sets of benchmarks and how a Java DataFlow machine might provide an effective execution platform. This chapter provides an overview description of this machine while Chapter 6 provides additional details. Note that since this machine description is still at a high level, there are some technology related decisions and details that are not fully defined. Examples of these are specific bus widths, tag widths, and machine state storage sizes. The advantage of combining the General Purpose Processor with the DataFlow Fabric is that when DataFlow technology limitations are met, processing can still proceed using the GPP.

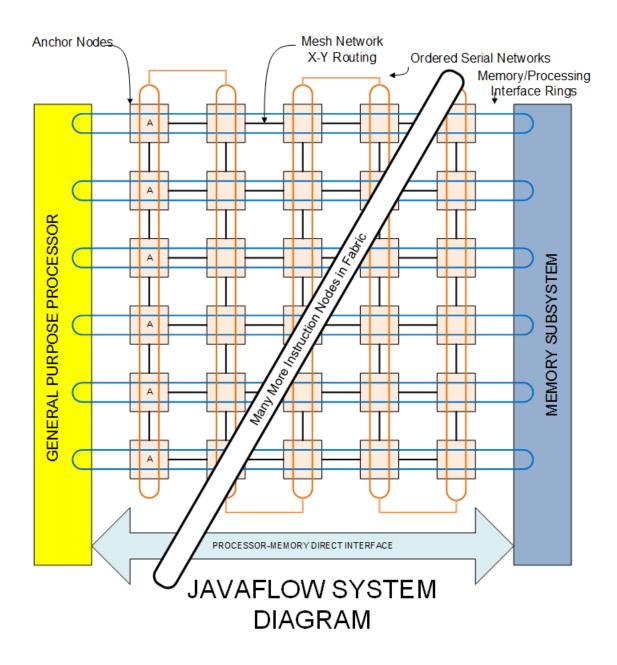

Figure 12 shows the overall machine configuration with the 3 types of networks, the DataFlow fabric, the GPP, and Memory. To address the challenges of global wiring not scaling as technology [8], a Globally Asynchronous / Locally Synchronous (GALS) [48, 49] design is utilized. Each Instruction Node can have its own synchronous clock to control processing functions; however data transfers between Instruction Nodes can be asynchronous and can proceed a different rates on each network and on sections of each network. Furthermore, the transfer protocols of the serial networks can be optimized for the lack of requirement for routing to reduce data transfer delays.

Figure 12 JavaFlow System Diagram

## **SECTION 4.2 - INSTRUCTION NODES**

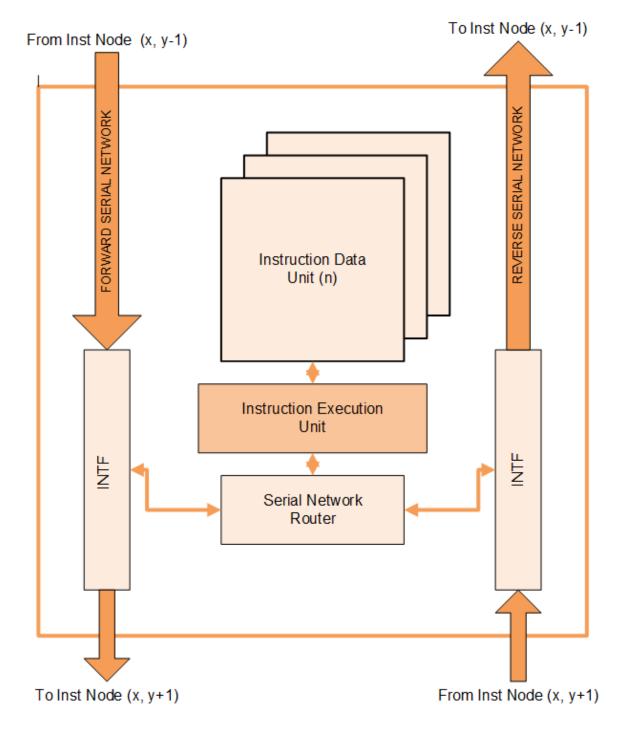

The basic element in the DataFlow Fabric is the Instruction Node. Each Instruction Node has a unique (x, y) address in the Fabric and contains the following components:

- Instruction Execution Unit. This is the actual processor that executes the decoded instructions in the node. This unit interfaces to both the routers and to the Instruction Data Unit(s).

- Instruction Data Unit(s). Each Instruction Node has one or more Instruction

Data Units which house the actual ByteCode instructions and all the

associated state information for the ByteCode instruction. Figure 13 shows

the resources for each Instruction Execution Unit which are explained as the

overall instruction processing is described.

- Serial Network Router. The interface to the forward and reverse serial networks which connect each Instruction Node and is used to manage the DataFlow Fabric and insure proper control flow is maintained with the DataFlow machine structure. Serial Tokens are used to communicate between Instruction Nodes on behalf of each Instruction Data Unit.

- Mesh Network Router. The interface to each of the four adjacent Instruction Nodes and the function that sends mesh messages throughout the DataFlow Fabric.

- GPP/Memory Interface. For selected Instruction Nodes this function is the interface between the Instruction Execution Node and the high speed ring networks to carry memory data and request/responses to the GPP

```

public class InstructionDataUnit {

/* General properties */

DataFlowAddress thisDataFlowAddress;

ByteCodeInstruction inst;

short[] sourceLinearAddresses;

DataFlowAddress[] targetDataFlowAddresses;

SerialMessage[] upboundDataFlowAddressResolutionQueue;

int pop;

int push;

/* Execution data */

MeshMessage[] inputData;

int popsReceived;

/* For Jump and GoTo groups */

short targetLinearAddress;

/* execution status flags */

boolean headTokenReceived;

boolean memoryTokenReceived;

boolean myRegisterTokenReceived;

boolean tailTokenReceived;

boolean waitingService;

boolean waitingTail;

boolean waitingMeshData;

boolean waitingRegister;

boolean ready;

boolean fired;

boolean initialized;

boolean exception;

boolean stopped;

}

```

Figure 13 Instruction Data Unit Resources

Each Instruction Data Node knows its own physical (x, y, p) Mesh address where 'p' represents the number of the Instruction Data Unit internal to the Instruction Node. When instructions are loaded they know their own serial address (offset from the first instruction of the method) and the addresses of the next instructions to be executed. If the next instruction is *sequential*, then the next instruction is the current instruction number incremented by one. If the instruction has a non-sequential next address, then the next serial address is included as part of the instruction. In the architecture for the ByteCode instruction may have variable lengths, and instruction addressing is based on byte addresses in the loaded instruction stream. At this level of the JavaFlow design, all instructions are a single length and the linear addresses are independent of the size of the ByteCode instructions. Each Instruction Data Unit has its own unique serial address which is the absolute number of the ByteCode instruction.

The sourceLinearAddresses contained in the Instruction Data Unit are the addresses of instructions that transfer control to that Instruction Data Unit. These sourceLinearAddresses are used in the address resolution where the operand addressing is translated to the DataFlow Fabric addresses. The resulting set of target DataFlow addresses are stored in an array in the Instruction Data Unit. This address resolution process is described in Section 6.2.

The various status items are set when specific Serial and Mesh messages arrive and when the instruction actually executes or 'fires.' The 'pop' value is the number of stack elements that are consumed by the instruction. The push value is the number of stack (DataFlow) elements that are produced by the instruction. The 'PopsReceived' value is a count of the number of data elements received so that when 'pop'=='PopsReceived', the instruction can fire.

The simplest case would be for each Instruction Node to house only a single ByteCode instruction. This would minimize any run time instruction decode and would allocate all resources in the Instruction Node to a single Instruction Execution Unit. However like previous distributed DataFlow machines each node is expected to house n instructions. A simple and reasonable value for this value is 64, although technology decisions may allow larger or smaller numbers. Note that these instructions could be from different methods or even different threads, as instructions are tagged with thread-method identifiers. The larger the number of instructions housed in each Instruction Node, the more complicated the control at each element becomes. If the number of instructions housed in each element were reduced to 1, then there would be more opportunity for single thread parallelism but with potentially longer mesh network transit times between Instruction Nodes. Allowing the number to grow to a very large number of instructions creates an implementation more similar to a modern multi-core machine where each core executes an entire instruction stream.

Instruction Nodes in the DataFlow Fabric can be heterogeneous. For example, for each 10 Instruction Nodes, 6 could be general purpose logic/arithmetic, 1 floating point, 2 storage, 1 control. Using a heterogeneous set would increase the transit times for data over the mesh network as would be distributed over a larger area of the chip. Results of methods loaded in this specific configuration are included in the performance analysis section of the Results: Chapter 7.

The goal of the JavaFlow machine is to implement the maximum number of Instruction Nodes consistent with technology ground rules. In addition, housing more instructions may be achieved with reasonable numbers of Instruction Data Units inside each Instruction node. For simplicity and to stress the DataFlow Fabric, the simulations in Chapter 7 utilize a single Instruction Data Unit in each Instruction Node.

## **SECTION 4.3 - LIMITATIONS**

One of the key advantages of the JavaFlow machine is that the state data for each method is distributed throughout the DataFlow Fabric. Since this state data is finite and small, there are several side effects that may limit some of the methods that can be deployed. Like the TRIPS machine, each method must execute atomically. This means that the Anchor node, which is the first node of a method may not allow any subsequent execution of the method until the current thread exits. Furthermore, recursive calls are not allowed. A thread may be executing multiple methods at any given time, but each individual method may have only one thread active at a time.

The ByteCode instruction set has a series of special instructions that cannot be directly executed by the elements in the DataFlow Fabric. These special instructions must send messages to the GPP for assistance. The instruction mix data indicates that this should occur infrequently and have minimal impact on system performance. Specific instructions are described in Section 6.3.

## **Chapter 5: Benchmarks**

## **SECTION 5.1 - OVERVIEW**

Prior to the detailed definition of the JavaFlow machine, it was necessary to understand the basic structure of Java Methods in real applications and to determine if a DataFlow structure could be defined and optimized for their execution. The benchmark analysis had several major components:

- Size of method

- Each method's effect on the overall benchmark performance

- Dynamic instruction mix

- Static instruction mix

- Number of jumps (control flow events)

- Maximum register and stack requirements for each method