https://theses.gla.ac.uk/

# Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

https://theses.gla.ac.uk/

# Theses Digitisation:

https://www.gla.ac.uk/myglasgow/research/enlighten/theses/digitisation/

This is a digitised version of the original print thesis.

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Enlighten: Theses

<a href="https://theses.gla.ac.uk/">https://theses.gla.ac.uk/</a>

research-enlighten@glasgow.ac.uk

# Reconfigurable Cores for Wireless Appliances: Turbo Codes

**VOLUME 1 (OF 2)**

**Edward Brown**

A themed portfolio submitted to The Universities of

> Edinburgh, Glasgow, Heriot-Watt and Strathclyde

For the Degree of Doctor of Engineering in System Level Integration

© Edward Brown, May 2004

ProQuest Number: 10754011

# All rights reserved

# INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

# ProQuest 10754011

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

#### **Abstract**

This portfolio thesis documents the work carried out by the author whilst enrolled in the Engineering Doctorate (EngD) programme. The author completed the majority of the work at the sponsoring company, Xilinx, in their Digital Signal Processing division.

The thesis introduces the subject of Turbo codes, highlighting the motivation behind their inclusion in international standards. Particular attention is given to the cdma2000 and UMTS third generation mobile telephony standards. Both the technical and commercial advantages/disadvantages of implementing Turbo codes in a Field Programmable Gate Array (FPGA) based system are discussed. The subject of third generation mobile technology is also discussed, this includes an introduction to spread spectrum and rake receivers.

The commercial relevance of all projects conducted is discussed. These projects allowed the sponsoring company to highlight the advantages of using FPGAs in third generation mobile base stations.

A novel system for testing forward error correction (FEC) codes is presented. Results obtained are shown and discussed. A novel parameterisable Turbo decoder will also be highlighted. The decoder in question allows the user to specify certain criteria that can be used to control the memory used by the decoder and its latency. A novel hardware architecture for Turbo decoders is proposed, as is a unique channel variance value that optimises a cdma2000 Turbo decoder. Other subjects covered are Duo-Binary Turbo codes, Turbo decoder hardware architectures and how to calculate the input values to Turbo decoders.

# **Declaration of Originality**

The material in this thesis is entirely the results of my own independent research under the supervision of Dr J. M. Irvine and Mr B. Wilkie and is not the outcome of any collaborative work. All published or unpublished material used in this thesis has been given full acknowledgement.

**Edward Brown**

28 September 2005

# Acknowledgements

On a professional level I would like to thank both of my supervisors, Bill Wilkie and Dr. James Irvine, for all the support and advice they have provided throughout my EngD. I am extremely grateful for the time they spent advising me on all matters, from reviewing my conference submissions to answering technical queries. Special thanks also go to Dr. Colin Carruthers and Dr. David Lawrie. Colin, along with Bill, awarded me the opportunity to work with Xilinx, while David proved an invaluable resource throughout the latter stages of my EngD project. I also would not have been able to enrol on the EngD without the help of my former supervisor, Patrick Lysaght. I would therefore, also like to thank Patrick for giving me the opportunity to do the EngD.

I would also like to thank all of Xilinx Edinburgh, especially the DSP team, for making me feel so welcome. Also to Ann and Rhona, thanks for driving and/or entertaining me on all those long journeys along the M8.

I would like to express my gratitude to the ISLI and all its staff, particularly Alexandra Buchanan for all the help and guidance she has provided. Other staff I would like to thank are Sian Williams for all her help in the library, and also for helping with EngD matters in the latter stages of my degree, including arranging my viva, and Wendy Glendinning for all her help during the MSc portion of the EngD.

On a more personal basis I'd like to thank my Mum and Dad for all the support they have given me throughout not only my EngD, but my undergraduate degree as well. I would like to thank my sister and nephew for always supporting me throughout both of my degrees. I'd like to thank all my friends, particularly Linda and Farah for supporting me throughout my EngD, Linda and Louise, my flatmates, for putting up with me throughout my write up and my golfing/drinking buddies, Richie, Steve, Nige, Jamie, Andy and Brian for providing some much needed distraction over the last 5 years.

# Glossary

3G Third generation mobile, an advancement from 2G standards, such as

GSM and IS-95, that allows higher data rates. The European standard is the UMTS standard, the United States of America

standard is the cdma2000 standard.

Alpha Probability One of the three probabilities required to calculate final Turbo

decoder output. The alpha probability is calculated by performing a

forward trace of the trellis.

ASIC Application Specific Integrated Circuit. An integrated circuit that is

not reconfigurable. It is used for one particular purpose.

AWGN channel Additive white Gaussian noise channel. A channel that is often used

in communication system models. The name comes from the fact that the noise is linear and has an average value of 1 over its entire

distribution.

BER Bit error rate. A measure for how many bits in a particular sequence

are in error. Usually, BER is given in powers of ten, e.g. 10<sup>-6</sup>,

meaning 1 bit in every 1 million bits are in error.

BER Tester. A platform that can be used to determine the BER of a

particular system.

Beta probability Required to calculate the final Turbo decoder output. Calculated by

performing a backward trace of the trellis.

Block code A type of forward error correction (FEC) code that relies only on the

current input for its output.

cdma2000 The 3G standard to be implemented in the United States of America.

Coding gain The difference in dB between two BER curves, when compared at

the same BER value.

Convolutional code A type of FEC code whose current output is dependent upon the

previous *m* inputs.

DSP Digital Signal Processor. A specialised microprocessor that is used

in digital signal processing (DSP). It contains components, such as

Multiply-Accumulators (MACs), that are often used in DSP.

DVB Digital Video Broadcasting. A standard that uses Turbo coding on

its reverse satellite channel.

| Еь |

|----|

| Nα |

A measure of signal to noise ratio, where  $E_{\text{b}}$  is the energy per bit and

$N_0$  is the noise spectral density.

Fading channel

A channel model that is more like a real mobile channel than the AWGN channel introduced earlier. The most common fading channels are the Rayleigh channel and the Rician channel. The Rayleigh channel is a model where the source and destination have no direct line of sight. In the Rician channel, the source and destination has a direct line of sight or has a dominant component among the signals received by the destination.

Fast termination

A method of reducing the average number of iterations performed by the Turbo decoder.

FEC

Forward Error Correction. A method of detecting and correcting errors in a communications system.

FER

Frame Error Rate. A measure of error in an FEC system. As data in 3G systems is transmitted in frames, this provides a quantifiable measure of how many frames would be dropped for any given system.

**FPGA**

Field Programmable Gate Array. A reconfigurable integrated circuit containing DSP specific components, such as multipliers.

Gamma probability

The gamma probability is required to calculate the final output from the Turbo decoder. It is also known as the branch probability.

Interleaver

An interleaver is used to de-correlate data entering the second Turbo component encoder from the first Turbo component encoder, improving the BER performance of the Turbo code in the process.

LLR

Log likelihood ratio. Data input to a Turbo decoder is in the format of a LLR. An LLR gives the probability of a particular symbol representing either a 1 or a 0. The larger the magnitude of the LLR, the higher the probability that it is correct.

Log-MAP

Applying the MAP algorithm in the logarithm domain allows it to be implemented in hardware more easily, operations such as exponentials disappear and multiplications turn into additions.

MAP

Maximum a posteriori. The MAP algorithm is used in Turbo codes to calculate the probability that a particular bit at a particular point in time is either a 1 or a 0.

Max-log-MAP A simpler variation of the log-MAP algorithm. The log-MAP

algorithm requires a look up table to produce its output. The max-log-MAP algorithm simplifies the log-MAP by removing the look up

table.

Max Scale The Max Scale is a variation of the max-log-MAP algorithm. It

applies a scaling factor to the Turbo decoder output, improving the

BER performance of the Turbo decoder.

Puncturing A method of increasing the information rate of a FEC code. The

FEC code is punctured by removing certain symbols at the Turbo encoder output. The punctured symbols are replaced by an all zero codeword at the Turbo decoder input, thereby decreasing the BER

performance.

RSC Recursive systematic convolutional. Turbo component encoders are

RSC encoders, an RSC encoder is one that contains feedback and

whose input is a part of the encoder output symbol.

SISO Soft-in, soft-out. Turbo component decoders are SISO decoders, by

both inputting and outputting soft bits each component decoder can share information on what they think the Turbo decoder output should be. The main types of SISO decoder used implement either

the MAP algorithm or the SOVA.

SOVA Soft output Viterbi algorithm. A variation of the Viterbi algorithm

that outputs soft bits, allowing it to be used to implement a Turbo

component decoder.

Spread spectrum Almost all 3G standards are based on spread spectrum systems.

Spread spectrum is a term that describes a system that allows users to

share both time and frequency.

Turbo code A turbo code is a type of FEC, traditional Turbo codes use RSC

encoders as a component encoder. Turbo product codes use block

encoders as component encoders.

Turbo encoder The Turbo encoder is used at the transmission side of the

communications system. It contains 2 encoders separated by an

interleaver. Each encoder is known as a component encoder.

Turbo decoder The Turbo decoder is used at the receiver side of the

communications system. It contains 2 SISO decoders separated by

an interleaver and de-interleaver. Each SISO decoder is known as a

component decoder.

UMTS The name of the 3G standard implemented in Europe.

VHDL Very high speed integrated circuit description language. A

programming language used to model hardware systems. Widely

used when designing FPGA circuits.

Sliding window A technique used to reduce the overall latency of a Turbo decoder,

allows the Turbo decoder to begin decoding before a complete set of

data has been received.

# **Symbols Used**

| $\alpha_i(s)$           | Forward state metric/probability      |

|-------------------------|---------------------------------------|

| $\beta_{t-1}(s')$       | Backward state metric/probability     |

| $\gamma_k(s', s)$       | Branch metric/probability             |

| τ                       | Measure of time                       |

| i                       | Number of decoder iterations          |

| L                       | Measure of memory                     |

| $L(u_k)$                | Log-likelihood ratio                  |

| $L^e(u_k)$              | Extrinsic data                        |

| $L_{IN}^{e}(u_{k})$     | Component decoder extrinsic input     |

| $L_{OUT}^{e}(u_{k})$    | Component decoder extrinsic output    |

| m                       | Number of component encoders/decoders |

| N                       | Block size                            |

| q                       | Symbol width                          |

| R                       | Code rate                             |

| S                       | Number of states in trellis           |

| $u_t$                   | Turbo encoder input                   |

| $\hat{u}_{i}$           | Turbo decoder output                  |

| w                       | Sliding window width                  |

| $X_{\iota}^{s}$         | RSC 1 systematic output               |

| $X_{t}^{S}$             | RSC 2 systematic output               |

| $X_{t}^{P}$             | RSC 1 parity output                   |

| $X_t^{'P}$              | RSC 2 parity output                   |

| $Y_{t}^{S}$             | SISO 1systematic input                |

| <i>Y</i> , 's           | SISO 2 systematic input               |

| $Y_t^P$                 | SISO 1 parity input                   |

| $Y_{\iota\lambda}^{'P}$ | SISO 2 parity input                   |

| y                       | Turbo decoder input                   |

# **Contents**

| 1.             | Executive Summary1      |

|----------------|-------------------------|

| 1.1.           | Projects1               |

| 1.2.           | Commercial Relevance3   |

| 1.3.           | Novelty3                |

| 1.4.           | Milestones4             |

| 2.             | Portfolio Organisation6 |

| 3.             | Taught Modules8         |

| 3.1.           | Technical Credits8      |

| 3.2.           | Business Modules9       |

| 4.             | Publications10          |

| 5.             | Commercial Relevance11  |

| 5.1.           | FPGAs11                 |

| 5.2.           | Contribution13          |

| 6.             | Technical Background15  |

| 6.1.           | Convolutional Codes16   |

| 6.2.           | Turbo Codes18           |

| 6 <b>.2.</b> 1 | . Turbo Encoder20       |

| 6.2.2 | . Interleaver22                      |

|-------|--------------------------------------|

| 6.2.3 | . Turbo Decoder23                    |

| 6.3.  | Field Programmable Gate Arrays28     |

| 6.4.  | Third Generation Mobile Technology30 |

| 7.    | Results and Discussion35             |

| 7.1.  | Bit Error Rate Test Platform35       |

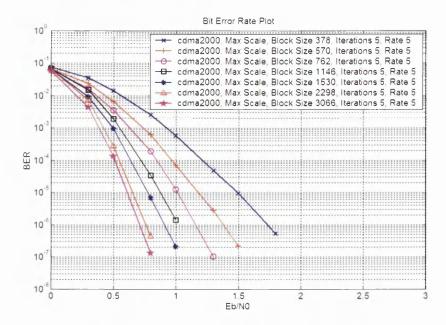

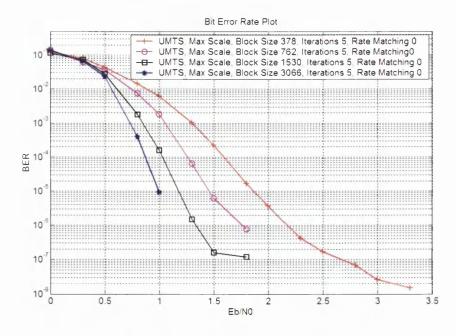

| 7.2.  | Block Size39                         |

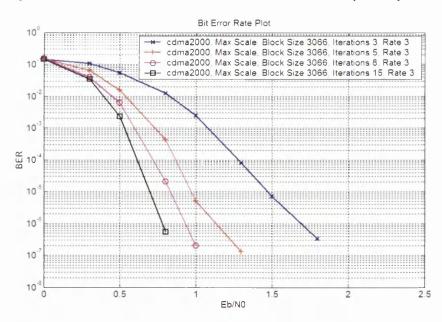

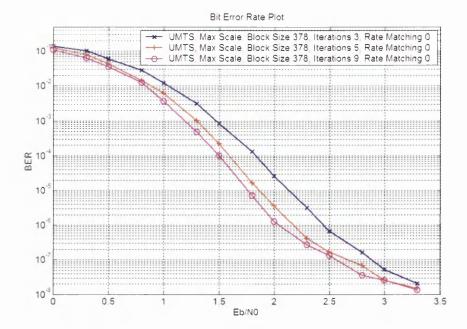

| 7.3.  | Iterations41                         |

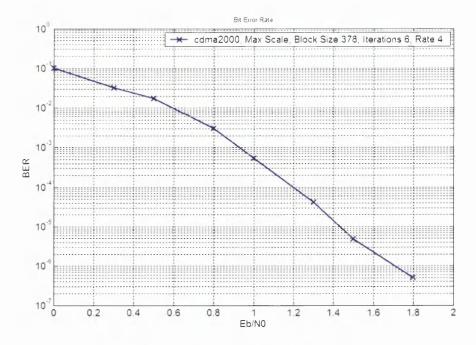

| 7.4.  | Code Rate45                          |

| 7.5.  | Parameterisable Turbo Decoder45      |

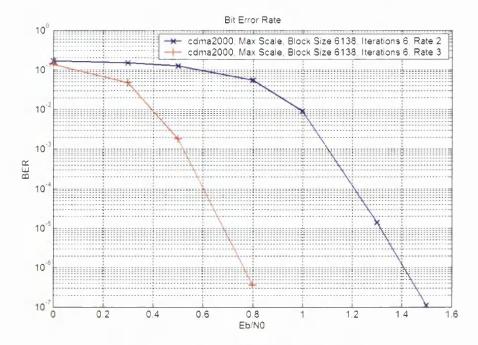

| 7.6.  | cdma2000 vs. UMTS53                  |

| 7.7.  | Channel Variance55                   |

| 7.8.  | Comparison With Published Results59  |

| 8.    | Conclusion65                         |

| 8.1.  | Future Direction67                   |

| 9.    | References                           |

# List of Figures

| Figure 1: Work carried out by the EngD over a four year period                | 5       |

|-------------------------------------------------------------------------------|---------|

| Figure 2: Organisation of Volume1                                             | 7       |

| Figure 3: Overview of a simple communications system                          | 15      |

| Figure 4: Convolutional encoder                                               | 16      |

| Figure 5: RSC encoder                                                         | 17      |

| Figure 6: RSC encoder with trellis termination                                | 17      |

| Figure 7: Top-level view of a Turbo encoder                                   | 18      |

| Figure 8: Top-level view of a Turbo decoder                                   | 19      |

| Figure 9: UMTS component encoder                                              | 20      |

| Figure 10: cdma2000 component encoder                                         | 20      |

| Figure 11: DVB component encoder                                              | 22      |

| Figure 12: cdma2000 standard interleaver                                      | 23      |

| Figure 13: Calculating alpha probability                                      | 25      |

| Figure 14: Calculating beta probability                                       | 26      |

| Figure 15: Add, compare, select, offset unit                                  | 27      |

| Figure 16: FPGA basic structure                                               | 28      |

| Figure 17: System Generator DSP design flow                                   | 29      |

| Figure 18: System Generator hardware design flow                              | 29      |

| Figure 19: Spread spectrum signal                                             | 30      |

| Figure 20: Multipath channel                                                  | 31      |

| Figure 21: Signal received at base station                                    | 31      |

| Figure 22: Rake receiver                                                      | 32      |

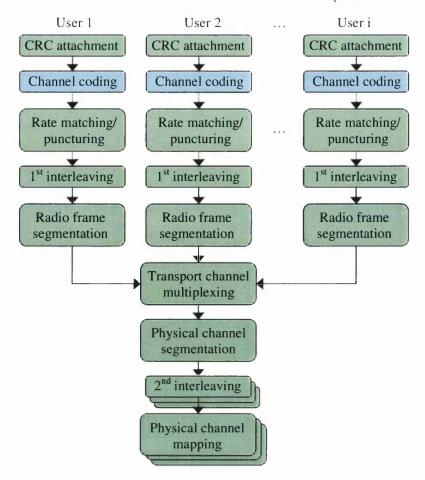

| Figure 23: Transport channel of a typical 3G system                           | 33      |

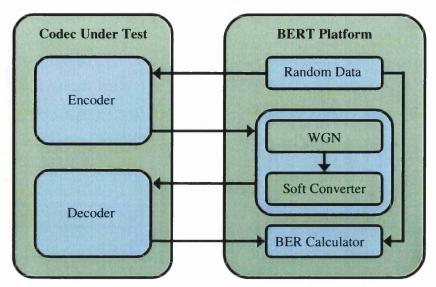

| Figure 24: BERT Platform top-level                                            | 36      |

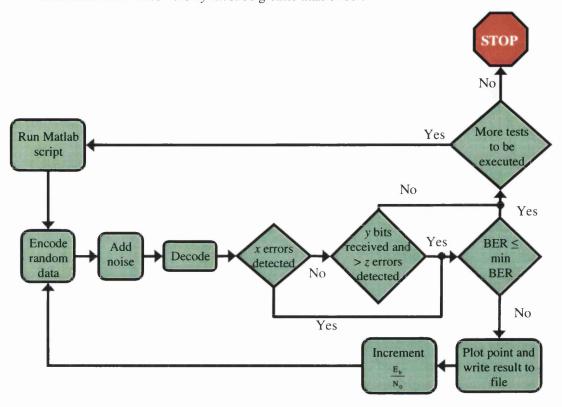

| Figure 25: Procedure for running BERT                                         | 37      |

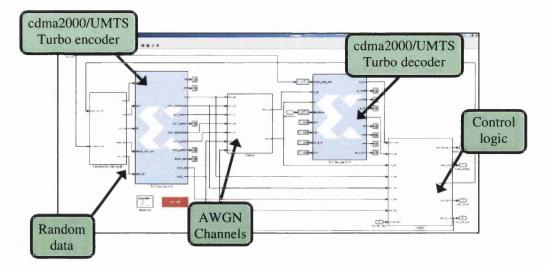

| Figure 26: System Generator implementation of BERT platform                   | 38      |

| Figure 27: BER performance of cdma2000 Turbo codec as block size changes      | 40      |

| Figure 28 BER performance of UMTS Turbo codec as block size changes           | 40      |

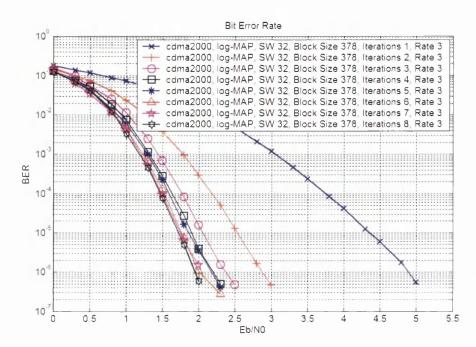

| Figure 29: BER performance of cdma2000 Turbo codec as number of iterations pe | rformed |

| increases                                                                     | 41      |

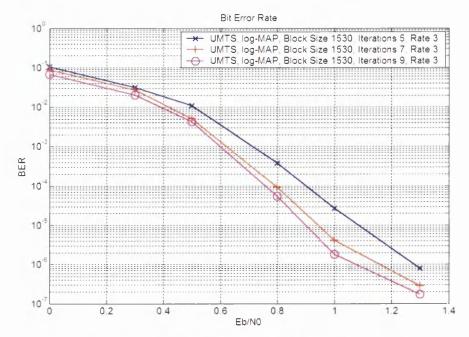

| Figure 30: BER performance of UMTS Turbo codec as number of iterations perfor | med     |

| increases                                                                     | 42      |

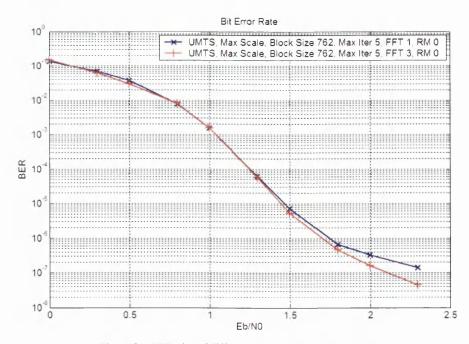

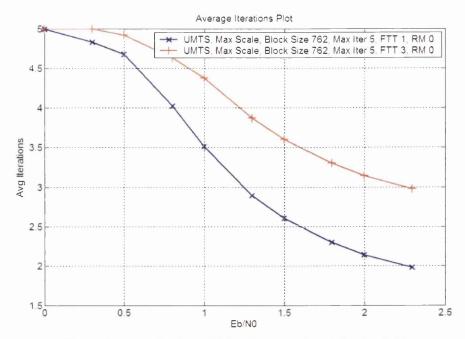

| Figure 31: BER plot of different fast termination thresholds                  | 43      |

| Figure 32: Average iterations plot for different fast termination thresholds                    | 44      |

|-------------------------------------------------------------------------------------------------|---------|

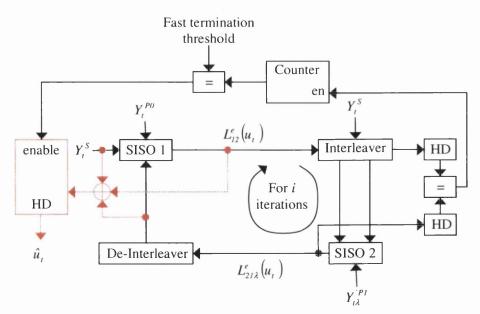

| Figure 33: Turbo decoder with fast termination implemented                                      | 44      |

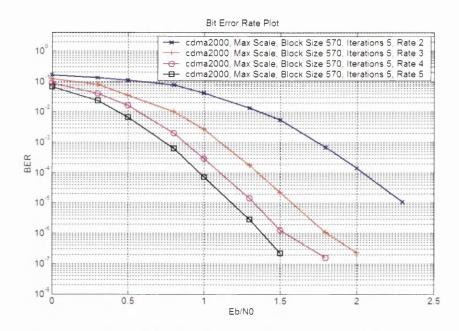

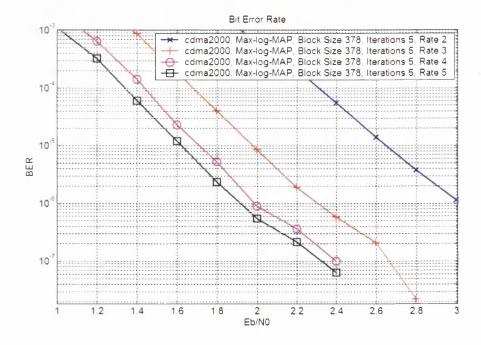

| Figure 34: Effect of using different code rates on BER performance in cdma2000 T                | Curbo   |

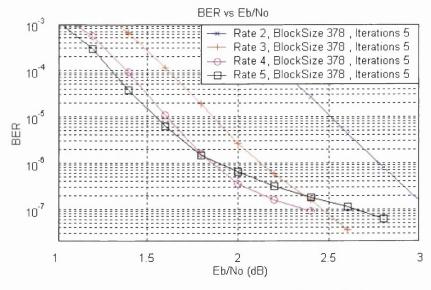

| codec                                                                                           | 45      |

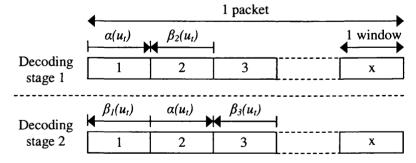

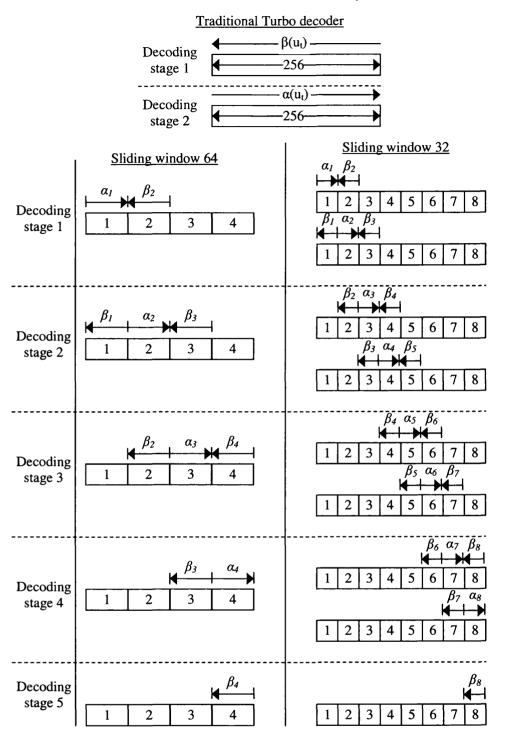

| Figure 35: Sliding window technique                                                             | 46      |

| Figure 36: Decoding of packet with block size 256 using traditional Turbo decoder               | , Turbo |

| decoder with sliding window 64 and Turbo decoder with sliding window 32                         | 48      |

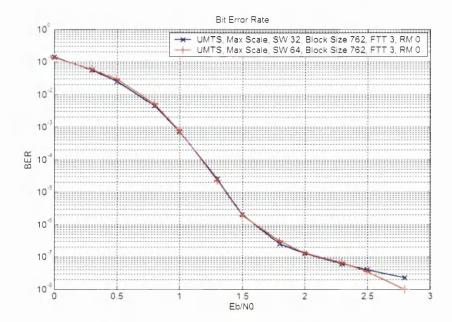

| Figure 37: FER plot showing different sliding window sizes                                      | 50      |

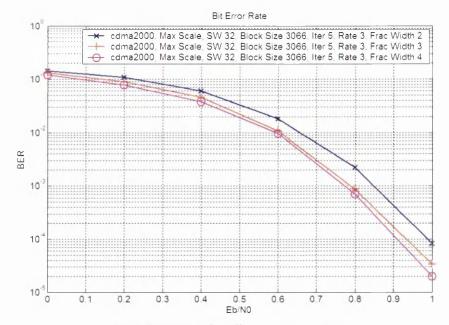

| Figure 38: BER plot for different internal metrics                                              | 51      |

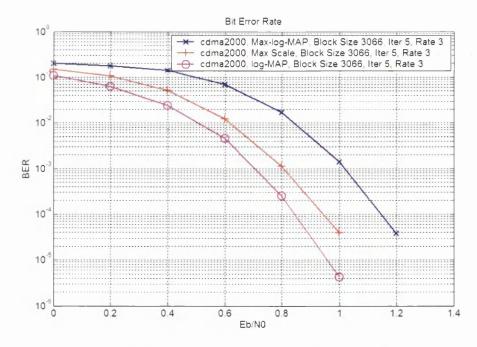

| Figure 39: BER performance of log-MAP, Max-log-MAP and Max Scale algorithm                      | n52     |

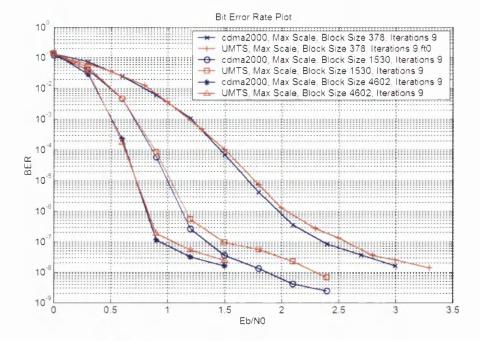

| Figure 40: Comparison of cdma2000 and UMTS Turbo decoders                                       | 54      |

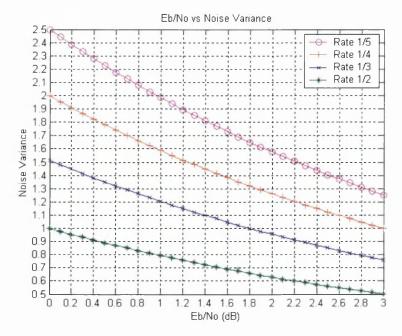

| Figure 41: Plot of $\frac{E_b}{N_0}$ against noise variance                                     | 56      |

| Figure 42: Non-optimal BER performance of code rate $\frac{1}{5}$ using $\sigma^2$ value of 1   | 57      |

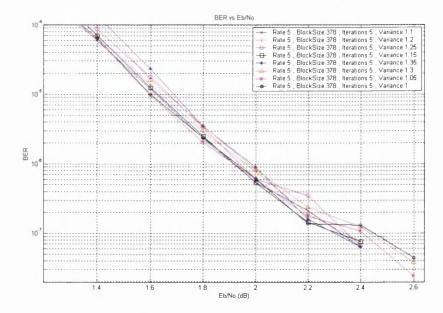

| Figure 43: Code rate ½ BER plots for noise variance values between 1 and 1.35                   | 58      |

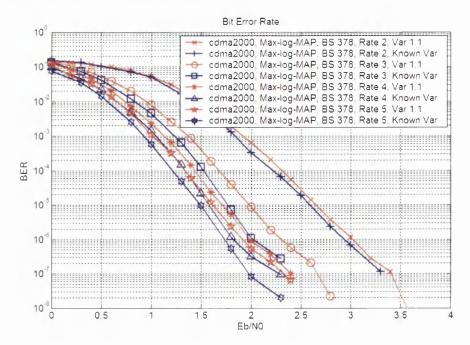

| Figure 44: Optimal BER performance of code rate $\frac{1}{5}$ using $\sigma^2$ value of 1·1     | 58      |

| Figure 45: Comparison of BER plots with known $\sigma^2$ and BER plots using $\sigma^2=1\cdot1$ | 59      |

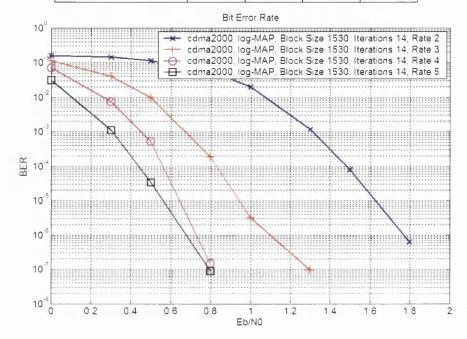

| Figure 46: BER plot for comparison with Valenti and Sun [57]                                    | 60      |

| Figure 47: BER plot for comparison with Qi [58]                                                 | 61      |

| Figure 48: BER plot for comparison with Sugimoto et al [59]                                     | 62      |

| Figure 49: BER plot for comparison with Sugimoto et al [59]                                     | 63      |

| Figure 50: BER plot for comparison with Valenti and Sun [57]                                    | 64      |

# **List of Tables**

| Table 1: Technical credits breakdown                                                   | 8    |

|----------------------------------------------------------------------------------------|------|

| Table 2: Business credits breakdown                                                    | 9    |

| Table 3: cdma2000 puncturing patterns for data                                         | 21   |

| Table 4: cdma2000 puncturing patterns for trellis termination                          | 21   |

| Table 5: DVB standard puncturing patterns                                              | 22   |

| Table 6: Resources available and resources required for various BERT implementations.  | 39   |

| Table 7: FPGA resources required for different internal fractional widths              | 51   |

| Table 8: FPGA resources used for different SISO algorithms                             | . 53 |

| Table 9: Comparison of Valenti and Sun [58] with results produced by the RE at BER of  | f    |

| 10 <sup>-6</sup>                                                                       | . 59 |

| Table 10: Comparison of Qi [58] with results produced by the RE                        | .61  |

| Table 11: Comparison of Sugimoto et al [59]                                            | .61  |

| Table 12: Comparison of Sugimoto et al [59]                                            | . 52 |

| Table 13: Comparison of Valenti and Sun [57] with results produced by the RE at BER of | of   |

| 10 <sup>-6</sup>                                                                       | . 63 |

# 1. Executive Summary

The initial specification of the Engineering Doctorate (EngD) industrial project stated that by the time of its completion the EngD Research Engineer (RE) would have had investigated new opportunities within wireless appliances to exploit the reconfigurability of Field Programmable Gate Arrays (FPGAs) as a key, product-differentiating feature. This was achieved through numerous projects, all of which were based around Turbo codes.

#### 1.1. Projects

The first stage of the industrial project was to decide on a task that was mutually beneficial to the sponsoring company, Xilinx, and the RE. Xilinx had acquired a Turbo encoder and Turbo decoder from Frontier Designs [1] that conformed to the UMTS specification [2]. To create the Turbo encoder and decoder, Frontier used their ART Designer tool [3, 4] to convert C++ code to a synthesizable VHDL netlist. As Xilinx intellectual property (IP) is written in structural VHDL it can take a relatively long time to simulate. To overcome this problem Xilinx usually supplied a behavioural model of the design to customers for simulation purposes, this had not been supplied by Frontier. It was decided that this would be a perfect learning opportunity for the RE to familiarise himself with Turbo codes, while producing something that benefited the sponsoring company and their customers. This stage of the project included both a literature search and practical work. The work carried out in this portion of the industrial project is summarised in Appendices A-C (vol. 2/pp. 1-25}. The time scale to complete this portion of the project can be obtained from Figure 1. The reports produced by the RE during this project were of great commercial relevance to Xilinx, particularly 'Investigation of Turbo Decoder Hardware Architectures', Appendix D (vol.2/pp. 26-40). At this time Xilinx were designing a Turbo codec that complied with the cdma2000 standard [5]. 'Investigation of Turbo Decoder Hardware Architectures' allowed Xilinx to determine what hardware architecture should be used for their cdma2000 Turbo decoder.

Figure 1 highlights the commercial relevance and novelty of all projects undertaken by the RE and shows milestones passed by the RE as the industrial project progressed.

The second project tackled was to use a bit error rate test (BERT) platform [6] created by Nallatech to test the Frontier Turbo codec. The forward error correction (FEC) designs

were instantiated in the BERT using a VHDL wrapper. The FEC designs could be either written in VHDL or be an EDIF netlist. The FEC design under test (DUT) could then be stimulated by random data supplied by a Matlab script. Throughout the life of this project there were conflicts between the EDIF netlist supplied by Frontier and the Nallatech BERT, as a result the Frontier Turbo codec could not be tested. The development of the Nallatech BERT was passed to a staff Engineer at Xilinx, while the RE began to develop a recursive systematic convolutional (RSC) encoder that conformed to the cdma2000 Turbo code standard. In between the two projects the RE was able to present a poster [7] highlighting the advantages of using both Turbo codes and FPGAs.

While the cdma2000 encoder was being developed Xilinx became interested in the subject of Duo-Binary Turbo codes, which were to be used in the Digital Video Broadcasting (DVB) standard [8]. The RE was asked to research the subject of Duo-Binary Turbo codes and compile a report on the subject, Appendix E {vol. 2/pp. 41-50}, paying particular attention to the differences between Duo-Binary and standard Turbo codes. This allowed Xilinx to determine the effort required to convert their cdma2000 codec to a DVB codec.

Once the cdma2000 Turbo codec was complete it was tested using the Nallatech BERT platform, this helped Xilinx verify that their codec design was working correctly while creating marketing data for their design. As with most Xilinx cores the Turbo decoder was parameterisable. The user could specify parameters such as sliding window size, decoder input width and which algorithm to use for the decoder. The parameterisable aspect of the design allowed the RE to test the design using various configurations. The results of these tests were presented by the RE in two separate publications [9, 10]. These papers helped Xilinx publicise the reconfigurable nature of their design while allowing the RE to publish novel research.

One subject that was of interest to the RE and Xilinx was the subject of how to manipulate the input data to a Turbo decoder so that the best possible BER performance was achieved. The result of this investigation was the discovery of a novel variance value that optimised the performance of Xilinx's Turbo decoder; this is documented in Appendix F {vol. 2/pp. 51-65}. When this literature search was taking place it became apparent that the Nallatech BERT platform was not performing optimally: often the BERT would crash when a test was running. It was therefore necessary that the problems with the Nallatech BERT be

solved or a new system be designed. Around the same time a new version of the Xilinx System Generator tool [11] had recently been released. It was decided that the RE should implement a BERT in System Generator. Implementing a BERT in System Generator allowed the RE to create something that was completely novel and allowed Xilinx to investigate how the System Generator tool performs when it is used in system development. All results presented in this thesis were obtained using the System Generator BERT. A System Generator design can be altered repeatedly and implemented on any compatible Xilinx FPGA platform [12, 13, 14] further highlighting the reconfigurable nature of the System Generator tool and Xilinx designs.

#### 1.2. Commercial Relevance

The subject of commercial relevance is dealt with more comprehensively in Chapter 5. A summary of the commercial relevance of all projects is summarised below in reference to Figure 1.

- Behavioural models and literature search: The report "Investigation of Turbo Decoder Hardware Architectures", Appendix D {vol. 2/pp. 26-40}.

- Nallatech BERT: The BERT was used by the RE to produce BER plots for Xilinx's cdma2000 Turbo codec, a selection of the results produced were presented by the RE [9].

- cdma2000 Turbo encoder: The RE designed a (RSC) encoder that conformed to the cdma2000 standard.

- Investigation of calculating Turbo decoder inputs: The outcome of this

investigation was a report entitled "Calculating Inputs to Turbo Decoders",

Appendix F {vol. 2/pp. 51-65}. The report suggested a novel value that could be

used for channel variance, the value proposed optimised the Turbo decoder core

created by Xilinx.

- SysGen BERT: The System Generator BERT allowed Xilinx to research and market their Turbo code cores and their 3G solutions in general.

# 1.3. Novelty

A summary of the novel aspects of the EngD project are shown below in reference to Figure 1.

Behavioural models and Literature search: Presentation of original hardware architectures.

- Nallatech BERT: This project highlighted a novel parameterisable Turbo decode [9].

- **cdma2000 Turbo encoder:** The RSC encoder was designed entirely using Xilinx structural libraries and was targeted to the Xilinx Virtex-II FPGA.

- **Investigation of calculating Turbo decoder inputs:** Presentation of a novel channel variance value that optimised the performance of a Turbo decoder.

- SysGen BERT: The System Generator BERT is novel due to the fact that it is

designed completely in System Generator. Designing in System Generator allowed

features to be added rapidly and for the testing system to be automated [15]. As it is

designed in System Generator it allows non-FPGA designers to use and upgrade the

BERT platform in an FPGA environment without using standard FPGA design

techniques such as HDLs.

# 1.4. Milestones

The milestones referenced in Figure 1 are detailed below.

- 1: June 2001, 120 taught technical credits achieved.

- 2: February 2002, Turbo encoder behavioural model complete. Report on encoder behavioural model complete, Introduction to Turbo codes report complete.

- 3: June 2002, Turbo decoder behavioural model partially complete. Report on decoder behavioural model complete, Investigation of Turbo Decoder Hardware Architectures report complete.

- 4: December 2002, poster presentation, SET for Europe.

- 5: May 2003, Duo-Binary Turbo Codes report complete.

- 6: September 2003, paper published at IEE Colloquium on DSP Enabled Radio.

- 7: November 2003, Calculating Input Values for Turbo Decoders report complete.

- 8: January 2004, 60 taught business credits achieved.

- 9: May 2004, paper published at World Wireless Congress.

- 10: June 2004, System Generator BERT completed.

Figure 1: Work carried out by the EngD over a four year period

# 2. Portfolio Organisation

The Portfolio Thesis is presented in two volumes. Volume 1 presents the main motivations and outcomes of the work. It also shows the commercial relevance and novelty of the work. Volume 2 presents numerous appendices containing papers and reports compiled by the RE as the EngD progressed. All reports presented are on the subject of Turbo codes but cover numerous areas within the Turbo code field.

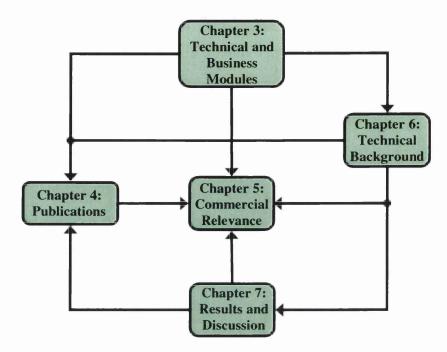

The remainder of Volume 1 is organised as follows: Chapter 3 discusses the taught technical and business credits that were chosen by the RE, showing how the classes chosen aided the RE in both his research and in gaining an understanding on how the projects undertaken impacted on Xilinx commercially. Chapter 4 highlights all publications made by the RE. The commercial relevance of projects undertaken by the RE is examined in Chapter 5. It is shown how the numerous projects conducted by the RE contributed to the commercial success of Xilinx's 3G solutions and how FPGAs can be used to reduce the cost of building a mobile base station.

Chapter 6 presents the technical background to the RE's industrial project. Firstly the subject of channel coding is introduced. Particular attention is given to the subject of convolutional codes and the differences between a standard convolutional encoder and a recursive systematic convolutional (RSC) encoder, used in Turbo codes, is given. An introduction to Turbo codes is then presented. Each component, the Turbo encoder, interleaver and Turbo decoder, in the Turbo codec are described separately. The Section on Turbo encoders includes a discussion on the standards looked at by the RE during the EngD, the UMTS [2], cdma2000 [5] and DVB [8]. The advantages and disadvantages of implementing a Turbo codec in a Field Programmable Gate Array (FPGA) based system are also discussed. Chapter 7 will highlight some of the results obtained by the RE and discuss the significance of these results. The results included tests that change inputs such as block size and code rate. Novel results such as a comparison between UMTS and cdma2000 Turbo codecs will also be analysed. Finally, Chapter 8 will summarise the thesis and propose future work that should be carried out.

Figure 2 shows how each of the chapters in Volume 1 relate to each other. All chapters in some way or another have an impact on the commercial relevance of the project. As stated

previously, the business modules have a direct link to the commercial relevance of the projects undertaken. Any results generated were used to promote Xilinx 3G solutions to potential customers, similarly any publications highlighting these results promoted Xilinx's 3G solutions to international audiences.

Figure 2: Organisation of Volume 1

# 3. Taught Modules

Taught technical credits were obtained in the RE's first year at the Institute for System Level Integration (ISLI). The 60 business credits were obtained from the University of Strathclyde Graduate Business School.

#### 3.1. Technical Credits

In total 120 credits were gained at the ISLI, the subjects taken by the RE to gain these credits are shown in Table 1. The classes at the ISLI provided an insight into many aspects of system on a chip (SoC) design. Classes that benefited the RE's industrial project were: Intellectual Property Block Authoring (IPBA); Intellectual Property Block Integration (IPBI); Communication Algorithms; and Mobile Communications. Both IPBA and IPBI contributed to the RE's knowledge of digital design with a particular emphasis on design reuse through parameterisation. Communication Algorithms and Mobile Communications helped the RE understand some of the basic concepts of mobile telephony and error control coding.

Table 1: Technical credits breakdown

| Class                                | Credits |

|--------------------------------------|---------|

| SoC Overview                         | 2       |

| System Partitioning                  | 12      |

| IPBA                                 | 12      |

| IPBI                                 | 12      |

| VLSI Design                          | 12      |

| Software Engineering                 | 15      |

| Microcontrollers and Microprocessors | 12      |

| Towards Deep Submicron               | 7       |

| Communications Algorithms            | 12      |

| Multimedia and Video                 | 7       |

| Mobile Communications                | 7       |

| Broadband and Digital Networks       | 10      |

| Total                                | 120     |

#### 3.2. Business Modules

Completing the business modules allowed the RE to be more aware of the commercial relevance of the work carried out during the industrial project. Sixty credits were gained by the RE from the Master of Business Administration (MBA) modules available at the University of Strathclyde Graduate Business School. The MBA modules chosen by the RE and their credit weighting are shown in Table 2.

Table 2: Business credits breakdown

| Class                               | Credits |  |

|-------------------------------------|---------|--|

| Marketing Management                | 12      |  |

| Data Management                     | 6       |  |

| Information Systems                 | 6       |  |

| Managing People in Organisations    | 12      |  |

| Finance and Financial Management    | 12      |  |

| Financial and Management Accounting | 12      |  |

| Total                               | 60      |  |

From a purely research point of view Information Systems was very beneficial for the RE. It helped the RE gain an understanding of how to manage and extract necessary information where an abundance of information is at the researcher's disposal. Both Finance and Financial Management and Financial and Management Accounting allowed the RE to recognise how important financial constraints and project deadlines were in allowing projects to be financially beneficial to the company. Marketing Management was of particular significance to the RE. It introduced the RE to new concepts that could be used to highlight work the RE had completed and allowed the RE to look at products from a customer's viewpoint. Gaining this ability meant that the RE could improve systems such as the System Generator BERT by adding features which improved its usability.

#### 4. Publications

The RE made numerous presentations at international conferences. The publications made by the RE are highlighted below.

- Reconfigurable Cores for Wireless Appliances [7]: An introduction to both FPGAs and Turbo codes. The RE also highlighted the advantages of implementing Turbo codes in FPGAs.

- A Memory-efficient Parameterisable FPGA Implementation of the cdma2000

Turbo Codec [9]: Presented a novel parameterisable Turbo decoder. The RE used the Nallatech BERT to produce results that showed how changing the parameters of the Turbo codec core affected performance.

- A Memory-efficient Parameterizable FPGA Implementation of the cdma2000

Turbo Codec [10]: The paper presented here showed how the BERT could be used to calculate novel results such as a channel variance value that optimised the Turbo codec core.

- Rapid Prototyping of a Test Harness for Forward Error Correcting Codes [16]: The paper concentrated on the implementation of the System Generator BERT designed by the RE. It highlighted a number of inputs that made the BERT user programmable. The publication was included in the conference session 'Novel Applications of Reconfigurability'.

- Rapid Prototyping of a Test Harness for Forward Error Correcting Codes

[15]: In this paper the RE presented a number of results that were produced using

the System Generator BERT. The results included a comparison between the

cdma2000 and UMTS Turbo codecs.

# 5. Commercial Relevance

By the time 3G mobile networks were launched in the UK [17] mobile telephony, due to its rapid acceptance by the consumer, was a relatively mature product. Consumers therefore had become accustomed to a certain level of quality for a certain price on mobile networks, for example seamless handover between base stations while on a call and near 100% network coverage. Mobile telephones were expected to be lightweight and compact, have a battery that could last for 2 to 3 days and offer basic functions such as games and a calendar. Both network operators and phone manufacturers faced problems when 3G telephony was initially launched, phones and network tariffs were expensive, battery life was short and phones were relatively large and heavy. One of the major technological challenges for 3G network operators was implementing an algorithm that could seamlessly handover calls between GSM and 3G networks. This is partly due to the fact that the UMTS standard implemented in Europe has no direct backward compatibility with GSM. Benson and Thomas [18], Jugl and Pampel [19] and Lugara et al [20] discuss the limitations of certain handover algorithms and present simulation results of these algorithms.

The majority of consumers did not see the advantages of 3G over more mature technologies such as GPRS. This led to a very slow take up in 3G phones. Three, the first company to launch 3G in the UK had only 210,000 customers by the end of their first year in March 2004, they had expected one million [21]. However, the market for 3G telephones is expanding, all but one of the companies able to provide 3G services was expected to launch 3G networks by December 2004 [22]. Three have attempted to attract customers by offering tariffs that are competitive with the 2G network operators' free minutes and free short message service (SMS) bundles. This has been backed with free trials of Three's 3G services such as football highlights and video conferencing. This seems to have been successful with Three reaching a total of 1·2 million customers in the UK by August 2004 [23].

# 5.1. FPGAs

The size and power consumption of FPGAs mean it is difficult for them to be used in mobile phones in the imminent future. However, given their reconfigurability they are ideal for use in mobile base stations or for hardware prototyping. The reconfigurable nature

of FPGAs is particularly important given the changing nature of 3G mobile standards. Both UMTS and cdma2000 standards changed a number of times between their inception and the final standard being set. This offers manufacturers of FPGAs a great advantage over the manufacturers of Application Specific Integrated Circuits (ASICs). An FPGA manufacturer can offer their 3G solutions to any customers and as the standards evolve so can the solutions offered by the FPGA manufacturers. However, when the final standard is released the ASIC manufacturer can offer a solution that is smaller, faster and consumes less power. Time to market is a very important part of any product development, the reconfigurability of FPGAs means that their solutions can always beat ASICs to the target market. As FPGAs are "off the shelf" parts they are also cheaper than ASICs for low volume production.

Initially FPGAs were used as 'glue logic' in mobile base stations, so called because it connected two or more complex systems. However, as the processing power of FPGAs has increased they have been used more extensively in base stations. Many base stations use a combination of ASICs, Digital Signal Processors (DSPs) and FPGAs to implement their desired system. ASICs offer the designer high speed, low power and small area, but are very costly to design and offer little freedom in terms of reconfiguration. DSPs and FPGAs both offer reconfigurability, while DSPs may be smaller and cheaper per unit than FPGAs they cannot offer the same processing power. This has led to FPGAs replacing both ASICs and DSPs in many base stations. FPGAs are ideal for use in components such as rake receivers and Turbo decoders as they allow multiple channels to be processed in parallel. This leads to FPGAs being less expensive per channel than DSPs [24]. Reconfigurability is not the unique selling point of FPGAs, as DSPs can also be reconfigured. The unique selling point of FPGAs is offering a chip that is reconfigurable and can offer the user a processing speed that can come relatively close to that of an ASIC.

As FPGA technology evolves they will eventually become small, low power devices relative to the ASICs of today. Obviously ASIC technology will also evolve and become smaller, faster and consume less power than future FPGAs. However, they cannot offer the reconfigurability and time to market advantages that future FPGAs will offer. Just as at the moment a base station manufacturer can reconfigure an FPGA remotely by transmitting a bit stream, in the future network operators will be able to reconfigure FPGAs on mobile telephones remotely. This is a key aim of software defined radio (SDR) [25]. The

reconfigurable nature of FPGAs may well allow them to eat into the ASICs share of the handset and base station market when SDR becomes common across all networks. The subject of SDR is discussed in more detail in Chapter 6.4.

# 5.2. Contribution

All work carried out by the RE has been of significant commercial relevance to Xilinx. The most significant piece of work carried out was undoubtedly the System Generator BERT. This was used both as a research tool and as a marketing tool. After creating their Turbo codec's the main problem facing Xilinx was functional verification and generating results to present to customers for marketing purposes. Initially the codec was functionally verified by comparing the output of the VHDL simulations with a C++ model of the codec. Any marketing or research data was also generated with the C++ model. The problem with this is that it can take weeks or even months to generate accurate plots. Using real hardware to test the system was the only real viable solution. The System Generator BERT was implemented in both a Nallatech XtremeDSP Kit [12] and an Annapolis WildcardII [13] PCMCIA card. Both of these contained Xilinx Virtex II 3000 chips [26]. Using the System Generator BERT meant that requests for plots could be taken from customers, generated and passed to the customer rapidly. In some cases the System Generator BERT could be given to the customer so that they could test the Turbo codec core for themselves. Another important aspect of the System Generator BERT is that it can be used in demonstrations and in conference presentations, an accurate BER plot could be generated in a matter of seconds. As the system was automated using various scripts it also meant that the user could set up a number of simulations and then leave the BERT running continuously. The BERT was designed to be extremely user friendly: to start a test the user needed only to be familiar with very basic Matlab skills, such as how to run a script.

The behavioural models designed by the RE were to be used by Xilinx customers who purchased the Xilinx/Frontier Turbo codec and therefore had great commercial relevance to Xilinx. The main purpose of the behavioural model was to allow the user to simulate the Turbo codec. As well as producing the same results as the structural design it also had to offer a significant simulation speed-up over the structural design and be easy to use. The behavioural model could also be used to verify the structural VHDL design.

The RE also designed a recursive systematic convolutional (RSC) encoder that conformed to the cdma2000 standard for Xilinx. Again, it could be used by customers in their cdma2000 codec.

The numerous reports created by the RE also had an impact on the commercial output from Xilinx. Two particular reports of significance were "Investigation of Turbo Decoder Hardware Architectures", Appendix D {vol. 2/pp. 26-40}, and "Calculating Input Values for Turbo Decoders"; Appendix F {vol. 2/pp. 51-65}. The latter proposed a novel value that optimised the performance of the Xilinx Turbo decoder. The former was used to determine which architecture should be used to implement the cdma2000 Turbo decoder.

# 6. Technical Background

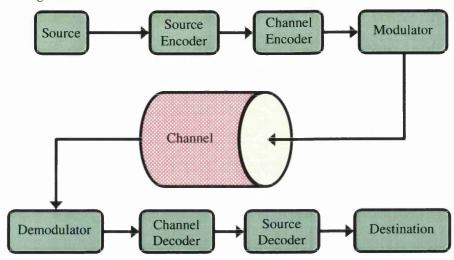

In 1948 Claude Shannon published his channel coding theorem [27], this theorem showed that data could be transmitted in a noisy channel with little or no error, provided that the data rate does not exceed the channel capacity. The publication of this paper led to a number of different theorems, and therefore channel coding techniques, on how to achieve this goal. Common between all techniques is the inclusion of a channel encoder and channel decoder to the communications system. A simple communications system is shown in Figure 3.

Figure 3: Overview of a simple communications system

The encoder and decoder implemented can perform simple error detection, where the system simply realises that one or more bits received is in error and take action such as requesting that the data in error be re-transmitted, or a more complex system called forward error correction (FEC). FEC systems both detect and correct errors, this enhancement is paid for by the complexity of the FEC decoder. Two coding techniques are used to implement FEC systems, block codes and convolutional codes. The major distinction between the two is that the output from a block encoder is completely reliant on its current input alone. The output from a convolutional code is reliant on the current input plus the previous m inputs, where m is the number of memory elements in the convolutional encoder. The number of memory elements in a convolutional encoder is known as the constraint length. Block encoders accept k-bits at its input and produce n parity bits from this input. In total, n+k bits are transmitted. Of the bits transmitted, n is redundant as they contain no real information. Redundancy can be measured in terms of code rate, R. For a

block code redundancy can be measured using (1). Code rate is inversely proportional to the number of parity bits generated. Hence, as redundancy increases the code rate decreases and less useful information is transmitted. The advantage of increasing redundancy is that the error correcting power of the code is increased.

$$R = \frac{k}{n+k} \tag{1}$$

The code rate of a convolutional encoder can be calculated using (2), where k is the number of bits into the encoder and n is the number of bits out.

$$R = \frac{k}{n} \tag{2}$$

As Turbo codes are a convolutional FEC technique this portfolio thesis shall look at this type of code in more depth. The reader is referred to more comprehensive publications on the subject of block codes [28, 29] for more information on this subject.

# 6.1. Convolutional Codes

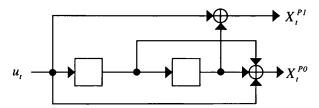

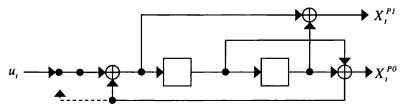

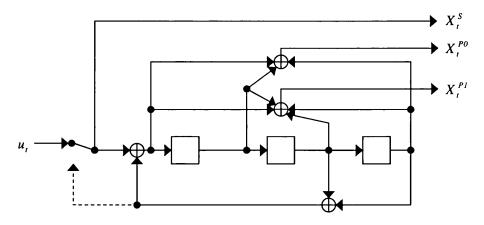

An example of a convolutional encoder is shown in Figure 4. The component encoders in Turbo encoders are recursive systematic convolutional (RSC) encoders. The encoder shown in Figure 4 is both non-recursive and non-systematic. The differences between the two types of convolutional encoders will be highlighted in this section. In Figure 4 the input,  $u_t$ , is passed through memory elements and modulo-2 adders to generate parity streams,  $X_t^{PO}$  and  $X_t^{PI}$ . Using (2) it can be shown that the code rate for this encoder is  $\frac{1}{2}$ .

Figure 4: Convolutional encoder

A convolutional encoder can be represented using a polynomial. The polynomial that represents  $X_t^{P0}$  is shown in (3); the polynomial that represents  $X_t^{P1}$  is shown in (4)

$$g_1(D) = 1 + D + D^2$$

(3)

$$\mathbf{g}_{2}(D) = I + D^{2} \tag{4}$$

Any non-systematic, non-recursive convolutional encoder can be converted to a RSC convolutional encoder using the rule shown in (5).

$$G(D) = I_1 \frac{g_2(D)}{g_1(D)}$$

(5)

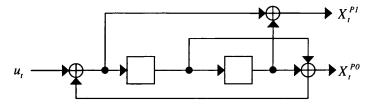

Figure 5 shows the equivalent RSC encoder created using (5) from (3) and (4).

Figure 5: RSC encoder

For Turbo codes the main advantage of using RSC instead of non-RSC encoders is that when RSC encoders are concatenated in parallel they produce relatively more high weight code words, leading to a better BER performance [30]. Berrou et al [31] and Benedetto et al [32] both show that the BER performance of an RSC encoder is better than the BER performance of the corresponding non-RSC encoder.

To decode a code word it is advantageous for the decoder to know the starting state of the encoder that produced the code word. This is done by returning the encoder to the all zero state after a packet has been encoded. This is relatively easy for the non-RSC encoder as all that is required is to input a sequence of m zeros, where m is the number of memory elements. For the RSC encoder a process known as trellis termination [33] must be used to return the encoder to the all zero state. Figure 6 shows the process of trellis termination. When a block has been encoded the data input,  $u_t$ , to the first XOR gate is replaced by the feedback input to the first XOR gate, thereby always producing an input of zero. The outputs of the encoder when in the trellis termination state are known as tail bits.

Figure 6: RSC encoder with trellis termination

#### 6.2. Turbo Codes

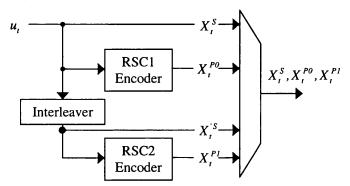

Introduced in 1993 Turbo codes [31] are a relatively recent innovation in channel coding research. They have already been included in numerous international standards, including deep space telemetry [34], digital video broadcasting (DVB) [8], UMTS [2] and cdma2000 [5]. Their popularity has grown due to their BER performance at low signal to noise ratios, the initial paper [31] came within 0.7dB of the Shannon limit. The unprecedented performance of Turbo codes can be attributed to three main factors: the use of parallel concatenated convolutional encoders; the use of an interleaver between each component encoder and the use of iterative decoding. A top-level view of a Turbo encoder is shown in Figure 7. The systematic and parity outputs can be punctured before transmission. Puncturing is a process where certain encoder outputs are deleted so that the code rate is increased, hence increasing the information rate. When an encoder output is punctured it is replaced with an all zero codeword at the decoder input. Using puncturing will usually result in a degraded BER performance, as will be shown in Chapter 7. The systematic output from RSC2, X's, is always punctured, in this case the BER performance is not compromised as  $X_i^{'s}$  can be reconstructed using an interleaver and the systematic data from RSC1,  $X_{i}^{S}$ . In Figure 7,  $X_{i}^{P0}$  represents parity data output by RSC1 and  $X_{i}^{P1}$  represents data output by RSC2.

Figure 7: Top-level view of a Turbo encoder

A Turbo encoder is created from three components, two recursive systematic convolutional encoders (RSCs), discussed in Section 6.2.1, and an interleaver, discussed in Section 6.2.2. Each RSC is known as a component encoder.

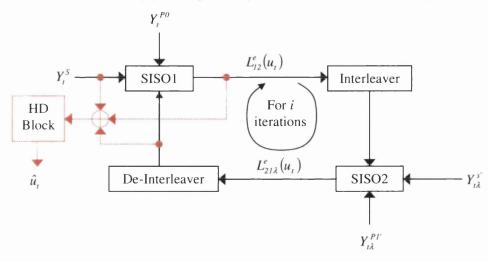

A Turbo decoder is created using four components, two soft-in soft-out decoders, an interleaver and a de-interleaver. The top-level of a Turbo decoder is shown in Figure 8.

For i iterations each SISO shares its output data with the preceding decoder. Data output from the SISO decoder,  $L_{ab}^{e}(u_{t})$ , is the SISO estimate of the original data input to the corresponding Turbo encoder and is known as extrinsic data. As (7) will show, the systematic input to the decoder,  $Y_t^s$ , is contained in the natural output of the SISO decoder,  $L(u_k)$ . Therefore, in a real hardware implementation it is unlikely that only  $L_{ab}^e(u_t)$  will be output by the SISO decoder, the actual value output will be  $L^{e}_{ab}(u_{\iota}) + Y^{s}_{\iota}$  . However, the SISO in Figure 8 shows only  $L_{ab}^{e}(u_{\tau})$  being output for clarity. In Figure 8, a  $\lambda$  subscript indicates that the associated variable is in interleaved form, relative to the original input data sequence.  $Y_i^{P0}$  represents the noisy version of the data output by RSC1 in Figure 7,  $Y_{i\lambda}^{PI'}$  represents the noisy version of the data output by RSC2, After i iterations, the components shown as dashed lines are initialized. The hard decision (HD) block is a basic thresholder that compares the summed input to 0. If the input is greater than 0 the decoder estimate,  $\hat{u}_k$ , is a binary 1. If the summed input is less than 0 the decoder is estimate is a binary 0. If the summed input is exactly 0 there is the same probability that the output should be a 0 or a 1. In this case the system designer must decide what the output should be. This could involve an additional algorithm, i.e. alternating the output for a 0 input between 0 and 1 or simply making the output always be 1 or 0 when a 0 input is received.

Figure 8: Top-level view of a Turbo decoder

Sharing of information between each SISO decoder is a major contribution to the performance of Turbo codes. The Turbo decoder and its components are discussed more comprehensively in Section 6.2.3.

#### 6.2.1. Turbo Encoder

The input to Turbo encoder comes from a data set of size N, known as the block size. Traditionally, the input to the encoder is 1 bit wide. However, systems such as the DVB Turbo encoder accept multiple bit inputs. As Figure 7 shows the systematic output from RSC 2 is not transmitted. This is achieved by puncturing the Turbo encoder output. Puncturing the output of a Turbo encoder involves deleting certain bits according to a puncturing pattern.

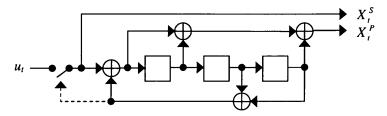

The component RSC encoder for the UMTS standard is shown in Figure 9.

Figure 9: UMTS component encoder

As each UMTS RSC encoder outputs only one parity stream the UMTS Turbo encoder has a standard code rate of  $\frac{1}{3}$ .

A cdma2000 component RSC encoder is shown in Figure 10.

Figure 10: cdma2000 component encoder

The cdma2000 RSC encoder has two parity stream outputs and can therefore have a code rate of  $\frac{1}{2}$ ,  $\frac{1}{3}$ ,  $\frac{1}{4}$  or  $\frac{1}{5}$ . The puncturing pattern of the cdma2000 standard is shown in Table 3.

Table 3: cdma2000 puncturing patterns for data

|                     | Code Rate |               |               |     |

|---------------------|-----------|---------------|---------------|-----|

| Output              | 1/2       | $\frac{1}{3}$ | $\frac{1}{4}$ | 1/5 |

| <i>X</i> , <i>s</i> | 11        | 11            | 11            | 11  |

| X, P0               | 10        | 11            | 11            | 11  |

| $X_{i}^{PI}$        | 00        | 00            | 10            | 11  |

| $X_{t}^{'s}$        | 00        | 00            | 00            | 00  |

| $X_{t}^{P0}$        | 01        | 11            | 01            | 11  |

| $X_{t}^{'PI}$       | 00        | 00            | 11            | 11  |

In the puncturing table a 0 represents a bit that is deleted and a non-zero number shows how many times the symbol in question is transmitted. For example, if data is being transmitted at a code rate of  $\frac{1}{2}$  the output from the encoder will be  $X_t^S$ ,  $X_t^{PO}$ ,  $X_t^S$ ,  $X_t^{PO}$ . When the trellis termination is initialised the puncturing pattern is altered so that  $X_t^{S}$  is transmitted, certain bits are repeated so that the code rate during trellis termination matches the code rate requested by the user. The puncturing pattern for trellis termination is shown in Table 4.

Table 4: cdma2000 puncturing patterns for trellis termination

|              | Code Rate |               |         |               |

|--------------|-----------|---------------|---------|---------------|

| Output       | 1/2       | $\frac{1}{3}$ | 1/4     | <u>1</u><br>5 |

| $X_{i}^{s}$  | 111 000   | 222 000       | 222 000 | 333 000       |

| X,PO         | 111 000   | 111 000       | 111 000 | 111 000       |

| $X_t^{Pl}$   | 000 000   | 000 000       | 111 000 | 111 000       |

| $X_{t}^{'s}$ | 000 111   | 000 222       | 000 222 | 000 333       |

| X, P0        | 000 111   | 000 111       | 000 111 | 000 111       |

| $X_{t}^{PI}$ | 000 000   | 000 000       | 000 111 | 000 111       |

The DVB component RSC encoder is fundamentally different from the UMTS and cdma2000 RSC component encoders as it accepts two binary inputs for each time period, t,

highlighted in Figure 11. Appendix E {vol. 2/pp. 41-50}, gives an in-depth overview on the subject of duo-binary Turbo codes.

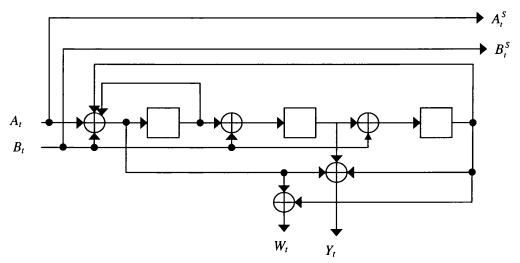

Figure 11: DVB component encoder

The DVB standard Turbo encoder can output data in any one of seven code rates. These code rates are shown in Table 5.

Code Rate <u>6</u> Output <u>2</u>  $\frac{1}{2}$ <u>4</u> 5  $Y_{t}$ 1 100 1000 11 1 10 100000  $W_{\iota}$ 0 00 000 0000 000000 1 10

Table 5: DVB standard puncturing patterns

# 6.2.2. Interleaver

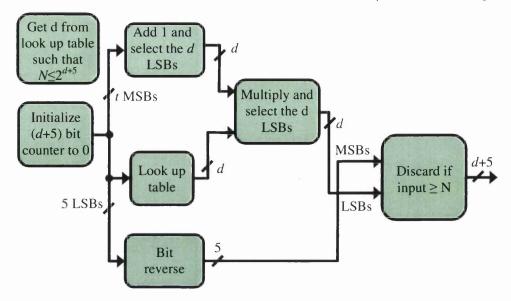

The interleaver improves the performance of the Turbo codec as it reduces the correlation between the data entering RSC1 and the data entering RSC2. By interleaving the data entering RSC2 it also protects the encoded data from burst errors. The input data to an interleaver is assigned an address. This address is then changed using a specific algorithm. A block diagram of the address generator for the cdma2000 interleaver is shown in Figure 12.

Figure 12: cdma2000 standard interleaver

If the address generated is greater than the block size of the current input data set then it is discarded. The components in the cdma2000 interleaver are easily implementable in hardware as they contain common mathematical operations such as counters, multipliers and bit reversals. The UMTS standard interleaver [2] is more mathematically complex and could be considered more difficult to implement in hardware.

### 6.2.3. Turbo Decoder

The key component of the Turbo decoder is the soft-in soft-out (SISO) decoder. SISO decoders, as their name suggests, accept soft value inputs and give soft value outputs. Soft values are *j* bits wide; the *j* bits represent a fractional number, an example of a decoder that accepts soft inputs is the Viterbi decoder [35]. One disadvantage of the traditional Viterbi decoder is that it only outputs single bits. By using soft inputs and soft outputs the BER performance of the decoder is improved. The main algorithms used to implement SISO decoders are the soft output Viterbi algorithm (SOVA) [36] and the Maximum a Posteriori (MAP) [37]. Using the MAP algorithm results in a better BER performance compared with the SOVA algorithm [38]. The MAP algorithm produces the most probable information bit per time instance for a given data set, the Viterbi algorithm produces a maximum likelihood sequence for a given data set. By performing a forward and backward traversal of the

trellis, the MAP algorithm produces two probabilities for the same time instance. This improves the BER performance of the Turbo decoder.

The Turbo decoders tested during the RE's industrial project were designed using variations of the MAP algorithm. Therefore, only this algorithm and its variants are described in this portfolio thesis. The variants described are the log-MAP algorithm, the Max-log-MAP algorithm and the Max Scale algorithm. All of these algorithms offer varying levels of performance and use varying levels of resources on the FPGA when implemented. Usually, as resources increase the BER performance of the implemented algorithm improves.

The soft inputs to the MAP algorithm are input in the form of a log-likelihood ratio,  $L(u_t)$ . A log-likelihood ratio shows the likelihood that a soft value represents a binary 1 or 0. Equation 6 shows how a log-likelihood ratio is calculated, where  $y_t$  represents the data received from the communications system demodulator.

$$L(u_t) = ln \left[ \frac{P(u_t = I \mid y_t)}{P(u_t = O \mid y_t)} \right]$$

$$(6)$$

If the result of (6) is positive then it is most likely that the result should be a binary 1, if the result is negative it is most likely that the result should be a binary 0. The probability that the result should be 0 or 1 increases as the magnitude of the result increases. If the result of (6) is exactly 0 then it is equally likely that the result is 0 or 1.

Ryan [39] shows that the output from a MAP decoder consists of three elements, shown in (7).

$$L(u_t) = L_{IN}^e(u_t) + L_{OUT}^e(u_t) + L_C Y_t^S$$

(7)

The variable  $L_C$  is dependent on the variance of the channel,  $L_{IN}^e(u_t)$  represents extrinsic data input to the SISO decoder, e.g.  $L_{I2}^e(u_t)$  into SISO2 in Figure 8.  $L_{OUT}^e(u_t)$  represents the extrinsic output from the SISO Decoder, e.g.  $L_{2I\lambda}^e(u_t)$  out of SISO2 in Figure 8.

The three main variables used to calculate the outputs from the MAP decoder are  $\alpha_t(s)$ , the alpha probability of state s at time t,  $\beta_t(s)$ , the beta probability of state s at time t, and  $\gamma_t(s', s)$ , the branch probability. The alpha probability is produced by performing a forward trace of the trellis, the beta probability is produced by a backward trace of the trellis.

The branch probability is the probability that the trellis moves from state s' at time t-1 to state s at time t. Ryan [39] shows that the branch metric can be calculated using (8).

$$\gamma_{t}(s',s) = exp\left[\frac{1}{2}X_{t}^{S}\left(L_{IN}^{e}\left(u_{t}\right) + L_{C}Y_{t}^{S}\right) + L_{C}\left(X_{t}^{P0}Y_{t}^{P0} + X_{t}^{P1}Y_{t}^{P1}\right)\right]$$

(8)

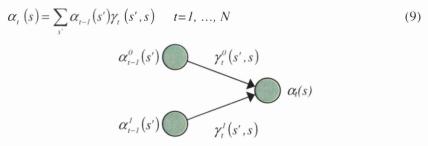

For a standard Turbo decoder each state in the trellis has two branches entering it. This means that each state is associated with two alpha probabilities and two beta probabilities, all four probabilities which have a branch probability associated with them. Equation (9) shows how  $\alpha_t(s)$  is calculated in a forward trace, this is shown graphically in Figure 13. The probability that the trellis is in state s at time t-l is equal to the probability that the previous state was s' and the trellis travelled along branch  $\gamma_t(s', s)$  to get to state s. As Figure 13 shows each branch is associated with either a 0 or a 1. If a branch is associated with a 0 then the state it comes from will have a negative  $\alpha$  probability, similarly a branch associated with a 1 will have come from a state with a positive alpha probability. Consequently (9) will yield either a positive or negative  $\alpha$  depending on the magnitude of the two previous states.

Figure 13: Calculating alpha probability

The beta probability is calculated in a similar fashion to the  $\alpha$  probability, except it is calculated when a backward trace is performed. Figure 14 shows graphically how the beta probability is calculated. The actual equation performed is shown in (10). The state, s, at time t-l has two probabilities associated with it. The probability that the state at time t was  $\beta_t^{i}(s')$  and the trellis travelled along branch  $\gamma_t^{i}(s',s)$  and the probability that the state at time t was  $\beta_t^{o}(s')$  and the trellis travelled along branch  $\gamma_t^{o}(s',s)$ . Whichever of the two probabilities is most likely will have the largest magnitude and therefore the output of (10) will be positive or negative depending on the result of (10).

$$\beta_{t-1}(s) = \sum_{s} \beta_{t}(s') \times \gamma_{t}(s', s)$$

$t = N, ..., 2$  (10)

Figure 14: Calculating beta probability

As Figure 8 shows the output of the decoder after i iterations is given by (11).

$$L(u_{t}) = L_{12}^{e}(u_{t}) + L_{21}^{e}(u_{t}) + L_{c}y_{t}^{s}(u_{t})$$

(11)

In terms of  $\alpha_k(s)$ ,  $\beta_k(s)$  and  $\gamma_k(s', s)$  the output from the decoder is calculated as shown in (12).

$$L(u_{t}) = \frac{\sum\limits_{\substack{(s',s)\\u_{t}=+l\\u_{t}=-l}} (\alpha_{t-l}(s') \times \gamma_{t}^{tXX}(s',s) \times \beta_{t}(s))}{\sum\limits_{\substack{(s',s)\\u_{t}=-l}} (\alpha_{t-l}(s') \times \gamma_{t}^{\rho XX}(s',s) \times \beta_{t}(s))}$$

$$(12)$$

The MAP algorithm gives exceptional BER results at relatively low  $\frac{E_b}{N_0}$ , however, the MAP algorithm is extremely difficult to implement in hardware as it contains mathematical operations such as logarithms and divisions which are costly in terms of hardware resources. A modification of the MAP algorithm is the log-MAP algorithm [40]. As the name suggests the log-MAP algorithm is an implementation of the MAP algorithm in the logarithm domain. Taking the logarithm of (8), (9) and (10) yields (13), (14) and (15).

$$A_{\epsilon}(s) = \ln(\alpha_{\epsilon}(s)) \tag{13}$$

$$B_{t}(s) = \ln(\beta_{t}(s)) \tag{14}$$

$$G_{s}(s',s) = ln(\gamma_{s}(s',s))$$

$$G_{t}(s',s) = \left(\frac{1}{2}X_{t}^{S}\left(L_{IN}^{e}(u_{t}) + L_{c}y_{t}^{S}\right)\right) + \left(\frac{1}{2}L_{c}\left(y_{t}^{P0}X_{t}^{P0} + y_{t}^{P1}X_{t}^{P1}\right)\right)$$

(15)

The Jacobian logarithm, (16), can be used to obtain a formula for both (13) and (14) that can be easily implemented in hardware, shown in (17) and (18).

$$MAX * (A_t^0, A_t^1) = ln(e^{A_t^0} + e^{A_t^1})$$

$$MAX * \left(A_t^o, A_t^l\right) = MAX\left(A_t^o, A_t^l\right) + ln\left(I + e^{-|A_t^o - A_t^l|}\right)$$

(16)

$$A_{t}(s) = MAX_{s'} * (A_{t-1}(s') + G_{t}(s', s))$$

$$t = 1, ..., N-1$$

(17)

$$B_{t-1}(s') = MAX * (B_t(s) + G_t(s', s)) t = N, ..., 2 (18)$$

Similarly the output from the decoder can also be calculated using the Jacobian logarithm, shown in (19).

$$L(u_{t}) = \underset{\substack{(s',s)\\u_{t}=1\\u_{t}=1}}{\text{MAX}} * (A_{t-1}(s') + G_{t}(s',s) + B_{t}(s))$$

$$- \underset{\substack{(s',s)\\u_{t}=-1\\u_{t}=-1}}{\text{MAX}} * (A_{t-1}(s') + G_{t}(s',s) + B_{t}(s))$$

(19)

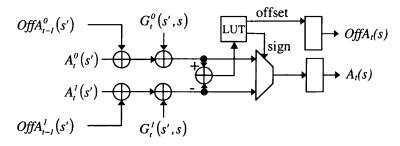

The Max\* computation involves adding both the alpha or beta metrics to the branch metric they are associated with, then comparing both of the summed metrics. The largest is selected and the offset is added from a look up table. This output is then passed to the next state in the trellis diagram. The add, compare, select, offset component is at the heart of all of the MAX\* computations, it is shown graphically in Figure 15 [41]. One ACSO unit is needed for every state in the trellis diagram.

Figure 15: Add, compare, select, offset unit

The log-MAP algorithm can be further simplified by excluding the offset,  $ln(I + e^{-|A_i^0 - A_i^1|})$ , in (16), resulting in an implementation called the Max-log-MAP algorithm. Chapter 7 will show that removing the offset results in a relatively poor BER performance. A compromise between the log-MAP and Max-log-MAP algorithm is the Max Scale algorithm. The Max Scale algorithm has a similar complexity to the Max-log-MAP algorithm but achieves a coding gain of between 0-2dB and 0-4dB compared with the Max-log-MAP algorithm [42]. The coding gain is achieved by multiplying the SISO decoder output by a scaling factor, sf, shown in (20).

$$L_{OUT}^{e}(u_{t}) = \left[L(u_{t}) - \left(L_{IN}^{e}(u_{t}) + L_{c}y_{t}^{S}\right)\right] \times sf$$

$$(20)$$

#### **6.3.** Field Programmable Gate Arrays

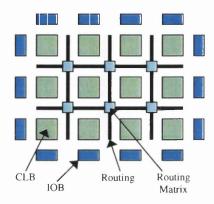

Field Programmable Gate Arrays (FPGAs) are off the shelf hardware parts that offer a compromise between the speed of ASICs and the reconfigurability of DSPs. There are three main basic elements in FPGAs, these are: configurable logic blocks (CLBs); input output blocks (IOBs) and routing. The basic structure of an FPGA is shown in Figure 16.

In the Xilinx Virtex-II FPGA each CLB contains 4 slices. Each slice contains two 4-input look-up tables (LUTs), two registers and some combinatorial logic, used to implement fast carry chains, and two multiplexers. The resources used by any given design are measured in slices.

Figure 16: FPGA basic structure

The routing matrix is programmable, allowing the user to change routing for each new design downloaded to the FPGA. As has been stated previously, FPGAs offer a speed advantage over DSPs and a reconfigurability advantage over ASICs. However, both DSPs and ASICs are smaller and consume less power than FPGAs. To compete with DSPs FPGAs now contain elements such as memory and embedded multipliers. The Xilinx Virtex-II FPGA [26] has up to 168 18bit x 18bit embedded multipliers (EMults), along with 168 18Kbit block RAMs (BRAMs). The Xilinx Virtex-II Pro [43] extended the programmability of Xilinx FPGAs by including up to 2 embedded PowerPC processors. Adding these extra components allows FPGAs to outperform DSPs in applications that require intensive computing.

It is well known that the development time of FPGA design is significantly shorter than ASICs. However, DSPs have a shorter design development time than FPGAs. This is

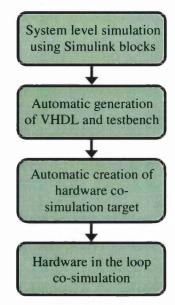

mainly due to the proliferation of tools available to DSP designers and the fact that DSPs can be programmed using high level languages. To combat this Xilinx introduced their System Generator tool. System Generator is a Matlab Simulink add-on that allows FPGAs to be designed using a simple schematic capture environment using a flow that DSP designers are familiar with. The System Generator design flow is shown in Figure 17 [44]. System Generator includes various library components that can be used for DSP design. These vary in complexity from simple logic gates to a Viterbi decoder. Library components are designed in low level VHDL so are highly optimised for implementation in Xilinx FPGAs.

Figure 17: System Generator DSP design flow

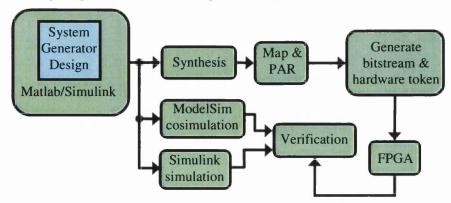

The System Generator design flow can also be presented in a fashion that is familiar to hardware design engineers, as shown in Figure 18 [15].

Figure 18: System Generator hardware design flow

This shows the flexibility of System Generator. While System Generator may not allow hardware engineers to fine tune designs in the same way a hardware description language (HDL) does, it does allow hardware and systems engineers to work together on the same design using a common platform, improving productivity.

## 6.4. Third Generation Mobile Technology

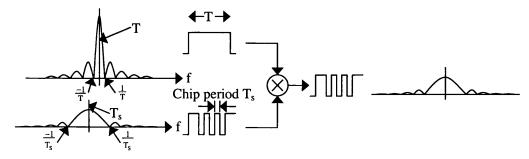

The main 3G standards are based around spread spectrum technology [45, 46, 47]. Spread spectrum uses spreading sequences such as Walsh codes and Gold codes to distinguish between different users. This is required as all users within a cell share both time and frequency. Figure 19 shows an example of the spreading process. Each user in a cell is assigned a specific chip sequence. The base station controlling a cell stores all chip sequences assigned to each user and uses a correlator to determine which user is transmitting to the base station. The chip rate for the cdma2000 standard is 3.6864 Mchips/sec<sup>1</sup>, UMTS has a chip rate of 3.84 Mchips/sec. One other difference between the two standards is that the cdma2000 standard is synchronised with a GPS clock while the UMTS standard is completely asynchronous. This makes the UMTS receiver more complex, however the cdma2000 receiver is dependent on government satellites for the required GPS information. The cdma2000 standard is to be implemented in the United States, the UMTS standard will be used in Europe. One advantage of deploying a spread spectrum system in the US is that previous 2G mobile standards used spread spectrum systems. Whereas in Europe, the previous 2G system uses the GSM standard. Meaning, handover in the US cdma2000 system is simpler than in the European UMTS system. This is because previous US standards also used spread spectrum systems such as cdmaOne, whereas previous European systems have been based on the non spread spectrum GSM standard.

Figure 19: Spread spectrum signal

<sup>&</sup>lt;sup>1</sup> Actual chip period used is usually 1.2288Mchip/sec, to match IS-95 standard.

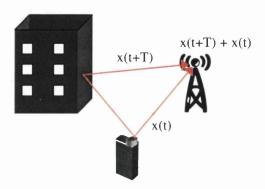

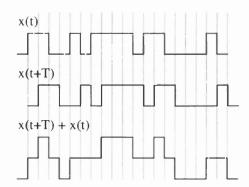

The multipath delays inherent to mobile channels can cause problems in spread spectrum systems as they reduce orthogonality. Figure 20 shows a multipath channel between a user and a base station, Figure 21 shows the affect this has on the signal received at the base station.

Figure 20: Multipath channel

Figure 21: Signal received at base station

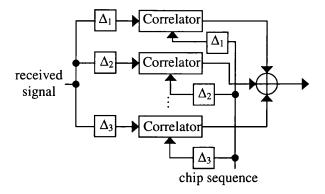

A simple solution could be to use the strongest signal received from each user. However, to obtain the best possible signal the base station must extract all signals received from each user. This is achieved in spread spectrum systems by using a rake receiver [48] at the base station. A pilot sequence is used to determine the characteristics of the channel, the pilot sequence is known by both the mobile and the base station. This pilot sequence can be used by the rake receiver to determine the different components of a user's transmitted signal. A rake receiver is shown in Figure 22, where  $\Delta_x$  represents the delay between each received signal.

Figure 22: Rake receiver