Macdonald, David Andrew (2019) *Enhancement of hydrogen terminated diamond FET performance through integration of electron acceptor oxides.* PhD thesis.

https://theses.gla.ac.uk/41167/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Enhancement of hydrogen terminated diamond FET performance through integration of electron acceptor oxides

David Andrew Macdonald

B.Eng

Submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Engineering

University of Glasgow

# **Abstract**

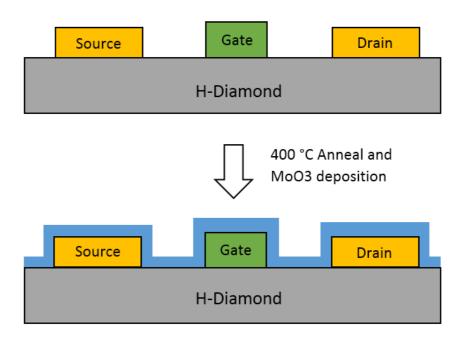

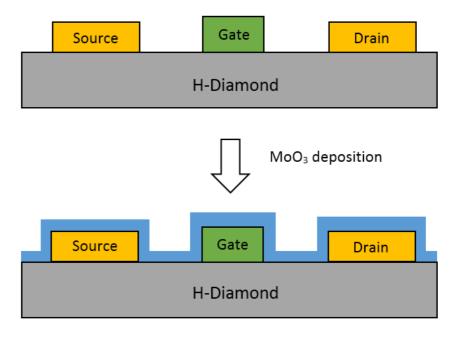

This work reports on the improvement to the performance of hydrogen terminated diamond field effect transistors (FETs) by replacing surface adsorbed atmospheric species with transition metal oxides MoO<sub>3</sub> and V<sub>2</sub>O<sub>5</sub>, and the implementation of a pre-deposition vacuum anneal at 400°C which is required to maintain the stability of the doping within the devices.

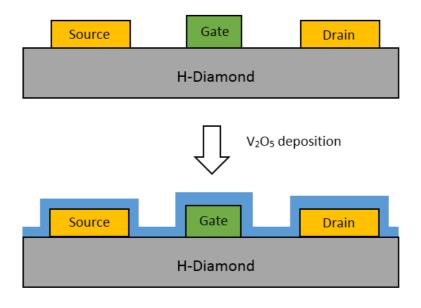

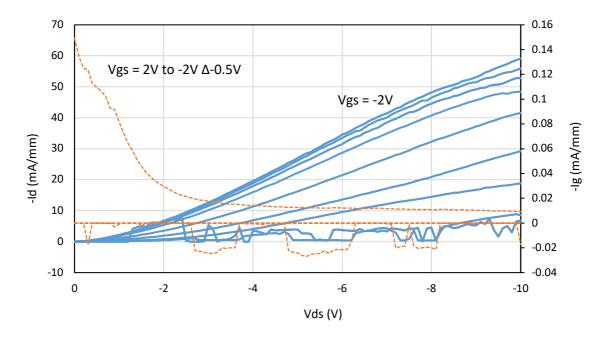

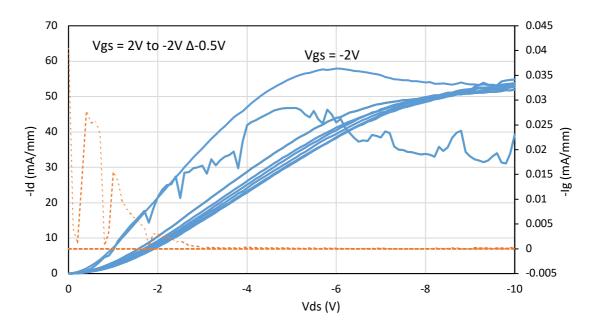

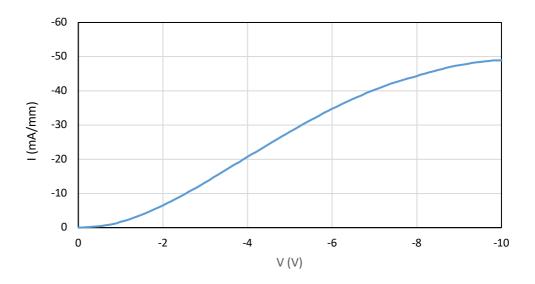

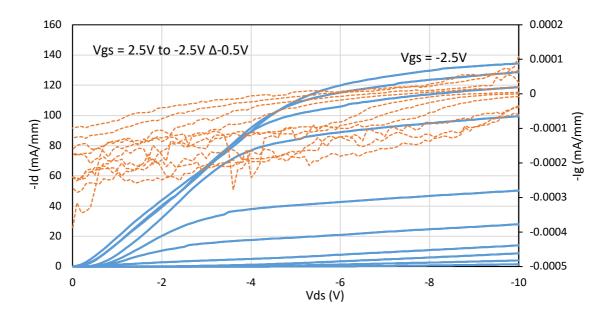

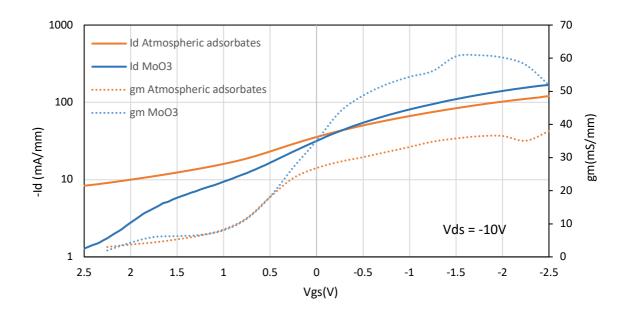

MESFET structures incorporating a metal/H-diamond gate contact were observed to be irreversibly damaged by exposure to the  $400^{\circ}$ C pre deposition vacuum annealing prior to deposition of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub>. Therefore preliminary investigation of devices including the MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub> without pre annealing was carried out. An increase in maximum drain current of up to 50% was observed when comparing output characteristics before and after deposition of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub> without the  $400^{\circ}$ C pre anneal.

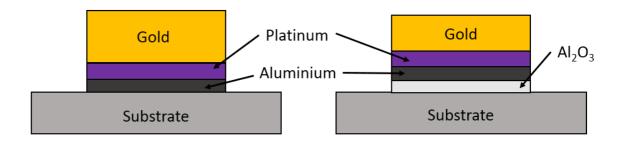

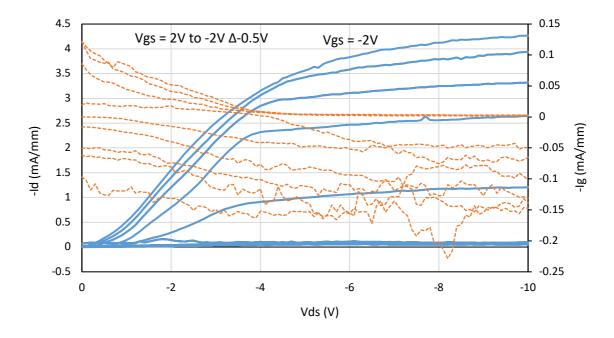

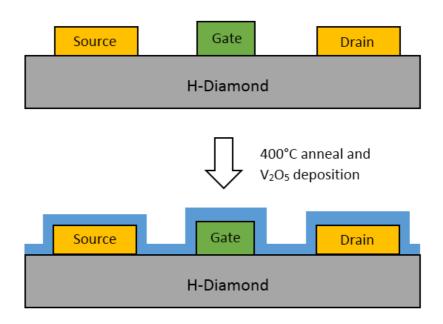

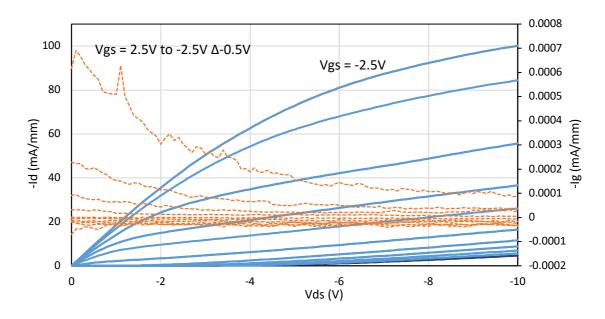

Following this, investigation of the inclusion of Al<sub>2</sub>O<sub>3</sub> into the FET structure as a gate dielectric was explored in order to increase the thermal robustness of the gate and allow inclusion of the pre deposition vacuum annealing at 400°C. It was shown that FETs fabricated using Al<sub>2</sub>O<sub>3</sub> as a gate dielectric maintained transistor operation after vacuum annealing at 400°C and deposition of 10nm of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub>. FETs were characterized after exposure to atmospheric adsorbates, and after deposition of 10nm of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub> and pre deposition 400°C vacuum anneal. FETs with Al<sub>2</sub>O<sub>3</sub> gate dielectric using V<sub>2</sub>O<sub>5</sub> and pre deposition annealing showed an increase in drain current of up to 276%. The V<sub>2</sub>O<sub>5</sub> FETs using Al<sub>2</sub>O<sub>3</sub> as a gate dielectric showed maximum drain currents of -376mA/mm, extrinsic transconductances of 97mS/mm, and on resistances as low as 17Ω.mm. These are important parameters for assessing the performance of power FETs.

# **Acknowledgements**

Firstly, my supervisor Dr. David Moran deserves my most sincere thanks for offering me this opportunity in the first place. He has been an excellent mentor, providing me with endless encouragement to do my best work and pushed me when I needed it. Thank you for organising stimulating Friday afternoon meetings and the more than occasional beer to end the week.

To all the staff at the JWNC, thank you for maintaining and running the excellent facility, without which none of this work would be possible. A special thank you to Susan and Helen who have always answered all my questions and helped me with countless e-beam jobs.

Thank you to my colleagues Andy and Kevin, and more recently Joe, with whom I have shared too many cups of coffee and laughs over the years. I value your friendships, which have made this a much less lonely undertaking.

Thank you to all my friends, your constant banter has at times been a welcome distraction.

Thank you to my Mum and Sandy, who have always guided and supported me in everything I have endeavoured my whole life. In particular I would like to thank you for your support over the last 6 months, feeding and encouraging me, allowing me to finish this work. To my brother Richard, and sister Rachael, thank you for your constant jokes, which can always lighten my mood, even if I am the butt of them. Thank you to my Dad and Eilidh, for your support and treats to dinner. Last, but certainly not least, thank you to my girlfriend Tania, who is the most patient and caring soul I have ever met, I would not have made it this far without her constant reassurance.

# **Associated Publications**

#### Journal Entries

- D. A. Macdonald, K. G. Crawford, A. Tallaire, R. Issaoui, and D. A. J. Moran, "Performance enhancement of Al<sub>2</sub>O<sub>3</sub>/H-diamond MOSFETs utilizing vacuum annealing and V<sub>2</sub>O<sub>5</sub> as a surface electron acceptor," *IEEE Electron Device Letters*, pp. 1-1, 2018.

- K. G. Crawford, A. Tallaire, X. Li, D. A. Macdonald, D. Qi, D. A. J. Moran, (2018), The role of hydrogen plasma power on surface roughness and carrier transport in transfer-doped H-diamond, Diamond and Related Materials, Volume 84, , Pages 48-54,

#### Conferences

- D. A. Macdonald, K. G. Crawford, A. Tallaire, R. Issaoui, and D. A. J. Moran, (2018) Improvement of hydrogen terminated diamond FET performance by vacuum annealing and surface transfer doping oxide deposition, Surface and Bulk Defects in Diamond (SBDD) workshop 2018, Hasselt, Belgium 7-9 March. (Oral)

- D. A. Macdonald, A. Tallaire, C. Verona, E. Limiti, and D. A. J. Moran, (2015) Stability of operation of atmosphere-exposed, hydrogen-terminated diamond FETs under constant operation. MRS fall meeting: Materials Research Society, Boston MA, USA, 29 Nov 4 Dec 2015, (Poster)

# Contents

| 1. Introduction                                            | 1  |

|------------------------------------------------------------|----|

| 2. Background: Diamond as an electronic material           | 6  |

| 2.1. Diamond Structure                                     | 6  |

| 2.2 Synthetic Diamond growth                               | 9  |

| 2.3 Doping of Diamond                                      | 10 |

| 2.4 Surface transfer doping of diamond                     | 12 |

| 2.5 Carrier transport in a Semiconductor                   | 14 |

| 2.6 Field Effect Transistor operation and figures of merit |    |

| 2.7 Metal Semiconductor interfaces                         |    |

| 3. Literature review                                       | 30 |

| 3.1 Surface transfer doping                                | 30 |

| 3.2 – Surface transfer doping FETs state of the art        | 38 |

| 3.3 Boron Doped diamond FETs                               | 46 |

| 3.4 Chapter Summary                                        | 47 |

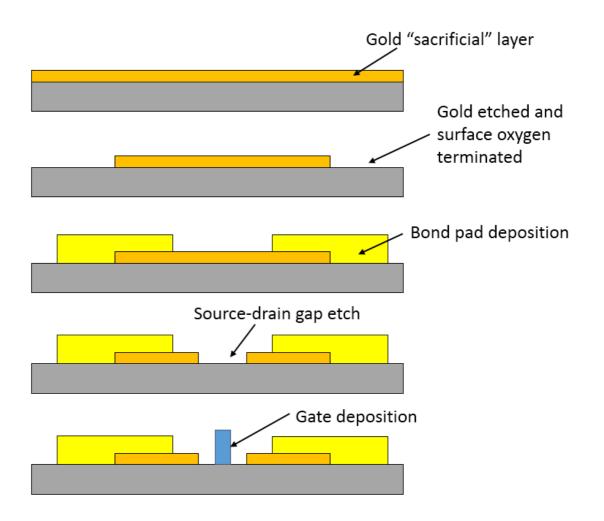

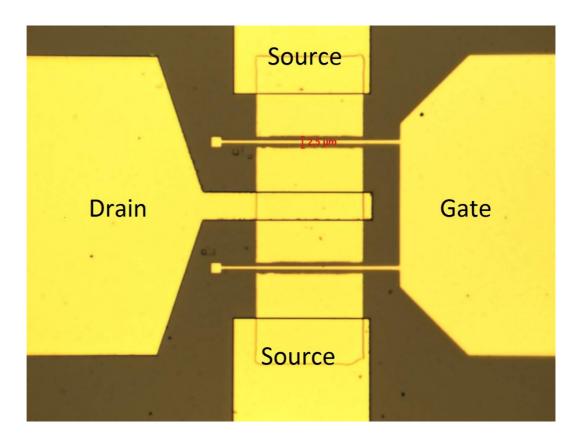

| 4. Fabrication and process flow                            | 53 |

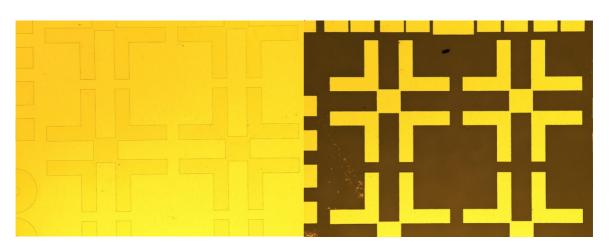

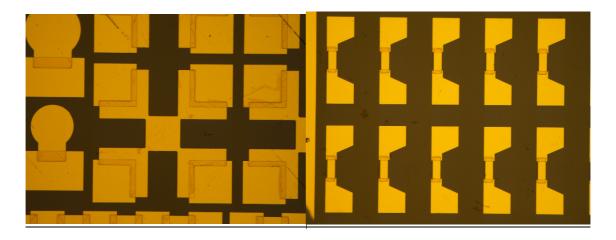

| 4.1 Substrate preparation                                  | 54 |

| 4.2 Hydrogen termination                                   | 54 |

| 4.3 Substrate cleaning                                     | 54 |

| 4.4 Resist spinning                                        | 55 |

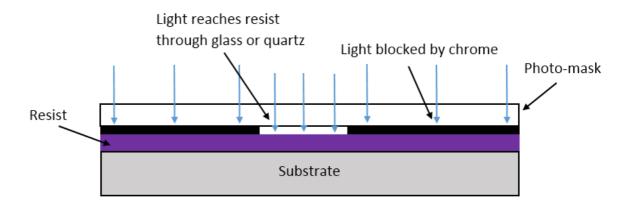

| 4.5 Photolithography exposure                              | 56 |

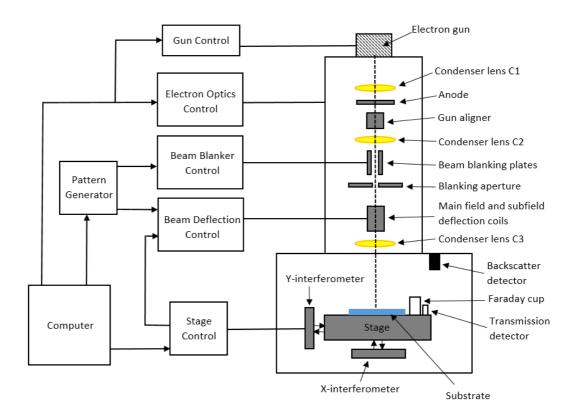

| 4.6 EBL exposure                                           | 56 |

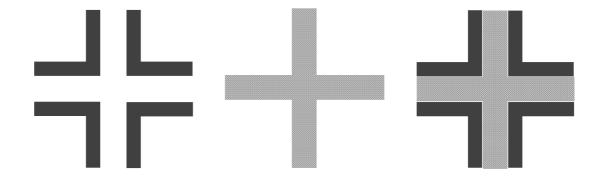

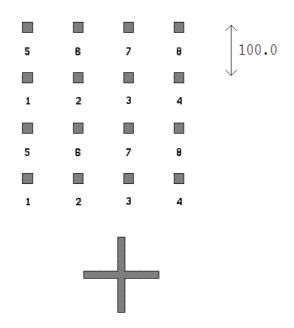

| 4.7 Alignment                                              | 58 |

| 4.8 Resist development                                     | 59 |

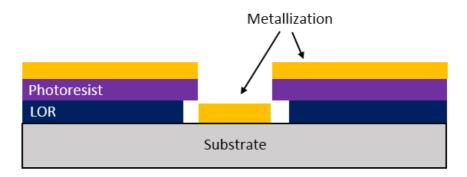

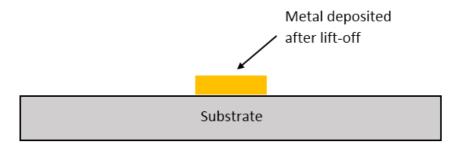

| 4.9 Lift-off metallization                                 | 60 |

| 4.10 Etching                                               | 61 |

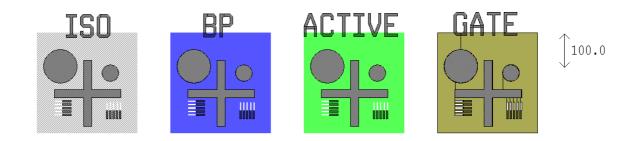

| 4.11 Pattern Generation                                    | 62 |

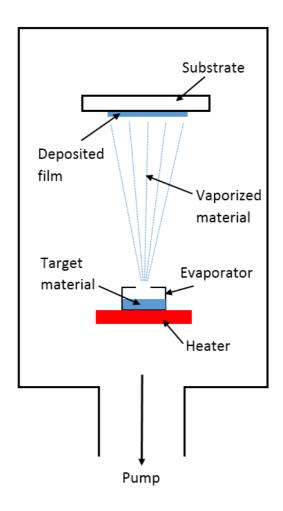

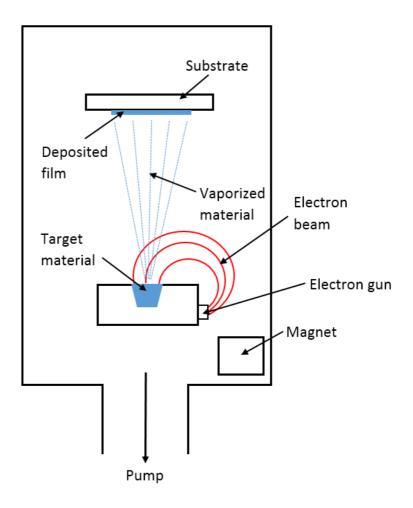

| 4.12 Physical Vapour Deposition                            | 62 |

| 4.13 Physical characterization                             | 65 |

| 4.14 Hydrogen terminated diamond FET Process Flow          | 67 |

| 4.14 Chapter Summary                                       | 77 |

| 5. Electrical characterization methods                     | 79 |

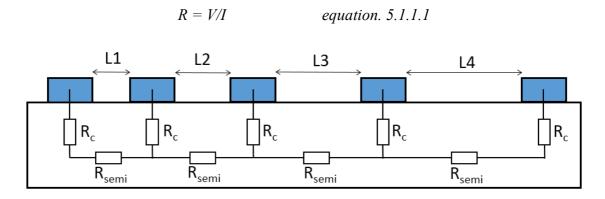

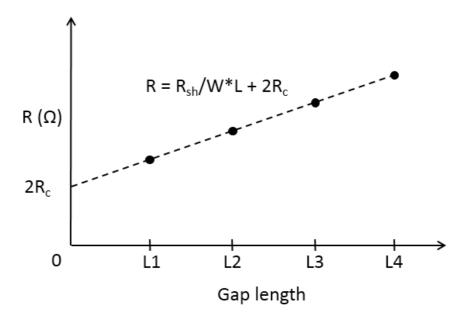

| 5.1 Material Characterization                              | 79 |

| 5.1.1 Transmission Line Measurement (TLM)                  | 79 |

| 5.1.2 Van Der Pauw measurements (VDP)                                                     | 80       |

|-------------------------------------------------------------------------------------------|----------|

| 5.2 Field Effect Transistor (FET) characterisation                                        | 84       |

| 5.2.1 Output Characteristics                                                              | 85       |

| 5.2.2 Transfer Characteristics                                                            | 88       |

| 5.3 Chapter Summary                                                                       | 90       |

| 6. Hydrogen terminated diamond MESFETs                                                    | 92       |

| 6.1 Hydrogen termination                                                                  | 92       |

| 6.2 - VDP and TLM structures with vacuum annealing and MoO3 deposition -                  | -        |

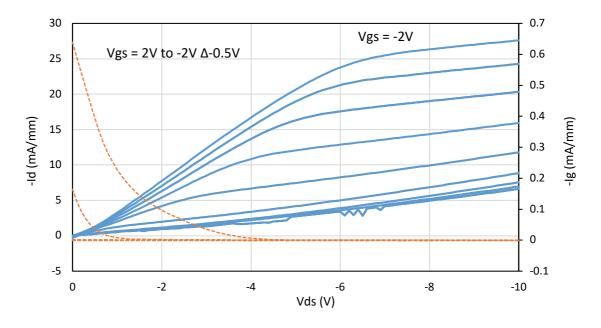

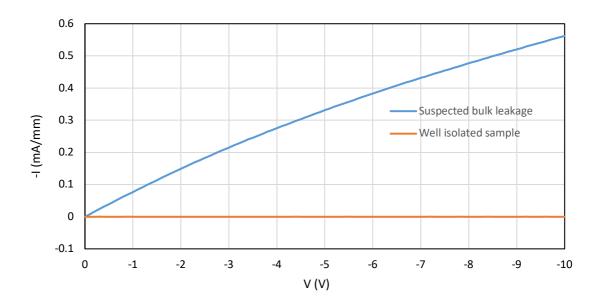

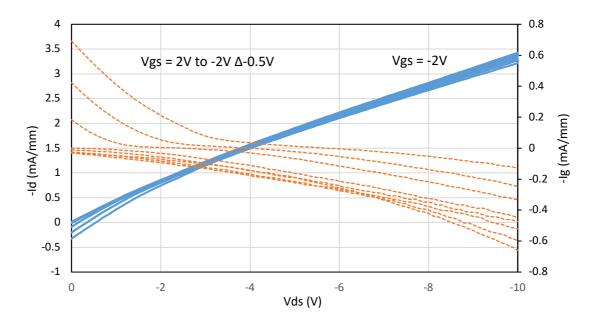

| 6.3 - MESFET with vacuum annealing and MoO <sub>3</sub> deposition – Sample B             | 97       |

| 6.4 MESFET with $V_2O_5$ , and vacuum annealing with $V_2O_5$ – Sample $C$                | 101      |

| 6.5 MESFETs with MoO <sub>3</sub> – Sample D                                              | 107      |

| 6.6 MESFET with V <sub>2</sub> O <sub>5</sub> – Sample E                                  | 118      |

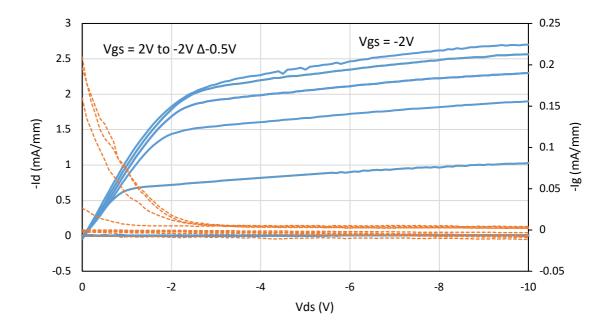

| 6.6.1 - DC Characteristics of Sample E                                                    |          |

| 6.6.2 - Repeated measurements on Sample E                                                 |          |

| 6.6.3 - Sweep Direction on Sample E                                                       |          |

| 6.6.4 - Off State Breakdown measurements on Sample E                                      |          |

| 6.5 - Chapter Summary                                                                     | 140      |

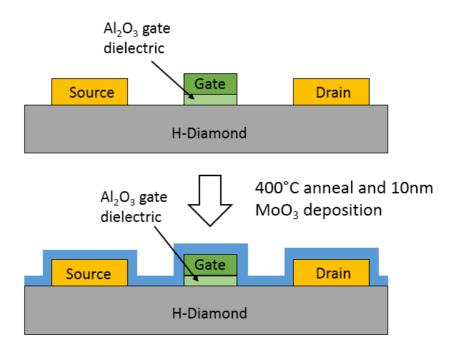

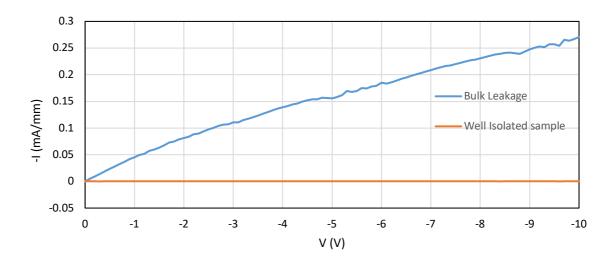

| 7. Hydrogen terminated diamond MOSFETs                                                    | 143      |

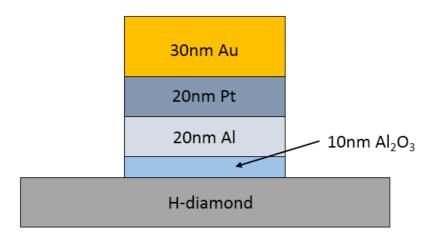

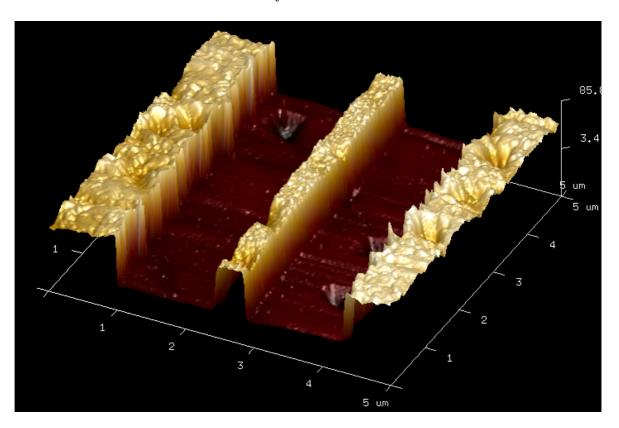

| 7.1 Al <sub>2</sub> O <sub>3</sub> deposition                                             | 143      |

| 7.2 $Al_2O_3$ MOSFET with 400°C vacuum annealing and 10nm MoO <sub>3</sub> deposition $F$ |          |

| 7.3 $Al_2O_3$ MOSFET with 400°C vacuum annealing and $V_2O_5$ deposition- Samp            | le G 156 |

| 7.3.1 DC Measurements of Sample G                                                         |          |

| 7.3.2 Repeated Measurement on Sample E                                                    |          |

| 7.3.3 Off-state breakdown measurements on Sample G                                        |          |

| 7.4 Conclusions                                                                           | 171      |

| 8 Conclusions and further work                                                            | 174      |

| 8.1 Conclusions                                                                           | 174      |

| 8.2 Further Work                                                                          | 175      |

| Annual dir. A Dunang aharta                                                               | 170      |

# 1. Introduction

The field effect transistor (FET) is one of the most important technological advances of the last century. The FET forms an electronic switch which can be turned on or off using just a small electronic voltage. Perhaps the best known implementation of FETs, and where they have had the greatest impact, is in logic circuits; every day we use microprocessors formed by cascading logic circuits in our phones and computers etc. Logic circuits operate at low voltages using small currents. However, there is also a need for switching higher powers at high frequencies as efficiently as possible for applications such as radar and satellite communications, FETs are suitable for this task too.

High power FETs, as their name would suggest, are used as high-power switches. Ideally when "on" they allow large currents to flow through the circuit with minimal electrical resistance; when "off" they block all current flow through a circuit and drop all voltage across the FET. In order to be as efficient as possible, high power FETs must consume as little power as possible. This means minimizing conduction loses when "on" and minimizing leakage current when "off". Banks of silicon based devices have previously been used for high power applications. However this is non-ideal as many devices must be used to allow high currents and block high voltages. This is both expensive and inefficient due to the poor thermal performance of silicon and the need for a large amount of die space. Thus there has been much interest in alternative materials which could surpass silicon in regards to current transport, high voltage breakdown and thermal management. The main competitors in this respect are the wide bandgap materials, GaN, SiC and diamond, as they have many desirable properties for high power operation.

|                             | Si   | CVD Diamond | GaN  | 4H-SiC |

|-----------------------------|------|-------------|------|--------|

| Bandgap (eV)                | 1.1  | 5.47        | 3.44 | 3.2    |

| Breakdown Field             | 0.3  | 10          | 5    | 3      |

| (MVcm <sup>-1</sup> )       |      |             |      |        |

| Electron Saturation         | 0.86 | 2           | 2.5  | 3      |

| Velocity $(x10^7 cms^{-1})$ |      |             |      |        |

| Hole Saturation             | 1    | 0.8         | n/a  | n/a    |

| Velocity $(x10^7 cms^{-1})$ |      |             |      |        |

| Electron Mobility           | 1450 | 4500        | 440  | 900    |

| $(cm^2V^{-1}s^{-1})$        |      |             |      |        |

| Hole Mobility               | 480  | 3800        | 200  | 120    |

| $(cm^2V^{-1}s^{-1})$        |      |             |      |        |

| Thermal Conductivity        | 1.5  | 24          | 1.3  | 5      |

| $(Wcm^{-1}K^{-1})$          |      |             |      |        |

| Johnson's FOM               | 1    | 8200        | 280  | 410    |

| Baliga's FOM                | 1    | 17200       | 910  | 290    |

Table 1.1 - Intrinsic properties of Diamond and its main competitors for high power performance GaN and SiC compared with Si, figures from [1.1].

Due to its large bandgap diamond has a very high theoretical breakdown voltage of >10MVcm<sup>-1</sup> [1.2]. High breakdown voltage means that diamond is suited for high power operations as it can be operated under strong electric fields before ionisation, avalanche or another breakdown mechanism occurs. Intrinsic diamond has very high intrinsic electron and hole mobility (4500cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 3800 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> respectively) [1.3] which contributes to current transfer in low fields. Diamond also has high electron and hole saturation velocities at 2x10<sup>7</sup>cms<sup>-1</sup> and 0.8x10<sup>7</sup>cms<sup>-1</sup> [1.4] respectively contributing to high current transfer in high field and high frequency performance. The saturation velocity can also be reached well before breakdown occurs. Diamond also has very high thermal conductivity at 24Wcm<sup>-1</sup>K<sup>-1</sup> [1.5] allowing for effective heat dissipation from high power operation and therefore low thermal losses. Diamond is radiation resistant due to its very large band gap of 5.5eV resulting in very high ionisation energy needed to excite electrons from the valence band into the conduction band. Its bandgap also contributes to its ability to operate at higher temperatures without excess thermal excitation of electrons into the conduction band.

Mechanical toughness is perhaps diamond's most well-known attribute. Its toughness is due to the short bond length of 1.54Å of carbon to carbon bonds and the diamond lattice.

As can be seen from the figures discussed and shown in *table 1.1* diamond excels in every metric for high power performance, theoretically outperforming both GaN and SiC as assessed by properties important for high power operation. High power and high frequency performance potential can be roughly represented by Johnson's Figure of Merit (JFOM). This is determined by the breakdown field and the saturation velocity of the material. Baliga's Figure of Merit (BFOM) describes the power loss at low frequency of a material. It presumes that all loss is due to the on resistance of a power FET and is determined by the dielectric constant, mobility and bandgap of a material [1.6].

Despite diamond's superior intrinsic properties, at present high quality diamond substrates are smaller area and more expensive to produce compared to GaN and SiC, which are more mature and have been demonstrated more extensively. GaN and SiC have seen successful high-power FETs make it to market. Diamond may therefore never be a direct replacement for GaN and SiC unless substantial progress in upscaling wafers is established. However diamond's intrinsic properties such as high thermal conductivity and radiation resistance may allow it to operate in extreme environments where GaN and SiC would see degradation of performance, and hence may form a more "niche" technology for military, space, aerospace, and oil and gas applications.

Although diamond grown using Chemical Vapor Deposition (CVD) has many properties which makes it an excellent candidate for the development of future high power electronic devices, natural diamond found in the earth's crust tends to have too many impurities and crystal defects to make it a good candidate for use in semiconductor devices as well as being prohibitively expensive.

Diamond, however is intrinsically an insulator. It is very challenging to substitutional dope due to the close spacing of the carbon atoms in the lattice resulting in few impurities being able to fit without distorting the lattice. It is further complicated by the high activation energies of potential dopants [1.7]. Substitutional doping of boron has been used to create conductive diamond with some success, although the high activation energy means that large concentrations of impurities must be incorporated resulting in low mobilities [1.8]. A technique known as "delta doping" has also been explored using boron in an effort to provide charge transfer layers with higher mobility [1.9]. A newer and more novel technique known as "surface transfer doping" has also been explored in diamond. Surface transfer doping relies on hydrogen termination of the diamond surface which results in a negative electron

affinity at the surface of the diamond. This allows electrons to leave the surface if a suitable "acceptor" material is in contact, the holes "left behind" form a 2 dimensional hole gas (2DHG) below the surface of the diamond [1.10]. So far surface transfer doping has been the most effective method for producing high power FETs on diamond; Achieving maximum breakdown voltages above 1500V [1.11] and -1.3A/mm maximum output current [1.12]. Therefore, the surface transfer doping technique and its application forms the focus of this thesis work.

The main body of this thesis focuses on overcoming the challenges of integrating the alternative surface electron acceptor materials on diamond such as molybdenum trioxide (MoO<sub>3</sub>) and vanadium pentoxide (V<sub>2</sub>O<sub>5</sub>) into the fabrication of hydrogen terminated diamond FETs with a view towards stable and high power device operation. The integration of MoO<sub>3</sub> and V<sub>2</sub>O<sub>5</sub> into H-diamond FETs is envisioned to improve important parameters for high power performance such as; maximum drain current, peak transconductance, and on-resistance. Aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) has been included in the gate stack in an effort to create a more thermally robust structure and to improve off-state breakdown characteristics.

The following chapter addresses the background of the diamond material system, surface transfer doping of hydrogen terminated diamond and the underlying semiconductor physics of device operation. Chapter 3 explores relevant literature on surface transfer doping of hydrogen terminated diamond and diamond FETs, detailing the development of the technology as well as the potential which has been shown for the technology thus far. Chapter 4 details the equipment and fabrication techniques used throughout the project in order to produce hydrogen terminated diamond FETs. Chapter 5 addresses the electrical characterization techniques used to assess material and FET performance. Chapters 6 details the initial efforts to include MoO<sub>3</sub> and V<sub>2</sub>O<sub>5</sub> into the H-diamond MESFET architecture. This chapter revealed that pre-annealing the diamond surface prior to the deposition of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub> resulted in degraded transistor performance. Chapter 7 details the inclusion of Al<sub>2</sub>O<sub>3</sub> as a gate dielectric into hydrogen terminated diamond FETs in order to produce a more thermally robust gate structure. The performance of the fabricated MOSFETs using atmospheric adsorbates to induce surface transfer doping and after pre deposition annealing and deposition of MoO<sub>3</sub> or V<sub>2</sub>O<sub>5</sub> is compared. Chapter 8 closes the thesis by discussing and summarizing what has been achieved through this research and details potential further work.

#### References

- [1.1] C. J. H. Wort and R. S. Balmer, "Diamond as an electronic material," *Materials Today*, vol. 11, pp. 22-28, 2008/01/01/ 2008.

- [1.2] K. Shenai, R. S. Scott, and B. J. Baliga, "Optimum semiconductors for high-power electronics," *IEEE Transactions on Electron Devices*, vol. 36, pp. 1811-1823, 1989.

- [1.3] J. Isberg, J. Hammersberg, E. Johansson, T. Wikström, D. J. Twitchen, A. J. Whitehead, *et al.*, "High carrier mobility in single-crystal plasma-deposited diamond," *Science*, vol. 297, p. 1670, 2002.

- [1.4] F. Nava, C. Canali, C. Jacoboni, L. Reggiani, and S. F. Kozlov, "Electron effective masses and lattice scattering in natural diamond," *Solid State Communications*, vol. 33, pp. 475-477, 1980/01/01/1980.

- [1.5] C. J. H. Wort, C. S. J. Pickles, A. C. Beale, C. G. Sweeney, M. R. McClymont, R. J. Saunders, *et al.*, "Recent advances in the quality of CVD diamond optical components," in *AeroSense* '99, 1999, p. 10.

- [1.6] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Letters*, vol. 10, pp. 455-457, 1989.

- [1.7] J. P. Goss, P. R. Briddon, R. Jones, and S. Sque, "Donor and acceptor states in diamond," *Diamond and Related Materials*, vol. 13, pp. 684-690, 2004/04/01/2004.

- [1.8] E. Yasu, N. Ohashi, T. Ando, J. Tanaka, M. Kamo, Y. Sato, *et al.*, "Hall mobility and carrier concentration of boron-doped homoepitaxially grown diamond (001) films," *Diamond and Related Materials*, vol. 4, pp. 59-61, 1994/12/01/1994.

- [1.9] H. El-Hajj, A. Denisenko, A. Bergmaier, G. Dollinger, M. Kubovic, and E. Kohn, "Characteristics of boron δ-doped diamond for electronic applications," *Diamond and Related Materials*, vol. 17, pp. 409-414, 2008.

- [1.10] F. Maier, M. Riedel, B. Mantel, J. Ristein, and L. Ley, "Origin of surface conductivity in diamond," *Physical Review Letters*, vol. 85, pp. 3472-3475, 10/16/ 2000.

- [1.11] H. Kawarada, T. Yamada, D. Xu, H. Tsuboi, T. Saito, and A. Hiraiwa, "Wide temperature (10K-700K) and high voltage (~1000V) operation of C-H diamond MOSFETs for power electronics application," in 2014 IEEE International Electron Devices Meeting, 2014, pp. 11.2.1-11.2.4.

- [1.12] K. Hirama, H. Sato, Y. Harada, H. Yamamoto, and M. Kasu, "Diamond field-effect transistors with 1.3 A/mm drain current density by Al<sub>2</sub>O<sub>3</sub> passivation layer," *Japanese Journal of Applied Physics*, vol. 51, p. 090112, 2012.

# 2. Background: Diamond as an electronic material

Diamond has many properties which make it an interesting candidate for electronic applications. This work will focus more specifically on the properties which make it an interesting candidate for high-power, robust electronic applications.

This chapter focuses on the physics behind diamond as a potential electronic material. It begins with the structure of the carbon atom and diamond crystal, and how these give rise to diamond's attractive properties for electronic applications. A brief introduction to the growth of synthetic diamond is included. Succeeding this is a discussion of the physics and challenges of doping diamond to achieve an extrinsic semiconductor with a special focus on the method of surface transfer doping, which is the doping method employed in this work. Following this is discussion of carrier transport in a semiconductor and the key parameters for assessing the performance of high power FETs. Finally the chapter covers metal-semiconductor and metal-oxide-semiconductor interfaces which will be used to produce the FETs in this work.

#### 2.1. Diamond Structure

What we call "Diamond" is an allotrope of carbon, other allotropes being graphite and graphene. Which of these forms carbon takes is determined by how the individual carbon atoms are bonded to their neighbors. The carbon atom has electrons in a  $(1s)^2(2s)^2(2p)^2$  orbital configuration and can have up to 4 covalent bonds [2.1].

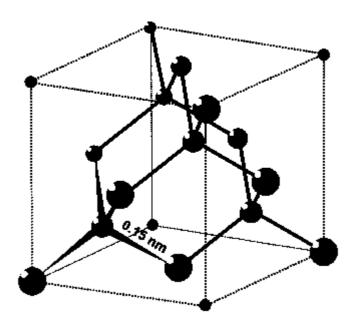

Sp<sup>2</sup> bonding of carbon atoms gives rise to graphene formation, where each carbon atom is bound to its 3 nearest neighbors. Graphene is conductive as it has one remaining electron which does not take part in bonding to other carbon atoms. Graphene is a 2 dimensional material and when many "sheets" of graphene are attracted to one another by a weak Van der Walls force it forms graphite [2.2]. Sp<sup>3</sup> bonded carbon forms a diamond lattice configuration. As can be seen from *figure 2.1.1*, the configuration can be viewed as each carbon atom forming tetrahedral covalent bonds to each of its 4 nearest neighbors[2.3].

Figure 2.1.1 Diamond lattice showing the unit cell of diamond formed by sp3 bonded carbon from [2.4].

Diamond's crystal structure is what gives rise to many of the properties for which it is well known. The atoms in the diamond lattice are close together as carbon has few "shells" available for covalent bonding, meaning electrons are pulled closer to the nuclei of the atom. The extreme physical robustness arises from the strength of these covalent bonds [2.4].

Diamond has very low phonon scattering due to the stiffness of the lattice, and a short bond length, which along with the periodicity of the diamond lattice contribute to fast transfer of phonons through the material. This results in diamond having the highest thermal conductivity of any 3 dimensional material of up to 24Wcm<sup>-1</sup>K<sup>-1</sup> [2.5], which allows for effective heat dissipation during device operation.

A large amount of energy is required to move an electron from the valence band of diamond into the conduction band due to the large energy difference between carbon atoms bonding and anti-bonding orbitals [2.3]. This gives rise to diamond's large band gap of 5.47eV, which makes diamond a wide band gap semiconductor. Diamond's wide band gap is important for power electronic applications as it leads to a very high theoretical breakdown voltage of  $10 \text{MVcm}^{-1}$  before avalanche breakdown [2.6].

In high electric fields carriers rapidly lose energy to the crystal lattice by emission of optical phonons as well as other scattering events, which limits the maximum velocity carriers can achieve in a material. Therefore, the optical phonon energy in a material can play a large role in determining the saturation velocity of charge carriers; and diamond possesses the largest optical phonon energy of any semiconductor [2.7]. Due to this, diamond has high velocity saturation for mobile charge which can be reached well before the electric field

breakdown, this is important for achieving high currents when operating at high electric field.

As will be discussed later in this chapter, the mobility of a semiconductor is determined by the effective mass and mean time between collisions of carriers[2.8]. As intrinsic diamond offers few scattering mechanisms to charge carriers (as will also be discussed in more detail later in this chapter) intrinsic diamond achieves a high mobility for both electrons and holes [2.9]. Mobility is an important metric as it determines how quickly carriers reach their saturation velocity.

The key figures discussed above are outlined below in *table 2.1.1* compared with values for Si and GaN.

| Property                                                          | Si   | GaN  | CVD Diamond |

|-------------------------------------------------------------------|------|------|-------------|

| Bandgap (eV)                                                      | 1.1  | 3.44 | 5.47        |

| Breakdown field MVcm <sup>-1</sup>                                | 0.3  | 5    | 10          |

| Electron saturation Velocity x10 <sup>7</sup>                     | 0.86 | 2.5  | 2           |

| cms <sup>-1</sup>                                                 |      |      |             |

| Hole Saturation velocity x10 <sup>7</sup>                         | 1    | n/a  | 0.8         |

| cms <sup>-1</sup>                                                 |      |      |             |

| Electron mobility cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | 1450 | 440  | 4500        |

| Hole mobility cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>     | 480  | 200  | 3800        |

| Thermal Conductivity Wcm <sup>-1</sup> K <sup>-1</sup>            | 1.5  | 1.3  | 24          |

Table 2.1.1. – Comparison between semiconductor properties for diamond and other semiconductor materials Si, and GaN, figures from [2.6].

There are a number of figures of merit which can be used to assess how material qualities can translate into real electronic device performance. For this work Johnson's figure of merit, Keye's figure of Merit and Baliga's figure of merit are of importance.

Johnson's figure of merit is defined as follows:

$$JFOM = \frac{E_c * v_s}{2\pi} \qquad equation \ 2.1.1$$

where  $E_c$  is the critical electric field for breakdown and  $v_s$  is the saturated drift velocity. This figure defines the power-frequency product [2.10].

Keye's figure of merit is defined as follows:

$$KFOM = \lambda \left[2.\frac{c*v_s}{4\pi\varepsilon}\right]^{1/2}$$

equation 2.1.2

where  $\lambda$  is the thermal conductivity, c is the speed of light,  $\varepsilon$  is the dielectric constant and  $v_s$  is the saturated drift velocity. KFOM provides a thermal limitation to the switching behavior of a transistor [2.11].

Baligas figure of merit is defined as follows:

$$BFOM = \varepsilon * \mu * E_q^3$$

equation 2.1.3

Where  $\varepsilon$  is the dielectric constant,  $\mu$  is is the mobility and  $E_g$  is the band gap. BFOM defines switching losses in power FETs assuming that the power losses are solely due to the power loss in the on-state current flow through the on resistance of an FET [2.12].

|      | Si | GaN | CVD Diamond |

|------|----|-----|-------------|

| JFOM | 1  | 280 | 8200        |

| KFOM | 1  | 1.8 | 32          |

| BFOM | 1  | 910 | 17200       |

Table 2.1.2 – Outlines Figures of merit values discussed in this body of work for Silicon, GaN and CVD diamond[2.6].

As can be seen from the above *table 2.1.2* Diamond's properties give rise to high values for the outlined figures of merit. This means that diamond is a very attractive candidate for high-power, high-frequency devices. Although these figures of merit provide a comparison between

## 2.2 Synthetic Diamond growth

Although diamond possesses many qualities which make it an interesting electronic material, these properties are not found consistently in natural diamond due to the inclusion of impurities or non-diamond carbon in the lattice. However, diamonds which possesses all these qualities can be produced synthetically.

The first diamonds grown synthetically were reported by General Electric in 1955 using the process of High Pressure High Temperature (HPHT). Essentially graphite was placed under immense pressures at high temperatures in an attempt to mimic the thermodynamic conditions of the earth's natural creation of diamonds [2.13]. Following this, groups also explored "detonation diamond" whereby immense temperatures and pressures are applied to graphite by close proximity to an explosive device[2.14]. Both of these techniques showed successful diamond growth, however each has its draw backs. HPHT diamond requires a large amount of energy, which increases exponentially with increased area. Detonation

diamond can only yield miniscule "seeds" of diamond, of little use for electronic device applications.

Chemical Vapour Deposition (CVD) growth is the main method used for the production of high quality, electronic grade diamond material today. CVD growth produces diamonds by heating a hydrocarbon gas in a low pressure (vacuum) environment. Typically the growth will nucleate on diamond already in the chamber, such as "seed" material grown using another method (HPHT or detonation). In the chamber some of the hydrocarbon gas is converted into atomic hydrogen and carbon usually by microwave plasma or by passing the gas over a hot filament. It is energetically favorable for the free carbon to form diamond in this environment. Graphite and non-diamond carbon react with the atomic hydrogen and evaporate into a newly formed gas phase[2.15].

During CVD diamond synthesis, where the growth ends the carbon is typically terminated with hydrogen atoms[2.16]. Hydrogen termination is typically stable at room temperature in normal atmopsheric conditions, however the hydrogen termination can be removed by strong acids or by exposing the surface to high temperatures (above 230°C) in normal atmosphere. In these cases the hydrogen is usually replaced with oxygen from the atmosphere leading to an oxygen terminated surface. If the hydrogen or oxygen terminated diamond surface is annealed at around 1000°C in Ultra High vacuum (UHV) the surface carbon atoms "reconstruct" leading to a clean surface[2.17].

## 2.3 Doping of Diamond

In order to increase the mobile charge carrier density in semiconducting material, doping is employed. By this method additional carriers are introduced into the lattice of a material typically by introduction of impurity atoms which either offer an additional electron to the lattice (n-type doping) or accept an electron from the lattice introducing an additional mobile vacancy (hole) (p-type doping). These impurity atoms will usually take the place of an intrinsic atom (substitutional doping)[2.18].

The main methods of introducing additional impurity dopant atoms into a semiconducting material is by diffusion, ion implantation and during growth[2.19]. During diffusion implantation atoms are placed on or near the surface of a semiconductor at elevated temperatures. These atoms migrate through the semiconducting material. The doping concentration is concentrated at the surface as the dopant must diffuse through the material from the surface. During ion implantation dopant atoms are accelerated to high velocities incident on the surface, becoming embedded in the lattice of the material. During growth

impurity atoms can be included in the gas or liquid phase of semiconductor material production and become included in the lattice.

For diamond there are few elements which can be used for this purpose, and they face a number of problems. If a large atom is implanted into the material it could disrupt the lattice, due to this only a few smaller atoms such as boron, nitrogen and phosphorus are options for incorporating into diamond. The tight spacing of the diamond lattice can make diffusion of impurities through the lattice very difficult [2.20], therefore diffusion implantation is not particularly desirable. Ion implantation can cause large amounts of damage to the lattice due to the high velocity ions colliding with atoms in the lattice. In order to reduce this damage in most semiconducting materials the material is annealed after implantation which reconstructs some of the damaged bonds in the material. However, in diamond high temperature annealing required to reform the bonds can also cause graphitization of the diamond (at around 1500K) [2.21]. Therefore the most common, and successful way of including impurities in diamond is to introduce them during the growth process.

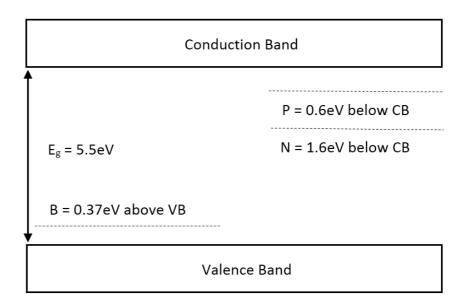

Figure 2.3.1 - Energy levels of impurity atoms suitable for implantation in diamond.

The few elements suitable for doping diamond due to their small size also have other draw backs. For n-type dopants phosphorus and nitrogen the activation energies are  $0.6 \,\mathrm{eV}[2.22]$  and  $1.6 \,\mathrm{eV}[2.23]$  respectively. This is very high when compared with other semiconductors (activation energies for arsenic and boron in silicon are  $0.049 \,\mathrm{eV}$  and  $0.045 \,\mathrm{eV}$  respectively [2.24]) and results in low carrier concentrations at room temperature which is not ideal. The activation energy for boron is lower at  $0.37 \,\mathrm{eV}[2.25]$ , but still results

in low activation of carriers at room temperature. In *figure 2.3.1* the activation energies of these impurity atoms can be seen in reference to either the conduction band or valence band. Boron doping can result in increased conductivity at room temperature but only in very high doping concentrations in order to offset the low number of carriers active at room temperature.

Diamond can be bulk doped by impurity atoms such as boron during CVD growth by introducing the impurities in the gas phase [2.26]. However this is not particularly controllable on the nanometer scale. As impurity concentrations in semiconductors are increased, the mobility of charge carriers can decrease due to increased impurity scattering events. As bulk boron doping in diamond requires a high concentration of boron in order to achieve appreciable carriers at room temperature this leads to low carrier mobility. In order to reduce the detrimental effect on mobility of incorporating large quantities of boron into diamond, the method of delta doping can be employed. Delta doping is a technique whereby a thin layer of doped diamond is grown during CVD growth including impurity atoms[2.27]. This thin layer is sandwiched between the intrinsic bulk of the diamond and a layer of intrinsic diamond grown on top of the doped layer. In theory this can result in a large density of charge being confined to a few atomic layers of doped diamond to act as a charge transfer layer. The wave functions of the carriers should extend into the intrinsic areas of the diamond reducing the scattering events as there are much fewer impurities in the intrinsic region. Carrier concentrations in the region of 10<sup>15</sup>/cm<sup>2</sup> have been reported at room temperature for delta doped layers, however this layer had a mobility of just 2.9 cm<sup>2</sup>/Vs [2.28], showing that delta doping still requires substantial progress to be made.

# 2.4 Surface transfer doping of diamond

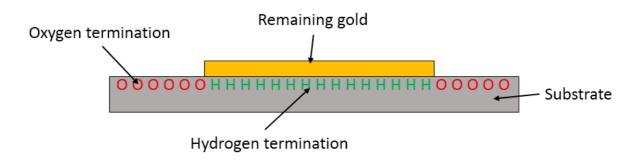

As discussed previously, diamond produced by CVD growth typically results in films with hydrogen terminated surfaces. This is not the only option regarding the satisfaction of dangling bonds on the surface of diamond. Other alternative elements can terminate diamond satisfying the "dangling" bonds. In this work the terminations of interest are hydrogen and oxygen.

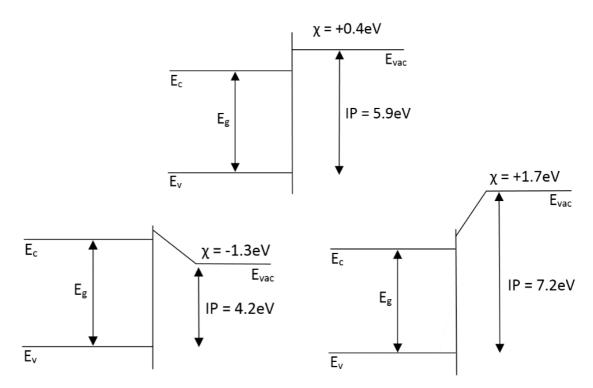

An "unterminated" diamond interface has an ionization potential (IP) (which is the energy required to excite an electron from the valence band to the vacuum level) of 5.9eV. This is due to the electron affinity (which is the energy required to move an electron from the conduction band minimum of a material to the vacuum level) being 0.4eV and the band gap being 5.5eV. Oxygen termination increases the electron affinity of the diamond surface to

1.7eV. This results in an ionization potential of oxygen terminated diamond of 7.2eV. Hydrogen termination results in the electron affinity of the diamond decreasing to -1.3eV. Thus the ionization potential of hydrogen terminated diamond at the surface is 4.2eV[2.29], the lowest of any semiconductor.

Fig 2.4.1 – Band alignment of unterminated diamond (top) Hydrogen terminated diamond (bottom left) and oxygen terminated diamond (bottom right).

The negative electron affinity of hydrogen terminated diamond is caused by the negative surface dipole which arises from the hydrogen-carbon bonds at the surface. The surface dipole pulls the vacuum level of the diamond surface below the conduction band maximum (CBM) by 1.3eV and reduces the ionization potential to 4.2eV. This means that if a suitable acceptor medium is near the surface of hydrogen-terminated diamond, it will become energetically favorable for electrons to leave the valence band of the diamond leaving behind free holes. These holes accumulate near the surface of the hydrogen terminated diamond and can be modeled as a 2 dimensional hole gas (2DHG).

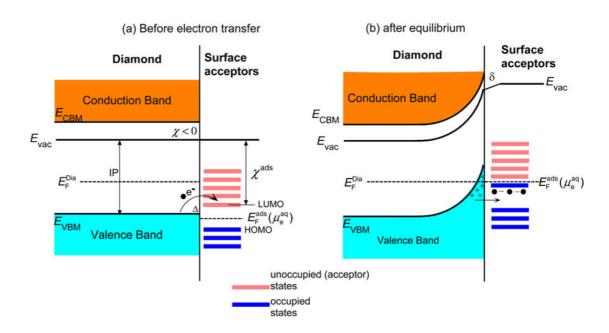

For a material to be a suitable surface acceptor it must have available energy levels close to or below the valence band maximum of hydrogen terminated diamond to make electron transfer energetically favorable[2.30]. Hydrogen terminated diamond in intimate contact with a suitable accepter layer before and after equilibrium can be seen in *figure 2.4.2*. For organic materials this means their lowest unoccupied molecular orbit (LUMO) must be greater than 4.2eV. For non-organic materials this means that the electron affinity must be more than 4.2eV. If a material has a LUMO or electron affinity much greater than 4.2eV

there is a greater level of transfer between the hydrogen terminated diamond and the material, leading to a greater concentration of electrons that can leave the diamond prior to equilibrium and therefore a larger concentration of holes accumulated at the surface.

Fig 2.4.2 – Shows band alignment of hydrogen terminated diamond before and after equilibrium with a suitable surface transfer doping material [2.30].

Whereas hydrogen termination results in a 2DHG forming near the surface of the material, oxygen termination does not. In this way oxygen termination of the surface can be used to "Isolate" conductivity and confine it only to desired areas (active device regions) in order to eliminate parasitic conductive paths. In alternative material systems such as HEMTs this same effect is typically achieved by a "Mesa" etch through the active, conduction layer in order to remove the two dimensional electron gas (2DEG).

#### 2.5 Carrier transport in a Semiconductor

To understand the performance of field effect transistors it is important to understand the transport of electrons and holes in a semiconductor.

The mobility of an electron or hole can be defined as follows[2.8]:

$$\mu = \frac{q\tau_c}{m^*}$$

equation 2.5.1

where q is the unit charge,  $\tau_c$  is the mean time between scattering events and  $m^*$  is the effective mass of the carrier.

We can see in *equation 2.5.1* that the mobility is highly dependent on the mean time between scattering events of charge carriers. Carrier scattering mechanisms lead to large variation in mobility of electrons and holes as it can drastically increase the mean time between collisions. Some of the main scattering mechanisms in semiconductors are phonon scattering, surface roughness scattering, carrier-carrier scattering and coulomb scattering [2.8].

Arguably the two most important scattering mechanisms in hydrogen terminated diamond are coulomb scattering, and surface roughness scattering[2.31]. Coulomb scattering occurs when carriers have their paths deflected by the influence of charge in the lattice, be that ionized impurities or some other charge in proximity to the carriers. The proximity of the 2DHG to the surface of the hydrogen terminated diamond means that surface roughness scattering can also play a large role in the mobility of the 2DHG.

Under an electric field, carriers are accelerated by the field during their motion between scattering events [2.8]. This is known as the drift velocity, which can be seen in *equation* 2.5.2.

$$v = \mu E$$

equation 2.5.2

where E is the electric field strength and v is the drift velocity.

As the distance between scattering events is not changed, the application of an electric field reduces the time between such events. As more scattering events occur with unit time more energy is lost to them. The result of this is that electrons and holes cannot be accelerated continuously and reach a saturation velocity.

#### 2.6 Field Effect Transistor operation and figures of merit

For discrete high-power field effect transistors (FETs), the most important parameters are maximum on state drain current, off state breakdown voltage, transconductance and on-resistance (R<sub>on</sub>). R<sub>on</sub> is important to minimize on state power loss (switching losses are more important for RF operation which is not discussed in detail in this work).

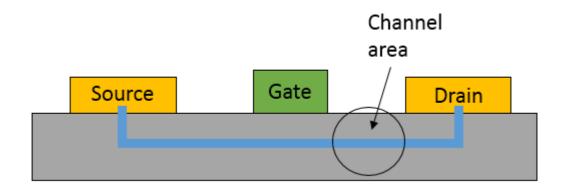

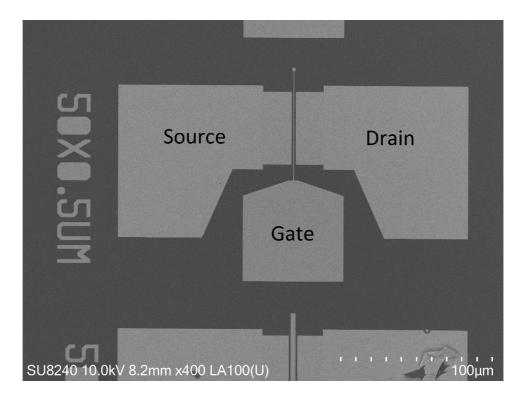

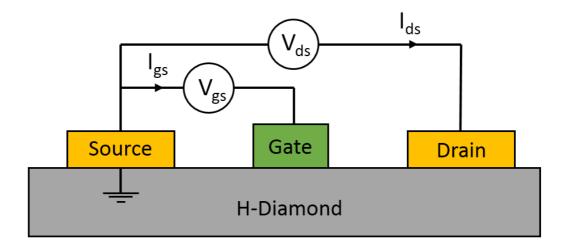

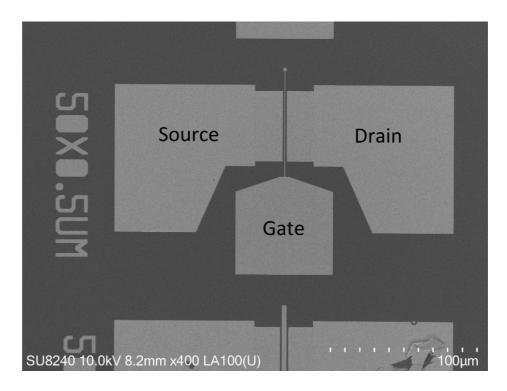

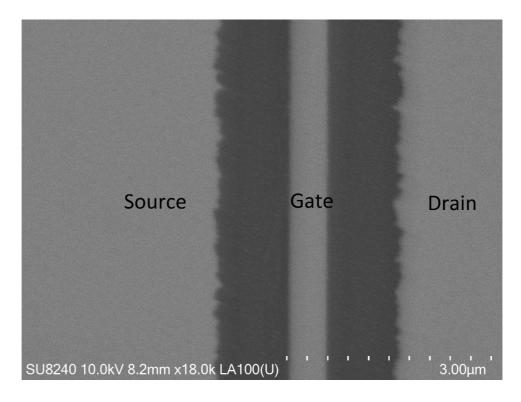

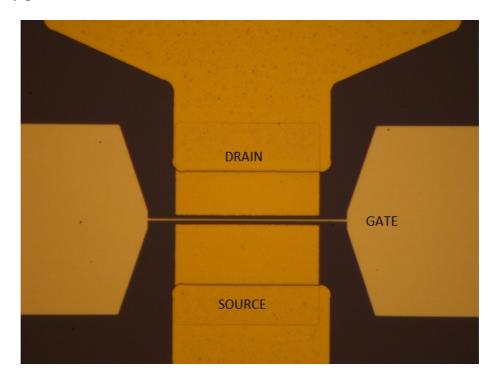

*Figure* – 2.6.1 – *Simplified FET model showing source, drain and gate contacts.*

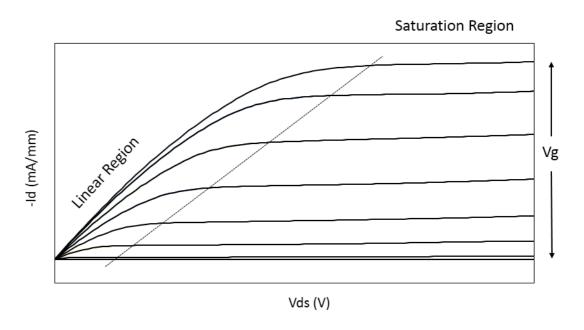

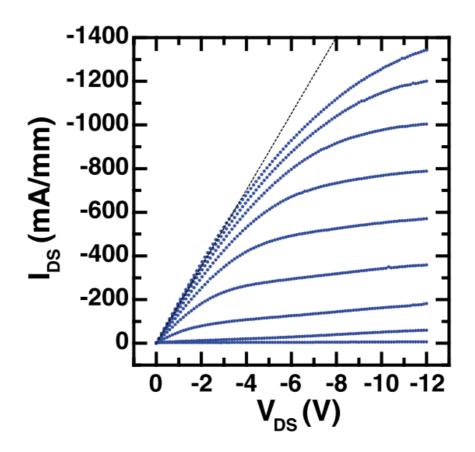

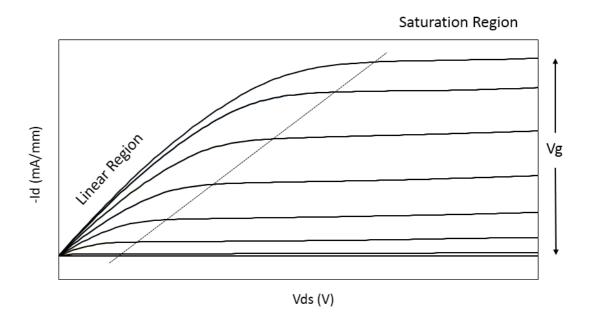

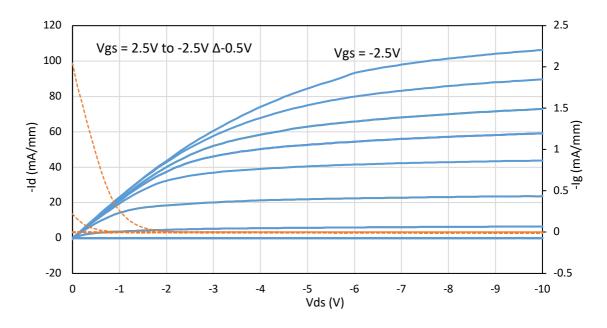

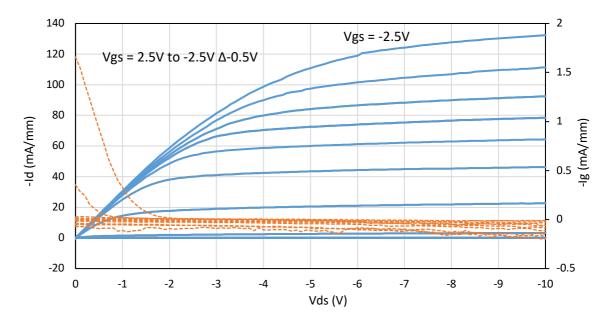

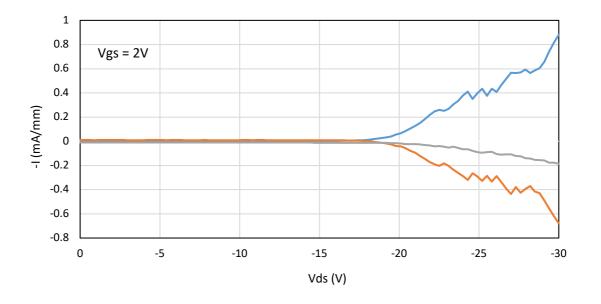

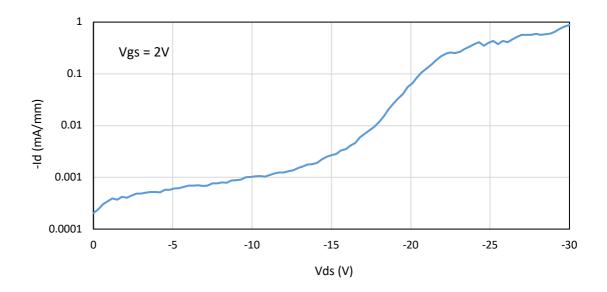

An FET consists of 2 ohmic contacts (source and drain) and a gate, fabricated on a semiconducting material. By applying a potential difference between the source and drain contacts (V<sub>ds</sub>) of an FET, current will flow between the source and drain, under the gate (assuming the gate is "on" as will be discussed shortly). This potential is typically applied between the source and drain contacts with the source grounded. In p-type electronics, as shown in this work, a negative potential is applied between the source and drain, allowing holes to flow from the source to the drain. In n-type electronics, a positive potential is applied for electrons flow from the source to the drain. As the potential is increased, the current through the FET increases due to the increasing velocity of the charge carriers in the channel. This is called the linear region as can be seen in *figure 2.6.2*. The velocity of the charge carriers will eventually saturate with increased electric field in the semiconductor, this, and pinch-off in the channel under the gate at increased drain potential, causes the current to saturate. This is called the saturation region as can be seen in *figure 2.6.2* If the potential is continually increased, eventually the FETs will be damaged due to the large electric field between the source and drain, and gate and drain, causing impact ionization in the material [2.32] or different breakdown mechanism at the metal-semiconductor interfaces.

A FET effectively operates as a switch, with the gate voltage ( $V_{gs}$ ) determining whether the FET is "off" or "on". This potential is applied between the source and gate contacts with the source grounded. In the p-type electronics shown in this work, when a positive voltage is applied to the gate holes are depleted away from the area under the gate, decreasing the concentration of carriers under the gate. When there is sufficiently low carriers the FET will be "off" as there should be no, or very little current flow. When a negative voltage is applied to the gate, holes are accumulated under the gate increasing the number of charge carriers and turning the FETs "on". As the voltage is pushed more negative, the concentration of carriers under the gate increases, resulting in larger current flow. If the gate voltage is pushed too negative however, the gate leakage currents will increase (as will be discussed in chapter

2.7), which is undesirable and can damage the gate-semiconductor interface. In n-type electronics, as a positive voltage is applied to the gate, electrons are depleted away from the gate interface, reducing the concentration of charge in the channel under the gate, impeding charge flow between the source and drain, turning the FETs "off". If a positive voltage is applied, the concentration of electrons under the gate increases, allowing current to flow between the source and drain, turning the FETs "on".

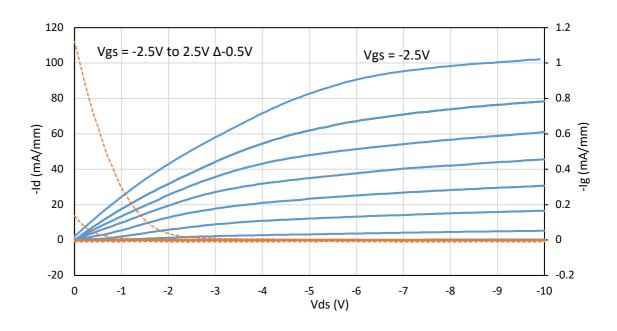

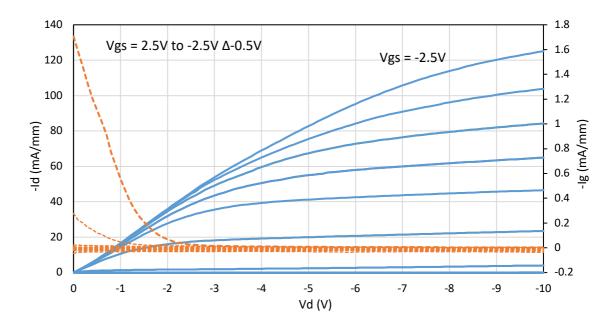

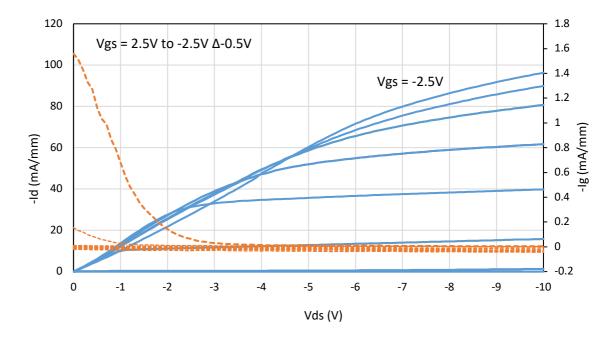

Figure 2.6.2 – Example output characteristic of p-type FETs characterized in this work.

A power FET should block high voltages when it is "off" and allow large current flows through the FET when it is "on". It must do this with minimal power losses.

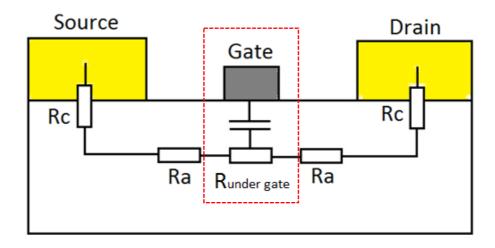

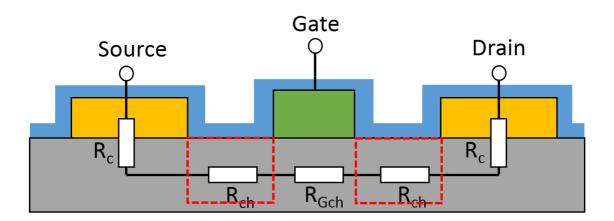

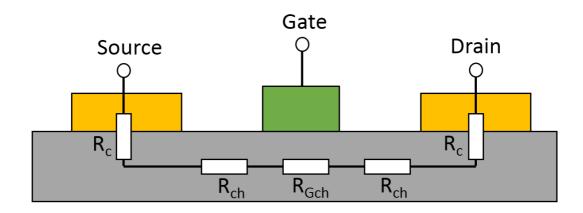

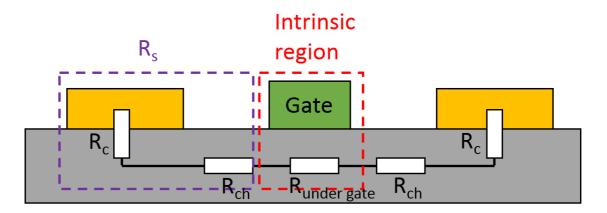

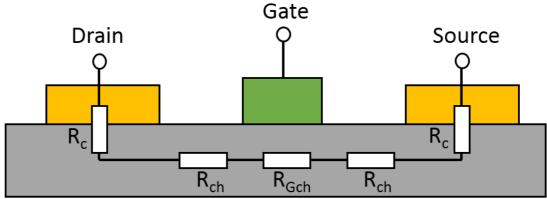

A FET can be visualised as a simple series resistor network when operating in the linear region. As with a real series resistor network the current path will be dominated by the largest resistances, thus it is important to minimise the resistance in each region of the device. As can be observed in the simplified FET model in *figure 2.6.3*, R<sub>c</sub> is the contact resistance and is determined by the "ohmic" contact made to the device channel. R<sub>a</sub> is the "access" or "channel" resistance, which is determined by the resistance of the intrinsic charge layer in the FET, R<sub>under gate</sub> is determined by the gate contact. For a p-type semiconductor, when a metal with a low work function comes into contact with the substrate a depletion region is formed (assuming the semiconductor is sensitive to metal work function, as hydrogen terminated diamond is) whereby holes are depleted away from the gate. When the gate contact is biased with a negative voltage holes accumulate at the surface of the diamond forming a channel for current to flow between the source and drain. Thusly the resistance under the gate is determined by the ability of the gate contact to accumulate and deplete charge beneath the gate.

Fig 2.6.3 – Simplified model of FET showing intrinsic area within red square.

$$R_{on} = 2R_c + 2R_a + R_{under\ gate}$$

equation 2.6.1

When an FET is operating at high drain bias, the maximum current can be defined as [2.33]:

$$I = Wvnq$$

equation 2.6.2

where W is the channel width, v the carrier saturation velocity, n is concentration of charge in the channel, and q is the unit charge.

It can be seen from *equation 2.6.3* the maximum current through an FET is heavily dependent on both the carrier density and carrier saturation velocity in the channel. These are both intrinsic to the semiconductor material in the channel areas, and dependent on the performance of the gate contact under the gate. Diamond has the potential for extremely high values for both carrier density and carrier saturation velocity. One of the key aspects of this work has been to increase the carrier concentration in the channel by including surface transfer doping oxides in the "access" regions of FETs.

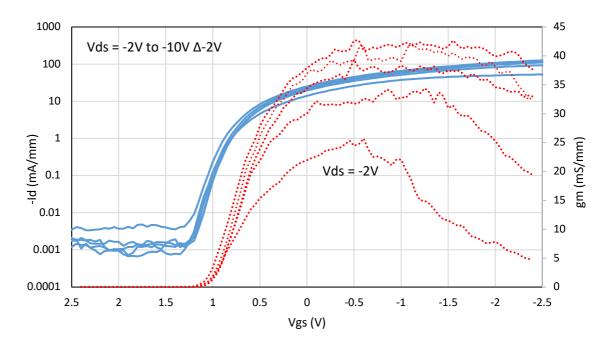

As mentioned previously, the concentration of carriers under the gate also heavily contributes to the maximum current as the carriers must pass under the gate, and the carrier concentration under the gate is dependent upon the voltage applied to the gate contact. Therefore, how well the gate can accumulate charge is important to understand. This can be assessed by the transconductance of the FETs. Intrinsic transconductance  $(g_m^*)$  is defined as the rate of change of drain-source current with respect to gate-source voltage for a constant drain-source bias as can be seen from *equation* 2.8.3[2.34].

$$g_m^* = \left(\frac{dI_{ds}}{dV_{gs}}\right)_{V_{ds}}$$

equation 2.6.3

The intrinsic transconductance  $(gm^*)$  only applies to the gate contact and does not take into account the voltage drop between the source and gate contacts. The extrinsic transconductance  $(g_m)$  which includes the source resistances,  $R_s$  (which is equal to  $R_c+R_a$ ) can be defined as follows in *equation 2.6.4* [2.35]:

$$g_m = \frac{g_m^*}{1 + g_m^* R_s} \qquad equation \ 2.6.4$$

#### 2.7 Metal Semiconductor interfaces

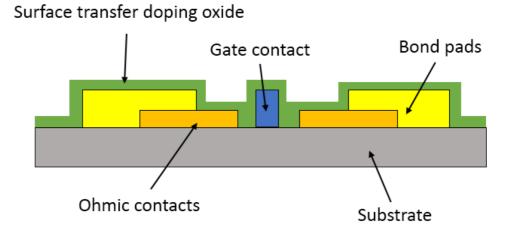

To utilize a semiconductor material in electronic device applications, there is a need to inject and eject charge from the material via ohmic contacts. To do this we must understand how the semiconducting material interfaces with metals. The gates of the FETs made in this work are produced by Schottky, or Metal Oxide Semiconductor (MOS) contacts which are used to accumulate or deplete charge under the gate. As this work relates to hydrogen terminated diamond which is a p-type semiconductor, only p-type interfaces will be discussed.

Due to the low density of pinning states at the surface, hydrogen terminated diamond obeys the Schottky- Mott rule and has an un-pinned fermi level allowing the fermi level of the diamond to align with metal it comes into contact with [2.36].

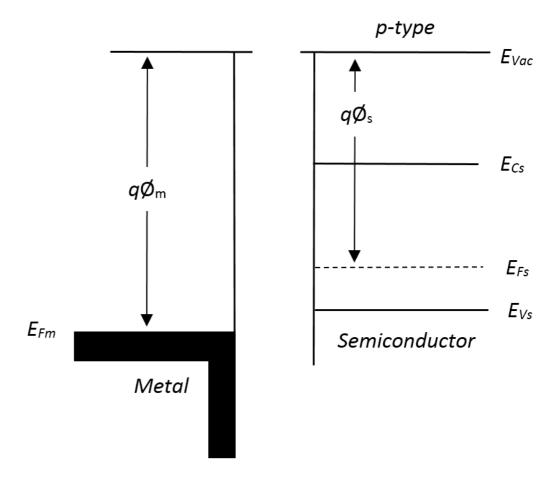

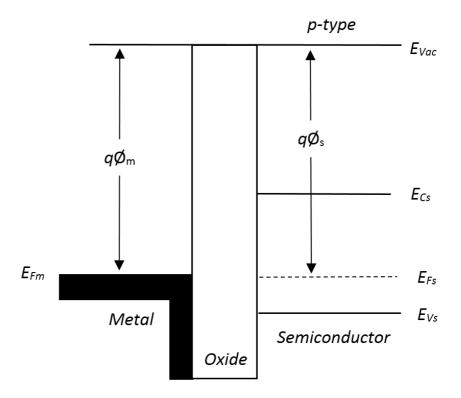

The work function of a metal  $(\emptyset_m)$  or semiconductor  $(\emptyset_s)$  is the energy required to remove an electron from the fermi level of the material to the vacuum level. If a metal and semiconductor with differing work functions come into intimate contact, charge transfer occurs until the fermi levels align at equilibrium by diffusion of electrons across the interface[2.37].

#### Ohmic Contacts

An ideal ohmic contact results in no barrier for carriers at the interface between the semiconductor and metal and provides a linear current response with applied voltage. Ohmic contacts are used in this work to form the source and drain contacts of the fabricated FETs.

To form a p-type ohmic contact, the work function of the metal must be greater than the work function of the semiconductor. This case can be seen in *figure 2.7.1*. As discussed previously, charge transfer occurs at the interface until equilibrium is reached. In this case,

electrons flow from the semiconductor to the metal, bending the bands downwards. After equilibrium holes flowing from the semiconductor to the metal see no barrier as can be seen in *figure 2.7.2*.

Fig 2.7.1— Metal with work function greater than p-type semiconductor prior to equilibrium.

Fig 2.7.2 - Metal with work function greater than p-type semiconductor after equilibrium.

#### Schottky contacts

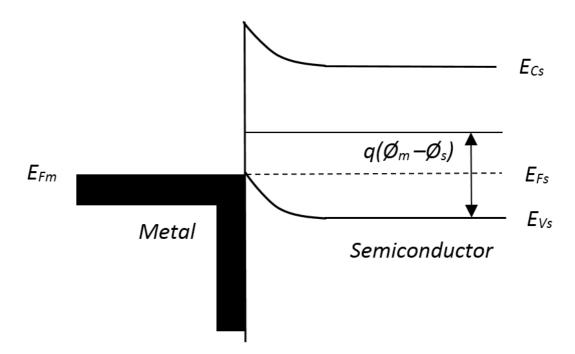

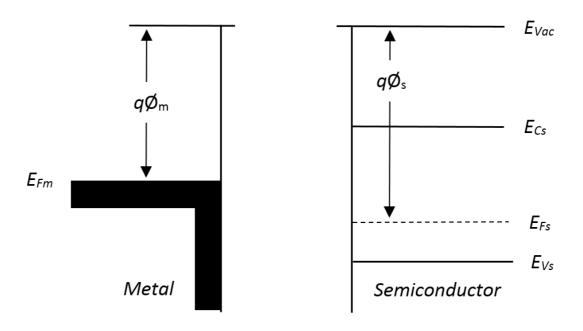

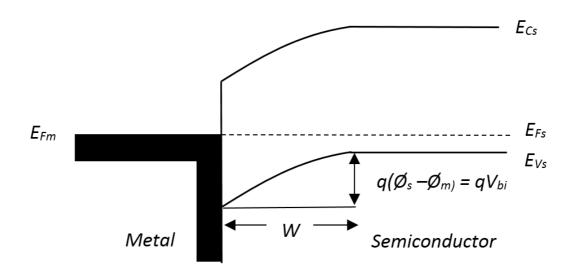

To form a Schottky contact on a p-type semiconductor the work function of the metal must be less than the work function of the semiconductor. Shottky contacts are used in this work to form the gates in a MESFET configuration.

As discussed previously charge transfer occurs between the metal and semiconductor until the fermi levels align at equilibrium. For equilibrium to be reached electrons must transfer between the metal and semiconductor, which causes a build-up of charge at the interface and bends the semiconductor bands upwards, forming a depletion region on the semiconductor side of the interface (W) as seen in *figure 2.7.4*. After equilibrium the barrier to hole flow from the semiconductor to the metal is shown in *figure 2.7.4* as  $qV_{bi}$ .

*Fig 2.7.3 – Metal with work function less than p-type semiconductor prior to equilibirum.*

Fig 2.7.4 – Metal with work function less than p-type semiconductor after equilibrium, showing potential barrier  $V_{bi}$  and depletion region W.

For charge to flow through a Schotty-semiconductor interface charge must find a way to overcome the potential barrier. The main ways carriers can do this is through Thermionic emission (TE), Field emission (FE). Thermionic emission is when a carrier has sufficient thermal energy to overcome the barrier height in the semiconductor-metal interface and is thus highly reliant on temperature. Field emission occurs when carrier's tunnel through the barrier, it is highly dependent on the "tunneling" probability, which is itself highly dependent on the concentration of carriers at the interface and the width of the potential barrier [2.38].

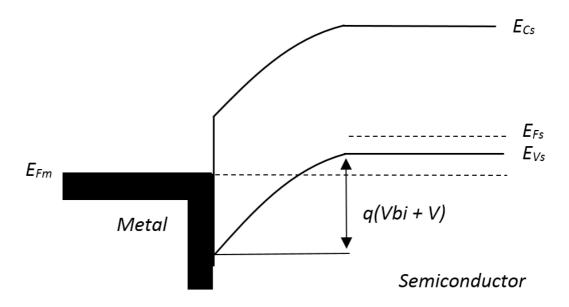

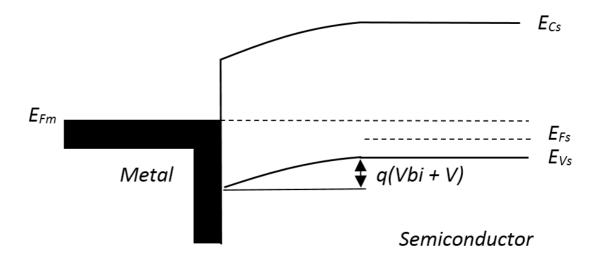

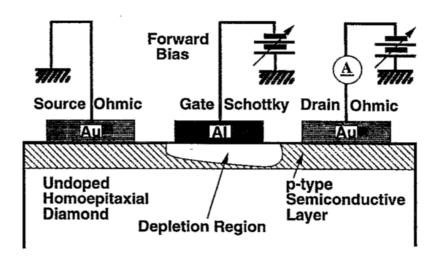

As mentioned previously, Schottky contacts have been used to create the gate contact of FET structures in a Metal-Semiconductor FET (MESFET) configuration in this work. When a positive voltage is applied to the metal contact, (as can be seen in *figure 2.7.5*) this results in a larger barrier to holes. This also depletes holes on the semiconductor side of the interface, leading to a lower concentration of carriers on the semiconductor side of the interface. In this work this is used to turn the FETs "off". When a negative voltage is applied to the metal side of the interface, this results in a lower barrier for holes (as seen in *figure 2.7.6*), which causes an accumulation of mobile holes on the semiconductor side of the interface if there are available mobile holes. In this work this is used to turn the FETs "on" and provide a charge transfer layer under the gate. At sufficiently negative voltage the schottky barrier height will be reduced enough that holes can flow easily from the semiconductor to the metal, resulting in gate leakage current.

Fig 2.7.5 – Shows p-type semiconductor Schottky contact under positive voltage resulting in increased potential barrier height.

Fig 2.7.6 – Shows p-type semiconductor Schottky contact under negative voltage resulting in decreased potential barrier height.

# MOS interface

A special mention must be given to the Metal-Oxide-Semiconductor (MOS) interface as this is used to create the gate contacts in a MOSFET configuration later in this work. The ideal MOS interface can be modeled as a parallel plate capacitor, with the gate metal acting as one plate and the semiconductor as the other[2.39]. For the discussion here of an ideal MOS interface we assume that the semiconductor and metal have the same work function.

Fig 2.7.8– Metal Oxide Semiconductor interface band diagram of a p-type semiconductor at V = 0.

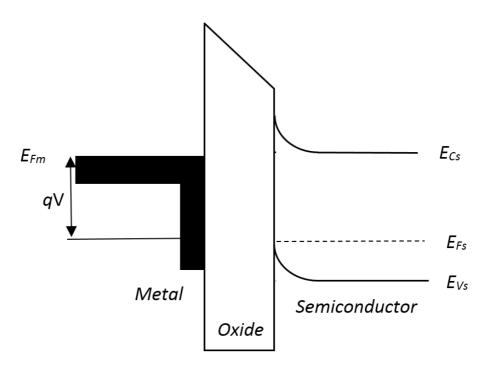

Fig 2.7.9 – Metal Oxide Semiconductor interface band diagram of a p-type semiconductor with voltage <0 applied to the gate metal.

When a negative voltage is applied to the metal contact, there is an accumulation of positive charge (mobile holes) on the semiconductor side of the oxide due to the negative charge on

the metal side as can be seen in *figure 2.7.9*. In this work this has been used to turn the FETs "on" by increasing the concentration of mobile holes beneath the gate contact.

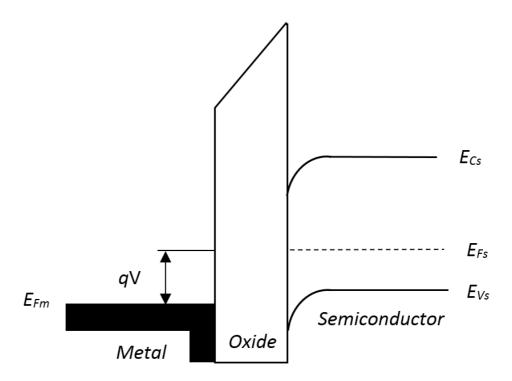

Fig 2.7.10– Metal Oxide Semiconductor interface band diagram of a p-type semiconductor with voltage >0 applied to the gate metal.

When a positive voltage is applied to the metal contact, there is an accumulation of negative charge at the semiconductor side of the interface due to the positive charge on the metal side as seen in *figure 2.7.10*. In this work this has been used to turn the FETs "off" by depleting the positive charge carriers (holes) away from the region under the gate contact, reducing the concentration of carriers under the gate.

As voltages become sufficiently large, tunneling currents through the oxide become increased. This can lead to permanent dielectric breakdown [2.40].

# Chapter Summary

This chapter has addresed the theory behind diamond as an electronic material, beginning by discussing the structure of the carbon atom and the diamond lattice, and how these give rise to the impressive intrinsic properties of diamond which could prove useful for electronic applications. Following this, the chapter discussed the growth of synthetic diamond for electronic applications. The chapter has also addressed the challenges of substitutionally doping diamond and the novel doping method of surface transfer doping which is utilised in the FETs in this work. Finally the chapter has discussed semicondutor physics, addressing

current transport through a semiconductor, the basic figures of merit for FET operation with respect to high power applications, metal-semiconductor interfaces, and metal-oxide-semiconductor interfaces which will be used to produce the FETs reported in this work.

#### References

- [2.1] H. A. Bent, "An appraisal of valence-bond structures and hybridization in compounds of the first-row elements," *Chemical Reviews*, vol. 61, pp. 275-311, 1961/06/01 1961.

- [2.2] M. S. A. Bhuyan, M. N. Uddin, M. M. Islam, F. A. Bipasha, and S. S. Hossain, "Synthesis of graphene," *International Nano Letters*, vol. 6, pp. 65-83, 2016/06/01 2016.

- [2.3] G. E. Kimball, "The Electronic structure of diamond," *The Journal of Chemical Physics*, vol. 3, pp. 560-564, 1935/09/01 1935.

- [2.4] J. J. Gracio, Q. H. Fan, and J. C. Madaleno, "Diamond growth by chemical vapour deposition," *Journal of Physics D: Applied Physics*, vol. 43, p. 374017, 2010.

- [2.5] D. J. Twitchen, C. S. J. Pickles, S. E. Coe, R. S. Sussmann, and C. E. Hall, "Thermal conductivity measurements on CVD diamond," *Diamond and Related Materials*, vol. 10, pp. 731-735, 2001/03/01/2001.

- [2.6] C. J. H. Wort and R. S. Balmer, "Diamond as an electronic material," *Materials Today*, vol. 11, pp. 22-28, 2008/01/01/2008.

- [2.7] R. S. Sussman, "CVD diamond for electronic devices and sensors," *John Wiley and Sons Inc.*, p. 40, 2009.

- [2.8] S. M. Sze and K. K. Ng, "Physics of semiconductor devices," *John Wiley and Sons Inc.*, p. 28, 2007.

- [2.9] J. Isberg, J. Hammersberg, E. Johansson, T. Wikstrom, D. J. Twitchen, A. J. Whitehead, *et al.*, "High carrier mobility in single-crystal plasma-deposited diamond," *Science*, vol. 297, pp. 1670-2, Sep 06 2002.

- [2.10] E. Johnson, "Physical limitations on frequency and power parameters of transistors," in *1958 IRE International Convention Record*, 1965, pp. 27-34.

- [2.11] R. W. Keyes, "Figure of merit for semiconductors for high-speed switches," *Proceedings of the IEEE*, vol. 60, pp. 225-225, 1972.

- [2.12] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Letters*, vol. 10, pp. 455-457, 1989.

- [2.13] F. P. Bundy, H. T. Hall, H. M. Strong, and R. H. Wentorf Jun, "Man-made diamonds," *Nature*, vol. 176, p. 51, 07/09/online 1955.

- [2.14] P. S. DeCarli and J. C. Jamieson, "Formation of diamond by explosive shock," *Science*, vol. 133, p. 1821, 1961.

- [2.15] S. T. Lee, Z. Lin, and X. Jiang, "CVD diamond films: nucleation and growth," *Materials Science and Engineering: R: Reports*, vol. 25, pp. 123-154, 1999/07/30/1999.

- [2.16] J. E. Butler, "Thin film diamond growth mechanisms," *Philosophical Transactions of the Royal Society of London. Series A: Physical and Engineering Sciences*, vol. 342, pp. 209-224, 1993.

- [2.17] B. B. Pate, "The diamond surface: atomic and electronic structure," *Surface Science*, vol. 165, pp. 83-142, 1986/01/01/1986.

- [2.18] M. S. Tayagi, "Introduction to Semiconductor Materials and Devices," *John Wiley and Sons Inc.*, pp. 67-72, 1992.

- [2.19] B. Streetman and S. Banerjee, "Solid State Electronic Devices," *Pearson*, pp. 156-160, 2005.

- [2.20] G. Popovici, R. G. Wilson, T. Sung, M. A. Prelas, and S. Khasawinah, "Diffusion of boron, lithium, oxygen, hydrogen, and nitrogen in type IIa natural diamond," *Journal of Applied Physics*, vol. 77, pp. 5103-5106, 1995/05/15 1995.

- [2.21] R. Kalish, "Ion-implantation in diamond and diamond films: doping, damage effects and their applications," *Applied Surface Science*, vol. 117-118, pp. 558-569, 1997/06/02/1997.

- [2.22] I. Stenger, M. A. Pinault-Thaury, T. Kociniewski, A. Lusson, E. Chikoidze, F. Jomard, et al., "Impurity-to-band activation energy in phosphorus doped diamond," *Journal of Applied Physics*, vol. 114, p. 073711, 2013/08/21 2013.

- [2.23] A. Mainwood, "Theoretical modelling of dopants in diamond," *Journal of Materials Science: Materials in Electronics*, vol. 17, pp. 453-458, 2006/06/01 2006.

- [2.24] F. J. Morin and J. P. Maita, "Electrical properties of silicon containing arsenic and boron," *Physical Review*, vol. 96, pp. 28-35, 10/01/1954.

- [2.25] J. F. Prins, "Activation of boron-dopant atoms in ion-implanted diamonds," *Physical Review B*, vol. 38, pp. 5576-5584, 09/15/1988.

- [2.26] J. Mort, D. Kuhman, M. Machonkin, M. Morgan, F. Jansen, K. Okumura, et al., "Boron doping of diamond thin films," *Applied Physics Letters*, vol. 55, pp. 1121-1123, 1989/09/11 1989.

- [2.27] A. V. M. Kunze, G. Dollinger, A. Bergmaier, E. Kohn, "Delta doping in diamond," *Carbon*, pp. 787–791, 1999.

- [2.28] G. Chicot, A. Fiori, P. N. Volpe, T. N. Tran Thi, J. C. Gerbedoen, J. Bousquet, *et al.*,

"Electronic and physico-chemical properties of nanometric boron delta-doped

Chapter 2 Background: Diamond as an electronic material

- diamond structures," *Journal of Applied Physics*, vol. 116, p. 083702, 2014/08/28 2014.

- [2.29] L. Ley, Electron affinity of plasma-hydrogenated and chemically oxidized diamond (100) Surfaces vol. 64, 2001.

- [2.30] W. Chen, D. Qi, X. Gao, and A. T. S. Wee, "Surface transfer doping of semiconductors," *Progress in Surface Science*, vol. 84, pp. 279-321, 2009/09/01/ 2009.

- [2.31] A. W. Oliver and B. J. Richard, "Surface conductivity on hydrogen terminated diamond," *Semiconductor Science and Technology*, vol. 18, p. S34, 2003.

- [2.32] B. J. Baliga, "Modern Power Devices" John Wiley and Sons Inc., p. 62, 1987.

- [2.33] S. M. Sze and K. K. Ng, "Physics of semiconductor devices," *John Wiley and Sons Inc.*, p. 387, 2007.

- [2.34] M. S. Tayagi, "Introduction to Semiconductor Materials and Devices," *John Wiley and Sons Inc.*, p. 492, 1992.

- [2.35] S. M. Sze and K. K. Ng, "Physics of semiconductor devices," *John Wiley and Sons Inc.*, p. 395, 2007.

- [2.36] H. Kawarada, M. Aoki, H. Sasaki, and K. Tsugawa, "Characterization of hydrogenterminated CVD diamond surfaces and their contact properties," *Diamond and Related Materials*, vol. 3, pp. 961-965, 1994/04/01/1994.

- [2.37] B. Streetman and S. Banerjee, "Solid State Electronic Devices," *Pearson*, pp. 227-233, 2005.

- [2.38] S. M. Sze and K. K. Ng, "Physics of semiconductor devices," *John Wiley and Sons Inc.*, p. 153, 2007.

- [2.39] B. Streetman and S. Banerjee, "Solid State Electronic Devices," *Pearson*, pp. 270-272, 2005.

- [2.40] S. M. Sze and K. K. Ng, "Physics of semiconductor devices," *John Wiley and Sons Inc.*, p. 234, 2007.

## 3. Literature review

This chapter begins by outlining the development of the model used to understand the surface conductivity of hydrogen terminated diamond. The first sub chapter also explores what has been achieved in the realm of improving the sheet resistance and high temperature stability of the 2DHG of hydrogen terminated diamond by investigating alternative surface electron acceptor materials.

The second sub-chapter follows the development of hydrogen-terminated diamond FETs, detailing the different surface materials used to control the surface transfer doping process which have been used to increase the performance of the FETs, as well as what has been achieved using surface transfer doping diamond FETs in the high power operating space, with particular focus placed on maximum drain current, extrinsic transconductance, off-state breakdown voltage, and stability of performance at elevated temperatures.

Finally, the chapter briefly explores what has been achieved in the development of boron doped diamond FETs.

## 3.1 Surface transfer doping

As discussed in chapter 2, surface transfer doping is the process which allows the creation of a two-dimensional hole gas (2DHG) by transfer of electrons across the hydrogen terminated diamond to acceptor materials on the surface, which leave behind mobile holes which can be used as a charge transfer layer. In this work the 2DHG is utilized to create FETs on hydrogen terminated diamond.

In 1989 M. Landstrass and K. Ravi observed that diamond grown by CVD growth terminated with hydrogen showed high surface conductivity. This effect was reported to be removed by heating the diamond films in atmosphere. At the time of the publication of this work the conductivity was thought to be due to hydrogen passivation of traps in the diamond films, which could be reversed by removal of the hydrogen termination by a high temperature anneal [3.1]. After a re-introduction to hydrogen plasma the conductivity was again observed, confirming that hydrogenation of the diamond surface played a key part in the observed conductivity.

It was not until the year 2000 that the now widely accepted model for conductivity of hydrogen terminated diamond was published by F. Maier *et al.* [3.2]. It was shown that the surface conductivity could be removed by annealing in ultra-high vacuum. This effect could

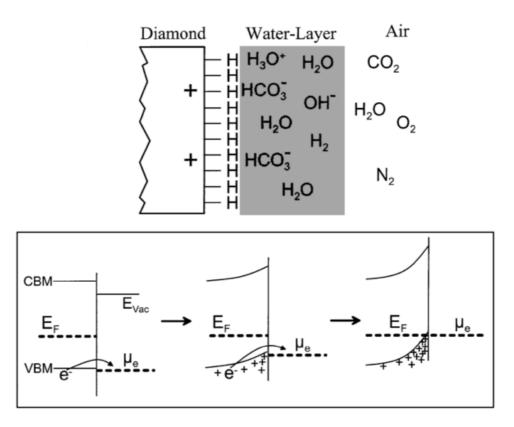

be reversed and the conductivity restored by re-exposure to normal atmosphere. If annealed above 230°C in atmosphere the effect of reducing the conductivity is irreversible. This was reported to be due to the removal of hydrogen termination of the surface and replacement with oxygen. This showed that the surface conductivity was due to both the hydrogen termination of the surface and it's interaction with atmospheric exposure. In this work a model for surface transfer doping was developed. It was proposed that due to the negative electron affinity of hydrogen terminated diamond electrons will readily leave the surface of the diamond. This negative electron affinity and it's properties of allowing unbound electrons to leave the diamond surface have been extensively explored in the past [3.3, 3.4]. If a material with an electron affinity or chemical potential larger than 4.2eV interfaces with the hydrogen terminated diamond surface electrons will leave the valence band of the diamond and leave behind holes which form a two dimensional hole gas (2DHG) near the surface of the diamond. This effect can be seen below in fig 3.1.1. It was calculated that a thin "water layer" which forms on all surfaces exposed to atmosphere would provide a layer with a chemical potential of around 4.4eV, placing it's Lowest Unoccupied Molecular Orbit (LUMO) below the valence band of hydrogen terminated diamond.

Fig 3.1.1 – Surface bending and accumulation of holes due to "water layer" on h-diamond surface proposed by F. Maier et al [3.2].

Following the publication of the model proposed by F. Maier *et al*, J. Goss *et al* reported simulations from first principles of various adsorbate layers with electron affinities close to or above 4.2eV such as  $NO_2$  and  $C_{60}$  [3.5]. In this publication Goss *et al* used local density functions to calculate the electron affinities of the adsorbate clusters. Of most interest from this paper was the demonstration of charge transfer between hydrogen terminated diamond and  $C_{60}$  fullerenes.

In the succeeding years the hypothesis of atmospheric adsorbates and hydrogen termination giving rise to surface conductivity, and the mechanism of hole transfer from diamond into the atmospheric adsorbates was investigated by M. Kubovic *et al.* The first effort was to expose hydrogen terminated diamond to NO<sub>2</sub> vapour, oxygen, and argon [3.6] and compare the sheet carrier concentration induced in each case. In this publication it was observed that exposure to NO<sub>2</sub> increased the carrier concentration in the 2DHG and exposure to oxygen and argon has little effect on the carrier concentration. It was also observed that increasing the concentration of NO<sub>2</sub> gas resulted in an increase in 2D carrier concentration up to 2.3x10<sup>14</sup> /cm<sup>2</sup>. However the concentration of carriers decreased exponentially when the diamond was exposed to normal atmospheric conditions, emphasizing the need for passivation of the H-diamond/NO<sub>2</sub> material system in order to maintain the increased carrier concentration.

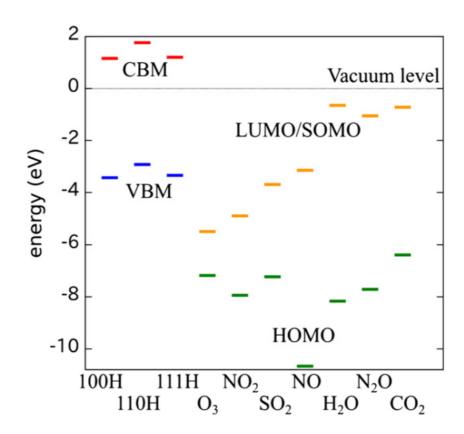

Y. Takagi *et al* [3.7] isolated the chemical composition of the previously vaguely described "atmospheric adsorbates" and calculated the LUMO and Highest Occupied Molecular Orbit (HOMO) of each. In *figure 3.1.2* it can be seen the LUMO and HOMO of various atmospheric species as well as that of hydrogen terminated diamond of each orientation (100, 110, 111). It was experimentally demonstrated that NO<sub>2</sub>, O<sub>3</sub>, SO<sub>2</sub> and NO demonstrate surface transfer doping. However, H<sub>2</sub>O, N<sub>2</sub>O and CO<sub>2</sub> show no surface transfer doping. This further promotes the hypothesis reached by Maier *et al.* It was also shown that the concentration of carriers in the diamond is dependent upon the energy level difference between the LUMO of the atmospheric adsorbate and VBM of hydrogen terminated diamond. The larger the energy difference, the more electrons are able to leave the surface of the hydrogen terminated diamond prior to equilibrium.

Fig 3.1.2 – Energy levels of hydrogen terminated diamond of orientations 100, 110 and 111 and the LUMO and HOMO levels of chemical components of atmospheric adsorbate layer from [3.7].

Following this, research groups investigated alternative materials with LUMOs lying below the valence band of hydrogen terminated diamond. Initially P. Strobel *et al.* showed success in utilizing fullerenes  $C_{60}$  and  $C_{60}F_{48}$  [3.8] to induce surface transfer doping, achieving carrier concentrations of  $10^{12}$ /cm<sup>2</sup> for  $C_{60}$  and  $10^{13}$ /cm<sup>2</sup> for  $C_{60}F_{48}$ , exceeding what had been shown with "atmospheric adsorbates". Following this it was also reported that without encapsulation these materials sublimate from the diamond surface at  $200^{\circ}C[3.9]$ . This work was followed by demonstration of the material "tetrafluoro-tetracyanoquinodimethane" (F<sub>4</sub>-TCNQ) by D. Qi *et al*, which showed a similar sheet hole density to what was achieved using  $C_{60}F_{48}$  [3.10]. These publications confirmed the simulations performed by Goss *et al* with regards to the surface transfer doping of  $C_{60}$ , and that alternative organic materials could be used to replace "atmospheric adsorbates" for the purpose of surface transfer doping hydrogen terminated diamond.

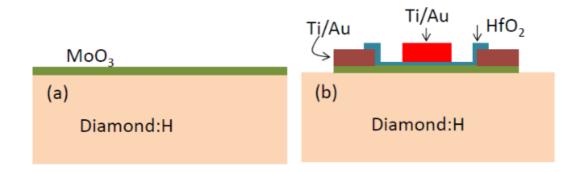

Although the demonstration of organic films was encouraging, it was also shown that they did not perform adequately at elevated temperatures without encapsulation. It was theorized that inorganic layers with electron affinities higher than 4.2eV could also be used as more thermally robust surface transfer doping layers. To this end it was demonstrated by S. Russel

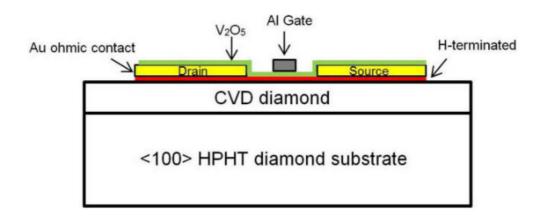

et al [3.11] that the material molybdenum trioxide (MoO<sub>3</sub>) could be utilized to surface transfer dope H-diamond. It was shown that the increased electron affinity in comparison to the potential energy of atmospheric adsorbates lead to greatly increased carrier concentration. It was reported that the carrier concentration of the sample in this work increased from  $1 \times 10^{13}$  with atmospheric adsorbates, to  $2.16 \times 10^{13}$  after deposition of MoO<sub>3</sub>. Although there was also decrease in mobility, this corresponded to a change in sheet resistance from  $9.1 \text{k}\Omega/\Box$  to  $5.6 \text{k}\Omega/\Box$ . In order to demonstrate that the MoO<sub>3</sub> is responsible for the surface transfer doping the surface of the diamond was annealed at 400 °C for 1 hour in order to remove all atmospheric adsorbates and ensure surface transfer doping was due only to the MoO<sub>3</sub>.

Following this work, M. Tordjman *et al* expanded on the demonstration of MoO<sub>3</sub> by showing that H-diamond using MoO<sub>3</sub> layers could maintain stable carrier concentrations at temperatures in excess of 300°C [3.12].

Following the publication of MoO<sub>3</sub> as a surface transfer doping medium, K. Crawford *et al* showed the surface transfer doping potential of another high electron affinity material vanadium pentoxide (V<sub>2</sub>O<sub>5</sub>) [3.13]. V<sub>2</sub>O<sub>5</sub> showed an increase in carrier concentration to 1.8x10<sup>13</sup> compared to a carrier concentration of 3x10<sup>12</sup> for atmospheric adsorbates and increased stability at elevated temperatures, with V<sub>2</sub>O<sub>5</sub> surface transfer doping remaining stable up to 250 °C.

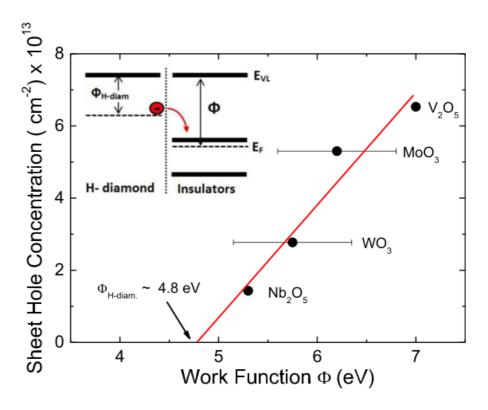

After the demonstration of high electron affinity inorganic layers as surface transfer dopants C. Verona *et al* demonstrated a comparison between MoO<sub>3</sub>, V<sub>2</sub>O<sub>5</sub> tungsten oxide (WO<sub>3</sub>), niobium oxide (NbO<sub>5</sub>), and aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) deposited by electron beam evaporation [3.14]. All of these materials exhibited surface transfer doping other than Al<sub>2</sub>O<sub>3</sub> which exhibited a higher sheet resistance than the control sample using atmospheric adsorbates after deposition. Al<sub>2</sub>O<sub>3</sub> has a low electron affinity and therefore should not induce surface transfer doping. It may be that any conductivity can attributed to atmospheric adsorbates encapsulated by the Al<sub>2</sub>O<sub>3</sub> deposition. This paper also shows a correlation between the work function of the surface transfer doping layer and the carrier concentration in the 2DHG as shown in *figure 3.1.3*. It was also reported that the mobility of charge decreases as the concentration of charge increases in the 2DHG for each of the demonstrated oxides.

Fig 3.1.3. - Relationship between the work function of some surface transfer layers and carrier concentration in diamond using these layers as shown by C. Verona et al [3.14].

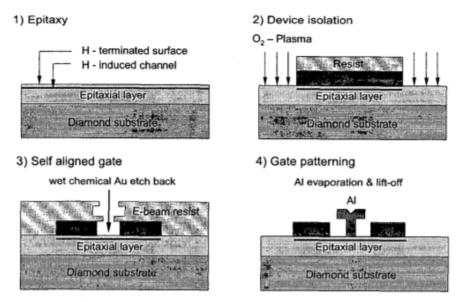

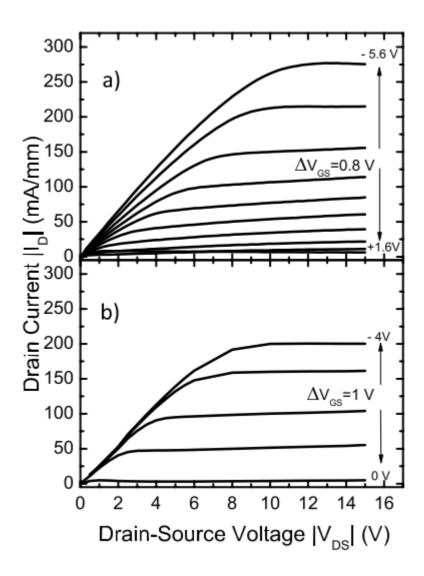

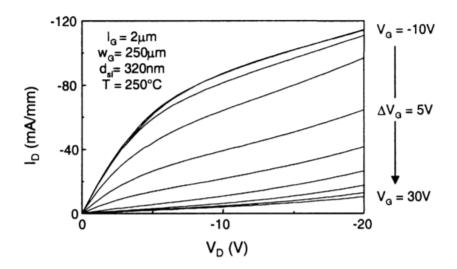

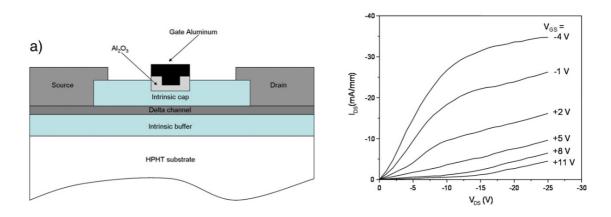

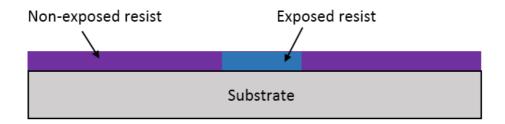

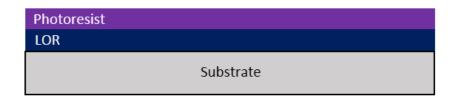

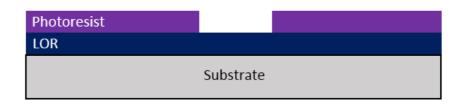

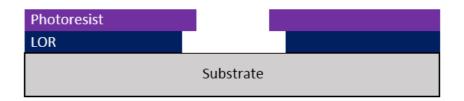

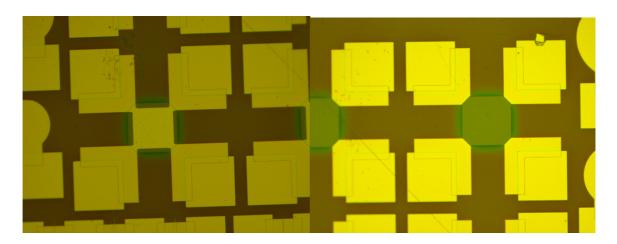

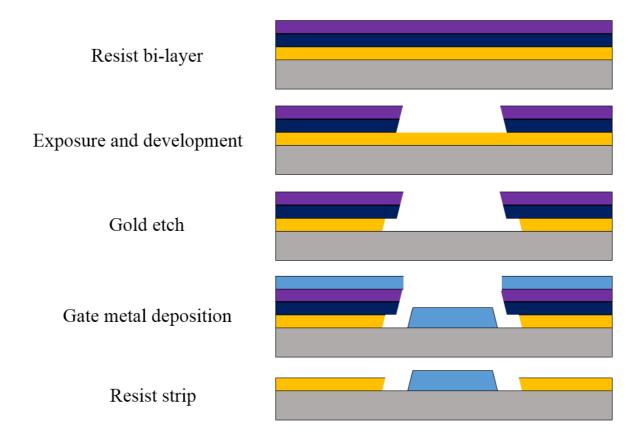

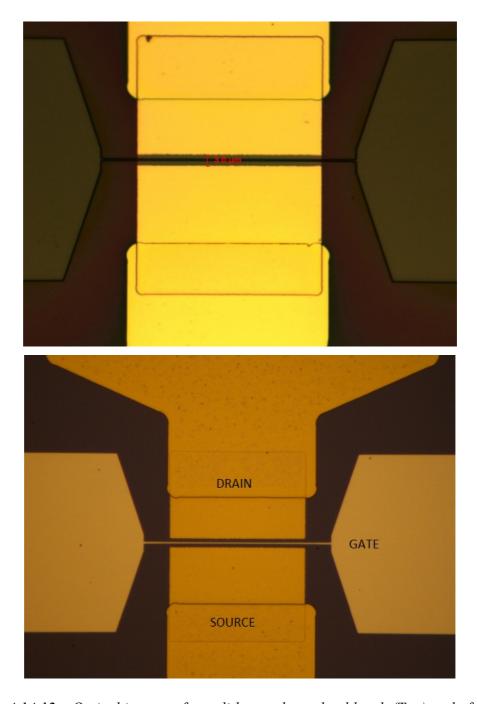

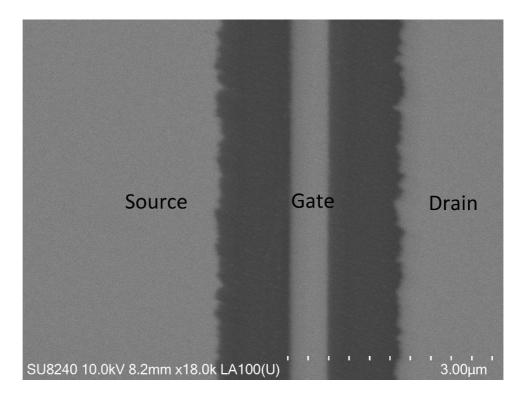

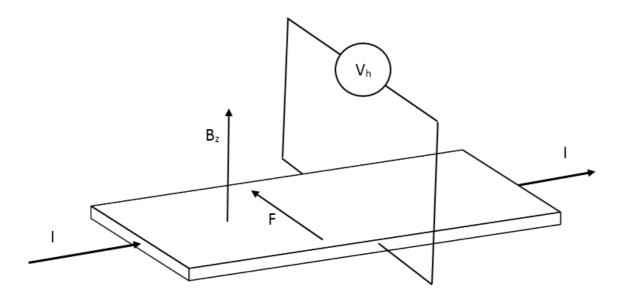

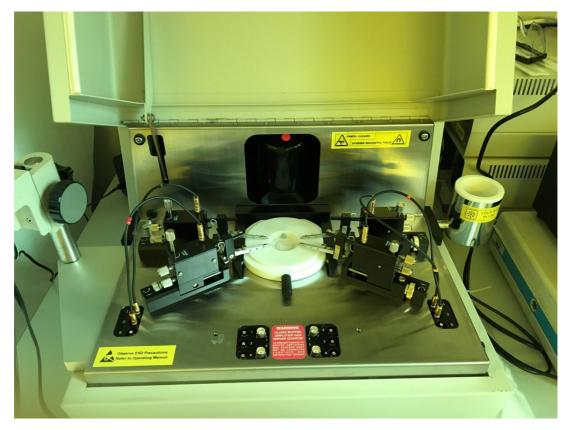

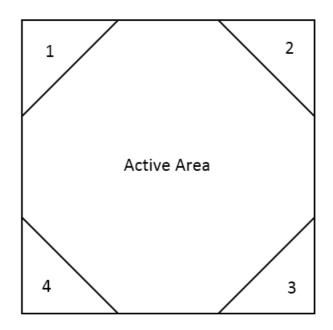

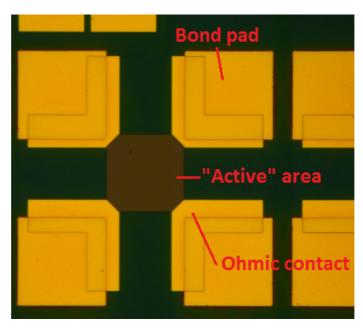

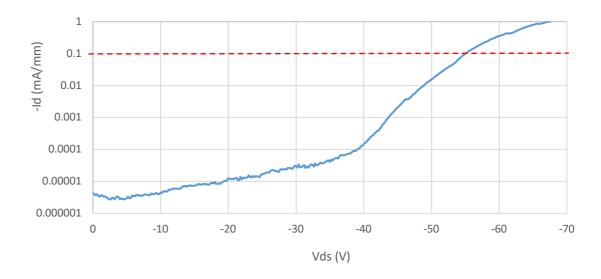

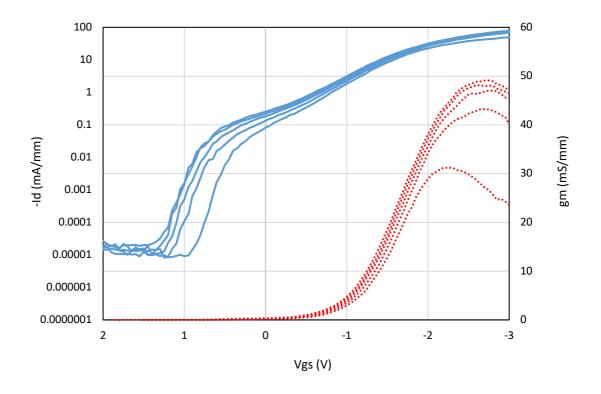

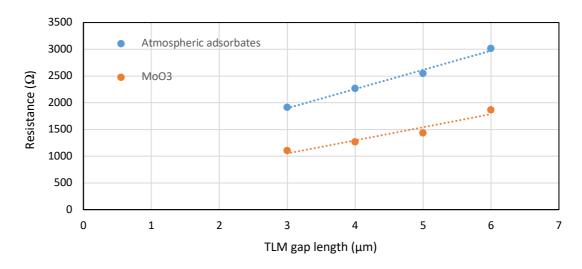

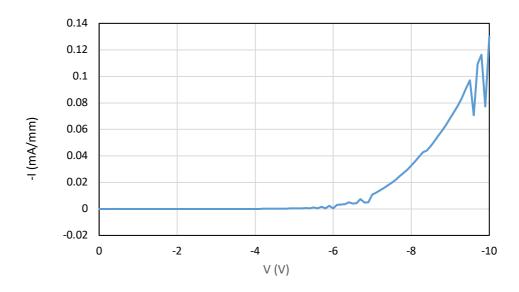

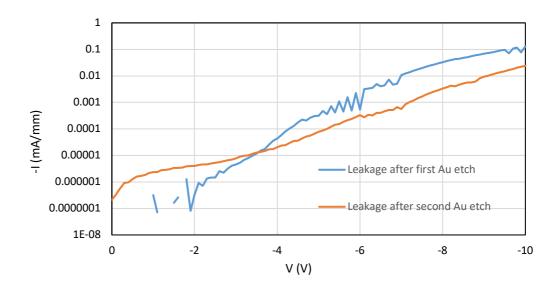

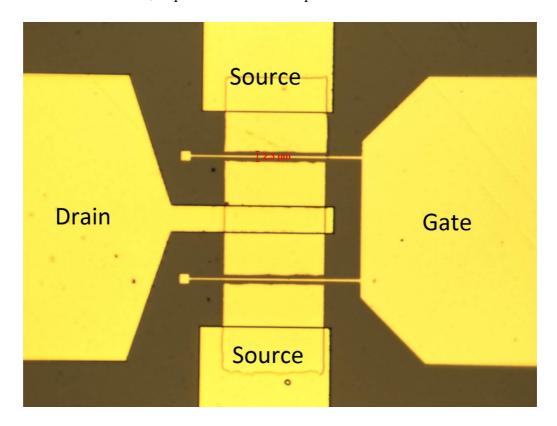

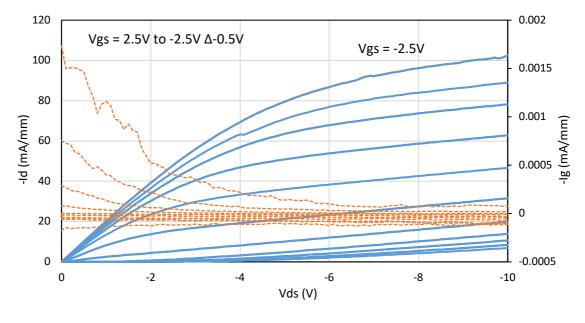

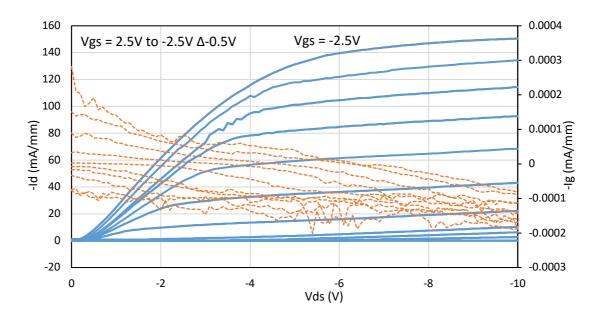

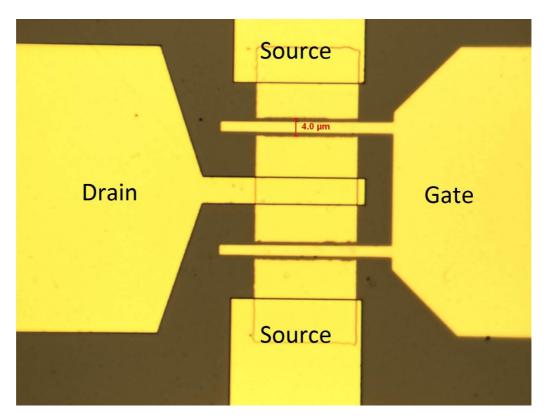

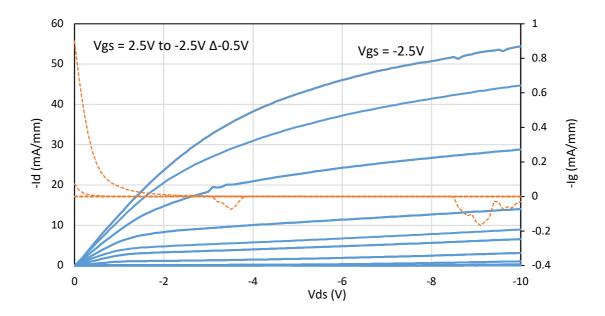

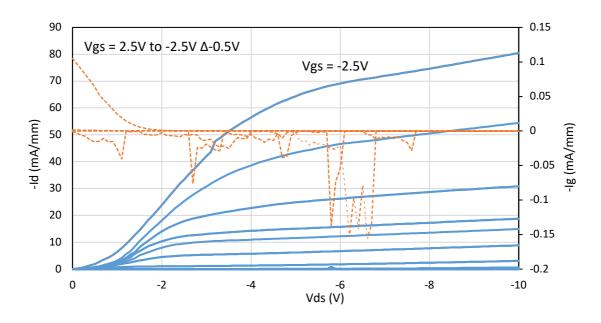

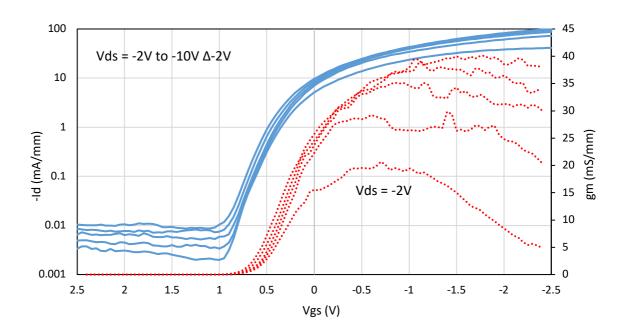

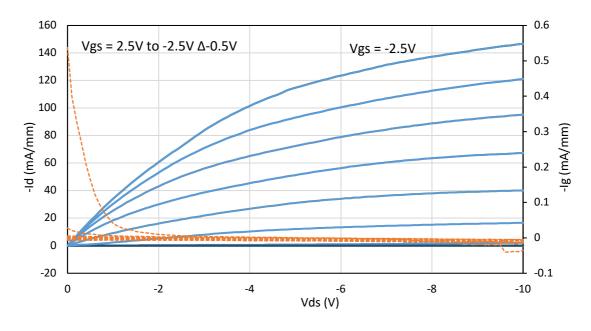

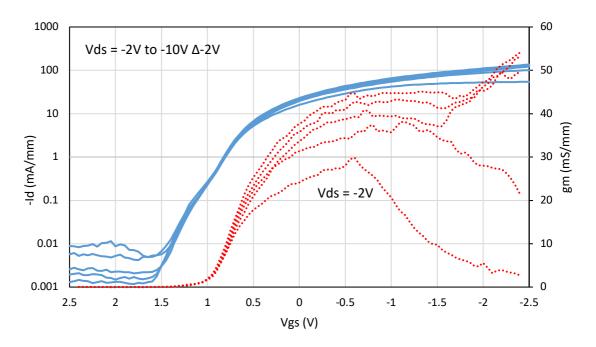

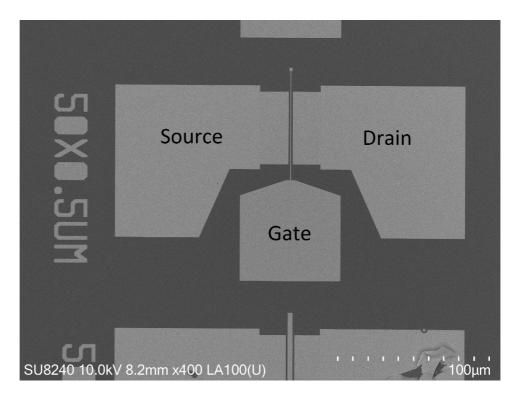

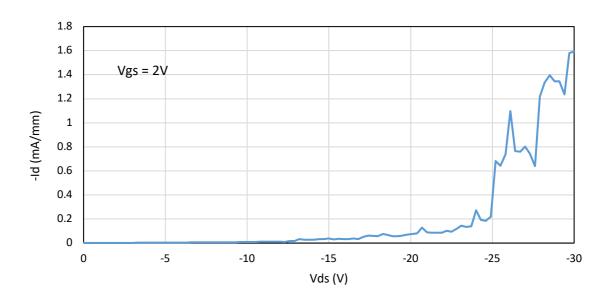

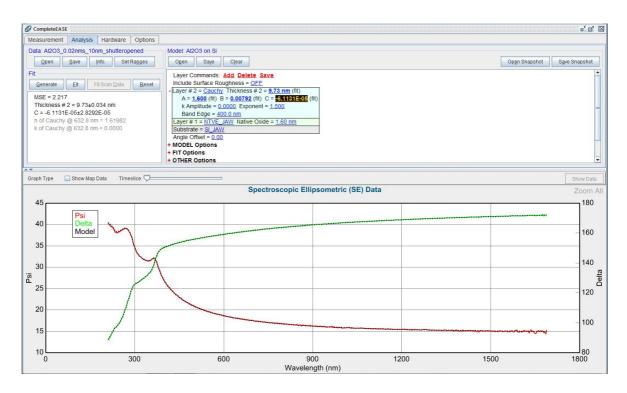

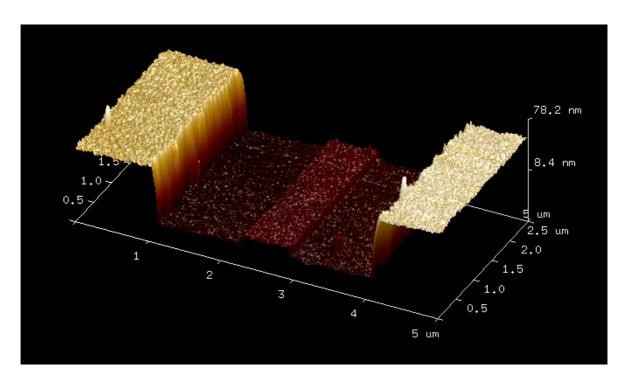

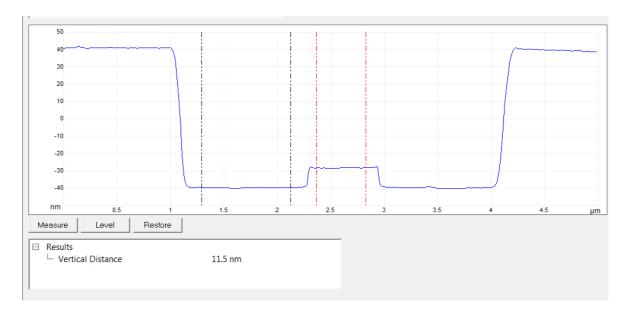

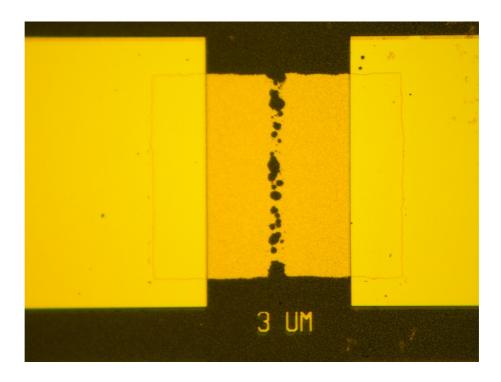

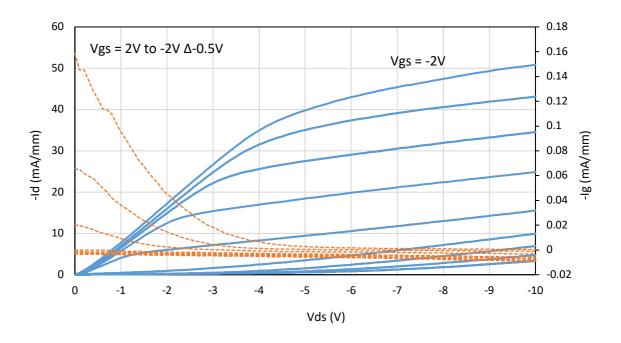

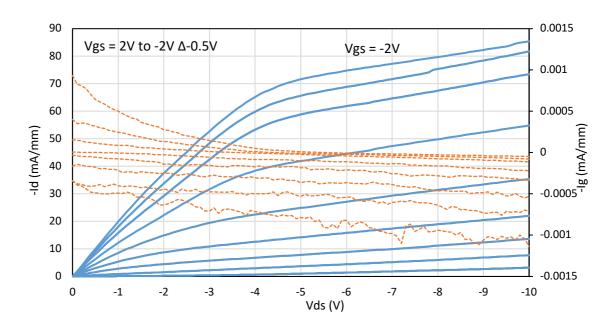

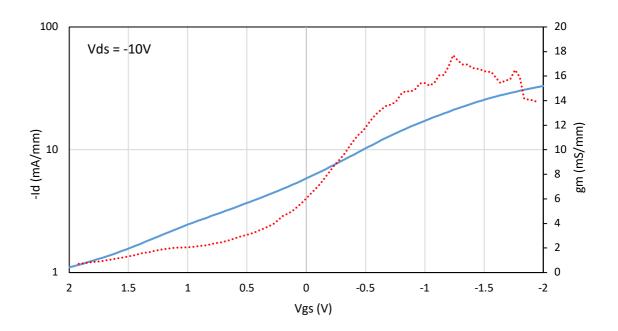

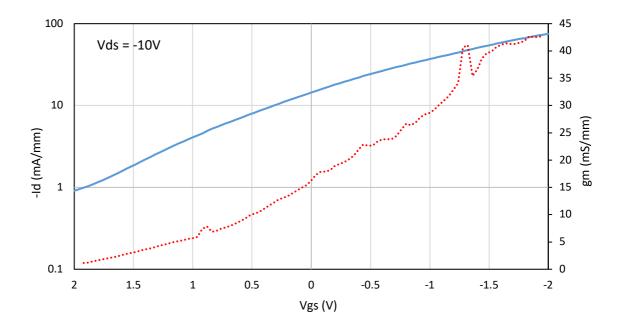

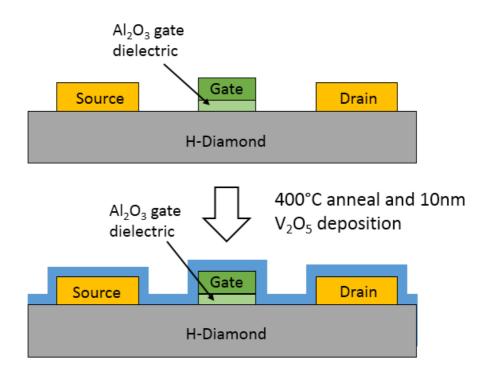

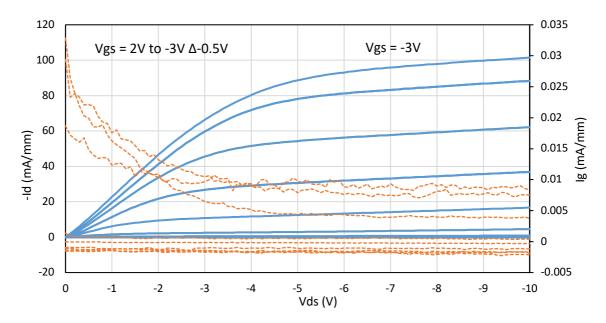

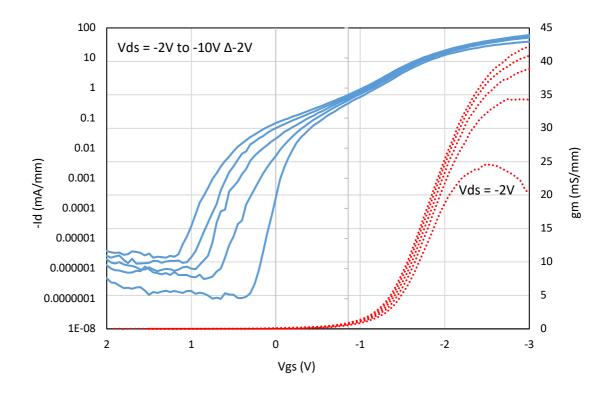

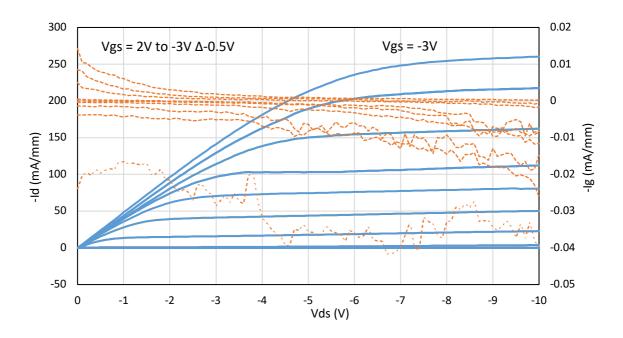

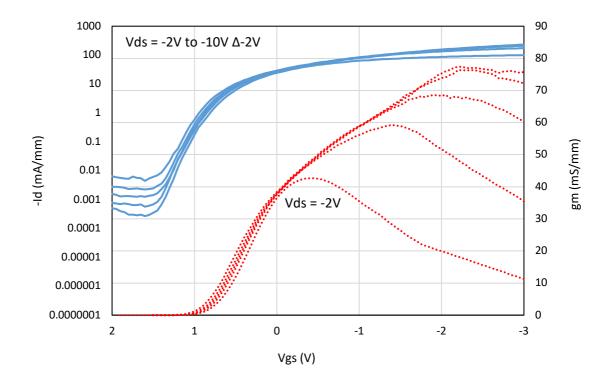

Following this work, M. Tordjman *et al* further showed the potential of WO<sub>3</sub> as a surface transfer doping oxide and introduced another potential surface transfer doping material in rhenium oxide (ReO<sub>3</sub>). In this publication it was shown that *Rafi et al* had achieved the highest reported carrier concentration in the 2DHG with WO<sub>3</sub>, reporting a carrier concentration of 4.78x10<sup>14</sup> /cm<sup>2</sup>. ReO<sub>3</sub> showed stable performance up to 450 °C in atmospheric conditions, the highest operational temperature demonstrated for surface transfer doping oxides [3.15].