Al-Khalidi, Abdullah Koutaiba (2015) *Advanced gallium nitride technology for microwave power amplifiers*. PhD thesis.

https://theses.gla.ac.uk/6785/

Copyright and moral rights for this work are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This work cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

UNIVERSITY OF GLASGOW

# Advanced Gallium Nitride Technology for Microwave Power Amplifiers

by

Abdullah Koutaiba Al-Khalidi

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

ELECTRONICS AND NANOSCALE ENGINEERING DIVISION SCHOOL OF ENGINEERING

September 2015

## Abstract

Gallium nitride (GaN) based technology has been heavily researched over the past two decades due to its ability to deliver higher powers and higher frequencies that are demanded by the market for various applications. One of GaN's main advantages lies in its ability to form heterojunctions to wider bandgap materials such as Aluminium Gallium Nitride (AlGaN) and Aluminium Nitride (AlN). The heterostructure results in the formation of the so called 2 dimensional electron gas (2DEG), which exhibits high electron densities of up to  $6 \times 10^{13}$  cm<sup>-2</sup> and high electron mobilities of up to 2000 cm<sup>2</sup>/V·s that enable the devices to support high current densities. Furthermore, it supports very high breakdown fields of 3.3 MV/cm due to its wide bandgap of 3.4 eV. The main objective of this work was to further advance the transistor technology using simple, cost effective and reliable techniques.

The AlN/GaN material system exhibits higher sheet carrier concentrations compared to the conventional ternary AlGaN barrier, but introduces additional challenges due to its reduced thickness of 2-6 nm compared to 18-30 nm of AlGaN. The additional challenges of the thin AlN binary barrier include strain relaxation, high gate leakage currents and high Ohmic contact resistances due to its high bandgap of 6.2 eV. In this work, a thin (5 nm) in-situ SiN<sub>x</sub> passivation layer was employed to reduce the strain relaxation, reduce gate leakage currents and improve Ohmic contacts resistances. The optimised Ohmic contact annealing condition resulted in an Ohmic contact resistance of 0.4  $\Omega$ ·mm and a sheet resistance of 300  $\Omega/\Box$ . This result opens the door for realising microwave power amplifier circuits using the AlN/GaN material system for the first time.

The conventional dry etching techniques used to achieve device isolation for GaN based transistor technologies results in a three dimensional device structure, the mesa structure. This leads to high leakage currents which impact the noise performance and breakdown voltages of the devices. A new approach to achieve device isolation that employs an oxygen plasma treatment was demonstrated in this project. It results in a planar device structure with devices exhibiting one order of magnitude less gate leakage currents compared to mesa isolated devices. The achieved leakage currents of 1  $\mu$ A/mm are comparable to those which employed the more complex and expensive ion implantation technique.

As GaN growth and device processing reaches maturity levels, thermal performance of the devices becomes the main limitation to achieving higher powers and higher frequencies since increased device self heating has a negative impact on the device performance. In this project, novel thermal management techniques were developed and include the use of dry etching techniques to create thermal vias that are located within few microns of the heat source in the semiconductor channel. The vias are then filled with copper, a metal with high thermal conductivity, that is in contact with the substrate to efficiently transport the heat from the channel into the SiC substrate. The thermally efficient fabricated devices could sustain a DC power density of 38 W/mm without degradation compared to standard devices that exhibit only 15 W/mm at 40 V.

# Acknowledgments

I thank Allah for giving me the strength and energy to complete the project...

I would like to thank the Defence Science and Technology Laboratories (DSTL) for funding this project. I thank my supervisor Dr. Edward Wasige for putting his faith in me, for giving me the opportunity to work in the exciting field of GaN technology and for his support, guidance and useful discussions throughout the project. I also thank Prof. Jim Wilson and Dr. Kevin Martin of DSTL for their input and advice during the project.

I would like to thank Dr. Ata Khalid for his wise words, useful tips and continuous encouragement.

I would like to thank my groupmates: Sanna Taking, Douglas Macfarlane, Salah Sharabi and Raphael Brown for helping me get started with my project and their support during the project. Many thanks to Marco Silvestri, from Bristol University for his help in doing pulsed IV measurements on my devices.

I would like to thank my friends Sankar Peralagu, Lourdes Ferre Llin, Vasileios Papageorgiou, Kevin Gallacher, James Grant and Fiona Grant for their support and fruitful discussions throughout my project.

Many thanks goes to the JWNC staff for their efforts in maintaining the day to day operation of the cleanroom.

Finally, I thank my family who were very supportive during my PhD project. Many thanks goes to my lovely wife Aysha who I fell in love with towards the end of my PhD.

## Patents

- 1. Patent on thermally efficient devices (under consideration).

- 2. Patent on device isolation (under consideration).

# List of publications

- 1. <u>A. Al-Khalidi</u>, A. Khalid and E. Wasige, "AlN/GaN HEMT technology with insitu SiN<sub>x</sub> passivation," *IEEE PRIME Conference*, Glasgow, UK, July 2015.

- <u>A. Al-Khalidi</u>, K. Gallacher, A. Khalid, D. Paul and E. Wasige, "0.25 Ω·mm Ohmic contacts to AlN/GaN HEMT structure with in-situ SiN passivation," 7th Space Agency - MOD Workshop on Wide Bandgap Semiconductors and Components, ESA/ESTEC, Frascati, Italy, September 2014.

- <u>A. Al-Khalidi</u>, K. Gallacher, A. Khalid, D. Paul and E. Wasige, "Effect of annealing time and temperature on Ohmic contacts to AlN/GaN HEMT structure with in-situ SiN passivation," UK Nitrides Consortium, Sheffield, July 2014.

- A. Al-Khalidi, A. Khalid and E. Wasige "Comparison of AlGaN/GaN HEMTs on silicon, sapphire and SiC substrates - a thermal perspective," *Compound Semiconductor Week*, Montpellier, France, May 2014.

- <u>A. Al-Khalidi</u>, S. Taking and E. Wasige, "AlN/GaN HEMTs with SiN passivation and recessed Ohmics," 6th Space Agency - MOD Workshop on Wide Bandgap Semiconductors and Components, ESA/ESTEC, Noordwijk, the Netherlands, October 2012.

- <u>A. Al-Khalidi</u>, D. Macfarlane and E. Wasige, "Self-aligned recessed Ohmic contacts for GaN-based High Electron Mobility Transistors (HEMTs)," UK Nitrides Consortium, Sheffield, July 2012.

- R. Brown, D. Macfarlane, <u>A. Al-Khalidi</u>, X. Li, G. Ternent, H. Zhou, I. Thayne and E. Wasige, "A sub-critical barrier thickness normally-off AlGaN/GaN MOS-HEMT," *IEEE Electron Device letters*, vol. 35, pp. 906-908, September 2014.

- R. Brown, <u>A. Al-Khalidi</u>, D. Macfarlane, S. Taking, G. Ternent, I. Thayne and E. Wasige, "Novel high performance AlGaN/GaN based enhancement-mode metal-oxide-semiconductor high electron mobility transistor," *Physica Status Solidi*, vol. 11, no. 3-4, pp. 844-847, January 2014.

- J. Möreke, M. Uren, S. Novikov, C. Foxon, S. Hosseini-Vajargah, D. Wallis, C. Humphreys, S. Haigh, <u>A. Al-Khalidi</u>, E. Wasige, I. Thayne and M. Kuball, "Investigation of the GaN-on-GaAs interface for vertical power device applications," *Journal of Applied Physics*, vol. 116, pp. 014502, January 2014.

- X. Li, G. Ternent, <u>A. Al-Khalidi</u>, K. Floros, E. Wasige and I. Thayne, "Low temperature Ohmic contact realisation with AlGaN/GaN structure on Si substrate through RIE recess etching in SiCl<sub>4</sub> chemistry," UK Nitrides Consortium, Sheffield, July 2014.

- S. Faramehr, <u>A. Al-Khalidi</u>, A. Khalid, E. Wasige, P. Igić, and K. Kalna, "Device simulation and optimization of i-GaN capped AlGaN/AlN/GaN HEMT," UK Nitrides Consortium, Sheffield, July 2014.

- R. Brown, <u>A. Al-Khalidi</u>, D. Macfarlane, S. Taking and E. Wasige, "A novel high performance AlGaN/GaN based enhancement-mode metal-oxide-semiconductor high electron mobility transistor," *International Conference on Nitride Semiconductors*, Washington, August 2013.

- R. Brown, <u>A. Al-Khalidi</u>, D. Macfarlane, S. Taking, G. Ternent, I. Thayne and E. Wasige, "A normally-off AlGaN/GaN HEMT technology," UK Nitrides Consortium, Sheffield, July 2013.

- R. Brown, <u>A. Al-Khalidi</u>, G. Ternent, I. Thayne and E. Wasige, "A normallyoff AlGaN/GaN MOSHEMT technology," *The 22nd European Workshop on Het*erostructure Technology, Glasgow, September 2013.

- J. Sinclair, R. Brown, <u>A. Al-Khalidi</u> and E. Wasige, "Fabrication and characterisation of normally-off GaN-based MOS-HEMTs," *The 7th Institution of Engineering and Technology International Conference on Power Electronics, Machines and Drives*, Manchester, April 2014.

# Contents

| List of Figures | x   |

|-----------------|-----|

| List of Tables  | xv  |

| Symbols         | xvi |

| 1 | Intr | oducti | on          |                                         | 1    |

|---|------|--------|-------------|-----------------------------------------|------|

|   | 1.1  | Overv  | iew         |                                         | . 1  |

|   | 1.2  | Proble | em statem   | ent                                     | . 3  |

|   |      | 1.2.1  | Ohmic c     | ontacts to AlN/GaN HEMT material system | . 3  |

|   |      | 1.2.2  | Device is   | solation for GaN-based HEMTs            | . 4  |

|   |      | 1.2.3  | Thermal     | management on AlGaN/GaN HEMTs           | . 5  |

|   | 1.3  | Resear |             | ives                                    |      |

|   | 1.4  | Thesis | structure   | 9                                       | . 7  |

| 2 | Gal  | N HEN  | IT Theo     | ry                                      | 9    |

|   | 2.1  | Introd | uction      |                                         | . 9  |

|   | 2.2  | Polari | sation in ( | GaN HEMT                                | . 9  |

|   |      | 2.2.1  | Spontan     | eous polarisation                       | . 10 |

|   |      | 2.2.2  | Piezoele    | ctric polarisation                      | . 11 |

|   |      | 2.2.3  | Device e    | ngineering using polarisation charges   | . 11 |

|   | 2.3  | Basic  | GaN HEM     | AT-substrates and growth                | . 13 |

|   |      | 2.3.1  | Substrat    | e                                       | . 14 |

|   |      |        | 2.3.1.1     | Silicon carbide (SiC)                   | . 15 |

|   |      |        | 2.3.1.2     | Silicon                                 | . 15 |

|   |      |        | 2.3.1.3     | Sapphire                                | . 15 |

|   |      |        | 2.3.1.4     | Freestanding GaN                        | . 16 |

|   |      |        | 2.3.1.5     | CVD Diamond                             | . 16 |

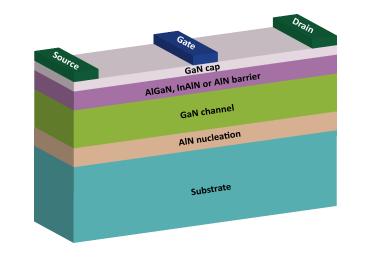

|   |      | 2.3.2  | GaN-bas     | ed HEMT structure                       | . 16 |

|   |      |        | 2.3.2.1     | Nucleation layer                        | . 17 |

|   |      |        | 2.3.2.2     | Channel layer                           | . 17 |

|   |      |        | 2.3.2.3     | Barrier layer                           | . 17 |

|   |      | 2.3.3  | Cap laye    | r                                       | . 18 |

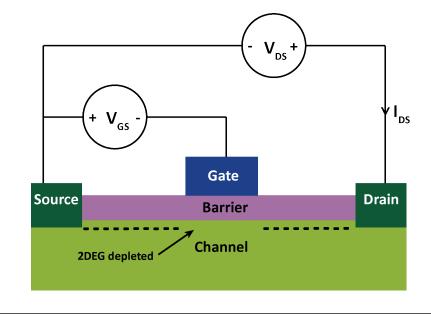

|   | 2.4  | Princi | ple of ope  | ration of GaN HEMTs                     | . 18 |

|   | 2.5  | Summ   | arv         |                                         | 22   |

| 3 | Gal   | N HEMT Device Fabrication                         | <b>23</b> |

|---|-------|---------------------------------------------------|-----------|

|   | 3.1   | Epitaxial material growth                         | 23        |

|   |       | 3.1.1 MOCVD                                       | 23        |

|   |       | 3.1.2 MBE                                         | 24        |

|   | 3.2   | Lithography                                       | 24        |

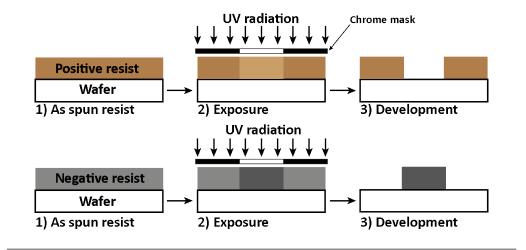

|   |       | 3.2.1 Photolithography                            | 24        |

|   |       | 3.2.2 Electron-beam lithography                   | 25        |

|   |       | 3.2.3 Photo-resists                               | 25        |

|   | 3.3   | Metallisation                                     | 27        |

|   |       | 3.3.1 Evaporation                                 | 27        |

|   |       | 3.3.2 Sputtering                                  | 27        |

|   |       | 3.3.3 Electroplating                              | 28        |

|   | 3.4   | Etching                                           | 29        |

|   |       | 3.4.1 Wet etching                                 | 30        |

|   |       | 3.4.2 Dry etching                                 | 30        |

|   | 3.5   | HEMT process flow                                 | 31        |

|   |       | 3.5.1 Mask design                                 | 31        |

|   |       | 3.5.2 Ohmic contact formation                     | 32        |

|   |       | 3.5.3 Mesa isolation                              | 33        |

|   |       | 3.5.4 Gate metallisation                          | 33        |

|   |       | 3.5.5 Bondpad metallisation                       | 33        |

|   | 3.6   | Summary                                           | 34        |

| 4 | Ohr   | mic Contacts on GaN-Based Transistor Material     | 35        |

|   | 4.1   | Introduction                                      |           |

|   | 4.2   | Metal-semiconductor interface theory              |           |

|   |       | -                                                 | 37        |

|   |       | 4.2.2 Ohmic contacts theory                       | 37        |

|   | 4.3   | Transmission line model                           | 38        |

|   |       | 4.3.1 Linear Transmission Line Model (LTLM)       | 38        |

|   |       | 4.3.2 Circular Transmission Line Model (CTLM)     |           |

|   | 4.4   | Literature review of GaN-based Ohmic contacts     |           |

|   | 4.5   | Ohmic contact optimisation on AlGaN/GaN           | 44        |

|   | 4.6   |                                                   | 48        |

|   | 4.7   | Device performance using optimised Ohmic contacts | 50        |

|   |       |                                                   | 50        |

|   |       |                                                   | 54        |

|   | 4.8   |                                                   | 56        |

| 5 | Дет   | vice Isolation Using Oxygen Plasma                | 57        |

| 0 | 5.1   |                                                   | 57        |

|   | 5.2   |                                                   | 57        |

|   | 9.2   |                                                   | 58        |

|   |       |                                                   | 59        |

|   |       |                                                   | 59        |

|   | 5.3   |                                                   | 60        |

|   | 5.4   | Mesa and oxygen plasma isolation: process details |           |

|   | ~ ~ ~ | r-boost double                                    |           |

|   |            | 5.4.1 Mesa isolation  | n process                               | 61  |

|---|------------|-----------------------|-----------------------------------------|-----|

|   |            | 5.4.2 Oxygen plasm    | na treatment                            | 62  |

|   | 5.5        | Experimental results  |                                         | 64  |

|   |            | 5.5.1 DC isolation    |                                         | 64  |

|   |            | 5.5.2 RF isolation    |                                         | 69  |

|   | 5.6        | Summary and discus    | sion                                    | 69  |

| 6 | The        | rmal Management       | of GaN HEMTs                            | 71  |

|   | 6.1        | Introduction          |                                         |     |

|   | 6.2        | Thermal consideration | ons for GaN HEMTs                       | 71  |

|   | 6.3        | Review of thermal m   | nanagement techniques for GaN HEMTs     |     |

|   | 6.4        |                       | on silicon, sapphire and SiC substrates |     |

|   | 6.5        |                       | ents                                    |     |

|   | 6.6        |                       | anagement approach                      |     |

|   | 6.7        |                       |                                         |     |

|   | 6.8        |                       | and experimental results                |     |

|   |            |                       | of nitride epi-layers                   |     |

|   |            |                       | 1g                                      |     |

|   |            |                       | pration                                 |     |

|   |            |                       | ering                                   |     |

|   |            |                       | coplating                               |     |

|   | <b>C O</b> |                       | vaporation                              |     |

|   | 6.9        |                       | grated heat sinks                       |     |

|   |            |                       | ery devices                             |     |

|   | 6 10       | · · ·                 | · · · · · · · · · · · · · · · · · · ·   |     |

|   | 0.10       | Summary               |                                         | 101 |

| 7 | Con        | clusions and Futur    |                                         | 108 |

|   | 7.1        |                       | lN/GaN HEMTs                            |     |

|   | 7.2        |                       | g oxygen plasma                         |     |

|   | 7.3        | Thermal managemen     | nt on AlGaN/GaN HEMTs                   | 110 |

|   |            |                       |                                         |     |

| A |            | Based HEMT De         |                                         | 111 |

|   | A.1        |                       | n using photolithography $\ldots$       |     |

|   |            |                       | $\operatorname{ing}$                    |     |

|   |            |                       | on                                      |     |

|   |            |                       | ice isolation using mesa isolation      |     |

|   |            |                       | ice isolation using oxygen plasma       |     |

|   |            |                       |                                         |     |

|   |            |                       |                                         |     |

|   |            |                       | etching                                 |     |

|   |            |                       | sink sputtering                         |     |

|   |            |                       | sink electroplating                     |     |

|   |            |                       | eat-sink evaporation                    |     |

|   | A.2        |                       | n using E-beam lithography              |     |

|   |            |                       |                                         |     |

| A.2.1 | E-beam alignment markers |

|-------|--------------------------|

| A.2.2 | Ohmic contacts           |

| A.2.3 | Device isolation         |

| A.2.4 | T-Gate process flow      |

| A.2.5 | Bondpads                 |

|       |                          |

## Bibliography

ix

# List of Figures

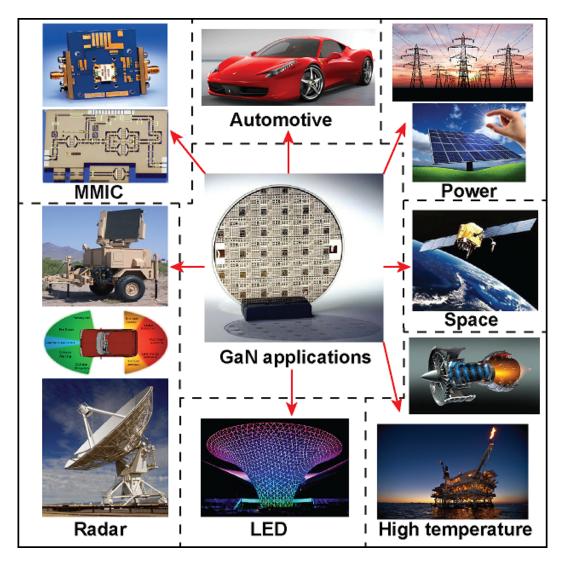

| 1.1  | Applications of GaN technology.                                                                                                                      | 3  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

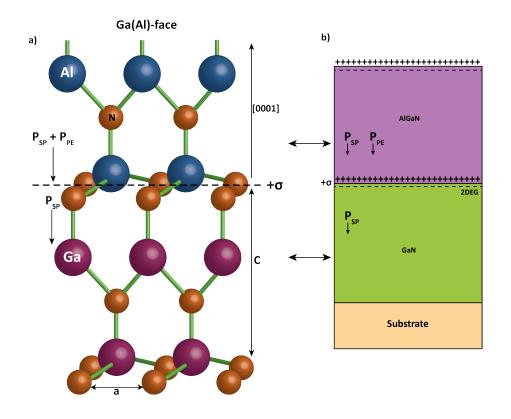

| 2.1  | Illustration of a) Ga(Al)-face crystal structure and b) polarisation induced sheet charge density and direction of the spontaneous and piezoelectric |    |

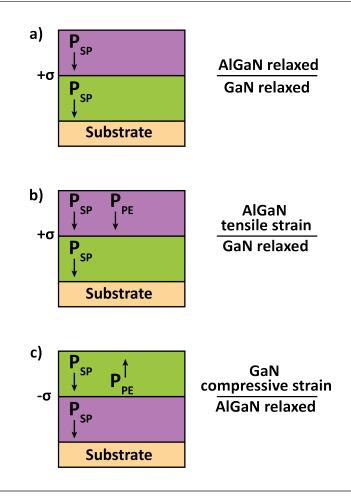

| 2.2  | polarisation in Ga-face strained AlGaN/GaN heterostructure Polarisation charges a) relaxed AlGaN/GaN, b) tensile strained AlGaN                      | 10 |

|      | on a relaxed GaN and c) compressively strained GaN on a relaxed AlGaN.                                                                               | 12 |

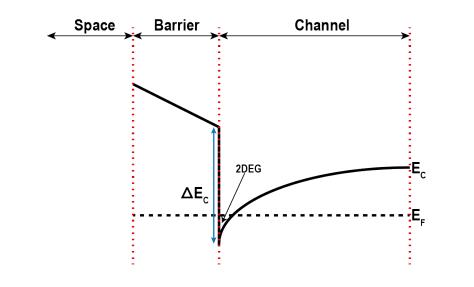

| 2.3  | Band diagram of a GaN HEMT.                                                                                                                          | 13 |

| 2.4  | Cross-section of a basic GaN HEMT structure.                                                                                                         | 14 |

| 2.5  | Illustration of HEMT operation principle and biasing.                                                                                                | 19 |

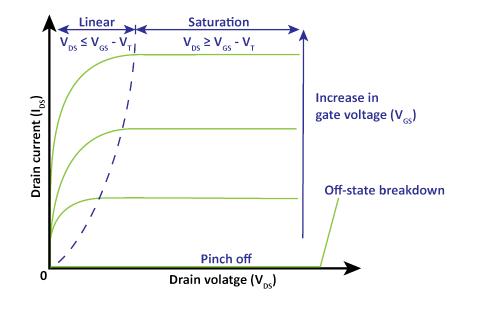

| 2.6  | Output IV characteristic of a typical GaN HEMT.                                                                                                      | 20 |

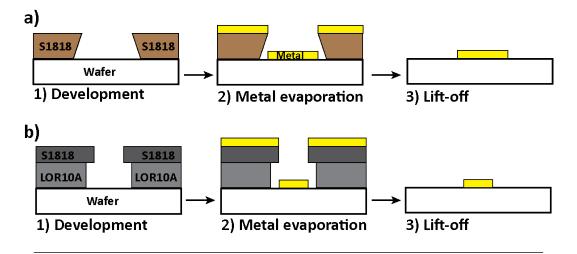

| 3.1  | Positive and negative photo-resist spinning and development.                                                                                         | 26 |

| 3.2  | Illustration of a lift-off process flow using a) a single layer photo-resist                                                                         |    |

|      | and b) a bilayer photo-resist.                                                                                                                       | 26 |

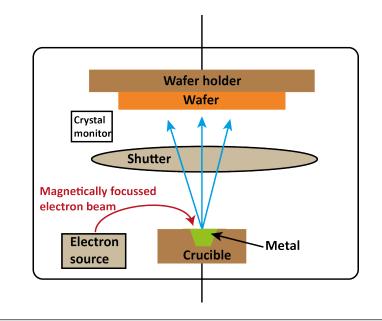

| 3.3  | Illustration of the metal electron beam evaporation mechanism                                                                                        | 28 |

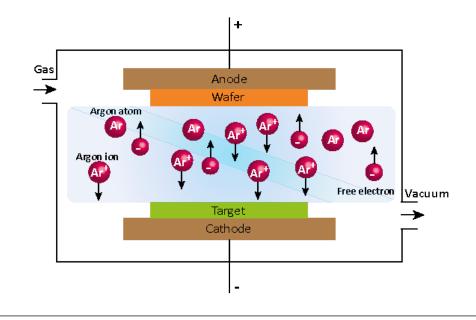

| 3.4  | Illustration of the metal sputtering mechanism.                                                                                                      | 29 |

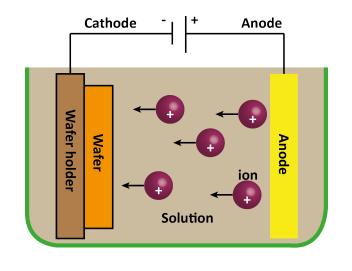

| 3.5  | Illustration of the metal electroplating process.                                                                                                    | 30 |

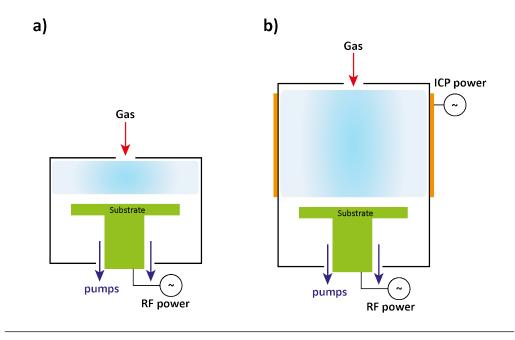

| 3.6  | Illustration of a) RIE system, b) ICP system                                                                                                         | 31 |

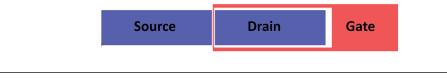

| 3.7  | Layout of a DC device                                                                                                                                | 32 |

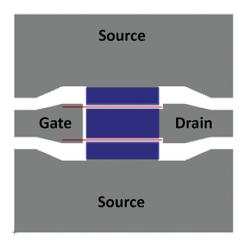

| 3.8  | Layout of an RF device.                                                                                                                              | 33 |

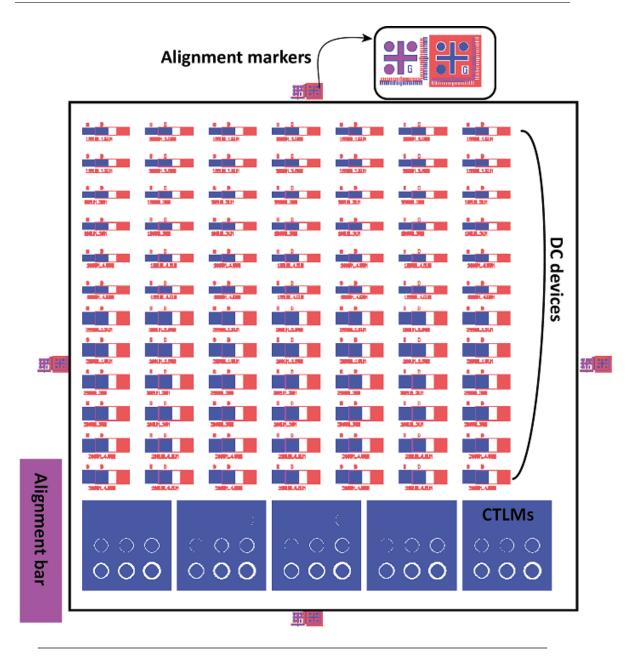

| 3.9  | Complete photolithography mask for DC devices which includes CTLM                                                                                    |    |

|      | structures and alignment markers.                                                                                                                    | 34 |

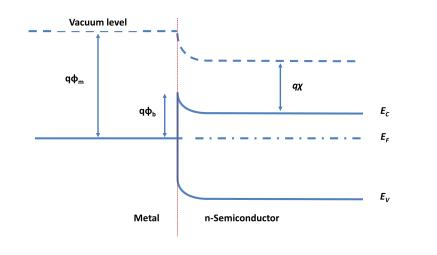

| 4.1  | Energy-band diagram of metal-semiconductor (n-type) contact.                                                                                         | 36 |

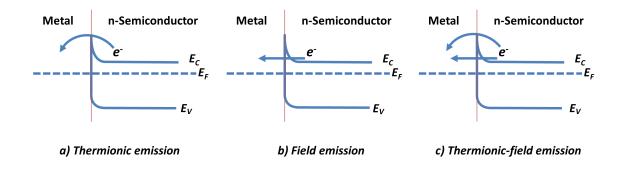

| 4.2  | The three types of emissions in a semiconductor, a) thermionic emission,                                                                             |    |

|      | b) field emission and c) thermionic field emission.                                                                                                  | 37 |

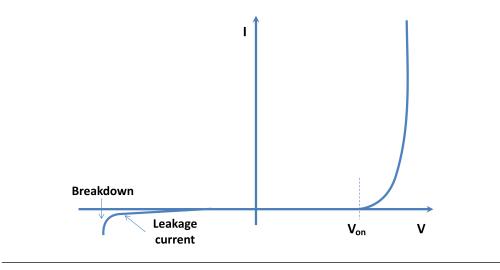

| 4.3  | Typical IV characteristics for a Schottky contact.                                                                                                   | 38 |

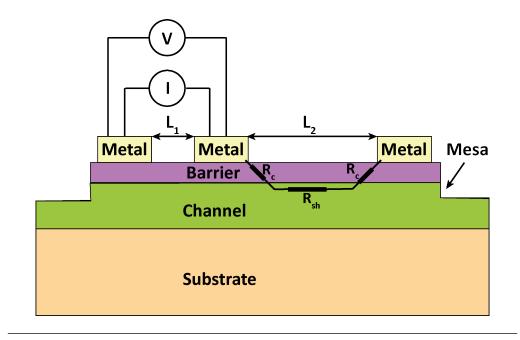

| 4.4  | Cross section of an LTLM structure.                                                                                                                  | 39 |

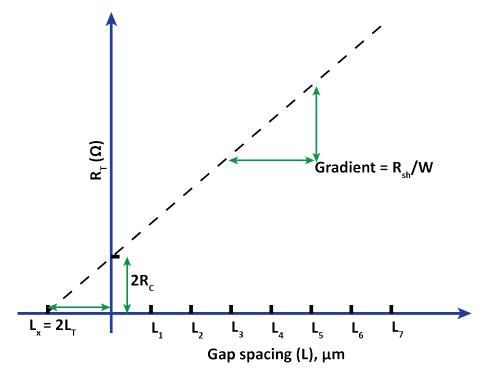

| 4.5  | Total resistance versus the varying gap spacings.                                                                                                    | 39 |

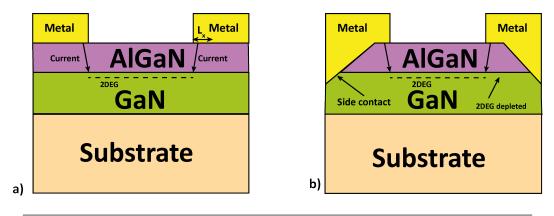

| 4.6  | Current flow in an LTLM structure (a) non-isolated and (b) isolated struc-                                                                           |    |

|      | tures                                                                                                                                                | 40 |

| 4.7  | Illustration of a) Reeves concentric circular contacts and b) Marlow's                                                                               |    |

|      | enclosed contacts                                                                                                                                    | 41 |

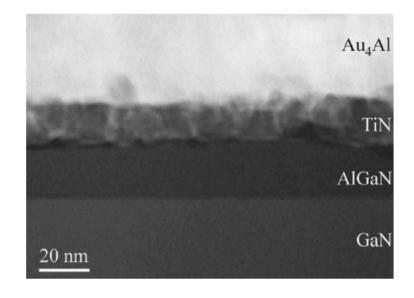

| 4.8  | TEM of TiN formed after high temperature annealing                                                                                                   | 42 |

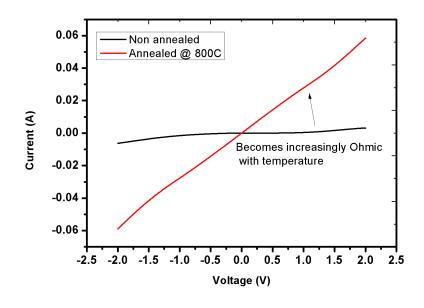

| 4.9  | Measured TLM pattern before and after annealing                                                                                                      | 43 |

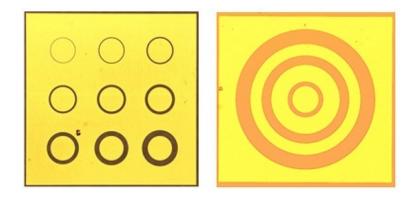

| 4.10 | Micrograph of a fabricated CTLM structure.                                                                                                           | 45 |

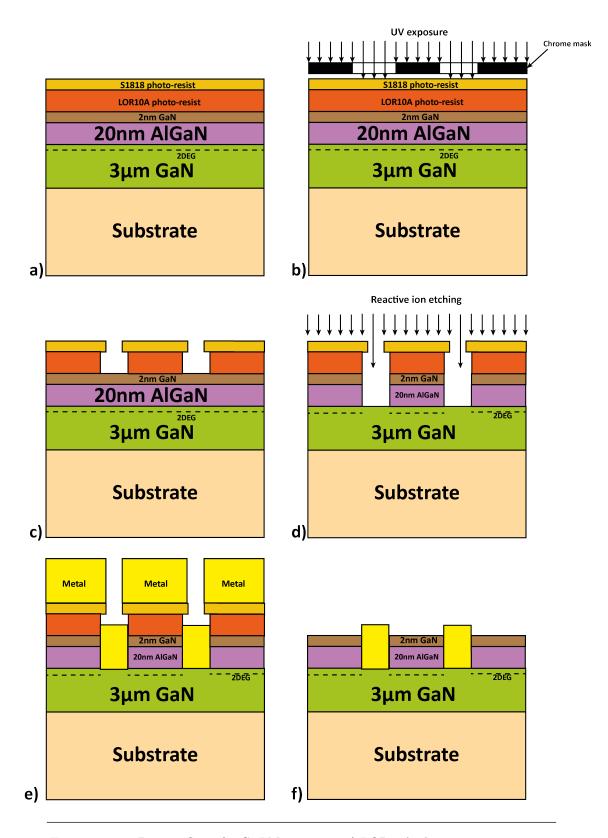

| 4.11 | Process flow of a CTLM structure, a) LOR10A photo-resist spinning fol-<br>lowed by S1818 photo-resist spinning, b) UV exposure for 6 seconds, c) |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | development using MF319 for 2:30 min:sec, d) reactive ion etching using $SiCl_4$ with a power of 75 W, flow rate and pressure of 30 sscm and 30  |            |

|      | mT, respectively, e) metallisation of Ti/Al/Ni/Au (30/180/40/100 nm)                                                                             |            |

|      | and f) lift-off using 1165 photo-resist stripper.                                                                                                | 46         |

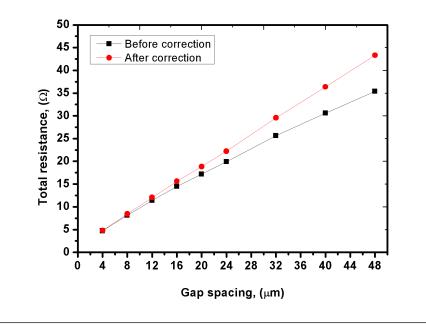

| 4.12 | Measured resistance versus gap spacing                                                                                                           | 47         |

| 4.13 | Illustration of the a) non-recessed and b) recessed Ohmic contacts after                                                                         |            |

|      | annealing. Both contacts exhibited similar contact resistances.                                                                                  | 47         |

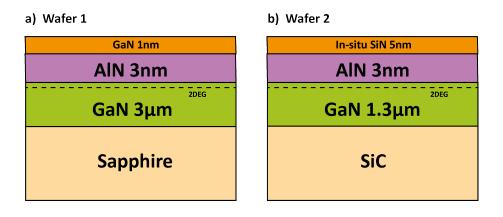

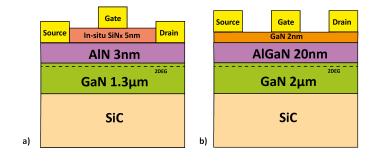

| 4.14 | Cross section of a) an MBE grown AlN/GaN HEMT on sapphire and b)                                                                                 |            |

|      | an MOCVD grown AlN/GaN HEMT on SiC.                                                                                                              | 48         |

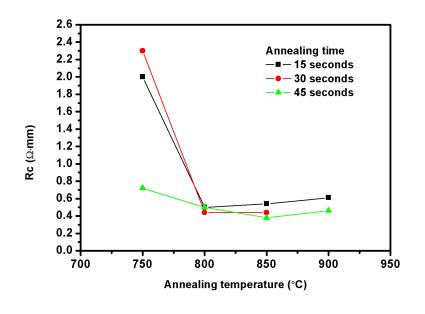

| 4.15 | Measured contact resistances under different RTA conditions                                                                                      | 49         |

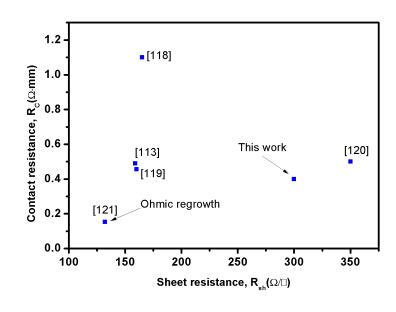

| 4.16 | Comparison of Ohmic contacts on AlN/GaN optimised for this work and                                                                              |            |

|      | other published work.                                                                                                                            | 50         |

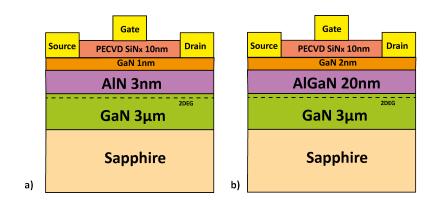

| 4.17 | Cross section of a) MBE grown AlN/GaN HEMT on sapphire and b)                                                                                    |            |

|      | MOCVD grown AlGaN/GaN HEMT on sapphire.                                                                                                          | 51         |

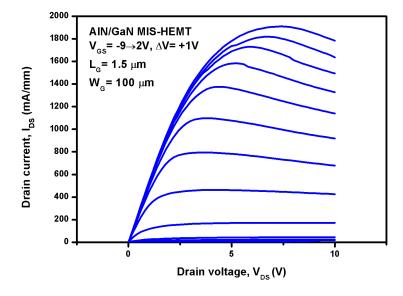

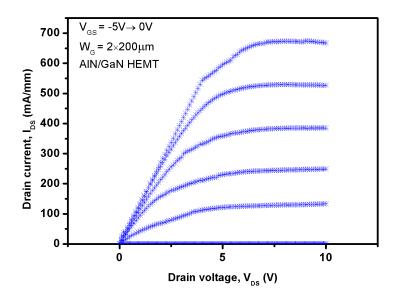

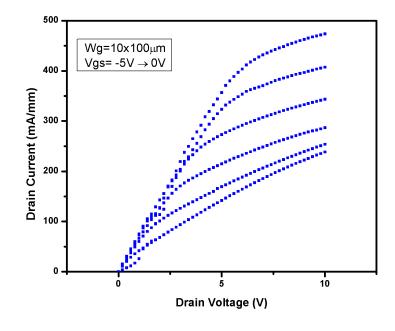

|      | Output IV characteristics of the AlN/GaN MIS-HEMT on sapphire                                                                                    | 52         |

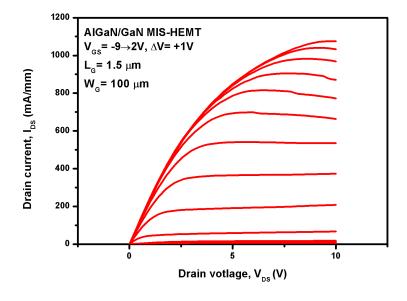

|      | Output IV characteristics of the AlGaN/GaN MIS-HEMT on sapphire.                                                                                 | 52         |

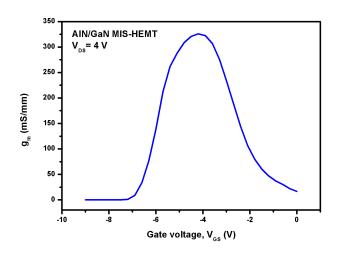

|      | Transconductance $(g_m)$ characteristics of the AlN/GaN MIS-HEMT                                                                                 | 53         |

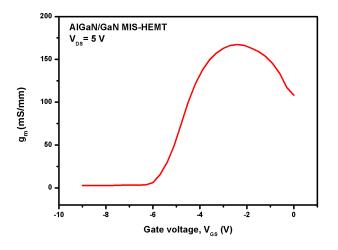

|      | Transconductance $(g_m)$ characteristics of the AlGaN/GaN MIS-HEMT.                                                                              | 53         |

| 4.22 | Cross section of a) MBE grown AlN/GaN HEMT on SiC and b) MOCVD                                                                                   | F 4        |

| 4.00 | grown AlGaN/GaN HEMT on SiC.                                                                                                                     | 54         |

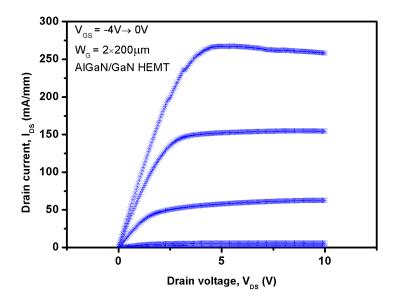

|      | Output IV characteristics of the AlCoN/GaN MIS-HEMT on SiC.                                                                                      | $55 \\ 55$ |

| 4.24 | Output IV characteristics of the AlGaN/GaN HEMT on SiC                                                                                           | 55         |

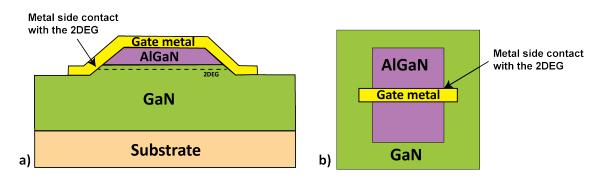

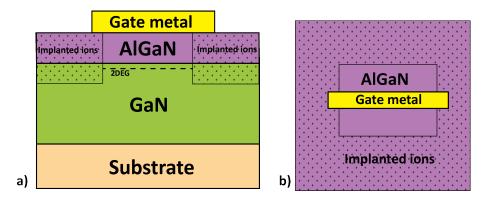

| 5.1  | Strucutre of devices isolated using dry etch down to the GaN buffer, a)                                                                          |            |

|      | cross-section and b) top-view.                                                                                                                   | 58         |

| 5.2  | Structure of devices isolated using ion implantation, a) cross-section and                                                                       |            |

|      | b) top-view.                                                                                                                                     | 59         |

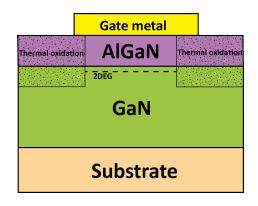

| 5.3  | Structure of devices isolated using thermal oxidation                                                                                            | 60         |

| 5.4  | Structure of devices isolated using oxygen plasma treatment.                                                                                     | 61         |

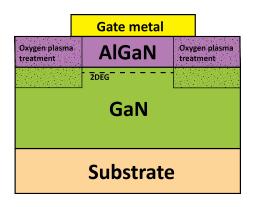

| 5.5  | Mesa isolation process flow: a) photo-resist spinning and UV exposure,                                                                           |            |

|      | b) development, c) photo-resist ashing, d) RIE etching, e) photo-resist                                                                          |            |

| •    | stripping and f) gate metal deposition.                                                                                                          | 62         |

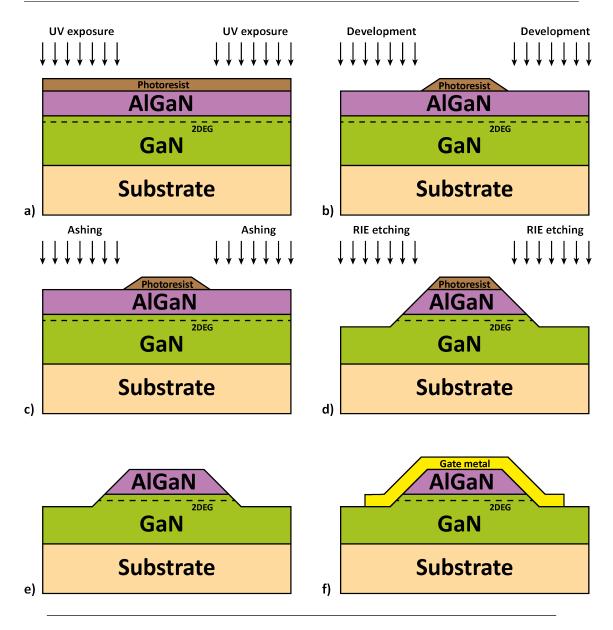

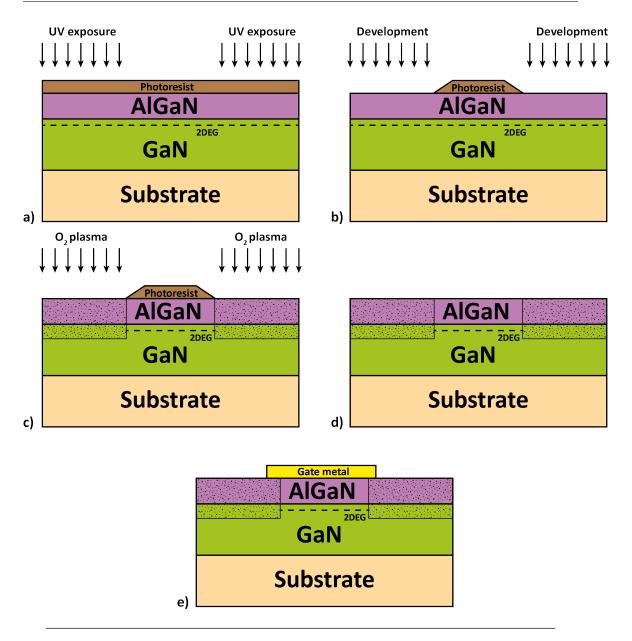

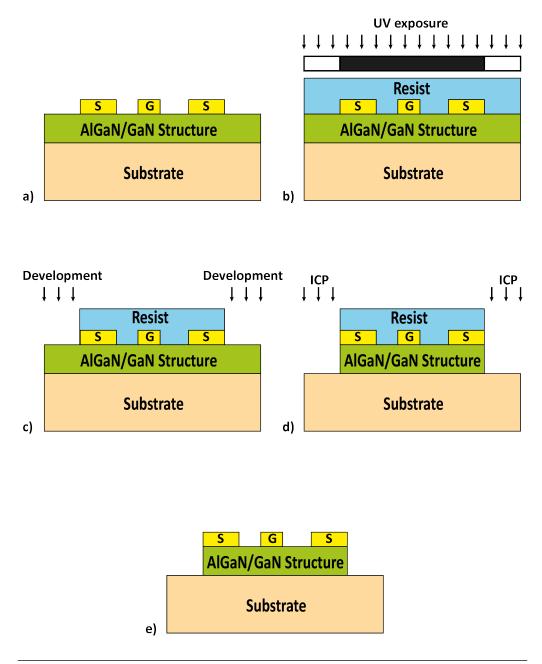

| 5.6  | Oxygen plasma treatment process flow: a) photo-resist spinning and UV                                                                            |            |

|      | exposure, b) development, c) oxygen plasma treatment, d) photo-resist                                                                            | 63         |

| 5.7  | stripping and e) gate metal deposition                                                                                                           | 05         |

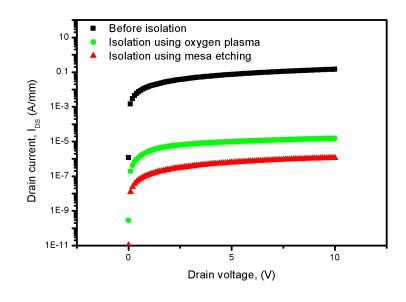

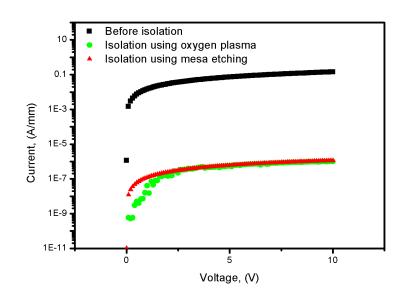

| 0.1  | fore isolation, isolation using oxygen plasma and isolation using mesa                                                                           |            |

|      | etching.                                                                                                                                         | 65         |

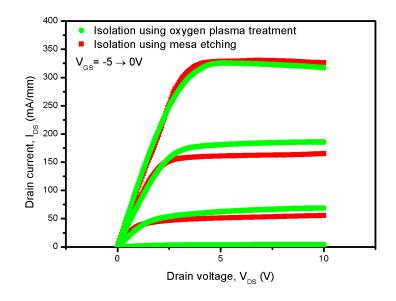

| 5.8  | Comparison of IV characteristics of devices isolated using: oxygen plasma                                                                        |            |

|      | and mesa etching.                                                                                                                                | 65         |

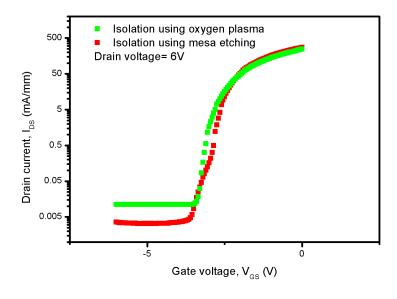

| 5.9  | $I_{DS}$ comparison of devices isolated using: oxygen plasma and mesa etching.                                                                   | 66         |

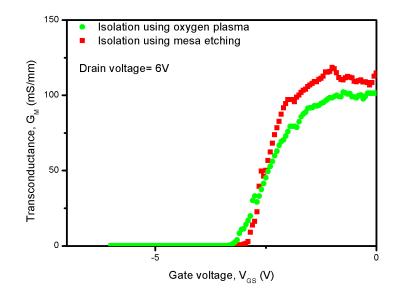

| 5.10 | Transconductance $(g_m)$ comparison of devices isolated using: oxygen                                                                            |            |

|      | plasma and mesa etching.                                                                                                                         | 67         |

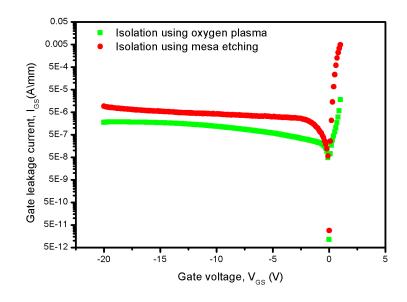

| 5.11 | Gate leakage comparison of devices isolated using: oxygen plasma and                                                                             |            |

|      | mesa etching.                                                                                                                                    | 68         |

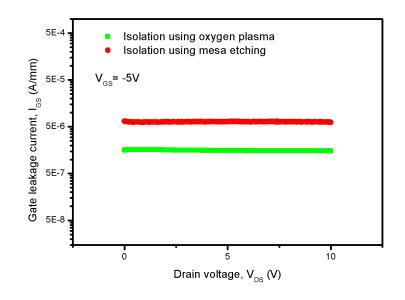

| 5.12                                      | Off state gate leakage comparison of devices isolated using: oxygen plasma and mesa etching.                                                                                                                  | 68         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.13                                      | Comparison of device-to-device current in three different situations: be-                                                                                                                                     |            |

|                                           | fore isolation, isolation using oxygen plasma and isolation using mesa<br>etching.                                                                                                                            | 69         |

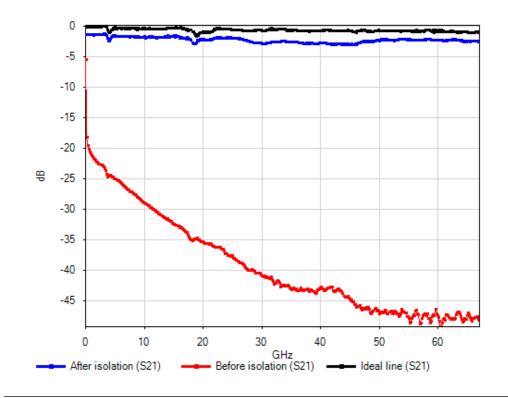

| 5.14                                      | RF characteristics (S21) of three transmission lines: Ideal, isolated and non-isolated.                                                                                                                       | 70         |

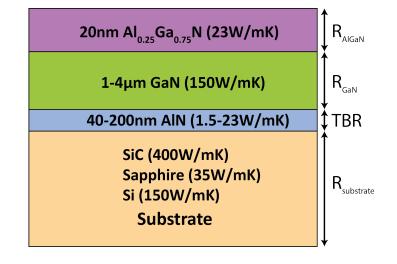

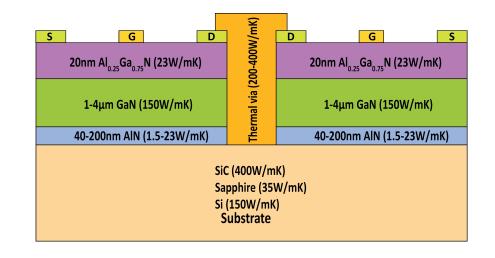

| 6.1                                       | Cross-section of a GaN-based HEMT with the thermal conductivities of                                                                                                                                          |            |

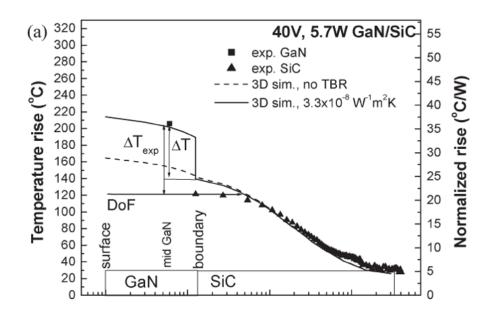

| 6.9                                       | the respective epi-layers                                                                                                                                                                                     | $73 \\ 73$ |

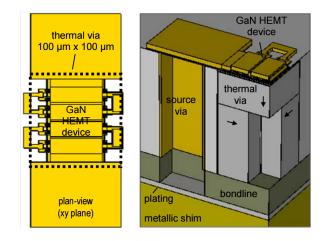

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | Simulated versus measured temperature of GaN on SiC substrate Thermal model renderings of (left) the HEMT and thermal via in plan-<br>view and (right) a section view with arrows indicating the diamond high |            |

| 6 4                                       | thermal conductivity orientation.                                                                                                                                                                             | 74         |

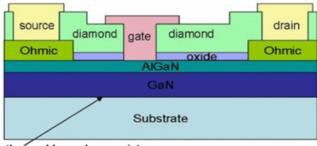

| 6.4                                       | Illustration of nano-crystalline diamond (NCD) on the surface of AlGaN/-<br>GaN HEMT.                                                                                                                         | 75         |

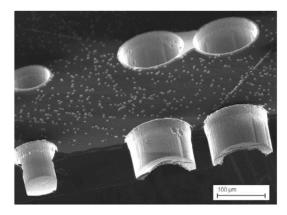

| 6.5                                       | Micrograph of thermal vias in SiC substrate filled with diamond                                                                                                                                               | 76         |

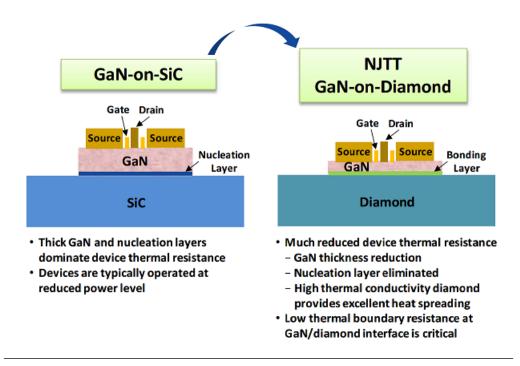

| 6.6                                       | Comparison of a conventional GaN-on SiC HEMT to the DARPA Near Junction Thermal Transport (NJTT) GaN-on-Diamond device.                                                                                       | 76         |

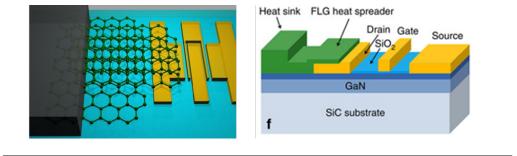

| 6.7                                       | Illustration of graphene on the drain side of the device                                                                                                                                                      | 77         |

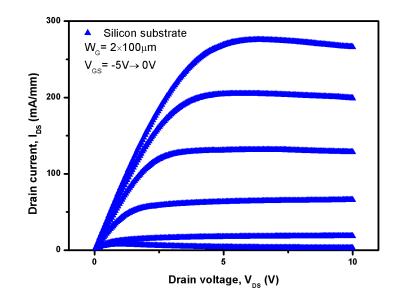

| 6.8                                       | Output IV characteristics of 2x100 $\mu$ m GaN HEMTs grown on a silicon                                                                                                                                       | -          |

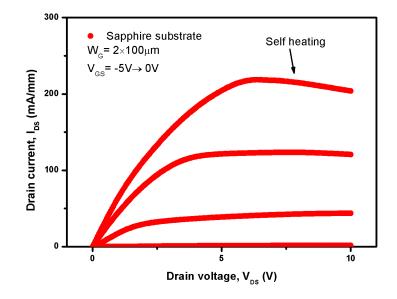

| 6.9                                       | substrate                                                                                                                                                                                                     | 78         |

| 0.9                                       | substrate.                                                                                                                                                                                                    | 78         |

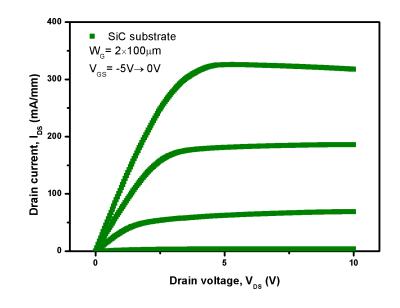

| 6.10                                      | Output IV characteristics of 2x100 $\mu$ m GaN HEMTs grown on a SiC substrate.                                                                                                                                | 79         |

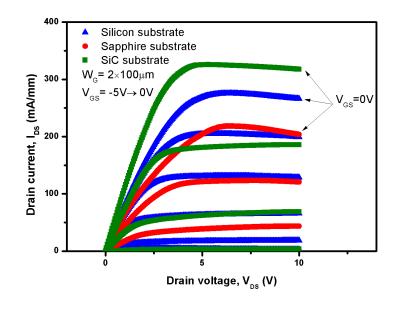

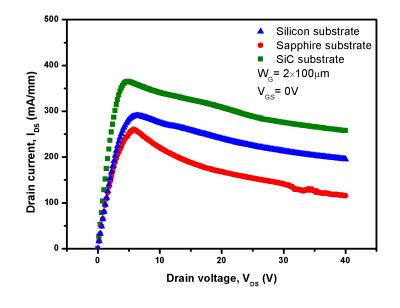

| 6.11                                      | Output IV characteristics of $2x100 \ \mu m$ GaN HEMTs grown on the three different substrates.                                                                                                               | 80         |

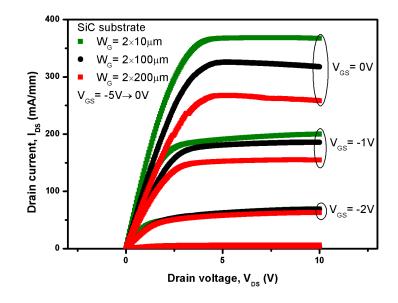

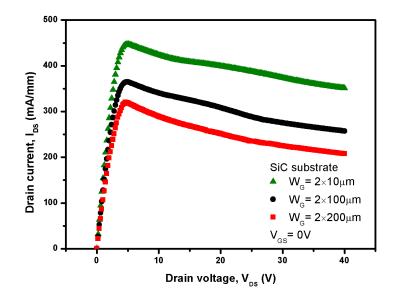

| 6.12                                      | Output IV characteristics of $2x10 \ \mu m$ , $2x100 \ \mu m$ and $2x200 \ \mu m$ GaN HEMTs grown on a SiC substrate.                                                                                         | 80         |

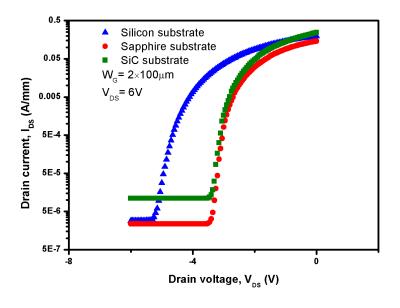

| 6.13                                      | $I_{DS}$ comparison of 2x100 $\mu$ m GaN HEMTs fabricated on the three different substrates.                                                                                                                  | 81         |

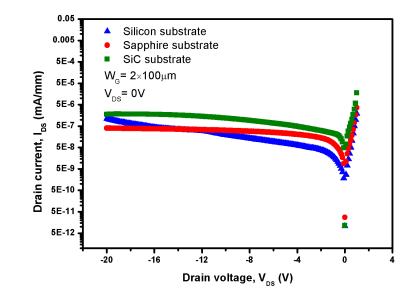

| 6.14                                      | Gate leakage current comparison of $2x100 \ \mu m$ GaN HEMTs fabricated<br>on the three different substrates.                                                                                                 | 82         |

| 6.15                                      | Output IV characteristics of $2x100 \ \mu m$ GaN HEMTs fabricated on the three different substrates.                                                                                                          | 82         |

| 6.16                                      | Output IV characteristics of $2x10 \ \mu m$ , $2x100 \ \mu m$ and $2x200 \ \mu m$ GaN HEMTs fabricated on a SiC substrate.                                                                                    | 83         |

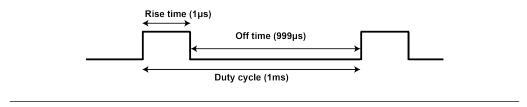

| 6.17                                      | Illustration of pulsed IV bias in the on and off state.                                                                                                                                                       | 84         |

|                                           | DC and pulsed IV characteristics of a Schottky gate HEMT. Drop in drain                                                                                                                                       | -          |

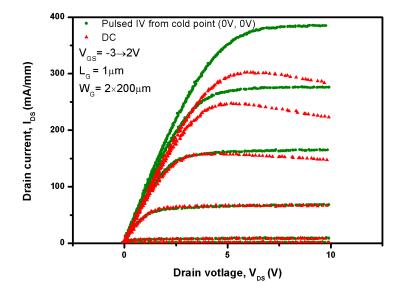

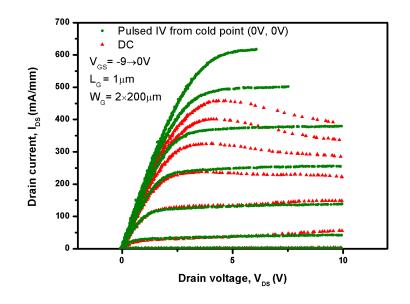

|                                           | current of 100 mA/mm at $V_{GS} = 0$ V can be observed                                                                                                                                                        | 85         |

| 6.19                                      | DC and Pulsed IV characteristics of a MIS-HEMT with 10nm of ICP-<br>CVD $SiN_x$ . Drop in drain current of 250 mA/mm at $V_{GS} = 0$ V can be                                                                 |            |

| 6.00                                      | observed. High drain currents are due to $SiN_x$ passivation                                                                                                                                                  | 86         |

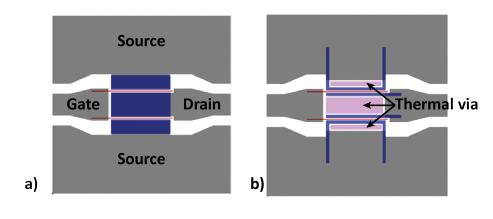

|                                           | Cross-section of a GaN-based HEMT structure with integrated heat sinks.<br>Layout of a) conventional RF device versus b) the new device with inte-                                                            | 87         |

|                                           | grated heat sinks.                                                                                                                                                                                            | 87         |

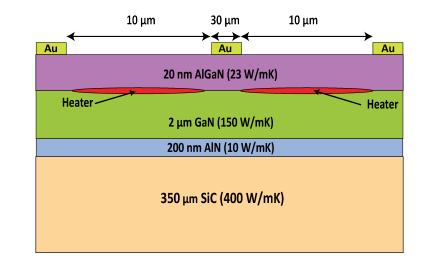

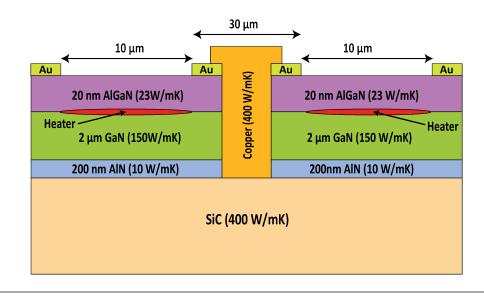

| 6.22                                      | Standard GaN HEMT model                                                                                                                                                                                       | 88         |

| 6.23 | GaN HEMT model with integrated copper heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 88 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

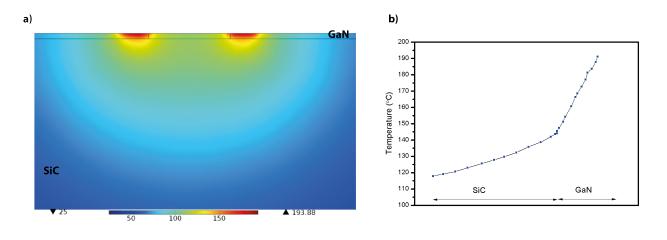

| 6.24 | a) Standard GaN HEMT with no TBR, b) temperature profile of GaN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|      | on SiC substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 89 |

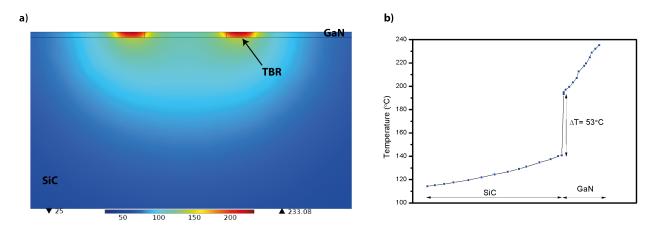

| 6.25 | a) Standard GaN HEMT with TBR, b) temperature profile of GaN on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|      | SiC substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 89 |

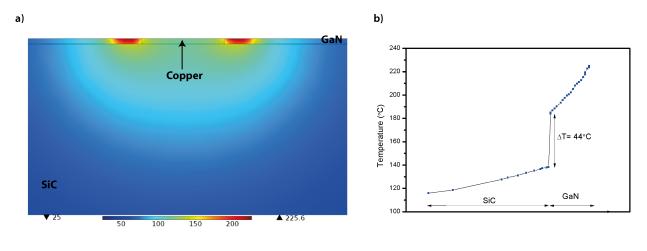

| 6.26 | a) GaN HEMT with integrated heat sink, b) temperature profile of GaN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|      | on SiC substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 89 |

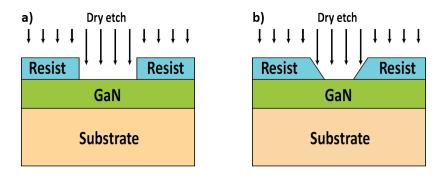

| 6.27 | Illustration of dry etching of nitride epi-layers process flow. Device struc-<br>ture after a) contact deposition , b) photo-resist spinning and UV expo-<br>sure, c) development, d) nitride epi-layers are etched and totally removed<br>down to the substrate creating thermal vias using ICP dry etching and<br>e) photo-resist stripping.                                                                                                                                                                                                                                                                                    | . 91 |

| 6.28 | Illustration of a) non-postbaked photo-resist profile and b) post-baked photo-resist profile.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 92 |

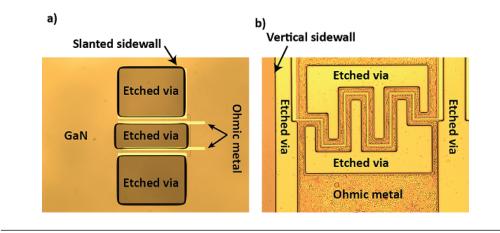

| 6.29 | Optical micrograph of a) etched vias with postbaked photo-resist and b) etched vias with non-postbaked photo-resist.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 93 |

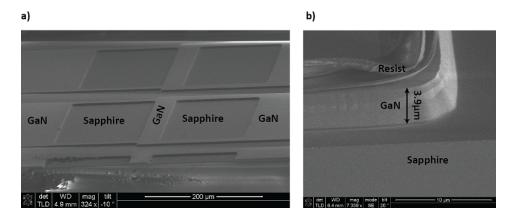

| 6.30 | SEM of a) GaN etched down to the substrate, b) GaN sidewalls with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|      | positive slope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 93 |

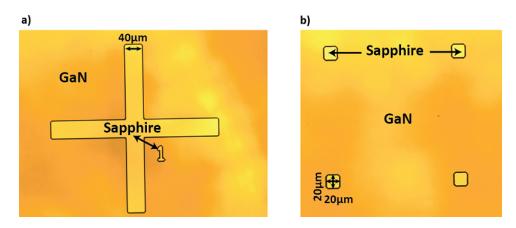

| 6.31 | Optical micrograph of a) features etched into GaN, b) 20 $\mu \rm m$ square                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|      | features etched into GaN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 93 |

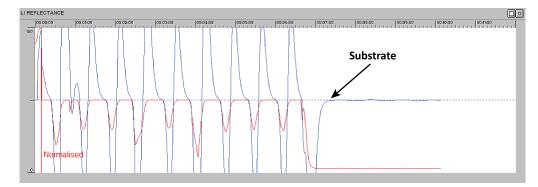

| 6.32 | Reflectance of interferometer to monitor etch depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 94 |

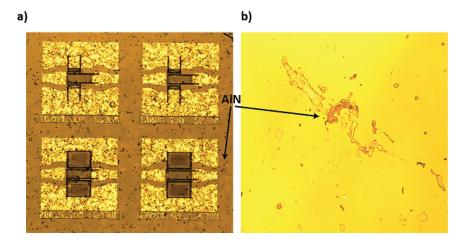

| 6.33 | AlN sputtered on a) fabricated devices and b) GaN surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 94 |

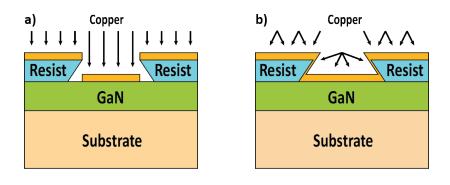

|      | Illustration of copper metallisation using a) evaporation, b) sputtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 95 |

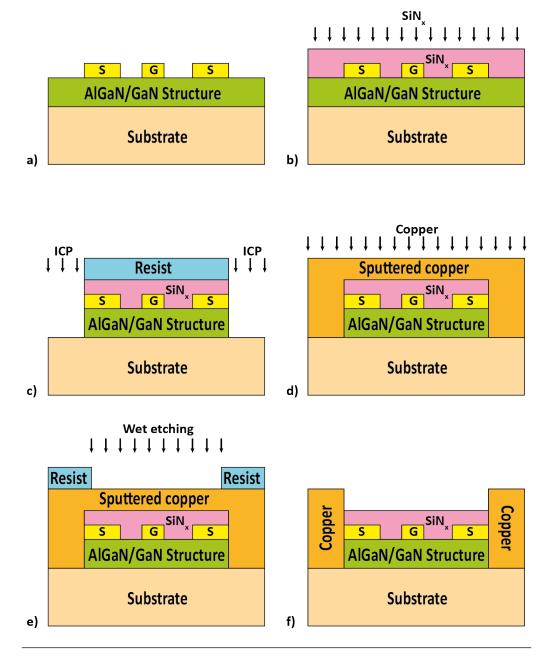

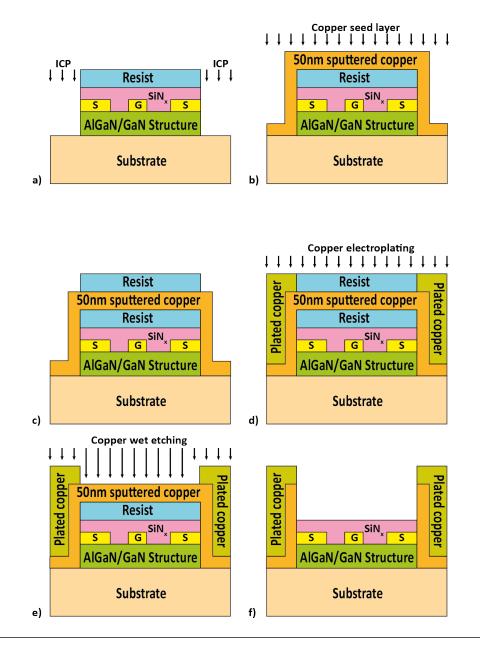

| 6.35 | Illustration of copper wet etching process flow for integrating Cu thermal vias in DC GaN devices. Device structure after a) contact deposition, b) $SiN_x$ passivation, c) nitride epi-layers are etched and totally removed down to the substrate creating a thermal via, d) blanket sputtering of Cu (RF sputtering: Plassys 3, 3 $\mu$ m thick Cu, pressure of $10^{-3}$ mT, 250 W RF power), e) patterning of copper to expose the transistor contacts-wet etching using dilute nitric acid (HNO <sub>3</sub> :H <sub>2</sub> O) 1:5 for 5 minutes: 600 nm/min using AZ4562 photo-resist as an etch mask) and finally f) the |      |

|      | remaining photo-resist is stripped using 1165 resist stripper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

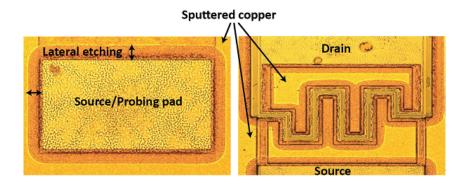

|      | Copper wet etching results in lateral etching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 97 |

| 6.37 | Copper electroplating process flow. Device structure after a) contact deposition, $SiN_x$ passivation, nitride epi-layers are etched and totally removed down to the substrate creating a thermal via, b) blanket sputtering of Cu seedlayer c) patterning of copper to expose the areas required to be electroplated, d) electroplating 3 $\mu$ m of copper, e) developing the photo-resist to access the underlying copper seedlayer followed by wetething the seed layer using HNO <sub>3</sub> :H <sub>2</sub> O 1:5 for 1 minute and finally f) the                                                                          |      |

|      | remaining photo-resist is stripped using 1165 resist stripper.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 98 |

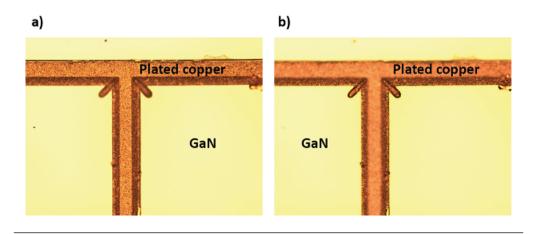

|      | Micrograph of 3 $\mu$ m electroplated copper (a) focus on the copper surface and (b) focus on the GaN surface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 99 |

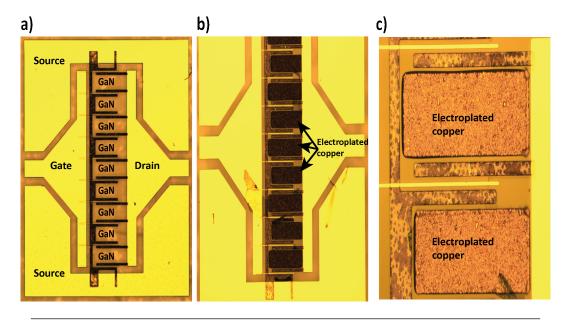

| 6.39 | Micrograph of a 10 finger device a) before etching thermal vias, b) after                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|      | etching and copper electroplating and c) enlarges image of b) to show the electroplated profile.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 99 |

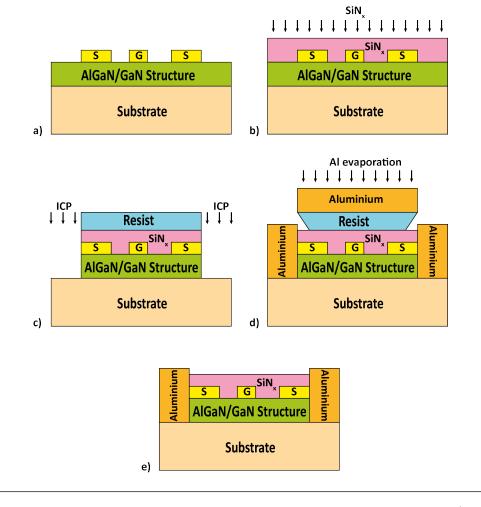

| 6.40 | Illustration of the Al lift-off process flow. Device structure after a) contact  |       |

|------|----------------------------------------------------------------------------------|-------|

|      | deposition, b) $SiN_x$ passivation, c) nitride epi-layers are etched and totally |       |

|      | removed down to the substrate creating a thermal via, d) aluminium               |       |

|      | evaporation using lift-off process and finally e) the remaining photo-resist     |       |

|      | is stripped using 1165 resist stripper.                                          | . 100 |

| 6.41 | SEM of evaporated Ti/Al on sapphire substrate with continuous side wall          |       |

|      | coverage.                                                                        | . 101 |

| 6.42 | Micrograph of standard devices and devices with etched vias with gate            |       |

|      | widths of 10, 30 60 and 100 $\mu$ m.                                             | . 101 |

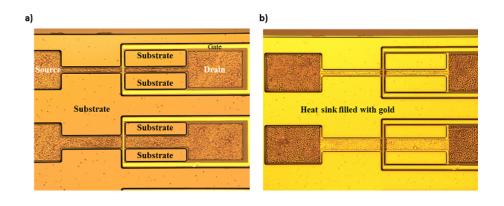

| 6.43 | Micrograph of 10 and 30 $\mu$ m wide fabricated devices (a) before and (b)       |       |

|      | after heat sink deposition.                                                      | . 102 |

| 6.44 | Micrograph of a 1 mm wide device (a) before and (b) after heat sink              |       |

|      | deposition.                                                                      | . 102 |

| 6.45 | Micrograph of an enlarged image of a fabricated device after heat sink           |       |

|      | deposition.                                                                      | . 102 |

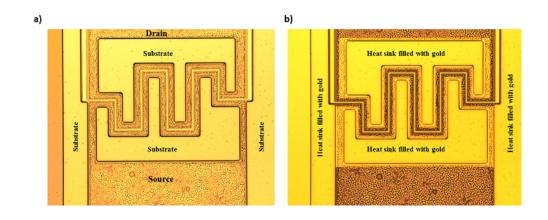

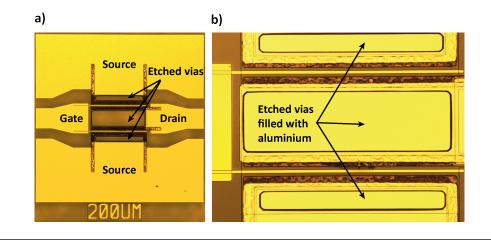

| 6.46 | Micrograph of a fabricated RF device (a) after etching thermal vias and          |       |

|      | (b) after aluminium heat sink deposition.                                        | . 104 |

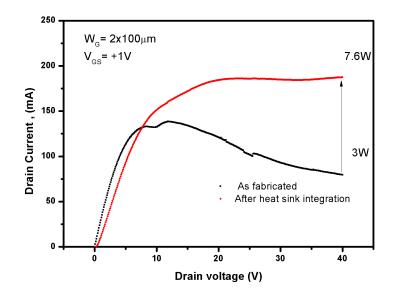

| 6.47 | DC performance of a standard (as fabricated) and advanced (after heat            |       |

|      | sink integration) AlGaN/GaN on SiC HEMT device.                                  | . 104 |

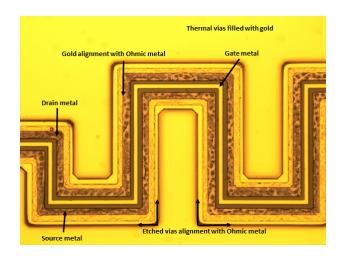

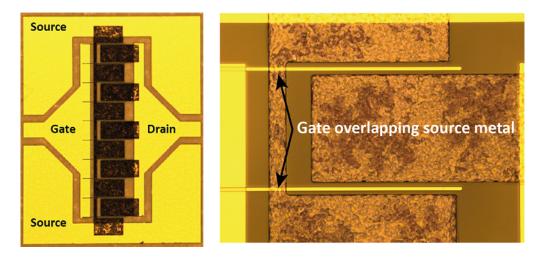

| 6.48 | Micrograph of (a) a 10 finger device and (b) enlarged image to show the          |       |

| 0.10 | gate overlap with the source contact.                                            | . 105 |

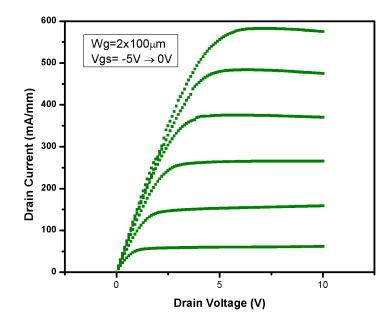

| 6.49 | Output IV characteristics of a 2x100 $\mu$ m device.                             |       |

|      | Output IV characteristics of a 10x100 $\mu$ m device                             |       |

| 0.00 |                                                                                  | . 100 |

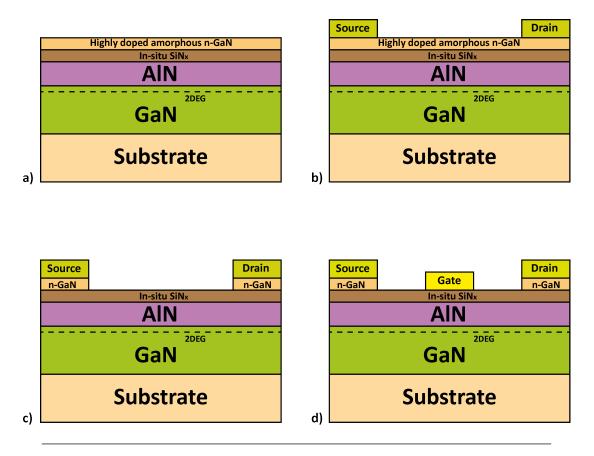

| 7.1  | Illustration of the new Ohmic contact to AlN/GaN material structure a)           |       |

|      | unprocessed epi-layer structure, b) Ohmic source and drain metals are            |       |

|      | deposited followed by RTA c) the n-GaN is selectively etched and finally         |       |

|      | d) the gate metal is directly deposited on the in-situ $SiN_x$                   | . 109 |

# List of Tables

| 1.1 | Material properties of conventional and wide-band gap semiconductors.                                                             | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Properties of commonly used substrates for the growth of GaN HEMTs.<br>CTE= Coefficient of Thermal Expansion.                     | 14 |

| 4.1 | Gap spacings with their equivalent correction factor.                                                                             | 41 |

| 6.1 | $I_{DSS}$ of devices on the different substrates employing variable gate widths of 2x10 $\mu$ m, 2x100 $\mu$ m and 2x200 $\mu$ m. | 81 |

|     | $I_{DSS}$ of 2x100 $\mu$ m devices on the different substrates                                                                    |    |

|     |                                                                                                                                   |    |

# Symbols

| 2DEG      | 2 Dimensional Electron Gas           |

|-----------|--------------------------------------|

| 2DHG      | 2 Dimensional Hole Gas               |

| AFM       | Atomic Force Microscopy              |

| Ar        | Argon                                |

| Al        | Aluminium                            |

| Au        | Gold                                 |

| AlGaN     | Aluminium Gallium Nitride            |

| AlN       | Aluminium Nitride                    |

| $BCl_3$   | Boron tri-chloride                   |

| Cu        | Copper                               |

| CTE       | Coefficient of Thermal Expansion     |

| CVD       | Chemical Vapor Deposition            |

| $Cl_2$    | Chlorine                             |

| CTLM      | Circular Transmission Line Model     |

| CW        | Continuous Wave                      |

| DC        | Direct Current                       |

| DI        | De-Ionised                           |

| $E_C$     | Conduction band energy               |

| $E_f$     | Fermi level energy                   |

| $E_g$     | Bandgap energy                       |

| $f_{max}$ | Maximum frequency of operation       |

| $f_T$     | Unity current gain cut-off frequency |

| Ga        | Gallium                              |

| GaN       | Gallium Nitride                      |

| GaAs      | Gallium Arsenide                     |

|           |                                      |

| $g_m$    | Transconductance                          |

|----------|-------------------------------------------|

| HF       | Hydrofluoric acid                         |

| $H_2O$   | Water                                     |

| HVPE     | Hydride Vapour Phase Epitaxy              |

| HEMT     | High Electron Mobility Transistor         |

| IV       | Current - Voltage                         |

| ICP      | Inductive Coupled Plasma                  |

| InP      | Indium Phosphide                          |

| InAlN    | Indium Aluminium Nitride                  |

| JWNC     | James Watt Nanofabrication Centre         |

| k        | Thermal conductivity                      |

| LTLM     | Linear Transmission Line Model            |

| $L_{GD}$ | Gate - drain distance                     |

| $L_{GS}$ | Gate - source distance                    |

| $L_{SD}$ | Source - drain distance                   |

| $L_T$    | Transfer length                           |

| LOR      | Lift-off resist                           |

| LED      | Light Emitting Diode                      |

| MMIC     | Monolithic Microwave Integrated Circuit   |

| MBE      | Molecular Beam Epitaxy                    |

| MOCVD    | Metal Organic Chemical Vapour Deposition  |

| N        | Nitrogen                                  |

| $n_s$    | Sheet carrier concentration               |

| Ni       | Nickel                                    |

| $P_{PE}$ | Piezoelectric polarization                |

| $P_{SP}$ | Spontaneous polarization                  |

| PECVD    | Plasma Enhanced Chemical Vapor Deposition |

| q        | Electron charge                           |

| RO       | Reverse Osmosis                           |

| RIE      | Reactive Ion Etching                      |

| $R_c$    | Ohmic contact resistance                  |

| $R_{sh}$ | Sheet resistance                          |

| $R_{ch}$ | Channel resistance                        |

| DD              |                                  |

|-----------------|----------------------------------|

| RF              | Radio Frequency                  |

| SiC             | Silicon Carbide                  |

| $SiCl_4$        | Silicon tetrachloride            |

| Si              | Silicon                          |

| $SiN_x$         | Silicon Nitride                  |

| TiN             | Titanium Nitride                 |

| Ti              | Titanium                         |

| TBR             | Thermal Boundary Resistance      |

| TEM             | Transmission electron microscope |

| $V_{BR}$        | Breakdown voltage                |

| $V_{DS}$        | Drain - source voltage           |

| $v_{eff}$       | Effective velocity               |

| $v_{sat}$       | Saturated electron Velocity      |

| $V_{GS}$        | Gate - Source voltage            |

| $V_p$           | Pinch-off voltage                |

| $V_T$           | Threshold voltage                |

| $W_g$           | Gate width                       |

| $\mu_n$         | Electron mobility                |

| ε               | Absolute permittivity            |

| $\epsilon_o$    | Vacuum permittivity              |

| $\varepsilon_r$ | Relative permittivity            |

| $\phi_b$        | Schottky barrier                 |

| σ               | Polarisation charge              |

|                 |                                  |

Dedicated to my parents: Dr. Koutaiba Al-Khalidi and Ibtehal Al-Hachim to whom I shall always be indebted...

# CHAPTER 1

# Introduction

## 1.1 Overview

Since the invention of the first electronic transistor in 1947, the demand for higher powers and higher frequencies has always increased. An alternative technology is needed to push the boundary beyond what is achievable with the existing silicon technology. The interest for III-V technologies such as Indium Phosphide (InP) [1], Gallium Arsenide (GaAs) [2] and Gallium Nitride (GaN) [3] based High Electron Mobility Transistors (HEMTs) has emerged as they exhibit higher electron mobilities which translates into higher operational frequencies. The wider bandgap of III-Vs enable higher operational voltages which translates into higher output powers. These technologies can therefore extend the transistor performance beyond what is possible with the current silicon technology. Among the III-V materials, GaN has been the favourite for high power and high frequency solid state applications due to its wider band gap (3.4 eV) compared to InP (1.35 eV) and GaAs (1.43 eV), and hence has higher breakdown voltages enabling it to deliver higher output powers. For example, GaN offers up to five times higher power density than GaAs [4, 5].

GaN technology has come a long way since the fabrication of the first GaN transistor in 1993 [6] in terms of growth maturity, design and fabrication techniques, allowing it to be adopted and implemented in many different applications. These include the automotive industry [7], photovoltaic power converters [8], DC-DC converters [9, 10], high power line converters, power switching [11], space applications [12], high efficiency LED lighting [13] and high power high frequency applications required for defence [14, 15] and wireless telecommunication systems [16]. High temperature operation of up to 1000°C has been demonstrated on InAlN/GaN HEMTs [17] making them suitable for the oil industry

| Property (Units)                                                 | GaN | SiC  | Diamond | Si   | GaAs | InP  |

|------------------------------------------------------------------|-----|------|---------|------|------|------|

| Relative permittivity, $\epsilon_r$                              |     | 10.1 | 5.5     | 11.8 | 12.8 | 12.8 |

| Band gap energy, $E_g$ (eV)                                      |     | 3.26 | 5.45    | 1.12 | 1.43 | 1.35 |

| Breakdown field, $E_c$ (MV/cm)                                   | 3.3 | 3    | 10      | 0.3  | 0.4  | 0.5  |

| 2DEG density, $n_s (x10^{13} \text{ cm}^{-2})$                   | 1   | -    | -       | -    | 0.2  | 0.2  |

| Thermal conductivity, $\kappa$ (W/m·K)                           | 130 | 400  | 2200    | 150  | 50   | 70   |

| Electron mobility, $\mu_n \ (\text{cm}^2/\text{V}\cdot\text{s})$ | 900 | 700  | 4800    | 1500 | 8500 | 5400 |

| Saturated electron velocity, $V_{sat}(x10^7 \text{ cm/s})$       | 2.5 | 2    | 2.7     | 1    | 1    | 1    |

| Power density, (W/mm)                                            | >30 | 10   | -       | 0.2  | 0.5  | -    |

and aircraft engines [18]. The fundamental material properties of GaN, SiC, Diamond, silicon, GaAs and InP are listed in Table 1.1.

TABLE 1.1: Material properties of conventional and wide-band gap semiconductors.

One of GaN's main advantages lies in its ability to form heterojunctions to wider band gap materials such as Aluminum Gallium Nitride (AlGaN) and Aluminium Nitride (AlN). In doing so, a 2 dimensional electron gas (2DEG) channel is formed which exhibits high electron densities  $(>10^{13}/\text{cm}^2)$  and high electron mobilities of up to 2000 cm<sup>2</sup>/V·s. Although this is lower than the mobilities of GaAs and InP, it compensates through having a much higher 2DEG density of  $10^{13}$  cm<sup>-2</sup>, resulting in an overall lower sheet resistance. This makes it suitable for high power high frequency applications like radar and space applications. The higher electron mobilities exhibited by the 2DEG compared to bulk GaN comes from the faster carrier transport in low-dimensional system due to reduced scattering and density of states. GaN has a relatively high band gap energy of 3.4 eV and breakdown field of 3.3 MV/cm compared to silicon, GaAs and InP. This enables high voltage operation of the GaN HEMTs before breaking down, which makes it suitable for high voltage applications like photovoltaic power converters and high power line converters. The thermal conductivity determines how quickly the heat can be extracted from the semiconductor, and since GaN has a thermal conductivity of 130 W/mK, this gives it a big advantage over GaAs and InP which have a much lower thermal conductivity. The wide bandgap and high thermal conductivity of GaN makes it suitable for high temperature applications such as oil industry and aircraft engine applications. Figure 1.1 illustrates some of the applications of GaN technology mentioned above.

FIGURE 1.1: Applications of GaN technology.

## **1.2** Problem statement

Despite rapid progress over the last few years, GaN technology still requires significant improvements in various aspects. This section describes the challenges addressed by the work done in this project, which includes Ohmic contacts for the AlN/GaN material system, device isolation and thermal management of GaN-based HEMTs.

### 1.2.1 Ohmic contacts to AlN/GaN HEMT material system

AlN/GaN is a very interesting material system as it can potentially deliver at least double the output power that is delivered by the conventional AlGaN/GaN material system. State of the art DC and RF devices based on AlN/GaN [19, 20] have been demonstrated, with maximum current densities of up to 4 A/mm, transconductance of 1 S/mm and  $f_T/f_{max}$  of 342/518GHz using a 20 nm T-gate process [21], where  $f_T$  is the unity current gain frequency and  $f_{max}$  is the unity power gain frequency. However, there are several obstacles in realising such a technology. One is the Ohmic contacts, the other is material growth, and lastly surface sensitivity during processing. The thin AlN barrier is sensitive to processing solutions and causes the fabricated devices to suffer from high leakage currents if not protected during processing [22, 23]. For example, the AZ400K photo-resist developer was shown to etch the AlN barrier layer [24]. Therefore, protecting the AlN layer during processing is important. One way to achieve such protection is the use of an in-situ SiN<sub>x</sub> passivation layer as will be described in chapter 4.

Ohmic contacts on the AlGaN/GaN material have been shown to exhibit a satisfactory contact resistance in the range of 0.2-0.5  $\Omega$ ·mm. On AlN/GaN, however, the formation of low Ohmic contacts becomes more challenging as AlN has a band gap of 6.2 eV, which is higher than the band gap of Al<sub>0.25</sub>GaN<sub>0.75</sub> of approximately 4 eV, and therefore devices exhibit contact resistance values in the range of 0.5-1  $\Omega$ ·mm. Contact resistances under 0.2  $\Omega$ ·mm are required for the performance of these devices to be competitive in terms of reaching the potential of high current densities and high output power. Low Ohmic contact resistance of 0.2  $\Omega$ ·mm could be achieved by either lowering the barrier height or by easing tunneling through the barrier. Lowering the barrier height could be achieved by high temperature anneals, by highly doping the GaN cap layer with silicon [25], or using the Ohmic regrowth technique to regrow silicon rich GaN in the contact areas before depositing the Ohmic metal [26]. Easing tunneling through the barrier could be achieved by either starting with a thin barrier or thinning the barrier using dry etching [27]. The aforementioned techniques are either requiring regrowths or the contact resistance is still high.

In this project, the use of in-situ  $SiN_x$  passivation layer is proposed to protect the AlN surface during processing, reduce gate leakage current and reduce the Ohmic contact resistance, as will be described in chapter 4.

#### 1.2.2 Device isolation for GaN-based HEMTs

Device isolation is required to electrically isolate devices from each other. The two common ways to isolate GaN based devices are mesa isolation and ion implantation. Mesa isolation is the most popular technique due to its low cost and availability in most research laboratories. Dry etch techniques are used to implement mesa isolation since GaN has strong ionic bonds, making it resistant to most acids and bases and therefore cannot be wet etched. The problem with dry etching is that it induces damage to the AlGaN surface, making it conductive [28, 29], and results in the gate metal having a direct contact with the 2DEG channel. This results in increasing gate leakage currents by at least one order of magnitude (from the conventional 1  $\mu$ A/mm to >10  $\mu$ A/mm) due to the gate metal being in direct contact with the 2DEG channel. This leads to the reduction of breakdown voltages, and therefore a planar device structure is desirable to avoid the direct contact of the gate metal with the 2DEG channel. Ion implantation is one way to achieve a planar device structure and although it involves complex processing and high equipment cost, it is still used due to its advantages [30]. In one published example, devices isolated using ion implantation (planar devices) exhibited higher breakdown voltages of 650 V compared to devices isolated using mesa isolation (three dimensional devices) exhibiting breakdown voltages of 350 V [31]. The three dimensional structure was also shown to deteriorate the noise performance of GaN HEMTs under gate bias stress which severely affects low noise amplifier performance [32]. When compared to three dimensional devices, planar devices were demonstrated to exhibit better RF performance [33].

Due to the complexity of the ion implantation process and high cost of the equipment, in this project a new technique is proposed to realise device isolation using a planar process that is based on oxygen plasma treatment. The new technique will be described and discussed in chapter 5.

#### 1.2.3 Thermal management on AlGaN/GaN HEMTs