Nicol, Robert Leiper (1997) Fabrication and characterization of ultrasmall tunnel junctions for single electron devices. PhD thesis.

http://theses.gla.ac.uk/5365/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

# Fabrication and Characterization of Ultra-small Tunnel Junctions for Single Electron Devices.

Robert Leiper Nicol.

Submitted for the degree of Doctor of Philosophy to the Department of Electronics and Electrical Engineering at the University of Glasgow.

September 1997.

© Robert L. Nicol, 1997.

To Trene,

and in memory of Dad.

### **S**UMMARY

This thesis presents research into the development and characterization of fabrication processes for high temperature single electron devices. Some background to single electron effects and the fabrication processes used in this work is presented. Analysis, development and characterization work on the fabrication processes for ultrasmall single electron devices is also presented. Electrical measurements on the films used and the single electron structures fabricated are then presented and discussed. The work on the fabrication processes is then discussed in the light of these electrical results. Conclusions are drawn with regard to the practicalities and technologies required for true high temperature operational single electron devices.

Work on the fabrication processes has shown that traditional tunnel junction formation techniques result in structure sizes which are too large to provide the high temperature effects required. Where lithographic techniques alone are used to shrink pattern dimensions, the processes become unreliable. In the case of the suspended mask shadow evaporation process used here, a limiting reliable overlap width of 40nm is expected and experienced. Attempts to fabricate structures below this size resulted in unreliable tunnel junction formation. The second technique investigated, the crossed track technique, suffered from serious problems arising from the angled evaporation process and from step coverage difficulties. The third fabrication technique attempts to control the placement of grains within the aluminium film. This technique has the advantages of simplicity and ability to form the smallest tunnel junctions with the material system used here. This system was chosen as the main fabrication process for investigation of high temperature single electron devices in this work.

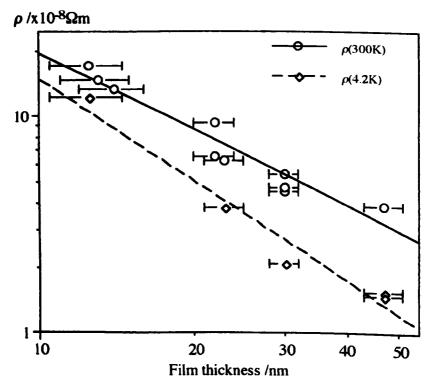

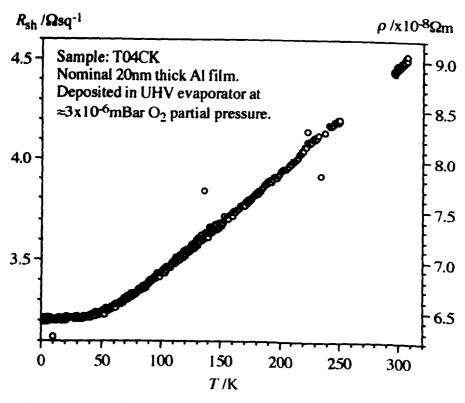

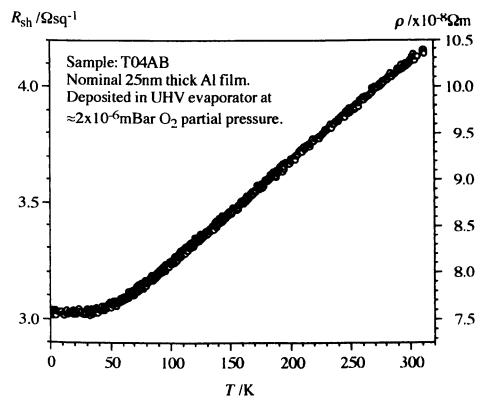

Measurements of resistivity and resistivity temperature dependence of the aluminium films were used to characterize the film types. The temperature dependence and magnitude of the resistivity have shown the films to be very conductive, or metallic. By virtue of this high conductivity, the structure behaviour should be dominated by the device, or tunnel junction, properties. The results obtained from the devices at 4.2K do

not show the presence of single electron effects. However, the fabricated structures did demonstrate tunnelling behaviour. The absence of single electron effects has been attributed to the structure sizes. Despite being among the smallest possible in aluminium metallizations, these granular structures are apparently too large. The explanation for this is derived from the presence of stray capacitances between the grains forming the tunnel junctions. This raises the junction capacitance and therefore reduces the charging energy of the junction and the temperature of operation.

Despite the failure to observe high temperature single electron effects, this work has shown that it is possible to control the placement of aluminium grains within a film to form tunnel junction structures. Were a self organizing system, such as this, to be produced on a smaller scale, it would be possible to significantly increase the temperature of operation of single electron devices.

### ACKNOWLEDGEMENTS

I would like to thank the staff and students of the Department of Electronics and Electrical Engineering, University of Glasgow, for helping make my research an enjoyable experience and this thesis possible. I would like to thank my supervisor, Professor Steve P. Beaumont, for his help with this project and for his patience during the writing of this thesis. Many thanks are due to the excellent support given to this work from the members of the Nanoelectronics Research Centre, the staff of the Mechanical and Electrical workshops and the Vacuum Laboratories. Special thanks are needed for Dave, Susan, Robert and Helen for many hours spent interpreting instructions on how to run yet another of my Beamwriter jobs. Thanks are also due to Steve Thoms and Douglas MacIntyre for their help and technical expertise. Thanks also go to John Weaver, Mahfuzur Rahman, Iain Thayne and Nigel Cameron for helping me find all kinds of electrons and showing me what to do with them.

Finally, I would like to thank my wife, Irene, and my parents for their love, support and understanding throughout my academic career. Special thanks go to Irene for correcting my chemistry, grammar and spelling and for many, many cups of coffee.

## CONTENTS

| SUMMARY          |                                  |                                                      | III |

|------------------|----------------------------------|------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS |                                  |                                                      | V   |

| Сна              | PTER O                           | ONE INTRODUCTION                                     | 1   |

| 1.1              | Develo                           | opments in electronics                               | 1   |

|                  | 1.1.1                            | The history of the transistor and integrated circuit | 2   |

|                  | 1.1.2                            | Miniaturization or scaling                           | 5   |

|                  | 1.1.3                            | Limitations to device scaling                        | 11  |

| 1.2              | Quantı                           | ım Effect Devices                                    | 13  |

|                  | 1.2.1                            | Reduced dimensionality                               | 13  |

|                  | 1.2.2                            | Quantum devices                                      | 16  |

| 1.3              | Motivation and aims of this work |                                                      | 18  |

| 1.4              | Organi                           | Organization of this thesis                          |     |

| 1.5              | Refere                           | nces                                                 | 23  |

| Сна              | PTER T                           | WO TUNNELLING AND SINGLE ELECTRON                    |     |

|                  |                                  | DEVICES                                              | 25  |

| 2.1              | Introdu                          | action                                               | 25  |

| 2.2              | Tunnel                           | lling                                                | 26  |

|                  | 2.2.1                            | Tunnelling Probability                               | 28  |

|                  | 2.2.2                            | Tunnel Current                                       | 33  |

|                  | 2.2.3                            | WKB approximation                                    | 36  |

| 2.3              | Single electron tunnelling       |                                                      | 38  |

|                  | 2.3.1                            | Coulomb blockade of tunnelling                       | 40  |

|                  | 2.3.2                            | Double tunnel junctions                              | 46  |

|                  | 2.3.3                            | One Dimensional Arrays                               | 58  |

|                  | 2.3.4                            | Two dimensional arrays and granular films            | 61  |

|      |                 |                                                        | VII |

|------|-----------------|--------------------------------------------------------|-----|

|      | 2.3.5           | Development of single electron devices                 | 63  |

| 2.4  | Refere          | •                                                      | 65  |

|      |                 |                                                        |     |

| Сна  | PTER T          | HREE FABRICATION TECHNIQUES                            | 69  |

|      |                 |                                                        |     |

| 3.1  | Introdu         | uction                                                 | 69  |

| 3.2  | Sample          | e preparation                                          | 70  |

|      | 3.2.1           | Organic contamination clean                            | 71  |

|      | 3.2.2           | Inorganic contamination clean                          | 71  |

|      | 3.2.3           | Oxidation                                              | 71  |

|      | 3.2.4           | Deoxidation or oxide etch                              | 72  |

| 3.3  | Lithog          | raphy                                                  | 72  |

|      | 3.3.1           | Electron beam lithography                              | 72  |

|      | 3.3.2           | Photolithography                                       | 83  |

| 3.4  | Metall          | ization and lift-off                                   | 86  |

|      | 3.4.1           | Lift-off processing                                    | 86  |

|      | 3.4.2           | Interconnect metallization                             | 87  |

|      | 3.4.3           | Device metallization                                   | 89  |

| 3.5  | Evapoi          | ration systems                                         | 90  |

|      | 3.5.1           | Plassys MEB450                                         | 90  |

|      | 3.5.2           | High vacuum evaporator                                 | 91  |

|      | 3.5.3           | Ultra High Vacuum Evaporator                           | 92  |

| 3.6  | Susper          | nded mask fabrication                                  | 96  |

|      | 3.6.1           | Mask layers                                            | 97  |

|      | 3.6.2           | Mask patterning                                        | 97  |

|      | 3.6.3           | Mask suspension                                        | 98  |

|      | 3.6.4           | Mask removal                                           | 98  |

| 3.7  | Pattern details |                                                        | 98  |

|      | 3.7.1           | Main interconnect layer                                | 99  |

|      | 3.7.2           | Thin film interconnect layer                           | 99  |

|      | 3.7.3           | Bonding layer                                          | 100 |

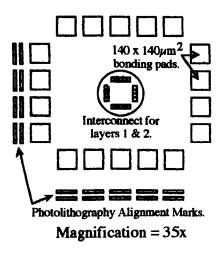

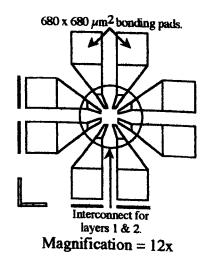

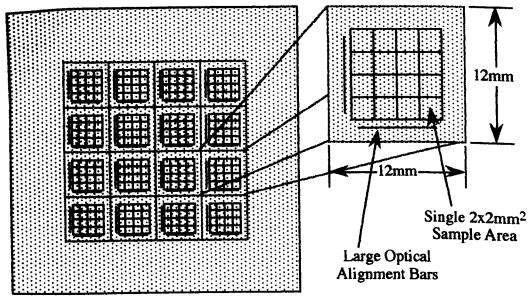

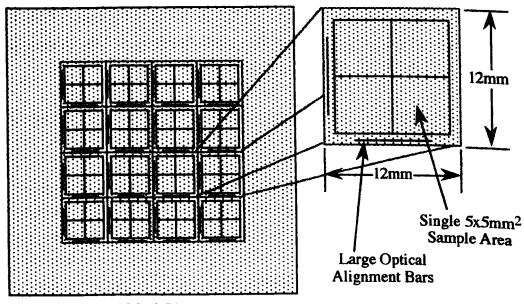

|      | 3.7.4           | Photolithography masks and sample layout               | 101 |

| 3.8  | Proces          | s details                                              | 102 |

|      | 3.8.1           | Lead frame (5X5MM <sup>2</sup> OR 2X2MM <sup>2</sup> ) | 103 |

|      | 3.8.2           | High resolution resist processes                       | 105 |

|      | 3.8.3           | Process for "single layer device and interconnect"     | 106 |

| 3.9  | Conclu          | usion                                                  | 107 |

| 3.10 | Refere          | ences                                                  | 108 |

| CHAPTER FOUR SINGLE ELECTRON DEVICE |         |                                                       |     |

|-------------------------------------|---------|-------------------------------------------------------|-----|

|                                     |         | FABRICATION                                           | 111 |

| 4.1                                 | Introdu | ction                                                 | 111 |

| 4.2                                 | Suspen  | Suspended mask structures                             |     |

|                                     | 4.2.1   | Angled evaporation device fabrication                 | 113 |

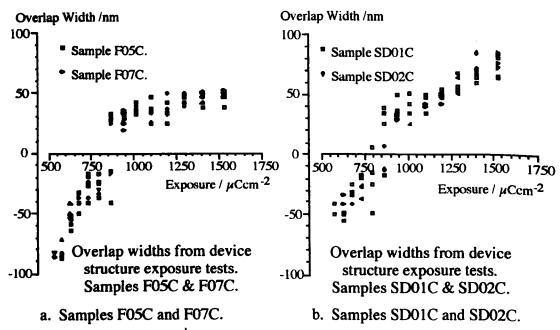

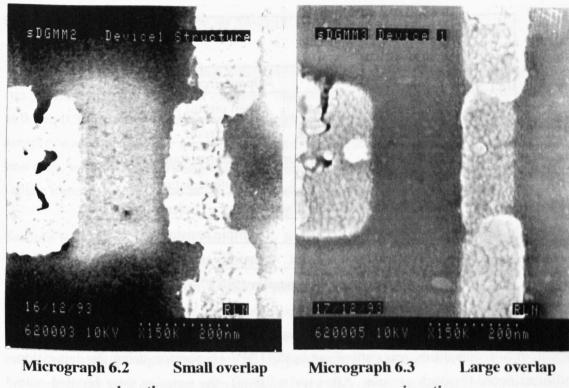

|                                     | 4.2.3   | Control over device fabrication                       | 114 |

| 4.3                                 | Crossec | d track structures                                    | 120 |

|                                     | 4.3.1   | Crossed track technique                               | 120 |

|                                     | 4.3.2   | Pattern design and development                        | 121 |

|                                     | 4.3.3   | Resist structure development                          | 123 |

|                                     | 4.3.4   | Fabrication problems                                  | 126 |

|                                     | 4.3.5   | Rejection of crossed track process                    | 131 |

| 4.4                                 | Pattern | ed granular film structures                           | 132 |

|                                     | 4.4.1   | Patterned thin film structure                         | 133 |

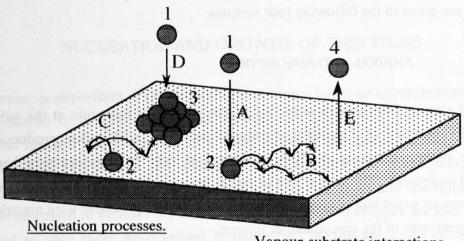

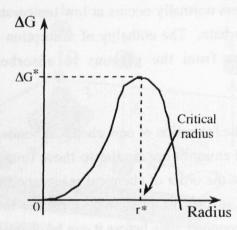

|                                     | 4.4.2   | Nucleation and growth of thin films                   | 134 |

|                                     | 4.4.3   | Characterization of film structure                    | 139 |

|                                     | 4.4.4   | Characterization of pattern and structure development | 149 |

| 4.5                                 | Conclu  | usions                                                | 158 |

| 4.6                                 | Refere  | ences                                                 | 160 |

| СНА                                 | APTER F | IVE THIN FILM ELECTRICAL                              |     |

|                                     |         | CHARACTERIZATION                                      | 161 |

| 5.1                                 | I +     | nation                                                |     |

| 5.1                                 |         | uction                                                | 161 |

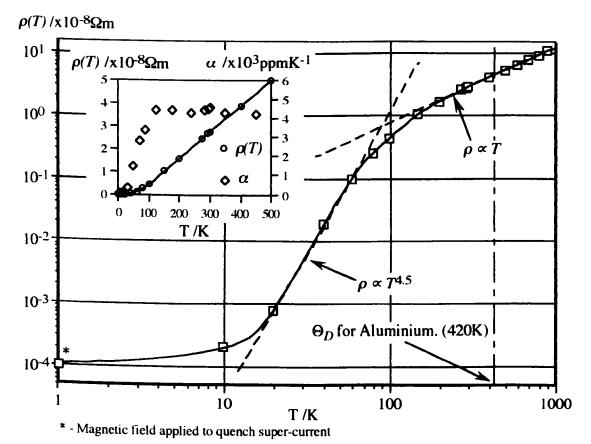

| 3.2                                 | 5.2.1   | lic film resistivity                                  | 162 |

|                                     | 5.2.1   | Metallic conduction                                   | 162 |

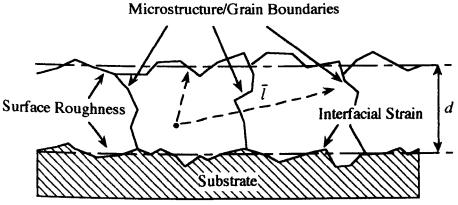

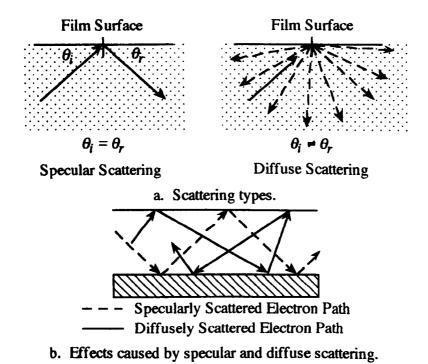

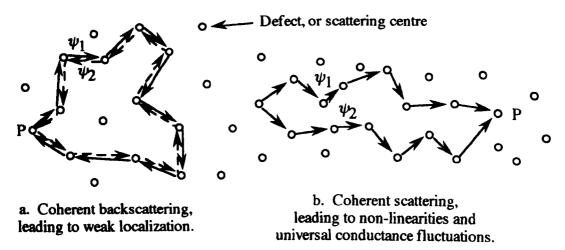

|                                     | 5.2.2   | Conduction Processes in thin metal films              | 168 |

|                                     | 5.2.4   | Conduction processes in granular films                | 175 |

| 5.3                                 |         | Conduction effects observed in aluminium              | 179 |

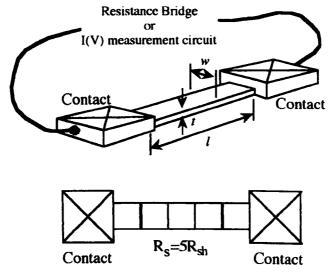

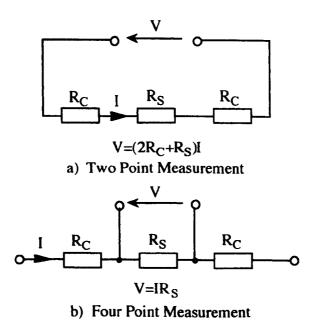

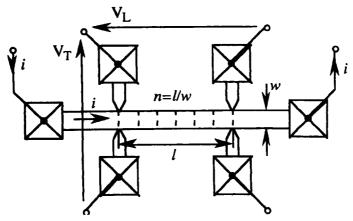

| 5.5                                 | 5.3.1   | tivity measurement techniques  Sheet resistance       | 181 |

|                                     | 5.3.2   |                                                       | 183 |

| 5.4                                 |         | stivity measurement system                            | 185 |

|                                     | 5.4.1   |                                                       | 187 |

|                                     | 5.4.2   | - ,                                                   | 188 |

|                                     | 5.4.3   | and a content Circuit                                 | 190 |

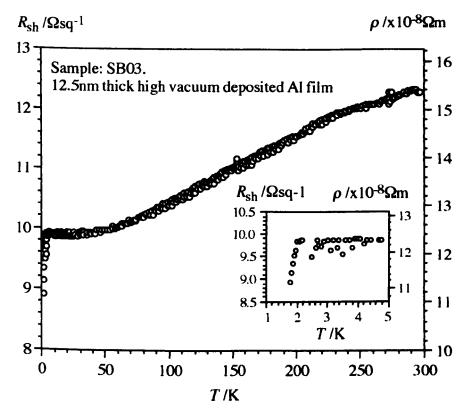

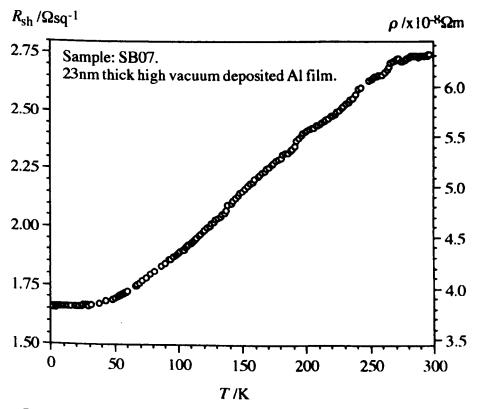

| 5.5                                 |         | stivity measurements                                  | 192 |

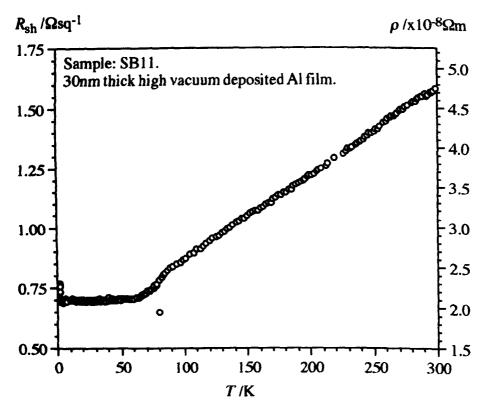

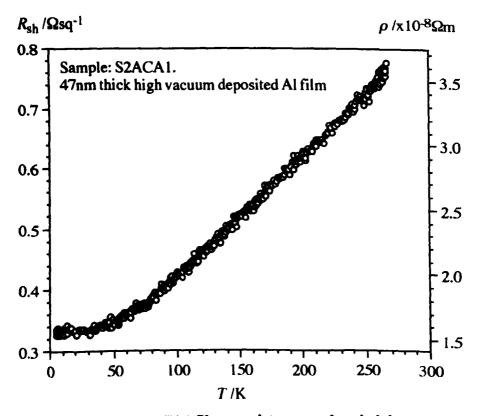

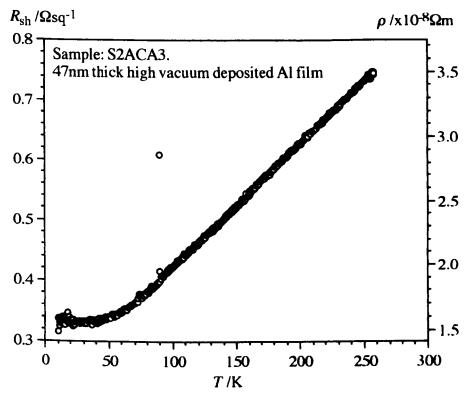

|                                     | 5.5.1   |                                                       | 193 |

|                                     | 2.2.1   | 511 recedin deposited milits.                         | 193 |

|     |                            |                                           | lX  |

|-----|----------------------------|-------------------------------------------|-----|

|     | 5.5.2                      | Ultra-high vacuum deposited films.        | 201 |

|     | 5.5.3                      | Thin film interconnect measurements.      | 206 |

| 5.6 | Conclus                    | sions                                     | 209 |

| 5.7 | Referen                    | nces                                      | 211 |

| Сна | PTER SI                    | X SINGLE ELECTRON DEVICE                  |     |

|     |                            | MEASUREMENTS                              | 213 |

| 6.1 | Introdu                    | ction                                     | 213 |

| 6.2 | Device                     | structures                                | 214 |

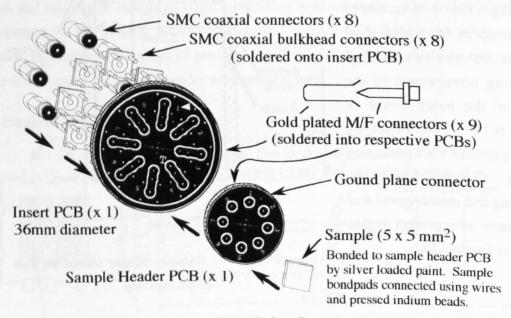

|     | 6.2.1                      | Fabrication test circuit                  | 214 |

| 6.3 | Measur                     | rement system design                      | 216 |

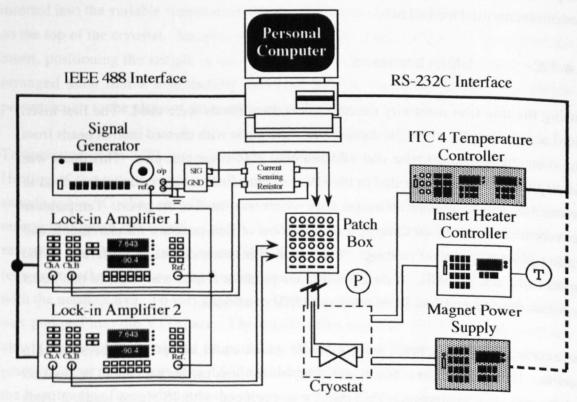

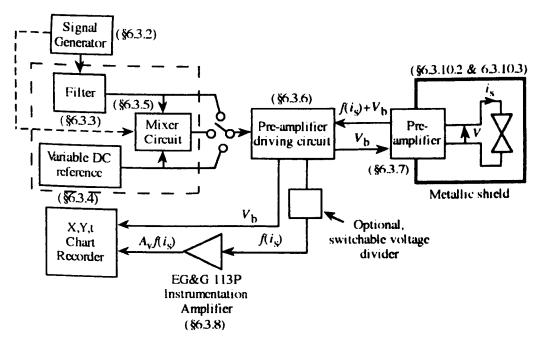

|     | 6.3.1                      | System Overview                           | 216 |

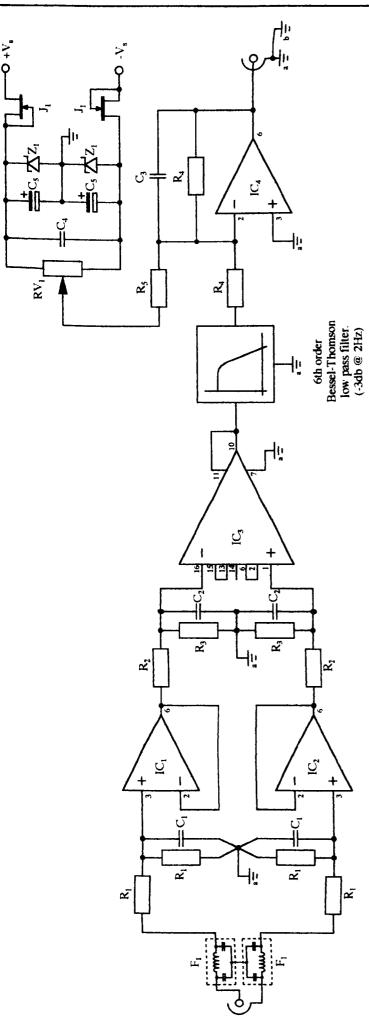

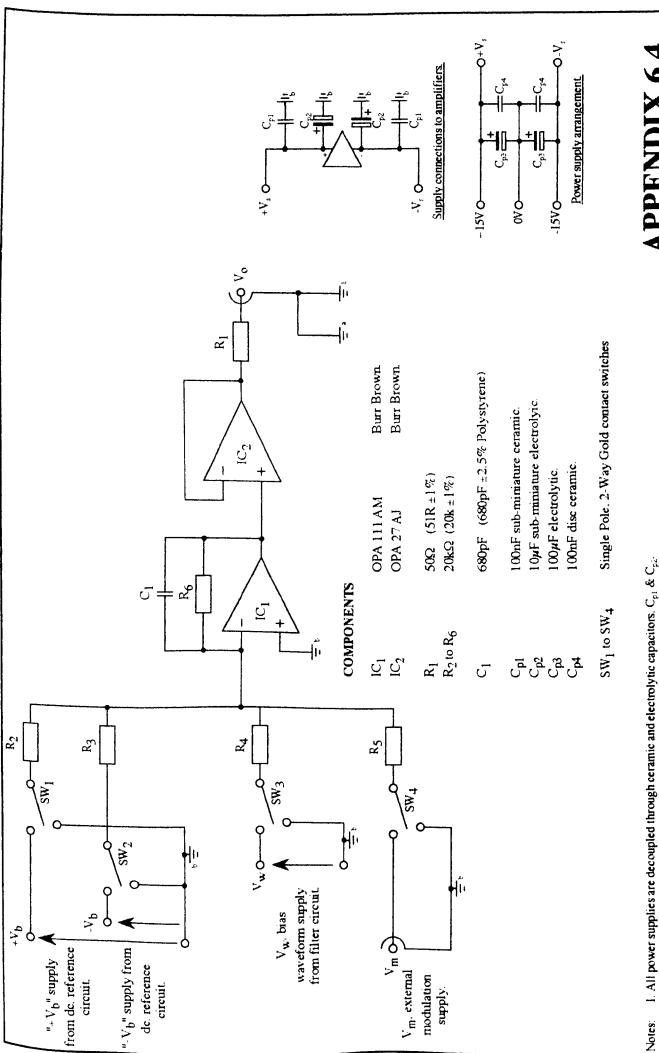

|     | 6.3.2                      | Signal generator                          | 218 |

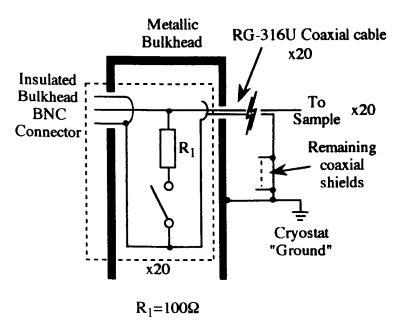

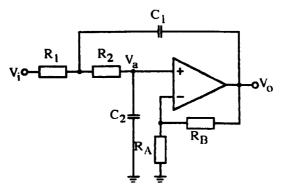

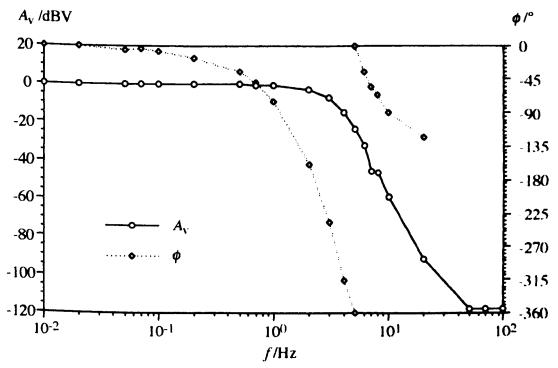

|     | 6.3.3                      | Filter stage                              | 218 |

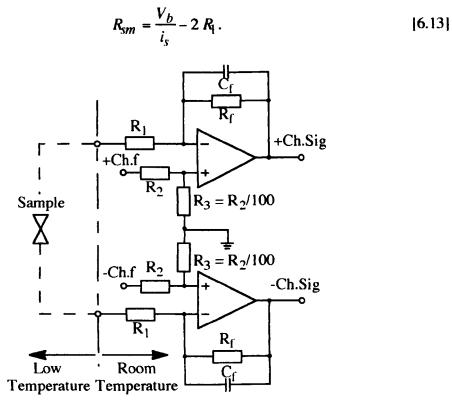

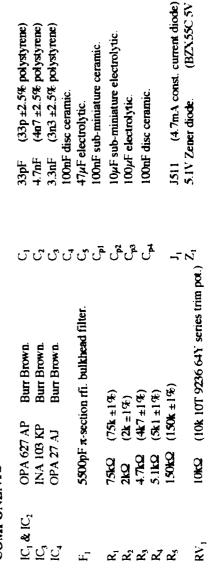

|     | 6.3.4                      | Variable dc. reference voltage            | 225 |

|     | 6.3.5                      | Mixer circuit                             | 226 |

|     | 6.3.6                      | Driving circuit                           | 227 |

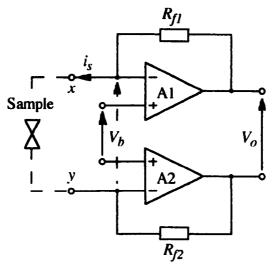

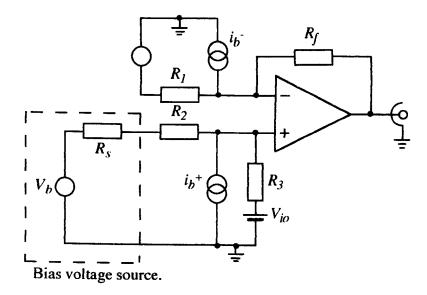

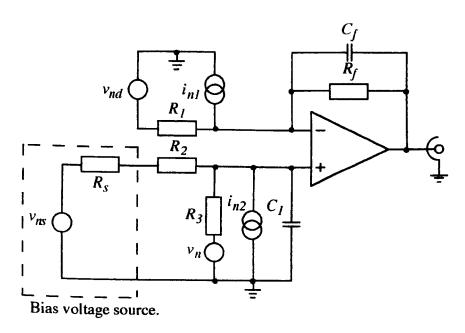

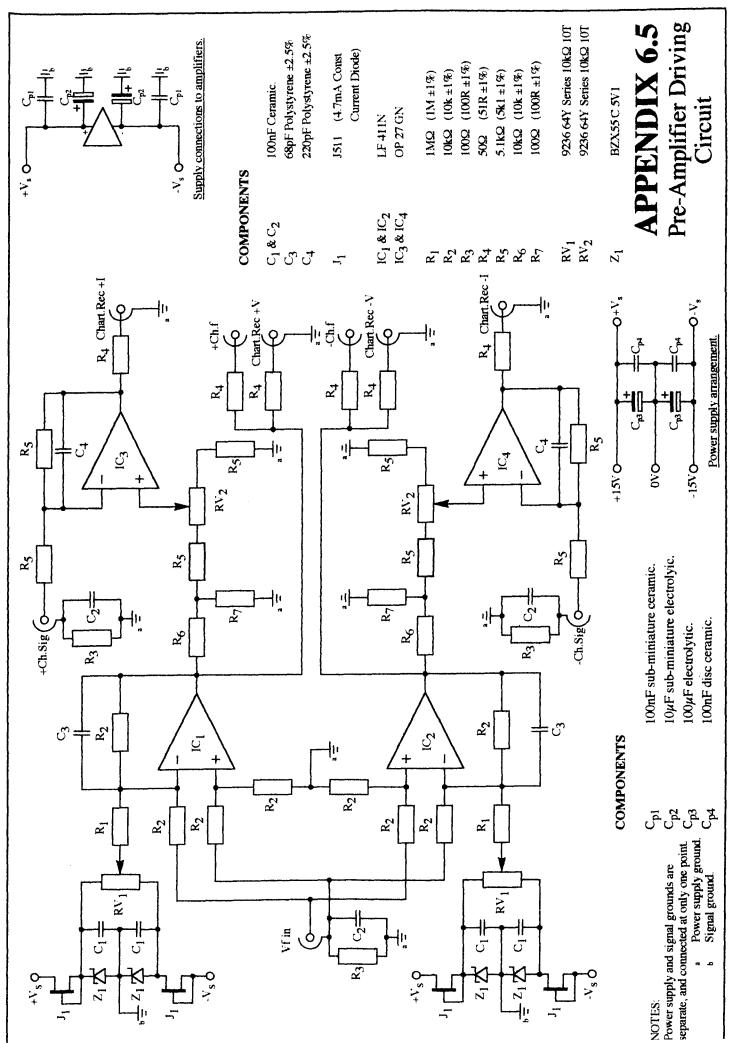

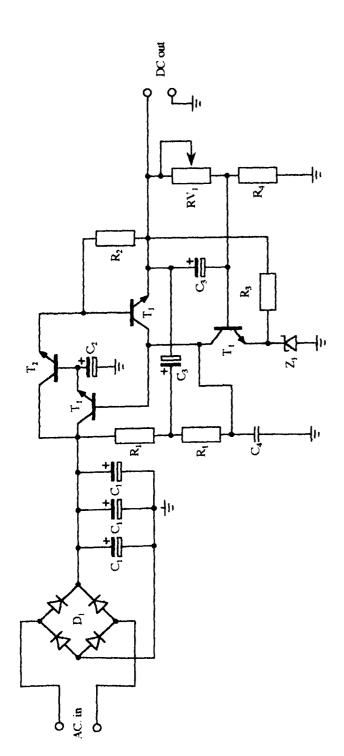

|     | 6.3.7                      | Pre-amplifier                             | 231 |

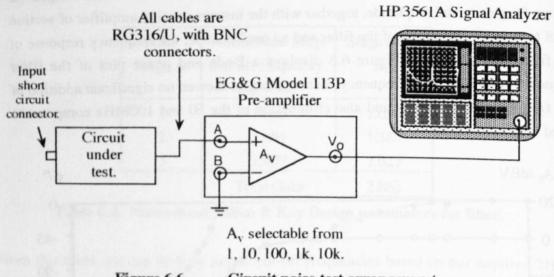

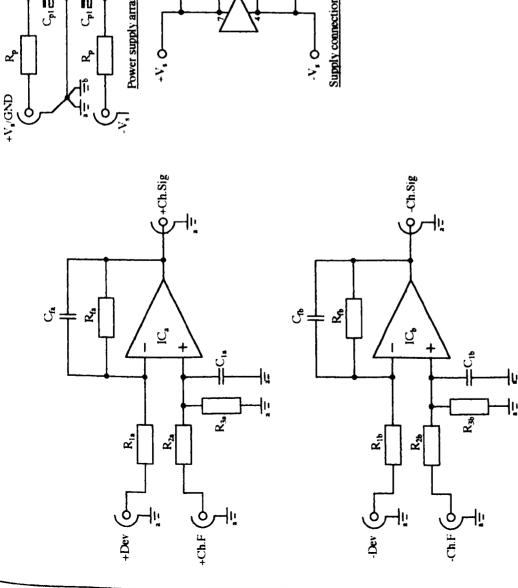

|     | 6.3.8                      | Instrumentation amplifier                 | 241 |

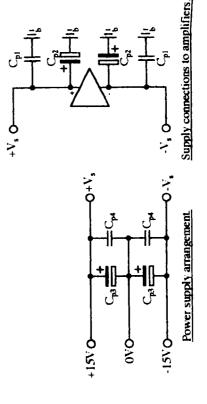

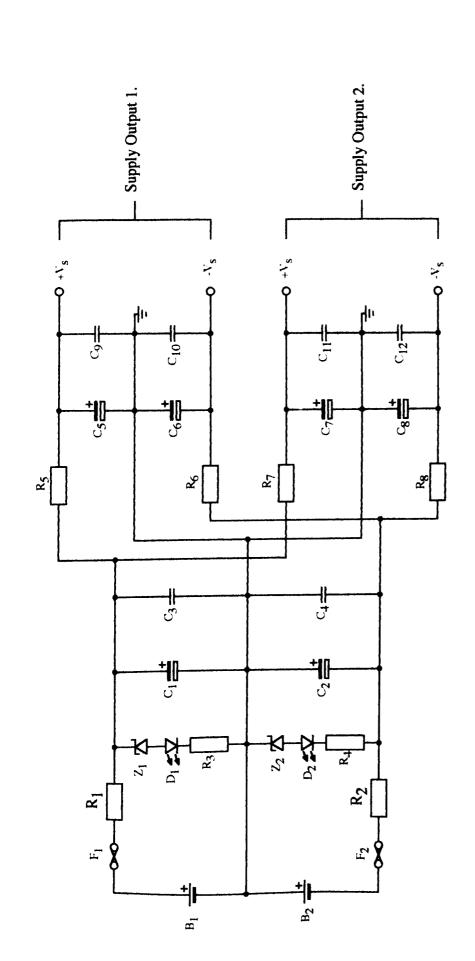

|     | 6.3.9                      | Power circuitry                           | 242 |

|     | 6.3.10                     | Mechanical construction                   | 243 |

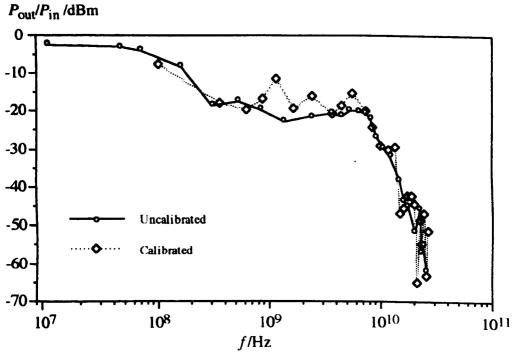

|     | 6.3.11                     | System operational characteristics        | 249 |

| 6.4 | Device measurement results |                                           | 249 |

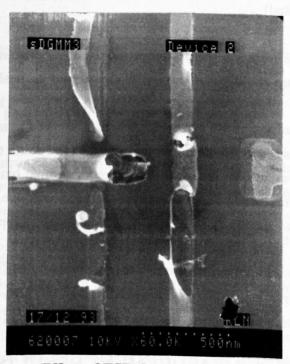

|     | 6.4.1                      | Suspended mask samples                    | 248 |

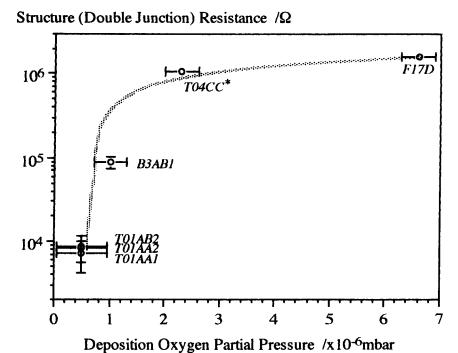

|     | 6.4.2                      | Granular "SET" electrometers              | 251 |

|     | 6.4.3                      | Granular single tunnel junctions          | 254 |

| 6.5 | Conclu                     |                                           | 255 |

| 6.6 | Refere                     | nces                                      | 258 |

|     | Appen                      | dicies for Chapter 6                      |     |

| Сна | APTER S                    | EVEN DISCUSSION                           | 259 |

| 7.1 | Introd                     | uction                                    | 259 |

| 7.2 | Structi                    | Structure formation and control           |     |

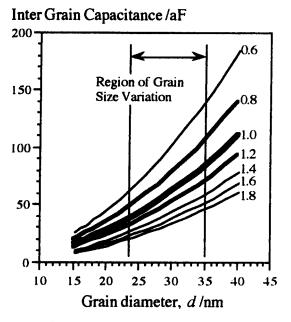

| 7.3 | Structi                    | ure capacitance                           | 264 |

| 7.4 |                            | er development of the granular technique  | 269 |

| 7.5 |                            | pilities for high temperature SET devices | 271 |

| 7.6 |                            | usions and further work                   | 272 |

| 7.7 | Refere | nces          | 277 |

|-----|--------|---------------|-----|

|     | 7.6.2  | Further work. | 275 |

|     | 7.6.1  | Conclusions   | 273 |

# CHAPTER ONE

#### Introduction

#### 1.1 DEVELOPMENTS IN ELECTRONICS

The modern electronics industry is exhibiting unprecedented levels of growth and development, with the semiconductor sector displaying up to 40% per annum growth in market value<sup>[1]</sup>. The growth in demand and applications for existing products results in a continual need for product and process development to meet the requirements of customers while maintaining profitability. The speed of development of electronic devices has arisen from the ability to integrate and miniaturize devices and systems. Currently it is possible to fabricate 1 to 3 million components onto a single square centimetre of silicon. This provides multifunctionality in a physically small area with good communication between system units and reduction in cost through mass production and economies of scale.

The ability to miniaturize is an overwhelming driving force for the industry which has, in some respects, become self-fulfilling. The need to continually scale processes in order to maintain profitability allows for increases in functionality and complexity. This trend is now assumed as standard and places requirements on the industry to continue a high rate of development and growth. The consumer electronics and

computer markets exemplify this situation. With product lifetimes in these markets being as short as three months to one year, relentless revisions increase the functionality, power and complexity of products, with no real cost increase. Indeed, in most cases the cost is effectively reduced when the complexity or functionality gain is considered.

The following sections of this chapter give a brief discussion of the development of the industry from its early beginnings. The current miniaturization trend and its future implications are also discussed. Research into new modes of device operation and new devices, of which this work is a part, are discussed. From this discussion the motivation and aims of this work are set out. Finally, the organization of this thesis is discussed.

## 1.1.1 THE HISTORY OF THE TRANSISTOR AND INTEGRATED CIRCUIT

It is tempting to think of the electronics and semiconductor industries emerging from the development of the transistor by J. Bardeen and W.H. Brattain<sup>[2]</sup> and the initial developments of transistor theory by W. Shockley<sup>[3]</sup>, J.L Moll and others. This view, however, ignores the long history of development in the field of electrical technology and electronics.

In 600BC, Thales of Miletus<sup>[4]</sup> discovered the ability of rubbed pieces of amber to attract straw. This represents one of the first documented experiments with electricity in any form. Indeed, the root word for the subject, electron, is derived from the Greek elektron, meaning amber. In 1751, Benjamin Franklin described electrical current as a fluid however, the basic ideas of atomistic and particulate theories of matter had been suggested by Robert Boyle nearly a century before. In his *The origins of forms and quantities* of 1666, Boyle describes his "corpuscular" theory of matter. This theory was adopted and modified by Issac Newton who added to the particulate theory of matter the possibility of attraction between particles<sup>[5]</sup>. Laws governing the interaction between charged particles were quantitatively described in the late eighteenth century through many experiments, most notably those of Charles Augustine Coulomb in 1785.

The early nineteenth century saw the subjects of electrical technology and engineering develop. In 1800, Alessandro Volta developed the Voltaic pile, or battery. This provided a means of storing electrical charge and providing a source of current for experiments into the nature and applications of electricity. In 1820, the hitherto separate subjects of electricity and magnetism were combined in Hans Christian Oersted's experiment using a wire carrying electrical current to deflect a compass

needle. This demonstrated that an electric current generates a magnetic field. Michael Faraday's experiments from 1821<sup>[6]</sup> into electricity and electromagnetic induction lead very quickly to the development of electrical power generating equipment, transformers and telegraphy for long distance communications. However, the fundamental natures of electrical current and light were and in some respects still are, subjects of contention.

Observations by Faraday in 1846 and Gustav Robert Kirchoff in 1857 suggested a connection between light and electromagnetism. James Clerk Maxwell then described light as a form of radiation containing both electric and magnetic components. His theory on The nature and propagation of electromagnetic radiation of 1864[7], addressed the wave nature of light and suggested the existence of other forms of electromagnetic radiation. In order to prove the theories of Maxwell, Heinrich Hertz conducted experiments in the propagation of what was to be termed radio-waves and by 1887 had produced equipment capable of transmitting and receiving electromagnetic waves. Experiments carried out by Joseph J. Thomson, in the late 1800's, on cathode rays lead to the discovery of the electron as the first sub-atomic particle. The ability to deflect free high energy electrons, or cathode rays, by means of electric and magnetic fields resulted from this work by 1887. In 1899, he measured the charge to mass ratio, e/m, of the electron. Further experiments, completed in 1913 by Robert A Millikan, produced an accurate measurement of the electron charge. The link between the particulate and wave nature of light, and matter, was provided by the development of Quantum Mechanics in the early 1900's [8].

After the discovery of the electron, Drude proposed a theory for metallic conduction in 1900<sup>[9]</sup>. This theory, which provided a good model for metallic conduction, was modified by Sommerfeld to include electron velocity distributions based on Fermi-Dirac statistics, rather than the classical Maxwell-Boltzman statistics. This development arose from the Pauli exclusion principle, a quantum mechanical argument. Further modifications to theories of conduction and greater use of quantum mechanics lead eventually to the band theory of solids<sup>[10]</sup>. This was an essential and fundamental step in the development of the current understanding of solid state electronic devices.

By the end of the 1920's, the subject of electronics was firmly developed. Advances in materials technology and the application of the theories and discoveries noted above lead to the invention of thermionic valves (diodes, triodes etc.), capable of rectifying or amplifying electrical signals. The main application for these "electronic" devices lay in the new fields of radio transmission and radio location, detection and ranging (RADAR). As such, by 1945, a large array of electronic circuits such as timers, flip-flops, oscillators, amplifiers (including feedback amplifiers<sup>[11,12]</sup>),

modulators/demodulators, signal detectors etc, all existed using valve based circuits. Electrical circuit theories and techniques were also well developed, to such an extent that developments in these electronic devices could be understood quickly and applied.

In 1948 the breakthrough in solid state electronics was provided by the point contact transistor, developed by Brattain and Bardeen. Some of these early developments had their root in earlier suggestions and work. For example, field effect transistors (FETs) are based on concepts first proposed in 1930 and 1935 by J. Lilienfeld and O. Heil respectively<sup>[13]</sup>. Prior to the development of the transistor, semiconductor based devices did exist but were limited to thermistors for temperature dependent applications and diodes for current rectification. The transistor, being a three terminal device, allowed control of the device state through the third terminal.

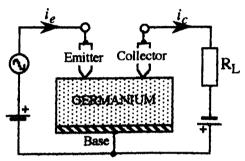

Figure 1.1. Bardeen & Brattain's Point Contact Transistor<sup>[2]</sup>.

The device created by Bardeen and Brattain, depicted in figure 1.1, consisted of a specially prepared n-type germanium block of around 10Ωcm resistivity. The emitter and collector contacts were of the point contact rectifying type while the base of the structure, the third terminal, was formed by the germanium block. This device operated as a current amplifying device, the bipolar transistor, and represented the birth of the modern semiconductor industry. Since then field effect transistors or unipolar devices, high frequency and microwave devices, high power devices and photonic devices have been developed providing a vast array of devices to choose from to fit the application at hand.

Developments in process technologies for crystal growth and wafer fabrication such as doping, etching, patterning, passivating and bonding have resulted in the planar monolithic integrated circuit. In this integrated circuit, only a few microns of the surface of the semiconductor are used to form resistors, capacitors, isolation, active devices and the interconnections. The small dimensions involved allow circuits to be fabricated on a small surface area of the semiconductor. This ability to integrate components together into a small area has resulted in the enormous success and rapid

development of the semiconductor industry.

#### 1.1.2 MINIATURIZATION OR SCALING

Scaling is a controlled form of miniaturization. Scaling requires the reduction of all device dimensions by a common factor, which can then be used to model the miniaturized device behaviour<sup>[15]</sup>. The ability of the semiconductor industry to continually increase the complexity and functionality of its products is a result of the ability to reliably scale structures. This process is driven by two basic needs; firstly the need to increase integration or packing densities of components in the circuits, secondly the need to increase the speed of operation of the circuits.

#### 1.1.2.1 INCREASED INTEGRATION DENSITY

As we have already discussed, the need to increase the integration density arises from a trade off between profitability and increased functionality. The same circuit when scaled utilizes a smaller surface area of the semiconductor thus providing more devices or circuits per unit area. This gain in device count comes at little extra cost as much the same process steps are required regardless of the circuit size. The cost of manufacture of a unit area of semiconductor is largely the same regardless of the number of components integrated on that area. This increased integration, in many cases, arises from customer demands for significant cost reductions during a product life cycle.

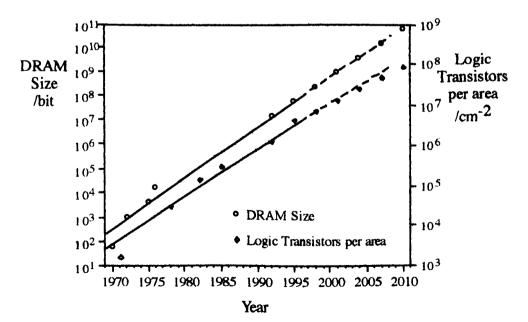

Figure 1.2. Graph of integration density vs. time.

The graph displayed in figure 1.2 gives an indication of the rate of increase in

integration density with time. Two graphs are plotted against time here; dynamic random access memory (DRAM) size and, the number of logic transistors per unit area. The points on the graphs represent the year of first introduction as a production component. DRAM size is generally taken to indicate the state of the industry in terms of raw integration capability. These circuits usually represent the highest device packing densities using the lowest geometries available at the time. The graph of logic transistor integration density is more representative of the bulk of the industry and gives an idea of the ability to integrate functional blocks, such as arithmetic logic units, I/O devices, encoders, decoders, multiplexers, analogue circuits, etc., as opposed to simple storage elements which form the bulk of the memory market.

#### 1.1.2.2 INCREASED OPERATIONAL SPEED

The need to increase the operational speed of devices also arises from the increasing functionality. Higher computational power, data handling rates and more demanding applications require higher operating frequencies from the devices making up the systems. The operational speed of microprocessors, memory chips, input/output devices, amplifiers etc. requires a decrease in device response times to take advantage of higher frequency bandwidth applications and faster information handling rates. For example, increased microprocessor power generally requires some increase in operation frequency to cope with higher information processing rates. This has a corresponding impact on access times for memories and data transfer speeds for input/output devices. Similarly, tele- and data- communication applications require speed increases to take advantage of unused higher frequency bandwidths. As digital circuits enter the telecommunications market, still higher device operational frequencies are required to adequately process and drive digital signals while still taking advantage of high frequency bandwidths, typically around 2.6GHz for current mobile telephone systems.

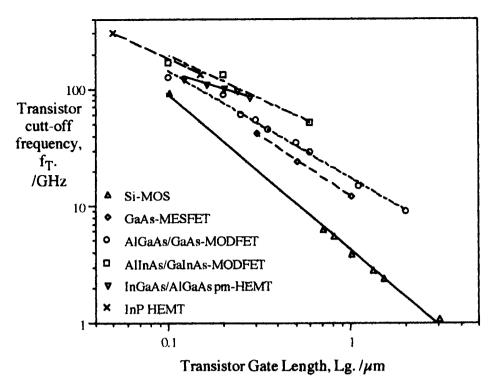

Speed increase within a transistor type is, to the greatest extent, a result of decreasing feature size. Reduction in feature size results in shorter electron paths and therefore shorter transit times. The operational frequency range of the device, i.e. the bandwidth over which useful gain exists, can be increased through device scaling. Figure 1.3 graphs cut-off frequencies for a number of FET technologies against the gate length to demonstrate this scaling effect. It is clear from this graph that speed increases can also be gained by changing the transistor material technology. For example, the higher electron mobility and lower electron effective mass in gallium arsenide based semiconductors results in a correspondingly higher operation frequency than in silicon based devices.

Figure 1.3. Graph of reported cut-off frequencies for differing technologies [15-17].

Reduction in the feature size reduces capacitances within the device leading to a reduction in the characteristic delay times. As device operational speed is generally limited through resistor-capacitor time constants, reduction of capacitances is a major goal of the scaling process. However, reduction in device size may not necessarily result in proportional scaling of parasitic capacitance elements and may result in resistance increase within the device. Therefore, careful process and device development is required to ensure the benefits of miniaturization are gained while minimizing the effect on device performance.

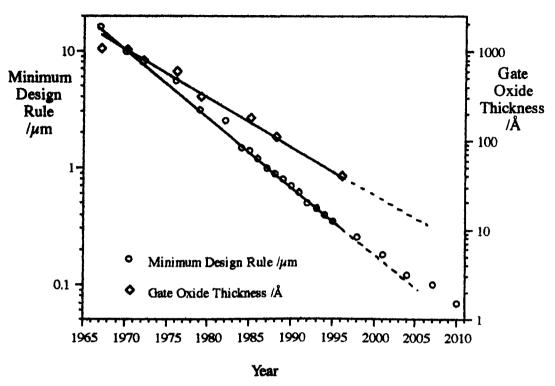

#### 1.1.2.3 SIZE REDUCTION TREND

The current industry direction is a continuation of the scaling phenomena of the last two decades. Figure 1.4 displays the reduction in two critical dimensions related to silicon metal oxide semiconductor (Si-MOS) structures. This graph shows scaling against time for both minimum design rule and gate oxide thickness. The year given is taken as the year of first introduction of a production process. Note that the gate oxide thicknesses given are derived from high speed devices and are around 60% thinner than typical production processes for the given technology design rule. The minimum design rule can be read as the minimum feature size which can be fabricated by a technology or process. This usually represents the gate length in Si-MOS devices. The thickness of the gate oxide in a MOS structure defines the gate to channel capacitance which, with

the gate resistance, is a speed limiting factor. The rate at which the gate oxide can be charged and discharged contributes to the definition of the channel current modulation upper frequency limit. Control of this oxide thickness is a fundamental process parameter, defining the uniformity of device characteristics across a wafer.

Figure 1.4. Graph of critical feature size reduction vs. time.

#### 1.1.2.4 THE FUTURE FOR SCALING

The Semiconductor Industry Association (SIA) published its "road-map" to the year 2010 in 1995<sup>[18]</sup>. This is designed to provide structure, focus and direction for the industry to overcome the hurdles which currently prevent mass production of 70nm minimum feature devices. To achieve this degree of size reduction, processing and lithography techniques must be developed beyond the current, largely experimental, state. Size reduction of this scale is not simply related to the patterning process. There are a number of technological hurdles to overcome in working at these small dimensions. For example, to make use of the projected 7 to 8 layer metal processes required, significant improvements in planarization technologies must be achieved. This is necessary not only to aid definition of the interconnect pattern but to help ensure reliability of the wiring levels by prevention of topology induced electromigration.

#### 1.1.2.5 LITHOGRAPHY FOR 70NM PRODUCTION

While other process problems require to be solved, we still require the ability to pattern

at and below the 70nm scale in a production environment. Development of photolithographic tools to meet these requirements is underway. The high industry investment in the photolithographic process and the great deal of experience within the industry tends to keep the pressure and focus on this patterning technique. The major light source in photolithography is still the mercury arc lamp. The spectral response of this lamp is well characterized and produces four usable spectral bands with the following band definitions and wavelengths; g-line (436nm), h-line (404nm), i-line (365nm) and broad-band (240 to 255nm, centre 248nm). Other sources becoming available are formed from excimer lasers which provide monochromatic light with wavelengths dependent on the gas used in the laser. For example KrF and ArF sources produce light at 248nm and 193nm respectively while F<sub>2</sub> produces light at 157nm wavelength.

Resolution,

$$R = \frac{k \lambda}{NA}$$

. [1.1]

Depth of focus, DoF =

$$\frac{k \lambda}{NA^2}$$

. [1.2]

Equations 1.1 and 1.2 give the relationships between wavelength and lens numerical aperture (NA) in terms of resolution and depth of focus. The k value in these equations represent a process dependent constant, typically taken at 0.8 for manufacturing technologies. Current lithographic practice, for  $0.35\mu$ m production, utilizes i-line and DUV (248nm) light, with NA values of 0.55 to 0.7, producing  $\pm 0.6\mu$ m to  $\pm 0.25\mu$ m depth of focus with  $0.36\mu$ m to  $0.28\mu$ m resolution. Resists used are still conventional Novolac resin based resists, with diazide as the photo active compounds. Prototyping of phase shifting masks, off axis illumination systems, and various wave-front engineering methods to gain resolution and contrast enhancements from the current exposure processes are already underway[19,20]. Meanwhile, the introduction of alternative light sources, such as excimer lasers, is designed to reduce the wavelength and therefore reduce printable feature sizes. However, development of new resists and processes is becoming essential to meet the demands of these advanced photo-lithographic systems.

Alternatively, the fields of X-ray, electron and ion beam lithography and also scanning probe lithography may yet provide solutions to these processing needs. However these are currently slow and largely experimental processes which do not fit within high volume semiconductor production environments. X-ray lithography has demonstrated feature dimensions of less than 20nm but mask fragility and manufacture is a serious problem for this technology<sup>[21]</sup>. With ion beam lithography, ultimate resolution is poor,

and may not reliably supply feature sizes below the  $0.1\mu m$  range. More encouragingly, electron beam lithography is capable of producing feature sizes into the sub 10nm regime but it is hampered by a slow, sequential, exposure process and slow resists, particularly at these small structure sizes. Finally, experimental scanning probe lithographic techniques are too slow to be considered as viable, production worthy technologies in their current state.

#### 1.1.2.6 TRENDS IN WAFER SIZE

One further feature of the scaling process is the effect on wafer size used within a process. As control of process parameters, such as film thicknesses, device dimensions, oxide thicknesses etc. becomes more and more critical, uniformity across a wafer becomes more important. Figure 1.5 depicts the trend towards increasing wafer size within the industry. This trend arises from two main sources; reduction of process edge effects and compensation for increasing die size. Most processes employed in device fabrication exhibit variations across the wafer diameter. These variations are generally greatest at the wafer extremities. High process variability at the wafer edge results in low device yield within these areas. In order to decrease the area affected by this type of variation, larger wafer diameters can be employed to provide a larger central wafer area, and comparatively smaller edge area. Thus increasing the circuit vield.

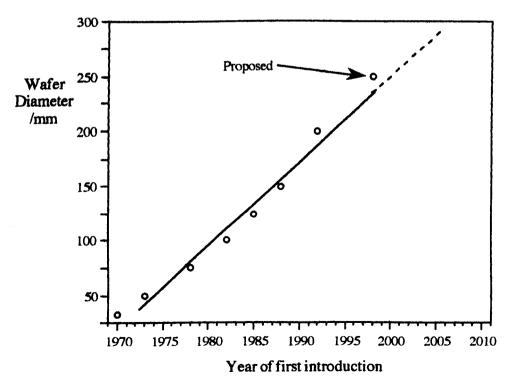

Figure 1.5. Wafer diameter increase with time.

In terms of the size increases, larger wafers are required to maintain profitability through the working die count at the end of the process. In terms of yield, there exists an exponential relationship between maximum possible yield and the die area [22]. Increasing the die area reduces the probable yield and therefore requires more silicon area to produce the same number of devices. The introduction of larger wafer diameters is mainly driven by the increases in die size. For example prototype 1GBit DRAMs have been fabricated with die sizes of  $18 \times 25 \text{mm}^2$ , and current microprocessor sizes are typically of the order of  $15 \times 15 \text{mm}^2$  or greater. The Digital Equipment Corporation Alpha processor, for example, is around  $22 \times 22 \text{mm}^2$ . As these are using minimum geometries of  $0.5\mu\text{m}$  to  $0.35\mu\text{m}$ , the devices are sensitive to particle diameters down to at least half the minimum geometry [23], that is  $0.25\mu\text{m}$  to  $0.12\mu\text{m}$  diameter. These device dimensions demand at least 200mm, if not 250mm, diameter wafers to maintain profitable working die counts per wafer.

#### 1.1.3 LIMITATIONS TO DEVICE SCALING

The trends discussed in the previous section have been driven predominantly by the technologies behind the silicon MOSFET. However, questions arise related to the fundamental limits of device scaling from two main areas. The first is simply in relation to the deep sub-micron dimensions being employed, while, secondly, we are concerned about the increasing electric field strengths which exist in smaller devices.

Reduced device dimensions require increased control of both linewidth and pattern registration. This not only places tighter requirements on the lithographic tooling, in terms of resolution, stability and registration accuracy, but also on the resist process, in terms of dimensional stability, contrast, resolution and process latitude. As device dimensions shrink, increased doping levels are required in smaller areas to reduce the size of depletion regions within the device. This leads to a degradation of the carrier mobility, resulting in relatively slower devices. As semiconductor-semiconductor junction dimensions become smaller and shallower, with bipolar technologies in particular, reduced thermal budgets come into force in the fabrication process. Each thermal cycle that a device is exposed to results in diffusion of all dopants in the structure. If careful process design and control are not carried out, this leads to excessive broadening of device regions. Again, as the devices get smaller the contact and spreading resistances within the device can limit the advantages gained by scaling.

Coupled with reduced dimensions is the question of increased field strength. Increasing the field strengths can result in electron velocity saturation, inversion layer broadening, lower voltage breakdown of pn junctions, lower electromigration limits and tunnelling through the thin gate insulator. These effects result in reduction of the speed increase on scaling, lower operating voltages, lower current carrying and power handling capacity, leakage between gate and channel portions of the device and higher susceptibility to noise.

Other limits to the scaling process arise from considering the energetics of device operation and quantum mechanical effects where small dimensions are involved. In terms of the energy relations, a major limit is imposed by the thermal energy of carriers in a device structure. The energy difference between logic states must be large when compared with this energy. This limit is particularly relevant when we are considering low voltage device operation in order to overcome high field effects. Where we have an energy difference between logic states of  $\Delta E_5$ , the probability of a thermal fluctuation of equal energy within the circuit or device response time,  $\tau$ , is given by the Boltzmann relation [24]:

$$P = exp - \frac{\Delta E_s}{k_B T},\tag{1.3}$$

resulting in a failure rate determined by:

$$\Gamma_f = \frac{1}{\tau} exp - \frac{\Delta E_s}{k_B T}.$$

[1.4]

expressed in failures per unit time per device. In order to ensure a low probability of error due to thermal fluctuations, energies of  $\Delta E_s \approx 100 k_B T$  are required. Thus, classical device operation must use state voltage differences of at least 2.6V in order to operate with low error rates at room temperature. Similarly, when examining new device phenomena, the energy scale of the process involved must have this magnitude of energy associated with it for useful operation at the temperature in question.

Similarly, quantum limitations on device operation are energy scale dependent. As with thermal limitations, we require the characteristic energy of the quantum process to be greater than other energy scales in the system before these effects become significant. However, it is possible for classical MOSFET structures to fail through tunnelling. In particular, if the gate oxide becomes thin enough tunnelling between the gate and channel can easily provide current of the same order of magnitude as the device channel current. In this instance severe modification to device operation results. It is important to note that on  $0.35\mu m$  MOS processes the gate oxide thickness is some 4nm, see figure 1.4. This dimension is within reach of the limit at which the gate oxide becomes thin enough to allow significant gate to channel leakage by quantum mechanical tunnelling.

#### 1.2 QUANTUM EFFECT DEVICES

Developments in the fields of molecular beam epitaxy (MBE) and metal-organic chemical vapour deposition (MOCVD) have resulted in a great deal of investigation into the properties of ultra thin semiconductor films. The use of advanced lithographic techniques to laterally pattern these structures and other materials to nanometre dimensions has resulted in a vast amount of work into nanometre scale devices and structures. This work has looked at a number of subjects; firstly the characteristics of conduction in specially fabricated, pure, ultra-thin materials and layers, secondly the basic fundamentals of the conduction processes in low dimensional structures or high purity materials and, thirdly, the possibility of utilizing these materials or conduction processes for new electronic devices.

MBE and MOCVD techniques allow interfaces between different materials to be defined on an atomic scale, producing well controlled, abrupt junctions between differing material types. Such control of the purity and composition of the material exerts control over the electrical and optical properties of the fabricated structures. In this way, techniques such as band-gap engineering [25] can be employed to determine the fundamental physical characteristics of a semiconducting material.

These techniques are in direct contrast with more traditional techniques for manipulating semiconductor-semiconductor interfaces, such as diffusion, ion-implantation, etching (both wet and dry), chemical and physical vapour deposition and sputtering. Interfaces produced by these techniques are neither atomically defined nor abrupt. Such interfaces tend to be diffuse, even where abrupt junctions are the intention, with the junction region extending over a number of inter-atomic spacings, typically tens of Angstroms at best. Similarly, metal-oxide, metal-semiconductor and oxide-semiconductor interfaces are neither uniform, well controlled, abrupt nor pure. These deficiencies result in a reduction in carrier mobility through crystal imperfections, surface roughness and strain. The amorphous nature of some of the deposited films used in semiconductor technologies results in further disorder within the device system and further degradation of the charge transport properties.

#### 1.2.1 REDUCED DIMENSIONALITY

Reducing the dimensions of an electronic structure leads not only to changes in the density of states, but also to the splitting of energy levels in the band. This becomes an important effect when the structure size approaches or becomes less than the electron

wavelength in that material. At this point the energy levels in the band structure separate, and the dimension which has been reduced is effectively removed from the device. In this way, a three dimensional material can be turned into a two dimensional electronic system, i.e. an electron plane - or gas. Further dimensional constraints reduce this to either a one-dimensional systems, a wire, or a zero-dimensional system, a dot.

#### 1.2.1.1 2 DIMENSIONAL SYSTEMS

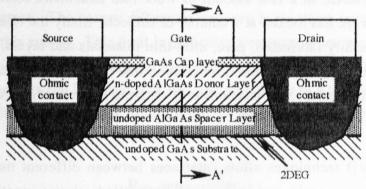

Physical device structure

Energy band diagram sketch, through section AA'

Figure 1.6. Two dimensional electron gas formation, and the MODFET

Two dimensional electron systems are, perhaps, the most common of reduced dimensionality systems. Removal of one dimension, typically that perpendicular to the surface, leaves what is termed a two-dimensional electron gas, or 2DEG, in the plane parallel to the surface. These structures are commonly used as a basis for studies in high purity, long electron mean free path materials and low dimensional device physics. Other uses for this type of material system have been in the development of high electron mobility transistors (HEMTs) for high speed electronic systems. Figure 1.3 displays cut off frequencies for four types of 2DEG transistor technologies, two formed as modulation doped FETs (MODFETs) and two as HEMT structures.

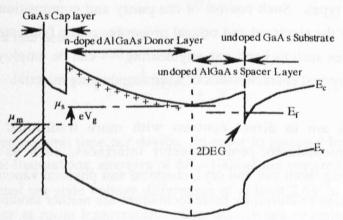

The electronic systems which form the basis of studies into quantum effects in semiconductors are generally derived from MBE grown heterostructure layers. Within these layers, two dimensional electron gas formation is achieved through arrangement of the layer structure. The MBE layered approach can also be used to form quantum well structures as the layers are grown through the use of large and small energy gap materials. It is possible to utilize these layers through both perpendicular and parallel conduction. Where parallel conduction is employed, the device types are generally conventional operation transistors such as HEMTs, MODFETs, or laterally patterned low dimensional structures.

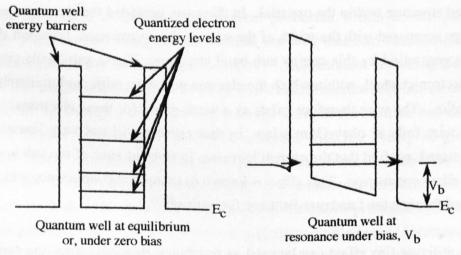

Where the charge transport is arranged to be perpendicular through the layer structure, a large number of transistor actions can be developed. Heterojunction bipolar transistors and hot electron transistors are commonly formed on these layers, as are resonant tunnelling diodes and transistors. With the resonant tunnelling devices, the ability to controllably form quantum wells within the material layers defines the resonant states within the device. The use of resonant tunnelling devices provides the possibility of device operation into the terahertz regime due to the strong negative differential resistance regions created in the device current-voltage curves through the resonant regions<sup>[26]</sup>.

Figure 1.7. Quantum well layer formation and band diagram.

#### 1.2.1.2 1 DIMENSIONAL AND ZERO DIMENSIONAL SYSTEMS

Reduction of either the x or y dimension results in sub-band creation in the remaining dimension and the creation of a one dimensional conduction channel. These systems are exemplified by quantum point contacts (QPCs) and 1D wires. QPCs like 1D wires exhibit resistance quantization and can be used as resistance standards or alternatively

16 Introduction

to define zero dimensional and other device types. Quantum wires have been used in studies on ballistic electron conduction<sup>[27]</sup> and localization<sup>[28]</sup>. However, particularly with QPCs, fluctuation effects which are manifestations of sample dependent universal conductance fluctuations<sup>[29]</sup> can be exhibited due to temperature effects, impurities and device non-idealities. These effects tend to limit the fabrication repeatability and therefore usefulness of such devices.

Zero dimensional systems provide resonant tunnelling and single electron tunnelling effects. In particular with zero dimensional systems coupling of energy into the structure is achievable through the energy levels which exist within the quantum wells created.

#### 1.2.2 QUANTUM DEVICES

Quantum effect devices are those whose operation and characteristics depend in some manner on quantum mechanical effects. These effects can arise from reduction of device dimensions or from quantum mechanical processes occurring with sufficient energy to become the dominant process in the device operation.

As previously mentioned, reduction in device geometries leads to a splitting of the energy band structure within the material. In this case, provided the electron mean free path is large compared with the width of the wire or the constriction, transport through the wire is controlled by this energy sub-band structure. These sub-bands provide a ballistic electron channel, within which the electron will exist with predominately wave characteristics. The wire therefore exists as a wave-guide for these electrons. At this point, the wire fails to obey Ohm's law, in that current will not vary linearly with voltage. Instead, we find that the current increases in steps as each of the sub-bands are opened to allow conduction. This effect is known as quantized conductance which may be described through the Landauer-Büttiker formalism<sup>[30]</sup>.

Structures utilizing this effect can be used as resistance standards since the resistance value depends on physical constants i.e.  $R_q=h/e^2$  per channel. Here we see a single conduction channel has a resistance of  $25.8k\Omega$ , or  $12.9k\Omega$  where there is no electron spin selection within the channel. This enforces a current limitation of  $77\mu$ A/V on any conduction channel defined in such devices, in the absence of magnetic effects. Another feature of this sub-band structure is the ability to use the constriction as an energy filter. The conduction channels that exist through the structure have given energies. In order for an electron to traverse the constriction or wire it must have the same energy as the channel. Therefore, transmitted electrons will exhibit a tightly

defined energy spectrum. In a similar vein, it is possible to use these types of structure to directly couple light of given wavelengths into an electrical circuit through the use of detectors formed from these structures.

The behaviour of structures in this quantum ballistic regime is termed non-local, in that the presence of a structure which causes an interference effect will affect the conductance behaviour in other parts of the structure<sup>[31]</sup>. This is exemplified by the Ahronov-Böhm<sup>[32]</sup> effect. In this effect, the interference of electron wave-functions which have traversed different but equal length paths (around a ring in most fabricated devices) modifies the transmission coefficients of the structure. Where the electron energy is changed, by application of a magnetic field in the Ahronov-Böhm effect, oscillations in this transmission coefficient can be observed. In the Ahronov-Böhm effect, these modifications are periodic in the magnetic flux threading the loop. This is a manifestation of a change in the interference behaviour of the electron paths. Other types of interference devices are proposed and under investigation, the most successful of which are superconducting quantum interference devices which provide very sensitive measurement of magnetic fields. In order to simulate optical elements and interferometers, work has also been carried out into electrical analogues of lenses and interferometers<sup>[33]</sup> in ballistic electron conduction materials.

One of the most utilized quantum mechanical processes within device physics is tunnelling. Electron tunnelling devices include not only standard tunnelling devices, such as tunnel diodes and tunnel base transistors[34], but resonant tunnelling diodes and transistors and single electron effect devices. As a tunnel current depends on the width and height of an energy barrier, it is relatively straight-forward to envisage and understand device applications. It is this, coupled with the ability to grow thin controllable layers into material structures and pattern on small dimensions, which makes the use of resonant tunnelling diodes and transistors attractive for use in electronics. Such devices are capable of operation far above present frequencies and provide the possibility of multi-state logic, through the multiple energy levels within the device<sup>[35]</sup>. Single electron devices, which are dealt with in Chapter 2, also are promising in the possibility of large bit storage capacities and the ability to operate at low current and power levels. Another feature of these devices is the ability to operate through the use of large confinement potentials defined in small structures. In such conditions, higher energies can be utilized in the device operation, allowing high temperature operation, whereas the temperature of operation for semiconductor based quantum ballistic electron devices may well be limited to below 77K

An important aspect of quantum devices is their ability to be used in metrology

18 Introduction

applications. As the device operation depends in some form or another on fundamental constants, it is possible to utilize these devices to great effect and accuracy in measurements of voltages, currents, resistances, magnetic fields etc. Therefore, the usefulness should not be ruled out on the basis of the low temperatures required for their operation.

#### 1.3 MOTIVATION AND AIMS OF THIS WORK

An enormous amount of research and development work is being carried out around the world into reduction of current device dimensions and development of new device types and modes of operation. All of these projects have similar goals in that they aim to better understand the conduction processes, the operation of current and future device types and to provide technologies, processes, and devices for the future electronics industry. Significant progress has been made in understanding conduction processes and the implications of quantum effects within low dimensional structures. Other areas where significant progress has been made are in the fabrication and operation of devices utilizing these principles. However, a large number of new devices and operation modes have limited applicability through two main constraints; low current operation and low temperature of operation. The low operating temperature is by far the most limiting factor since buffering may be employed to overcome low current operation, although this is not an ideal solution.

The device dimensions currently being employed in semiconductor systems tend to result in quantum mechanically derived effects being observable only where noise. lattice vibrations and subsequent scattering are eliminated through reduction of their relevant energy scales below that of the effect under observation. semiconductor systems, significant difficulties arise when attempting to push device dimensions into the sub-40nm regime. At this point, the rate of change of electric field within these systems can become too low to provide adequate confinement potentials. Where the confinement potential is defined by grown structures (MBE or MOCVD), the problem is less acute as the material builds in these potentials. Where patterning is employed to make a functional device from this material, the confinement potentials become blurred and structures sizes tend to be larger than expected. For example, reactive ion etching of structures introduces damage resulting in non-abrupt surface potentials. These potentials can reach some way into the device and damage the clectrical structure being defined [36]. Similarly, where electric fields are being used to define regions within a device, the dielectric constants result in active area dimensions too large to achieve adequate confinement potentials at high temperature.

The work presented in this thesis examines a system which may be defined on a small enough scale to allow high temperature operation of single electron devices. These devices operate, as their name suggests, on the effect of only one electron. The potentials set up within the device can result in state switching controlled by the presence or absence of a single electronic charge. The benefits of such a device technology are those of ultra low power operation, multi-state logic, hyper sensitive current measurement and, potentially, enormous bit storage densities due to the very small device sizes required for this technology. Currently, around 10<sup>4</sup> to 10<sup>5</sup> electrons are used to store 1 bit of information within a DRAM memory element. In the case of single electron logic, the possibility of using one electron to store that bit, and the use of multi-state logic opens up tremendous logic and information handling possibilities for the future.

Although single electron effects have been observed with characteristic temperatures well above room temperature, these systems have generally been uncontrollable and difficult to make use of within an engineered system. Where devices have been specifically engineered, useful device applications are prohibited by low operation temperatures. The aims of this work are therefore to investigate the fabrication techniques for metal-insulator-metal tunnel junction based single electron systems with a view to decreasing the structure size and thereby increasing the temperature of operation. The goal for these aims is to achieve a fabricated single electron transistor, or electrometer, operating at 4.2K or above. The goal of 4.2K is to be seen as a first step in raising the operation temperature above room temperature.

#### 1.4 ORGANIZATION OF THIS THESIS

The work presented in this thesis divides into three main parts. Firstly, a review of the theory and development of single electron devices is given in chapter two. Secondly, fabrication techniques are presented in chapters three and four. Thirdly, chapters five and six present the work carried out on electrical measurements of the materials used and single electron device structures fabricated during this work. To conclude this thesis, chapter seven reviews and discusses the work in terms of its aims and results and presents areas for further work and investigation.

Discussion of the theory of single electron effects, given in chapter two, divides into three main parts. Firstly, an introduction to the theory of tunnelling is given, with a discussion of metal based devices. The theory of single electron tunnelling devices is reviewed, with the emphasis being on normal metal, as opposed to superconducting, single electron devices. Finally, a review of the work carried out in the development of

usable single electron structures is given.

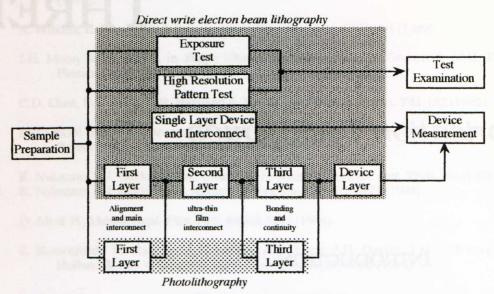

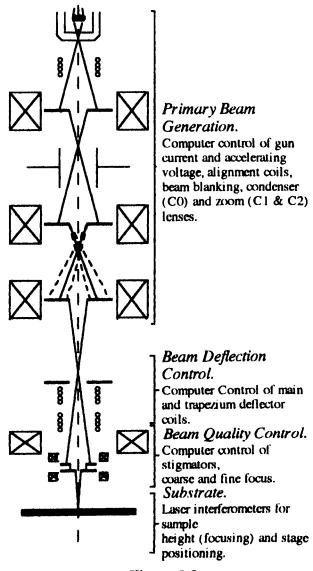

The experimental work documented in this thesis is presented in chapter three to six, and the order of the work requires some description and background at this point. Due to the small scale of the structures being fabricated in this work, it is necessary to fabricate lead frame structures to electrically connect to the devices. While not directly relevant to the devices of interest this is an enabling technology without which the devices could not be measured. Chapter three, therefore, discusses the general fabrication techniques used in this work with specific reference to the interconnect lead frame as an example. This allows presentation of the general fabrication details without confusion with the techniques involved in ultrasmall device fabrication. Chapter three concludes with a description of the process used to fabricate suspended masks and a detailed description of all process flows used in this work.

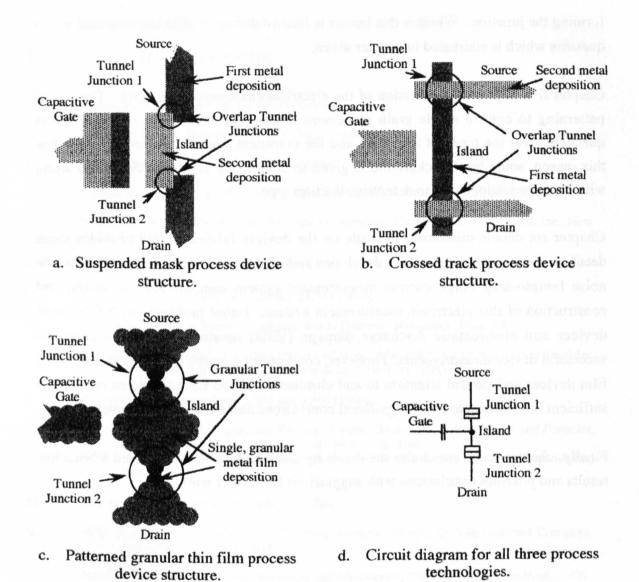

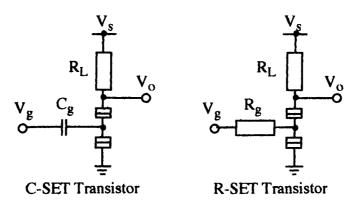

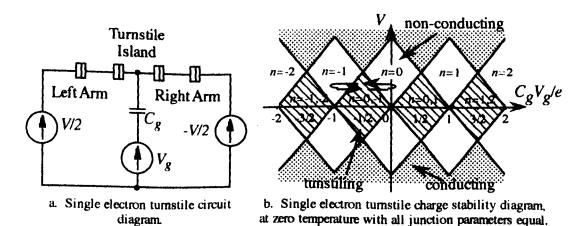

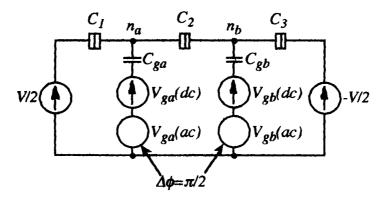

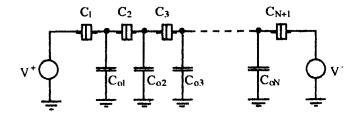

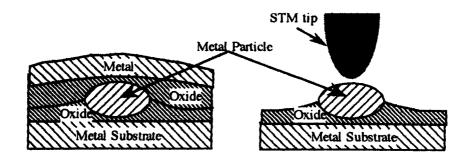

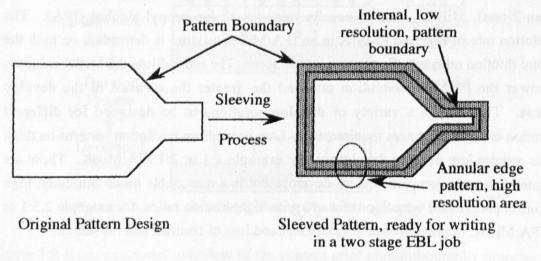

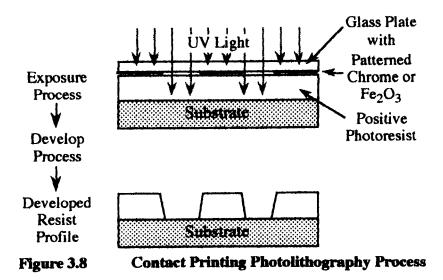

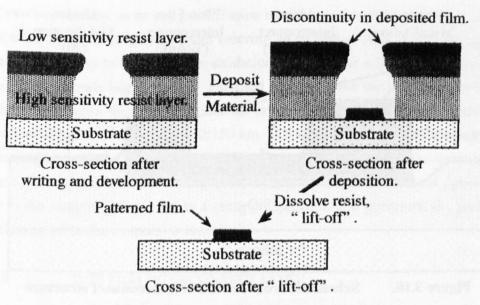

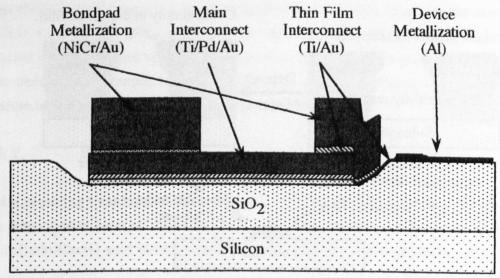

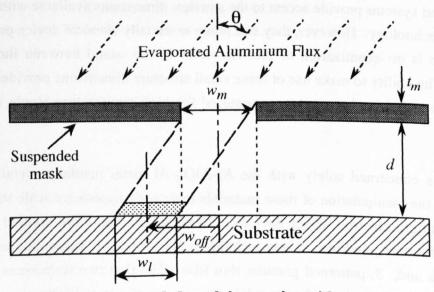

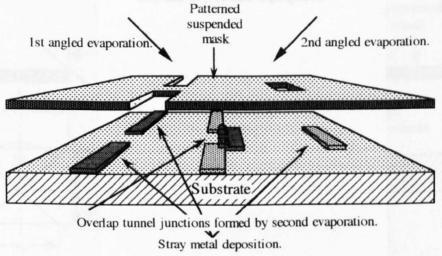

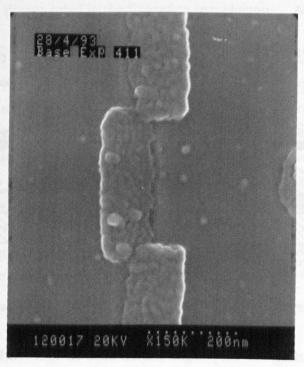

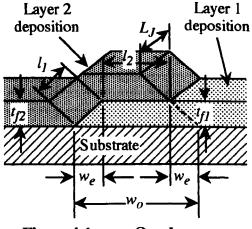

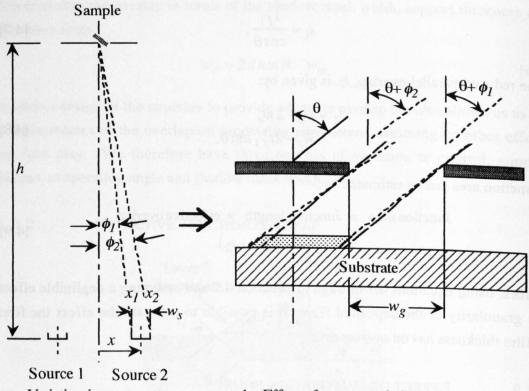

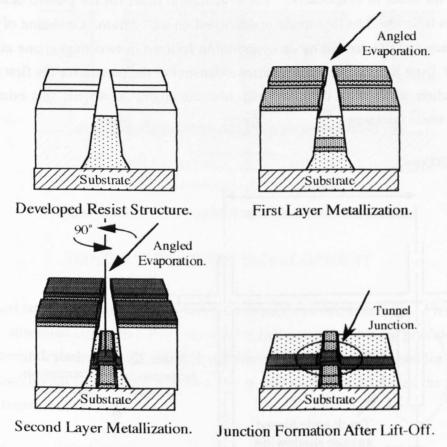

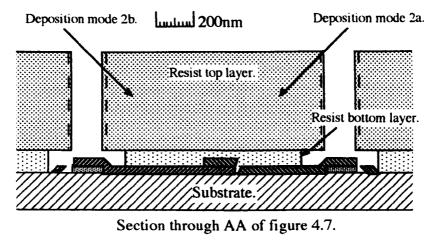

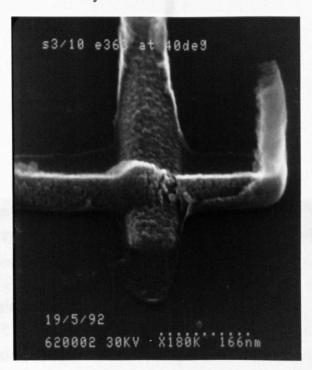

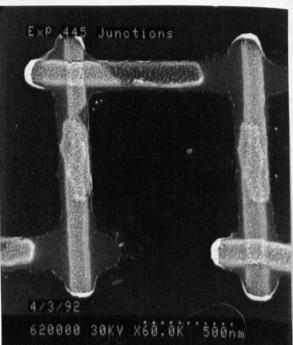

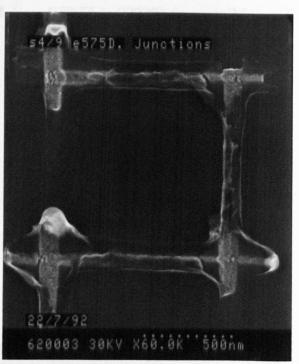

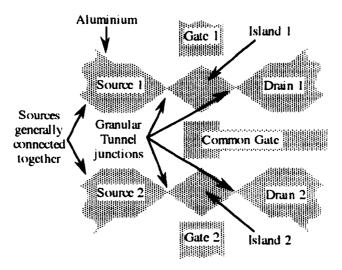

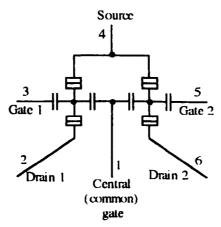

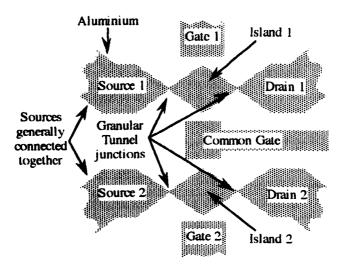

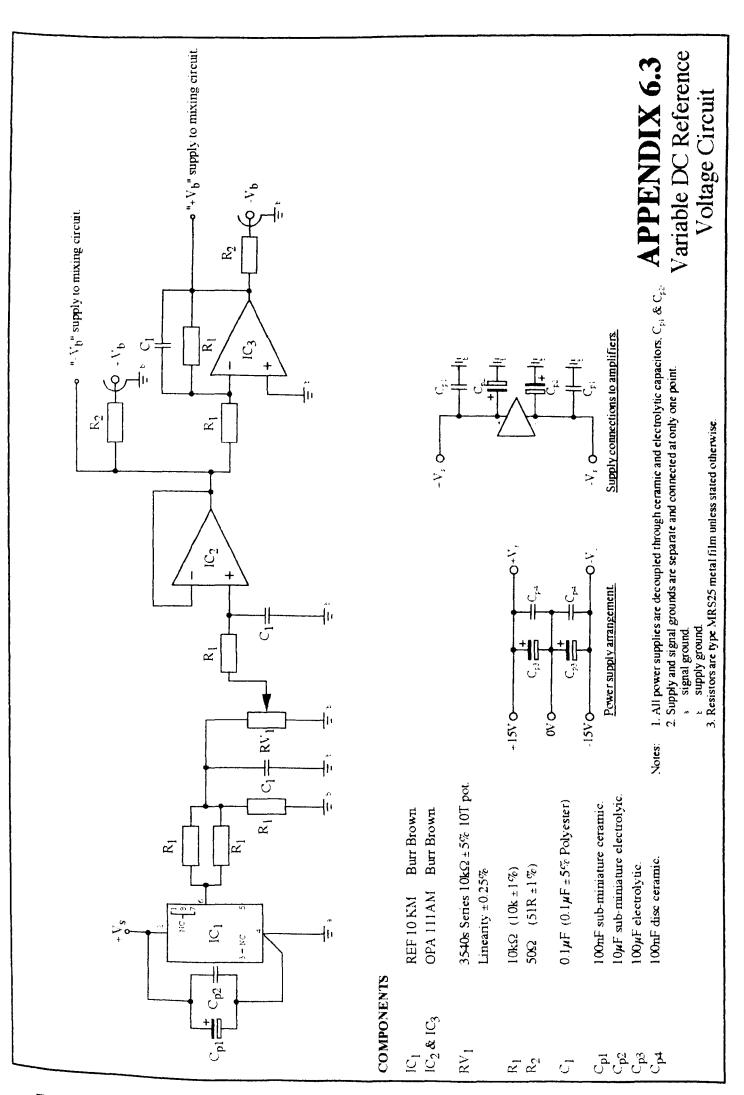

Chapter four deals with the detailed fabrication and characterization work for the three device technologies under investigation. The first technology creates overlay tunnel junctions using shadow mask techniques and is described in detail in section 4.2. The shadow mask can be used with multiple angled evaporations to selectively deposit areas of the pattern and produce an overlap between two layers of metal. Provided the underlying layer is oxidized to form a tunnel barrier, a tunnel junction is formed in the overlap. Figure 1.8a depicts the device structure formed by this technique where a single electron transistor (gated island, double tunnel junction) is to be formed. The circuit diagram for a single electron transistor is given in figure 1.8d for reference.

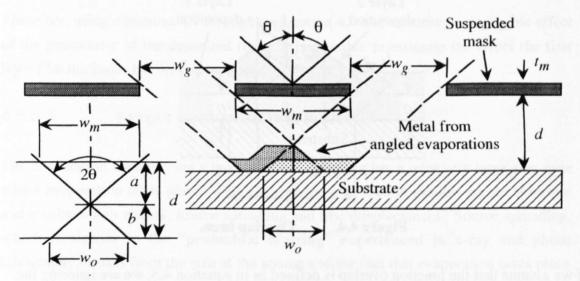

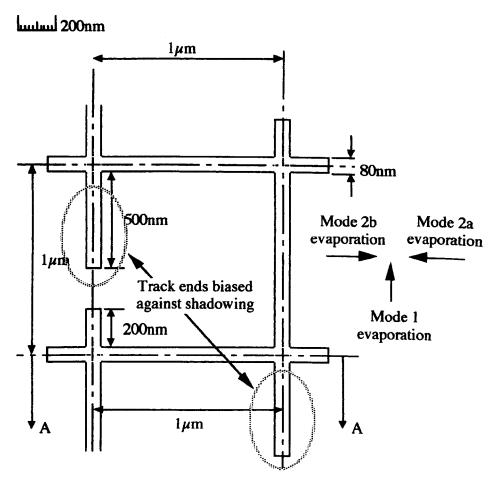

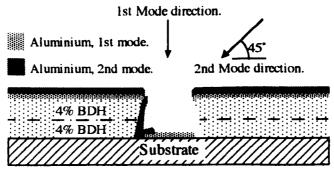

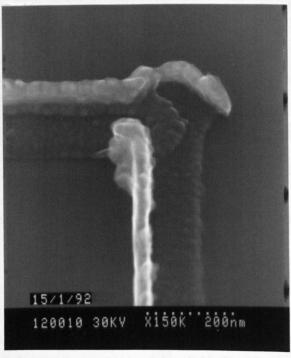

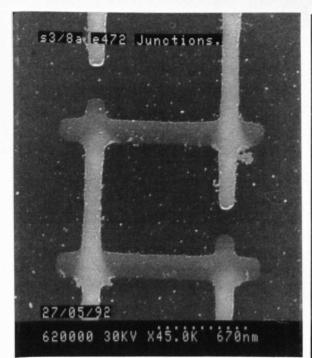

The suspended mask technique is a standard technique and was adopted in this work to provide a known working process for development of overlap tunnel junction. The process does, however, limit the flexibility of the pattern and produces unwanted areas of film deposition. To attempt to remove the difficulties with the suspended mask process, the crossed track process was investigated. In the crossed track process, multiple angled evaporations are again used, but with resist shadowing is employed to produce overlap tunnel junctions where the resist tracks cross. The structures to be formed with this process are depicted in figure 1.8b. This process provides a planar structure with the only pattern constraint being that tunnel junctions are formed by the overlap, or crossing, of perpendicular metal tracks. Again oxidation between the deposition of the two metal layers results in the formation of a tunnel barrier. This process exhibited a number of significant problems and was never used to fabricate devices for electrical measurements. However, the problems manifested by the process partly lead to the development of the third process investigated. The process, investigation work and difficulties are discussed in detail in section 4.3.

Figure 1.8 Schematics of device structures under investigation.

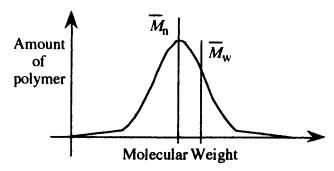

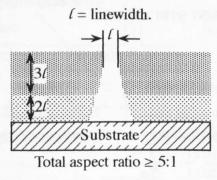

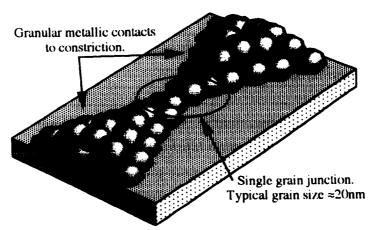

The third process under investigation used patterned granular thin films. This process attempts to form tunnel junctions in the connection between grains in the aluminium film. Figure 1.8c depicts the structure of devices formed with this process. The aim with this process was to produce the smallest possible tunnel junctions using aluminium films, thereby reducing the junction capacitance to raise the transition temperature for observing single electron effects. Both the previous processes exhibited unreliable processing when the tunnel junction size was significantly reduced therefore, the patterned granular thin film process was seen as the best possibility for high temperature single electron effects. As this technique requires the patterning process to define the grain positions and to some extent size, a large amount of film and pattern characterization work was required. This work is documented in section 4.4, along with the technique itself. The tunnel junction in this process is formed by creating an oxide film on the grain surface. This should result in an oxide barrier between the grains

22 Introduction

forming the junction. Whether this barrier is formed during or after the evaporation is a question which is addressed in chapter seven.

Chapter five begins the discussion of the electrical characterization work. The use of patterning to control single grain placement in the film and device structure raises questions over the types of film used and the dominant conduction mechanisms. For this reason, some brief background is given to conduction effects in thin films along with characterization work to determine the film type.

Chapter six details measurement made on the devices fabricated and provides some detail on the measurement system developed and used in this work. The need for a low noise fempto-amp range current measurement system necessitated the design and construction of this electronic measurement system. Initial problems with fabricated devices and electrostatic discharge damage (ESD) resulted in a low number of successful device measurements. However, concentration on the patterned granular thin film devices and careful attention to and elimination of the ESD problems resulted in sufficient information to allow significant conclusions about the device character.

Finally, chapter seven concludes the thesis by discussion of the device and fabrication results and provides conclusions with suggestions for further work.

#### 1.5 REFERENCES

- 1. R. Amatruda, Semicond. Int. 19(10),63 (1996).

- 2. J. Bardeen & W.H. Brattain, Phys. Rev. 74,230 (1948).

- 3. W. Shockley, Bell. Syst. Tech. J. 28,435 (1949).

- 4. D.Halliday & R.Resnick, Physics, 3rd Ed., Ch. 26, p565, J Wiley & Sons, Toronto, 1978.

- 5. H.M. Leicester, The Historical Background to Chemistry, Ch.12. Dover Publications Inc., New York, 1971.

- B. Bowers, IEE Review. 37(9),291 (1991). 6.

- 7. J.C. Maxwell, Proc. Royal Soc. London 13,513 (1864).

- 8. B.H. Bransden & C.J. Joachain, Introduction to Quantum Mechanics, Ch.s. 1 & 2., Longman Scientific and Technical, Essex, 1989.

- and R. Eisberg & R. Resnick, Quantum Physics of Atoms, Molecules, Solids, Nuclei and Particles, Chs. 1 to 5., 2nd Ed., John Wiley and Sons, New York, 1985.

- 9. P. Drude, Annalen der Physik 1,566 and 3,369 (1900).

- 10. R. Eisberg & R. Resnick, Quantum Physics of Atoms, Molecules, Solids, Nuclei and Particles, Ch. 13., 2nd Ed., John Wiley and Sons, New York, 1985.

- and N.W. Ashcroft and N.D. Mermin, Solid State Physics, W.B. Saunders Company, Philadelphia, 1976

- 11. H.S. Black, Bell System Tech. J. 14(1),1 (1934).

- 12. H.W. Bode, Network Analysis and Feedback Amplifier Design, D. Van Nostrand Company, Princeton, New Jersey, 1945.

- 13. See G.W. Drummer, Electronic Inventions and Discoveries, 2nd Ed., Pergammon Press, 1978.

- 14. J. Mavor, M.A. Jack & P.B. Denyer, Introduction to MOS LSI, Ch. 3., Addison-Wesley Publishers Ltd, 1983.

- 15. S.M. Szc, High Speed Semiconductor Devices, Ch. 1, John Wiley & Sons Inc., New York,

- 16. N. Cameron, H. McLelland, M.C. Holland, M.R.S. Taylor, S.P. Beaumont., IEE Colloquium on "Modelling, design and applications of MMICs, IEE Digest No: 1994/092, Professional group E12, (1994).

- 17. C.M. Snowden, IEE Electronics & Communication Engineering Journal. 8(2),51 (1996).

- 18. R.M. Burger, J.A. Glaze, T. Seidel & O. Williams, Solid State Technol. 38(1),38 (1995).

- 19. M.D. Levenson, Solid State Technol. 38(2),57 (1995).

- 20. M.D. Levenson, Microlithography World. 1(1),6 (1992). G. Cognić. Microlithography World. 1(1),13 (1992).

- and

- H.G. Craighead, Proc., 38th Scottish Universities Summer School in Physics, eds., J.H. Davies 21. & A.R. Long, IOP Publishing, Bristol, England, 1992.

- S.M. Szc, Semiconductor Devices Physics and Technology, p435, John Wiley & Sons, New 22. York, 1985.

- 23. J.B. Khare, W. Maly, S. Greip & D. Schmitt-Landsiedel, IEEE. Trans. Semicond. Manufacturing 8(2),195 (1995).

- 24. C. Mead & L. Conway., Introduction to VLSI systems, Ch. 9., Addison-Wesley Publising Co., Reading, Massachusetts, 1980.

- 25. E.H. Li & B.L. Weiss, IEE Electronics and Communication Eng. J. 3(2),63 (1991).

- 26. M.A. Reed, W.R. Frensley, R.J. Matyi, J.N. Randall & A.C. Seabaugh, Appl. Phys. Lett. 54,1034 (1989).

- D.A. Wharam, T.J. Thornton, R. Newbury, M. Pepper, H. Ahamed, J.E.F. Frost, D.G. Hasko,

D.C. Peacock, D.A. Ritchie & G.A.C. Jones, J. Phys. C. 21,L209 (1988).

- 28. G. Bergmann, *Physics Reports*. 107(1),1 (1984).

- H. Haucke, S. Washburn, A.D. Benoit, C.P. Umbach & R.A. Webb, Phys. Rev. B. 41(18),12454 (1990).

- 30. M. Büttiker, Phys. Rev. Lett. 57,1761 (1986).

- 31. C.P. Umbach, P. Santhanam, C. van Haesendonck & R.A. Webb, Appl. Phys. Lett. 50,1289 (1987).

- 32. C.J.B. Ford, T.J. Thornton, R. Newbury, M. Pepper, H. Ahmed, C.T. Foxon, J.J. Harris & C. Roberts, J. Phys. C (Solid State Physics), 21,L325 (1989).

- 33. C. Weisbuch & B. Vinter, Quantum Semiconductor Structures, Ch. 6., Academic Press Ltd. London, 1991.

- 34. S.M. Sze, Physics of Semiconductor Devices, Ch. 9., John Wiley & Sons. New York, 1981.

- 35. F. Capasso & S. Datta, Physics Today. 2,74 (1990).

- 36. M. Rahman, Electron Transport in Dry-Etched n<sup>+</sup>-GaAs Nanostructures, Chs. 3 & 4., Ph.D. Thesis, University of Glasgow, 1992.

## CHAPTER Two

# Tunnelling and Single Electron Devices

#### 2.1 Introduction

Devices which operate on the basis of single electron transport are possible through the process of quantum mechanical tunnelling and its impact on the charging energy of a tunnel barrier. In this chapter the tunnelling process is introduced in terms of the wave mechanics formulation of quantum theory. After discussing the tunnelling effect and results relevant to aluminium tunnel junctions, the subject of single electron tunnelling is developed. Most of the references cited develop the theory in a more general sense, including single electron effects observable in superconducting systems. Studies of single electron effects in semiconducting systems also exist but these are not discussed in detail within this work. Reviews by Beenakker[1], van Houten[2] and Kastner[3] with papers by Scott-Thomas[4], Meirav[5] and Kouwenhoven[6] provide a good introduction to the semiconductor field. Effects observed through scanning tunnelling microscope probing of granular films are mentioned, where relevant, as these fit easily into the theory for normal metal systems.

The theory discussed in this chapter follows the development by Averin and Likharev [7] in 1985/86, which has become termed the orthodox theory of single electron tunnelling. Various modifications have been added to the theory to account for other effects, such as noise (both inherent and coupled), leakage, environmental effects, effects in more

complex junction systems and effects in 2-3 dimensional systems. As such, the field has become subject to an increasingly large number of publications over the past ten years. Discussion of these additional effects is limited to their main points and conclusions.

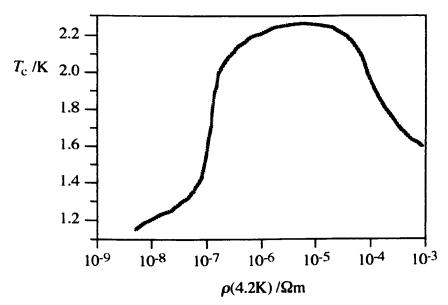

The limitation of the discussion to normal metal systems is due to the aims of this thesis, as set out in section 1.3. Use of the available lithographic capabilities to reduce device dimensions to the extent that higher temperature operation of these devices is possible precludes the use of superconducting systems in this work. This work solely employs aluminium based devices having a superconducting transition temperature of  $T_c\approx 1.178$ K for bulk Al, with a  $T_c$  as high as 3.5K reported in granular Al films<sup>[8]</sup>. As we are aiming for greater than 4.2K operation (the temperature of liquid <sup>4</sup>He at latm. pressure), superconductive effects are not relevant in these devices.

This chapter divides into two sections and serves as a fuller introduction to the background and work of this thesis. Section 2.2, covers the theory of tunnelling and some relevant tunnelling experiments. Section 2.3 discusses single electron tunnelling by a brief introduction to the theory and discussion of the effects observed. Where relevant the discussion points out the potential device applications and circuit structures with a description of their operation. At the end of section 2.3, some discussion of the applications of single electron devices and technological requirements for useful single electron devices is given.

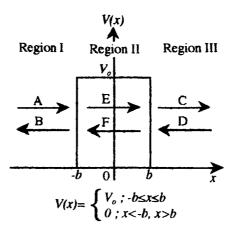

# 2.2 TUNNELLING

Development of the theory of quantum mechanics led very quickly to an explanation for the phenomenon of tunnelling. Application of quantum mechanical ideas to the calculation of particle behaviour in a region with a potential barrier provided contradictory results to that of the classical mechanics description. The theory of tunnelling demonstrates the ability to penetrate barriers which are, classically, impenetrable. In the classical description, a particle with insufficient energy to overcome a barrier will be reflected. Also, particles with sufficient energy are able to freely cross the barrier with no impact on their state. In this instance, the particle traverses the barrier with unity probability. Conversely, in a quantum mechanical description a particle with insufficient energy retains a finite probability of traversing the barrier. Where the particle has sufficient energy to cross the barrier, quantum mechanics does not guarantee unity probability of transmission. Quantum mechanically, the probability of transmission depends upon exponential functions of the barrier height and width. Barriers which are wide or high may yield a vanishingly

small, but non-zero, probability of transmission.

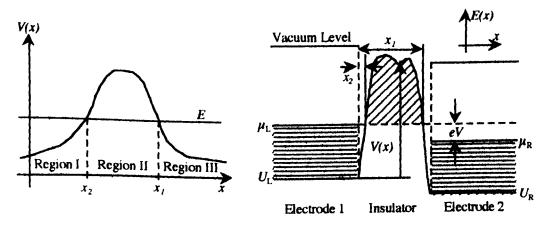

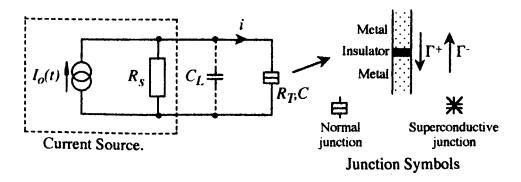

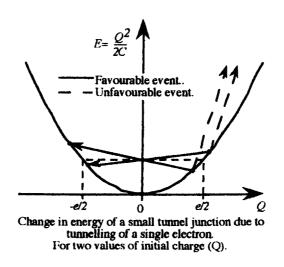

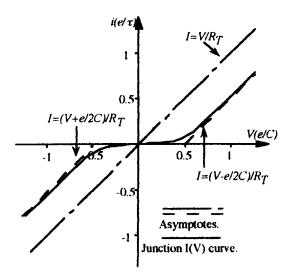

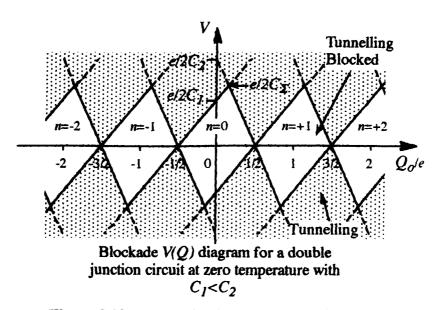

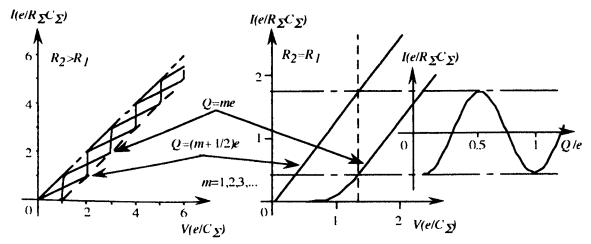

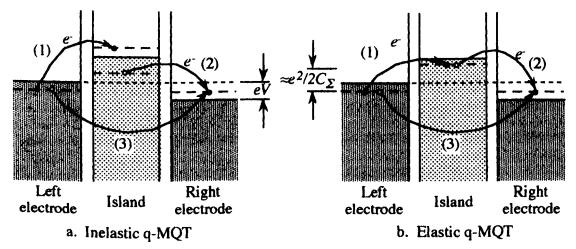

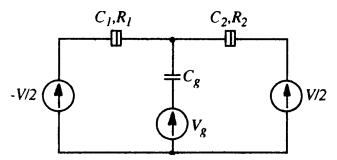

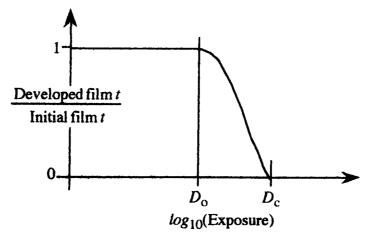

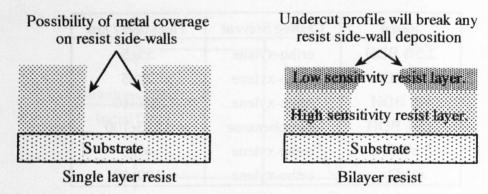

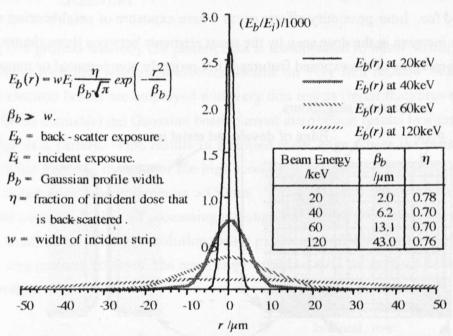

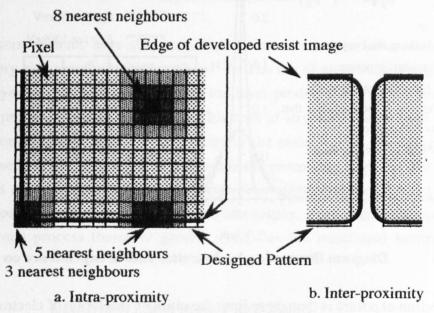

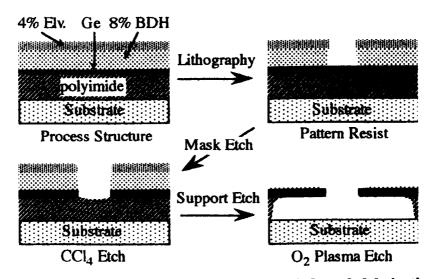

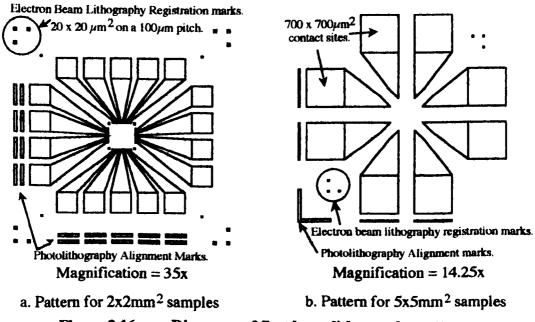

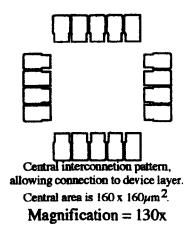

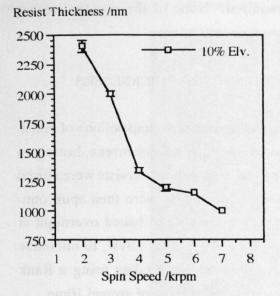

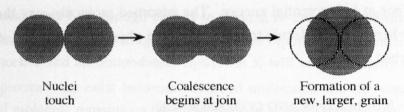

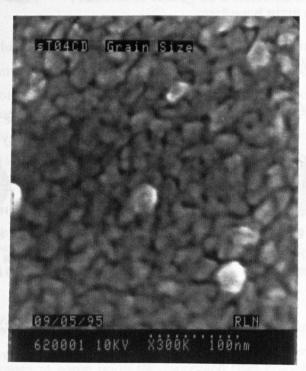

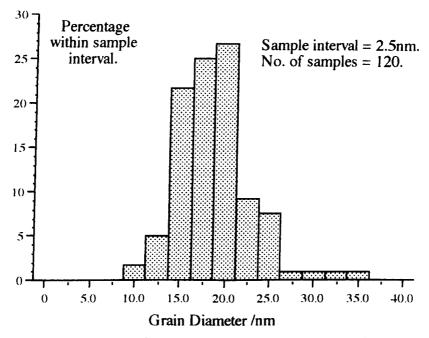

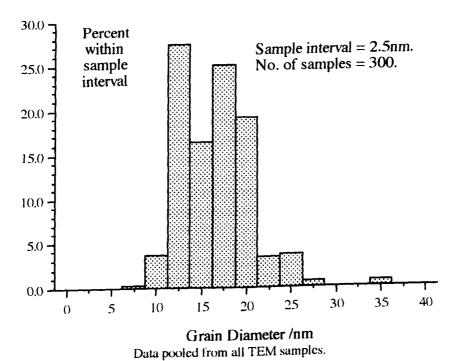

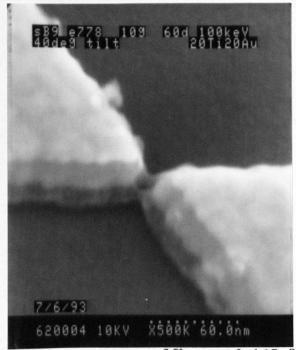

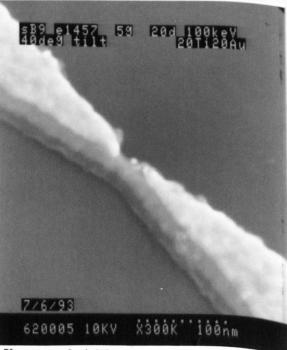

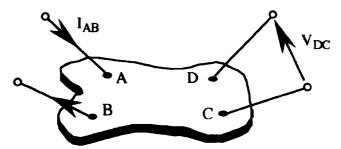

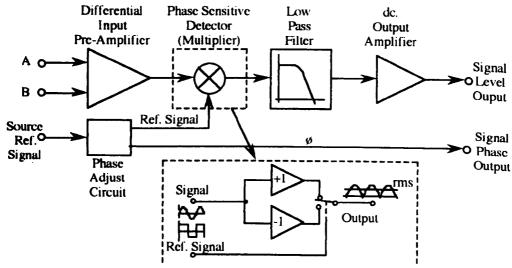

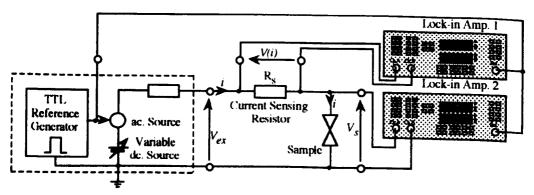

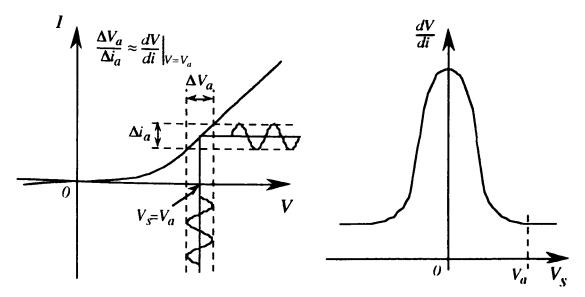

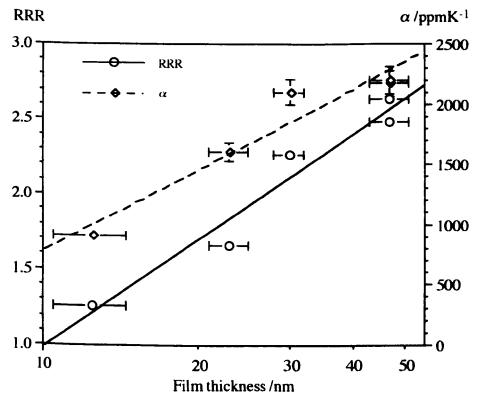

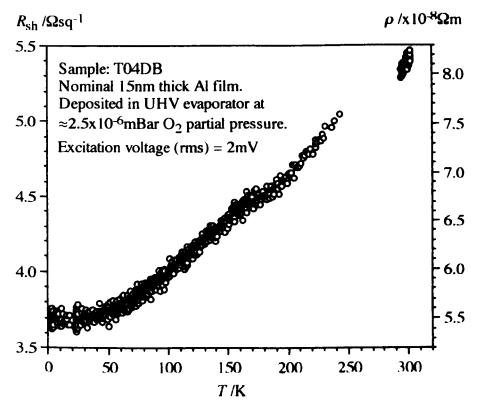

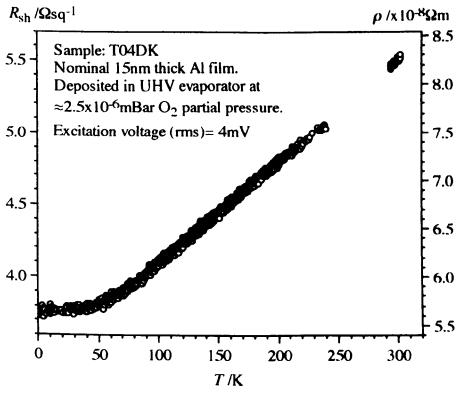

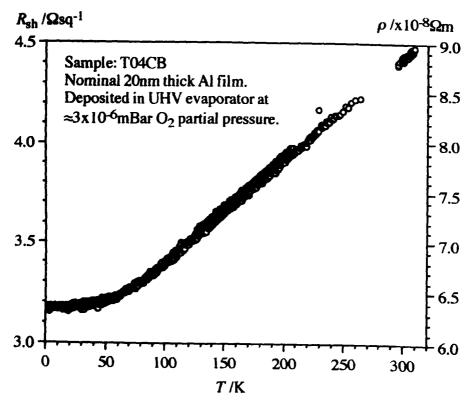

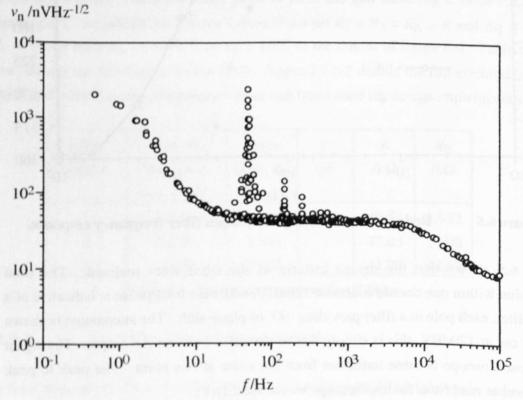

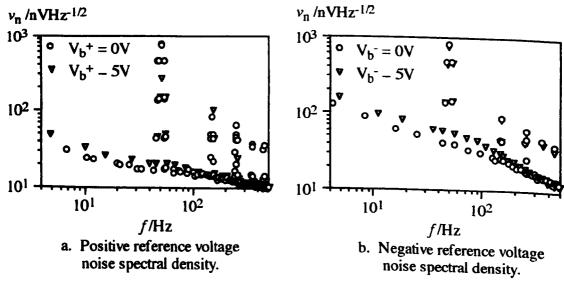

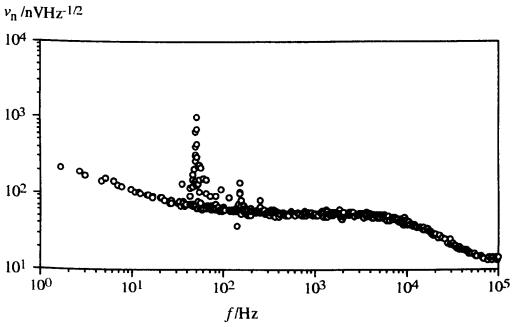

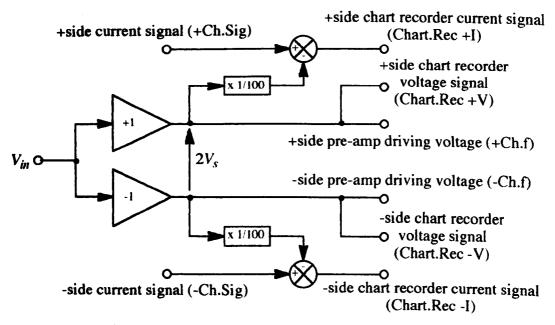

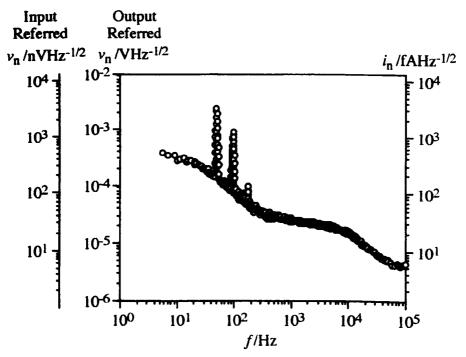

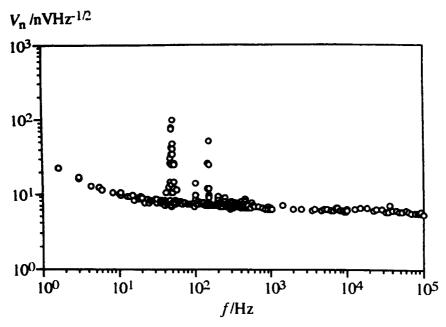

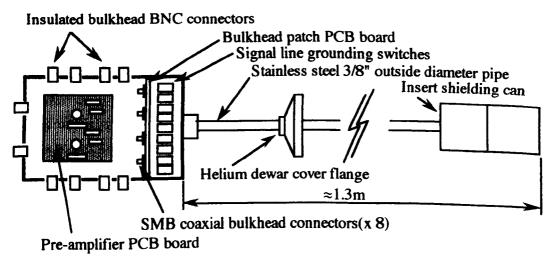

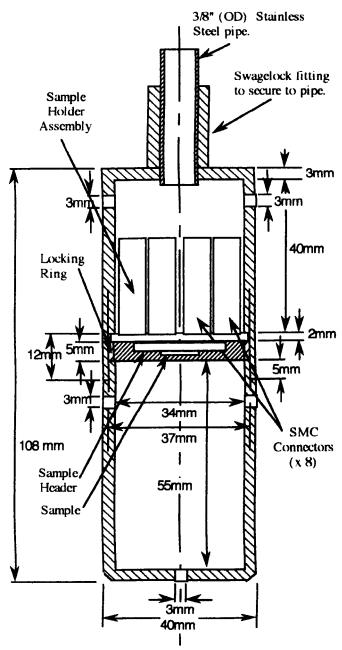

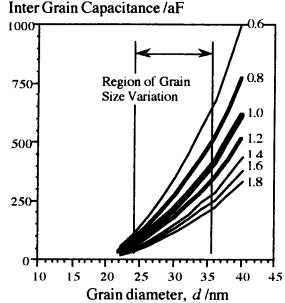

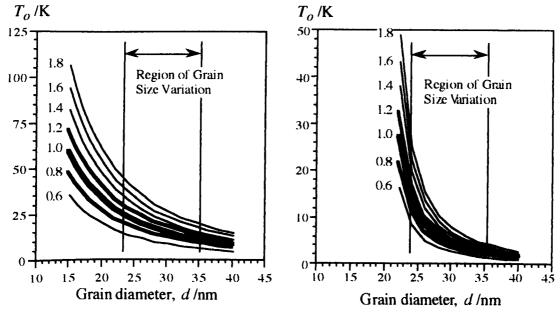

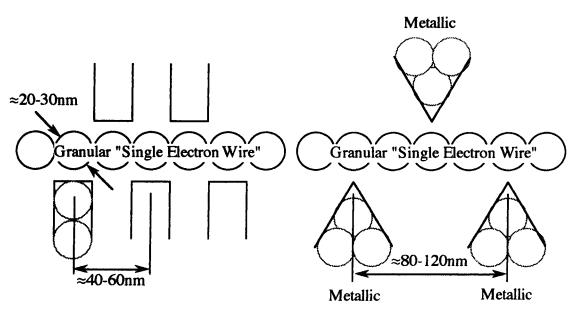

During the late 1920s and early 1930s, quantum theory was applied to a number of physical problems. In 1928, field ionization of atomic hydrogen was described by Oppenheimer. Again in 1928, Fowler and Nordheim described field emission from a free electron metal and Gamow, Condon and Gurney independently described alpha particle decay using the theory of tunnelling. Of more relevance to this work, the 1930's saw Frenkel<sup>[9]</sup> describe electron transport between disconnected metals through metal-vacuum-metal tunnelling and subsequently, in 1933, Sommerfeld and Bethe described metal-insulator-metal (MIM) tunnelling.