Blair, Calum Grahame (2014) *Real-time video scene analysis with heterogeneous processors*. EngD thesis.

http://theses.gla.ac.uk/5061/

Copyright and moral rights for this thesis are retained by the author

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the Author

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the Author

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given

Glasgow Theses Service http://theses.gla.ac.uk/ theses@gla.ac.uk

### Real-time Video Scene Analysis with Heterogeneous Processors

Calum Grahame Blair M.Eng.

A thesis submitted to The Universities of Glasgow, Edinburgh, Heriot-Watt, and Strathclyde

for the degree of Doctor of Engineering in System Level Integration

© Calum Grahame Blair

May 2014

### Abstract

Field-Programmable Gate Arrays (FPGAs) and General Purpose Graphics Processing Units (GPUs) allow acceleration and real-time processing of computationally intensive computer vision algorithms. The decision to use either architecture in any application is determined by task-specific priorities such as processing latency, power consumption and algorithm accuracy. This choice is normally made at design time on a heuristic or fixed algorithmic basis; here we propose an alternative method for automatic runtime selection.

In this thesis, we describe our PC-based system architecture containing both platforms; this provides greater flexibility and allows dynamic selection of processing platforms to suit changing scene priorities. Using the Histograms of Oriented Gradients (HOG) algorithm for pedestrian detection, we comprehensively explore algorithm implementation on FPGA, GPU and a combination of both, and show that the effect of data transfer time on overall processing performance is significant. We also characterise performance of each implementation and quantify tradeoffs between power, time and accuracy when moving processing between architectures, then specify the optimal architecture to use when prioritising each of these.

We apply this new knowledge to a real-time surveillance application representative of anomaly detection problems: detecting parked vehicles in videos. Using motion detection and car and pedestrian HOG detectors implemented across multiple architectures to generate detections, we use trajectory clustering and a Bayesian contextual motion algorithm to generate an overall scene anomaly level. This is in turn used to select the architectures to run the compute-intensive detectors for the next frame on, with higher anomalies selecting faster, higher-power implementations. Comparing dynamic context-driven prioritisation of system performance against a fixed mapping of algorithms to architectures shows that our dynamic mapping method is 10% more accurate at detecting events than the power-optimised version, at the cost of 12W higher power consumption.

## Acknowledgements

I would like to acknowledge the consistent and enthusiastic help and constructive advice given to me by my supervisor, Neil Robertson, throughout the course of this doctorate.

I would also like to thank Siân Williams for all her procedural advice, before, during and after the winding-up of the ISLI.

I'm also grateful for the work done by Scott Robson during his internship at Thales. Acknowledgements are also given to the funders of this research, EPSRC and Thales Optronics.

Thanks are due also to my friends especially Chris, Kenny and Johnathan, for dragging me out to the pub whenever this degree started to get too overwhelming. Doubly so for those – including Marek – willing to accompany me as I dragged them up and down various Munros.

My thanks also go to Rebecca for her continued understanding, patience and enthusiasm.

Above all, I would like to thank my family, Mum, Dad, Mhairi and Catriona, for all the support and encouragement they have given me throughout this period, and particularly for their frequent offers to appear — especially with the dog — in my video datasets.

# Contents

| Ab  | ostrac         |                                           | iii  |

|-----|----------------|-------------------------------------------|------|

| Ac  | know           | edgements                                 | v    |

| Lis | st of I        | ublications                               | x    |

| Lis | st of T        | bles                                      | xi   |

| Lis | st of I        | gures                                     | xii  |

| Lis | st of <i>I</i> | obreviations                              | xv   |

| De  | eclara         | on of Originality x                       | viii |

| 1.  | Intro          | uction                                    | 19   |

|     | 1.1.           | Academic Motivation and Problem Statement | 21   |

|     |                | 1.1.1. A Motivating Scenario              | 21   |

|     |                | 1.1.2. Specifying Surveillance Subtasks   | 23   |

|     |                | 1.1.3. Wider Applicability                | 24   |

|     | 1.2.           | ndustrial Motivation                      | 25   |

|     | 1.3.           | Aims                                      | 28   |

|     | 1.4.           | Knowledge Transfer                        | 29   |

|     |                | 1.4.1. Research Outputs                   | 29   |

|     |                | 1.4.2. Knowledge Transfer within Thales   | 29   |

|     | 1.5.           | Contributions                             | 31   |

|     | 1.6.           | Thesis Roadmap                            | 31   |

| 2.  | Rela           | ed Work                                   | 35   |

|     | 2.1.           | Data Processing Architectures             | 35   |

|     |                | 2.1.1. Processor Taxonomy                 | 36   |

|     |                | 2.1.2. Methods for CPU Acceleration       | 39   |

|    |      | 2.1.3. Graphics Processing Units                       | 39 |

|----|------|--------------------------------------------------------|----|

|    |      | 2.1.4. Field-Programmable Gate Arrays                  | 42 |

|    |      | 2.1.5. FPGA vs. GPU                                    | 46 |

|    |      | 2.1.6. Alternative Architectures                       | 48 |

|    | 2.2. | Parallelisable Detection Algorithms                    | 48 |

|    |      | 2.2.1. Algorithms for Pedestrian Detection             | 50 |

|    |      | 2.2.2. Classification Methods: Support Vector Machines | 55 |

|    |      | 2.2.3. HOG Implementations                             | 57 |

|    | 2.3. | Surveillance for Anomalous Behaviour                   | 60 |

|    | 2.4. | Design Space Exploration                               | 66 |

|    | 2.5. | Conclusion                                             | 70 |

| 3. | Sen  | sors, Processors and Algorithms                        | 72 |

|    | 3.1. | Introduction                                           | 73 |

|    | 3.2. | Sensors                                                | 73 |

|    |      | 3.2.1. Infrared                                        | 73 |

|    |      | 3.2.2. Visual                                          | 74 |

|    | 3.3. | Processing Platforms                                   | 75 |

|    |      | 3.3.1. Ter@pix Processor                               | 76 |

|    | 3.4. | Simulation or Hardware?                                | 77 |

|    |      | 3.4.1. Modelling                                       | 77 |

|    | 3.5. | Algorithms for Scene Segmentation                      | 80 |

|    |      | 3.5.1. Vegetation Segmentation                         | 80 |

|    |      | 3.5.2. Road Segmentation                               | 81 |

|    |      | 3.5.3. Sky Segmentation                                | 81 |

|    | 3.6. | Automatic Processing Pipeline Generation               | 82 |

|    | 3.7. | Conclusions                                            | 85 |

| 4. | Syst | tem Architecture                                       | 87 |

|    | 4.1. | Processor Specifications                               | 87 |

|    | 4.2. | System Architecture                                    | 88 |

|    |      | 4.2.1. PCIe                                            | 89 |

|    |      | 4.2.2. Interface                                       | 93 |

|    |      | 4.2.3. Interface Limitations                           | 95 |

|    | 4.3. | Conclusion                                             | 95 |

| 5. | Algo | orithm- | Level Partitioning                          | 96       |

|----|------|---------|---------------------------------------------|----------|

|    | 5.1. | HOG     | Algorithm Analysis                          | 96       |

|    |      | 5.1.1.  | Algorithm Steps                             | 98       |

|    |      | 5.1.2.  | Partitioning                                | 100      |

|    | 5.2. | Hardv   | ware Implementation                         | 101      |

|    |      | 5.2.1.  | Cell Histogram Operations                   | 103      |

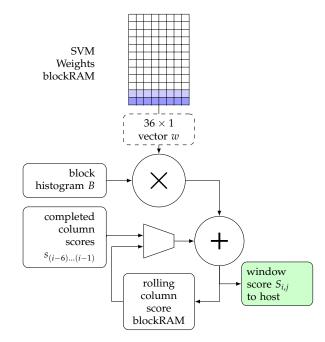

|    |      | 5.2.2.  | Window Classification Operations            | 105      |

|    | 5.3. | Softwa  | are and System Implementation Details       | 107      |

|    | 5.4. | Classi  | fier Training                               | 108      |

|    | 5.5. | Result  | ts                                          | 109      |

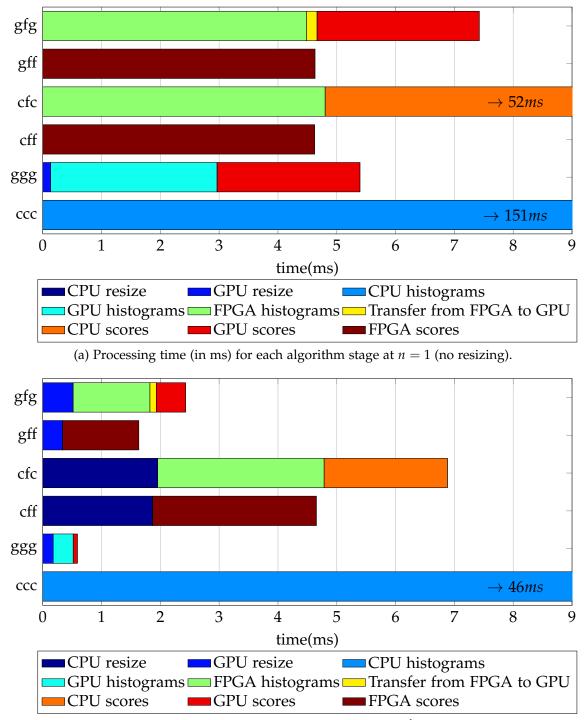

|    |      | 5.5.1.  | Performance Considerations                  | 109      |

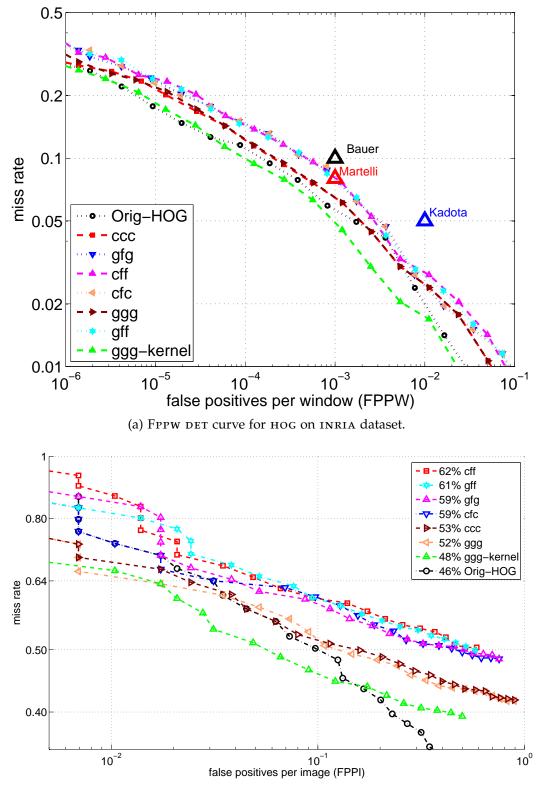

|    |      | 5.5.2.  | Detection Performance                       | 114      |

|    |      | 5.5.3.  | Performance Tradeoffs                       | 114      |

|    |      | 5.5.4.  | Analysis, Limitations, and State-of-the-Art | 121      |

|    | 5.6. | Variat  | ions                                        | 124      |

|    |      | 5.6.1.  | Kernel SVM Classification                   | 124      |

|    |      | 5.6.2.  | Pinned Memory                               | 125      |

|    |      | 5.6.3.  | Version Switching                           | 126      |

|    |      | 5.6.4.  | Embedded Evaluation                         | 127      |

|    | 5.7. | Concl   | usion                                       | 129      |

| 6. | Task | -Level  | Partitioning for Anomaly Detection          | 131      |

|    |      |         | luction                                     | 131      |

|    |      |         | ets                                         | 133      |

|    |      | 6.2.1.  |                                             | 134      |

|    |      | 6.2.2.  | i-LIDS Dataset                              | 134      |

|    | 6.3. |         | blem Description and Related Work           | 136      |

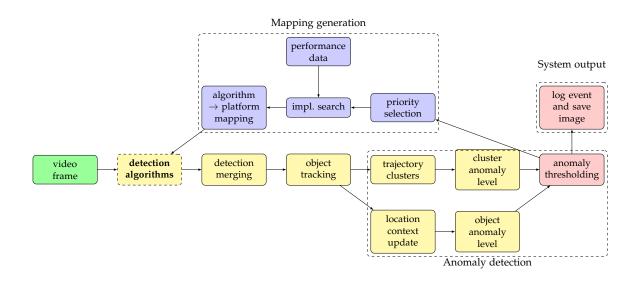

|    | 6.4. |         | level Algorithm                             | 136      |

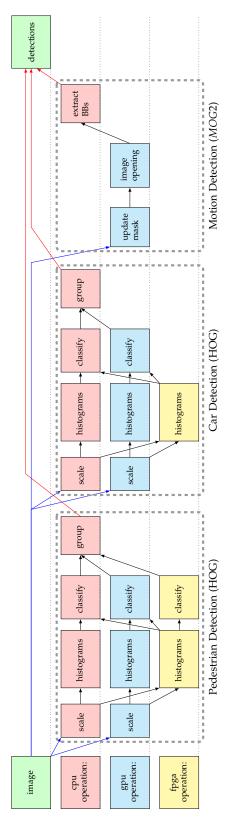

|    | 6.5. |         | ithm Implementations                        | 140      |

|    | 5    | 6.5.1.  | Pedestrian Detection with HOG               | '<br>140 |

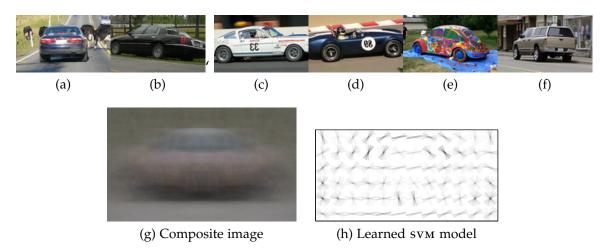

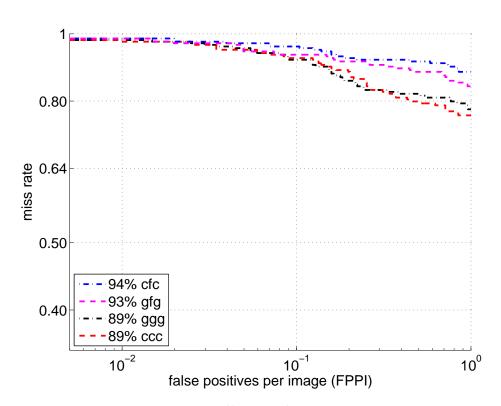

|    |      | 6.5.2.  | Car Detection with HOG                      | 141      |

|    |      | 6.5.3.  | Background Subtraction                      | 145      |

|    |      | 6.5.4.  | Detection Combination                       | 146      |

|    |      | 6.5.5.  | Detection Matching and Tracking             | 146      |

|    |      | 6.5.6.  | Trajectory Clustering                       | '<br>148 |

|    |      | 6.5.7.  | Contextual Knowledge                        | י<br>150 |

|    |      | ~ .     | 0                                           | ~        |

|     |        | 6.5.8.  | Anomaly Detection                      | 151 |

|-----|--------|---------|----------------------------------------|-----|

|     | 6.6.   | Dynan   | nic Mapping                            | 154 |

|     |        | 6.6.1.  | Priority Recalculation                 | 155 |

|     |        | 6.6.2.  | Implementation Mapping                 | 156 |

|     | 6.7.   | Evalua  | tion Methodology                       | 157 |

|     | 6.8.   | Results | 5                                      | 158 |

|     |        | 6.8.1.  | Detection Performance on BankSt videos | 158 |

|     |        | 6.8.2.  | Detection Performance on i-LIDS videos | 159 |

|     | 6.9.   | Analys  | sis                                    | 165 |

|     |        | 6.9.1.  | Comparison to State-of-the-Art         | 167 |

|     |        | 6.9.2.  | System Architecture Improvements       | 169 |

|     |        | 6.9.3.  | Algorithm-Specific Improvements        | 170 |

|     |        | 6.9.4.  | Task-Level Improvements                | 170 |

|     | 6.10.  | Conclu  | asion                                  | 171 |

| 7.  | Cond   | clusion |                                        | 173 |

|     | 7.1.   | Summ    | ary                                    | 173 |

|     | 7.2.   | Contri  | butions                                | 175 |

|     |        | 7.2.1.  | Outcomes                               | 176 |

|     | 7.3.   | Future  | Research Directions and Improvements   | 176 |

| Α.  | Math   | ematic  | al Formulae                            | 178 |

|     | A.1.   | Vector  | Norms                                  | 178 |

|     | A.2.   | Kalma   | n Filter                               | 178 |

|     | A.3.   | Planar  | Homography                             | 179 |

| Bił | oliogr | aphy    |                                        | 180 |

## **List of Publications**

- *Characterising Pedestrian Detection on a Heterogeneous Platform,* C. Blair, N. M. Robertson, and D. Hume, in Workshop on Smart Cameras for Robotic Applications (SCaBot '12), IROS 2012.

- Characterising a Heterogeneous System for Person Detection in Video using Histograms of Oriented Gradients: Power vs. Speed vs. Accuracy, C. Blair, N. M. Robertson, and D. Hume, IEEE Journal of Emerging and Selected Topics in Circuits and Systems, V3(2) pp. 236–247, 2013.

- Event-Driven Dynamic Platform Selection for Power-Aware Real-Time Anomaly Detection in Video, C. G. Blair & N. M. Robertson, International Conference on Computer Vision Theory and Applications (VISAPP) 2014.

## **List of Tables**

| 2.1. | Data processing architectural comparison                              | 38  |

|------|-----------------------------------------------------------------------|-----|

| 3.1. | List of simple image processing algorithm candidates                  | 85  |

| 5.1. | Data generated by each stage of нос                                   | 100 |

| 5.2. | Resource Utilisation for HOG application and PCIe link logic on FPGA. | 107 |

| 5.3. | Processing times for each execution path                              | 110 |

| 5.4. | Processing time with smaller GPU                                      | 110 |

| 5.5. | Hog power consumption using ML605 FPGA and GTX560 GPU                 | 111 |

| 5.6. | Power consumption above reference for each execution path             | 112 |

| 5.7. | HOG power consumption using ML605 FPGA and Quadro 2000 GPU            | 112 |

| 5.8. | Hog implementation tradeoffs                                          | 118 |

| 5.9. | Pinned and non-pinned memory processing time                          | 126 |

| 5.10 | . Differences in processing times when switching between versions     | 127 |

| 6.1. | Algorithms and implementations used in anomaly detection              | 141 |

| 6.2. | Parameters for car detection with HOG                                 | 142 |

| 6.3. | Resource Utilisation for pedestrian and car HOG detectors on FPGA.    | 144 |

| 6.4. | Implementation Performance Characteristics                            | 156 |

| 6.5. | Detection performance for parked vehicle events on all prioritisation |     |

|      | modes on i-LIDS sequence PV3                                          | 160 |

| 6.6. | Detection performance for parked vehicle events on all prioritisation |     |

|      | modes on <i>daylight sequences only</i> in i-LIDS sequence PV3        | 160 |

| 6.7. | $F_1$ -scores for all prioritisation modes on i-LIDS sequence PV3     | 161 |

| 6.8. | Processing performance for all prioritisation modes on PV3            | 163 |

| 6.9. | Processing performance for all prioritisation modes on Pv3 (daylight  |     |

|      | sequences only)                                                       | 165 |

# **List of Figures**

| 1.1.                              | Mastiff land defence vehicle                                       | 21 |

|-----------------------------------|--------------------------------------------------------------------|----|

| 1.2.                              | Routine behaviour in a surveillance scene                          | 23 |

| 1.3.                              | Demonstration platform with user-driven performance prioritisation | 30 |

| 1.4.                              | Power vs. time tradeoffs for runtime deployment                    | 32 |

| 1.5.                              | Example anomalous event detection                                  | 32 |

| 1.6.                              | Power vs. time: design space exploration for multiple detectors    | 33 |

| 2.1.                              | Image Processing Pipeline                                          | 36 |

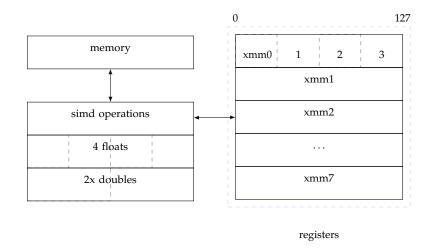

| 2.2.                              | SIMD register structure in modern x86 processors                   | 39 |

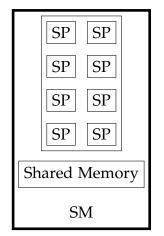

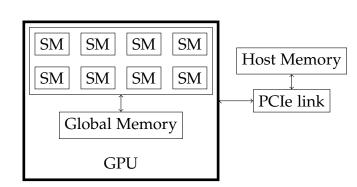

| 2.3.                              | Cuda gpu Architecture                                              | 41 |

| 2.4.                              | FPGA Architecture                                                  | 43 |

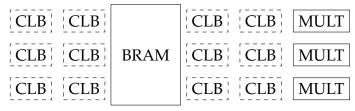

| 2.5.                              | Throughput comparison for image processing operations              | 46 |

| 2.6.                              | Improved PCIe transfer via fewer device copy stages                | 48 |

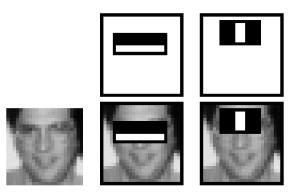

| 2.7.                              | Face detection with Haar features                                  | 49 |

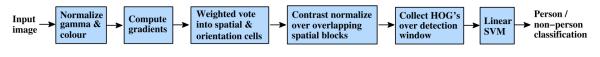

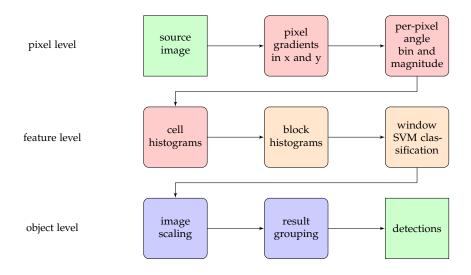

| 2.8.                              | Hog algorithm pipeline                                             | 50 |

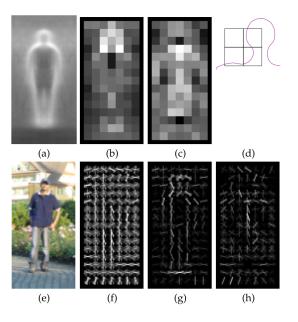

| 2.9.                              | Graphical representation of нос steps                              | 51 |

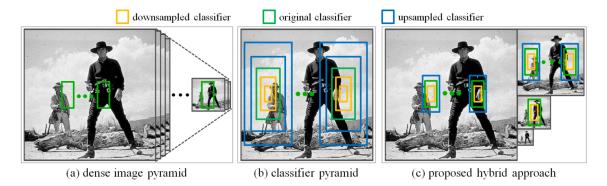

| 2.10                              | The Fastest Pedestrian Detector in the West                        | 52 |

| 2.11.                             | INRIA and Caltech dataset sample images                            | 52 |

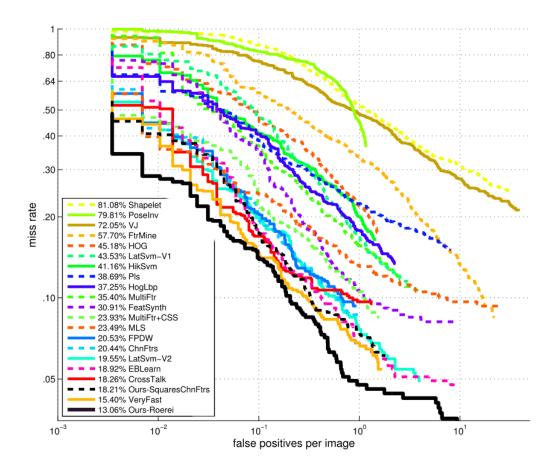

| 2.12.                             | State-of-the-Art Pedestrian Detection Performance                  | 53 |

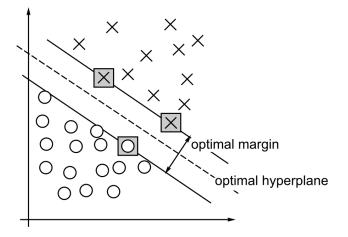

| 2.13.                             | Support Vectors                                                    | 55 |

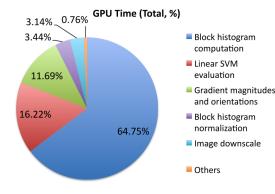

| 2.14.                             | HOG workload on GPU                                                | 58 |

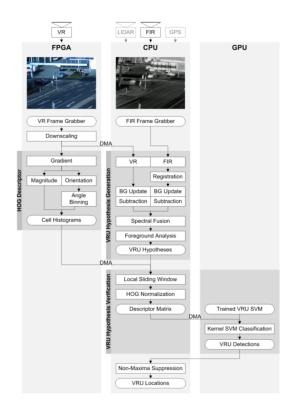

| 2.15.                             | HOG pipeline on a hybrid FPGA-GPU system                           | 59 |

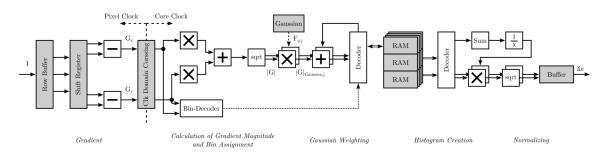

| 2.16.                             | Fast HOG pipeline on a FPGA system: histogram generation           | 60 |

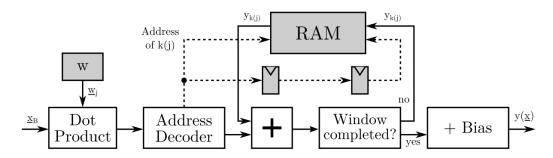

| 2.17.                             | Fast Hog pipeline on a FPGA system: classification                 | 60 |

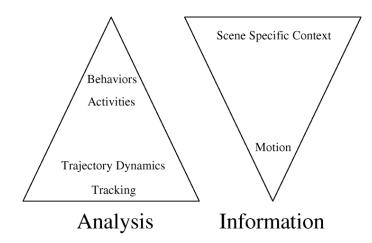

| 2.18                              | Analysis and information hierarchies in surveillance video         | 61 |

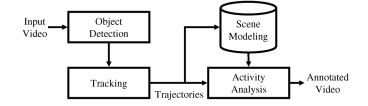

| 2.19.                             | Surveillance analysis block diagram                                | 61 |

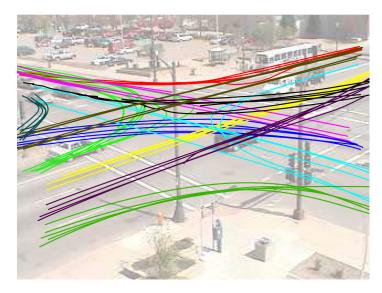

| 2.20. Traffic trajectory analysis |                                                                    |    |

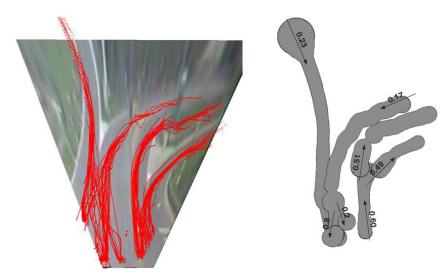

| 2.21.                             | Trajectory analysis via subtrees                                   | 63 |

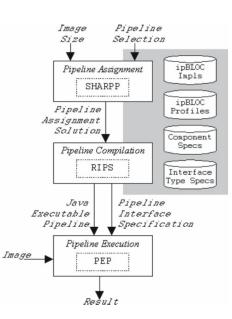

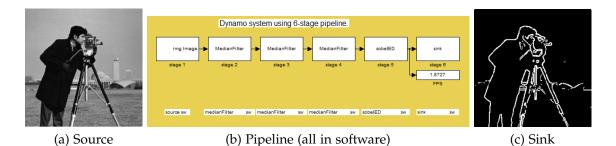

| 2.22. | . Pipeline assignment in the Dynamo system                         | 68   |

|-------|--------------------------------------------------------------------|------|

| 2.23. | . Resulting allocations from the Dynamo system                     | 68   |

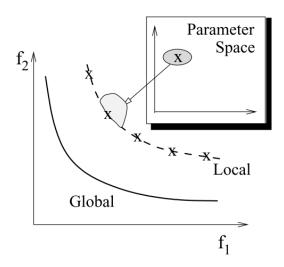

| 2.24. | . Global and local Pareto optimality                               | 69   |

| 3.1.  | A person shown on infrared and visual cameras.                     | 74   |

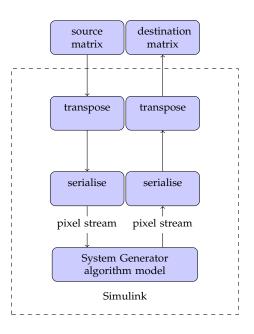

| 3.2.  | Modelling a FPGA algorithm from within MATLAB                      | 78   |

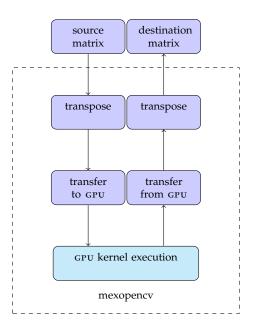

| 3.3.  | Running a GPU kernel in an OpenCV framework from within MATLAB     | • 79 |

| 3.4.  | Registered source cameras and vegetation index                     | 81   |

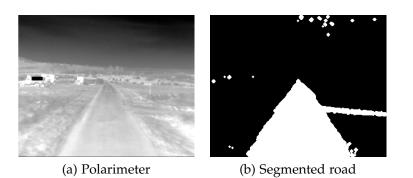

| 3.5.  | Road segmentation from IR polarimeter data.                        | 81   |

| 3.6.  | Sky segmentation from visual camera                                | 82   |

| 3.7.  | Simulink image processing pipeline                                 | 83   |

| 4.1.  | Accelerator cards in development system                            | 88   |

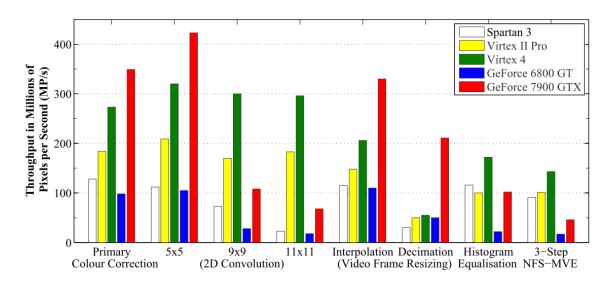

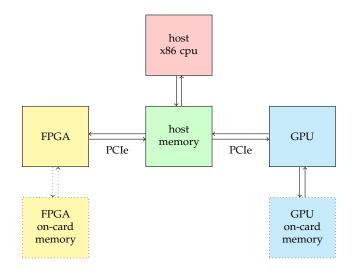

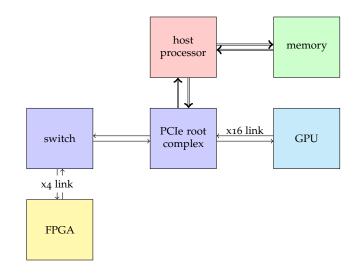

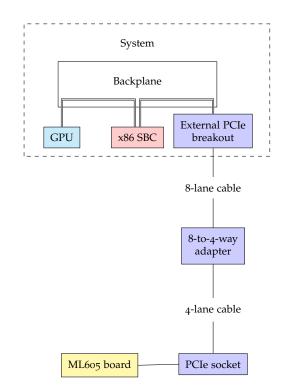

| 4.2.  | System functional diagram showing processor communications         | 89   |

| 4.3.  | PcI-express topology diagram                                       | 90   |

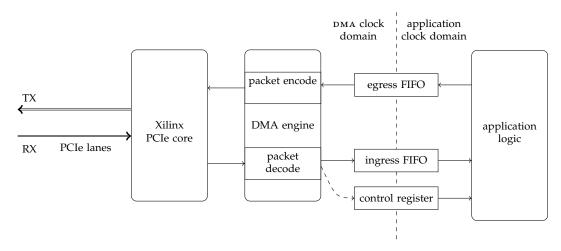

| 4.4.  | System internal FPGA architecture.                                 | 93   |

| 5.1.  | Hog algorithm stages                                               | 97   |

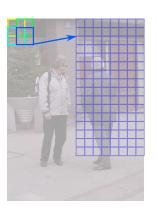

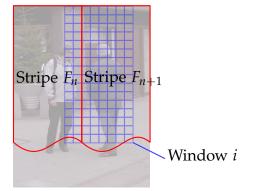

| 5.2.  | Cells, blocks and windows                                          | 98   |

| 5.3.  | Histogram orientation binning                                      | 98   |

| 5.4.  | Svм person model generated by нос training                         | 99   |

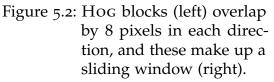

| 5.5.  | Hog algorithm processing paths                                     | 102  |

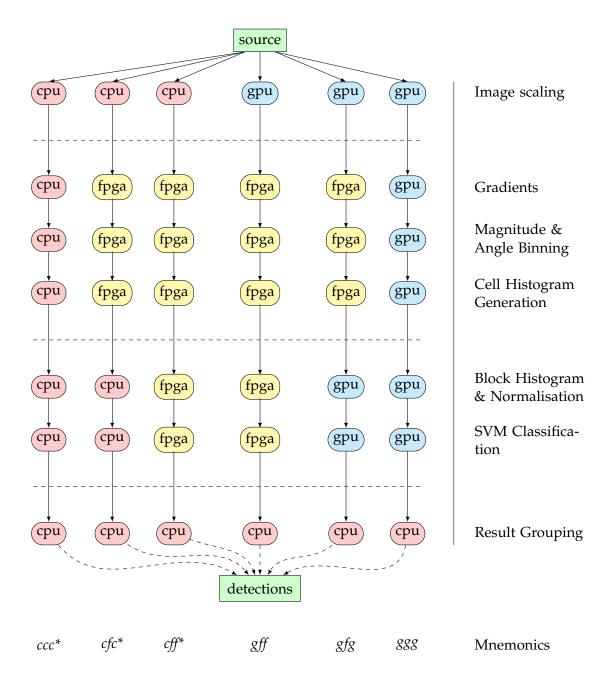

| 5.6.  | Hog stripe processors within an image                              | 103  |

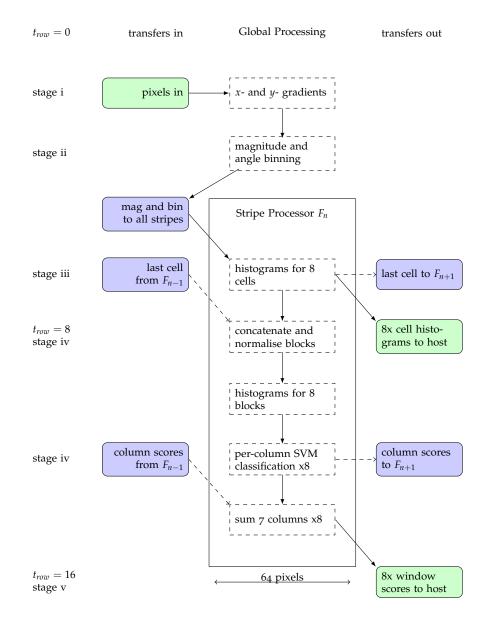

| 5.7.  | Operation of a нос stripe processor                                | 104  |

| 5.8.  | Operation of a нос block classifier                                | 105  |

| 5.9.  | Time taken to process each algorithm stage for each implementation | 113  |

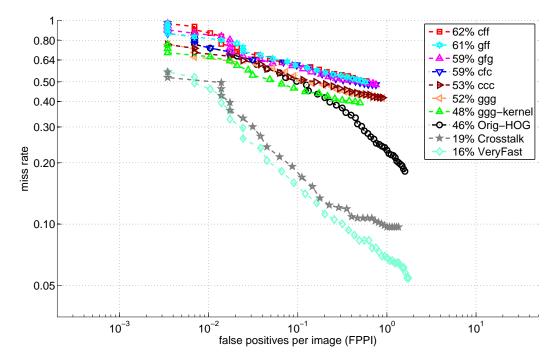

| 5.10. | DET curves for Algorithm Implementations                           | 115  |

| 5.11. | DET curves comparing implementations to state-of-the-art           | 116  |

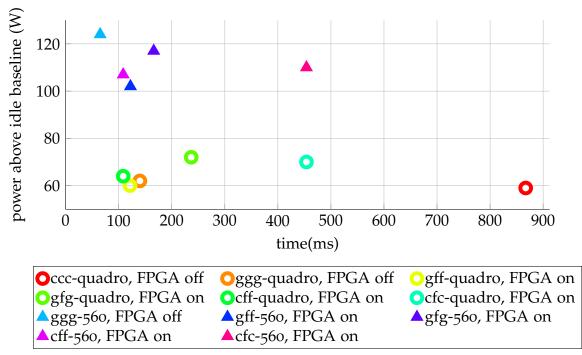

| 5.12. | Power vs. time: design time and run time analysis                  | 117  |

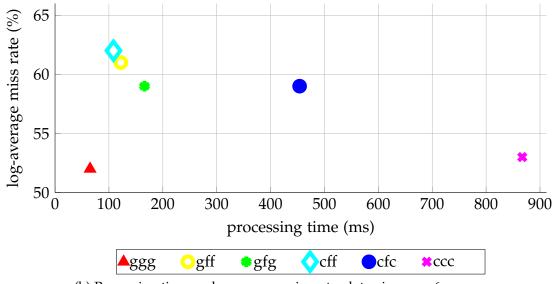

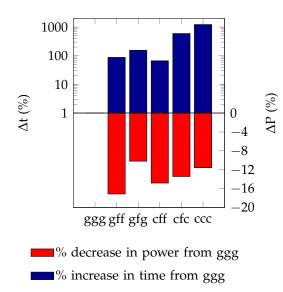

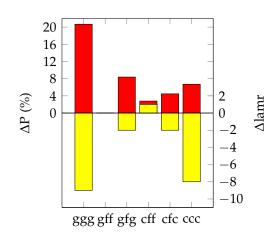

| 5.13. | . Run-time tradeoffs for various pairs of characteristics on нос   | 119  |

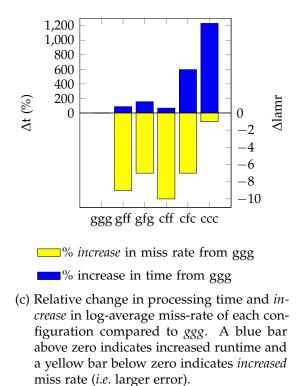

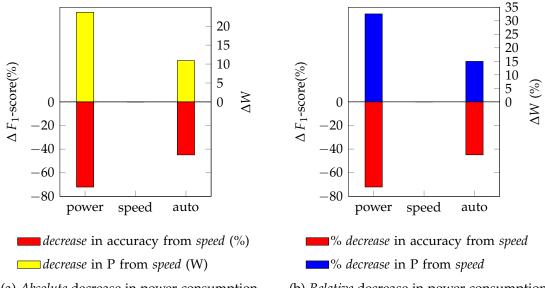

| 5.14. | . Relative tradeoffs between individual characteristics            | 120  |

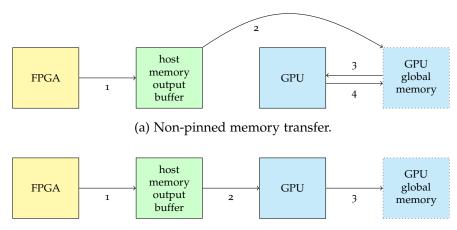

| 5.15. | . Comparison of pinned and non-pinned transfers                    | 126  |

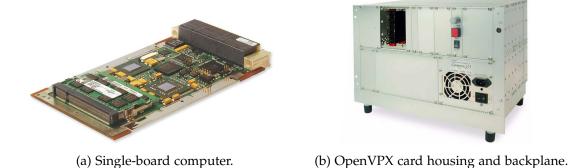

| 5.16. | Embedded system components                                         | 128  |

|       | Processor connections in an embedded system                        | 128  |

| 6.1.  | Algorithm mapping loop in anomaly detection system                 | 133  |

| 6.2.  | Sample images with traffic from each dataset used                  | 134  |

| 6.3.  | All possible mappings of image processing algorithms to hardware   | 137  |

|       |                                                                    |      |

| 6.4.  | Hog detector false positives                                             | 142   |

|-------|--------------------------------------------------------------------------|-------|

| 6.5.  | Car detector training details                                            | 143   |

| 6.6.  | Det curves for car detector implementations                              | 143   |

| 6.7.  | Bounding box extraction from background subtraction algorithm            | 145   |

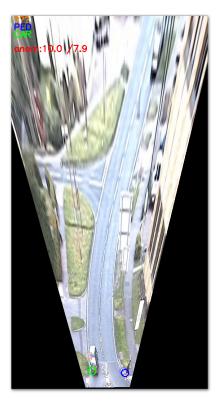

| 6.8.  | Object tracking on an image projected onto the ground plane              | 148   |

| 6.9.  | Learned object clusters projected onto camera plane                      | 150   |

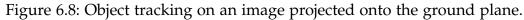

| 6.10. | Presence intensity maps                                                  | 152   |

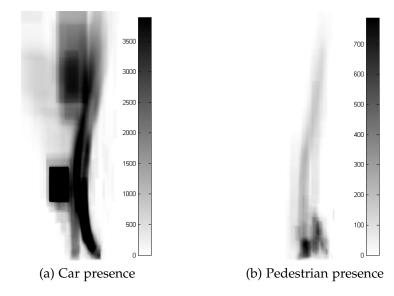

| 6.11. | Motion intensity maps                                                    | 152   |

| 6.12. | Anomaly detected by system                                               | 155   |

| 6.13. | Dashboard for user- or anomaly-driven priority selection                 | 155   |

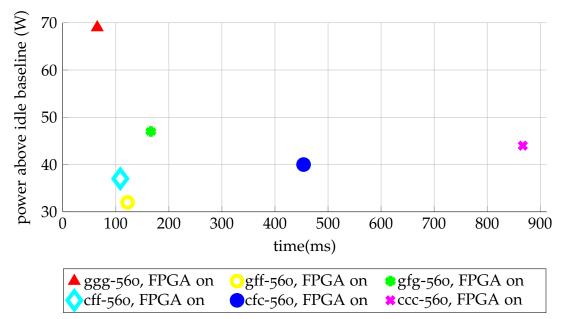

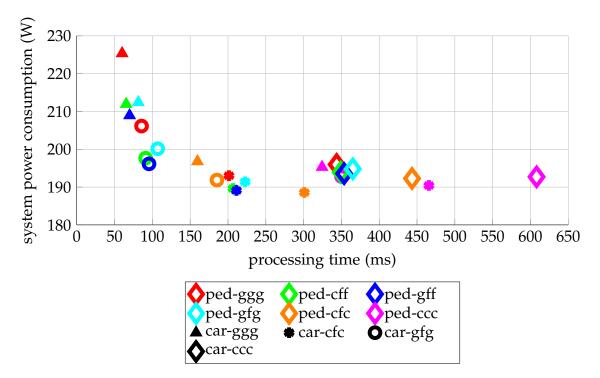

| 6.14. | Power and time mappings for all accelerated detectors                    | 161   |

| 6.15. | Power and time mappings for all accelerated detectors: full legend .     | 162   |

| 6.16. | Parked vehicle detection in BankSt dataset                               | 162   |

| 6.17. | Impact of video quality on object classification                         | 163   |

| 6.18. | True detections and example failure modes of anomaly detector            | 164   |

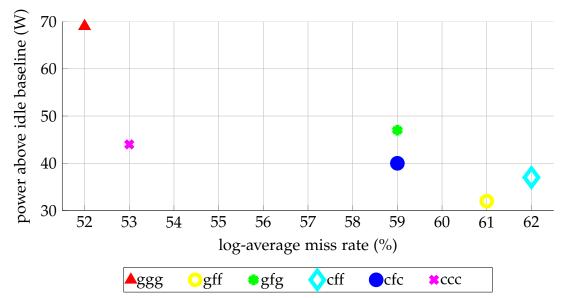

| 6.19. | Relative tradeoffs: power vs. error rate for dynamically-mapped detector | r 167 |

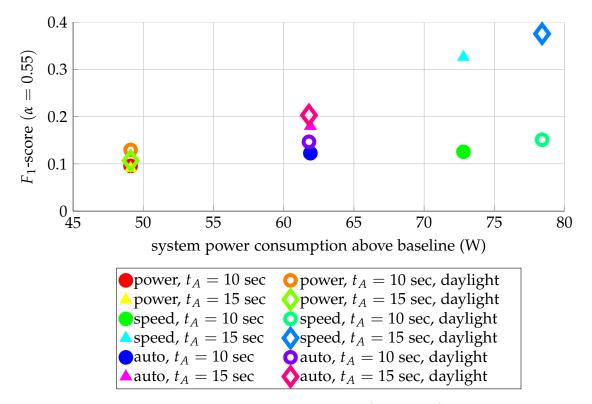

| 6.20. | Accuracy and power tradeoffs                                             | 168   |

|       |                                                                          |       |

## **List of Abbreviations**

| AP    | Activity Path.                            |

|-------|-------------------------------------------|

| API   | Application Programming Interface.        |

| ASIC  | Application-Specific Integrated Circuit.  |

| ASR   | Addressable Shift Register.               |

|       |                                           |

| BAR   | Base Address Register.                    |

|       |                                           |

| CLB   | Combinatorial Logic Block.                |

| COTS  | Commercial Off-the-Shelf.                 |

| CPU   | Central Processing Unit.                  |

| CUDA  | Compute Unified Device Architecture.      |

|       |                                           |

| DET   | Detection Error Tradeoff.                 |

| DMA   | Direct Memory Access.                     |

| DSE   | Design Space Exploration.                 |

|       |                                           |

| FIFO  | First-In First-Out buffer.                |

| FPGA  | Field Programmable Gate Array.            |

| FPPI  | False Positives per Image.                |

| FPPW  | False Positives per Window.               |

| FPS   | Frames per second.                        |

|       |                                           |

| GB/S  | Gigabytes per second.                     |

| GPGPU | General-Purpose Graphics Processing Unit. |

| GPU   | Graphics Processing Unit.                 |

|       |                                           |

| GT/S            | Gigatransfers per second.                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| HOG             | Histogram of Oriented Gradients.                                                                                             |

| i-LIDS<br>ISTAR | Imagery Library for Intelligent Detection Systems.<br>Intelligence, Surveillance, Target Acquisition, and<br>Reconnaissance. |

| MAC/S           | Multiply-Accumulate Operations per second.                                                                                   |

| MB/S            | Megabytes per second.                                                                                                        |

| MOG             | Mixture of Gaussians.                                                                                                        |

| MPS             | Maximum Payload Size.                                                                                                        |

| NMS             | Non-Maximal Suppression.                                                                                                     |

| NPP             | Nvidia Performance Primitives.                                                                                               |

| PCIE            | PCI Express.                                                                                                                 |

| PE              | Processing Element.                                                                                                          |

| POI             | Point of Interest.                                                                                                           |

| QVGA            | Quarter VGA, $320 \times 240$ resolution.                                                                                    |

| RBF             | Radial Basis Function.                                                                                                       |

| ROC             | Receiver Operating Characteristic.                                                                                           |

| RTL             | Register Transfer Level.                                                                                                     |

| SBC             | Single-Board Computer.                                                                                                       |

| SIMD            | Single Instruction Multiple Data.                                                                                            |

| SIMT            | Single Instruction Multiple Thread.                                                                                          |

| SM              | Streaming Multiprocessor.                                                                                                    |

| SP              | Stream Processor.                                                                                                            |

| SSE             | Streaming SIMD Extensions.                                                                                                   |

| SVM             | Support Vector Machine.                                                                                                      |

**TLP** Transaction Layer Packet.

# **Declaration of Originality**

Except where I have explicitly acknowledged the contributions of others, all work contained in this thesis is my own. It has not been submitted for any other degree.

## 1. Introduction

Computer vision, or the science of extracting meaning from images, is a large and growing field within the domains of electronic engineering and computer science. As humans, vision is our primary sense and many of our everyday tasks depend heavily on an ability to see our surroundings. Teaching or programming machines to perceive the world as we do opens up a myriad of possibilities: routine, repetitive tasks can be automated, dangerous situations made safer, and many more options for entertainment become feasible. Autonomous vehicles equipped with cameras allow us to explore areas of our world and universe which would be extremely hostile to humans. Grand aims such as these cover much of the motivation for research in this field.

From an engineering perspective, many tasks within computer vision are difficult problems. The human brain has specialised hardware built for processing information from images, with a design time of millions of years. It is capable of forming images, extracting shapes, recognising objects, inferring meaning and intent to observed motion, and using this information to interact with the world around it — fast enough that we can catch a flying ball or step out of the way of a speeding car. A machine built or programmed to perform tasks which require interpretation of visual data must operate *accurately* enough to be effective and complete its task fast enough that the data it extracts is timely enough to be usable. In many cases, this is in real time; we must process images at the same speed or faster than they are received, and we accept some known time delay or *latency* between starting and finishing processing of a single image.

And what of the underlying processing hardware that we rely on to do this work? The state of the art in electronics has continued to advance rapidly; using computers built within the last few years we can now make reasonable progress towards creating implementations of complex signal processing algorithms which can run in real time. These same advances have allowed devices containing sensors and processors to shrink to where they become handheld or even smaller. Their ubiquity and low cost, along with their size, further expand the potential benefits of mobile computing systems, and offer even more applications for embedded or autonomous vision systems. However, the *power consumption* of any machine must be considered, and this is the limiting factor affecting processing devices at all scales, from handhelds to supercomputers. These three characteristics — power consumption, latency and accuracy — are ones which we will return to repeatedly in this thesis.

The thesis itself describes the research undertaken for the Engineering Doctorate in System Level Integration. The work is in the technical field of characterization and deployment of heterogeneous architectures for acceleration of image processing algorithms, with a focus on real-time performance. This was carried out in combination with the Visionlab, part of the Institute for Sensors, Signals and Systems at Heriot-Watt University<sup>1</sup>, and Thales Optronics Ltd<sup>2</sup>. It was sponsored jointly by the Engineering and Physical Sciences Research Council (EPSRC) and Thales Optronics. It was managed by the Institute for System Level Integration, a joint venture between the schools of engineering in the four Universities of Glasgow, Edinburgh, Heriot-Watt and Strathclyde. Operating between 1999 and 2012, it ran courses for postgraduate taught and research students, along with commercial electronics design consultancy services. Its website was shut down following its closure in 2012, but an archived copy is available<sup>3</sup>.

This chapter is laid out as follows: in Section 1.1 we give an overall statement of the problem studied and our motivation for conducting research in this area. As the EngD involves carrying out commercially relevant research, Section 1.2 places this work in a commercial context and gives the business motivation behind it. We then concentrate on the specific aims of this thesis in Section 1.3. This is followed in Section 1.4 by our research outputs and knowledge transfer outputs to industry. Finally, Section 1.5 states the contributions made by this work and Section 1.6 gives a roadmap for the rest of this thesis.

<sup>&</sup>lt;sup>1</sup>http://visionlab.eps.hw.ac.uk

<sup>&</sup>lt;sup>2</sup>http://www.thalesgroup.com/

<sup>&</sup>lt;sup>3</sup>http://web.archive.org/web/20130527020950/http://www.isli.ac.uk/

Figure 1.1: Land defence vehicles such as the British Army's Mastiff now include cameras for local situational awareness.

### 1.1 Academic Motivation and Problem Statement

We start by considering the problem of situational awareness. Locally, this involves monitoring of one's own environment. In a military situation, simply looking at a scene to identify threats has its own problems; visual range is limited, and merely being in an unsafe area to monitor it involves some level of risk to the observers. Visual and infrared sensors allow situational awareness of both local and remote environments with reduced risk; the current generation of land defence vehicles for the British Army now include multiple cameras for this reason (see Figure 1.1).

However, the deterioration of performance of human operators over time when performing *vigilance* tasks such as monitoring radar or closed-circuit TV screens, or standing sentry duty, is well-known [1]. It was first established by Mackworth in 1948; he showed that human capability to detect events decreased dramatically after only half an hour on watch, with this degradation continuing over longer watches [2]. Donald argues that CCTV surveillance falls under the taxonomy of vigilance work and should be treated the same way [3]. In both military and civilian domains, there is thus a clear benefit to deploying machines which can perform automated situational awareness tasks.

#### 1.1.1 A Motivating Scenario

We now consider the situations in which such a machine could be deployed. The vehicle in Figure 1.1 is likely to perform two main types of tasks: (i) situational awareness while moving and on patrol, and (ii) surveillance while stationary. In each

case, some image processing of visual or infrared sensor data must be done. When the vehicle is moving, fast detections and a high framerate may be required so that actions may be taken quickly, in response to changes in the vehicle's environment which may pose a threat. The engine will be running, so plenty of electrical power will be available for image processing. In the second scenario, we assume the vehicle is performing surveillance and is stationary with the engine turned off. Any processing done in this state should not drain the battery to the point where (i) the engine can no longer start or possibly (ii) where continued surveillance operations become impossible. The operating priorities of such a system will change so that power conservation becomes more important than fast processing.

Expanding on this, if we consider a scenario where the degree of computational operations increases with the number of objects or amount of clutter in an image then the weighting given to power consumption, latency and accuracy of object classification may change dynamically. This would require the system to either change the way it processes data (starting or stopping processing entirely) or moving processing to different platforms more suited to the current priorities.

In an ideal world, we would have a processing platform and an algorithm which is *the most accurate, the fastest and the least power-hungry when compared to all possible alternatives*. However, as we explain in detail later in this thesis, any combination of processor and algorithm involves a compromise and no such consistently optimal solution exists. Any solution is a tradeoff between power, time, accuracy, and various other less critical factors. It is this *problem of adapting our system performance and behaviour to best fit the changing circumstances of the operating environment* that we wish to study here.

So far we have used the example of a military patrol vehicle, but this problem is also one faced by autonomous vehicles or remotely operated sensors — indeed, any device which must conserve battery power while doing some kind of signal processing. This would encompass civilian applications such as disaster recovery or driver assistance, as well as the military example we use throughout this thesis.

Figure 1.2: An example scene: normal pedestrian and vehicle behaviour is to some extent dictated by the structure of the scene, and these patterns can be learned via prolonged observation. However, unexpected behaviour (cars driving onto pavement or running red lights, or a person running across the road) is still possible.

#### 1.1.2 Specifying Surveillance Subtasks

Given that we wish to automate some existing surveillance task – under power and complexity constraints – we now consider what this might involve. We choose to focus on the detection of pedestrians and vehicles, for several reasons:

- Humans (and, to a lesser extent, vehicles controlled by humans) are arguably the most important objects in any scene. They will often have a routine or pattern of life affected by their surroundings, but be capable of easily deviating from this. Consider the scene in Figure 1.2; the position of the road and pavement influences pedestrian and vehicle location, and features such as traffic lights and double yellow "No Parking" lines influence their behaviour but not to the extent that illegal parking or jaywalking is impossible.

- There are clear advantages to deploying this technology in military and civilian applications, and a tangible benefit to doing this in real time. The car manufacturer Volvo is already including pedestrian detection systems for driver assistance which rely on video and radar in their latest generation of cars [4]. However, doing this on a mobile phone-sized device and without relying on active sensing is still a challenge.

• The algorithms necessary to perform pedestrian detection generalise well to other object detection tasks; *e.g.* an existing pedestrian detector can produce state-of-the-art results when applied to a road sign classification problem [5].

#### 1.1.3 Wider Motivations

The UK Ministry of Defence's research division, the Defence Science and Technology Laboratory, has identified around thirty technical challenges in the area of signal processing [6], and, together with the Engineering and Physical Sciences Research Council, has provided £8m in funding for research which will directly address these, under the umbrella of the Universities Defence Research Collaboration<sup>4</sup>. While these were formulated well after this project was started, the themes of this thesis are nevertheless applicable to the open problems faced by the wider defence and security research community today. Several UDRC challenges touch on the area of anomaly detection in video ("Video Pattern Recognition" and "Statistical Anomaly Detection in an Under-Sampled State Space"), while another specifically addresses the implementation of algorithms on mobile or handheld devices ("Reducing Size, Weight and Power Requirements through Efficient Processing").

In the civilian domain, the UN World Health Organisation's 2013 Road Safety Report notes that half of all road deaths are from vulnerable traffic users (pedestrians, cyclists, and motorcyclists) and calls for improved infrastructure and more consideration of the needs of these vulnerable users. Starting in 2014, the European New Car Assessment Programme will include test results of Autonomous Emergency Braking systems for cars. These detect pedestrians or other vehicles ahead of the car, then brake automatically if the driver is inattentive [7]. Finally, in 2013 the first instance of an unmanned aerial vehicle being used to locate and allow the rescue of an injured motorist was recorded [8], demonstrating the applications of this technology for disaster recovery scenarios in the future.

To summarise our motivations at this point: within the field of computer vision, the problem of pedestrian and vehicle detection has a wide variety of applications, many of which involve anomaly detection and surveillance scenarios. Many of these scenarios require real-time solutions operating under low power constraints. We comprehensively survey progress towards these solutions in Chapter 2, but we note

<sup>&</sup>lt;sup>4</sup>http://www.mod-udrc.org/technical-challenges

here that this is an open field with advances required in all three metrics of accuracy, speed and power.

#### 1.2 Commercial and Industrial Motivation

There are several commercial factors which have influenced this work. We start by briefly considering the field of high-performance computing, then narrow our focus to look at the factors affecting Thales Optronics.

Within the last decade, computing applications have no longer been able to improve performance by continually increasing the clock speed of the processors they run on. The "power wall" acts to limit the upper clock speed available, and development efforts have instead focused on increasing the number of cores in a processor; the "Concurrency Revolution" [9]. This allows improved performance of concurrent and massively parallel applications. Taken to its logical conclusion, this has allowed, firstly, the development of processors with thousands of cores on them, all capable of reasonable floating-point performance [10]; secondly, division of labour inside a computer system or network. A *multicore* processor optimised for fast execution of one or two threads may control overall program flow, but the embarrassingly parallel calculations which make up the majority of "big data" scientific data computation and signal processing operations can be farmed out to throughput-optimised *massively multicore accelerators*. Such an approach is known as *heterogeneous computing*. The validity of this approach is borne out by the Top 500 list of most powerful supercomputers; as of November 2013, 53 computers on the list were using some form of accelerator, including the first and second most powerful (using Intel Xeon Phi and Nvidia Graphics Processing Unit (GPU) accelerators respectively) [11].

As we will discuss in Chapter 2, the choice of processing platform to use for a specific application has significant implications for performance. Thales is an engineering firm which designs and manufactures opto-electronic systems for applications throughout the defence sector, including naval, airborne and land defence. Changing customer requirements in recent years have lead to an increase in the processing capability included in the systems they develop. This is part of a move from current image *enhancement* (such as performing non-uniformity correction on the output from an infrared camera) to near-term future image *processing* capability, such as detection and tracking of potential targets. The Ministry of Defence has formalised the requirements for interoperability of such systems for land defence applications [12], meaning that cameras from one vendor can in theory be paired with signal processing equipment from another, and processing equipment can be easily upgraded when required.

Thales are thus concerned with the deployment of image-processing algorithms in embedded systems, and are aware that such technology operating with realtime performance has a wide variety of current and future applications, limited in many cases by the size, weight and power of any developed solution. As these are designed for military operations, various other economic factors must be considered. Small, irregular production runs are the norm. Rather than a company defining its own product release roadmap to a regular schedule as in the telecommunications industry, development and release of new products is customer-driven in response to contracts or tenders. Products must also be supported by the manufacturer for much longer than commercial devices; requirements to be able to provide support and replacement parts for twenty years are not unusual. Military devices must also operate in more extreme temperature ranges than commercial products. Taken together, all these constraints preclude the use of Application-Specific Integrated Circuits (ASICS), many Commercial Off-the-Shelf (COTS) parts, and the ability to make use of economies of scale. In the last decade or so, Field Programmable Gate Arrays (FPGAS) have been used to perform most image and signal processing tasks in embedded systems. FPGA boards are available in form factors designed for defence applications, such as OpenVPX cards. Unlike ASICS, FPGAS can be reprogrammed at some point in their operational lifetime to add new features, without replacing the entire unit.

However, the long development times and limited potential for component reuse between different designs (a high *Non-Recurring Engineering* cost) have meant that FPGA development has been regarded as time-consuming, complicated and expensive. The recent growth of GPU computing has offered firms like Thales an alternative to this. The faster development cycle of GPU programming and in some cases its lower cost must be weighed against a probable increase in power consumption when compared to FPGA. Another major concern is availability of parts in twenty years time, particularly for products where a new generation is launched around every 18–24 months. The wide availability of highly optimised matrix mathematics libraries on GPU may further reduce development time.

GPUS have another advantage over ASICS in that they are quickly reprogrammable at runtime (new kernels can be launched in under  $10\mu s$  [13]). Dynamically reconfigurable FPGAS also behave similarly. These approaches allow the same hardware to be used for different tasks within the same mission, reducing the size, weight and power of the equipment carried. (As an example, consider a system running different algorithms on the same processing platforms, using visual sensors in daylight and infrared at night, or automatically selecting different segmentation or detection algorithms in urban and rural environments). Again, the differing approaches of the GPU ("run a new task on a fixed architecture") and FPGA ("shut down parts of the chip and reprogram it") to these changing mission profiles should be contrasted.

A comparison of the performance of FPGA compared to GPU for image processing applications, then, is a pressing business requirement for Thales. This can be split into a commercial side — studying hardware costs, design time and expenditure, and how to manage longevity — and a technical one. The technical study would use one or more signal processing tasks to investigate the relative performance of FPGA and GPU in the three metrics of power, latency and accuracy, as these have direct and indirect effects on SWaP.

We concentrate on the technical question in this thesis. Previous comparisons have been reported in the literature, and are discussed in Chapter 2. These assume a direct choice between a single FPGA and GPU in a system. We wished to build on this earlier work by characterizing the performance of a joint system containing three processors: FPGA, GPU and Central Processing Unit (CPU). Such a system, if built today, would have little integration between the different accelerator types; the complexity of data transfer between devices has already been demonstrated [14]. However, commercial embedded devices containing both reconfigurable logic and manycore processors on the same platform are now becoming available (such as the Parallella<sup>5</sup>). In the near future, integration of these devices on the same die can be expected, and this approach could offer substantial performance and SWaP improvements.

<sup>&</sup>lt;sup>5</sup>http://www.parallella.org/board/

### 1.3 Aims

To summarise our dual motivations from the previous section, we wish to investigate the performance of processing architectures capable of pedestrian and vehicle detection, within a surveillance context. Conceptually, we use a vehicle with some onboard processing capability as a target platform, while keeping in mind its power constraints.

Our commercial motivations involve ascertaining the best architecture to run such a system on, and also whether or not a system with multiple heterogeneous processors outperforms *e.g.* a single-GPU one. As we argue in the previous section, knowledge gained from studying this problem has implications for defence and civilian applications, and is both relevant and timely. We thus apply our academic and industrial motivations to a specific problem within the field of surveillance.

This work aims to answer two questions:

- 1. "How does the performance of an algorithm when partitioned temporally across a heterogeneous array of processors compare to the performance of the same algorithm in a singly-accelerated system, when considering a real-world image processing problem?"

- 2. "What is the optimal mapping of a set of algorithms to a heterogeneous set of processors? Does this change over time, and does a system with this architecture offer any advantage in a real-world image processing task?"

We answer these in detail in Chapters 5 and 6 respectively, while the remainder of this thesis places this in more context and provides details of the underlying hard-ware which these results depend on. Chapter 5 considers the effects on performance of partitioning parts of a single algorithm, while Chapter 6 addresses the same topic at task level.

Note that throughout this work we refer to "real-time" operation. This uses the "soft" definition of real-time computing, where results received after a deadline are less useful. In a "hard" real-time system, failure to generate results by a deadline would be catastrophic. We use the frame rate of 30 frames per second, and accept a small measure of latency during processing.

#### 1.4 Knowledge Transfer

#### 1.4.1 Research Outputs

- A workshop paper [15] was presented at the Workshop on Smart Cameras for Robotic Applications at the IEEE Conference on Intelligent Robots and Systems in 2012.

- This was followed by a longer journal paper "Characterising a Heterogeneous System for Person Detection in Video using Histograms of Oriented Gradients: Power vs. Speed vs. Accuracy" [16], based on the work carried out in Chapter 5. This was published in a special issue on Smart Cameras in the IEEE Journal of Selected and Emerging Topics in Circuits and Systems.

- An invited talk on the subject of "Power, Speed and Accuracy Tradeoffs: Characterising a Heterogeneous System for Person Detection in Video using HOG" was given at a BMVA Symposium on "Vision in an Increasingly Mobile World", in May 2013.

- A paper was presented at the International Conference on Computer Vision Theory and Applications, in January 2014. This was based on the work in Chapter 6, titled "Event-Driven Dynamic Platform Selection for Power-Aware Real-Time Anomaly Detection in Video" [17]. This was accepted for a full oral presentation.

#### 1.4.2 Knowledge Transfer within Thales

Thales Research and Technology, the research division within the multinational Thales Group, hosts an annual research day called "Journee de Palaiseau". This allows PhD students seconded to various divisions and countries within Thales, who are working on a common theme defined as "Software and Critical Information Systems", to present updates to their work and explore opportunities for collaboration. Work from this thesis was presented at these days on two occasions. Based on this, the algorithms discussed within this thesis were considered for implementation on another hardware architecture platform developed within Thales. This involved undertaking training on the Ter@pix architecture and the steps required to evaluate its performance on an algorithm. This occurred both at a low level, involving

(a) Power consumption given priority

(b) Processing time given priority

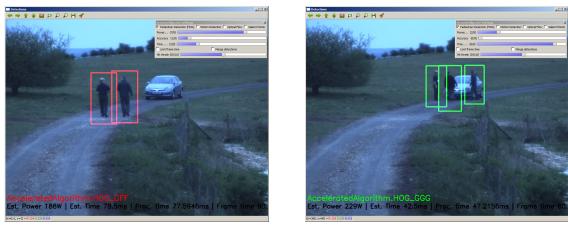

Figure 1.3: Screenshots of demonstration platform with user-driven selection of performance priorities. In (a), increasing the priority of "Time" causes algorithm processing to be moved from FPGA to GPU. This increases speed at the expense of power consumption, as shown at the bottom of (b).

*operators* (analogous to Compute Unified Device Architecture (CUDA) kernels or basic image processing steps), and a higher algorithmic level, involving operator performance, data processing capacity and host/device transfer characteristics. Ultimately, the Ter@pix platform was not used in this project, but this is discussed further in Chapter 3 and Chapter 7.

A demonstration of the dynamic architecture selection parts of this thesis (a userdriven version of the system described in Chapter 6) was also given at a Thales Research Day, in conjunction with another student's work. In this technology demonstrator, emphasis was given to changing power, time and accuracy priorities and their effect on dynamic selection of algorithm implementations within a system. Examples of this are shown in Figure 1.3. A main theme in other work shown at this exhibition was products to improve Intelligence, Surveillance, Target Acquisition, and Reconnaissance (ISTAR). These were demonstrated to various customers of Thales in the defence and security sectors, and conveyed Thales' capability for system development in the future. The demonstration we gave also fitted within this broad theme.

Throughout this project, several presentations were also given to engineers and managers within Thales to inform them about current research developments, and

to receive feedback on potential approaches for future work. Finally, priorities for future architecture and system-level research within Thales have been identified based on the conclusions from work documented in this thesis.

#### 1.5 Contributions

The key contributions of this thesis are as follows:

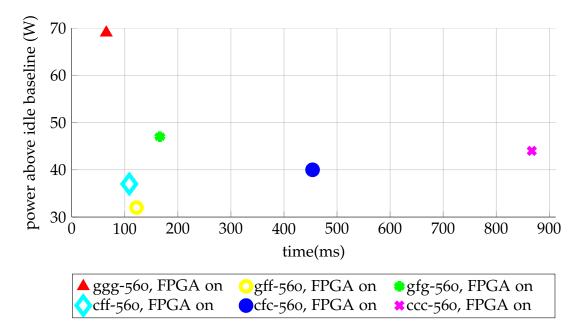

- We give a comprehensive analysis of the performance of a complex signal processing algorithm when applied to a platform with multiple heterogeneous accelerators (FPGA and GPU). Taking into account processing time, power consumption and accuracy, we show the cost (in absolutes and in percentage change from best measurement for that characteristic) of trading one of these against the other. An example of this is shown in Figure 1.4.

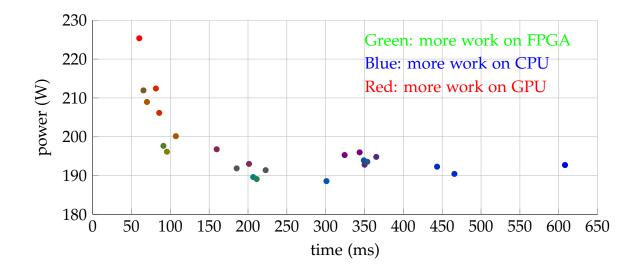

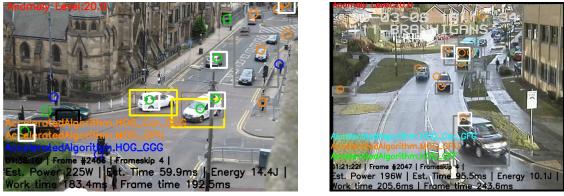

- We construct and describe the performance of a real-time image processing system for anomaly detection. This is capable of detecting vehicles parked in prohibited locations, as shown in Figure 1.5. This system responds to events within a scene by dynamically modifying the arrangement of processing elements it uses and and hence its power consumption characteristics. From this we show a clear tradeoff of event detection accuracy against power consumption. We also show the tradeoffs made when moving algorithm subtasks between heterogeneous processors; see Figure 1.6.

#### 1.6 Thesis Roadmap

The remainder of this thesis is laid out as follows:

• **Chapter 2** describes related work. This covers the architecture of the various processors used, examples of their use in image processing to date, and relevant object and anomaly detection algorithms used throughout the thesis. We also consider techniques for mapping algorithms to architecture.

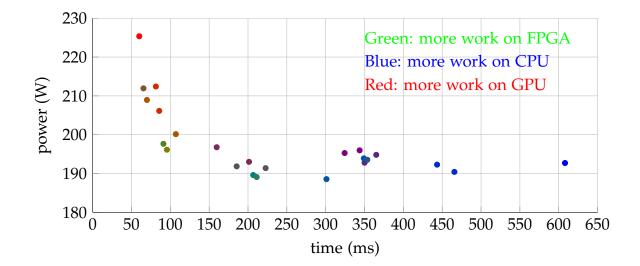

Figure 1.4: Run-time design space exploration: power vs. time for various implementations of HOG pedestrian detection using a GPU and FPGA. Power consumption shown as increase over baseline of 147W. Each version shown here can be selected at runtime. Letters denote the architecture which each algorithm segment is run on; *e.g.* for *gff*, resizing is done on GPU, followed by feature extraction and classification on FPGA.

Figure 1.5: Real-time anomaly detection. The van parked on the left-hand side of the road is highlighted with a red square, signifying an anomaly. The overlaid text shows current system performance characteristics.

- Figure 1.6: Power and time plots of all possible solutions for car, pedestrian and motion detectors across FPGA and GPU. A mainly red dot indicates most processing is done on GPU, while a dot closer to green indicates most processing is done on FPGA.

- **Chapter 3** moves on from the academic literature to consider implementation details. We explore a simulation-oriented compared to a hardware-only approach and consider whether image segmentation is required. We then focus on our choice of heterogeneous processors and discuss algorithms for exploring design space.

- **Chapter 4** is shaped by the previous chapter, and documents the system architecture we will use to perform real-time detection and hence surveillance. We give specifications of the processors used and discuss the interface for data transfer between them.

- **Chapter 5** uses the system constructed in the previous chapter. Here we perform an in-depth study of the performance characteristics which result from implementing the Histogram of Oriented Gradients algorithm for pedestrian detection on a system of heterogeneous processors: FPGA, GPU and CPU. We analyse the algorithm, identify the different types of computation involved in each stage of the algorithm (resizing, feature extraction and classification), and justify our approach to partitioning computation between architectures in this way. We then report power, accuracy and latency numbers for each of six

arrangements, and the tradeoffs involved in moving between arrangements: i.e. *if power consumption is reduced by* 10%, *how much longer does processing take?*

- **Chapter 6** builds on the work of Chapters 4 and 5 and describes a system for anomaly detection in video. This performs detection of parked vehicles in real time by dynamically allocating parts of the detection algorithms onto each processor (FPGA, GPU and CPU) depending on the level of anomaly seen in the frame. Again, we explore the performance of Histogram of Oriented Gradients (HOG) when running both car and pedestrian detections, and show the resulting tradeoffs between power, accuracy and processing time. As this system operates in real time, we concentrate on power and accuracy; *if power consumption is reduced by 10%, how many more parked vehicle events will be missed?*

- **Chapter 7** concludes this thesis. Here we summarise the key points of each chapter and highlight relevant results. We finish with a short discussion on directions for future work.

Note that in system architecture and processing diagrams throughout this thesis, we have tried to use a consistent colour scheme. Yellow boxes signify operations carried out on FPGA or the FPGA itself. Similarly, blue boxes represent GPU operations, red ones refer to work done on CPU, and green boxes represent accesses to host memory from any device.

## 2. Related Work

The problem of obtaining real-time performance from sophisticated image processing algorithms operating on large quantities of data is important and timely. This is evidenced by the ongoing focus of both industrial and academic research and development. In this chapter dealing with existing literature, we cover four relevant topics as part of this problem:

- 1. current hardware architectures for generalised and parallelised data processing and approaches to programming them;

- *2. a description of certain processing-intensive image processing algorithms for object detection and classification;*

- 3. a survey of higher-level algorithms for scene surveillance and anomaly detection;

- 4. *a review of approaches taken to the problem of assigning algorithms to a hardware platform.*

Following this, we summarise and restate the problem around which this thesis is centred; that of dynamic mapping of algorithms to hardware.

### 2.1 Data Processing Architectures

In recent years, computer architectures designed for massively-parallel data processing have become more widespread and affordable; alongside this, embedded versions of these same processors have become available. Using these, tasks such as face detection [19], which would have been infeasible in real-time ten years ago, are now performed in realtime within most consumer cameras and mobile phones [20].

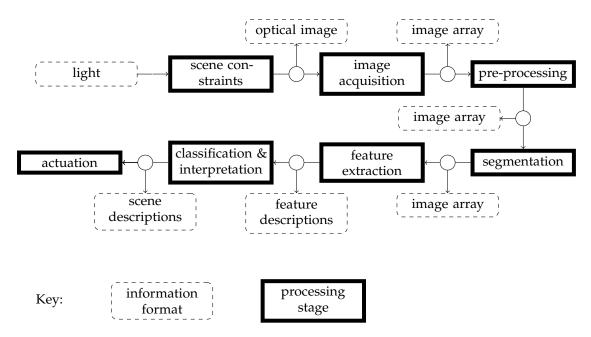

Figure 2.1: Image Processing Pipeline (from Awcock & Thomas [18]). Each stage in the pipeline can be considered another layer of abstraction.

We now review the various platforms for algorithm acceleration which were either used or considered for use in this work. Any implementation of an algorithm on one or more of these platforms will exist at some point in *design space*. This is defined as a multidimensional space with dimensions specific to the problem at hand, such as power consumption, chip area, ease of programming, processing time, and accuracy of result [21].

#### 2.1.1 Processor Taxonomy

We start by considering the domain of image processing algorithms in more detail. Figure 2.1 shows a standard machine vision processing pipeline, as described by Awcock and Thomas in 1995, and still widely in use today [18]. Applying the *Berkeley dwarves paradigm* to this pipeline is instructive.

The Berkeley dwarves are defined as "algorithmic method[s] that capture a pattern of computation and communication" which "present a method for capturing the common requirements of classes of applications while being reasonably divorced from individual implementations" [22]. The original seven computational dwarves were: dense and sparse linear algebra, spectral methods, n-body methods, structured and unstructured grids and Monte Carlo methods. In a wide-ranging technical report from Berkeley, Asanovic *et al.* renamed Monte Carlo to the more general MapReduce, and extended this list to thirteen to include combinational logic, graph traversal, graphical models, finite state machines, dynamic programming and backtrack and branch-and-bound.

These dwarves were based on a generalisation of existing benchmarks; this approach allows classification of signal processing operations into groups. The most relevant dwarf to image processing is arguably dense linear algebra (vector-vector, matrix-vector and matrix-matrix operations). Specifically, all processing operations described in the rest of this thesis use dense linear algebra. The only exception is the trajectory clustering algorithm described in Chapter 6 which we class as graph traversal (object property search, involving "indirect table lookups and little computation"). However, this is not computationally demanding enough to consider as a candidate for acceleration.

Other researchers note that vision processing is inherently parallel, and is one of the application domains described as "embarrassingly parallel" [23, 24], especially the early pixel-processing operations found when working at low levels of abstraction. Embarrassingly parallel applications are those which have "a high degree of parallelism and it is possible to make efficient use of many processors, [but] the granularity is large enough that no cooperation between the processors is required within the matrix computations" [25]. This situation is where Amdahl's law [26] applies:

$$s = \frac{1}{r_s + \frac{r_p}{n}},\tag{2.1}$$

where the speedup *s* is determined by the ratio of the parallel section of code  $r_p$  to the serial portion  $r_s$ , in a system containing *n* parallel processors. For large *n*, the proportion of sequential code limits the overall speedup available.

Returning to the pipeline, the greatest potential for parallelisation is in its early stages: preprocessing, segmentation and feature extraction, where the same operations are performed on most pixels. Here the system must handle large volumes of data quickly; several operations are often required for each pixel, of which there can be millions in a single frame. Real-time processing requires doing this dozens of times per second, which leaves only a few nanoseconds to process a single pixel [27]. Moving from the problem domain to the hardware domain, in this section we

|                             | FPGA                | GPU            | X86 SSE        | Multicore CPU  |

|-----------------------------|---------------------|----------------|----------------|----------------|

| Power<br>Consumption        | low                 | high           | medium         | medium         |

| Clock Speed                 | low                 | medium         | high           | high           |

| Ease of<br>Programming      | hard                | medium         | low            | low            |

| Speed gain                  | high                | high           | medium         | medium         |

| Floating-point<br>Precision | arbitrary,<br>fixed | single/ double | single/ double | single/ double |

Table 2.1: Summarised comparison of data processing architectures (compared to a reference x86).

consider various candidate architectures, the structure of each one, methods of programming, and any other relevant information.

The processing architectures themselves can be arranged using Flynn's taxonomy, which categorises systems into the groups below [28].

- **SISD** Single instruction single data: normal single-core processors, *e.g.* a single core of an x86 chip.

- **SIMD** Single instruction multiple data: Flynn puts systems which express parallelism both temporally (via pipelining) and spatially (via multiple discrete processing elements) in this category. This includes x86 Streaming SIMD Extensions (SSE) vectorisation, GPUS and FPGAS.

**MISD** Multiple instruction streams working on a single data stream.

**MIMD** Multiple instruction multiple data: independent multiprocessor systems with some level of shared memory *e.g.* multicore processor systems.

This is summarised in Table 2.1. We now consider each architecture in that Table in detail.

Figure 2.2: SIMD register structure in modern x86 processors. Eight 128-bit registers (right) can be used by the vector processing unit (left) for packed fixedand floating-point operations.

# 2.1.2 Methods for CPU Acceleration

Intel and derivative x86 processors provide a SIMD vectorisation unit which works on 128 bits of data (see Figure 2.2). For *e.g.* single-precision floating point calculations, this can offer an up to  $4 \times$  speedup in arithmetic and logic operations. This is an example of SIMD parallelism and does not require much hardware knowledge to apply; in certain circumstances, certain compilers can automatically vectorise code to make best use of this hardware.

Multithreading can also be used to spread work out over multiple cores and hide processing stalls while waiting for memory or 1/0 operations to complete, although in general this speedup is limited as only a few cores are available to share the work onto.

#### 2.1.3 Graphics Processing Units

The General-Purpose Graphics Processing Unit (GPGPU or GPU) grew out of the increasing computational power available in consumer graphics cards in the mid-2000s, along with changes in the way these cards could be programmed. They have become very prevalent in the area of high-performance computing, so much so that the current Top 500 list of supercomputers contains 39 systems which are CUDA-accelerated<sup>1</sup>. Early literature on GPU computing, such as a review by Owens *et al.* [29] in 2007, framed all processing operations in computer graphics terms, such as vertex buffers, fragment processors and texture memory, and relied on custom languages such as Cg and Brook. In their review the following year [30], the same authors noted that "One of the historical difficulties in programming GPGPU applications has been that despite their general-purpose tasks having nothing to do with graphics, the applications still had to be programmed using their graphics Application Programming Interfaces (APIS)". GPU-accelerated research work on certain applications was done at this point (for example on particle filtering [31]), but problems such as the floating-point calculations not conforming to the published IEEE standard were still prevalent [32].

That changed with the advent of NVIDIA'S CUDA<sup>2</sup> and the Khronos Group's crossplatform OpenCL<sup>3</sup>, two general-purpose C-based languages designed to expose the underlying parallelism in GPUS. Both function on the basis of *kernels*, processing functions applied to *streams* of data. As CUDA was the language used in this work, we focus on that; the extensions to CUDA beyond standard C mostly relate to choosing which architecture to run a kernel on (host or device), and arrangements for partitioning and accessing data between processing elements. Rather than using one of Flynn's taxonomy entries [28] to describe their architecture, NVIDIA describe CUDA as Single Instruction Multiple Thread, similar to SIMD.

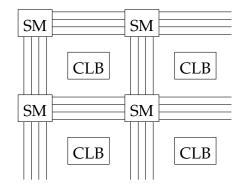

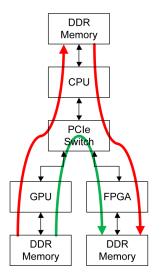

An overview of CUDA architecture is shown in Figure 2.3; multiple Stream Processors (SPS), each with their own arithmetic and logic unit, make up a Streaming Multiprocessor. Within a Streaming Multiprocessor (SM), each SP can share data with its neighbours using a small amount of shared memory, very close to the SM and hence fast to access. Multiple SMS are arranged on chip, with each SP also being able to access slightly slower global memory (on the same board as the GPU) and, with even more latency, the host PC's main memory (Figure 2.3b). This memory hierarchy also has two levels of caching (not shown), which is managed automatically, and from the point of view of the programmer, the same mechanism is used to access the various types of memory (shared, texture, global, and host). Each SM is scheduled to run multiple groups of processing threads simultaneously; the central idea behind this architecture is that context switching between threads on a SM is very fast, and

<sup>&</sup>lt;sup>1</sup>Details at http://www.top500.org/lists/2013/06/highlights/

<sup>&</sup>lt;sup>2</sup>Available from https://developer.nvidia.com/what-cuda

<sup>&</sup>lt;sup>3</sup>Available from http://www.khronos.org/opencl/

(a) Structure and memory interface of a streaming multiprocessor in a CUDA GPU.

Figure 2.3: CUDA Architecture: (a) multiple stream processors (SP) make up a streaming multiprocessor (SM) and have access to a small, fast shared memory region. (b) SMS are arranged within a GPU and can access global device and host memory.

low cost, so thousands of threads can be queued for execution at once across a card. A group of 32 threads executed on an SM is known as a *warp*, and in the latest generation of chips, up to 32 warps can be queued at once. Thus, the inefficiencies involved in multiple levels of memory access will be hidden, because while one warp waiting for data access is stalled, another which requires processing can be run in its place. Despite this technique for *latency hiding*, memory accesses are still slower than processing operations, and CUDA cards obtain their best performance when performing lots of operations on a limited amount of data, *i.e.* maximising the ratio of computations to data transfers. This is a very brief overview of the CUDA architecture, focusing on the main benefits for general-purpose computing: a comprehensive description is given in [10].

#### Application to Image Processing

GPUS have now become mainstream in accelerating a wide variety of signal processing applications. There are numerous utilities available to help this process, such as specific linear algebra (cuBLAS) and fast Fourier transform (cuFFT) libraries and image and signal processing primitives (NPP). The most well-known in the vision community is probably OpenCV<sup>4</sup>, a general image processing library in which a large number of algorithms are now GPU-accelerated. This includes algorithms for segmentation [33, 34], Viola and Jones' face detection work [19, 35, 36] and medical imaging applications [37], many of which have now been incorporated into OpenCV as summarised in [38]. A general theme among these publications is that some level of knowledge of the hardware is required to gain a speedup.

Mobile devices which are CUDA or OpenCL-capable have increased the potential for deployment of algorithms such as these on handheld platforms; accelerated SIFT (Scale Invariant Feature Transform) for descriptor generation by Wang *et al.* [39] is one recent example of this.

## 2.1.4 Field-Programmable Gate Arrays

One of the alternatives to mapping large computations to a fixed hardware architecture is to adapt that hardware to the processing required – hence the appearance of FPGAs. The concept of a reconfigurable parallel processing system was first described in the 1960s by Estrin *et al.* [40], and is similar in form to modern Xilinx and Altera devices. As Xilinx FPGAs hold around 50% of the market share<sup>5</sup>, and Xilinx devices were used within Thales, we concentrate on Xilinx devices here. However, everything discussed in this section is true for alternatives such as Altera as well.

The structure of a modern FPGA is shown in Figure 2.4. Processing is done by programming Combinatorial Logic Blocks (CLBS), as shown in Figure 2.4a, to perform application-specific logic functions. These CLBS contain programmable look-up tables followed by a storage element (flip-flops). They are connected by programmable switch matrices. Modern heterogeneous devices also contain commonly-used elements such as blockRAMS and embedded multiplier-accumulators (DSP48s in Xilinx terminology), allowing the CLBS to be used for other operations. All programmable elements within the device are configured at bootup time by pushing a *configuration bitstream* through a set of configuration registers on the chip. FPGAS may also contain specialised high-speed transceiver blocks for communications, and allow general-purpose processors to be instantiated on the fabric, whether designed for close integration with the chip (such as a Microblaze [41]) or not [42].

<sup>&</sup>lt;sup>4</sup>http://opencv.itseez.com

<sup>&</sup>lt;sup>5</sup>See http://www.xilinx.com/about/company-overview/

(a) Combinatorial logic blocks (containing look-up tables and storage elements) are connected by a configurable switch matrix.

(b) Heterogeneous FPGA containing fabric, blockRAM and embedded multipliers.

Figure 2.4: FPGA Architecture: (a) CLBS are connected by switch matrices. (b) Other components such as memory and embedded multipliers can also be incorporated on-chip.

#### Programming

An overview of the whole FPGA programming process is given by Bacon *et al.* [43]. Programming an FPGA, particularly when starting with an existing signal processing algorithm, has been described as "very time consuming" by Bailey [44]. This is especially true when considering traditional methods of capturing designs at Register Transfer Level (RTL), using Verilog or VHDL; this step has also been described by Johnston *et al.* as "difficult and cumbersome for large and complex algorithms" [27]. The gulf between a high-level algorithm description as described by MATLAB code, and one written in RTL is quite large, especially if any changes must be made to the original design. This has led to multiple methods for programming FPGAs from a high-level language or model (model-based design). Zoss *et al.* [45] compare various extensions to MATLAB which allow production of bitstreams from a Simulink model. They note that manufacturer tools (*e.g.* Xilinx System