# Coordination of Mechanical DCCBs and Temporary Blocking of Half Bridge MMC

M. Zaja, D. Jovcic

University of Aberdeen, United Kingdom, m. zaja@abdn.ac.uk, d.jovcic@abdn.ac.uk

Keywords: MMC, HVDC, dc grid protection, DCCB

#### **Abstract**

This paper proposes a dc grid protection strategy based on temporary MMC blocking in combination with mechanical DCCBs on dc lines. MMCs are blocked for only a short period of time while DCCBs operate and resume operation afterwards. A comparison is made with a protection strategy in which MMC blocking is avoided. The study analyses the impact of dc faults on dc power flow, ac system, DCCB dimensioning and MMC's antiparallel diodes. Operation is demonstrated on a point-to-point HVDC and a three-terminal dc grid, also using thermal model of MMC's IGBT module. Main benefits of the proposed strategy are simplicity and low protection system cost. On the downside, antiparallel diodes are exposed to greater current and thermal stress.

# 1 Introduction

The vulnerability of half-bridge (HB) modular-multilevel converters (MMCs) to dc faults remains one of biggest challenges in dc grid development [1]. When a dc fault occurs, MMC's dc current rises rapidly and MMC blocks to protect insulated gate bipolar transistors (IGBTs) against high currents. A blocked MMC acts like a diode bridge rectifier and cannot control voltage, current or power on either ac or dc side. Meanwhile, ac system continues to feed fault current through MMC's antiparallel diodes until the fault is isolated. This exposes the diodes to substantial current and thermal stress.

Because of negative consequences of converter blocking, methods for avoiding converter blocking are being explored. Fault-tolerant converters such as full-bridge (FB) MMC [1, 2] can suppress fault current but require a greater number of switches compared to HB MMC. This not only increases the cost but conduction losses as well [3]. Another option is to use large DCCB inductors to maintain fault current within rated values for the duration of DCCB opening [4, 5] but this approach increases stored magnetic energy in normal operation and can cause stability issues [6]. Moreover, required inductor size increases significantly with DCCB opening time [7] and costly hybrid DCCBs (HCBs) [8] need to be employed instead of cost-effective mechanical DCCBs (MCBs) [9, 10]. Ac-side LCL filters [11] can suppress fault current contribution from the ac grid but lead to increased conduction losses at partial loading. Superconductive fault current limiters [12, 13] can reduce MMC's fault current and do not impact grid dynamics

in normal operation but technology is complex, immature and lacks substantial field experience.

This paper proposes a dc protection strategy based on temporary MMC blocking. As shown in [14], it is possible to block the converter during DCCB operation and quickly reestablish the power flow afterwards. If power recovery is fast enough, the impact on ac system stability is negligible even if a large converter is disconnected [15]. Main benefits of this approach are simplicity and low protection system cost. The proposed strategy will be demonstrated on a three-terminal dc grid and compared against a protection strategy where blocking is avoided. Thermal valve model is required to assess thermal stress on MMC's antiparallel diodes.

# 2 Temporary MMC blocking

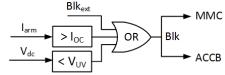

Conventional MMC blocking logic is shown in Figure 1. It consists of overcurrent and undervoltage protection, as well as manually controlled external blocking signal. Manual blocking  $Blk_{ext}$  is used to trip the converter in exceptional circumstances by the grid operator and will not be discussed further. Overcurrent protection activates when MMC's arm current  $I_{arm}$  exceeds maximum operating current of IGBTs  $I_{OC}$ , typically twice the rated current. Undervoltage protection blocks the converter when its dc voltage  $V_{dc}$  falls below the diode bridge voltage  $V_{UV}$  (defined by the connected ac system), typically at 80 % of nominal dc voltage. Blocking the converter instantaneously turns all of its transistors off and sends an opening command to ACCBs. As ACCB opens, the whole converter station becomes de-energized and it might take up to several minutes to restart the converter.

Figure 1: Conventional MMC blocking schematic

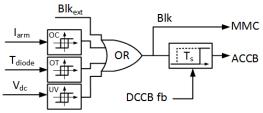

The proposed temporary blocking logic is shown in Figure 2. Unlike with conventional blocking, temporary blocking does not immediately trip ACCBs. Instead, ACCB trip command is suppressed for the duration of DCCB opening plus a safety margin ( $T_s$ ) to confirm that DCCB opened successfully. If confirmation (DCCB fb) is received, ACCB trip is cancelled. However, if confirmation does not arrive within the specified time period, DCCB failure is assumed and ACCBs are tripped in addition to all DCCBs participating in backup protection.

Figure 2: Proposed MMC blocking schematic for temporary blocking

Overcurrent and undervoltage protection are implemented using hysteresis control. This ensures that currents and voltages return to their normal limits before the converter deblocks and prevents unwanted triggering during oscillatory transients. Overcurrent (OC) blocking and de-blocking thresholds are 2.0 and 1.1 p.u. respectively while undervoltage (UV) blocking and de-blocking thresholds are 0.8 and 0.82 p.u. Because MMC blocking exposes MMC's antiparallel diodes to high currents, their temperature is monitored to ensure MMC does not resume operation if diodes are overheated. Overtemperature (OT) protection thresholds are 125 and 95 °C.

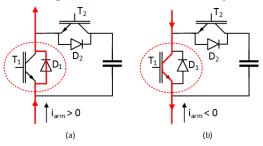

#### 3 Thermal valve model

Blocking the converter under a dc fault exposes its antiparallel diodes to high surge currents. The diodes heat up due to increased conduction losses which can cause permanent damage if diodes' thermal limits are exceeded. Therefore, it is critical to evaluate temporary blocking from not only electrical but thermal viewpoint as well. Figure 3 shows a single HB MMC cell with the IGBT module of interest. In normal operation, arm current passes through the module if the cell is off (capacitor bypassed).  $D_1$  conducts if arm current is positive while  $T_1$  conducts if arm current is negative. When a fault occurs and MMC blocks,  $D_1$  takes full surge current and, because of diode bridge operation, conducts until the fault is cleared. Therefore,  $D_1$  is exposed to highest thermal stress and peak module temperature will be observed at its junction.

Figure 3: Half bridge MMC cell

Junction temperature of  $D_1$  is a product of three factors:

- 1. Fault current passing through  $D_1$

- 2. Pre-fault current passing through  $D_1$

- 3. Pre-fault current passing through  $T_1$

Factor number 3 occurs because  $D_1$  and  $T_1$  are part of the same package and some of the heat generated by  $T_1$  transfers to  $D_1$  even though  $D_1$  is not conducting. This is known as diode-IGBT cross-talk [16]. While the converter is operating, each MMC's arm consists of both inserted (on) and bypassed (off)

cells at any point in time. The number of on and off cells in each arm is determined by the modulation index while the selection of inserted and bypassed cells is made by the energy balancing algorithm. Therefore, each cell spends a portion of time off and a portion of time on in normal conditions. However, in protection studies such as this one, worst case scenario needs to be considered. For each arm of the MMC, it will be assumed there is at least one permanently bypassed cell where  $T_1$  and  $D_1$  conduct at all times, depending on arm current direction. This yields highest theoretical operating temperature of IGBT modules in normal operation.

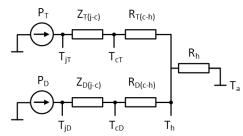

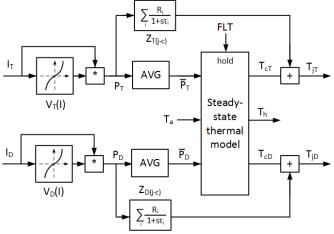

Equivalent thermal circuit of the IGBT module is shown in Figure 4 [16, 17]. Power sources  $P_T$  and  $P_D$  represent conduction losses of the IGBT and diode respectively. Switching losses are neglected because it is assumed the cell is permanently bypassed.  $Z_{T(j-c)}$  and  $Z_{D(j-c)}$  represent junction-to-case thermal impedances of the IGBT and diode,  $R_{T(c-h)}$  and  $R_{D(c-h)}$  thermal resistance between the case and heat sink for IGBT and diode and  $R_h$  represents thermal resistance between the heat sink and ambient.  $T_{jT}$  and  $T_{jD}$  represent junction temperatures of IGBT and diode while  $T_{cT}$  and  $T_{cD}$  represent their respective case temperatures. Heat sink temperature is denoted by  $T_h$  while  $T_a$  stands for ambient temperature.

Figure 4: Equivalent thermal circuit of the IGBT module

Steady-state temperatures are calculated as

$$T_h = (\bar{P}_T + \bar{P}_D) \cdot R_h + T_a \tag{1}$$

$$T_{cT} = \bar{P}_T \cdot R_{T(c-h)} + T_h \tag{2}$$

$$T_{cD} = \bar{P}_T \cdot R_{D(c-h)} + T_h \tag{3}$$

$$T_{iT} = \bar{P}_T \cdot Z_{T(i-c)} + T_{cT} \tag{4}$$

$$T_{jT} = \bar{P}_D \cdot Z_{D(j-c)} + T_{cD} \tag{5}$$

where  $\bar{P}_T$  and  $\bar{P}_D$  represent average conduction loss of semiconductors. These formulas suffice for load-flow studies where the average power loss changes slowly. However, to accurately calculate junction temperatures during fast transients such as dc faults, transient thermal impedance needs to be considered [16, 17]. This impedance (junction-to-case) is provided by manufacturers as an analytical function, also known as Foster model:

$$Z_{(j-c)}(t) = \sum_{i}^{n} R_{i} (1 - e^{-\frac{t}{\tau_{i}}})$$

(6)

The advantage of Foster model is that a typically very complex physical model can be simplified to a sum of first-order filters with gain  $R_i$  and time constant  $\tau_i$ . However, because these coefficients have no physical meaning, the model comes with

some limitations, namely that series connection with other thermal circuit elements yields inaccurate results in the lower time regime [16]. This occurs because Foster model is realized as a series connection of RC elements and power flow at the input always equals power flow at the output. In an actual physical system, input and output power flow differ because some of the heat is absorbed by module's thermal capacitance. This is particularly prominent during fast transients where capacitive component is dominant. Applied to the circuit in Figure 4, this means that majority of excess heat is absorbed by the junction layer during dc faults instead of being passed through the case and heat sink.  $R_{T(c-h)}$ ,  $R_{D(c-h)}$  and  $R_h$  should not contribute to a rise in junction temperature if no heat flows through them in an actual physical system but that would be the case if Foster model was inserted directly into the circuit.

To surpass these limitations, a two-step approach is proposed. Since the observed timeframe for protection system operation is short (tens of milliseconds), it can be assumed that case and heat sink temperatures remain fairly constant during this period [16]. Therefore, the model can be divided in two parts: calculating steady-state temperatures and calculating transient temperature increase under dc faults. The resulting thermal valve model is shown in Figure 5. Instantaneous conduction losses are calculated from IGBT and diode currents using I-V curves provided by the manufacturer. Average power loss is fed into the steady-state thermal model where case and heat sink temperatures are calculated using (1)-(3) while instantaneous power loss is fed into the Foster model to obtain junction-to-case temperature difference. When a fault (FLT) is applied, thermal circuit's outputs are frozen to prevent an unrealistic jump in case and heat sink temperatures. The benefit of this approach is that case and heat sink temperatures adjust with the operating point of the MMC and cross-talk is also taken into account. Meanwhile, manufacturer-provided Foster model is used for accurate transient temperature calculation.

Figure 5: Proposed thermal valve model

# 4 IGBT module selection

Thermal model parameters are taken from ABB press-pack 5SNA 2000K450300 datasheet [18]. The module's operating limit is 125 °C while thermal limit is 150 °C. Press-pack IGBT modules have much lower thermal impedance compared to

conventional modules [19] so bypass thyristors [20], installed to protect diodes against high currents, might not be needed. In point-to-point VSC-HVDC, MMC's diodes are dimensioned to withstand short circuit current for the duration of ACCB opening. It is assumed that same design principles apply to MMCs in dc grids. To evaluate IGBT module selection, 1 GW,  $\pm$  320 kV VSC-HVDC system shown in Figure 6 is developed in PSCAD. MMCs are modelled using the average value model while cable uses the frequency dependent model. Main system parameters are given in Table 1 and base per-unit parameters in Table 2. Both MMCs and ac systems are identical but MMC 1 controls power while MMC 2 controls dc voltage. Self-protection scheme from Figure 1 is employed with ACCB opening time of 100 ms.

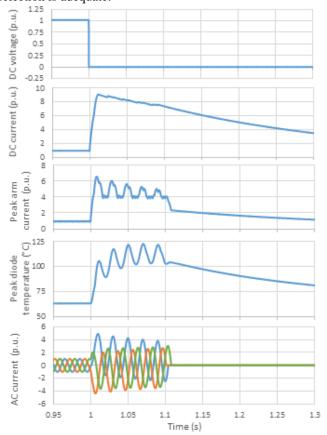

Figure 7 shows MMC 1's response for a pole-to-pole dc fault. Undervoltage protection blocks the converter almost instantaneously and trips ACCBs which open 100 ms later. Despite arm current reaching 6.7 p.u., diode temperature remains below the operating limit of 125 °C. This is partly caused by the fact that arm current overshoots and naturally starts declining before ACCBs open and partly because IGBT module's transient thermal impedance is low for fast transients. Overall, a margin of over 25 °C is achieved with respect to module's thermal limit so it is concluded that component selection is adequate.

Figure 7: MMC 1 variables for VSC-HVDC dc fault

| Parameter                  | Value      |

|----------------------------|------------|

| MMC power rating           | 1000 MVA   |

| Nominal dc voltage         | ± 320 kV   |

| Transformer voltage rating | 372/360 kV |

| Transformer reactance      | 0.15 p.u.  |

| Nominal ac voltage         | 372 kV     |

| Nominal ac frequency       | 50 Hz      |

| Short circuit ratio        | 10         |

| X/R ratio                  | 10         |

Table 1: Test system parameters

| Parameter        | Value     |

|------------------|-----------|

| Base dc voltage  | 640 kV    |

| Base dc current  | 1.6 kA    |

| Base arm current | 1.7 kA    |

| Base ac voltage  | 303.74 kV |

| Base ac current  | 2.2 kA    |

Table 2: Base units for per-unit analysis

# 5 DC grid protection

# 5.1 Protection system design

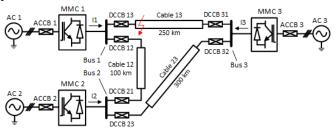

Figure 8 shows a three-terminal dc grid test system. MMC, ac system and cable modelling is identical as in section 4 with same per-unit parameters as in Table 1. MMCs 1 and 2 are rated for 1000 MVA and control power while MMC 3 is rated for 2000 MVA and controls voltage. Each cable is rated for 1 p.u. current. Ac system's RL impedance and MMC transformer are omitted from Figure 8 due to space constraints but are present in the simulation model.

Figure 8: Dc grid test system

Protection system is fully selective with each cable protected by two DCCBs. Fault detection and location is made locally using the rate-of-change-of-voltage method [21]. Each DCCB has a series inductor installed to limit the fault current slope. In case of DCCB failure, secondary protection opens the adjacent DCCB as well as ACCB. DCCB failure is detected if DCCB's current differential remains positive 1 ms after its expected opening time. ACCB opening time is 100 ms, as in section 4.

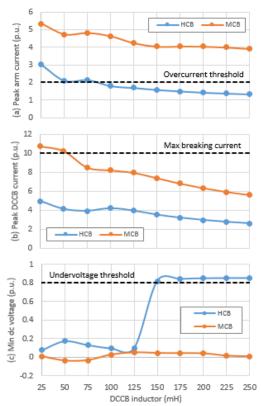

Two protection system strategies are implemented for comparison, as summarized in Table 3. The first, benchmark strategy, uses fast hybrid DCCBs in combination with larger inductors to avoid MMC blocking. The second, newly proposed strategy, uses slower mechanical DCCBs but temporary MMC blocking is allowed. The process behind inductor sizing is illustrated in Figure 9. Arm current, DCCB current and dc voltage of MMC 1 are compared against design limitations depending on inductor size and breaker type. For

strategy 1 (HCB) where blocking is avoided, all three criteria need to be satisfied. For strategy 2 (MCB), only DCCB current must satisfy. Minimal inductor sizes fitting all relevant criteria are taken, yielding 150 and 75 mH respectively. In reality, a substantial margin would be applied to DCCB inductor selection and HCBs would likely require much larger inductors.

| Strategy                  | HCB             | MCB             |

|---------------------------|-----------------|-----------------|

| DCCB type                 | Hybrid          | Mechanical      |

| DCCB opening time         | 2 ms            | 10 ms           |

| DCCB inductor size        | 150 mH          | 75 mH           |

| Max DCCB breaking current | 16 kA (10 p.u.) | 16 kA (10 p.u.) |

| MMC blocking              | Avoided         | Temporary       |

Table 3: Dc grid protection strategies

Figure 9: Protection system design variables versus DCCB inductor size

#### 5.2 Dc grid response

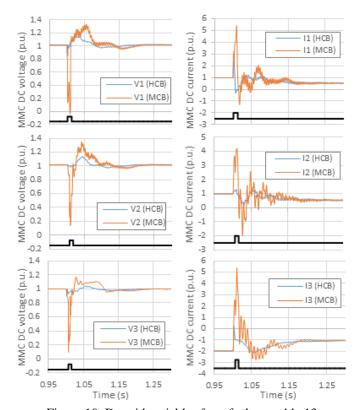

Figure 10 shows dc grid terminal voltages and currents for a fault on cable 13 for both protection strategies. After DCCBs 13 and 31 isolate the fault, MMCs 1 and 2 readjust their power output to accommodate for a change in grid topology. Black solid line indicates MMC blocking signal. Clear benefit of HCB strategy is lower current and voltage deviations and less oscillations. However, it takes roughly the same time (~200 ms) for the grid to stabilize and adjust to a new set point as with MCBs. Assuming the equipment can withstand stress in both cases, two strategies produce very similar results at system level. Terminal blocking lasts less than 12 ms during which cell capacitors preserve charge, allowing MMCs to quickly resume operation and recover from the fault.

Figure 10: Dc grid variables for a fault on cable 13

# 5.3 Impact on ac system

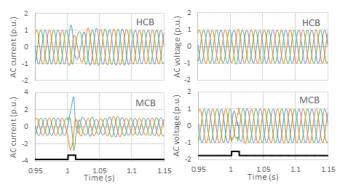

Figure 11 shows ac voltages and currents at MMC 1's point of common coupling (PCC) for a cable 13 fault. To eliminate the impact of power reference adjustment and enable fairer comparison, MMC 1's power reference is kept constant while MMC 2 adjusts for grid topology change. Using HCBs, virtually no impact on ac voltage is observed while ac current increases negligibly. With MCBs, ac voltage dips while the converter is blocked and ac current rises substantially. This could interfere with remote ac protection equipment and needs to be taken into consideration, however, such disturbance lasts only half a grid period.

Figure 11: Ac voltages and currents at MMC 1's PCC

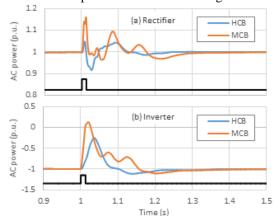

Figure 12 shows ac power under the fault for operation in (a) rectification and (b) inversion. Rectifier is substantially more fault tolerant because fault current direction coincides with the direction of d-axis current and MMC can counteract the

disturbance by reducing the modulation index. Inverter on the other hand needs to increase the modulation index which, already operating at full power, saturates the current controller. In both cases the impact is reduced if blocking is avoided.

Figure 12: Ac power at MMC 1's PCC under dc fault

#### 5.4 Impact on DCCB

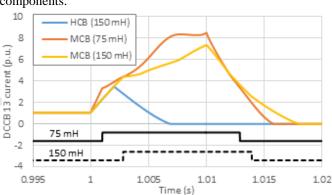

DCCB 13 current is shown in Figure 13 with an additional response where MCB and HCB use same series inductors. Prior to MMC blocking, DCCB current rises at an almost constant slope but as soon as MMC blocks, the slope significantly decreases. This occurs because MMC blocking collapses dc voltage and prevents discharging of submodule capacitors. If MMC blocking is avoided, dc voltage remains above 0.8 p.u. and drives the increase of DCCB current. The benefits of temporary blocking are demonstrated further in Table 4. Owing to much shorter opening time, HCB's energy absorption is lower than MCB's. However, MCBs are utilized more efficiently because of MMC blocking, as seen from average di/dt and average inductor voltage during DCCB opening. Given that the cost of HCB can be significantly higher than the cost of MCB [1], the reduction in energy absorption by HCBs is irrelevant since surge arresters are low-cost components.

Figure 13: DCCB 13 current for a fault on cable 13

| DCCB type                | Hybrid     | Mechanical |            |

|--------------------------|------------|------------|------------|

| Inductor size            | 150 mH     | 75 mH      | 150 mH     |

| Energy absorption        | 12.2 MJ    | 34.6 MJ    | 39.0 MJ    |

| Average di/dt            | 1.97 kA/ms | 1.19 kA/ms | 1.01 kA/ms |

| Average inductor voltage | 294.3 kV   | 89.3 kV    | 151.8 kV   |

Table 4: DCCB 13 performance indicators

#### 5.5 Impact on diode temperature

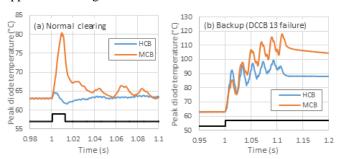

Figure 14 (a) shows peak diode temperature of MMC 1 for normal fault clearing and (b) DCCB 13 failure. In case (a) there is virtually no impact on diode temperature with HCBs because fault clearing time is very short and arm current remains below 2 p.u. Blocking strategy results in a very brief 17 °C increase so delaying de-blocking to cool down diodes is not needed. In case (b) DCCB 13 fails and the fault is cleared by DCCB 12 and ACCB 1. Both strategies yield lower peak temperature than the VSC-HVDC system despite longer protection operating time (delayed ACCB operation). This is a result of DCCB 13 inductor reducing dc current overshoot. Therefore, thermal design principles for point-to-point system are applicable to dc grids as well.

Figure 14: MMC 1 peak diode temperature for (a) normal fault clearing and (b) DCCB 13 failure

### 6 Conclusion

Dc grid protection strategy based on temporary MMC blocking allows utilization of low-cost mechanical DCCBs with small inductors. MMC blocking collapses dc voltage but preserves cell charge, reducing fault current di/dt while allowing the converter to quickly recover from the fault. On the downside, dc faults have a more prominent impact on the ac system than when blocking is avoided. Thermal stress on diodes is higher, but not as high as in VSC-HVDC systems. Therefore, same design principles can be applied to MMC's IGBT modules.

## References

- D. Jovcic and K. Ahmed, "High Voltage Direct Current Transmission: Converters, Systems and DC Grids", Wiley, 2015.

- [2] D. Jovcic, W. Lin, S. Nguefeu and H. Saad, "Low-Energy Protection System for DC Grids Based on Full-Bridge MMC Converters," in *IEEE Transactions on Power Delivery*, vol. 33, no. 4, pp. 1934-1943, Aug. 2018.

- [3] A. A. Elserougi, A. M. Massoud and S. Ahmed, "A Switched-Capacitor Submodule for Modular Multilevel HVDC Converters With DC-Fault Blocking Capability and a Reduced Number of Sensors,", *IEEE Transactions on Power Delivery*, vol. 31, no. 1, pp. 313-322, Feb. 2016.

- [4] Weixing Lin, D. Jovcic, S. Nguefeu and H. Saad, "Coordination of MMC converter protection and DC line protection in DC grids", 2016 IEEE Power and Energy Society General Meeting, Boston, MA, 2016, pp. 1-5.

- [5] D. Döring, D. Ergin, K. Würflinger, J. Dorn, F. Schettler and E. Spahic, "System integration aspects of DC circuit breakers", *IET Power Electronics*, 9 (2), pp.219-227, Feb. 2016.

- [6] W. Wang, M. Barnes, O. Marjanovic and O. Cwikowski, "Impact of DC Breaker Systems on Multiterminal VSC-HVDC Stability", *IEEE Transactions on Power Delivery*, 31 (2), pp.769-779., Apr. 2016.

- [7] M. Zaja, D. Jovcic, M. Hajian, "Capacitive element for limiting VSC fault current in DC grids", 2018 IEEE Power and Energy Society General Meeting, Portland, OR, 2018, pp. 1-5.

- [8] R. Derakhshanfar, T. U. Jonsson, U. Steiger and M. Habert, "Hybrid HVDC breaker – A solution for future HVDC system", CIGRE Session 2014, Paris, France, 2014, pp. 1-12.

- [9] T. Eriksson, M. Backman and S. Halen, "A low loss mechanical HVDC breaker for HVDC grid applications", *CIGRE Session* 2014, Paris, France, 2014, pp. 1-8.

- [10] K. Tahata, S. El Oukaili, K. Kamei, D. Yoshida, Y. Kono, R. Yamamoto and H. Ito, "HVDC circuit breakers for HVDC grid applications", 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 2015, pp. 1-9.

- [11] M. Hajian, L. Zhang and D. Jovcic, "DC Transmission Grid With Low-Speed Protection Using Mechanical DC Circuit Breakers", *IEEE Transactions on Power Delivery*, 30 (3), pp.1383-1391, June 2015.

- [12] W. R. L. Garcia, A. Bertinato, P. Tixador, B. Raison and B. Luscan, "Full-selective protection strategy for MTDC grids based on R-type superconducting FCLs and mechanical DC circuit breakers," 5th IET International Conference on Renewable Power Generation (RPG), London, 2016, pp. 1-7.

- [13] W. R. Leon Garcia, P. Tixador, B. Raison, A. Bertinato, B. Luscan and C. Creusot, "Technical and Economic Analysis of the R-Type SFCL for HVDC Grids Protection," in IEEE Transactions on Applied Superconductivity, vol. 27, no. 7, pp. 1-9, Oct. 2017

- [14] O. Cwikowski, A. Wood, A. Miller, M. Barnes and R. Shuttleworth, "Operating DC Circuit Breakers With MMC", *IEEE Transactions on Power Delivery*, 33 (1), pp.260-270, Feb. 2018.

- [15] M. Abedrabbo, M. Wang, P. Tielens, F. Z. Dejene, W. Leterme, J. Beerten and D. Van Hertem, "Impact of DC grid contingencies on AC system stability", 13th IET International Conference on AC and DC Power Transmission, 2017, pp. 1-7.

- [16] ABB, "Thermal design and temperature ratings of IGBT modules", Application note 5SYA 2093-00, Lenzburg, 2013.

- [17] ABB, "Applying IGBTs", Application note 5SYA 2053-04, Lenzburg, Switzerland, 2013.

- [18] ABB, "5SNA 2000K450300 datasheet", Lenzburg, CH, 2014.

- [19] ABB, "5SNA 1500E330305 datasheet", Lenzburg, CH, 2018.

- [20] M. Spence, A. Plumpton, C. Rout, A. Millington and R. Keyse, "Design and Characterisation of Optimised Protective Thyristors for VSC Systems," *PCIM Europe 2016;* Nuremberg, Germany, 2016, pp. 1-8.

- [21] J. Sneath and A. D. Rajapakse, "Fault Detection and Interruption in an Earthed HVDC Grid Using ROCOV and Hybrid DC Breakers", *IEEE Transactions on Power Delivery*, 31 (3), June 2016.